**ADS1118**

JAJSHX5F - OCTOBER 2010-REVISED SEPTEMBER 2019

# ADS1118 超小型、低消費電力 16 ビット A/D コンバータ、 SPI™互換インターフェイス、内部基準電圧、温度センサ付き

# 1 特長

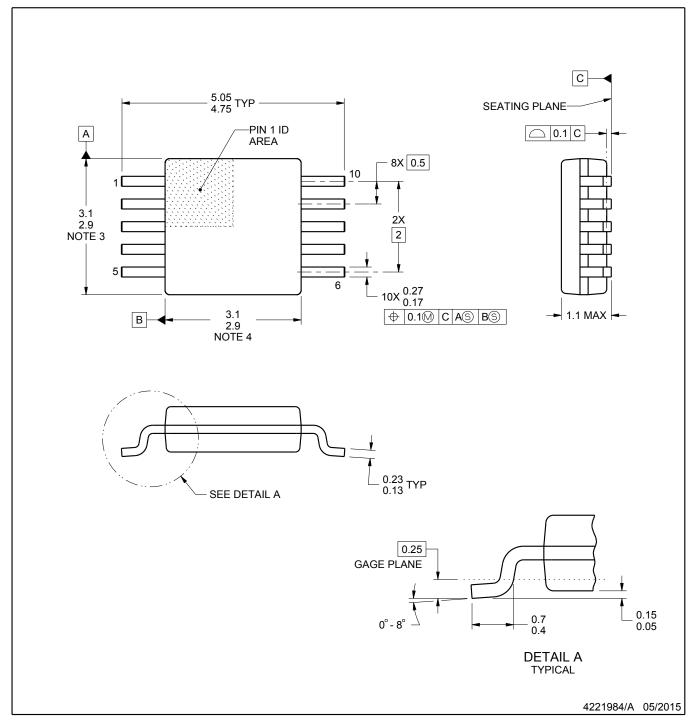

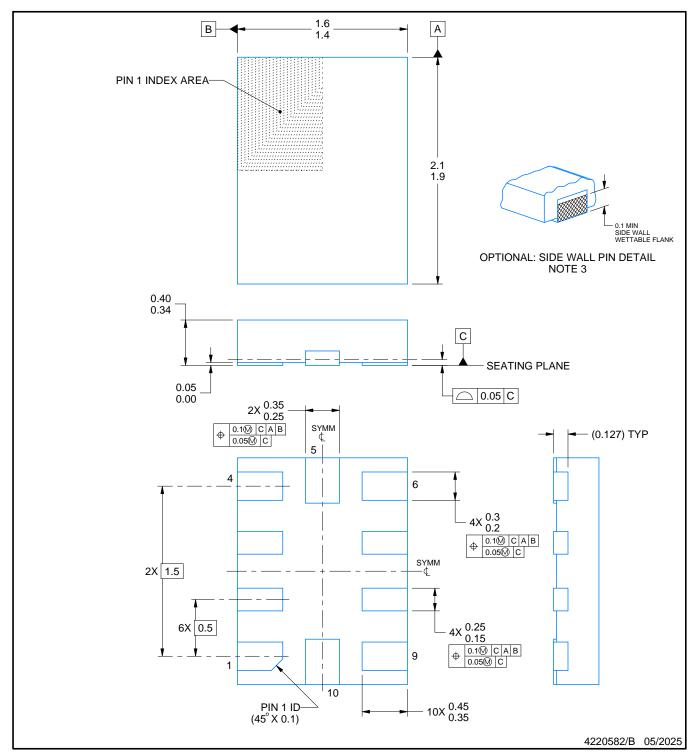

超小型 X2QFN パッケージ:2mm × 1.5mm × 0.4mm

- 広い電源電圧範囲:2V~5.5V

- 低消費電流

- 連続モード:わずか 150µA

- シングル・ショット・モード:自動パワー・ダウン

- データ・レートを設定可能: 8SPS~860SPS

- 収束時間は1サイクル

- 低ドリフト基準電圧を内蔵

- 内蔵温度センサ: 誤差 0.5℃ (最大値):0℃~70℃

- 内蔵発振器

- 内蔵 PGA

- 4 つのシングル・エンドまたは2 つの差動入力

# 2 アプリケーション

- 温度測定

- 熱電対測定

- 冷接点補償

- サーミスタ測定

- ポータブル機器

- ファクトリ・オートメーションとプロセス制御

# 3 概要

ADS1118 は、高精度、低消費電力の 16 ビット・アナログ /デジタル・コンバータ (ADC) であり、最も一般的なセンサ 信号を測定するために必要なすべての機能を超小型リードレス X2QFN-10 パッケージまたは VSSOP-10 パッケージに統合しています。ADS1118 はプログラマブル・ゲイン・アンプ (PGA)、基準電圧、発振器、高精度温度センサを内蔵しています。これらの機能を備え 2V~5.5V の幅広い電源電圧範囲に対応する ADS1118 は、電力とスペースの制約が厳しいセンサ測定アプリケーションに理想的です。

ADS1118 は、最大 860 サンプル/秒 (SPS) のデータ・レートで変換を実行できます。 PGA は

±256mV~±6.144V の入力範囲に対応しているため、大きな信号でも小さな信号でも高分解能で測定できます。入力マルチプレクサ (MUX) により、2 つの差動または 4 つのシングル・エンド入力を測定できます。高精度温度センサは、システム・レベルの温度監視または熱電対の冷接点補償に使用できます。

# 製品情報(1)

| 型番      | パッケージ      | 本体サイズ(公称)     |  |

|---------|------------|---------------|--|

| ADC4440 | X2QFN (10) | 1.50mm×2.00mm |  |

| ADS1118 | VSSOP (10) | 3.00mm×3.00mm |  |

(1) 提供されているすべてのパッケージについては、データシートの末 尾にある注文情報を参照してください。

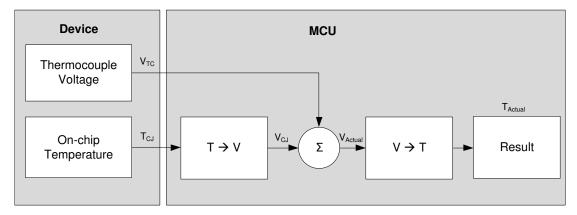

# K タイプの熱電対測定 内蔵温度センサによる冷接点補償

**Page**

| ` <i>\</i> |

|------------|

|            |

|            |

| 1  | 特長1                                                |    | 10.3 Feature Description       | 19 |

|----|----------------------------------------------------|----|--------------------------------|----|

| 2  | アプリケーション1                                          |    | 10.4 Device Functional Modes   | 23 |

| 3  | 概要1                                                |    | 10.5 Programming               | 24 |

| 4  | 改訂履歴                                               |    | 10.6 Register Maps             | 27 |

| 5  | 概要(続き)5                                            | 11 | Application and Implementation | 29 |

| 6  | Device Comparison Table 6                          |    | 11.1 Application Information   | 29 |

| -  | •                                                  |    | 11.2 Typical Application       | 34 |

| 7  | Pin Configuration and Functions                    | 12 | Power Supply Recommendations   | 37 |

| 8  | Specifications7                                    |    | 12.1 Power-Supply Sequencing   | 37 |

|    | 8.1 Absolute Maximum Ratings                       |    | 12.2 Power-Supply Decoupling   |    |

|    | 8.2 ESD Ratings                                    | 13 | Layout                         |    |

|    | 8.3 Recommended Operating Conditions               |    | 13.1 Layout Guidelines         |    |

|    | 8.4 Thermal Information                            |    | 13.2 Layout Example            |    |

|    | 8.5 Electrical Characteristics                     | 14 | デバイスおよびドキュメントのサポート             |    |

|    | 8.6 Timing Requirements: Serial Interface          |    | 14.1 ドキュメントのサポート               |    |

|    | 8.7 Switching Characteristics: Serial Interface 10 |    | 14.2 ドキュメントの更新通知を受け取る方法        |    |

|    | 8.8 Typical Characteristics                        |    | 14.3 コミュニティ・リソース               |    |

| 9  | Parameter Measurement Information 17               |    | 14.3 コミューティ・リン 一へ              |    |

|    | 9.1 Noise Performance                              |    | 14.5 静電気放電に関する注意事項             |    |

| 10 | Detailed Description 18                            |    |                                |    |

|    | 10.1 Overview                                      | 45 | 14.6 Glossary                  |    |

|    | 10.2 Functional Block Diagram                      | 15 | メカニカル、パッケージ、および注文情報            | 40 |

|    | -<br>-                                             |    |                                |    |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

Revision E (October 2015) から Revision F に変更

| •  | Changed maximum VDD voltage from 5.5 V to 7 V in the <i>Absolute Maximum Ratings</i> table                                                                                     |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _  | Changed bit description of Config Register bit 0                                                                                                                               |

| Re | evision D (October 2013) から Revision E に変更 Page                                                                                                                                |

| •  | 「 <i>ESD</i> 定格」表、「機能説明」セクション、「ノイズ特性」セクション、「デバイスの機能モード」セクション、「アプリケーションと実<br>装」セクション、「電源に関する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セクショ<br>ン、「メカニカル、パッケージ、および注文情報」セクション 追加 |

| •  | タイトル、「概要」セクション、「特長」セクション、および前面ページのブロック図を変更                                                                                                                                     |

| •  | Changed title from Product Family to Device Comparison Table and deleted Package Designator column                                                                             |

| •  | Updated descriptions and changed name of I/O column in Pin Configurations and Functions table                                                                                  |

| •  | Changed digital input voltage range and added minimum specification for T <sub>J</sub> in <i>Absolute Maximum Ratings</i> table                                                |

| •  | Added Differential input impedance specification in Electrical Characteristics                                                                                                 |

| •  | Changed Condition statement in Timing Requirements: Serial Interface                                                                                                           |

| •  | Moved t <sub>CSDOD</sub> , t <sub>DOPD</sub> , and t <sub>CSDOZ</sub> parameters from <i>Timing Requirements</i> to <i>Switching Characteristics</i>                           |

| •  | Moved t <sub>CSDOD</sub> and t <sub>CSDOZ</sub> values from MIN column to MAX column.                                                                                          |

| •  | Deleted Noise vs Input Signal, Noise vs Supply Voltage, and Noise vs Input Signal plots                                                                                        |

Updated Overview section and deleted "Gain = 2/3, 1, 2, 4, 8, or 16" from Functional Block Diagram18Updated Analog Inputs section20Updated Full-Scale Range (FSR) and LSB Size section21Updated Reset and Power Up section23Updated 32-Bit Data Transmission Cycle section26Updated Register Maps section27

| www.ti | I.CO.ID |

|--------|---------|

|        |         |

| •  | Updated Application Information section                                                                                                | 29               |

|----|----------------------------------------------------------------------------------------------------------------------------------------|------------------|

| •  | Updated Figure 48                                                                                                                      | 32               |

| •  | Deleted Thermocouple Measurement With Cold Junction Temperature section, and moved Figure 50 to Typical Application section            | 34               |

| Re | evision C (February 2013) から Revision D に変更                                                                                            | Page             |

| •  | デバイスの図 削除                                                                                                                              | 1                |

| •  | Changed bit 1 to NOP0 in Figure 44                                                                                                     | 27               |

| •  | Changed NOP bit description in Figure 44: changes bits[2:0] to bits [2:1] and changed NOP to NOP[1:0]                                  | 28               |

| Re | evision B (August 2012) から Revision C に変更                                                                                              | Page             |

| •  | ドキュメントを現行の標準に変更                                                                                                                        | 1                |

| •  | 「特長」の「低消費電流」の箇条書き項目に、シングル・ショット・モードの副項目を変更                                                                                              | 1                |

| •  | 「特長」の内蔵温度センサについての箇条書き項目を変更                                                                                                             | 1                |

| •  | 「概要」セクション 変更                                                                                                                           | 1                |

| •  | Changed Product Family table                                                                                                           | 6                |

| •  | Changed Function column name in Pin Descriptions table                                                                                 | 6                |

| •  | Changed Analog Input, Full-scale input voltage range parameter row in Electrical Characteristics table                                 | <mark>7</mark>   |

| •  | Changed footnotes 1 and 2 in Electrical Characteristics table                                                                          | <b>7</b>         |

| •  | Changed conditions for Electrical Characteristics table                                                                                | 8                |

| •  | Changed System Performance, Integral nonlinearity and Gain Error test conditions in Electrical Characteristics table                   | e <mark>8</mark> |

| •  | Changed first two Temperature Sensor, <i>Temperature sensor accuracy</i> parameter test conditions in Electrical Characteristics table | 8                |

| •  | Changed Power-Supply Requirements, Supply current parameter test conditions in Electrical Characteristics table                        | 9                |

| •  | Changed footnote 3 of Timing Requirements: Serial Interface Timing table                                                               | 10               |

| •  | Updated Figure 3                                                                                                                       | 11               |

| •  | Updated Figure 9                                                                                                                       | 11               |

| •  | Changed title of Figure 11 to Figure 14                                                                                                | 11               |

| •  | Updated Figure 15 and Figure 33                                                                                                        | 12               |

| •  | Changed conditions in Figure 21 to Figure 25                                                                                           | 13               |

| •  | Updated Figure 20                                                                                                                      | 14               |

| •  | Changed comments in Figure 27 to Figure 31                                                                                             | 14               |

| •  | Changed Overview section                                                                                                               | 18               |

| •  | Updated Multiplexer section                                                                                                            | 19               |

| •  | Changed Full-Scale Input section                                                                                                       | 21               |

| •  | Changed Voltage Reference section                                                                                                      | 21               |

| •  | Changed Oscillator section                                                                                                             | 21               |

| •  | Added multiplication points to example equations in Converting from Digital Codes to Temperature section                               | 22               |

| •  | Changed Serial Interface, Chip Select, Serial Clock, Data Input, and Data Output and Data Ready sections                               | 24               |

| •  | Changed Data Retrieval section                                                                                                         | 25               |

| •  | Changed Registers section                                                                                                              | 27               |

| •  | Changed Aliasing, Reset and Power Up, Operating Modes, and Duty Cycling for Low Power sections                                         | 30               |

| •  | Updated Figure 50                                                                                                                      | 34               |

| Re | evision A (July 2011) から Revision B に変更           | Pag | je |

|----|---------------------------------------------------|-----|----|

| •  | Added (VSSOP) to titles of Figure 20 to Figure 25 | 1   | 4  |

| •  | Added Figure 26 to Figure 31                      | 1   | 5  |

# 5 概要(続き)

ADS1118 は連続変換モードとシングル・ショット・モード (変換後、自動的にパワー・ダウン状態に移行する) のどちらででも動作します。 シングル・ショット・モードを使用すると、アイドル期間中の消費電流を大幅に低減できます。 データは、シリアル・ペリフェラル・インターフェイス (SPI™) で転送されます。 ADS1118 は、-40℃~+125℃で動作が規定されています。

# 6 Device Comparison Table

| DEVICE  | RESOLUTION<br>(Bits) | MAXIMUM SAMPLE<br>RATE<br>(SPS) | INPUT CHANNELS<br>Differential<br>(Single-Ended) | PGA | INTERFACE        | SPECIAL<br>FEATURES |

|---------|----------------------|---------------------------------|--------------------------------------------------|-----|------------------|---------------------|

| ADS1118 | 16                   | 860                             | 2 (4)                                            | Yes | SPI              | Temperature sensor  |

| ADS1018 | 12                   | 3300                            | 2 (4)                                            | Yes | SPI              | Temperature sensor  |

| ADS1115 | 16                   | 860                             | 2 (4)                                            | Yes | I <sup>2</sup> C | Comparator          |

| ADS1114 | 16                   | 860                             | 1 (1)                                            | Yes | I <sup>2</sup> C | Comparator          |

| ADS1113 | 16                   | 860                             | 1 (1)                                            | No  | I <sup>2</sup> C | None                |

| ADS1015 | 12                   | 3300                            | 2 (4)                                            | Yes | I <sup>2</sup> C | Comparator          |

| ADS1014 | 12                   | 3300                            | 1 (1)                                            | Yes | I <sup>2</sup> C | Comparator          |

| ADS1013 | 12                   | 3300                            | 1 (1)                                            | No  | I <sup>2</sup> C | None                |

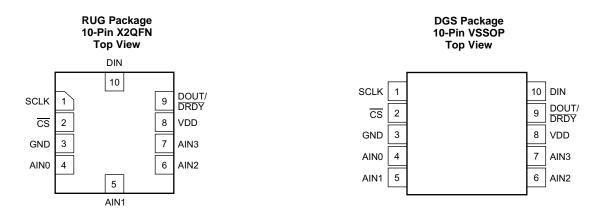

# 7 Pin Configuration and Functions

# **Pin Functions**

|     | PIN       | TYPE           | DESCRIPTION                                                              |

|-----|-----------|----------------|--------------------------------------------------------------------------|

| NO. | NAME      | ITPE           | DESCRIPTION                                                              |

| 1   | SCLK      | Digital input  | Serial clock input                                                       |

| 2   | CS        | Digital input  | Chip select; active low. Connect to GND if not used.                     |

| 3   | GND       | Supply         | Ground                                                                   |

| 4   | AIN0      | Analog input   | Analog input 0. Leave unconnected or tie to VDD if not used.             |

| 5   | AIN1      | Analog input   | Analog input 1. Leave unconnected or tie to VDD if not used.             |

| 6   | AIN2      | Analog input   | Analog input 2. Leave unconnected or tie to VDD if not used.             |

| 7   | AIN3      | Analog input   | Analog input 3. Leave unconnected or tie to VDD if not used.             |

| 8   | VDD       | Supply         | Power supply. Connect a 100-nF power supply decoupling capacitor to GND. |

| 9   | DOUT/DRDY | Digital output | Serial data output combined with data ready; active low                  |

| 10  | DIN       | Digital input  | Serial data input                                                        |

# 8 Specifications

## 8.1 Absolute Maximum Ratings

over operating ambient temperature range (unless otherwise noted)<sup>(1)</sup>

|                           |                                  | MIN       | MAX       | UNIT |

|---------------------------|----------------------------------|-----------|-----------|------|

| Power-supply voltage      | VDD to GND                       | -0.3      | 7         | V    |

| Analog input voltage      | AINO, AIN1, AIN2, AIN3           | GND - 0.3 | VDD + 0.3 | V    |

| Digital input voltage     | DIN, DOUT/DRDY, SCLK, CS         | GND - 0.3 | VDD + 0.3 | V    |

| Input current, continuous | Any pin except power supply pins | -10       | 10        | mA   |

| Tomporatura               | Junction, T <sub>J</sub>         | -40       | 150       | °C   |

| Temperature               | Storage, T <sub>stg</sub>        | -60       | 150       | 10   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 8.2 ESD Ratings

|                    |               |                                                                     | VALUE | UNIT |

|--------------------|---------------|---------------------------------------------------------------------|-------|------|

| V                  | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±4000 | \/   |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±1000 | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 8.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)

|                     |                                    |                                    | MIN | NOM        | MAX | UNIT |

|---------------------|------------------------------------|------------------------------------|-----|------------|-----|------|

| POWER               | R SUPPLY                           |                                    |     |            | •   |      |

| VDD                 | Power supply                       | VDD to GND                         | 2   |            | 5.5 | V    |

| ANALO               | G INPUTS <sup>(1)</sup>            |                                    |     |            |     |      |

| FSR                 | Full-scale input voltage range (2) | $V_{IN} = V_{(AINP)} - V_{(AINN)}$ | Se  | ee Table 3 |     |      |

| V <sub>(AINx)</sub> | Absolute input voltage             |                                    | GND |            | VDD | V    |

| DIGITA              | INPUTS                             |                                    | •   |            | ·   |      |

|                     | Input voltage                      |                                    | GND |            | VDD | V    |

| TEMPE               | RATURE RANGE                       |                                    |     |            |     |      |

| T <sub>A</sub>      | Operating ambient temperature      |                                    | -40 |            | 125 | °C   |

|                     |                                    | ·                                  |     |            |     |      |

- (1) AINP and AINN denote the selected positive and negative inputs. AINx denotes one of the four available analog inputs.

- (2) This parameter expresses the full-scale range of the ADC scaling. No more than VDD + 0.3 V or 5.5 V (whichever is smaller) must be applied to this device.

## 8.4 Thermal Information

|                        |                                              | ADS         |             |      |

|------------------------|----------------------------------------------|-------------|-------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | DGS (VSSOP) | RUG (X2QFN) | UNIT |

|                        |                                              | 10 PINS     | 10 PINS     |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 186.8       | 245.2       | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 51.5        | 69.3        | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 108.4       | 172         | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 2.7         | 8.2         | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 106.5       | 170.8       | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | n/a         | n/a         | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 8.5 Electrical Characteristics

Maximum and minimum specifications apply from  $T_A = -40^{\circ}\text{C}$  to +125°C. Typical specifications are at  $T_A = 25^{\circ}\text{C}$ . All specifications are at VDD = 3.3 V, data rate = 8 SPS, and full-scale range (FSR) = ±2.048 V (unless otherwise noted).

|       | PARAMETER                     | TEST CONDITIONS                                      | MIN            | TYP            | MAX   | UNIT   |

|-------|-------------------------------|------------------------------------------------------|----------------|----------------|-------|--------|

| ANALO | G INPUTS                      |                                                      |                |                |       |        |

|       |                               | FSR = ±6.144 V <sup>(1)</sup>                        |                | 8              |       |        |

|       |                               | FSR = ±4.096 V <sup>(1)</sup> , FSR = ±2.048 V       |                | 6              |       |        |

|       | Common-mode input impedance   | FSR = ±1.024 V                                       |                | 3              |       | МΩ     |

|       |                               | FSR = ±0.512 V, FSR = ±0.256 V                       |                | 100            |       |        |

|       |                               | FSR = ±6.144 V <sup>(1)</sup>                        |                | 22             |       |        |

|       |                               | FSR = ±4.096 V <sup>(1)</sup>                        |                | 15             |       |        |

|       | Differential input impedance  | FSR = ±2.048 V                                       |                | 4.9            |       | МΩ     |

|       |                               | FSR = ±1.024 V                                       |                | 2.4            |       |        |

|       |                               | FSR = ±0.512 V, FSR = ±0.256 V                       |                | 710            |       | kΩ     |

| SYSTE | M PERFORMANCE                 |                                                      |                |                | '     |        |

|       | Resolution (No missing codes) |                                                      | 16             |                |       | Bits   |

| DR    | Data rate                     |                                                      | 8, 16, 32, 64, | 128, 250, 475, | 860   | SPS    |

|       | Data rate variation           | All data rates                                       | -10%           |                | 10%   |        |

|       | Output noise                  |                                                      | See Noise P    | erformance sec | tion  |        |

| INL   | Integral nonlinearity         | DR = 8 SPS, FSR = ±2.048 V <sup>(2)</sup>            |                |                | 1     | LSB    |

|       | 011-1                         | FSR = ±2.048 V, differential inputs                  |                | ±0.1           | ±2    | 1.00   |

|       | Offset error                  | FSR = ±2.048 V, single-ended inputs                  |                | ±0.25          |       | LSB    |

|       | Offset drift                  | FSR = ±2.048 V                                       |                | 0.002          |       | LSB/°C |

|       | Offset power-supply rejection | FSR = ±2.048 V, DC supply variation                  |                | 0.2            |       | LSB/V  |

|       | Offset channel match          | Match between any two inputs                         |                | 0.6            |       | LSB    |

|       | Gain error <sup>(3)</sup>     | FSR = ±2.048 V, T <sub>A</sub> = 25°C                |                | 0.01%          | 0.15% |        |

|       |                               | FSR = ±0.256 V                                       |                | 7              |       |        |

|       | Gain drift <sup>(3)(4)</sup>  | FSR = ±2.048 V                                       |                | 5              | 40    | ppm/°C |

|       |                               | FSR = ±6.144 V <sup>(1)</sup>                        |                | 5              |       |        |

|       | Gain power-supply rejection   |                                                      |                | 10             |       | ppm/V  |

|       | Gain match <sup>(3)</sup>     | Match between any two gains                          |                | 0.01%          | 0.1%  |        |

|       | Gain channel match            | Match between any two inputs                         |                | 0.01%          | 0.1%  |        |

|       |                               | At DC, FSR = ±0.256 V                                |                | 105            |       |        |

|       |                               | At DC, FSR = ±2.048 V                                |                | 100            |       |        |

| CMRR  | Common-mode rejection ratio   | At DC, FSR = $\pm 6.144 \text{ V}^{(1)}$             |                | 90             |       | dB     |

|       |                               | f <sub>CM</sub> = 50 Hz, DR = 860 SPS                |                | 105            |       |        |

|       |                               | f <sub>CM</sub> = 60 Hz, DR = 860 SPS                |                | 105            |       |        |

| TEMPE | RATURE SENSOR                 |                                                      |                |                |       |        |

|       | Temperature range             |                                                      | -40            |                | 125   | °C     |

|       | Temperature resolution        |                                                      |                | 0.03125        |       | °C/LSB |

|       |                               | T <sub>A</sub> = 0°C to 70°C                         |                | 0.2            | ±0.5  |        |

|       |                               | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |                | 0.4            | ±1    | °C     |

|       |                               | vs supply                                            |                | 0.03125        | ±0.25 | °C/V   |

<sup>(1)</sup> This parameter expresses the full-scale range of the ADC scaling. No more than VDD + 0.3 V or 5.5 V (whichever is smaller) must be applied to this device.

<sup>(2)</sup> Best-fit INL; covers 99% of full-scale.

<sup>(3)</sup> Includes all errors from onboard PGA and voltage reference.

<sup>(4)</sup> Maximum value specified by characterization.

# **Electrical Characteristics (continued)**

Maximum and minimum specifications apply from  $T_A = -40^{\circ}\text{C}$  to +125°C. Typical specifications are at  $T_A = 25^{\circ}\text{C}$ . All specifications are at VDD = 3.3 V, data rate = 8 SPS, and full-scale range (FSR) =  $\pm 2.048$  V (unless otherwise noted).

|                 | PARAMETER                 | TEST CONDITIONS                   | MIN                                   | TYP | MAX     | UNIT |

|-----------------|---------------------------|-----------------------------------|---------------------------------------|-----|---------|------|

| DIGIT           | AL INPUTS/OUTPUTS         |                                   |                                       |     |         |      |

| $V_{IH}$        | High-level input voltage  |                                   | 0.7 VDD                               |     | VDD     | V    |

| V <sub>IL</sub> | Low-level input voltage   |                                   | GND                                   |     | 0.2 VDD | V    |

| V <sub>OH</sub> | High-level output voltage | I <sub>OH</sub> = 1 mA            | 0.8 VDD                               |     |         | V    |

| V <sub>OL</sub> | Low-level output voltage  | I <sub>OL</sub> = 1 mA            | GND                                   |     | 0.2 VDD | V    |

| I <sub>H</sub>  | Input leakage, high       | V <sub>IH</sub> = 5.5 V           | -10                                   |     | 10      | μΑ   |

| IL              | Input leakage, low        | V <sub>IL</sub> = GND             | -10                                   |     | 10      | μΑ   |

| POWE            | R SUPPLY                  | ,                                 | , , , , , , , , , , , , , , , , , , , |     | ,       |      |

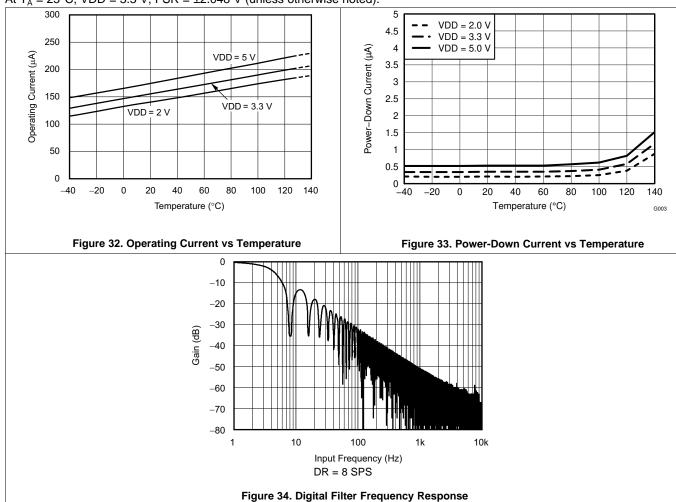

|                 |                           | Power down, T <sub>A</sub> = 25°C |                                       | 0.5 | 2       |      |

|                 | 0                         | Power down                        |                                       |     | 5       |      |

| $I_{VDD}$       | Supply current            | Operating, T <sub>A</sub> = 25°C  |                                       | 150 | 200     | μА   |

|                 |                           | Operating                         |                                       |     | 300     |      |

| P <sub>D</sub>  |                           | VDD = 5 V                         |                                       | 0.9 |         |      |

|                 | Power dissipation         | VDD = 3.3 V                       |                                       | 0.5 |         | mW   |

|                 |                           | VDD = 2 V                         |                                       | 0.3 |         |      |

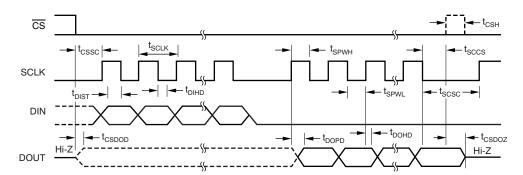

# 8.6 Timing Requirements: Serial Interface

Over operating ambient temperature range and VDD = 2 V to 5.5 V (unless otherwise noted)

|                   |                                                                           | MIN MAX | UNIT |  |  |  |

|-------------------|---------------------------------------------------------------------------|---------|------|--|--|--|

| t <sub>CSSC</sub> | Delay time, CS falling edge to first SCLK rising edge (1)                 | 100     | ns   |  |  |  |

| t <sub>SCCS</sub> | Delay time, final SCLK falling edge to $\overline{\text{CS}}$ rising edge |         |      |  |  |  |

| t <sub>CSH</sub>  | Pulse duration, CS high                                                   | 200     | ns   |  |  |  |

| t <sub>SCLK</sub> | SCLK period                                                               | 250     | ns   |  |  |  |

| t <sub>SPWH</sub> | Pulse duration, SCLK high                                                 | 100     | ns   |  |  |  |

|                   | Pulse duration, SCLK low <sup>(2)</sup>                                   | 100     | ns   |  |  |  |

| t <sub>SPWL</sub> | Pulse duration, SCLK low 4                                                | 28      | B ms |  |  |  |

| t <sub>DIST</sub> | Setup time, DIN valid before SCLK falling edge                            | 50      | ns   |  |  |  |

| t <sub>DIHD</sub> | Hold time, DIN valid after SCLK falling edge                              | 50      | ns   |  |  |  |

| t <sub>DOHD</sub> | Hold time, SCLK rising edge to DOUT invalid                               | 0       | ns   |  |  |  |

$<sup>\</sup>overline{\text{CS}}$  can be tied low permanently in case the serial bus is not shared with any other device. Holding SCLK low longer than 28 ms resets the SPI interface.

# 8.7 Switching Characteristics: Serial Interface

Over operating ambient temperature range (unless otherwise noted)

|                    | PARAMETER                                                     | TEST CONDITIONS                    | MIN | TYP MAX | UNIT |

|--------------------|---------------------------------------------------------------|------------------------------------|-----|---------|------|

| t <sub>CSDOD</sub> | Propagation delay time, CS falling edge to DOUT driven        | DOUT load = 20 pF    100 kΩ to GND |     | 100     | ns   |

| t <sub>DOPD</sub>  | Propagation delay time,<br>SCLK rising edge to valid new DOUT | DOUT load = 20 pF    100 kΩ to GND | 0   | 50      | ns   |

| t <sub>CSDOZ</sub> | Propagation delay time, CS rising edge to DOUT high impedance | DOUT load = 20 pF    100 kΩ to GND |     | 100     | ns   |

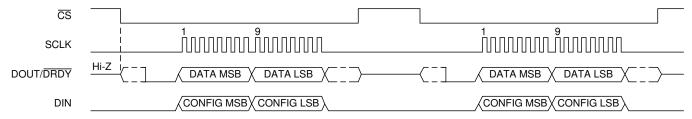

Figure 1. Serial Interface Timing

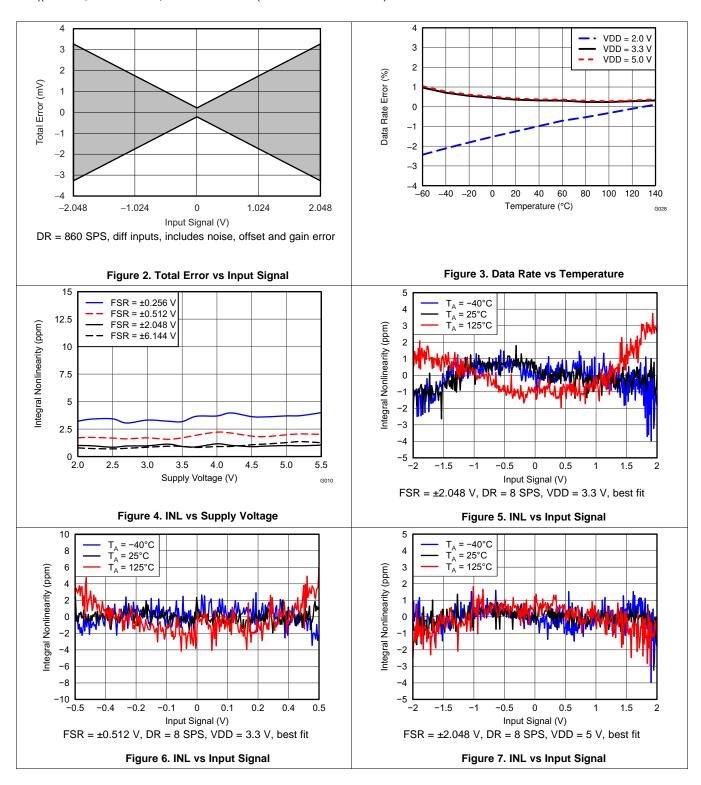

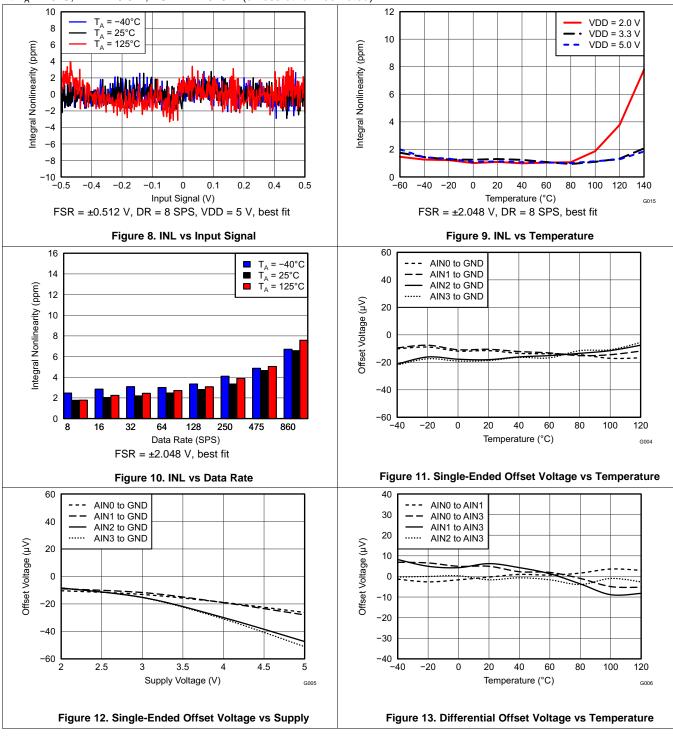

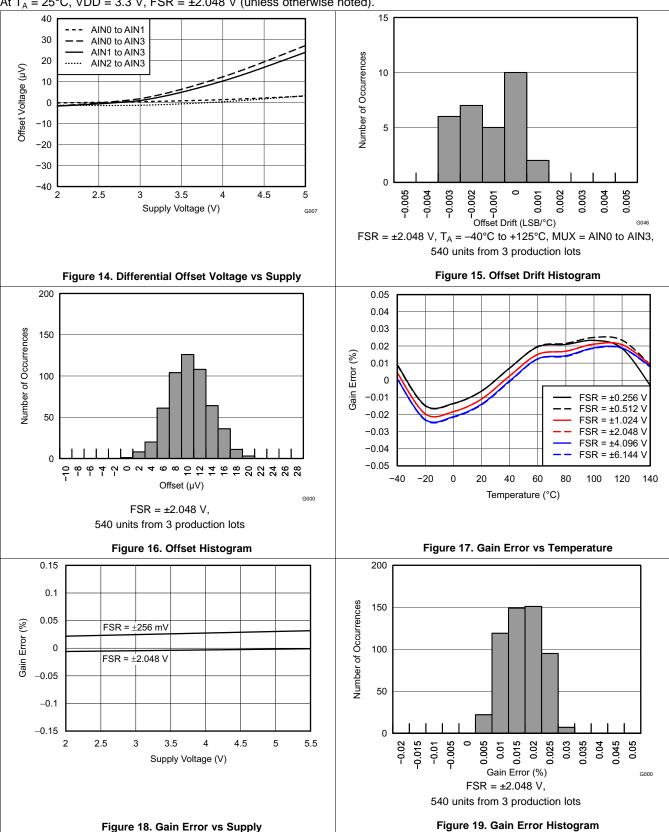

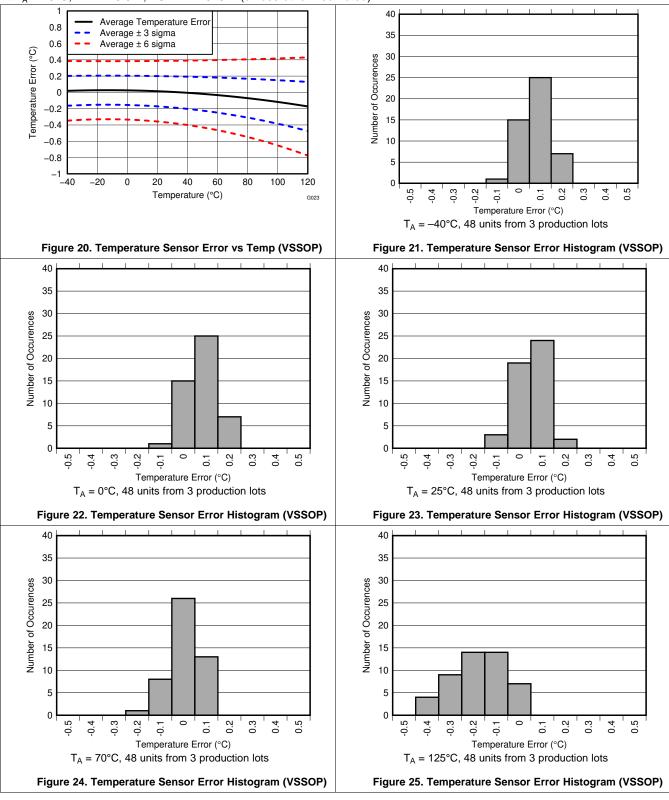

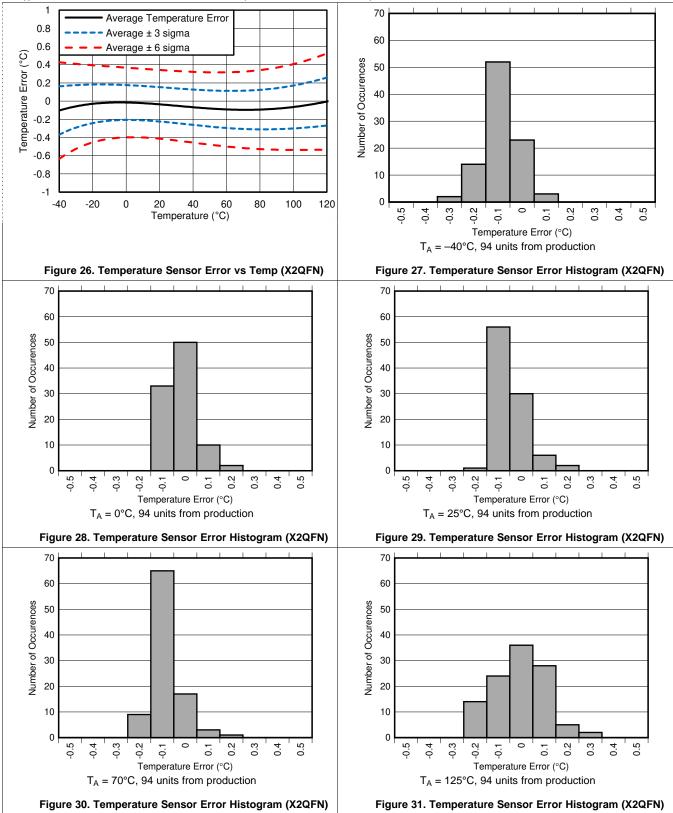

# 8.8 Typical Characteristics

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

# **Typical Characteristics (continued)**

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

# **Typical Characteristics (continued)**

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

#### 9 Parameter Measurement Information

#### 9.1 Noise Performance

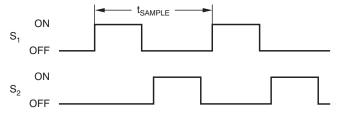

Delta-sigma  $(\Delta\Sigma)$  analog-to-digital converters (ADCs) are based on the principle of oversampling. The input signal of a  $\Delta\Sigma$  ADC is sampled at a high frequency (modulator frequency) and subsequently filtered and decimated in the digital domain to yield a conversion result at the respective output data rate. The ratio between modulator frequency and output data rate is called *oversampling ratio* (OSR). By increasing the OSR, and thus reducing the output data rate, the noise performance of the ADC can be optimized. In other words, the input-referred noise drops when reducing the output data rate because more samples of the internal modulator are averaged to yield one conversion result. Increasing the gain also reduces the input-referred noise, which is particularly useful when measuring low-level signals.

Table 1 and Table 2 summarize the device noise performance. Data are representative of typical noise performance at  $T_A = 25^{\circ}\text{C}$  with the inputs shorted together externally. Table 1 show the input-referred noise in units of  $\mu\text{V}_{RMS}$  for the conditions shown. Note that  $\mu\text{V}_{PP}$  values are shown in parenthesis. Table 2 shows the corresponding data in effective number of bits (ENOB) calculated from  $\mu\text{V}_{RMS}$  values using Equation 1. The noise-free bits calculated from peak-to-peak noise values using Equation 2 are shown in parenthesis.

$$ENOB = In (FSR / V_{RMS-Noise}) / In(2)$$

(1)

Noise-Free Bits =

$$\ln (FSR / V_{PP-Noise}) / \ln(2)$$

(2)

Table 1. Noise in  $\mu V_{RMS}$  ( $\mu V_{PP}$ ) at VDD = 3.3 V

|           |                        |              | P - KINIO (P - FF) |               |               |              |  |  |  |  |

|-----------|------------------------|--------------|--------------------|---------------|---------------|--------------|--|--|--|--|

| DATA RATE | FSR (Full-Scale Range) |              |                    |               |               |              |  |  |  |  |

| (SPS)     | ±6.144 V               | ±4.096 V     | ±2.048 V           | ±1.024 V      | ±0.512 V      | ±0.256 V     |  |  |  |  |

| 8         | 187.5 (187.5)          | 125 (125)    | 62.5 (62.5)        | 31.25 (31.25) | 15.62 (15.62) | 7.81 (7.81)  |  |  |  |  |

| 16        | 187.5 (187.5)          | 125 (125)    | 62.5 (62.5)        | 31.25 (31.25) | 15.62 (15.62) | 7.81 (7.81)  |  |  |  |  |

| 32        | 187.5 (187.5)          | 125 (125)    | 62.5 (62.5)        | 31.25 (31.25) | 15.62 (15.62) | 7.81 (7.81)  |  |  |  |  |

| 64        | 187.5 (187.5)          | 125 (125)    | 62.5 (62.5)        | 31.25 (31.25) | 15.62 (15.62) | 7.81 (7.81)  |  |  |  |  |

| 128       | 187.5 (187.5)          | 125 (125)    | 62.5 (62.5)        | 31.25 (31.25) | 15.62 (15.62) | 7.81 (12.35) |  |  |  |  |

| 250       | 187.5 (252.09)         | 125 (148.28) | 62.5 (84.03)       | 31.25 (39.54) | 15.62 (16.06) | 7.81 (18.53) |  |  |  |  |

| 475       | 187.5 (266.92)         | 125 (227.38) | 62.5 (79.08)       | 31.25 (56.84) | 15.62 (32.13) | 7.81 (25.95) |  |  |  |  |

| 860       | 187.5 (430.06)         | 125 (266.93) | 62.5 (118.63)      | 31.25 (64.26) | 15.62 (40.78) | 7.81 (35.83) |  |  |  |  |

Table 2. ENOB from RMS Noise (Noise-Free Bits from Peak-to-Peak Noise) at VDD = 3.3 V

| DATA RATE | FSR (Full-Scale Range) |            |            |            |            |            |  |  |  |  |

|-----------|------------------------|------------|------------|------------|------------|------------|--|--|--|--|

| (SPS)     | ±6.144 V               | ±4.096 V   | ±2.048 V   | ±1.024 V   | ±0.512 V   | ±0.256 V   |  |  |  |  |

| 8         | 16 (16)                | 16 (16)    | 16 (16)    | 16 (16)    | 16 (16)    | 16 (16)    |  |  |  |  |

| 16        | 16 (16)                | 16 (16)    | 16 (16)    | 16 (16)    | 16 (16)    | 16 (16)    |  |  |  |  |

| 32        | 16 (16)                | 16 (16)    | 16 (16)    | 16 (16)    | 16 (16)    | 16 (16)    |  |  |  |  |

| 64        | 16 (16)                | 16 (16)    | 16 (16)    | 16 (16)    | 16 (16)    | 16 (16)    |  |  |  |  |

| 128       | 16 (16)                | 16 (16)    | 16 (16)    | 16 (16)    | 16 (16)    | 16 (15.33) |  |  |  |  |

| 250       | 16 (15.57)             | 16 (15.75) | 16 (15.57) | 16 (15.66) | 16 (15.96) | 16 (14.75) |  |  |  |  |

| 475       | 16 (15.49)             | 16 (15.13) | 16 (15.66) | 16 (15.13) | 16 (14.95) | 16 (14.26) |  |  |  |  |

| 860       | 16 (14.8)              | 16 (14.9)  | 16 (15.07) | 16 (14.95) | 16 (14.61) | 16 (13.8)  |  |  |  |  |

17

# 10 Detailed Description

#### 10.1 Overview

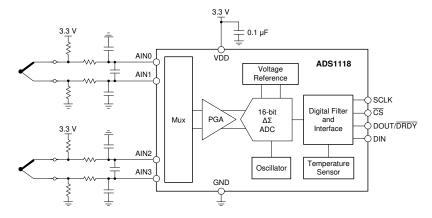

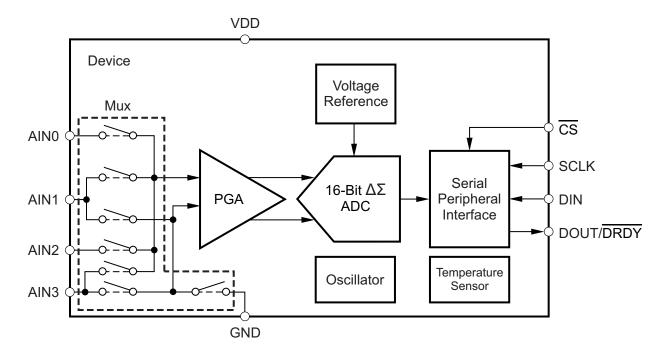

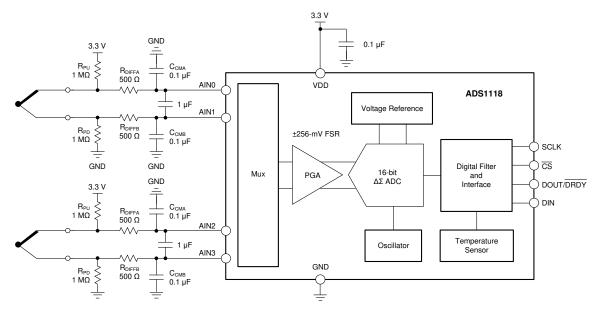

The ADS1118 is a very small, low-power, 16-bit, delta-sigma ( $\Delta\Sigma$ ) analog-to-digital converter (ADC). The ADS1118 consists of a  $\Delta\Sigma$  ADC core with adjustable gain, an internal voltage reference, a clock oscillator, and an SPI. This device is also a highly linear and accurate temperature sensor. All of these features are intended to reduce required external circuitry and improve performance. *Functional Block Diagram* shows the ADS1118 functional block diagram.

The ADS1118 ADC core measures a differential signal,  $V_{IN}$ , that is the difference of  $V_{(AINP)}$  and  $V_{(AINN)}$ . The converter core consists of a differential, switched-capacitor  $\Delta\Sigma$  modulator followed by a digital filter. This architecture results in a very strong attenuation in any common-mode signals. Input signals are compared to the internal voltage reference. The digital filter receives a high-speed bitstream from the modulator and outputs a code proportional to the input voltage.

The ADS1118 has two available conversion modes: single-shot mode and continuous conversion mode. In single-shot mode, the ADC performs one conversion of the input signal upon request and stores the value to an internal conversion register. The device then enters a power-down state. This mode is intended to provide significant power savings in systems that require only periodic conversions or when there are long idle periods between conversions. In continuous conversion mode, the ADC automatically begins a conversion of the input signal as soon as the previous conversion is completed. The rate of continuous conversion is equal to the programmed data rate. Data can be read at any time and always reflect the most recently completed conversion.

## 10.2 Functional Block Diagram

## 10.3 Feature Description

# 10.3.1 Multiplexer

The ADS1118 contains an input multiplexer (mux), as shown in Figure 35. Either four single-ended or two differential signals can be measured. Additionally, AIN0, AIN1, and AIN2 can be measured differentially to AIN3. The multiplexer is configured by bits MUX[2:0] in the Config register. When single-ended signals are measured, the negative input of the ADC is internally connected to GND by a switch within the multiplexer.

Figure 35. Input Multiplexer

When measuring single-ended inputs, the device does not output negative codes. These negative codes indicate negative differential signals; that is,  $(V_{(AINP)} - V_{(AINN)}) < 0$ . Electrostatic discharge (ESD) diodes to VDD and GND protect the ADS1118 inputs. To prevent the ESD diodes from turning on, keep the absolute voltage on any input within the range given in Equation 3:

$$GND - 0.3 \text{ V} < V_{(A|Nx)} < \text{VDD} + 0.3 \text{ V}$$

(3)

If the voltages on the input pins can possibly violate these conditions, use external Schottky diodes and series resistors to limit the input current to safe values (see the *Absolute Maximum Ratings* table).

Also, overdriving one unused input on the ADS1118 may affect conversions currently taking place on other input pins. If overdriving unused inputs is possible, clamp the signal with external Schottky diodes.

# Feature Description (continued)

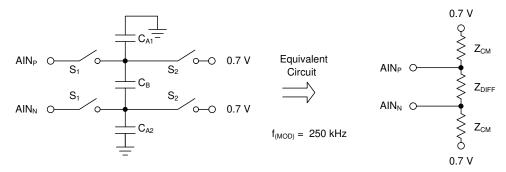

## 10.3.2 Analog Inputs

The ADS1118 uses a switched-capacitor input stage where capacitors are continuously charged and then discharged to measure the voltage between AIN<sub>P</sub> and AIN<sub>N</sub>. This frequency at which the input signal is sampled is called the sampling frequency or the modulator frequency ( $f_{(MOD)}$ ). ADS1118 has a 1 MHz internal oscillator which is further divided by a factor of 4 to generate the modulator frequency at 250 kHz. The capacitors used in this input stage are small, and to external circuitry, the average loading appears resistive. This structure is shown in Figure 36. The resistance is set by the capacitor values and the rate at which they are switched. Figure 37 shows the setting of the switches illustrated in Figure 36. During the sampling phase, switches  $S_1$  are closed. This event charges  $C_{A1}$  to  $V_{(AINP)}$ ,  $C_{A2}$  to  $V_{(AINN)}$ , and  $C_B$  to  $(V_{(AINP)} - V_{(AINN)})$ . During the discharge phase,  $S_1$  is first opened and then  $S_2$  is closed. Both  $C_{A1}$  and  $C_{A2}$  then discharge to approximately 0.7 V and  $C_B$  discharges to 0 V. This charging draws a very small transient current from the source driving the ADS1118 analog inputs. The average value of this current can be used to calculate the effective impedance ( $Z_{eff}$ ), where  $Z_{eff} = V_{IN} / I_{AVERAGE}$ .

Figure 36. Simplified Analog Input Circuit

Figure 37. S<sub>1</sub> and S<sub>2</sub> Switch Timing

The common-mode input impedance is measured by applying a common-mode signal to the shorted  $AIN_P$  and  $AIN_N$  inputs and measuring the average current consumed by each pin. The common-mode input impedance changes depending on the full-scale range, but is approximately 6 M $\Omega$  for the default full-scale range. In Figure 36, the common-mode input impedance is  $Z_{CM}$ .

The differential input impedance is measured by applying a differential signal to  $AIN_P$  and  $AIN_N$  inputs where one input is held at 0.7 V. The current that flows through the pin connected to 0.7 V is the differential current and scales with the full-scale range. In Figure 36, the differential input impedance is  $Z_{DIFF}$ .

Make sure to consider the typical value of the input impedance. Unless the input source has a low impedance, the ADS1118 input impedance may affect the measurement accuracy. For sources with high-output impedance, buffering may be necessary. Active buffers introduce noise, and also introduce offset and gain errors. Consider all of these factors in high-accuracy applications.

The clock oscillator frequency drifts slightly with temperature; therefore, the input impedances also drift. For most applications, this input impedance drift is negligible, and can be ignored.

# **Feature Description (continued)**

## 10.3.3 Full-Scale Range (FSR) and LSB Size

A programmable gain amplifier (PGA) is implemented before the ADS1118  $\Delta\Sigma$  core. The full-scale range is configured by three bits (PGA[2:0]) in the Config Register and can be set to ±6.144 V, ±4.096 V, ±2.048 V, ±1.024 V, ±0.512 V, ±0.256 V. Table 3 shows the FSR together with the corresponding LSB size. LSB size is calculated from full-scale voltage by the formula shown in Equation 4. However, analog input voltages may never exceed the analog input voltage limits given in the *Electrical Characteristics*. If a supply voltage of VDD greater than 4 V is used, the ±6.144 V full-scale range allows input voltages to extend up to the supply. Note though that in this case, or whenever the supply voltage is less than the full-scale range (for example, VDD = 3.3 V and fullscale range = ±4.096 V), a full-scale ADC output code cannot be obtained. This inability means that some dynamic range is lost.

$$LSB = FSR / 2^{16}$$

(4)

**FSR LSB SIZE** ±6.144 V<sup>(1)</sup> 187.5 μV ±4.096 V<sup>(1)</sup> 125 μV ±2.048 V 62.5 μV ±1.024 V 31.25 μV ±0.512 V 15.625 μV ±0.256 V 7.8125 μV

Table 3. Full-Scale Range and Corresponding LSB Size

## 10.3.4 Voltage Reference

The ADS1118 has an integrated voltage reference. An external reference cannot be used with this device. Errors associated with the initial voltage reference accuracy and the reference drift with temperature are included in the gain error and gain drift specifications in the *Electrical Characteristics*.

#### 10.3.5 Oscillator

The ADS1118 has an integrated oscillator running at 1 MHz. No external clock is required to operate the device. Note that the internal oscillator drifts over temperature and time. The output data rate will scale proportional with the oscillator frequency.

This parameter expresses the full-scale range of the ADC scaling. No more than VDD + 0.3 V must be applied to this device.

## 10.3.6 Temperature Sensor

The ADS1118 offers an integrated precision temperature sensor. The temperature sensor mode is enabled by setting bit TS\_MODE = 1 in the Config Register. Temperature data are represented as a 14-bit result that is left-justified within the 16-bit conversion result. Data are output starting with the most significant byte (MSB). When reading the two data bytes, the first 14 bits are used to indicate the temperature measurement result. One 14-bit LSB equals 0.03125°C. Negative numbers are represented in binary twos complement format, as shown in Table 4.

**Table 4. 14-Bit Temperature Data Format**

| TEMPERATURE (°C) | DIGITAL OUTPUT (BINARY) | HEX  |

|------------------|-------------------------|------|

| 128              | 01 0000 0000 0000       | 1000 |

| 127.96875        | 00 1111 1111 1111       | 0FFF |

| 100              | 00 1100 1000 0000       | 0C80 |

| 75               | 00 1001 0110 0000       | 0960 |

| 50               | 00 0110 0100 0000       | 0640 |

| 25               | 00 0011 0010 0000       | 0320 |

| 0.25             | 00 0000 0000 1000       | 8000 |

| 0.03125          | 00 0000 0000 0001       | 0001 |

| 0                | 00 0000 0000 0000       | 0000 |

| -0.25            | 11 1111 1111 1000       | 3FF8 |

| -25              | 11 1100 1110 0000       | 3CE0 |

| -40              | 11 1011 0000 0000       | 3B00 |

## 10.3.6.1 Converting from Temperature to Digital Codes

## For positive temperatures:

Twos complement is not performed on positive numbers. Therefore, simply convert the number to binary code in a 14-bit, left justified format with the MSB = 0 to denote the positive sign.

**Example:**  $50^{\circ}$ C /  $(0.03125^{\circ}$ C/count) = 1600 = 0640h = 0001100100000

# For negative temperatures:

Generate the twos complement of a negative number by complementing the absolute binary number and adding 1. Then denote the negative sign with the MSB = 1.

**Example:**  $|-25^{\circ}\text{C}|$  /  $(0.03125^{\circ}\text{C/count}) = 800 = 0320\text{h} = 00\ 0011\ 0010\ 0000$ Twos complement format: 11 1100 1101 1111 + 1 = 11 1100 1110 0000

#### 10.3.6.2 Converting from Digital Codes to Temperature

To convert from digital codes to temperature, first check whether the MSB is a 0 or a 1. If the MSB is a 0, simply multiply the decimal code by  $0.03125^{\circ}$ C to obtain the result. If the MSB = 1, subtract 1 from the result and complement all of the bits. Then multiply the result by  $-0.03125^{\circ}$ C.

**Example:** The device reads back 0960h: 0960h has an MSB = 0.

$0960h \times 0.03125$ °C =  $2400 \times 0.03125$ °C = 75°C

**Example:** The device reads back 3CE0h: 3CE0h has an MSB = 1.

Subtract 1 and complement the result:  $3CE0h \rightarrow 0320h$   $0320h \times (-0.03125^{\circ}C) = 800 \times (-0.03125^{\circ}C) = -25^{\circ}C$

#### 10.4 Device Functional Modes

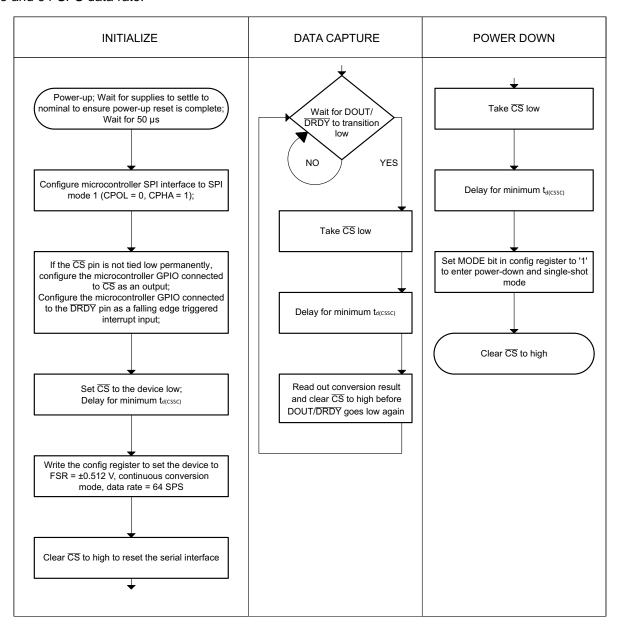

## 10.4.1 Reset and Power Up

When the ADS1118 powers up, a reset is performed. As part of the reset process, the ADS1118 sets all of its bits in the Config Register to the respective default settings. By default, the ADS1118 enters a power-down state at start-up. The device interface and digital blocks are active, but no data conversions are performed. The initial power-down state of the ADS1118 is intended to relieve systems with tight power-supply requirements from encountering a surge during power up.

## 10.4.2 Operating Modes

The ADS1118 operates in one of two modes: continuous-conversion or single-shot. The MODE bit in the Config register selects the respective operating mode.

#### 10.4.2.1 Single-Shot Mode and Power-Down

When the MODE bit in the Config register is set to 1, the ADS1118 enters a power-down state, and operates in single-shot mode. This power-down state is the default state for the ADS1118 when power is first applied. Although powered down, the device still responds to commands. The ADS1118 remains in this power-down state until a 1 is written to the single-shot (SS) bit in the Config register. When the SS bit is asserted, the device powers up, resets the SS bit to 0, and starts a single conversion. When conversion data are ready for retrieval, the device powers down again. Writing a 1 to the SS bit while a conversion is ongoing has no effect. To switch to continuous-conversion mode, write a 0 to the MODE bit in the Config register.

#### 10.4.2.2 Continuous-Conversion Mode

In continuous-conversion mode (MODE bit set to 0), the ADS1118 continuously performs conversions. When a conversion completes, the ADS1118 places the result in the Conversion register and immediately begins another conversion. To switch to single-shot mode, write a 1 to the MODE bit in the Config register, or reset the device.

#### 10.4.3 Duty Cycling for Low Power

The noise performance of a  $\Delta\Sigma$  ADC generally improves when lowering the output data rate because more samples of the internal modulator can be averaged to yield one conversion result. In applications where power consumption is critical, the improved noise performance at low data rates may not be required. For these applications, the ADS1118 supports duty cycling that can yield significant power savings by periodically requesting high data rate readings at an effectively lower data rate. For example, an ADS1118 in power-down state with a data rate set to 860 SPS can be operated by a microcontroller that instructs a single-shot conversion every 125 ms (8 SPS). Because a conversion at 860 SPS only requires approximately 1.2 ms, the ADS1118 enters power-down state for the remaining 123.8 ms. In this configuration, the ADS1118 consumes approximately 1/100th the power that is otherwise consumed in continuous conversion mode. The duty cycling rate is completely arbitrary and is defined by the master controller. The ADS1118 offers lower data rates that do not implement duty cycling and also offers improved noise performance if required.

# 10.5 Programming

#### 10.5.1 Serial Interface

The SPI-compatible serial interface consists of either four signals ( $\overline{CS}$ , SCLK, DIN, and DOUT/ $\overline{DRDY}$ ), or three signals (in which case  $\overline{CS}$  may be tied low). The interface is used to read conversion data, read and write registers, and control device operation.

# 10.5.2 Chip Select (CS)

The chip select pin ( $\overline{\text{CS}}$ ) selects the ADS1118 for SPI communication. This feature is useful when multiple devices share the same serial bus. Keep  $\overline{\text{CS}}$  low for the duration of the serial communication. When  $\overline{\text{CS}}$  is taken high, the serial interface is reset, SCLK is ignored, and DOUT/ $\overline{\text{DRDY}}$  enters a high-impedance state. In this state, DOUT/ $\overline{\text{DRDY}}$  cannot provide data-ready indication. In situations where multiple devices are present and DOUT/ $\overline{\text{DRDY}}$  must be monitored, lower  $\overline{\text{CS}}$  periodically. At this point, the DOUT/ $\overline{\text{DRDY}}$  pin either immediately goes high to indicate that no new data are available, or immediately goes low to indicate that new data are present in the Conversion register and are available for transfer. New data can be transferred at any time without concern of data corruption. When a transmission starts, the current result is locked into the output shift register and does not change until the communication completes. This system avoids any possibility of data corruption.

#### 10.5.3 Serial Clock (SCLK)

The serial clock (SCLK) features a Schmitt-triggered input and is used to clock data on the DIN and DOUT/DRDY pins into and out of the ADS1118. Even though the input has hysteresis, TI recommends keeping SCLK as clean as possible to prevent glitches from accidentally shifting the data. If SCLK is held low for 28 ms, the serial interface resets and the next SCLK pulse starts a new communication cycle. This time-out feature can be used to recover communication when a serial interface transmission is interrupted. When the serial interface is idle, hold SCLK low.

#### 10.5.4 Data Input (DIN)

The data input pin (DIN) is used along with SCLK to send data to the ADS1118. The device latches data on DIN on the SCLK falling edge. The ADS1118 never drives the DIN pin.

#### 10.5.5 Data Output and Data Ready (DOUT/DRDY)

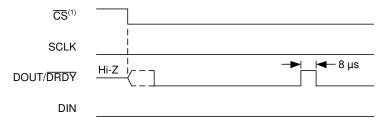

The data output and data ready pin (DOUT/DRDY) is used with SCLK to read conversion and register data from the ADS1118. Data on DOUT/DRDY are shifted out on the SCLK rising edge. DOUT/DRDY is also used to indicate that a conversion is complete and new data are available. This pin transitions low when new data are ready for retrieval. DOUT/DRDY is also able to trigger a microcontroller to start reading data from the ADS1118. In continuous-conversion mode, DOUT/DRDY transitions high again 8 µs before the next data ready signal (DOUT/DRDY low) if no data are retrieved from the device. This transition is shown in Figure 38. Complete the data transfer before DOUT/DRDY returns high.

(1)  $\overline{\text{CS}}$  may be held low. If  $\overline{\text{CS}}$  is low, DOUT/ $\overline{\text{DRDY}}$  asserts low indicating new data are available.

Figure 38. DOUT/DRDY Behavior Without Data Retrieval in Continuous Conversion Mode

When  $\overline{\text{CS}}$  is high,  $\overline{\text{DOUT}/\text{DRDY}}$  is configured by default with a weak internal pullup resistor. This feature reduces the risk of DOUT/DRDY floating near midsupply and causing leakage current in the master device. To disable this pullup resistor and place the device into a high-impedance state, set the PULL\_UP\_EN bit to 0 in the Config Register.

# **Programming (continued)**

#### 10.5.6 Data Format

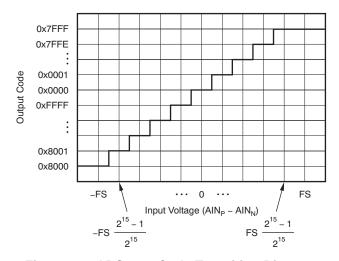

The ADS1118 provides 16 bits of data in binary twos complement format. A positive full-scale input produces an output code of 7FFFh and a negative full-scale input produces an output code of 8000h. The output clips at these codes for signals that exceed full-scale. Table 5 summarizes the ideal output codes for different input signals. Figure 39 shows code transitions versus input voltage.

Table 5. Input Signal versus Ideal Output Code

(1) Excludes the effects of noise, INL, offset, and gain errors.

Figure 39. ADS1118 Code Transition Diagram

# 10.5.7 Data Retrieval

Data is written to and read from the ADS1118 in the same manner for both single-shot and continuous conversion modes, without having to issue any commands. The operating mode for the ADS1118 is selected by the MODE bit in the Config register.

Set the MODE bit to 0 to put the device in continuous-<u>con</u>version mode. In continuous-conversion mode, the device is constantly starting new conversions even when <del>CS</del> is high.

Set the MODE bit to 1 for single-shot mode. In single-shot mode, a new conversion only starts by writing a 1 to the SS bit.

The conversion data are always buffered, and retain the current data until replaced by new conversion data. Therefore, data can be read at any time without concern of data corruption. When DOUT/DRDY asserts low, indicating that new conversion data are ready, the conversion data are read by shifting the data out on DOUT/DRDY. The MSB of the data (bit 15) on DOUT/DRDY is clocked out on the first SCLK rising edge. At the same time that the conversion result is clocked out of DOUT/DRDY, new Config register data are latched on DIN on the SCLK falling edge.

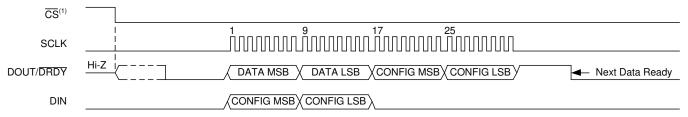

The ADS1118 also offers the possibility of direct readback of the Config register settings in the same data transmission cycle. One complete data transmission cycle consists of either 32 bits (when the Config register data readback is used) or 16 bits (only used when the CS line can be controlled and is not permanently tied low).

## 10.5.7.1 32-Bit Data Transmission Cycle

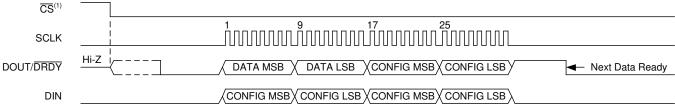

The data in a 32-bit data transmission cycle consists of four bytes: two bytes for the conversion result, and an additional two bytes for the Config Register read back. The device always reads the MSB first.

Write the same Config register setting twice during one transmission cycle as shown in Figure 40. If convenient, write the Config register setting once during the first half of the transmission cycle, and then hold the DIN pin either low (as shown in Figure 41) or high during the second half of the cycle. If no update to the Config register is required, hold the DIN pin either low or high during the entire transmission cycle. The Config register setting written in the first two bytes of a 32-bit transmission cycle is read back in the last two bytes of the same cycle.

(1)  $\overline{\text{CS}}$  can be held low if the ADS1118 does not share the serial bus with another device. If  $\overline{\text{CS}}$  is low, DOUT/ $\overline{\text{DRDY}}$  asserts low indicating new data are available.

Figure 40. 32-Bit Data Transmission Cycle With Config Register Readback

(1)  $\overline{\text{CS}}$  can be held low if the ADS1118 does not share the serial bus with another device. If  $\overline{\text{CS}}$  is low, DOUT/ $\overline{\text{DRDY}}$  asserts low indicating new data are available.

Figure 41. 32-Bit Data Transmission Cycle: DIN Held Low

## 10.5.7.2 16-Bit Data Transmission Cycle

If Config Register data are not required to be readback, the ADS1118 conversion data can also be clocked out in a short 16-bit data transmission cycle, as shown in Figure 42. Therefore, CS must be taken high after the 16th SCLK cycle. Taking  $\overline{CS}$  high resets the SPI interface. The next time  $\overline{CS}$  is taken low, data transmission starts with the currently buffered conversion result on the first SCLK rising edge. If DOUT/DRDY is low when data retrieval starts, the conversion buffer is already updated with a new result. Otherwise, if DOUT/DRDY is high, the same result from the previous data transmission cycle is read.

Figure 42. 16-Bit Data Transmission Cycle

# 10.6 Register Maps

The ADS1118 has two registers that are accessible through the SPI interface. The Conversion Register contains the result of the last conversion. The Config Registerallows the user to change the ADS1118 operating modes and query the status of the devices.

## 10.6.1 Conversion Register [reset = 0000h]

The 16-bit Conversion register contains the result of the last conversion in binary twos complement format. Following power up, the Conversion register is cleared to 0, and remains 0 until the first conversion is completed. The register format is shown in Figure 43.

Figure 43. Conversion Register

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |

|------|------|------|------|------|------|------|------|

| D15  | D14  | D13  | D12  | D11  | D10  | D9   | D8   |

| R-0h |

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

| R-0h |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## **Table 6. Conversion Register Field Descriptions**

| Bit  | Field   | Туре | Reset | Description              |

|------|---------|------|-------|--------------------------|

| 15:0 | D[15:0] | R    | 0000h | 16-bit conversion result |

# 10.6.2 Config Register [reset = 058Bh]

The 16-bit Config register can be used to control the ADS1118 operating mode, input selection, data rate, full-scale range, and temperature sensor mode. The register format is shown in Figure 44.

Figure 44. Config Register

| 15      | 14 13  |          | 12      | 11         | 10       | 9    | 8        |

|---------|--------|----------|---------|------------|----------|------|----------|

| SS      |        | MUX[2:0] |         |            | PGA[2:0] |      | MODE     |

| R/W-0h  | R/W-0h |          |         |            | R/W-2h   |      | R/W-1h   |

| 7       | 6      | 5        | 4       | 3          | 2        | 1    | 0        |

| DR[2:0] |        |          | TS_MODE | PULL_UP_EN | NOP      | 1:0] | Reserved |

|         | R/W-4h |          | R/W-0h  | R/W-1h     | R/W      | -1h  | R-1h     |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## **Table 7. Config Register Field Descriptions**

| Bit   | Field    | Туре   | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|-------|----------|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|       | 15 SS I  | R/W 0h |       | Single-shot conversion start  This bit is used to start a single conversion. SS can only be written when in power-down state and has no effect when a conversion is ongoing.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 15    |          |        | Oh    | When writing: 0 = No effect 1 = Start a single conversion (when in power-down state) Always reads back 0 (default).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|       |          |        |       | Input multiplexer configuration These bits configure the input multiplexer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 14:12 | MUX[2:0] | R/W    | 0h    | $\begin{array}{l} 000 = \text{AIN}_P \text{ is AINO and AIN}_N \text{ is AIN1 (default)} \\ 001 = \text{AIN}_P \text{ is AIN0 and AIN}_N \text{ is AIN3} \\ 010 = \text{AIN}_P \text{ is AIN1 and AIN}_N \text{ is AIN3} \\ 011 = \text{AIN}_P \text{ is AIN2 and AIN}_N \text{ is AIN3} \\ 100 = \text{AIN}_P \text{ is AIN0 and AIN}_N \text{ is GND} \\ 101 = \text{AIN}_P \text{ is AIN1 and AIN}_N \text{ is GND} \\ 110 = \text{AIN}_P \text{ is AIN2 and AIN}_N \text{ is GND} \\ 111 = \text{AIN}_P \text{ is AIN3 and AIN}_N \text{ is GND} \\ 111 = \text{AIN}_P \text{ is AIN3 and AIN}_N \text{ is GND} \\ \end{array}$ |  |  |

# **Table 7. Config Register Field Descriptions (continued)**

| Bit  | Field      | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11:9 | PGA[2:0]   | R/W  | 2h    | Programmable gain amplifier configuration These bits configure the programmable gain amplifier.  000 = FSR is ±6.144 V <sup>(1)</sup> 001 = FSR is ±4.096 V <sup>(1)</sup> 010 = FSR is ±2.048 V (default) 011 = FSR is ±1.024 V 100 = FSR is ±0.512 V 101 = FSR is ±0.256 V 110 = FSR is ±0.256 V 111 = FSR is ±0.256 V                                                                                                                                                                                                                                                                        |

| 8    | MODE       | R/W  | 1h    | Device operating mode This bit controls the ADS1118 operating mode.  0 = Continuous conversion mode 1 = Power-down and single-shot mode (default)                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7:5  | DR[2:0]    | R/W  | 4h    | Data rate These bits control the data rate setting.  000 = 8 SPS 001 = 16 SPS 010 = 32 SPS 011 = 64 SPS 100 = 128 SPS (default) 101 = 250 SPS 110 = 475 SPS 111 = 860 SPS                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4    | TS_MODE    | R/W  | Oh    | Temperature sensor mode This bit configures the ADC to convert temperature or input signals.  0 = ADC mode (default) 1 = Temperature sensor mode                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3    | PULL_UP_EN | R/W  | 1h    | Pullup enable This bit enables a weak internal pullup resistor on the DOUT/DRDY pin only when CS is high. When enabled, an internal 400-kΩ resistor connects the bus line to supply. When disabled, the DOUT/DRDY pin floats.  0 = Pullup resistor disabled on DOUT/DRDY pin 1 = Pullup resistor enabled on DOUT/DRDY pin (default)                                                                                                                                                                                                                                                             |

| 2:1  | NOP[1:0]   | R/W  | 1h    | No operation The NOP[1:0] bits control whether data are written to the Config register or not. For data to be written to the Config register, the NOP[1:0] bits must be '01'. Any other value results in a NOP command. DIN can be held high or low during SCLK pulses without data being written to the Config register.  00 = Invalid data, do not update the contents of the Config register 01 = Valid data, update the Config register (default) 10 = Invalid data, do not update the contents of the Config register 11 = Invalid data, do not update the contents of the Config register |

| 0    | Reserved   | R    | 1h    | Reserved Writing either 0 or 1 to this bit has no effect. Always reads back 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

<sup>(1)</sup> This parameter expresses the full-scale range of the ADC scaling. No more than VDD + 0.3 V must be applied to this device.

# 11 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

# 11.1 Application Information

The ADS1118 is a precision, 16-bit  $\Delta\Sigma$  ADC that offers many integrated features to ease the measurement of the most common sensor types including various type of temperature and bridge sensors. The following sections give example circuits and suggestions for using the ADS1118 in various situations.

## 11.1.1 Serial Interface Connections

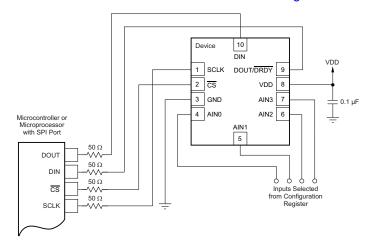

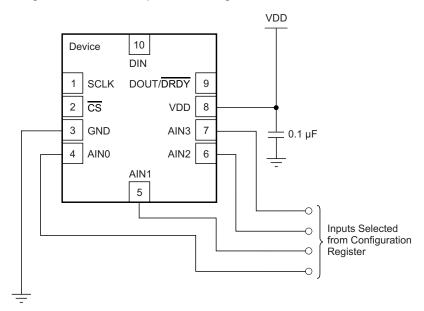

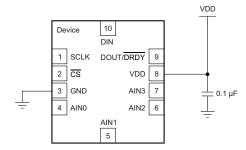

The principle serial interface connections for the ADS1118 are shown in Figure 45.

Figure 45. Typical Connections of the ADS1118

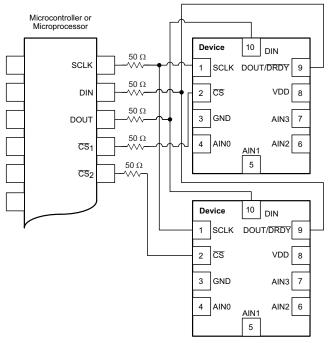

Most microcontroller SPI peripherals can operate with the ADS1118. The interface operates in SPI mode 1 where CPOL = 0 and CPHA = 1. In SPI mode 1, SCLK idles low and data are launched or changed only on SCLK rising edges; data are latched or read by the master and slave on SCLK falling edges. Details of the SPI communication protocol employed by the ADS1118 can be found in the *Timing Requirements: Serial Interface* section.

It is a good practice to place  $50-\Omega$  resistors in the series path to each of the digital pins to provide some short circuit protection. Care must be taken to still meet all SPI timing requirements because these additional series resistors along with the bus parasitic capacitances present on the digital signal lines could slew the signals.

The fully-differential input of the ADS1118 is ideal for connecting to differential sources (such as thermocouples and thermistors) with a moderately low source impedance. Although the ADS1118 can read fully-differential signals, the device cannot accept negative voltages on either of its inputs because of ESD protection diodes on each pin. When an input exceeds supply or drops below ground, these diodes turn on to prevent any ESD damage to the device.

#### 11.1.2 GPIO Ports for Communication

Most microcontrollers have programmable input/output (I/O) pins that can be set in software to act as inputs or outputs. If an SPI controller is not available, the ADS1118 can be connected to GPIO pins and the SPI bus protocol can be simulated. Using GPIO pins to generate the SPI interface only requires that the pins be configured as push or pull inputs or outputs. Furthermore, if the SCLK line is held low for more than 28 ms, the communication times out. This condition means that the GPIO ports must be capable of providing SCLK pulses with no more than 28 ms between pulses.

## 11.1.3 Analog Input Filtering

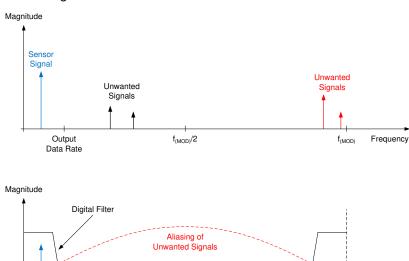

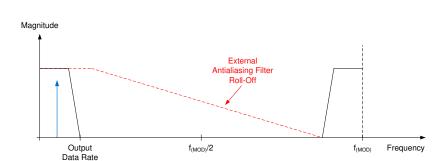

Analog input filtering serves two purposes: first, to limit the effect of aliasing during the sampling process and second, to reduce external noise from being a part of the measurement.

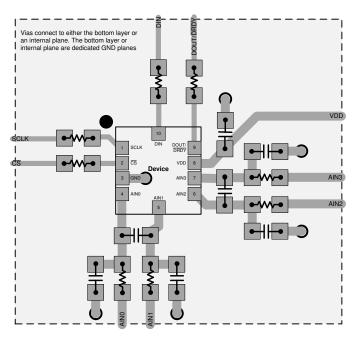

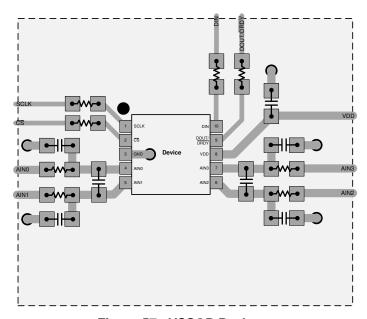

As with any sampled system, aliasing can occur if proper antialias filtering is not in place. Aliasing occurs when frequency components are present in the input signal that are higher than half the sampling frequency of the ADC (also known as the *Nyquist frequency*). These frequency components fold back and show up in the actual frequency band of interest below half the sampling frequency. The filter response of the digital filter repeats at multiples of the sampling frequency, also known as the modulator frequency ( $f_{(MOD)}$ ), as shown in Figure 46. Signals or noise up to a frequency where the filter response repeats are attenuated to a certain amount by the digital filter depending on the filter architecture. Any frequency components present in the input signal around the modulator frequency or multiples thereof are not attenuated and alias back into the band of interest, unless attenuated by an external analog filter.