🕳 Order

Now

### BQ24725A

JAJSGI6C - SEPTEMBER 2011 - REVISED JANUARY 2020

# BQ24725A N チャネル・パワー MOSFET セレクタ搭載、SMBus 1~4 セル Li+ 降圧バッテリ充電コントローラ

# 1 特長

Texas

INSTRUMENTS

- スイッチング周波数を 615kHz、750kHz、885kHz にプログラム可能な、SMBus ホスト制御の NMOS-NMOS 同期整流降圧コンバータ

- N チャネル MOSFET でシステム電源を自動選択 (アダプタ、内部チャージ・ポンプによるバッテリ 駆動)

- 過電圧保護、過電流保護、バッテリ、インダク タ、MOSFET 短絡保護による高度な安全性機能

- 入力電流、充電電圧、充電電流の制限値をプログ ラム可能

- 充電電圧 (最大 19.2V) の精度:±0.5%

- 充電電流 (最大 8.128A) の精度:±3%

- 入力電流 (最大 8.064A) の精度:±3%

- 20x アダプタ電流または充電電流アンプの出力精度:±2%

- バッテリ放電スレッショルドをプログラム可能、 バッテリ LEARN 機能付き

- アダプタ検出およびインジケータをプログラム可能

- ソフトスタート内蔵

- ループ補償を内蔵

- ILIM ピンでのリアルタイムのシステム制御により 充電電流を制限

- AC アダプタの動作範囲:4.5V~24V

- オフ状態のバッテリ放電電流:5µA

- アダプタのスタンバイ時静止電流: 0.65mA (最大 0.8mA)

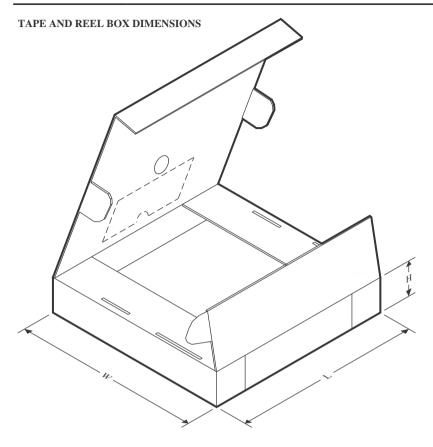

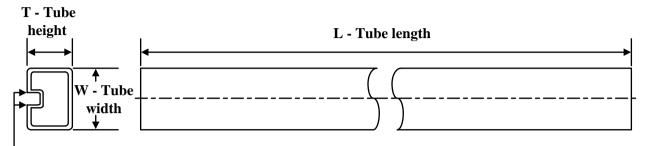

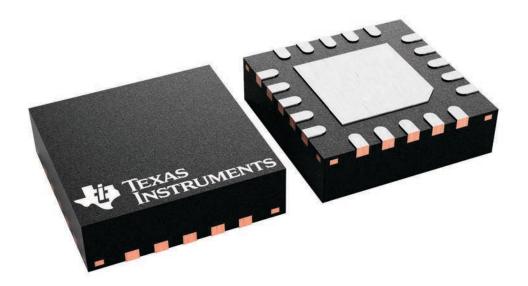

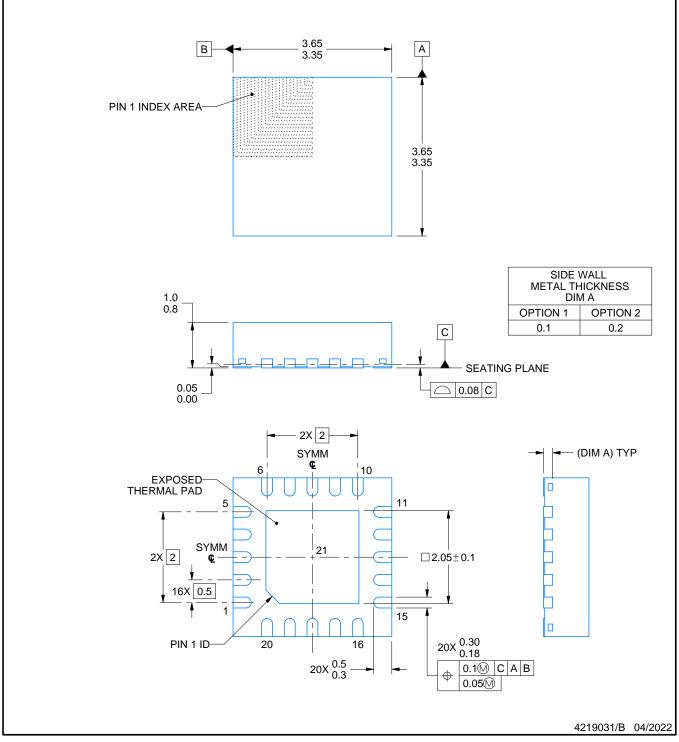

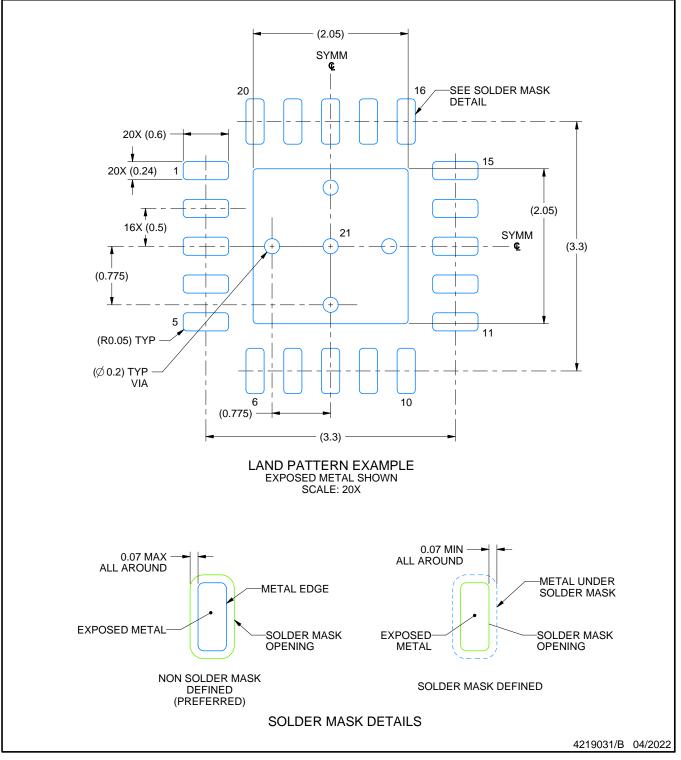

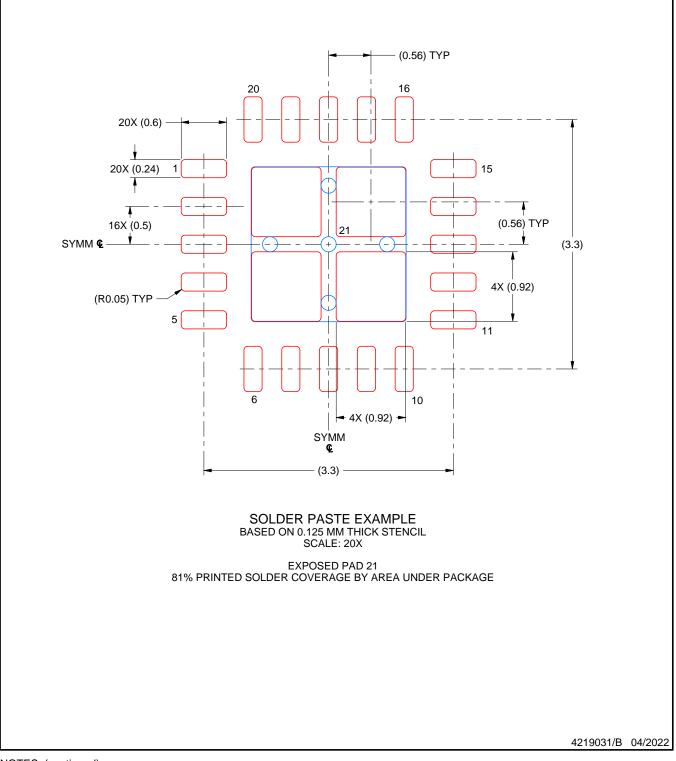

- 20ピン、3.5×3.5mm<sup>2</sup>のVQFNパッケージ

# 2 アプリケーション

- 携帯用ノート PC、UMPC、超薄型ノート PC、 ネットブック

- ハンドヘルド端末

- 産業用および医療用機器

- 携帯機器

# 3 概要

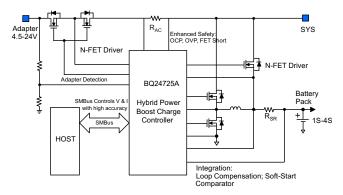

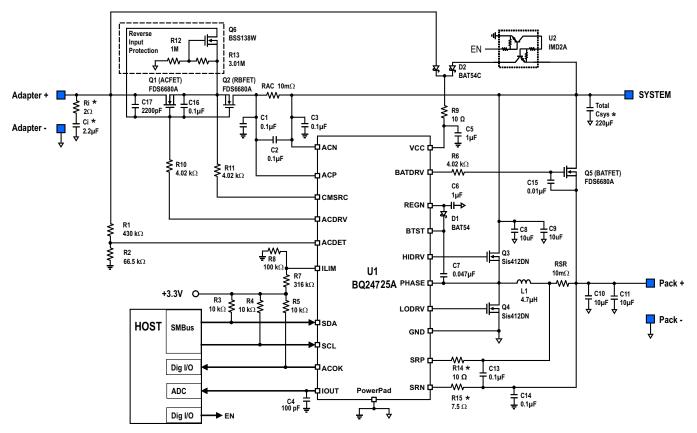

BQ24725A は複数の種類のバッテリに対応する、スペースに制約のある充電アプリケーションに適した、部品数が少ない高効率の同期整流バッテリ充電器です。

BQ24725A は 2 つのチャージ・ポンプを利用して、N チャネル MOSFET (ACFET、RBFET、BATFET) を別々 に駆動し、システム電源を自動的に選択します。

入力電流、充電電流、充電電圧のDACをSMBusで制御 することで、非常に高いレギュレーション精度が得られま す。また、これらはシステム電源管理のマイクロコントロー ラで簡単にプログラムできます。

BQ24725A は、内部入力電流レジスタまたは外部の ILIM ピンを使用して PWM のデューティ・サイクルを低減 し、充電電流を低減します。

BQ24725A は 1、2、3、4 直列の Li+ セルを充電できます。

製品情報<sup>(1)</sup>

|          | 34466 112 114 |               |

|----------|---------------|---------------|

| 型番       | パッケージ         | 本体サイズ(公称)     |

| BQ24725A | VQFN (20)     | 3.50mm×3.50mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

# 目次

9

| 1 | 特長   | 1                                  |

|---|------|------------------------------------|

| 2 | アプ   | リケーション1                            |

| 3 | 概要   | ·1                                 |

| 4 | 改訂   | 「履歴2                               |

| 5 | Pin  | Configuration and Functions 3      |

| 6 | Spe  | cifications 4                      |

|   | 6.1  | Absolute Maximum Ratings 4         |

|   | 6.2  | ESD Ratings 5                      |

|   | 6.3  | Recommended Operating Conditions 5 |

|   | 6.4  | Thermal Information 5              |

|   | 6.5  | Electrical Characteristics 6       |

|   | 6.6  | Timing Characteristics 10          |

|   | 6.7  | Typical Characteristics 10         |

| 7 | Para | ameter Measurement Information 12  |

| 8 | Deta | ailed Description 13               |

|   | 8.1  | Overview 13                        |

|   | 8.2  | Functional Block Diagram 14        |

|   | 8.3  | Feature Description 15             |

#### 改訂履歴 4

| R | Revision B (November 2018) から Revision C に変更 P     |    |  |

|---|----------------------------------------------------|----|--|

| • | タイトル 変更                                            |    |  |

| • | Added Description for Figure 18                    | 28 |  |

| • | Added Simplified System without Power Path section |    |  |

|   |                                                    |    |  |

# Revision A (August 2014) から Revision B に変更

| • | Changed the Notes to Figure 27 for additional resistor requirement to the application circuit when using low $V_{GS}$ input FETs |    |

|---|----------------------------------------------------------------------------------------------------------------------------------|----|

| • |                                                                                                                                  |    |

| • | Added the Application NOTE                                                                                                       | 28 |

| • | Moved T <sub>stg</sub> From: Handling Ratings table To: Absolute Maximum Ratings                                                 | 5  |

|   | Changed Handling Ratings To: ESD Ratings                                                                                         |    |

| • | 新しい TI 標準にフォーマットを変更                                                | 1 |

|---|--------------------------------------------------------------------|---|

| • | 製品情報の表を追加                                                          | 1 |

| • | Added LODRV, HIDRV, and PHASE (2% duty cycle) to the Abs Max Table | 4 |

| • | Added the Handling Ratings table                                   | 5 |

8.4 Device Functional Modes...... 16 8.5 Register Maps ..... 22

Application and Implementation ...... 28 11.1 Layout Guidelines ...... 38 11.2 Layout Example ...... 39 12 デバイスおよびドキュメントのサポート ...... 40 12.1 デベロッパー・ネットワークの製品に関する免責事項.40 12.2 ドキュメントの更新通知を受け取る方法...... 40 12.3 サポート・リソース...... 40 12.4 商標...... 40 12.5 静電気放電に関する注意事項 ...... 40 12.6 Glossary ...... 40 13 メカニカル、パッケージ、および注文情報 ...... 40

| www.ti.com |  |

|------------|--|

|            |  |

|            |  |

| P | a | g | e |

|---|---|---|---|

| Г | a | y | C |

Page

### BQ24725A JAJSGI6C – SEPTEMBER 2011 – REVISED JANUARY 2020

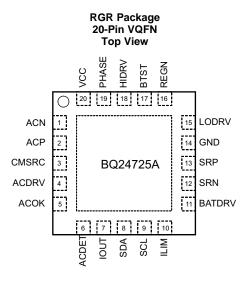

# 5 Pin Configuration and Functions

### **Pin Functions**

|     | PIN    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. | NAME   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

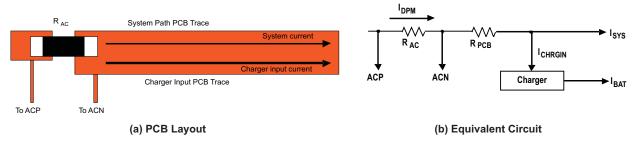

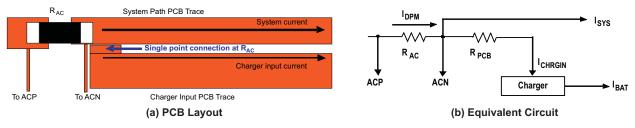

| 1   | ACN    | Input current sense resistor negative input. Place an optional 0.1µF ceramic capacitor from ACN to GND for common-<br>mode filtering. Place a 0.1µF ceramic capacitor from ACN to ACP to provide differential mode filtering.                                                                                                                                                                                                                                                                            |  |  |

| 2   | ACP    | Input current sense resistor positive input. Place a 0.1µF ceramic capacitor from ACP to GND for common-mode filtering. Place a 0.1µF ceramic capacitor from ACN to ACP to provide differential-mode filtering.                                                                                                                                                                                                                                                                                          |  |  |

| 3   | CMSRC  | ACDRV charge pump source input. Place a $4k\Omega$ resistor from CMSRC to the common source of ACFET (Q1) and RBFET (Q2) limits the in-rush current on CMSRC pin.                                                                                                                                                                                                                                                                                                                                        |  |  |

| 4   | ACDRV  | Charge pump output to drive both adapter input n-channel MOSFET (ACFET) and reverse blocking n-channel MOSFET (RBFET). ACDRV voltage is 6V above CMSRC when voltage on ACDET pin is between 2.4V to 3.15V, voltage on VCC pin is above UVLO and voltage on VCC pin is 275mV above voltage on SRN pin so that ACFET and RBFET can be turned on to power the system by AC adapter. Place a $4k\Omega$ resistor from ACDRV to the gate of ACFET and RBFET limits the in-rush current on ACDRV pin.          |  |  |

| 5   | ACOK   | AC adapter detection open drain output. It is pulled HIGH to external pull-up supply rail by external pull-up resistor when voltage on ACDET pin is between 2.4V and 3.15V, and voltage on VCC is above UVLO and voltage on VCC pin is 275mV above voltage on SRN pin, indicating a valid adapter is present to start charge. If any one of the above conditions can not meet, it is pulled LOW to GND by internal MOSFET. Connect a 10k $\Omega$ pull up resistor from ACOK to the pull-up supply rail. |  |  |

| 6   | ACDET  | Adapter detection input. Program adapter valid input threshold by connecting a resistor divider from adapter input to ACDET pin to GND pin. When ACDET pin is above 0.6V and VCC is above UVLO, REGN LDO is present, ACOK comparator and IOUT are both active.                                                                                                                                                                                                                                           |  |  |

| 7   | IOUT   | Buffered adapter or charge current output, selectable with SMBus command ChargeOption(). IOUT voltage is 20 times the differential voltage across sense resistor. Place a 100pF or less ceramic decoupling capacitor from IOUT pin to GND.                                                                                                                                                                                                                                                               |  |  |

| 8   | SDA    | SMBus open-drain data I/O. Connect to SMBus data line from the host controller or smart battery. Connect a $10k\Omega$ pull-<br>up resistor according to SMBus specifications.                                                                                                                                                                                                                                                                                                                           |  |  |

| 9   | SCL    | SMBus open-drain clock input. Connect to SMBus clock line from the host controller or smart battery. Connect a $10k\Omega$ pull-up resistor according to SMBus specifications.                                                                                                                                                                                                                                                                                                                           |  |  |

| 10  | ILIM   | Charge current limit input. Program ILIM voltage by connecting a resistor divider from system reference 3.3V rail to ILIM pin to GND pin. The lower of ILIM voltage or DAC limit voltage sets charge current regulation limit. To disable the control on ILIM, set ILIM above 1.6V. Once voltage on ILIM pin falls below 75mV, charge is disabled. Charge is enabled when ILIM pin rises above 105mV.                                                                                                    |  |  |

| 11  | BATDRV | Charge pump output to drive Battery to System n-channel MOSFET (BATFET). BATDRV voltage is 6V above SRN to turn on BATFET to power the system from battery. BATDRV voltage is SRN voltage to turn off BATFET to power system from AC adapter. Place a $4k\Omega$ resistor from BATDRV to the gate of BATFET limits the in-rush current on BATDRV pin.                                                                                                                                                    |  |  |

TEXAS INSTRUMENTS

www.ti.com

### Pin Functions (continued)

| PIN       |       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.       | NAME  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 12 SRN    |       | Charge current sense resistor negative input. SRN pin is for battery voltage sensing as well. Connect SRN pin to a 7.5 $\Omega$ resistor first then from resistor another terminal connect a 0.1µF ceramic capacitor to GND for common-mode filtering and connect to current sensing resistor. Connect a 0.1µF ceramic capacitor between current sensing resistor to provide differential mode filtering. See application information about negative output voltage protection for hard shorts on battery to ground or battery reverse connection by adding small resistor. |

| 13 SRP    |       | Charge current sense resistor positive input. Connect SRP pin to a 10 $\Omega$ resistor first then from resistor another terminal connect to current sensing resistor. Connect a 0.1µF ceramic capacitor between current sensing resistor to provide differential mode filtering. See application information about negative output voltage protection for hard shorts on battery to ground or battery reverse connection by adding small resistor.                                                                                                                         |

| 14        | GND   | IC ground. On PCB layout, connect to analog ground plane, and only connect to power ground plane through the power pad underneath IC.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15 LODRV  |       | Low side power MOSFET driver output. Connect to low side n-channel MOSFET gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 16        | REGN  | Linear regulator output. REGN is the output of the 6V linear regulator supplied from VCC. The LDO is active when voltage on ACDET pin is above 0.6V and voltage on VCC is above UVLO. Connect a 1µF ceramic capacitor from REGN to GND.                                                                                                                                                                                                                                                                                                                                     |

| 17        | BTST  | High side power MOSFET driver power supply. Connect a 0.047µF capacitor from BTST to PHASE, and a bootstrap Schottky diode from REGN to BTST.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 18        | HIDRV | High side power MOSFET driver output. Connect to the high side n-channel MOSFET gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 19        | PHASE | High side power MOSFET driver source. Connect to the source of the high side n-channel MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

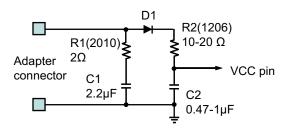

| 20        | VCC   | Input supply, diode OR from adapter or battery voltage. Use $10\Omega$ resistor and $1\mu$ F capacitor to ground as low pass filter to limit inrush current.                                                                                                                                                                                                                                                                                                                                                                                                                |

| PowerPAD™ |       | Exposed pad beneath the IC. Analog ground and power ground star-connected only at the PowerPAD plane. Always solder PowerPad to the board, and have vias on the PowerPAD plane connecting to analog ground and power ground planes. It also serves as a thermal pad to dissipate the heat.                                                                                                                                                                                                                                                                                  |

# 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup> (2)

|                            |                                                | MIN  | MAX | UNIT |

|----------------------------|------------------------------------------------|------|-----|------|

|                            | SRN, SRP, ACN, ACP, CMSRC, VCC                 | -0.3 | 30  |      |

|                            | PHASE                                          | -2   | 30  |      |

|                            | ACDET, SDA, SCL, LODRV, REGN, IOUT, ILIM, ACOK | -0.3 | 7   |      |

| Voltage range              | BTST, HIDRV, ACDRV, BATDRV                     | -0.3 | 36  |      |

|                            | LODRV (2% duty cycle)                          | -4   | 7   | V    |

|                            | HIDVR (2% duty cycle)                          | -4   | 36  |      |

|                            | PHASE (2% duty cycle)                          | -4   | 30  |      |

| Maximum difference voltage | SRP–SRN, ACP–ACN                               | -0.5 | 0.5 |      |

| Junction temperature       | range, T <sub>J</sub>                          | -40  | 155 | °C   |

| Storage temperature        | range, T <sub>stg</sub>                        | -55  | 155 | °C   |

(1) Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to GND if not specified. Currents are positive into, negative out of the specified terminal. Consult Packaging Section of the data book for thermal limitations and considerations of packages.

# 6.2 ESD Ratings

|                    |                         |                                                                                                       | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>                           | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all $\ensuremath{\text{pins}}^{(2)}$ | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                   |                                                | MIN  | NOM MAX | UNIT |

|-----------------------------------|------------------------------------------------|------|---------|------|

| Voltage range                     | SRN, SRP, ACN, ACP, CMSRC, VCC                 | 0    | 24      |      |

|                                   | PHASE                                          | -2   | 24      | V    |

|                                   | ACDET, SDA, SCL, LODRV, REGN, IOUT, ILIM, ACOK | 0    | 6.5     |      |

|                                   | BTST, HIDRV, ACDRV, BATDRV                     | 0    | 30      |      |

| Maximum difference voltage        | SRP-SRN, ACP-ACN                               | -0.2 | 0.2     | V    |

| Junction temperature range, $T_J$ |                                                | 0    | 125     | °C   |

### 6.4 Thermal Information

|                     |                                              | BQ24725A   |                |

|---------------------|----------------------------------------------|------------|----------------|

|                     | THERMAL METRIC <sup>(1)</sup>                | RGR [VQFN] | UNIT           |

|                     |                                              | 20 PIN     |                |

| $R_{\theta JA}$     | Junction-to-ambient thermal resistance       | 46.8       |                |

| R <sub>0JCtop</sub> | Junction-to-case (top) thermal resistance    | 56.9       |                |

| $R_{\theta JB}$     | Junction-to-board thermal resistance         | 46.6       | 8 <b>0</b> AA/ |

| ΨJT                 | Junction-to-top characterization parameter   | 0.6        | °C/W           |

| ΨЈВ                 | Junction-to-board characterization parameter | 15.3       |                |

| $R_{\theta JCbot}$  | Junction-to-case (bottom) thermal resistanc  | 4.4        |                |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

**BQ24725A**

JAJSGI6C - SEPTEMBER 2011 - REVISED JANUARY 2020

www.ti.com

ÈXAS NSTRUMENTS

# 6.5 Electrical Characteristics

4.5 V  $\leq$  V<sub>VCC</sub>  $\leq$  24 V, 0°C  $\leq$  T<sub>J</sub>  $\leq$  125°C, typical values are at T<sub>A</sub> = 25°C, with respect to GND (unless otherwise noted)

|                           | PARAMETER                                              | TEST CONDITIONS                                  | MIN                                                                      | TYP    | MAX   | UNIT |

|---------------------------|--------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------|--------|-------|------|

| OPERATING CO              | NDITIONS                                               | 1                                                |                                                                          |        |       |      |

| V <sub>VCC_OP</sub>       | VCC Input voltage operating range                      |                                                  | 4.5                                                                      |        | 24    | V    |

|                           | GE REGULATION                                          | Т                                                |                                                                          |        |       |      |

| VBAT_REG_RNG              | Battery voltage range                                  |                                                  |                                                                          |        |       | V    |

|                           |                                                        | ChargeVoltage() = 0x41A0H                        |                                                                          | 16.8   |       | V    |

|                           |                                                        |                                                  |                                                                          | 10 500 |       |      |

|                           |                                                        | ChargeVoltage() = 0x3130H                        |                                                                          | 12.592 |       | V    |

| V <sub>BAT_REG_ACC</sub>  | Charge voltage regulation accuracy                     |                                                  |                                                                          | 0.4    |       |      |

|                           |                                                        | ChargeVoltage() = 0x20D0H                        |                                                                          | 8.4    |       | V    |

|                           |                                                        |                                                  |                                                                          | 4 102  |       | V    |

|                           |                                                        | ChargeVoltage() = 0x1060H                        |                                                                          | 4.192  |       | v    |

|                           | ENT REGULATION                                         |                                                  | -0.7%                                                                    |        | 0.7%  |      |

|                           | Charge current regulation differential                 |                                                  |                                                                          |        |       |      |

| V <sub>IREG_CHG_RNG</sub> | voltage range                                          | $V_{IREG_{CHG}} = V_{SRP} - V_{SRN}$             | 0                                                                        |        | 81.28 | mV   |

|                           |                                                        | ChargeCurrent() = 0x100011                       | 3973                                                                     | 4096   | 4219  | mA   |

|                           |                                                        | ChargeCurrent() = 0x1000H                        | -3%                                                                      |        | 3%    |      |

|                           |                                                        | ChargeCurrent() = 0x0800H                        | 1946                                                                     | 2048   | 2150  | mA   |

|                           |                                                        |                                                  | -5%                                                                      |        | 5%    |      |

|                           | Charge current regulation accuracy $10m\Omega$         | ChargeCurrent() = 0x0200H                        | 410                                                                      | 512    | 614   | mA   |

| CHRG_REG_ACC              | current sensing resistor                               |                                                  | $\begin{tabular}{ c c c c } \hline & & & & & & & & & & & & & & & & & & $ |        |       |      |

|                           |                                                        | ChargeCurrent() = 0x0100H                        | 172                                                                      | 256    | 340   | mA   |

|                           |                                                        |                                                  | -33%                                                                     |        | 33%   |      |

|                           |                                                        | ChargeCurrent() = 0x0080H                        | 64                                                                       | 128    | 192   | mA   |

|                           |                                                        |                                                  | -50%                                                                     |        | 50%   |      |

| INPUT CURRENT             |                                                        | Т                                                |                                                                          |        |       |      |

| VIREG_DPM_RNG             | Input current regulation differential voltage<br>range | $V_{IREG_DPM} = V_{ACP} - V_{ACN}$               | 0                                                                        |        | 80.64 | mV   |

|                           |                                                        |                                                  | 3973                                                                     | 4096   | 4219  | mA   |

|                           |                                                        | InputCurrent() = 0x1000H                         |                                                                          |        |       |      |

|                           |                                                        |                                                  | 1946                                                                     | 2048   | 2150  | mA   |

|                           | Input current regulation accuracy $10m\Omega$          | InputCurrent() = 0x0800H                         | -5%                                                                      |        | 5%    |      |

| DPM_REG_ACC               | current sensing resistor                               |                                                  | 870                                                                      | 1024   | 1178  | mA   |

|                           |                                                        | InputCurrent() = 0x0400H                         | -15%                                                                     |        | 15%   |      |

|                           |                                                        |                                                  | 384                                                                      | 512    | 640   | mA   |

|                           |                                                        | InputCurrent() = 0x0200H                         | -25%                                                                     |        | 25%   |      |

|                           | T OR CHARGE CURRENT SENSE AMPLIFIEF                    | ۲                                                | · ·                                                                      |        |       |      |

| V <sub>ACP/N_OP</sub>     | Input common mode range                                | Voltage on ACP/ACN                               | 4.5                                                                      |        | 24    | V    |

| V <sub>SRP/N_OP</sub>     | Output common mode range                               | Voltage on SRP/SRN                               | 0                                                                        |        | 19.2  | V    |

| V <sub>IOUT</sub>         | IOUT output voltage range                              |                                                  | 0                                                                        |        | 3.3   | V    |

| I <sub>IOUT</sub>         | IOUT output current                                    |                                                  | 0                                                                        |        | 1     | mA   |

| A <sub>IOUT</sub>         | Current sense amplifier gain                           | V(ICOUT)/V(SRP-SRN) OF V(ACP-ACN)                |                                                                          | 20     |       | V/V  |

|                           |                                                        | $V_{(SRP-SRN)}$ or $V_{(ACP-ACN)} = 40.96mV$     | -2%                                                                      |        | 2%    |      |

|                           |                                                        | $V_{(SRP-SRN)}$ or $V_{(ACP-ACN)} = 20.48mV$     | -4%                                                                      |        | 4%    |      |

| V <sub>IOUT_ACC</sub>     | Current sense output accuracy                          | $V_{(SRP-SRN)}$ or $V_{(ACP-ACN)} = 10.24mV$     | -15%                                                                     |        | 15%   |      |

| - IOUT_AUU                |                                                        | $V_{(SRP-SRN)}$ or $V_{(ACP-ACN)} = 5.12mV$      | -20%                                                                     |        | 20%   |      |

|                           |                                                        | $V_{(SRP-SRN)}$ or $V_{(ACP-ACN)} = 2.56mV$      | -33%                                                                     |        | 33%   |      |

|                           |                                                        | $V_{(SRP-SRN)}$ or $V_{(ACP-ACN)} = 1.28mV$      | -50%                                                                     |        | 50%   |      |

| C <sub>IOUT_MAX</sub>     | Maximum output load capacitance                        | For stability with 0 to 1mA load                 |                                                                          |        | 100   | pF   |

| REGN REGULAT              | OR                                                     | 1                                                |                                                                          |        |       |      |

| V <sub>REGN_REG</sub>     | REGN regulator voltage                                 | $V_{VCC} > 6.5V, V_{ACDET} > 0.6V$ (0-45mA load) | 5.5                                                                      | 6      | 6.5   | V    |

# **Electrical Characteristics (continued)**

### 4.5 V $\leq$ V<sub>VCC</sub> $\leq$ 24 V, 0°C $\leq$ T<sub>J</sub> $\leq$ 125°C, typical values are at T<sub>A</sub> = 25°C, with respect to GND (unless otherwise noted)

|                             | PARAMETER                                                                                                                                                           | TEST CONDITIONS                                                                                                                   | MIN   | TYP  | MAX   | UNIT |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

|                             |                                                                                                                                                                     | $V_{\text{REGN}}$ = 0V, $V_{\text{VCC}}$ > UVLO charge enabled and not in TSHUT                                                   | 50    | 75   |       | mA   |

| IREGN_LIM                   | REGN current limit                                                                                                                                                  | $V_{\text{REGN}}$ = 0V, $V_{\text{VCC}}$ > UVLO charge disabled or in TSHUT                                                       | 7     | 14   |       | mA   |

| C <sub>REGN</sub>           | REGN output capacitor required for stability                                                                                                                        | $I_{LOAD} = 100\mu A \text{ to } 50 \text{mA}$                                                                                    |       | 1    |       | μF   |

| INPUT UNDERVO               | DLTAGE LOCKOUT COMPARATOR (UVLO)                                                                                                                                    | · · · · · · · · · · · · · · · · · · ·                                                                                             |       |      |       |      |

|                             | Under voltage rising threshold                                                                                                                                      | V <sub>VCC</sub> rising                                                                                                           | 3.5   | 3.75 | 4     | V    |

| UVLO                        | Under voltage hysteresis, falling                                                                                                                                   | V <sub>VCC</sub> falling                                                                                                          |       | 340  |       | mV   |

| FAST DPM COM                | PARATOR (FAST_DPM)                                                                                                                                                  |                                                                                                                                   |       |      |       |      |

| V <sub>FAST_DPM</sub>       | Fast DPM comparator stop charging rising t<br>across input sense resistor rising edge                                                                               | hreshold with respect to input current limit, voltage                                                                             | 103%  | 107% | 111%  |      |

| QUIESCENT CUP               | RRENT                                                                                                                                                               |                                                                                                                                   |       |      |       |      |

| I <sub>BAT_BATFET_OFF</sub> | Battery BATFET OFF STATE Current,<br>BATFET off,<br>I <sub>SRP</sub> + I <sub>SRN</sub> + I <sub>PHASE</sub> + I <sub>ACP</sub> + I <sub>ACN</sub>                  | $V_{VBAT}$ = 16.8V, VCC disconnect from battery, BATFET charge pump off, BATFET turns off, $T_{\rm J}$ = 0 to 85°C                |       |      | 5     | μA   |

| I <sub>BAT_BATFET_ON</sub>  | Battery BATFET ON STATE Current,<br>BATFET on,<br>I <sub>SRP</sub> + I <sub>SRN</sub> + I <sub>PHASE</sub> + I <sub>VCC</sub> + I <sub>ACP</sub> + I <sub>ACN</sub> | $V_{VBAT}$ = 16.8V, VCC connect from battery, BATFET charge pump on, BATFET turns on, $T_{\rm J}$ = 0 to 85°C                     |       |      | 25    | μA   |

| ISTANDBY                    | Standby quiescent current, $I_{VCC} + I_{ACP} + I_{ACN}$                                                                                                            | $V_{VCC}$ > UVLO, $V_{ACDET}$ > 0.6V, charge disabled,<br>T <sub>.1</sub> = 0 to 85°C                                             |       | 0.65 | 0.8   | mA   |

| I <sub>AC_NOSW</sub>        | Adapter bias current during charge,<br>I <sub>VCC</sub> + I <sub>ACP</sub> + I <sub>ACN</sub>                                                                       | $V_{VCC}$ > UVLO, 2.4V < $V_{ACDET}$ < 3.15V,<br>charge enabled, no switching, $T_J$ = 0 to 85°C                                  |       | 1.5  | 3     | mA   |

| I <sub>AC_SW</sub>          | Adapter bias current during charge, $I_{VCC} + I_{ACP} + I_{ACN}$                                                                                                   | V <sub>VCC</sub> > UVLO, 2.4V < V <sub>ACDET</sub> < 3.15V,<br>charge enabled, switching, MOSFET Sis412DN                         |       | 10   |       | mA   |

| ACOK COMPARA                | ATOR                                                                                                                                                                |                                                                                                                                   |       |      |       |      |

| V <sub>ACOK_RISE</sub>      | ACOK rising threshold                                                                                                                                               | V <sub>VCC</sub> > UVLO, V <sub>ACDET</sub> rising                                                                                | 2.376 | 2.4  | 2.424 | V    |

| VACOK_FALL_HYS              | ACOK falling hysteresis                                                                                                                                             | V <sub>VCC</sub> > UVLO, V <sub>ACDET</sub> falling                                                                               | 35    | 55   | 75    | mV   |

|                             |                                                                                                                                                                     | V <sub>VCC</sub> > UVLO, V <sub>ACDET</sub> rising above 2.4V,<br>First time OR ChargeOption() bit [15] = 0                       | 100   | 150  | 200   | ms   |

| $V_{ACOK_RISE_DEG}$         | ACOK rising deglitch (Specified by design)                                                                                                                          | V <sub>VCC&gt;</sub> UVLO, V <sub>ACDET</sub> rising above 2.4V,<br>(NOT First time) AND ChargeOption() bit [15] = 1<br>(Default) | 0.9   | 1.3  | 1.7   | s    |

| V <sub>WAKEUP_RISE</sub>    | WAKEUP detect rising threshold                                                                                                                                      | V <sub>VCC</sub> > UVLO, V <sub>ACDET</sub> rising                                                                                |       | 0.57 | 0.8   | V    |

| V <sub>WAKEUP_FALL</sub>    | WAKEUP detect falling threshold                                                                                                                                     | V <sub>VCC</sub> > UVLO, V <sub>ACDET</sub> falling                                                                               | 0.3   | 0.51 |       | V    |

| VCC to SRN COM              | IPARATOR (VCC_SRN)                                                                                                                                                  |                                                                                                                                   |       |      |       |      |

| V <sub>VCC-SRN_FALL</sub>   | VCC-SRN falling threshold                                                                                                                                           | V <sub>VCC</sub> falling towards V <sub>SRN</sub>                                                                                 | 70    | 125  | 200   | mV   |

| V <sub>VCC-SRN</sub> _RHYS  | VCC-SRN rising hysteresis                                                                                                                                           | V <sub>VCC</sub> rising above V <sub>SRN</sub>                                                                                    | 100   | 150  | 200   | mV   |

| ACN to SRN COM              | MPARATOR (ACN_SRN)                                                                                                                                                  |                                                                                                                                   |       |      |       |      |

| V <sub>ACN-SRN_FALL</sub>   | ACN to BAT falling threshold                                                                                                                                        | V <sub>ACN</sub> falling towards V <sub>SRN</sub>                                                                                 | 120   | 200  | 280   | mV   |

| V <sub>ACN-SRN_RHYS</sub>   | ACN to BAT rising hysteresis                                                                                                                                        | V <sub>ACN</sub> rising above V <sub>SRN</sub>                                                                                    | 40    | 80   | 120   | mV   |

|                             | LT COMPARATOR (IFAULT_HI) <sup>(1)</sup>                                                                                                                            | L                                                                                                                                 |       |      |       |      |

| VIFAULT_HI_RISE             | ACP to PHASE rising threshold                                                                                                                                       | ChargeOption() bit [8] = 1 (Default)<br>ChargeOption() bit [8] = 0 Disable function                                               | 450   | 750  | 1200  | mV   |

|                             | T COMPARATOR (IFAULT_LOW) <sup>(1)</sup>                                                                                                                            |                                                                                                                                   |       |      |       |      |

|                             |                                                                                                                                                                     | ChargeOption() bit [7] = 0 (Default)                                                                                              | 70    | 135  | 220   |      |

| VIFAULT_LOW_RISE            | PHASE to GND rising threshold                                                                                                                                       | ChargeOption() bit [7] = 1                                                                                                        | 140   | 230  | 340   | mV   |

|                             | LTAGE COMPARATOR (ACOV)                                                                                                                                             |                                                                                                                                   |       |      |       |      |

| V <sub>ACOV</sub>           | ACDET over voltage rising threshold                                                                                                                                 | V <sub>ACDET</sub> rising                                                                                                         | 3.05  | 3.15 | 3.25  | V    |

| V <sub>ACOV_HYS</sub>       | ACDET over voltage falling hysteresis                                                                                                                               | V <sub>ACDET</sub> falling                                                                                                        | 50    | 75   | 100   | mV   |

| INPUT OVER-CU               | RRENT COMPARATOR (ACOC) <sup>(1)</sup>                                                                                                                              |                                                                                                                                   |       |      |       |      |

|                             | Adapter over current rising threshold with                                                                                                                          | ChargeOption() bit [1] = 1 (Default)                                                                                              | 300%  | 333% | 366%  |      |

| V <sub>ACOC</sub>           | respect to input current limit, voltage<br>across input sense resistor rising edge                                                                                  | ChargeOption() bit [1] = 0 Disable function                                                                                       |       |      |       |      |

(1) User can adjust threshold via SMBus ChargeOption() REG0x12.

# **Electrical Characteristics (continued)**

# 4.5 V $\leq$ V<sub>VCC</sub> $\leq$ 24 V, 0°C $\leq$ T<sub>J</sub> $\leq$ 125°C, typical values are at T<sub>A</sub> = 25°C, with respect to GND (unless otherwise noted)

|                            | PARAMETER                                                                     | TEST CONDITIONS                                                           | MIN    | TYP    | MAX   | UNIT |

|----------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------|--------|-------|------|

| V <sub>ACOC_min</sub>      | Min ACOC threshold clamp voltage                                              | ChargeOption() Bit [1] = 1 (333%),<br>InputCurrent () = 0x0400H (10.24mV) | 40     | 45     | 50    | mV   |

| V <sub>ACOC_max</sub>      | Max ACOC threshold clamp voltage                                              | ChargeOption() Bit [1] = 1 (333%),<br>InputCurrent () = 0x1F80H (80.64mV) | 135    | 150    | 165   | mV   |

| t <sub>ACOC_DEG</sub>      | ACOC deglitch time (Specified by design)                                      | Voltage across input sense resistor rising to disable charge              | 2.3    | 4.2    | 6.6   | ms   |

| BAT OVER-VOLT              | TAGE COMPARATOR (BAT_OVP)                                                     |                                                                           |        |        |       |      |

| V <sub>OVP_RISE</sub>      | Over voltage rising threshold as percentage of $V_{BAT\_REG}$                 | V <sub>SRN</sub> rising                                                   | 103%   | 104%   | 106%  |      |

| V <sub>OVP_FALL</sub>      | Over voltage falling threshold as percentage of $V_{\text{BAT}_{\text{REG}}}$ | V <sub>SRN</sub> falling                                                  |        | 102%   |       |      |

| CHARGE OVER-               | CURRENT COMPARATOR (CHG_OCP)                                                  |                                                                           |        |        |       |      |

|                            | Charge over current rising threshold,                                         | ChargeCurrent()=0x0xxxH                                                   | 54     | 60     | 66    | mV   |

| V <sub>OCP_RISE</sub>      | measure voltage drop across current                                           | ChargeCurrent()=0x1000H - 0x17C0H                                         | 80     | 90     | 100   | mV   |

|                            | sensing resistor                                                              | ChargeCurrent()=0x1800 H- 0x1FC0H                                         | 110    | 120    | 130   | mV   |

| CHARGE UNDER               | R-CURRENT COMPARATOR (CHG_UCP)                                                | L                                                                         |        |        | 1     |      |

| VUCP FALL                  | Charge under-current falling threshold                                        | V <sub>SRP</sub> falling towards V <sub>SRN</sub>                         | 1      | 5      | 9     | mV   |

|                            | MPARATOR (LIGHT_LOAD)                                                         |                                                                           |        |        |       |      |

| V <sub>LL FALL</sub>       | Light load falling threshold                                                  | Measure the voltage drop across current sensing                           |        | 1.25   |       | mV   |

| V <sub>LL RISE HYST</sub>  | Light load rising hysteresis                                                  | resistor                                                                  |        | 1.25   |       | mV   |

|                            | ETION COMPARATOR (BAT_DEPL) [1]                                               |                                                                           |        |        |       |      |

|                            | · - /···                                                                      | ChargeOption() bit [12:11] = 00                                           | 55.53% | 59.19% | 63.5% |      |

|                            | Battery depletion falling threshold,                                          | ChargeOption() bit [12:11] = 01                                           | 58.68% |        | 67.5% |      |

| VBATDEPL_FALL              | percentage of voltage regulation limit, V <sub>SRN</sub> falling              | ChargeOption() bit [12:11] = 10                                           | 62.17% |        | 71.5% |      |

|                            | laining                                                                       | ChargeOption() bit [12:11] = 11 (Default)                                 | 66.06% |        | 77%   |      |

|                            |                                                                               | ChargeOption() bit $[12:11] = 00$                                         | 225    | 305    | 400   | mV   |

|                            |                                                                               | ChargeOption() bit [12:11] = 01                                           | 240    | 325    | 430   | mV   |

| V <sub>BATDEPL_RHYST</sub> | Battery depletion rising hysteresis, V <sub>SRN</sub> rising                  | ChargeOption() bit $[12:11] = 01$                                         | 255    | 345    | 450   | mV   |

|                            | c .                                                                           | ChargeOption() bit [12:11] = 11 (Default)                                 | 280    | 370    | 490   | mV   |

| t <sub>BATDEPL_RDEG</sub>  | Battery Depletion Rising Deglitch (Specified by design)                       | Delay to turn off ACFET and turn on BATFET during<br>LEARN cycle          | 200    | 600    | 100   | ms   |

| BATTERY LOWV               | / COMPARATOR (BAT_LOWV)                                                       |                                                                           |        |        |       |      |

| V <sub>BATLV_FALL</sub>    | Battery LOWV falling threshold                                                | V <sub>SRN</sub> falling                                                  | 2.4    | 2.5    | 2.6   | V    |

| VBATLV_FALL                | Battery LOWV rising hysteresis                                                | V <sub>SRN</sub> rising                                                   | 2.1    | 200    | 2.0   | mV   |

|                            | Battery LOWV charge current limit                                             | $10 \text{ m}\Omega$ current sensing resistor                             |        | 0.5    |       | A    |

| IBATLV                     | DOWN COMPARATOR (TSHUT)                                                       |                                                                           |        | 0.0    |       |      |

|                            | Thermal shutdown rising temperature                                           | Temperature rising                                                        |        | 155    |       | °C   |

| T <sub>SHUT</sub>          |                                                                               |                                                                           |        |        |       |      |

| ISHUT_HYS                  | Thermal shutdown hysteresis, falling                                          | Temperature falling                                                       |        | 20     |       | °C   |

|                            |                                                                               | V folling                                                                 | 60     | 75     | 00    |      |

| VILIM_FALL                 | ILIM as CE falling threshold                                                  | V <sub>ILIM</sub> falling                                                 | 60     | 75     | 90    | mV   |

|                            | ILIM as CE rising threshold                                                   | V <sub>ILIM</sub> rising                                                  | 90     | 105    | 120   | mV   |

| LOGIC INPUT (S             | · · · · ·                                                                     |                                                                           |        |        |       |      |

| V <sub>IN_LO</sub>         | Input low threshold                                                           |                                                                           | -      |        | 0.8   | V    |

| V <sub>IN_ HI</sub>        | Input high threshold                                                          |                                                                           | 2.1    |        |       | V    |

|                            |                                                                               | V = 7 V                                                                   | -1     |        | 1     | μA   |

|                            | OPEN DRAIN (ACOK, SDA)                                                        |                                                                           |        |        |       |      |

| V <sub>OUT_LO</sub>        | Output saturation voltage                                                     | 5 mA drain current                                                        |        |        | 500   | mV   |

| I <sub>OUT_ LEAK</sub>     | Leakage current                                                               | V = 7 V                                                                   | -1     |        | 1     | μA   |

| ANALOG INPUT               | ,                                                                             | Ι                                                                         |        |        |       |      |

| I <sub>IN_ LEAK</sub>      | Input bias current                                                            | V = 7 V                                                                   | -1     |        | 1     | μA   |

| PWM OSCILLAT               | OR                                                                            |                                                                           |        |        |       |      |

| F <sub>SW</sub>            | PWM switching frequency                                                       | ChargeOption () bit [9] = 0 (Default)                                     | 600    | 750    | 900   | kHz  |

# **Electrical Characteristics (continued)**

| $4.5 \text{ V} \le \text{V}_{\text{VCC}} \le 24 \text{ V}, 0^{\circ}\text{C} \le \text{T}_{1}$ | ≤ 125°C. typical values | are at T <sub>A</sub> = 25°C, with resp | pect to GND (unless otherwise noted) |

|------------------------------------------------------------------------------------------------|-------------------------|-----------------------------------------|--------------------------------------|

|                                                                                                |                         |                                         |                                      |

|                           | PARAMETER                                                       | TEST CONDITIONS                                                           | MIN  | TYP  | MAX  | UNIT |

|---------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------|------|------|------|------|

| F <sub>SW+</sub>          | PWM increase frequency                                          | ChargeOption() bit [10:9] = 11                                            | 665  | 885  | 1100 | kHz  |

| F <sub>SW-</sub>          | PWM decrease frequency                                          | ChargeOption() bit [10:9] = 01                                            | 465  | 615  | 765  | kHz  |

| BATFET GATE D             | DRIVER (BATDRV)                                                 |                                                                           |      |      |      |      |

| IBATFET                   | BATDRV charge pump current limit                                |                                                                           | 40   | 60   |      | μA   |

| VBATFET                   | Gate drive voltage on BATFET                                    | $V_{\text{BATDRV}}$ - $V_{\text{SRN}}$ when $V_{\text{SRN}}$ > UVLO       | 5.5  | 6.1  | 6.5  | V    |

| R <sub>BATDRV_LOAD</sub>  | Minimum load resistance between<br>BATDRV and SRN               |                                                                           | 500  |      |      | kΩ   |

| R <sub>BATDRV_OFF</sub>   | BATDRV turn-off resistance                                      | Ι = 30 μΑ                                                                 | 5    | 6.2  | 7.4  | kΩ   |

| ACFET GATE DF             | RIVER (ACDRV)                                                   |                                                                           |      |      |      |      |

| I <sub>ACFET</sub>        | ACDRV charge pump current limit                                 |                                                                           | 40   | 60   |      | μΑ   |

| V <sub>ACFET</sub>        | Gate drive voltage on ACFET                                     | $V_{\text{ACDRV}} – V_{\text{CMSRC}}$ when $V_{\text{VCC}} > \text{UVLO}$ | 5.5  | 6.1  | 6.5  | V    |

| R <sub>ACDRV_LOAD</sub>   | Minimum load resistance between ACDRV and CMSRC                 |                                                                           | 500  |      |      | kΩ   |

| R <sub>ACDRV_OFF</sub>    | ACDRV turn-off resistance                                       | Ι = 30 μΑ                                                                 | 5    | 6.2  | 7.4  | kΩ   |

| V <sub>ACFET_LOW</sub>    | ACDRV Turn-Off when Vgs voltage is low<br>(Specified by design) |                                                                           |      | 5.9  |      | V    |

| PWM HIGH SIDE             | DRIVER (HIDRV)                                                  |                                                                           |      |      |      |      |

| R <sub>DS_HI_ON</sub>     | High side driver turn-on resistance                             | $V_{BTST} - V_{PH} = 5.5 \text{ V}, I = 10 \text{ mA}$                    |      | 6    | 10   | Ω    |

| R <sub>DS_HI_OFF</sub>    | High side driver turn-off resistance                            | $V_{BTST} - V_{PH} = 5.5 \text{ V}, I = 10 \text{ mA}$                    |      | 0.65 | 1.3  | Ω    |

| V <sub>BTST_REFRESH</sub> | Bootstrap refresh comparator threshold voltage                  | $V_{\text{BTST}}-V_{\text{PH}}$ when low side refresh pulse is requested  | 3.85 | 4.3  | 4.7  | V    |

| PWM LOW SIDE              | DRIVER (LODRV)                                                  |                                                                           |      |      |      |      |

| R <sub>DS_LO_ON</sub>     | Low side driver turn-on resistance                              | V <sub>REGN</sub> = 6 V, I = 10 mA                                        |      | 7.5  | 12   | Ω    |

| R <sub>DS_LO_OFF</sub>    | Low side driver turn-off resistance                             | V <sub>REGN</sub> = 6 V, I = 10 mA                                        |      | 0.9  | 1.4  | Ω    |

| PWM DRIVER TI             | MING                                                            |                                                                           |      |      |      |      |

| t <sub>LOW_HIGH</sub>     | Driver dead time from low side to high side                     |                                                                           |      | 20   |      | ns   |

| t <sub>HIGH_LOW</sub>     | Driver dead time from high side to low side                     |                                                                           |      | 20   |      | ns   |

| INTERNAL SOFT             | START                                                           |                                                                           |      |      |      |      |

| I <sub>STEP</sub>         | Soft start current step                                         | In COM mode 10m0 surrent consists register                                |      | 64   |      | mA   |

| t <sub>STEP</sub>         | Soft start current step time                                    | In CCM mode 10m $\Omega$ current sensing resistor                         |      | 240  |      | μS   |

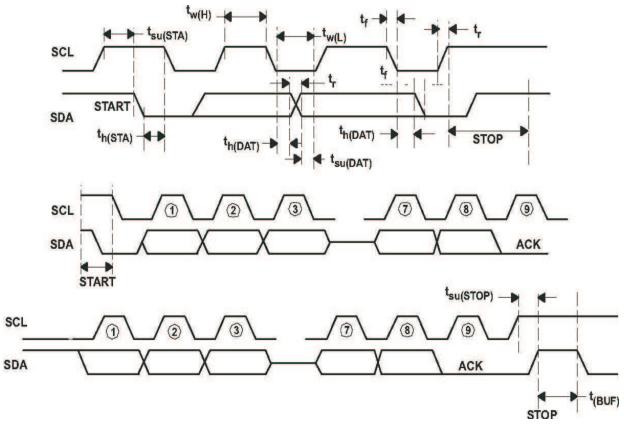

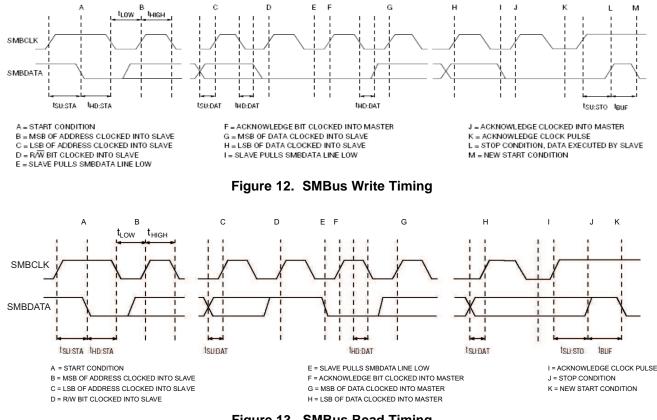

| SMBus TIMING              | CHARACTERISTICS                                                 |                                                                           |      |      |      |      |

| t <sub>R</sub>            | SCLK/SDATA rise time                                            |                                                                           |      |      | 1    | μS   |

| t <sub>F</sub>            | SCLK/SDATA fall time                                            |                                                                           |      |      | 300  | ns   |

| t <sub>W(H)</sub>         | SCLK pulse width high                                           |                                                                           | 4    |      | 50   | μs   |

| t <sub>W(L)</sub>         | SCLK Pulse Width Low                                            |                                                                           | 4.7  |      |      | μS   |

| t <sub>SU(STA)</sub>      | Setup time for START condition                                  |                                                                           | 4.7  |      |      | μS   |

| t <sub>H(STA)</sub>       | START condition hold time after which first of                  | clock pulse is generated                                                  | 4    |      |      | μS   |

| t <sub>SU(DAT)</sub>      | Data setup time                                                 |                                                                           | 250  |      |      | ns   |

| t <sub>H(DAT)</sub>       | Data hold time                                                  |                                                                           | 300  |      |      | ns   |

| t <sub>SU(STOP)</sub>     | Setup time for STOP condition                                   |                                                                           | 4    |      |      | μs   |

| t <sub>(BUF)</sub>        | Bus free time between START and STOP co                         | ondition                                                                  | 4.7  |      |      | μS   |

| F <sub>S(CL)</sub>        | Clock Frequency                                                 |                                                                           | 10   |      | 100  | kHz  |

|                           | ICATION FAILURE                                                 |                                                                           |      |      |      |      |

| t <sub>timeout</sub>      | SMBus bus release timeout <sup>(2)</sup>                        |                                                                           | 25   |      | 35   | ms   |

| t <sub>BOOT</sub>         | Deglitch for watchdog reset signal                              |                                                                           | 10   |      |      | ms   |

|                           | Watchdog timeout period, ChargeOption() b                       | it [14:13] = 01 <sup>(3)</sup>                                            | 35   | 44   | 53   | S    |

| t <sub>WDI</sub>          | Watchdog timeout period, ChargeOption() b                       | • •                                                                       | 70   | 88   | 105  | S    |

|                           | Watchdog timeout period, ChargeOption() b                       | it [14:13] = 11 <sup>(3)</sup> (Default)                                  | 140  | 175  | 210  | S    |

(2) Devices participating in a transfer will timeout when any clock low exceeds the 25ms minimum timeout period. Devices that have detected a timeout condition must reset the communication no later than the 35ms maximum timeout period. Both a master and a slave must adhere to the maximum value specified as it incorporates the cumulative stretch limit for both a master (10ms) and a slave (25ms).

(3) User can adjust threshold via SMBus ChargeOption() REG0x12.

JAJSGI6C-SEPTEMBER 2011-REVISED JANUARY 2020

www.ti.com

STRUMENTS

EXAS

# 6.6 Timing Characteristics

4.5 V  $\leq$  V<sub>VCC</sub>  $\leq$  24 V, 0°C  $\leq$  T<sub>J</sub>  $\leq$  125°C, typical values are at T<sub>A</sub> = 25°C, with respect to GND (unless otherwise noted)

|                       | PARAMETER                                                                         | MIN | TYP | MAX | UNIT |

|-----------------------|-----------------------------------------------------------------------------------|-----|-----|-----|------|

| SMBus TIMIN           | IG CHARACTERISTICS                                                                |     |     |     |      |

| t <sub>R</sub>        | SCLK/SDATA rise time                                                              |     |     | 1   | μS   |

| t <sub>F</sub>        | SCLK/SDATA fall time                                                              |     |     | 300 | ns   |

| t <sub>W(H)</sub>     | SCLK pulse width high                                                             | 4   |     | 50  | μS   |

| t <sub>W(L)</sub>     | SCLK Pulse Width Low                                                              | 4.7 |     |     | μS   |

| t <sub>SU(STA)</sub>  | Setup time for START condition                                                    | 4.7 |     |     | μS   |

| t <sub>H(STA)</sub>   | START condition hold time after which first clock pulse is generated              | 4   |     |     | μS   |

| t <sub>SU(DAT)</sub>  | Data setup time                                                                   | 250 |     |     | ns   |

| t <sub>H(DAT)</sub>   | Data hold time                                                                    | 300 |     |     | ns   |

| t <sub>SU(STOP)</sub> | Setup time for STOP condition                                                     | 4   |     |     | μs   |

| t <sub>(BUF)</sub>    | Bus free time between START and STOP condition                                    | 4.7 |     |     | μS   |

| F <sub>S(CL)</sub>    | Clock Frequency                                                                   | 10  |     | 100 | kHz  |

|                       | UNICATION FAILURE                                                                 |     |     |     | -    |

| t <sub>timeout</sub>  | SMBus bus release timeout <sup>(1)</sup>                                          | 25  |     | 35  | ms   |

| t <sub>BOOT</sub>     | Deglitch for watchdog reset signal                                                | 10  |     |     | ms   |

|                       | Watchdog timeout period, ChargeOption() bit [14:13] = 01 <sup>(2)</sup>           | 35  | 44  | 53  | s    |

| t <sub>WDI</sub>      | Watchdog timeout period, ChargeOption() bit [14:13] = 10 <sup>(2)</sup>           | 70  | 88  | 105 | S    |

|                       | Watchdog timeout period, ChargeOption() bit [14:13] = 11 <sup>(2)</sup> (Default) | 140 | 175 | 210 | S    |

(1) Devices participating in a transfer will timeout when any clock low exceeds the 25ms minimum timeout period. Devices that have detected a timeout condition must reset the communication no later than the 35ms maximum timeout period. Both a master and a slave must adhere to the maximum value specified as it incorporates the cumulative stretch limit for both a master (10ms) and a slave (25ms).

(2) User can adjust threshold via SMBus ChargeOption() REG0x12.

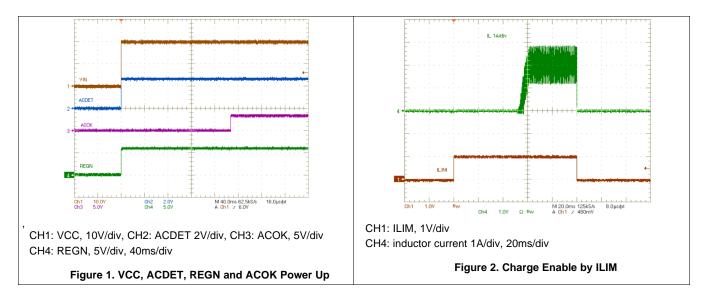

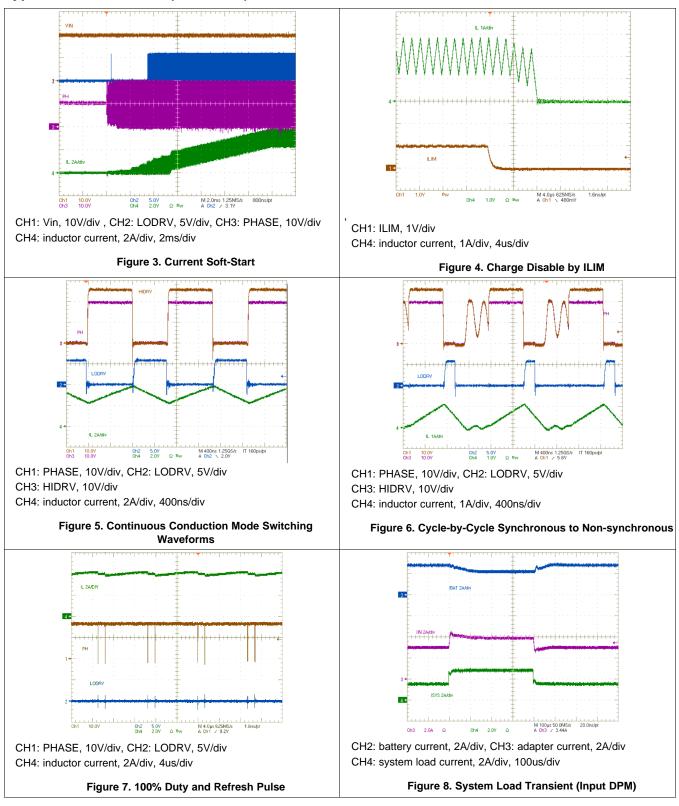

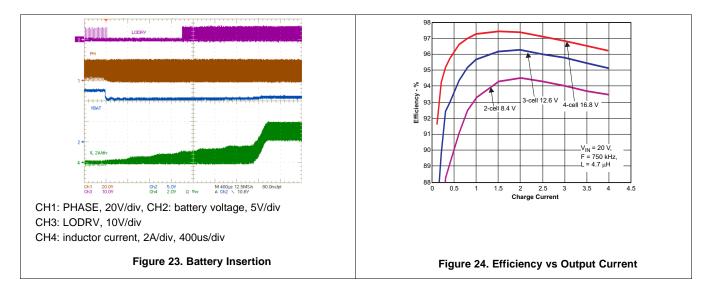

# 6.7 Typical Characteristics

### **Typical Characteristics (continued)**

# 7 Parameter Measurement Information

Figure 9. SMBus Communication Timing Waveforms

# 8 Detailed Description

### 8.1 Overview

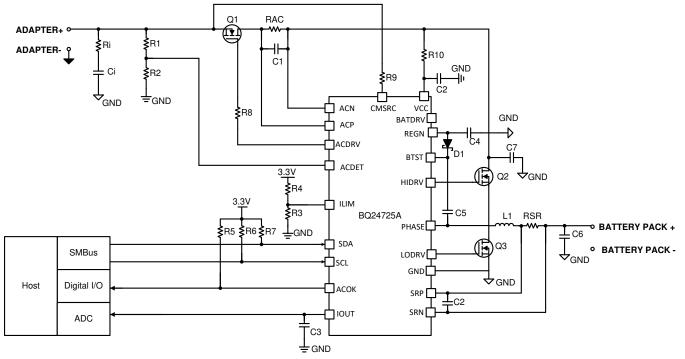

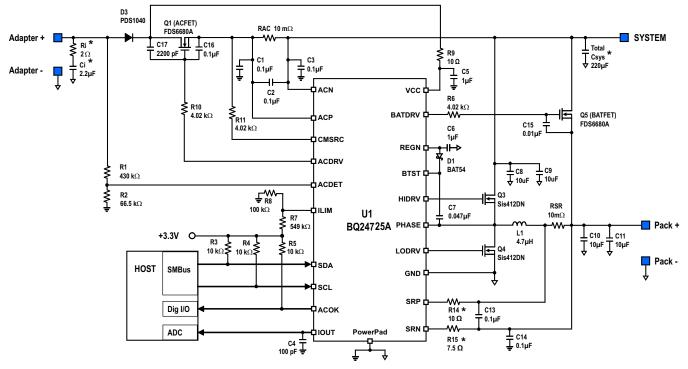

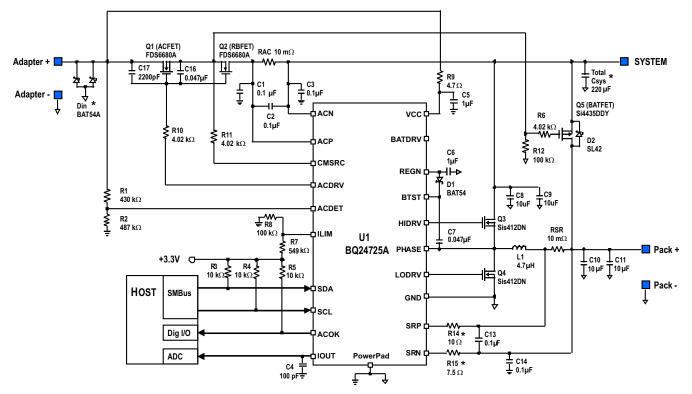

The BQ24725A is a 1-4 cell battery charge controller with power selection for space-constrained, multi-chemistry portable applications such as notebook and detachable ultrabook. It supports wide input range of input sources from 4.5V to 24V, and 1-4 cell battery for a versatile solution.

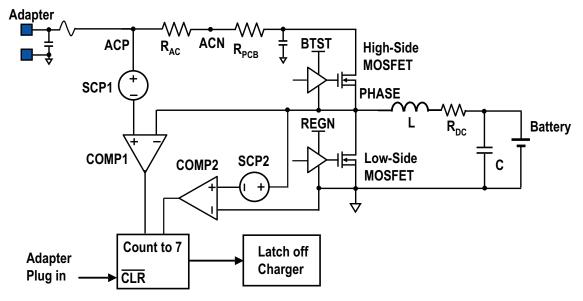

The BQ24725A supports automatic system power source selection with separate drivers for n-channel MOSFETS on the adapter side and battery side.

The BQ24725A features Dynamic Power Management (DPM) to limit the input power and avoid AC adapter over-loading. During battery charging, as the system power increases, the charging current will reduce to maintain total input current below adapter rating.

The SMBus controls input current, charge current and charge voltage registers with high resolution, high accuracy regulation limits.

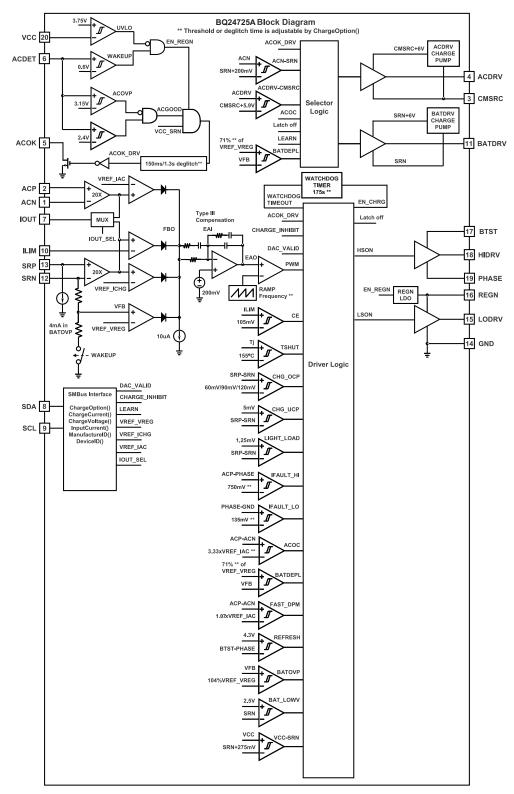

### 8.2 Functional Block Diagram

Figure 10. Functional Block Diagram for BQ24725A

### 8.3 Feature Description

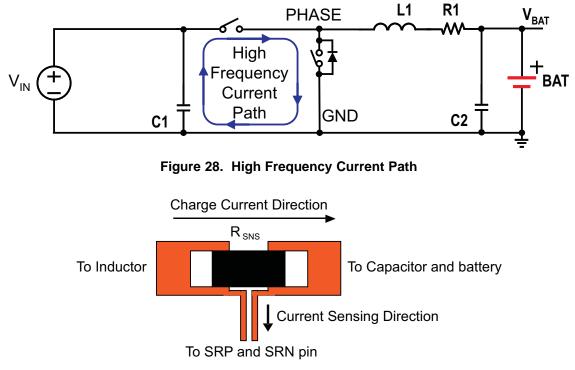

### 8.3.1 SMBus Interface