🕳 Order

Now

### bq27545-G1

JAJSFF8E-OCTOBER 2012-REVISED MAY 2018

# bq27545-G1 バッテリ・パック内蔵用シングルセル・リチウムイオン・ バッテリ残量計

## 1 特長

Texas

INSTRUMENTS

- 最大容量14,500mAhの1シリーズ(1sXp)リチウム イオン・アプリケーション用バッテリ残量計

- マイクロコントローラ・ペリフェラルによる機能

- バッテリ温度レポート用の内部または外部温度センサ

- SHA-1/HMAC認証機能

- 全寿命を通じたデータ記録

- 64バイトの不揮発性スクラッチ・パッド・フラッシュ

- 特許を取得した Impedance Track™技術に基づく バッテリ残量計測

- バッテリ放電曲線をモデリングし、バッテリが空になるまでの時間を正確に予測

- 経年変化、自己放電、温度およびレート非効率性 の影響を自動的に調整

- 値の低い検出抵抗(5mΩ~20mΩ)

- 高度な残量計測機能

- 内部短絡検出

- タブ切断検出

- ホスト・システムとの通信用HDQおよび I<sup>2</sup>C™インターフェイス・フォーマット

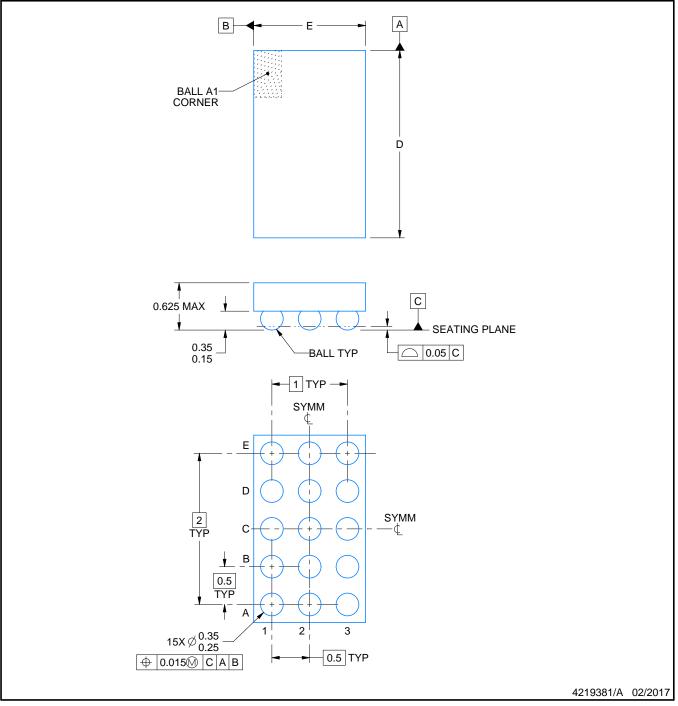

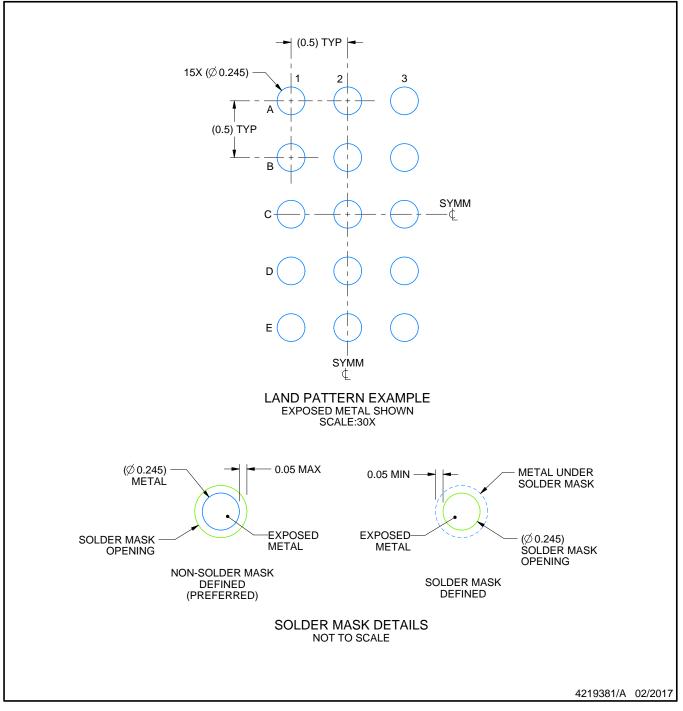

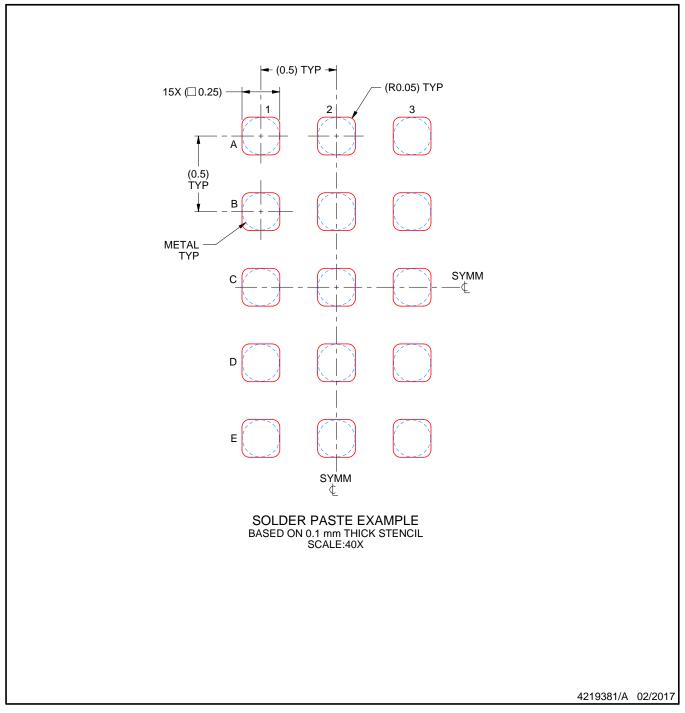

- 小型の15ボール Nano-Free™(DSBGA)パッケージ

- 2 アプリケーション

- スマートフォン

- タブレット

- デジカメ / ビデオ・カメラ

- ハンドヘルド端末

- MP3またはマルチメディア・プレーヤ

### 3 概要

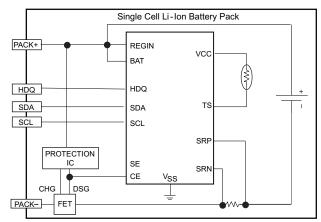

bq27545-G1リチウムイオン・バッテリ残量計は、シングル セル・リチウムイオン・バッテリ・パックの残量計測を行うマ イクロコントローラ・ペリフェラルで、最小限のシステム・マイ クロコントローラ・ファームウェア開発で高精度のバッテリ残 量計測を実現できます。bq27545-G1はバッテリ・パック内 または組み込みバッテリ(取り外し不可)を実装したシステ ムの主基板に配置されます。

bq27545-G1は特許取得のImpedance Track™アルゴリズムを残量計測に使用し、残りのバッテリ容量(mAh)、充電状態(%)、残り動作時間(最小値)、バッテリ電圧(mV)、温度(℃)などの情報を取得します。内部短絡やタブ切断などの事象も検出できます。

また、bq27545-G1はSHA-1/HMAC認証アルゴリズムを 使用する、セキュアなバッテリ・パック認証のサポートを内 蔵しています。

このデバイスは15ボールのNano-Free™ DSBGAパッ ケージ(2.61mm×1.96mm)で供給され、スペースに制約 のあるアプリケーションに理想的です。

### 製品情報<sup>(1)</sup>

| 型番         | パッケージ    | 本体サイズ(公称)     |  |  |

|------------|----------|---------------|--|--|

| bq27545-G1 | YZF (15) | 2.61mm×1.96mm |  |  |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

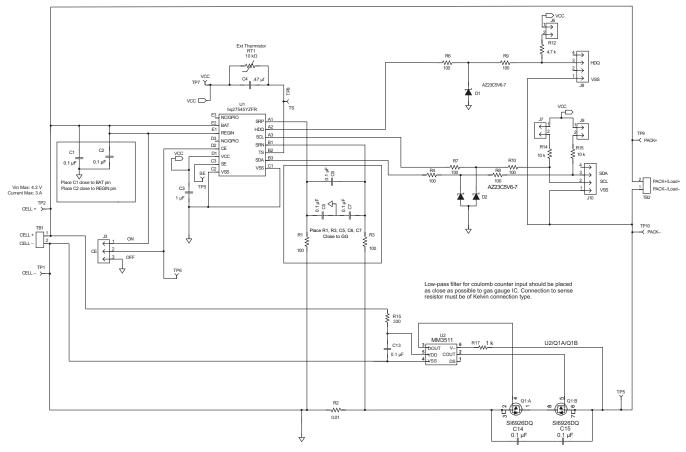

### 概略回路図

53

# 目次

8

9

| 1 | 特長   |                                                                |

|---|------|----------------------------------------------------------------|

| 2 | アプ   | リケーション 1                                                       |

| 3 | 概要   |                                                                |

| 4 | 改訂   | 履歴2                                                            |

| 5 | Devi | ce Comparison Table 3                                          |

| 6 | Pin  | Configuration and Functions                                    |

| 7 | Spe  | cifications 4                                                  |

|   | 7.1  | Absolute Maximum Ratings 4                                     |

|   | 7.2  | ESD Ratings 4                                                  |

|   | 7.3  | Recommended Operating Conditions 4                             |

|   | 7.4  | Thermal Information 4                                          |

|   | 7.5  | Electrical Characteristics: Supply Current5                    |

|   | 7.6  | Electrical Characteristics: Digital Input and Output           |

|   |      | DC 5                                                           |

|   | 7.7  | Electrical Characteristics: Power-On Reset 5                   |

|   | 7.8  | Electrical Characteristics: 2.5-V LDO Regulator 5              |

|   | 7.9  | Electrical Characteristics: Internal Clock Oscillators. 6      |

|   | 7.10 | Electrical Characteristics: Integrating ADC                    |

|   |      | (Coulomb Counter) Characteristics                              |

|   | 7.11 | Electrical Characteristics: ADC (Temperature and Cell Voltage) |

|   | 7.12 |                                                                |

|   | 7.13 | HDQ Communication Timing Characteristics                       |

|   | 7.14 | $I^2$ C-Compatible Interface Timing Characteristics 7          |

|   |      |                                                                |

| Л | 改訂履歴 |

|---|------|

| 4 | 以訂履篮 |

2

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

# Revision D (November 2015) から Revision E に変更

| 「 <i>概略回路図</i> 」変更<br>Changed the description for the SRP pin | 1<br>3 |

|---------------------------------------------------------------|--------|

|                                                               | _      |

## Revision C (September 2015) から Revision D に変更

|   | 「 <i>代表的なアプリケーション回路図</i> 」を「概略回路図」に 変更<br>本体サイズ 変更               |     |

|---|------------------------------------------------------------------|-----|

|   | Changed "Device Options" to "Device Comparison Table"            |     |

| • | Changed the descriptions for the SRP and SRN pins                | . 3 |

| • | Changed Electrical Characteristics: Power-On Reset               | . 5 |

| • | Changed all instances of "relaxation mode" to "RELAX mode"       | 13  |

| • | Added "FULLSLEEP mode" to the introduction in <i>Power Modes</i> | 19  |

### Revision B (October 2012) から Revision C に変更

|                      | ٤.                                   |

|----------------------|--------------------------------------|

| 「ーションと実装」セクション、「電源に関 |                                      |

| ート」セクション、「メカニカル、パッケー |                                      |

| 1                    | ĺ                                    |

| 5                    | ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |

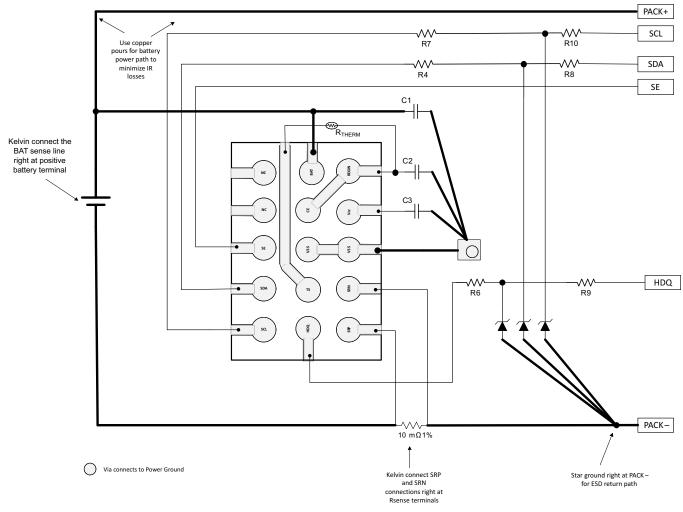

### Detailed Description ..... 10 8.1 Overview ...... 10 8.2 Functional Block Diagram ..... 11 8.3 Feature Description..... 11 8.5 Programming...... 24 8.6 Register Maps...... 39 Application and Implementation ...... 41 9.1 Application Information..... 41 9.2 Typical Application ..... 41 10 Power Supply Recommendations ...... 45 10.1 Power Supply Decoupling...... 45 11 Layout...... 45 11.1 Layout Guidelines ...... 45 11.2 Layout Example ..... 46 12 デバイスおよびドキュメントのサポート ...... 47

12.2 コミュニティ・リソース...... 47 12.3 商標...... 47 12.4 静電気放電に関する注意事項 ...... 47 12.5 Glossary...... 47 13 メカニカル、パッケージ、および注文情報 ...... 47

www.ti.com

Page

Page

### Page

# 5 Device Comparison Table

| PART<br>NUMBER <sup>(1)</sup> | FIRMWARE<br>VERSION | PACKAGE <sup>(2)</sup> | T <sub>A</sub> COMMUNICATION FORMA |                                      |

|-------------------------------|---------------------|------------------------|------------------------------------|--------------------------------------|

| BQ27545-G1                    | 2.24                | CSP-15                 | -40°C to 85°C                      | I <sup>2</sup> C, HDQ <sup>(1)</sup> |

(1) bq27545-G1 is shipped in  $I^2C$  mode.

(2) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

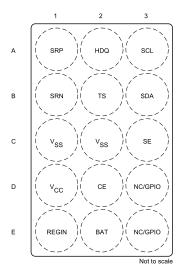

# 6 Pin Configuration and Functions

### **Pin Functions**

| PIN             |        | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                        |  |

|-----------------|--------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME            | NO.    | ITPE.               | DESCRIPTION                                                                                                                                                        |  |

| SRP             | A1     | IA                  | Analog input pin connected to the internal coulomb counter where SRP is nearest the CELL– connection. Connect to a 5-m $\Omega$ to 20-m $\Omega$ sense resistor.   |  |

| SRN             | B1     | IA                  | Analog input pin connected to the internal coulomb counter where SRN is nearest the PACK– connection. Connect to the 5-m $\Omega$ to 20-m $\Omega$ sense resistor. |  |

| V <sub>SS</sub> | C1, C2 | Р                   | Device ground                                                                                                                                                      |  |

| SE              | C3     | 0                   | Shutdown Enable output. Push-pull output.                                                                                                                          |  |

| V <sub>CC</sub> | D1     | Р                   | Regulator output and processor power. Decouple with 1-µF ceramic capacitor to V <sub>SS</sub> .                                                                    |  |

| REGIN           | E1     | Р                   | Regulator input. Decouple with 0.1-µF ceramic capacitor to V <sub>SS</sub> .                                                                                       |  |

| HDQ             | A2     | I/O                 | HDQ serial communications line (Slave). Open drain.                                                                                                                |  |

| TS              | B2     | IA                  | Pack thermistor voltage sense (use 103AT-type thermistor). ADC input.                                                                                              |  |

| CE              | D2     | I                   | Chip Enable. Internal LDO is disconnected from REGIN when driven low.                                                                                              |  |

| BAT             | E2     | IA                  | Cell-voltage measurement input. ADC input. Recommend 4.8-V maximum for conversion accuracy.                                                                        |  |

| SCL             | A3     | I                   | Slave I <sup>2</sup> C serial communications clock input line for communication with system (Master). Use with 10-k $\Omega$ pullup resistor (typical).            |  |

| SDA             | B3     | I/O                 | Slave $l^2C$ serial communications data line for communication with system (Master). Open-drain I/O. Use with 10-k $\Omega$ pullup resistor (typical).             |  |

| NC/GPIO         | D3, E3 | NC                  | Do not connect for proper operation; reserved for future GPIO.                                                                                                     |  |

(1) IA = Analog input, I/O = Digital input/output, P = Power connection, NC = No connect

## 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                                             | MIN  | MAX                   | UNIT |

|------------------|-------------------------------------------------------------|------|-----------------------|------|

| VI               | Regulator input, REGIN                                      | -0.3 | 5.5                   | V    |

| V <sub>CC</sub>  | Supply voltage                                              | -0.3 | 2.75                  | V    |

| V <sub>IOD</sub> | Open-drain I/O pins (SDA, SCL, HDQ)                         | -0.3 | 5.5                   | V    |

| $V_{BAT}$        | BAT input, (pin E2)                                         | -0.3 | 5.5                   | V    |

| VI               | Input voltage range to all others (pins GPIO, SRP, SRN, TS) | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| T <sub>A</sub>   | Operating free-air temperature                              | -40  | 85                    | °C   |

| T <sub>F</sub>   | Functional temperature                                      | -40  | 100                   | °C   |

| T <sub>stg</sub> | Storage temperature                                         | -65  | 150                   | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                    |                                                 |                                                         |                         | VALUE | UNIT |

|--------------------|-------------------------------------------------|---------------------------------------------------------|-------------------------|-------|------|

|                    | Human-body model (HBM), per ANSI/ESDA/JEDEC JS- | BAT pin                                                 | ±1500                   |       |      |

| V <sub>(ESD)</sub> | uischarge                                       | 001 <sup>(1)</sup>                                      | all pins                | ±2000 | V    |

|                    |                                                 | Charged-device model (CDM), per JEDEC specification JES | D22-C101 <sup>(2)</sup> | ±500  |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

$T_A = -40^{\circ}C$  to 85°C; typical values at  $T_A = 25^{\circ}C$  and  $V_{REGIN} = V_{BAT} = 3.6$  V (unless otherwise noted)

|                    |                                                                         |                                                                                                                  | MIN  | NOM | MAX | UNIT |

|--------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| VI                 | Supply voltage, REGIN                                                   | No operating restrictions                                                                                        | 2.8  |     | 4.5 | V    |

|                    |                                                                         | No FLASH writes                                                                                                  | 2.45 |     | 2.8 |      |

| C <sub>REGIN</sub> | External input capacitor for internal LDO between REGIN and $V_{SS}$    | Nominal capacitor values specified.<br>Recommend a 5% ceramic X5R type capacitor<br>located close to the device. |      | 0.1 |     | μF   |

| C <sub>LDO25</sub> | External output capacitor for internal LDO between $V_{CC}$ an $V_{SS}$ |                                                                                                                  | 0.47 | 1   |     | μF   |

| t <sub>PUCD</sub>  | Power-up communication delay                                            |                                                                                                                  |      | 250 |     | ms   |

### 7.4 Thermal Information

|                       |                                              | bq27545-G1  |      |

|-----------------------|----------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | YZF (DSBGA) | UNIT |

|                       |                                              | 15 PINS     |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 70          | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 17          | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 20          | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 1           | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 18          | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A         | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 7.5 Electrical Characteristics: Supply Current

$T_A = 25^{\circ}C$  and  $V_{REGIN} = V_{BAT} = 3.6 V$  (unless otherwise noted)

|                        | PARAMETER                                       | TEST CONDITIONS                                                              | MIN | TYP | MAX | UNIT |

|------------------------|-------------------------------------------------|------------------------------------------------------------------------------|-----|-----|-----|------|

| I <sub>CC</sub>        | Normal operating mode current <sup>(1)</sup>    | Fuel gauge in NORMAL mode<br>I <sub>LOAD</sub> > <b>Sleep Current</b>        |     | 118 |     | μA   |

| I <sub>(SLP)</sub>     | Low-power operating mode current <sup>(1)</sup> | Fuel gauge in SLEEP mode<br>I <sub>LOAD</sub> < <i>Sleep Current</i>         |     | 62  |     | μA   |

| I <sub>(FULLSLP)</sub> | Low-power operating mode current <sup>(1)</sup> | Fuel gauge in FULLSLEEP mode<br>I <sub>LOAD</sub> < <i>Sleep Current</i>     |     | 23  |     | μA   |

| I <sub>(HIB)</sub>     | HIBERNATE operating mode current <sup>(1)</sup> | Fuel gauge in HIBERNATE mode<br>I <sub>LOAD</sub> < <i>Hibernate Current</i> |     | 8   |     | μA   |

(1) Specified by design. Not tested in production.

### 7.6 Electrical Characteristics: Digital Input and Output DC

$T_A = -40^{\circ}C$  to 85°C; typical values at  $T_A = 25^{\circ}C$  and  $V_{REGIN} = V_{BAT} = 3.6$  V (unless otherwise noted)

|                     | PARAMETER                              | TEST CONDITIONS                                | MIN                     | TYP MAX | UNIT |

|---------------------|----------------------------------------|------------------------------------------------|-------------------------|---------|------|

| V <sub>OL</sub>     | Output voltage low (HDQ, SDA, SCL, SE) | I <sub>OL</sub> = 3 mA                         |                         | 0.4     | V    |

| V <sub>OH(PP)</sub> | Output high voltage (SE)               | $I_{OH} = -1 \text{ mA}$                       | V <sub>CC</sub> -0.5    |         | V    |

| V <sub>OH(OD)</sub> | Output high voltage (HDQ, SDA, SCL)    | External pullup resistor connected to $V_{CC}$ | V <sub>CC</sub> -0.5    |         | V    |

| VIL                 | Input voltage low (HDQ, SDA, SCL)      |                                                | -0.3                    | 0.6     | V    |

| V <sub>IH</sub>     | Input voltage high (HDQ, SDA,<br>SCL)  |                                                | 1.2                     | 5.5     | V    |

| V <sub>IL(CE)</sub> | CE Low-level input voltage             | VREGIN = 2.8 V to 4.5 V                        | 2.65                    | 0.8     | V    |

| V <sub>IH(CE)</sub> | CE High-level input voltage            | VREGIN = 2.0 V 10 4.5 V                        | V <sub>REGIN</sub> -0.5 | 0.8     | v    |

| l <sub>lkg</sub>    | Input leakage current (I/O pins)       |                                                |                         | 0.3     | μA   |

### 7.7 Electrical Characteristics: Power-On Reset

$T_A = -40^{\circ}C$  to 85°C,  $C_{(REG)} = 0.47 \ \mu\text{F}$ , 2.45 V <  $V_{(REGIN)} = V_{BAT}$  < 5.5 V; typical values at  $T_A = 25^{\circ}C$  and  $V_{(REGIN)} = V_{BAT} = 3.6 \text{ V}$  (unless otherwise noted)

|                  | PARAMETER                                        | TEST CONDITIONS | MIN  | TYP  | MAX | UNIT |

|------------------|--------------------------------------------------|-----------------|------|------|-----|------|

| V <sub>IT+</sub> | Positive-going battery voltage input at $V_{CC}$ |                 | 2.05 | 2.15 | 2.2 | V    |

| V <sub>HYS</sub> | Power-on reset hysteresis                        |                 |      | 115  |     | mV   |

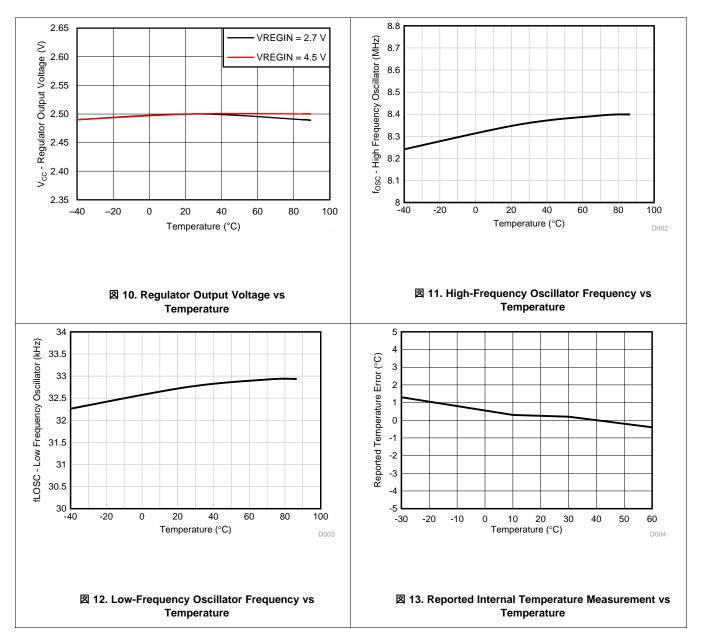

### 7.8 Electrical Characteristics: 2.5-V LDO Regulator

$T_{A} = -40^{\circ}C \text{ to } 85^{\circ}C, C_{(REG)} = 0.47 \ \mu\text{F}, 2.45 \ \text{V} < \text{V}_{(REGIN)} = \text{V}_{BAT} < 5.5 \ \text{V}; \text{ typical values at } T_{A} = 25^{\circ}C \text{ and } \text{V}_{(REGIN)} = \text{V}_{BAT} = 3.6 \ \text{V} \text{ (unless otherwise noted)}$

|                 | PARAMETER                          | TEST CONDITION                                                                                            | MIN | TYP | MAX | UNIT |

|-----------------|------------------------------------|-----------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>cc</sub> | Regulator output voltage, $V_{CC}$ | $2.8 \text{ V} \leq \text{V}_{(\text{REGIN})} \leq 4.5 \text{ V},$<br>$I_{\text{OUT}} \leq 16 \text{ mA}$ | 2.3 | 2.5 | 2.6 | V    |

|                 |                                    | 2.45 V $\leq$ V <sub>(REGIN)</sub> $<$ 2.8 V (low battery), I <sub>OUT</sub> $\leq$ 3 mA                  | 2.3 |     |     | V    |

STRUMENTS

XAS

### 7.9 Electrical Characteristics: Internal Clock Oscillators

$T_A = -40^{\circ}$ C to 85°C, 2.4 V < V<sub>CC</sub> < 2.6 V; typical values at  $T_A = 25^{\circ}$ C and V<sub>CC</sub> = 2.5 V (unless otherwise noted)

| PARAMETER           |                     | TEST CONDITIONS | MIN | TYP    | MAX | UNIT |

|---------------------|---------------------|-----------------|-----|--------|-----|------|

| f <sub>(OSC)</sub>  | Operating frequency |                 |     | 2.097  |     | MHz  |

| f <sub>(LOSC)</sub> | Operating frequency |                 |     | 32.768 |     | kHz  |

### 7.10 Electrical Characteristics: Integrating ADC (Coulomb Counter) Characteristics

$T_A = -40^{\circ}$ C to 85°C,  $C_{(REG)} = 0.47 \mu$ F, 2.45 V <  $V_{(REGIN)} = V_{BAT}$  < 5.5 V; typical values at  $T_A = 25^{\circ}$ C and  $V_{(REGIN)} = V_{BAT} = 3.6$  V (unless otherwise noted)

|                       | PARAMETER                                        | TEST CONDITIONS                  | MIN    | TYP    | MAX    | UNIT |

|-----------------------|--------------------------------------------------|----------------------------------|--------|--------|--------|------|

| V <sub>SR</sub>       | Input voltage range, $V_{(SRN)}$ and $V_{(SRP)}$ | $V_{SR} = V_{(SRN)} - V_{(SRP)}$ | -0.125 |        | 0.125  | V    |

| t <sub>CONV(SR)</sub> | Conversion time                                  | Single conversion                |        | 1      |        | S    |

|                       | Resolution                                       |                                  | 14     |        | 15     | bits |

| V <sub>OS(SR)</sub>   | Input offset                                     |                                  |        | 10     |        | μV   |

| INL                   | Integral nonlinearity error                      |                                  |        | ±0.007 | ±0.034 | FSR  |

| Z <sub>IN(SR)</sub>   | Effective input resistance <sup>(1)</sup>        |                                  | 2.5    |        |        | MΩ   |

| I <sub>lkg(SR)</sub>  | Input leakage current <sup>(1)</sup>             |                                  |        |        | 0.3    | μA   |

(1) Specified by design. Not production tested.

### 7.11 Electrical Characteristics: ADC (Temperature and Cell Voltage)

$T_{A} = -40^{\circ}C \text{ to } 85^{\circ}C, C_{(REG)} = 0.47 \ \mu\text{F}, 2.45 \ \text{V} < \text{V}_{(REGIN)} = \text{V}_{BAT} < 5.5 \ \text{V}; \text{ typical values at } T_{A} = 25^{\circ}C \text{ and } \text{V}_{(REGIN)} = \text{V}_{BAT} = 3.6 \ \text{V} \text{ (unless otherwise noted)}$

|                        | PARAMETER                                       | TEST CONDITIONS                               | MIN                     | TYP | MAX      | UNIT  |

|------------------------|-------------------------------------------------|-----------------------------------------------|-------------------------|-----|----------|-------|

| V <sub>IN(TS)</sub>    | Input voltage range (TS)                        |                                               | V <sub>SS</sub> – 0.125 |     | $V_{CC}$ | V     |

| V <sub>IN(BAT)</sub>   | Input voltage range (BAT)                       |                                               | V <sub>SS</sub> – 0.125 |     | 5        | V     |

| V <sub>IN(ADC)</sub>   | Input voltage range to ADC                      |                                               | 0.05                    |     | 1        | V     |

| G <sub>(TEMP)</sub>    | Temperature sensor voltage gain                 |                                               |                         | -2  |          | mV/°C |

| t <sub>CONV(ADC)</sub> | Conversion time                                 |                                               |                         |     | 125      | ms    |

|                        | Resolution                                      |                                               | 14                      |     | 15       | bits  |

| V <sub>OS(ADC)</sub>   | Input offset                                    |                                               |                         | 1   |          | mV    |

| Z <sub>(TS)</sub>      | Effective input resistance (TS) $^{(1)}$        | bq27545-G1 not measuring external temperature | 8                       |     |          | MΩ    |

| -                      |                                                 | bq27545-G1 not measuring cell voltage         | 8                       |     |          | MΩ    |

| Z <sub>(BAT)</sub>     | Effective input resistance (BAT) <sup>(1)</sup> | bq27545-G1 measuring cell voltage             |                         | 100 |          | kΩ    |

| I <sub>lkg(ADC)</sub>  | Input leakage current                           |                                               |                         |     | 0.3      | μA    |

(1) Specified by design. Not production tested.

### 7.12 Electrical Characteristics: Data Flash Memory

$T_A = -40^{\circ}C$  to 85°C,  $C_{(REG)} = 0.47 \mu$ F, 2.45 V <  $V_{(REGIN)} = V_{BAT}$  < 5.5 V; typical values at  $T_A = 25^{\circ}C$  and  $V_{(REGIN)} = V_{BAT} = 3.6$  V (unless otherwise noted)

|                       | PARAMETER                                     | TEST CONDITIONS | MIN    | TYP | MAX | UNIT   |

|-----------------------|-----------------------------------------------|-----------------|--------|-----|-----|--------|

| t <sub>DR</sub>       | Data retention <sup>(1)</sup>                 |                 | 10     |     |     | Years  |

|                       | Flash programming write-cycles <sup>(1)</sup> |                 | 20,000 |     |     | Cycles |

| t <sub>WORDPROG</sub> | Word programming time <sup>(1)</sup>          |                 |        |     | 2   | ms     |

| I <sub>CCPROG</sub>   | Flash-write supply current <sup>(1)</sup>     |                 |        | 5   | 10  | mA     |

| t <sub>DFERASE</sub>  | Data flash master erase time <sup>(1)</sup>   |                 | 200    |     |     | ms     |

| t <sub>PGERASE</sub>  | Flash page erase time <sup>(1)</sup>          |                 | 20     |     |     | ms     |

(1) Specified by design. Not production tested.

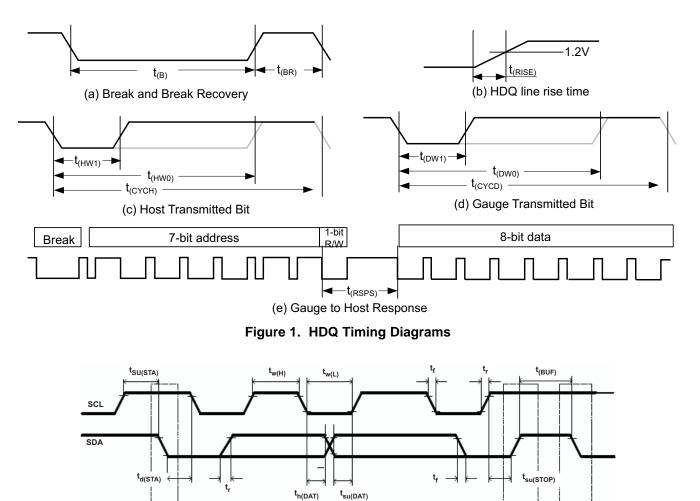

### 7.13 HDQ Communication Timing Characteristics

$T_A = -40^{\circ}$ C to 85°C,  $C_{REG} = 0.47 \mu$ F, 2.45 V <  $V_{REGIN} = V_{BAT}$  < 5.5 V; typical values at  $T_A = 25^{\circ}$ C and  $V_{REGIN} = V_{BAT} = 3.6$  V (unless otherwise noted)

| PARAMETER                               | TEST CONDITIONS                                                                                                                                                                                                                    | MIN                                                                                                                                                                                                                                | NOM                                                                                                                                                                                                                                                                                                                                                                                                                       | MAX                                                                                                                                                                                                                                                                                                                                                                                                    | UNIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cycle time, host to bq27545-G1          |                                                                                                                                                                                                                                    | 190                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                        | μS                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Cycle time, bq27545-G1 to host          |                                                                                                                                                                                                                                    | 190                                                                                                                                                                                                                                | 205                                                                                                                                                                                                                                                                                                                                                                                                                       | 250                                                                                                                                                                                                                                                                                                                                                                                                    | μS                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Host sends 1 to bq27545-G1              |                                                                                                                                                                                                                                    | 0.5                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                           | 50                                                                                                                                                                                                                                                                                                                                                                                                     | μS                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| bq27545-G1 sends 1 to host              |                                                                                                                                                                                                                                    | 32                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                           | 50                                                                                                                                                                                                                                                                                                                                                                                                     | μS                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Host sends 0 to bq27545-G1              |                                                                                                                                                                                                                                    | 86                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                           | 145                                                                                                                                                                                                                                                                                                                                                                                                    | μS                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| bq27545-G1 sends 0 to host              |                                                                                                                                                                                                                                    | 80                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                           | 145                                                                                                                                                                                                                                                                                                                                                                                                    | μS                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Response time, bq27545-G1 to host       |                                                                                                                                                                                                                                    | 190                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                           | 950                                                                                                                                                                                                                                                                                                                                                                                                    | μS                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Break time                              |                                                                                                                                                                                                                                    | 190                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                        | μS                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Break recovery time                     |                                                                                                                                                                                                                                    | 40                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                        | μS                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| HDQ line rising time to logic 1 (1.2 V) |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                           | 950                                                                                                                                                                                                                                                                                                                                                                                                    | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                         | Cycle time, host to bq27545-G1Cycle time, bq27545-G1 to hostHost sends 1 to bq27545-G1bq27545-G1 sends 1 to hostHost sends 0 to bq27545-G1bq27545-G1 sends 0 to hostResponse time, bq27545-G1 to hostBreak timeBreak recovery time | Cycle time, host to bq27545-G1Cycle time, bq27545-G1 to hostHost sends 1 to bq27545-G1bq27545-G1 sends 1 to hostHost sends 0 to bq27545-G1bq27545-G1 sends 0 to hostResponse time, bq27545-G1 to hostBreak timeBreak recovery time | Cycle time, host to bq27545-G1         190           Cycle time, bq27545-G1 to host         190           Host sends 1 to bq27545-G1         0.5           bq27545-G1 sends 1 to host         32           Host sends 0 to bq27545-G1         86           bq27545-G1 sends 0 to host         80           Response time, bq27545-G1 to host         190           Break time         190           Break time         40 | Cycle time, host to bq27545-G1         190           Cycle time, bq27545-G1 to host         190         205           Host sends 1 to bq27545-G1         0.5         0.5           bq27545-G1 sends 1 to host         32         32           Host sends 0 to bq27545-G1         86         80           bq27545-G1 sends 0 to host         80         190           Break time         190         40 | Cycle time, host to bq27545-G1         190           Cycle time, bq27545-G1 to host         190         205         250           Host sends 1 to bq27545-G1         0.5         50           bq27545-G1 sends 1 to host         32         50           Host sends 0 to bq27545-G1         86         145           bq27545-G1 sends 0 to host         80         145           bq27545-G1 sends 0 to host         190         950           Break time         190         40 |

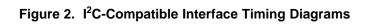

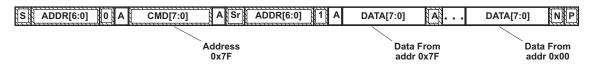

### 7.14 I<sup>2</sup>C-Compatible Interface Timing Characteristics

$T_A = -40^{\circ}$ C to 85°C,  $C_{REG} = 0.47 \mu$ F, 2.45 V <  $V_{REGIN} = V_{BAT}$  < 5.5 V; typical values at  $T_A = 25^{\circ}$ C and  $V_{REGIN} = V_{BAT} = 3.6$  V (unless otherwise noted)

|                       | PARAMETER                            | TEST CONDITIONS | MIN  | NOM | MAX | UNIT |

|-----------------------|--------------------------------------|-----------------|------|-----|-----|------|

| t <sub>r</sub>        | SCL/SDA rise time                    |                 |      |     | 300 | ns   |

| t <sub>f</sub>        | SCL/SDA fall time                    |                 |      |     | 300 | ns   |

| t <sub>w(H)</sub>     | SCL pulse width (high)               |                 | 600  |     |     | ns   |

| t <sub>w(L)</sub>     | SCL pulse width (low)                |                 | 1.3  |     |     | μS   |

| t <sub>su(STA)</sub>  | Setup for repeated start             |                 | 600  |     |     | ns   |

| t <sub>d(STA)</sub>   | Start to first falling edge of SCL   |                 | 600  |     |     | ns   |

| t <sub>su(DAT)</sub>  | Data setup time                      |                 | 1000 |     |     | ns   |

| t <sub>h(DAT)</sub>   | Data hold time                       |                 | 0    |     |     | ns   |

| t <sub>su(STOP)</sub> | Setup time for stop                  |                 | 600  |     |     | ns   |

| t <sub>BUF</sub>      | Bus free time between stop and start |                 | 66   |     |     | μS   |

| f <sub>SCL</sub>      | Clock frequency <sup>(1)</sup>       |                 |      |     | 400 | kHz  |

If the clock frequency (f<sub>SCL</sub>) is > 100 kHz, use 1-byte write commands for proper operation. All other transactions types are supported at 400 kHz. (Refer to <u>PC Interface</u>.)

> REPEATED START

STOP

START

www.ti.com

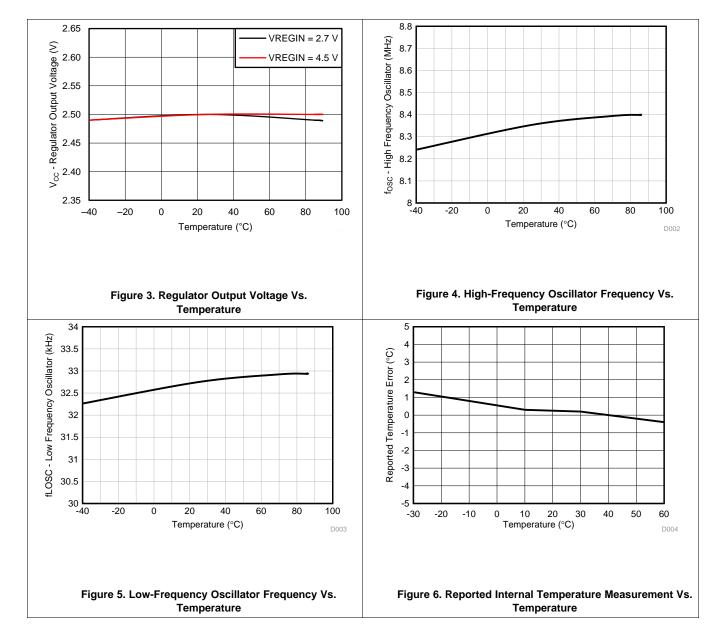

### 7.15 Typical Characteristics

### 8 Detailed Description

### 8.1 Overview

The bq27545-G1 accurately predicts the battery capacity and other operational characteristics of a single Libased rechargeable cell. It can be interrogated by a system processor to provide cell information, such as stateof-charge (SOC) and time-to-empty (TTE).

Information is accessed through a series of commands, called Standard Commands. Further capabilities are provided by the additional Extended Commands set. Both sets of commands, indicated by the general format *Command()*, are used to read and write information in the bq27545-G1 control and status registers, as well as its data flash locations. Commands are sent from the system to the gauge using the bq27545-G1 serial communications engine, and can be executed during application development, pack manufacture, or end-equipment operation.

Cell information is stored in the bq27545-G1 in non-volatile flash memory. Many of these data flash locations are accessible during application development. They cannot, generally, be accessed directly during end-equipment operation. To access to these locations, use the bq27546-G1 companion evaluation software, individual commands, or a sequence of data-flash-access commands. To access a desired data flash location, the correct data flash Subclass and offset must be known.

The bq27545-G1 provides 64 bytes of user-programmable data flash memory, partitioned into two (2) 32-byte blocks: *Manufacturer Info Block A* and *Manufacturer Info Block B*. This data space is accessed through a data flash interface. For specific details on accessing the data flash, see *Manufacturer Information Blocks*. The key to the bq27545-G1 high-accuracy gas gauging prediction is Texas Instrument's proprietary Impedance Track algorithm. This algorithm uses cell measurements, characteristics, and properties to create state-of-charge predictions that can achieve less than 1% error across a wide variety of operating conditions and over the lifetime of the battery.

The bq27545-G1 measures charge/discharge activity by monitoring the voltage across a small-value series sense resistor (5 m $\Omega$  to 20 m $\Omega$  typical) located between the CELL– and the battery's PACK– terminal. When a cell is attached to the bq27545-G1, cell impedance is learned based on cell current, cell open-circuit voltage (OCV), and cell voltage under loading conditions.

The bq27545-G1 external temperature sensing is optimized with the use of a high accuracy negative temperature coefficient (NTC) thermistor with R25 =  $10 \text{ k}\Omega \pm 1\%$  and B25/85 =  $3435 \text{ K} \pm 1\%$  (such as Semitec 103AT) for measurement. The bq27545-G1 can also be configured to use its internal temperature sensor. The bq27545-G1 uses temperature to monitor the battery-pack environment, which is used for fuel gauging and cell protection functionality.

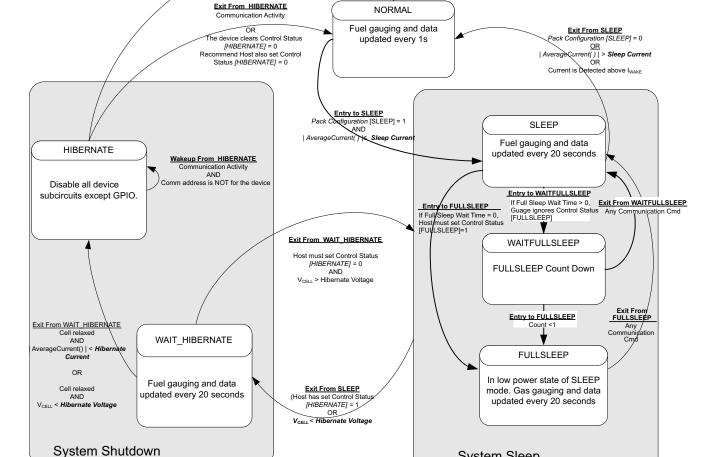

To minimize power consumption, the bq27545-G1 has different power modes: NORMAL, SLEEP, FULLSLEEP, and HIBERNATE. The bq27545-G1 passes automatically between these modes, depending upon the occurrence of specific events, though a system processor can initiate some of these modes directly. *Power Modes* has more details.

### NOTE

### FORMATTING CONVENTIONS IN THIS DOCUMENT:

**Commands:** *italics* with *parentheses()* and no breaking spaces. e.g., *RemainingCapacity()*

Data Flash: italics, bold, and breaking spaces. e.g., Design Capacity

Register bits and flags: italics with brackets[]. e.g., [TDA]

Data flash bits: *italics*, **bold**, and brackets[]. *e.g.*, *[LED1]*

Modes and states: ALL CAPITALS. e.g., UNSEALED mode

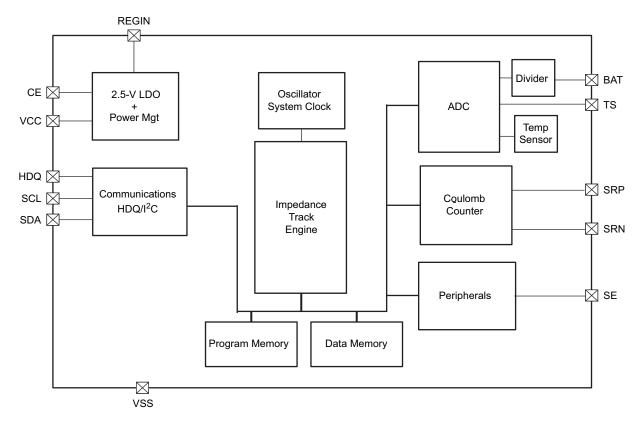

### 8.2 Functional Block Diagram

### 8.3 Feature Description

### 8.3.1 Fuel Gauging

The bq27545-G1 measures the cell voltage, temperature, and current to determine battery SOC based on Impedance Track algorithm (see the *Theory and Implementation of Impedance Track Battery Fuel-Gauging Algorithm Application Report* [SLUA450] for more information). The bq27545-G1 monitors charge and discharge activity by sensing the voltage across a small-value resistor (5 m $\Omega$  to 20 m $\Omega$  typical) between the SRP and SRN pins and in series with the cell. By integrating charge passing through the battery, the battery's SOC is adjusted during battery charge or discharge.

The total battery capacity is found by comparing states of charge before and after applying the load with the amount of charge passed. When an application load is applied, the impedance of the cell is measured by comparing the OCV obtained from a predefined function for present SOC with the measured voltage under load. Measurements of OCV and charge integration determine chemical state of charge and chemical capacity (Qmax). The initial Qmax values are taken from a cell manufacturers' data sheet multiplied by the number of parallel cells. It is also used for the value in Design Capacity. The bq27545-G1 acquires and updates the battery-impedance profile during normal battery usage. It uses this profile, along with SOC and the Qmax value, to determine FullChargeCapacity() and StateOfCharge(), specifically for the present load and temperature. FullChargeCapacity() is reported as capacity available from a fully charged battery under the present load and temperature until Voltage() reaches the Terminate Voltage. NominalAvailableCapacity() and FullAvailableCapacity() are the uncompensated (no or light load) versions of RemainingCapacity() and FullChargeCapacity() respectively.

The bq27545-G1 has two flags accessed by the *Flags()* function that warns when the battery's SOC has fallen to critical levels. When *RemainingCapacity()* falls below the first capacity threshold, specified in **SOC1 Set** *Threshold*, the [SOC1] (State of Charge Initial) flag is set. The flag is cleared once *RemainingCapacity()* rises above **SOC1 Clear Threshold**. All units are in mAh.

### **Feature Description (continued)**

When *RemainingCapacity()* falls below the second capacity threshold, **SOCF Set Threshold**, the [SOCF] (State of Charge Final) flag is set, serving as a final discharge warning. If **SOCF Set Threshold** = -1, the flag is inoperative during discharge. Similarly, when *RemainingCapacity()* rises above **SOCF Clear Threshold** and the [SOCF] flag has already been set, the [SOCF] flag is cleared. All units are in mAh.

The bq27545-G1 has two additional flags accessed by the *Flags()* function that warns of internal battery conditions. The fuel gauge monitors the cell voltage during relaxed conditions to determine if an internal short has been detected. When this condition occurs, *[ISD]* will be set. The bq27545-G1 also has the capability of detecting when a tab has been disconnected in a 2-cell parallel system by actively monitoring the *SOH*. When this conditions occurs, *[TDD]* will be set.

### 8.3.2 Impedance Track Variables

The bq27545-G1 has several data flash variables that permit the user to customize the Impedance Track algorithm for optimized performance. These variables are dependent upon the power characteristics of the application as well as the cell itself.

### 8.3.2.1 Load Mode

Load Mode is used to select either the constant-current or constant-power model for the Impedance Track algorithm as used in *Load Select* (see *Load Select*). When *Load Mode* is 0, the *Constant Current Model* is used (default). When Load Mode is 1, the *Constant Power Model* is used. The *[LDMD]* bit of CONTROL\_STATUS reflects the status of *Load Mode*.

### 8.3.2.2 Load Select

*Load Select* defines the type of power or current model to be used to compute load-compensated capacity in the Impedance Track algorithm. If *Load Mode* = 0 (*Constant Current*), then the options presented in Table 1 are available.

| Load Select Value | CURRENT MODEL USED                                                                                                                                                                                            |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                 | Average discharge current from previous cycle: There is an internal register that records the average discharge current through each entire discharge cycle. The previous average is stored in this register. |

| 1 (default)       | Present average discharge current: This is the average discharge current from the beginning of this discharge cycle until present time.                                                                       |

| 2                 | Average current: based off the AverageCurrent()                                                                                                                                                               |

| 3                 | Current: based off of a low-pass-filtered version of AverageCurrent() ( $\tau = 14 \text{ s}$ )                                                                                                               |

| 4                 | Design capacity/5: C Rate based off of Design Capacity /5 or a C/5 rate in mA.                                                                                                                                |

| 5                 | Use the value specified by AtRate()                                                                                                                                                                           |

| 6                 | Use the value in User_Rate-mA: This gives a completely user-configurable method.                                                                                                                              |

### Table 1. Constant-Current Model Used When Load Mode = 0

If *Load Mode* = 1 (*Constant Power*) then the following options are available:

### Table 2. Constant-Power Model Used When Load Mode = 1

| Load Select Value | POWER MODEL USED                                                                                                                                                                                          |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                 | Average discharge power from previous cycle: There is an internal register that records the average discharge power through each entire discharge cycle. The previous average is stored in this register. |

| 1                 | Present average discharge power: This is the average discharge power from the beginning of this discharge cycle until present time.                                                                       |

| 2                 | Average current × voltage: based off the AverageCurrent() and Voltage().                                                                                                                                  |

| 3                 | Current × voltage: based off of a low-pass-filtered version of AverageCurrent() (τ = 14 s) and Voltage()                                                                                                  |

| 4                 | Design energy/5: C Rate based off of Design Energy /5 or a C/5 rate in mA.                                                                                                                                |

| 5                 | Use the value specified by AtRate()                                                                                                                                                                       |

| 6                 | Use the value in User_Rate-Pwr. This gives a completely user-configurable method.                                                                                                                         |

### 8.3.2.3 Reserve Cap-mAh

**Reserve Cap-mAh** determines how much actual remaining capacity exists after reaching 0 *RemainingCapacity()*, before **Terminate Voltage** is reached when **Load Mode** = 0 is selected. A loaded rate or no-load rate of compensation can be selected for *Reserve Cap* by setting the [RESCAP] bit in *Pack Configuration* data flash register.

### 8.3.2.4 Reserve Energy

**Reserve Energy** determines how much actual remaining capacity exists after reaching 0 RemainingCapacity() which is equivalent to 0 remaining power, before **Terminate Voltage** is reached when **Load Mode** = 1 is selected. A loaded rate or no-load rate of compensation can be selected for *Reserve Cap* by setting the [RESCAP] bit in *Pack Configuration* data flash register..

### 8.3.2.5 Design Energy Scale

**Design Energy Scale** is used to select the scale/unit of a set of data flash parameters. The value of **Design Energy Scale** can be either 1 or 10 only, other values are not supported. For battery capacities larger than 6 AHr, **Design Energy Scale** = 10 is recommended.

| DATA FLASH            | DESIGN ENERGY SCALE = 1 (default) | DESIGN ENERGY SCALE = 10 |  |  |

|-----------------------|-----------------------------------|--------------------------|--|--|

| Design Energy         | mWh                               | cWh                      |  |  |

| Reserve Energy        | mWh                               | cWh                      |  |  |

| Avg Power Last Run mW |                                   | cW                       |  |  |

| User Rate-Pwr         | mWh                               | cWh                      |  |  |

| T Rise                | No Scale                          | Scaled by ×10            |  |  |

### Table 3. Data Flash Parameter Scale/Unit Based On Design Energy Scale

### 8.3.2.6 Dsg Current Threshold

This register is used as a threshold by many functions in the bq27545-G1 to determine if actual discharge current is flowing into or out of the cell. The default for this register should be sufficient for most applications. This threshold should be set low enough to be below any normal application load current but high enough to prevent noise or drift from affecting the measurement.

### 8.3.2.7 Chg Current Threshold

This register is used as a threshold by many functions in the bq27545-G1 to determine if actual charge current is flowing into or out of the cell. The default for this register should be sufficient for most applications. This threshold should be set low enough to be below any normal charge current but high enough to prevent noise or drift from affecting the measurement.

### 8.3.2.8 Quit Current, Dsg Relax Time, Chg Relax Time, and Quit Relax Time

The **Quit Current** is used as part of the Impedance Track algorithm to determine when the bq27545-G1 enters RELAX mode from a current flowing mode in either the charge direction or the discharge direction. The value of Quit Current is set to a default value that should be above the standby current of the system.

Either of the following criteria must be met to enter RELAX mode:

- 1. | AverageCurrent() | < | Quit Current | for Dsg Relax Time.

- 2. | AverageCurrent() | < | Quit Current | for Chg Relax Time.

After about 6 minutes in RELAX mode, the bq27545-G1 attempts to take accurate OCV readings. An additional requirement of dV/dt < 1  $\mu$ V/s is required for the bq27545-G1 to perform Qmax updates. These updates are used in the Impedance Track algorithms. It is critical that the battery voltage be relaxed during OCV readings and that the current is not higher than C/20 when attempting to go into RELAX mode.

**Quit Relax Time** specifies the minimum time required for AverageCurrent() to remain above the **QuitCurrent** threshold before exiting RELAX mode.

### 8.3.2.9 Qmax

**Qmax** contains the maximum chemical capacity of the active cell profiles, and is determined by comparing states of charge before and after applying the load with the amount of charge passed. They also correspond to capacity at low rate of discharge, such as C/20 rate. For high accuracy, this value is periodically updated by the bq27545-G1 during operation. Based on the battery cell capacity information, the initial value of chemical capacity should be entered in **Qmax** field. The Impedance Track algorithm will update this value and maintain it in the **Pack** profile.

### 8.3.2.10 Update Status

The **Update Status** register indicates the status of the Impedance Track algorithm.

| UPDATE STATUS | STATUS                                                                                                                                              |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x02          | Qmax and Ra data are learned, but Impedance Track is not enabled. This should be the standard setting for a golden image.                           |

| 0x04          | Impedance Track is enabled but Qmax and Ra data are not learned.                                                                                    |

| 0x05          | Impedance Track is enabled and only Qmax has been updated during a learning cycle.                                                                  |

| 0x06          | Impedance Track is enabled. Qmax and Ra data are learned after a successful learning cycle. This should be the operation setting for end equipment. |

Table 4. Update Status Definitions

This register should only be updated by the bq27545-G1 during a learning cycle or when *IT\_ENABLE* subcommand is received. Refer to the *How to Generate Golden Image for Single-Cell Impedance Track Device Application Note* (SLUA544) for learning cycle details.

### 8.3.2.11 Avg I Last Run

The bq27545-G1 logs the current averaged from the beginning to the end of each discharge cycle. It stores this average current from the previous discharge cycle in this register. This register should never be modified. It is only updated by the bq27545-G1 when required.

### 8.3.2.12 Avg P Last Run

The bq27545-G1 logs the power averaged from the beginning to the end of each discharge cycle. It stores this average power from the previous discharge cycle in this register. To get a correct average power reading the bq27545-G1 continuously multiplies instantaneous current times *Voltage()* to get power. It then logs this data to derive the average power. This register should never require modification. It is only updated by the bq27545-G1 when required.

### 8.3.2.13 Delta Voltage

The bq27545-G1 stores the maximum difference of *Voltage()* during short load spikes and normal load, so the Impedance Track algorithm can calculate remaining capacity for pulsed loads. It is not recommended to change this value.

### 8.3.2.14 Ra Tables and Ra Filtering Related Parameters

These tables contain encoded data and are automatically updated during device operation. The bq27545-G1 has a filtering process to eliminate unexpected fluctuations in Ra values while the Ra values are being updated. The DF parameters **RaFilter**, **RaMaxDelta**, **MaxResfactor**, and **MinResfactor** control the Filtering process of Ra values. **RaMaxDelta** Limits the change in Ra values to an absolute magnitude. **MinResFactor** and **MaxResFactor** parameters are cumulative filters which limit the change in Ra values to a scale on a per discharge cycle basis. These values are data flash configurable. No further user changes should be made to Ra values except for reading/writing the values from a pre-learned pack (part of the process for creating golden image files).

### 8.3.2.15 MaxScaleBackGrid

*MaxScaleBackGrid* parameter limits the resistance grid point after which back scaling will not be performed. This variable ensures that the resistance values in the lower resistance grid points remain accurate while the battery is at a higher DoD state.

### 8.3.2.16 Max DeltaV, Min DeltaV

Maximal/Minimal value allowed for delta V, which will be subtracted from simulated voltage during remaining capacity simulation.

### 8.3.2.17 Qmax Max Delta %

Maximal change of Qmax during one update, as percentage of *Design Capacity*. If the gauges attempts to change Qmax exceeds this limit, changed value will be capped to old value  $\pm$  DesignCapacity  $\times$  QmaxMaxDelta/100.

### 8.3.2.18 Fast Resistance Scaling

When Fast Resistance Scaling is enabled by setting the [FConvEn] bit in Pack Configuration B, the algorithm improves accuracy at the end of discharge. The RemainingCapacity() and StateOfCharge() should smoothly converge to 0. The algorithm starts convergence improvements when cell voltage goes below (Terminate Voltage + Term V Delta) or StateofCharge() goes below Fast Scale Start SOC. For most applications, the default value of Term V Delta and Fast Scale Start SOC are recommended. Also TI recommends keeping (Terminate Voltage + Term V Delta) below 3.6 V for most battery applications.

### 8.3.2.19 StateOfCharge() Smoothing

When operating conditions change (such as temperature, discharge current, and resistance, for example), it can lead to large changes of compensated battery capacity and battery capacity remaining. These changes can result in large changes of *StateOfCharge()*. When *[SmoothEn]* is enabled in *Pack Configuration C*, the smoothing algorithm injects gradual changes of battery capacity when conditions vary. This results in a gradual change of *StateOfCharge()* and can provide a better end-user experience for *StateOfCharge()* reporting.

The *RemainingCapacity()*, *FullChargeCapacity()*, and *StateOfCharge()* are modified depending on [*SmoothEn*] as below.

| [SmoothEn] | RemainingCapacity() | FullChargeCapacity() | StateOfCharge()                |

|------------|---------------------|----------------------|--------------------------------|

| 0          | UnfilteredRM()      | UnfilteredFCC()      | UnfilteredRM()/UnfilteredFCC() |

| 1          | FilteredRM()        | FilteredFCC()        | FilteredRM()/FilteredFCC()     |

### 8.3.2.20 DeltaV Max Delta

Maximal change of Delta V value. If attempted change of the value exceeds this limit, change value will be capped to old value ±DeltaV Max Delta.

### 8.3.2.21 Lifetime Data Logging Parameters

The Lifetime Data logging function helps development and diagnosis with the bq27545-G1. IT\_ENABLE must be enabled (Command 0x0021) for lifetime data logging functions to be active. bq27545-G1 logs the lifetime data as specified in the *Lifetime Data* and *Lifetime Temp Samples* data Flash Subclasses. The data log recordings are controlled by the *Lifetime Resolution* data flash subclass.

The Lifetime Data Logging can be started by setting the IT\_ENABLE bit and setting the Update Time register to a non-zero value.

Once the Lifetime Data Logging function is enabled, the measured values are compared to what is already stored in the data flash. If the measured value is higher than the maximum or lower than the minimum value stored in the data flash by more than the *Resolution* set for at least one parameter, the entire Data Flash Lifetime Registers are updated after at least LTUpdateTime.

LTUpdateTime sets the minimum update time between DF writes. When a new maximum or minimum is detected, a LT Update window of [update time] second is enabled and the DF writes occur at the end of this window. Any additional max/min value detected within this window will also be updated. The first new maximum or minimum value detected after this window will trigger the next LT Update window.

Internal to bq27545-G1, there exists a RAM maximum or minimum table in addition to the DF maximum or minimum table. The RAM table is updated independent of the resolution parameters. The DF table is updated only if at least one of the RAM parameters exceeds the DF value by more than resolution associated with it. When DF is updated, the entire RAM table is written to DF. Consequently, it is possible to see a new maximum or minimum value for a certain parameter even if the value of this parameter never exceeds the maximum or minimum value stored in the data flash for this parameter value by the resolution amount.

The Life Time Data Logging of one or more parameters can be reset or restarted by writing new default (or starting) values to the corresponding data flash registers through sealed or unsealed access as described below. However, when using unsealed access, new values will only take effect after device reset

The logged data can be accessed as R/W in UNSEALED mode from Lifetime Data Subclass (Subclass ID = 59) of data flash. Lifetime data may be accessed (R/W) when sealed using a process identical Manufacturer Info Block B. The DataFlashBlock command code is 4. Note only the first 32 bytes of lifetime data (not resolution parameters) can be R/W when sealed. See *Manufacturer Information Blocks* for sealed access. The logging settings such as Temperature Resolution, Voltage Resolution, Current Resolution, and Update Time can be configured only in UNSEALED mode by writing to the Lifetime Resolution Subclass (SubclassID = 66) of the data flash.

The Lifetime resolution registers contain the parameters that set the limits related to how much a data parameter must exceed the previously logged maximum or minimum value to be updated in the lifetime log. For example, V must exceed MaxV by more than Voltage Resolution to update MaxV in the data flash.

### 8.4 Device Functional Modes

### 8.4.1 System Control Function