## 8チャネル高速ADC内蔵、 16チャネル可変ゲイン・アンプ(VGA)

### 特 長

- 可変ゲイン・アンプ (VGA) ×16

- 最大1V<sub>PP</sub>振幅のシングルエンド・バッファリング入力 ×16

- VCA入力ノイズ : 5.5nV/ $\sqrt{\text{Hz}}$  (ゲイン31dB時)

- 可変ゲイン : -5dB～31dB(0.125dBステップ)

- デジタル・ゲイン制御

- カットオフ周波数をプログラミング可能 (7.5、10、14MHz) な3次アンチエイリアシング・フィルタ

- クランプ回路

- A/Dコンバータ (ADC)

- 8チャネル、12ビット、65MSPS

- 入力チャネルあたり最大32.5MSPS

- 各ADCで2つのVGA出力を交互にサンプリング

- 内部/外部リファレンスをサポート

- リファレンス用外付けデカッピングが不要

- シリアルLVDS出力

- 電源 : 1.8Vおよび3.3V

- チャネルあたり合計電力 : 39mW (32.5MSPS時)

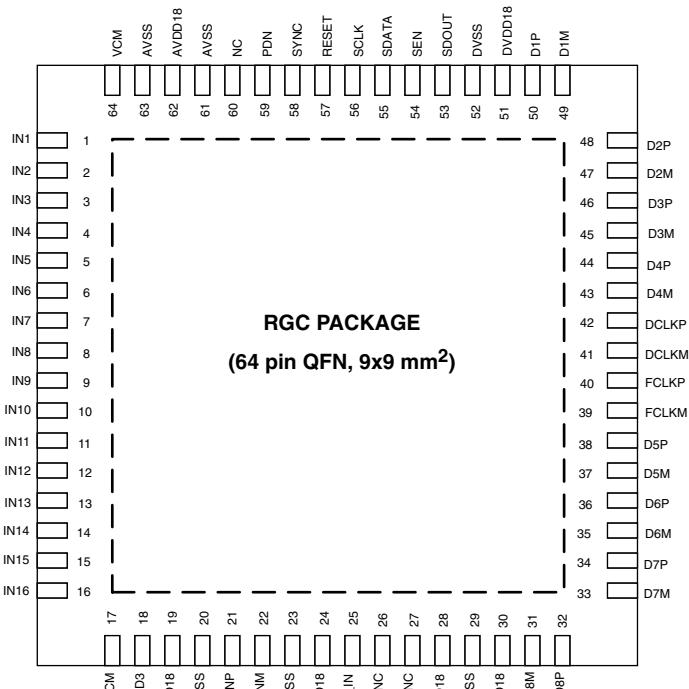

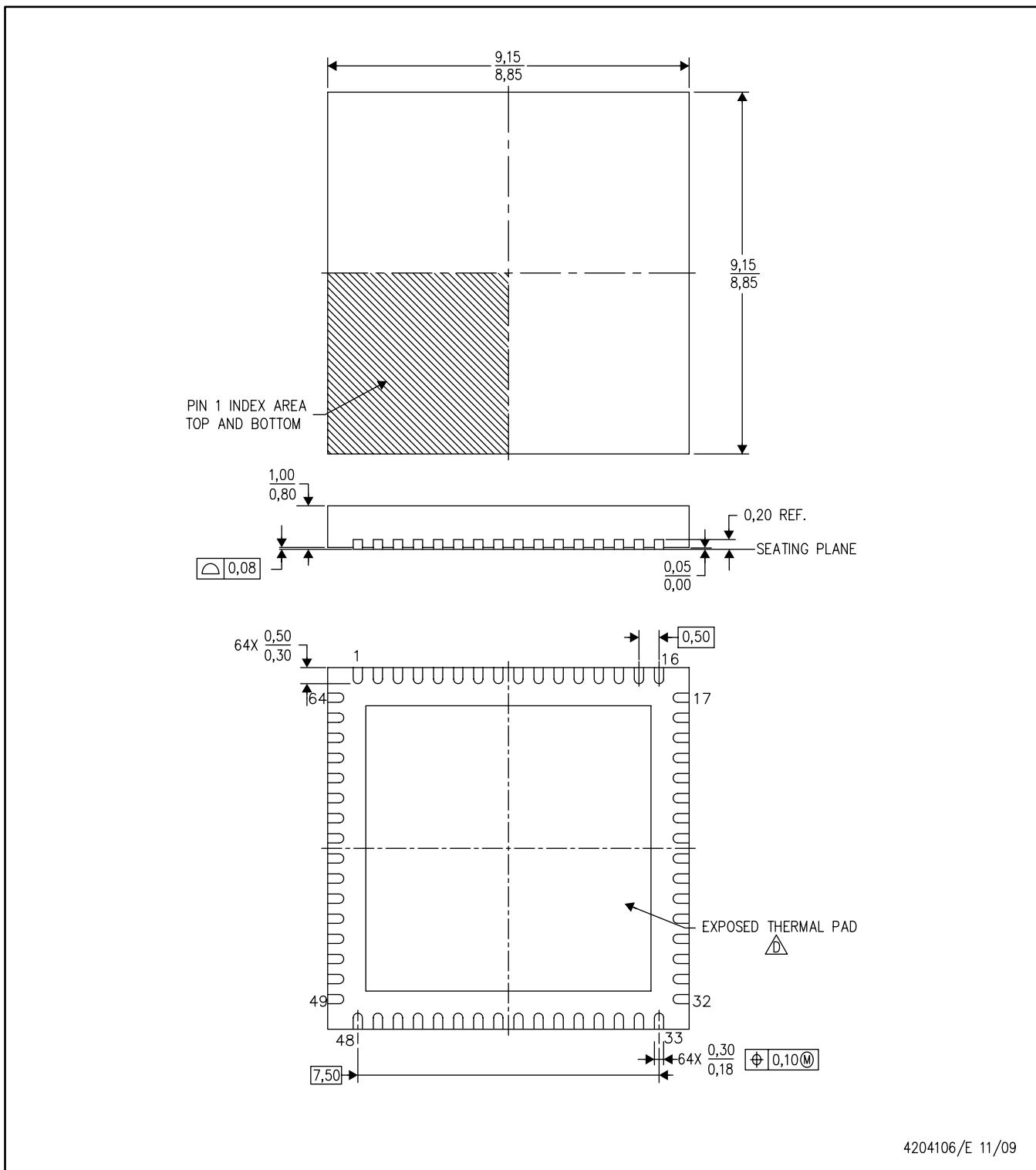

- 64ピンQFNパッケージ (9mm × 9mm)

### アプリケーション

- イメージング : 超音波、PET

### 関連デバイス

- AFE5801 : 8チャネルVGA+ADC、65MSPS/チャネル

### 概 要

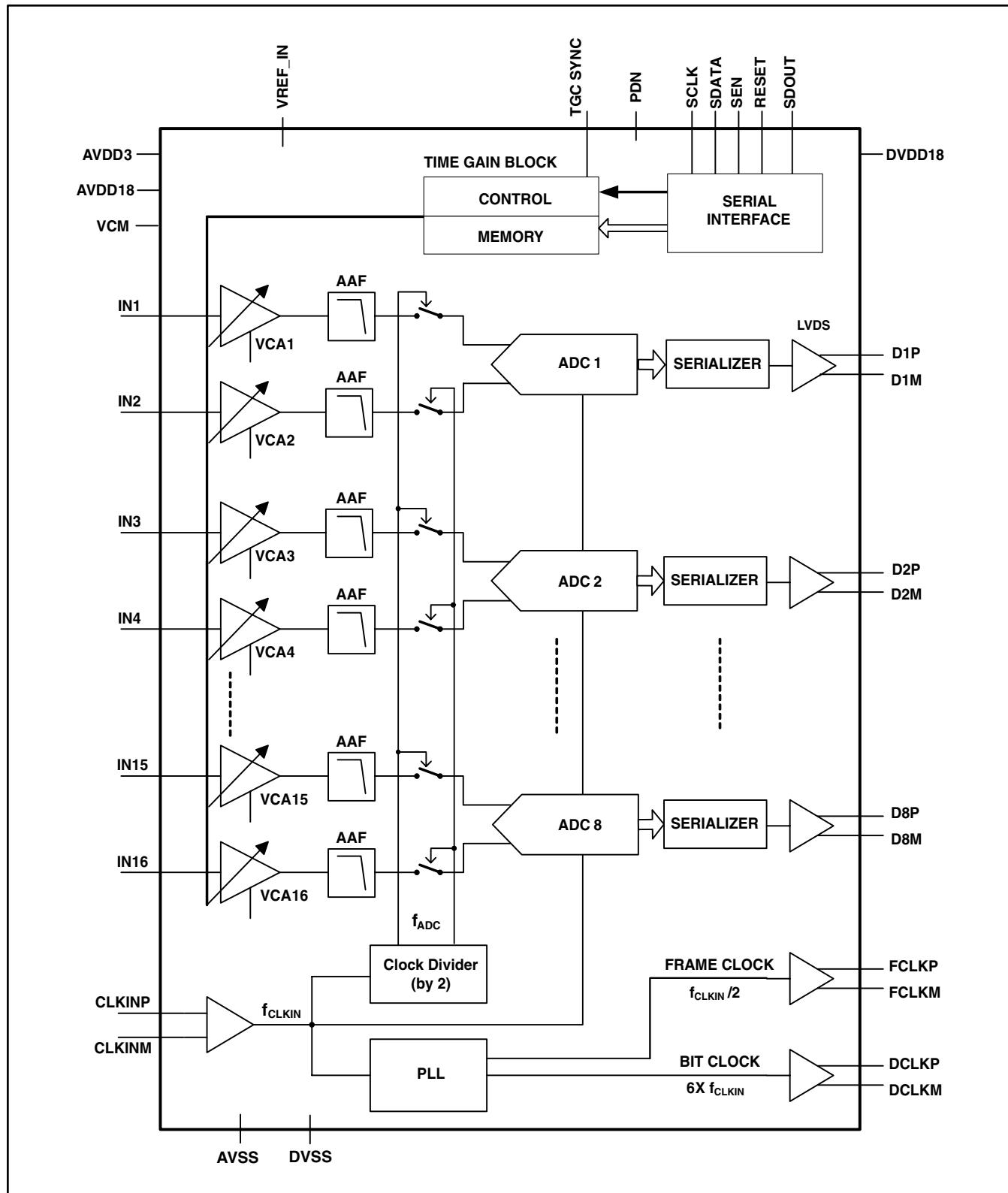

AFE5851は、電力および集積度が重要となるアプリケーション向けのアナログ・フロントエンドです。16個の可変ゲイン・アンプ (VGA) に続き、8チャネルの高速 (最大65MSPS) A/Dコンバータ (ADC) を内蔵しています。

16個のシングルエンド入力はそれぞれバッファリングされ、入力振幅は最大1V<sub>PP</sub>です。VGAのゲイン範囲は、-5dB～31dBです。VGAのゲインはデジタル制御され、時間に対するゲイン曲線は、シリアル・インターフェイス経由でデバイスに内蔵されたメモリに格納できます。

また、各チャネルのVGAとADCの間には、クランプおよびアンチエイリアシング用の選択可能なローパス・フィルタ (7.5、10、または14MHzで3dBの減衰) が内蔵されています。VGA/アンチエイリアシング・フィルタは、差動出力 (2V<sub>PP</sub>に制限) によって、12ビット、65MSPSの内蔵ADCを駆動します。消費電力を最適化するため、各ADCは2つのVGAで共有されます。各VGA出力はクロック・サイクル毎に交互にサンプリングされ、実効的なサンプリング周波数は入力クロック・レートの1/2となります。また、低いサンプリング・レートを選択すると、ADCの消費電力はそれに応じて低減されます。

ADCの出力はLVDSストリームでシリアル化され、電力と基板領域をさらに削減します。AFE5851は64ピンQFNパッケージ ( $9 \times 9\text{mm}^2$ ) で供給され、産業用温度範囲の全体 (-40°C～85°C) で仕様が規定されています。

SWIFTはテキサス・インスツルメンツの登録商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

## 静電気放電対策

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時に、MOSゲートに対する静電破壊を防止するために、リード線どうしを短絡しておくか、デバイスを導電性のフォームに入れる必要があります。

## ブロック図

## ピン配置

## ピン機能

| 名前                               | 番号                   | 説明                                             |

|----------------------------------|----------------------|------------------------------------------------|

| IN1-IN16                         | 1-16                 | チャネル1~16のシングルエンド・アナログ入力ピン。                     |

| CLKINP, CLKINM                   | 21, 22               | 差動クロック入力ピン。シングルエンド・クロックもサポートされます(「クロック入力」を参照)。 |

| VCM                              | 17, 64               | アナログ入力信号のバイアス用の同相出力ピン。                         |

| VREF_IN                          | 25                   | 外部リファレンス・モード時のリファレンス入力。                        |

| RESET                            | 57                   | ハードウェア・リセット・ピン(アクティブ・ハイ)。                      |

| SCLK                             | 56                   | シリアル・インターフェイスのクロック入力。                          |

| SDATA                            | 55                   | シリアル・インターフェイスのデータ入力。                           |

| SEN                              | 54                   | シリアル・インターフェイスのイネーブル入力。                         |

| SDOUT                            | 53                   | シリアル・インターフェイスのデータ読み出し出力。                       |

| PDN                              | 59                   | グローバル・パワーダウン制御入力(アクティブ・ハイ)。                    |

| SYNC                             | 58                   | TGC/VGA同期信号入力。                                 |

| D1P/M... D4P/M<br>D5P/M... D8P/M | 50... 43<br>38... 31 | チャネル1/2、3/4、5/6、... 15/16のLVDS出力。              |

| FCLKM, FCLKP                     | 39, 40               | LVDSフレーム・クロック出力。                               |

| DCLKM,DCLP                       | 41, 42               | LVDSビット・クロック出力。                                |

| AVDD3                            | 18                   | 3.3Vアナログ電源電圧。                                  |

| AVDD18                           | 19, 24, 62           | 1.8Vアナログ電源電圧。                                  |

| DVDD18                           | 28, 30, 51           | 1.8V LVDSバッファ電源電圧。                             |

| AVSS                             | 20, 23, 61, 63       | アナログ・グランド。                                     |

| DVSS                             | 29, 52               | デジタル・グランド。                                     |

| NC                               | 26, 27, 60           | 接続しません。                                        |

| サーマル・パッド                         | パッケージ底面              | AVSSに接続します。                                    |

## 製品情報<sup>(1)</sup>

| 製品名     | パッケージ・リード             | パッケージ・コード | 規定温度範囲        | パッケージ<br>捺印 | 型番           | 出荷形態、<br>数量  |

|---------|-----------------------|-----------|---------------|-------------|--------------|--------------|

| AFE5851 | QFN-64 <sup>(2)</sup> | RGC       | −40°C to 85°C | AFE5851     | AFE5851IRGCT | テープ・リール、250  |

|         |                       |           |               | AFE5851     | AFE5851IRGCR | テープ・リール、2000 |

(1) 最新のパッケージ情報とご発注情報については、このデータシートの巻末にある「付録：パッケージ・オプション」を参照するか、またはTIのWebサイト([www.ti.com](http://www.ti.com)または[www.tij.co.jp](http://www.tij.co.jp))をご覧ください。

(2) パッケージのサーマル・パッドのサイズについては、このドキュメントの巻末にあるメカニカル図面を参照してください。

## 絶対最大定格<sup>(1)</sup>

動作温度範囲内(特に記述のない限り)

|                                             | レンジ                                | 単位 |

|---------------------------------------------|------------------------------------|----|

| AVDD3 ~ AVSS                                | −0.3 ~ 3.8                         | V  |

| AVDD18 ~ AVSS                               | −0.3 ~ 2.2                         | V  |

| DVDD18 ~ DVSS                               | −0.3 ~ 2.2                         | V  |

| AVSS-DVSS間の電圧                               | −0.3 ~ 0.3                         | V  |

| アナログ入力ピン(IN <sub>i</sub> ) ~ AVSS           | −0.3V ~ (3.6またはAVDD3+0.3のいずれか小さい方) | V  |

| VREF_IN ~ AVSS                              | −0.3 ~ 2.2                         | V  |

| V <sub>CLKP</sub> 、V <sub>CLKM</sub> ~ AVSS | −0.3 ~ 2.2                         | V  |

| デジタル制御ピン～DVSS                               | −0.3 ~ 2.2                         | V  |

| ESD 人体モデル                                   | 2                                  | kV |

| T <sub>J</sub> 最大動作接合部温度                    | 125                                | °C |

| T <sub>sig</sub> 保存温度範囲                     | −60 ~ 150                          | °C |

(1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示しており、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

## 熱特性

動作温度範囲内(特に記述のない限り)

|                 |                                              | TYP   | 単位   |

|-----------------|----------------------------------------------|-------|------|

| θ <sub>JA</sub> | OLFM エア・フロー                                  | 23.17 | °C/W |

| θ <sub>JC</sub> | 2オンス銅パターン、JEDEC標準4層3インチ × 3インチPCBにパッドを直接半田付け | 22.1  | °C/W |

## 推奨動作条件

| パラメータ                |                                       | MIN     | TYP     | MAX  | 単位 |

|----------------------|---------------------------------------|---------|---------|------|----|

| T <sub>A</sub>       | 周囲温度                                  | −40     | 85      | 85   | °C |

| <b>電源</b>            |                                       |         |         |      |    |

| AVDD3                | アナログ電源電圧(VGA)                         | 3.0     | 3.3     | 3.6  | V  |

| AVDD18               | アナログ電源電圧(ADC)                         | 1.7     | 1.8     | 1.9  | V  |

| DVDD18               | デジタル電源電圧(ADC、LVDS)                    | 1.7     | 1.8     | 1.9  | V  |

| <b>アナログ入力</b>        |                                       |         |         |      |    |

| IN <sub>i</sub>      | 入力電圧                                  | VCM−0.5 | VCM+0.5 | V    |    |

| 外部リファレンス・モードのVREF_IN |                                       | 1.35    | 1.4     | 1.45 | V  |

| VCM負荷                |                                       | 3       |         | mA   |    |

| <b>クロック入力</b>        |                                       |         |         |      |    |

| f <sub>CLKIN</sub>   | 入力クロック周波数                             | 5       | 65      | MHz  |    |

| f <sub>Channel</sub> | チャネル・サンプリング周波数(f <sub>CLKIN</sub> /2) | 2.5     | 32.5    | MSPS |    |

| 入力クロック・デューティ・サイクル    |                                       | 40%     | 50%     | 60%  |    |

## 推奨動作条件

| パラメータ               |                                       | MIN | TYP | MAX | 単位       |

|---------------------|---------------------------------------|-----|-----|-----|----------|

| $V_{CLKINP-CLKINP}$ | 正弦波、AC結合                              | 0.5 |     |     | $V_{PP}$ |

|                     | LVPECL、AC結合                           |     | 1.6 |     | $V_{PP}$ |

|                     | LVDS、AC結合                             |     | 0.7 |     | $V_{PP}$ |

| $V_{CLKINP}$        | LVCMOS、シングルエンド、 $V_{CLKINP}$ をAVSSに接続 |     | 1.8 |     | $V_{PP}$ |

| デジタル出力              |                                       |     |     |     |          |

| $C_{LOAD}$          | 各出力ピン-DVSS間の外部負荷容量                    |     | 5   |     | $pF$     |

| $R_{LOAD}$          | LVDS出力ペア間の差動負荷抵抗(外部)                  |     | 100 |     | $\Omega$ |

## 電気的特性

特に記述のない限り、標準値は25°C、最小値および最大値は $T_{min} = -40^{\circ}\text{C}$ ～ $T_{max} = 85^{\circ}\text{C}$ の全温度範囲、AVDD3 = 3.3V、AVDD18 = 1.8V、DVDD18 = 1.8V、-1dBFSアナログ入力を0.1μFでAC結合、内部リファレンス・モード、最大定格チャネル・サンプリング周波数(32.5 MSPS)、LVCMOS(シングルエンド)クロック、50%デューティ・サイクル、アンチエイリアシング・フィルタを14MHz(3dBコナー)に設定、出力クランプはディスエーブル、アナログ・ハイパス・フィルタはイネーブルです。

| パラメータ                | 測定条件                                     | MIN           | TYP  | MAX  | 単位             |

|----------------------|------------------------------------------|---------------|------|------|----------------|

| 可変ゲイン・アンプ(VGA)       |                                          |               |      |      |                |

| 最大入力電圧振幅             | 直線動作                                     | 1             |      |      | $V_{pp}$       |

| VCM 同相電圧             | 入力におけるDCレベル                              | 1.6           |      |      | V              |

| ゲイン範囲                | 最大ゲイン - 最小ゲイン                            | 36            |      |      | dB             |

| 最大ゲイン                |                                          | 29.5          | 31   | 32.5 |                |

| ゲイン分解能               |                                          | 0.125<br>または1 |      |      | dB             |

| 入力抵抗                 | 入力～DCバイアス・レベル                            | 5             |      |      | $k\Omega$      |

| 入力容量                 | 入力～AVSS                                  | 2             |      |      | $pF$           |

| アンチエイリアシング・フィルタ(AAF) |                                          |               |      |      |                |

| AAFカットオフ周波数          | 7.5MHz フィルタを選択                           | -3 dB         | 7.5  |      | MHz            |

|                      | 10MHz フィルタを選択                            |               | 10   |      |                |

|                      | 14MHz フィルタを選択                            |               | 14   |      |                |

| AAF遮断帯域減衰            | 7.5MHz フィルタを選択                           | -6 dB         | 10   |      | MHz            |

|                      | 10MHz フィルタを選択                            |               | 14   |      |                |

|                      | 14MHz フィルタを選択                            |               | 20   |      |                |

| AAF帯域内減衰             | 7.5MHz フィルタを選択                           | -12 dB        | 18   |      | MHz            |

|                      | 10MHz フィルタを選択                            |               | 24   |      |                |

|                      | 14MHz フィルタを選択                            |               | 30   |      |                |

| フルチャネル特性             | 7.5MHz フィルタを選択                           | 3.2MHz時       | 1.2  |      | dB             |

|                      | 10MHz フィルタを選択                            |               | 0.5  |      |                |

|                      | 14MHz フィルタを選択                            |               | 0.2  |      |                |

| ゲイン・マッチング            |                                          |               |      |      |                |

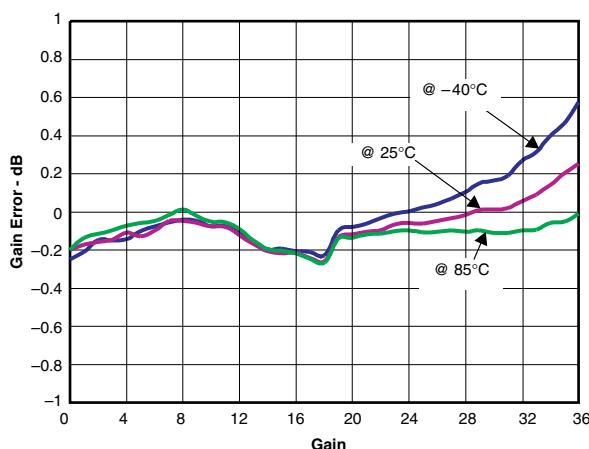

| ゲイン誤差                | チャネル間およびデバイス間                            | +0.1          | +0.6 |      | dB             |

|                      | -5～28dBゲイン                               | -1.2          | ±0.3 | 1.2  | dB             |

| > 28dBゲイン            |                                          | -1.8          | ±0.5 | 1.8  |                |

| オフセット誤差              | 31dBゲイン                                  | -50           | 50   |      | LSB            |

| 入力換算ノイズ電圧            | 5MHz、VGAゲイン31dB、低ノイズ・モード                 | 5             | 6.5  |      | $nV/\sqrt{Hz}$ |

|                      | 5MHz、VGAゲイン31dB、デフォルト・ノイズ・モード            |               | 5.5  |      |                |

| SNR 信号対雑音比           | -1dBFS ADC入力、ゲイン6dB                      | 66            |      |      | dBFS           |

| HD2 2次高調波歪           | -1dBFS ADC入力、VGAゲイン17dB、 $f_{in} = 2MHz$ | -48           | -55  |      | dBc            |

|                      | -1dBFS ADC入力、VGAゲイン31dB、 $f_{in} = 2MHz$ | -55           | -65  |      |                |

| HD3 3次高調波歪           | -1dBFS ADC入力、VGAゲイン17dB、 $f_{in} = 2MHz$ | -52           | -63  |      | dBc            |

|                      | -1dBFS ADC入力、VGAゲイン31dB、 $f_{in} = 2MHz$ | -48           | -58  |      |                |

## 電気的特性

特に記述のない限り、標準値は25°C、最小値および最大値は $T_{min} = -40^{\circ}\text{C}$ ～ $T_{max} = 85^{\circ}\text{C}$ の全温度範囲、AVDD3 = 3.3V、AVDD18 = 1.8V、DVDD18 = 1.8V、-1dBFSアナログ入力を $0.1\mu\text{F}$ でAC結合、内部リファレンス・モード、最大定格チャネル・サンプリング周波数(32.5 MSPS)、LVC MOS(シングルエンド)クロック、50%デューティ・サイクル、アンチエイリアシング・フィルタを14MHz(3dBコーナー)に設定、出力クランプはディスエーブル、アナログ・ハイパス・フィルタはイネーブルです。

| パラメータ                   | 測定条件                                                                                          | MIN | TYP       | MAX | 単位          |

|-------------------------|-----------------------------------------------------------------------------------------------|-----|-----------|-----|-------------|

| SFDR スピアスフリー・ダイナミック・レンジ | -1dBFS ADC入力、VGAゲイン17dB、 $f_{in} = 2\text{MHz}$                                               |     | 55        |     | dBc         |

| THD 全高調波歪               | -1dBFS ADC入力、VGAゲイン17dB、 $f_{in} = 2\text{MHz}$                                               |     | 4         |     | dBc         |

| IMD 相互変調歪               | $f_{in1} = 1\text{MHz}$ 、 $f_{in2} = 2\text{MHz}$ 、 $A_{in1,in2} = -7\text{dBFS}$ 、VGAゲイン30dB |     | -70       |     | dBFS        |

| 群遅延変動                   | $f_{in} = 100\text{kHz}$ ～14MHz、ゲイン設定間およびチャネル間                                                |     | $\pm 3.5$ |     | ns          |

|                         | $f_{in} = 100\text{kHz}$ ～14MHz、チャネル間                                                         |     | $\pm 1.5$ |     |             |

| 入力過負荷回復                 | $\leq 6\text{dB}$ の過負荷から1%以内まで                                                                |     | 1         |     | 入力クロック・サイクル |

| クランプ・レベル                | 増幅後。クランプはデフォルトでイネーブル。                                                                         |     | 3         |     | dB          |

| ADCビット数                 |                                                                                               |     | 12        |     |             |

| クロストーク                  | アグレッサ： $f_{in} = 2\text{MHz}$ 、ADCフルスケールの1dB下<br>ピクティム(同じADCを共有するチャネル)：50ΩをAVSSに接続            |     | 65        |     | dB          |

| 消費電力                    |                                                                                               |     |           |     |             |

| 合計消費電力                  | デフォルト・ノイズ・モード                                                                                 | 633 | 723       |     | mW          |

|                         | 低ノイズ・モード                                                                                      | 715 | 831       |     |             |

| $I_{AVDD3}$ AVDD3消費電流   |                                                                                               | 4.7 | 7         |     | mA          |

| $I_{AVDD18}$ AVDD18消費電流 | デフォルト・ノイズ・モード                                                                                 | 259 | 290       |     | mA          |

|                         | 低ノイズ・モード                                                                                      | 310 | 350       |     |             |

| $I_{DVDD18}$ DVDD18消費電流 |                                                                                               | 81  | 100       |     | mA          |

| パワーダウン                  | スタンバイ・モード                                                                                     | 64  |           |     | mW          |

|                         | フル・パワーダウン・モード                                                                                 | 5   | 30        |     | mW          |

| AC PSRR 電源除去比           |                                                                                               | -30 |           |     | dBc         |

## デジタル特性<sup>(1)</sup>

DC仕様は、デジタル出力のスイッチングなし、有効な論理レベル0または1に固定、の条件で規定されています。

特に記述のない限り、標準値は25°C、最小値および最大値は $T_{min} = -40^{\circ}\text{C}$ ～ $T_{max} = 85^{\circ}\text{C}$ の全温度範囲、AVDD3 = 3.3V、AVDD18 = 1.8V、DVDD18 = 1.8V、LVDS出力ペア間の外付け差動負荷抵抗 $R_{load} = 100\Omega$ です。

| パラメータ              | 測定条件                                   | MIN  | TYP  | MAX | 単位            |

|--------------------|----------------------------------------|------|------|-----|---------------|

| デジタル入力             |                                        |      |      |     |               |

| “High” レベル入力電圧     |                                        | 1.4  | 3.6  |     | V             |

| “Low” レベル入力電圧      |                                        |      | 0.8  |     | V             |

| “High” レベル入力電流     |                                        | 10   |      |     | $\mu\text{A}$ |

| “Low” レベル入力電流      |                                        | 10   |      |     | $\mu\text{A}$ |

| 入力容量               |                                        | 4    |      |     | pF            |

| デジタル出力             |                                        |      |      |     |               |

| “High” レベル出力電圧     |                                        | 1375 |      |     | mV            |

| “Low” レベル出力電圧      |                                        | 1025 |      |     |               |

| 出力差動電圧 $ V_{Opl} $ |                                        | 270  | 380  | 490 |               |

| 出力オフセット電圧 $V_{OS}$ | D <sub>P</sub> およびD <sub>M</sub> の同相電圧 | 0.9  | 1.15 | 1.5 | V             |

| 出力容量               | デバイス内部の出力容量、一方の出力からDVSS間               | 2    |      |     | pF            |

(1) 注：すべてのLVDS仕様は、特性で規定される値であり、実製品のテストは行っていません。

## 出力インターフェイス・タイミング<sup>(1)</sup>

標準値は25°Cの値、AVDD3 = 3.3V、AVDD18 = DVDD = 1.8V、LVC MOS(シングルエンド)クロック、C<sub>LOAD</sub> = 5pF、R<sub>LOAD</sub> = 100Ω、I<sub>O</sub> = 3.5mA(特に記述のない限り)。最小値および最大値はT<sub>MIN</sub> = -40°C～T<sub>MAX</sub> = 85°Cの全温度範囲での値。

| パラメータ                                          | 測定条件                                                                  | MIN                                                                                            | TYP  | MAX  | 単位          |    |

|------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|------|-------------|----|

| t <sub>a</sub><br>アバーチャ遅延                      | 入力サンプリング・クロックの立ち上がりエッジから、実際にサンプリングが行われるまでの遅延時間                        | 0.7                                                                                            | 3    |      | ns          |    |

| アバーチャ遅延マッチング                                   | 同じデバイス内のチャネル間                                                         |                                                                                                | ±150 |      | ps          |    |

| t <sub>j</sub><br>アバーチャ・ジッタ                    |                                                                       |                                                                                                | 450  |      | fs rms      |    |

| ウェイクアップ時間                                      | スタンバイ・モードから出た後、有効なデータまでの時間                                            | 10                                                                                             | 50   |      | μs          |    |

|                                                | PDNグローバル・モードから出た後、有効なデータまでの時間                                         | 50                                                                                             | 200  |      |             |    |

|                                                | 入力クロックを停止および再起動した後、有効なデータまでの時間                                        | 30                                                                                             | 200  |      |             |    |

| ADCレイテンシ                                       | デフォルト、リセット後                                                           |                                                                                                | 11   |      | 入力クロック・サイクル |    |

| t <sub>delay</sub>                             | 入力クロックの立ち上がりエッジ(ゼロ・クロス)からフレーム・クロックの立ち上がりエッジ(ゼロ・クロス) - 入力クロック周期(T)の1/2 | 3                                                                                              | 4.7  | 6.4  | ns          |    |

| t <sub>delay</sub><br>変動                       | 固定電源、Tの差が20°C                                                         | -1                                                                                             | 1    |      | ns          |    |

| t <sub>RISE</sub><br>t <sub>FALL</sub>         | データ立ち上がり時間<br>データ立ち下がり時間                                              | 立上がり時間は-100mVから100mVまでを測定<br>立ち下がり時間は100mVから-100mVまでを測定<br>10 MHz < f <sub>CLKIN</sub> < 65MHz | 0.1  | 0.25 | 0.4         | ns |

| t <sub>FCLKRISE</sub><br>t <sub>FCLKFALL</sub> | フレーム・クロック立ち上がり時間<br>フレーム・クロック立ち下がり時間                                  | 立上がり時間は-100mVから100mVまでを測定<br>立ち下がり時間は100mVから-100mVまでを測定<br>10MHz < f <sub>CLKIN</sub> < 65MHz  | 0.1  | 0.25 | 0.4         | ns |

|                                                | フレーム・クロックのデューティ・サイクル                                                  | 立上がりエッジのゼロ・クロスから立ち下がりエッジのゼロ・クロスまで                                                              | 48   | 50   | 52          | ns |

| t <sub>DCLKRISE</sub><br>t <sub>DCLKFALL</sub> | ビット・クロック立ち上がり時間<br>ビット・クロック立ち下がり時間                                    | 立上がり時間は-100mVから100mVまでを測定<br>立ち下がり時間は100mVから-100mVまでを測定<br>10MHz < f <sub>CLKIN</sub> < 65MHz  | 0.1  | 0.2  | 0.35        | ns |

|                                                | ビット・クロックのデューティ・サイクル                                                   | 立上がりエッジのゼロ・クロスから立ち下がりエッジのゼロ・クロスまで<br>10MHz < f <sub>CLKIN</sub> < 65MHz                        | 44%  | 50%  | 56%         |    |

| f <sub>CLKIN</sub> 、入力クロック周波数<br>[2×チャネル・サンプリング周波数] | 周期<br>(T) | セットアップ・タイム(tsu)、ns                    | ホールド・タイム(th)、ns                       | tpdi = 0.5 × T + t <sub>delay</sub> 、ns                         |      |       |

|-----------------------------------------------------|-----------|---------------------------------------|---------------------------------------|-----------------------------------------------------------------|------|-------|

| MHz                                                 | ns        | ゼロ・クロス・データから<br>ゼロ・クロス・クロック<br>(両エッジ) | ゼロ・クロス・クロックから<br>ゼロ・クロス・データ<br>(両エッジ) | 入力クロックのゼロ・クロス<br>(立ち上がりエッジ)からフレーム・<br>クロックのゼロ・クロス<br>(立ち上がりエッジ) |      |       |

|                                                     |           | MIN                                   | TYP                                   | MAX                                                             |      |       |

| 65                                                  | 15        | 0.35                                  | 0.65                                  | 0.3                                                             | 0.6  | 12.35 |

| 50                                                  | 20        | 0.5                                   | 0.8                                   | 0.5                                                             | 0.8  | 14.6  |

| 40                                                  | 25        | 0.75                                  | 1.05                                  | 0.75                                                            | 1.05 | 17.04 |

| 30                                                  | 33        | 1                                     | 1.4                                   | 1                                                               | 1.4  | 21.19 |

| 20                                                  | 50        | 1.7                                   | 2.1                                   | 1.7                                                             | 2.1  | 29.52 |

| 10                                                  | 100       | 3.8                                   | 4.2                                   | 3.8                                                             | 4.2  | 54.71 |

表 1. 出力インターフェイス・タイミング<sup>(1)</sup>

(1) 次ページのタイミング図を参照してください。

## 代表的特性

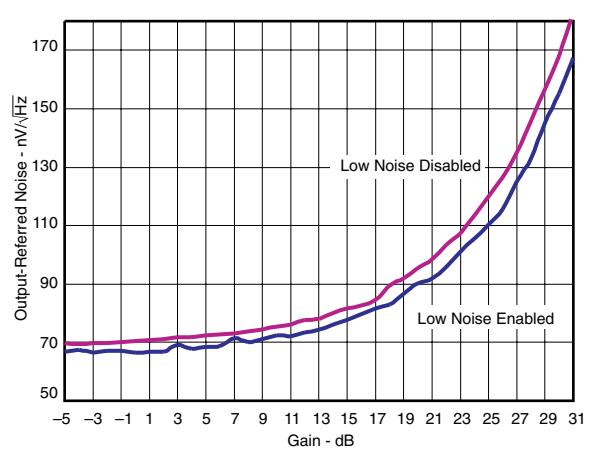

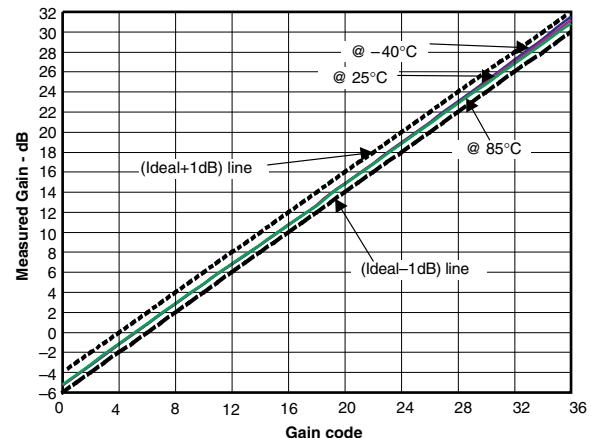

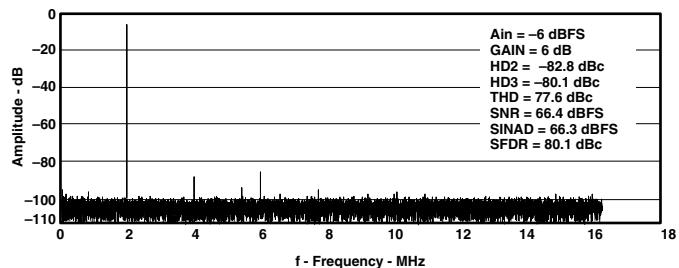

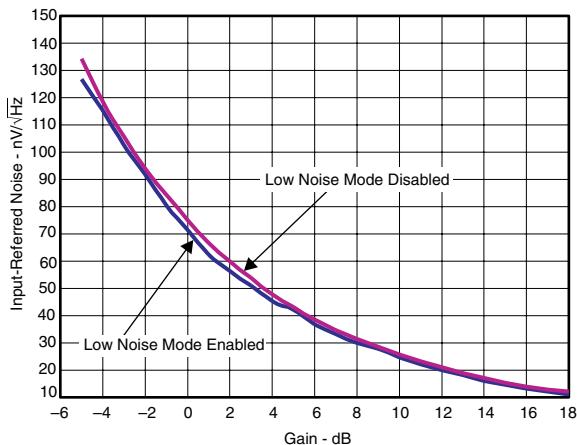

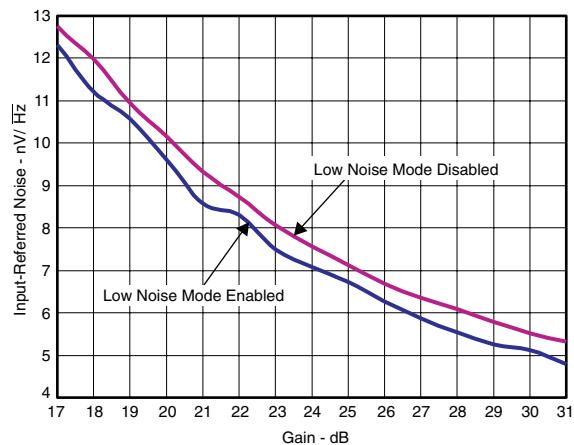

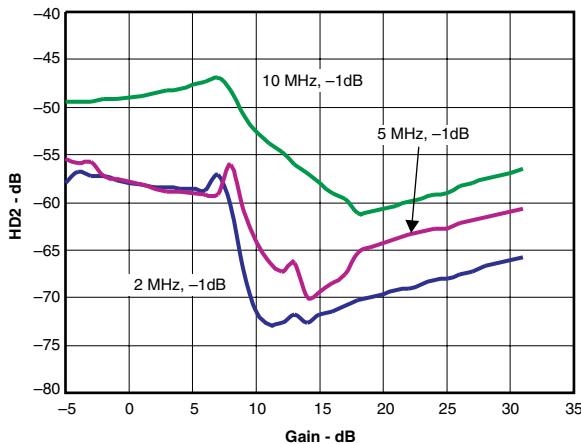

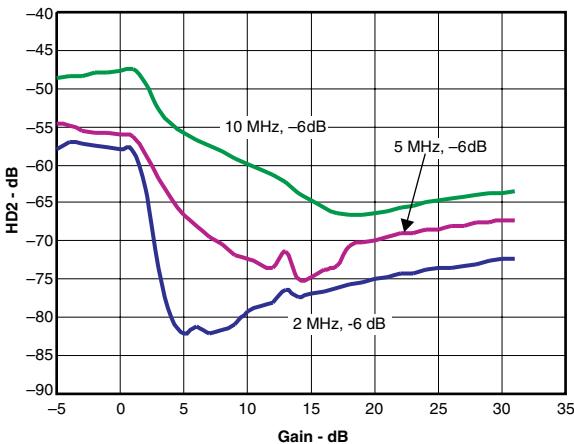

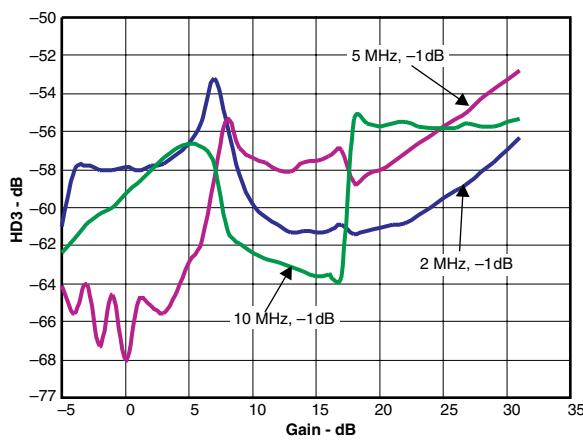

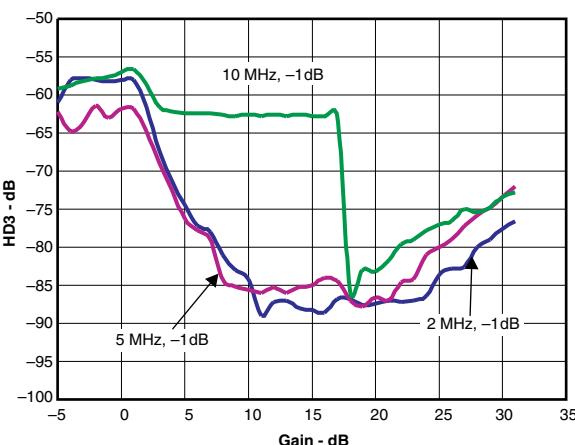

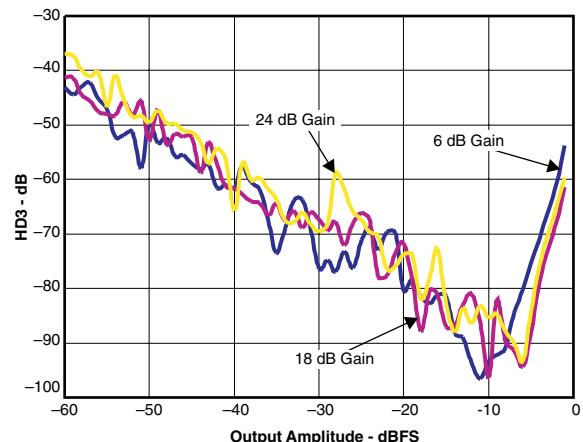

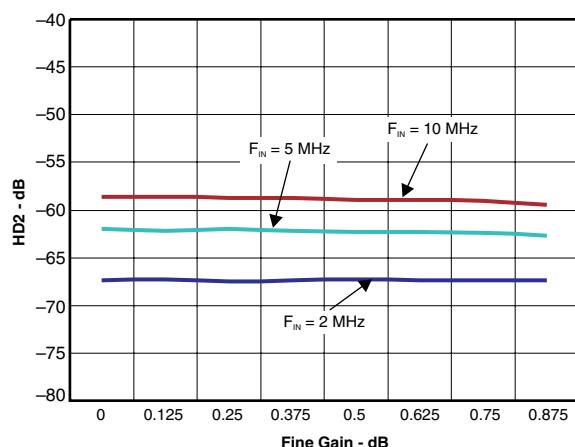

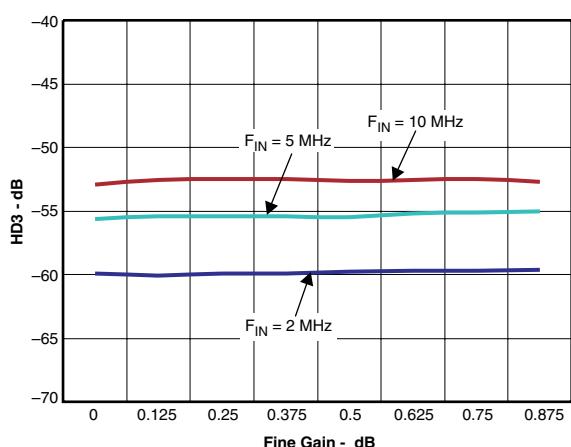

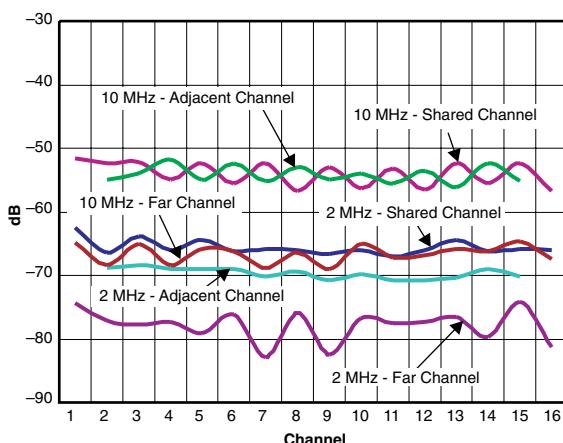

すべてのグラフを25°Cで測定、AVDD3 = 3.3V、AVDD18 = DVDD18 = 1.8V、-1dBFSアナログ入力を0.1μFでAC結合、内部リファレンス・モード、最大定格チャネル・サンプリング周波数(32.5 MSPS)、LVC MOS(シングルエンド)クロック、50%デューティ・サイクル、 $f_{IN}$  = 2MHz、アンチエイリアシング・フィルタを14MHz(3dBコーナー)に設定、出力クランプはディスエーブル、アナログ・ハイパス・フィルタはイネーブルです。

## 代表的特性

すべてのグラフを25°Cで測定、AVDD3 = 3.3V、AVDD18 = DVDD18 = 1.8V、-1dBFSアナログ入力を0.1μFでAC結合、内部リファレンス・モード、最大定格チャネル・サンプリング周波数(32.5 MSPS)、LVC MOS(シングルエンド)クロック、50%デューティ・サイクル、 $f_{IN} = 2\text{MHz}$ 、アンチエイリアシング・フィルタを14MHz(3dBコーナー)に設定、出力クランプはディスエーブル、アナログ・ハイパス・フィルタはイネーブルです。

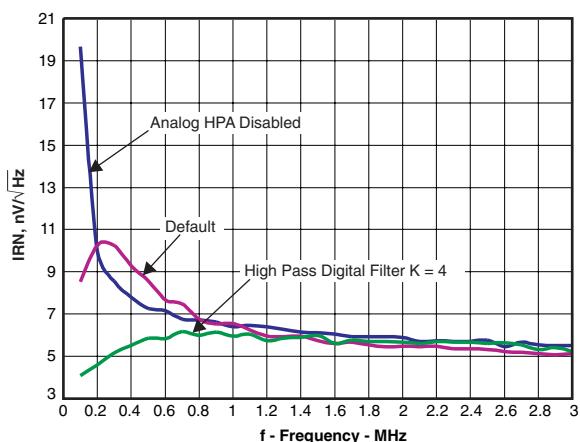

図 7. 低ゲイン時の入力換算ノイズ

図 8. 高ゲイン時の入力換算ノイズ

図 9. 粗調ゲインおよび3種類のFinに対するHD2(-1dBFS)<sup>(1)</sup>

図 10. 粗調ゲインおよび3種類のFinに対するHD2(-6dBFS)<sup>(2)</sup>

図 11. 粗調ゲインおよび3種類のFinに対するHD3(-1dBFS)<sup>(1)</sup>

図 12. 粗調ゲインおよび3種類のFinに対するHD3(-6dBFS)<sup>(2)</sup>

(1) ゲインが5dB以上の場合には、-1dBFSとなるよう入力振幅を調節します。ゲインが5dBの場合、入力振幅は4dBmです(-1dBFSに対応)。

ゲインが5dB未満の場合、入力は4dBmに保持しています。

(2) ゲインが0dB以上の場合には、-6dBFSとなるよう入力振幅を調節します。ゲインが0dBの場合、入力振幅は4dBmです(-6dBFSに対応)。

ゲインが0dB未満の場合、入力は4dBmに保持しています。

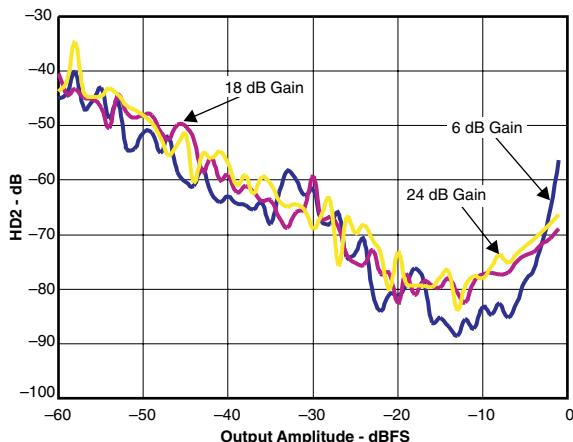

## 代表的特性

すべてのグラフを25°Cで測定、AVDD3 = 3.3V、AVDD18 = DVDD18 = 1.8V、-1dBFSアナログ入力を0.1μFでAC結合、内部リファレンス・モード、最大定格チャネル・サンプリング周波数(32.5 MSPS)、LVC MOS(シングルエンド)クロック、50%デューティ・サイクル、 $f_{IN} = 2\text{MHz}$ 、アンチエイリアシング・フィルタを14MHz(3dBコーナー)に設定、出力クランプはディスエーブル、アナログ・ハイパス・フィルタはイネーブルです。

図 13. HD2 vs 出力振幅

図 14. HD3 vs 出力振幅

図 15. 微調ゲインに対するHD2(ゲイン24dB時)

図 16. 微調ゲインに対するHD3(ゲイン24dB時)

図 17. クロストーク<sup>(3)</sup>

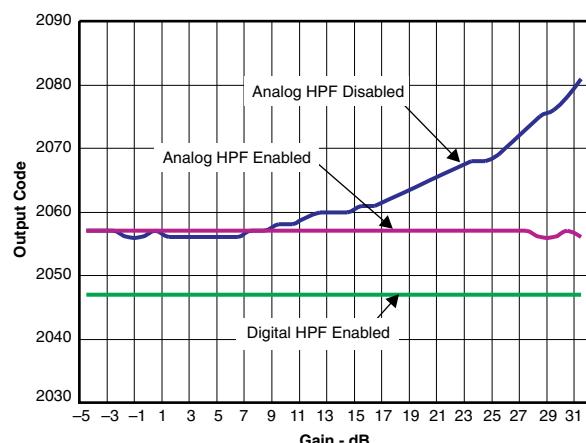

図 18. 出力オフセット vs TGCゲイン

- (3) 一度に1チャネルのみに対して-1dB信号を印加し、次の出力を観察：

1. 共有チャネル - ADCを共有するペアの2番目のチャネル

2. 隣接チャネル - アグレッサ・チャネルの隣りのチャネル(共有チャネルではない)

3. 遠隔チャネル - 他のすべてのチャネル(共有でも隣接でもないチャネル)

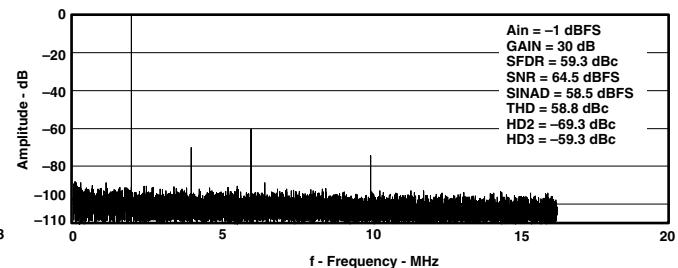

## 代表的特性

すべてのグラフを25°Cで測定、AVDD3 = 3.3V、AVDD18 = DVDD18 = 1.8V、-1dBFSアナログ入力を0.1μFでAC結合、内部リファレンス・モード、最大定格チャネル・サンプリング周波数(32.5 MSPS)、LVC MOS(シングルエンド)クロック、50%デューティ・サイクル、 $f_{IN} = 2\text{MHz}$ 、アンチエイリアシング・フィルタを14MHz(3dBコーナー)に設定、出力クランプはディスエーブル、アナログ・ハイパス・フィルタはイネーブルです。

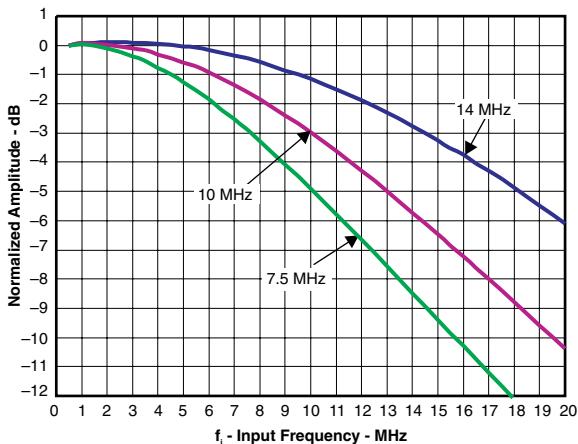

図19. アンチエイリアシング・フィルタの周波数応答

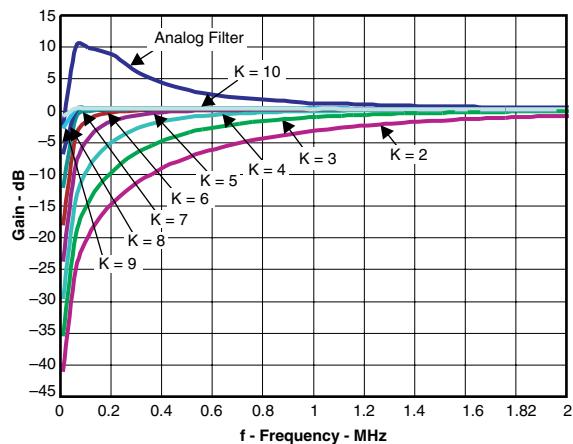

図20. ハイパス・フィルタ・オプション

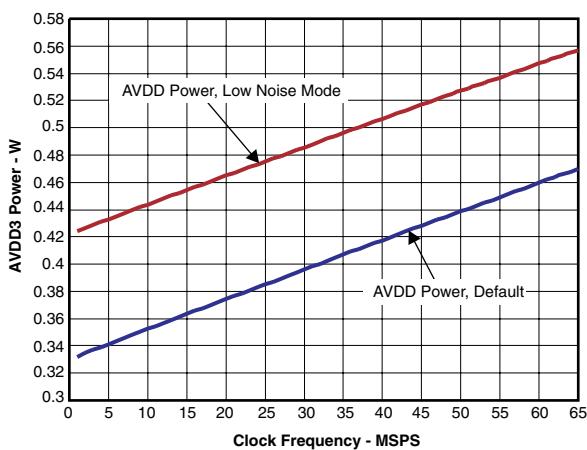

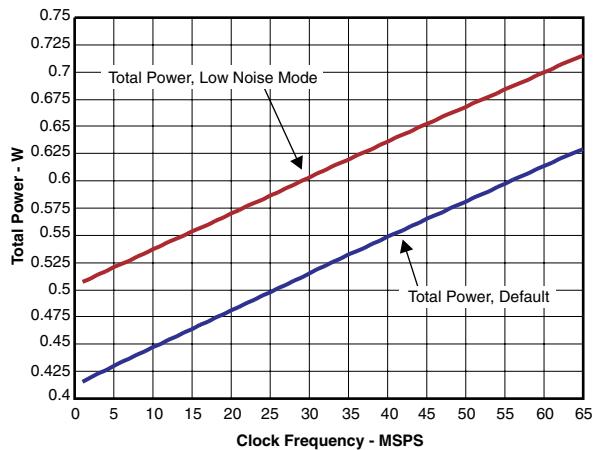

図21. アナログ電力 vs 入力クロック周波数

図22. 合計電力 vs 入力クロック周波数

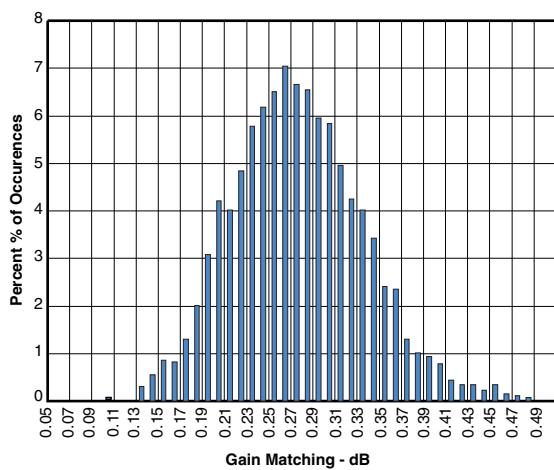

図23. 3つの温度で測定されたゲイン・マッ칭ング。単一ゲイン(30dB)設定により、各デバイスのチャネル間でゲインのピーク・ツー・ピーク変動として測定。各温度での各デバイスを1つのイベントとしてカウント。

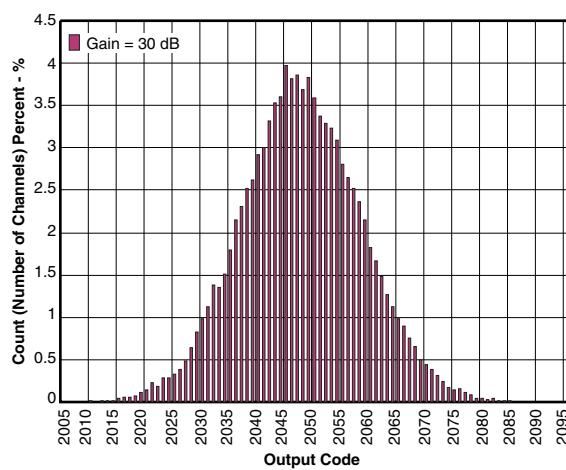

図24. 信号印加時のオフセット(平均コード)。

各チャネルを1つのイベントとしてカウント。

## 代表的特性

すべてのグラフを25°Cで測定、AVDD3 = 3.3V、AVDD18 = DVDD18 = 1.8V、-1dBFSアナログ入力を0.1μFでAC結合、内部リファレンス・モード、最大定格チャネル・サンプリング周波数(32.5 MSPS)、LVC MOS(シングルエンド)クロック、50%デューティ・サイクル、 $f_{IN} = 2\text{MHz}$ 、アンチエイリアシング・フィルタを14MHz(3dBコーナー)に設定、出力クランプはディスエーブル、アナログ・ハイパス・フィルタはイネーブルです。

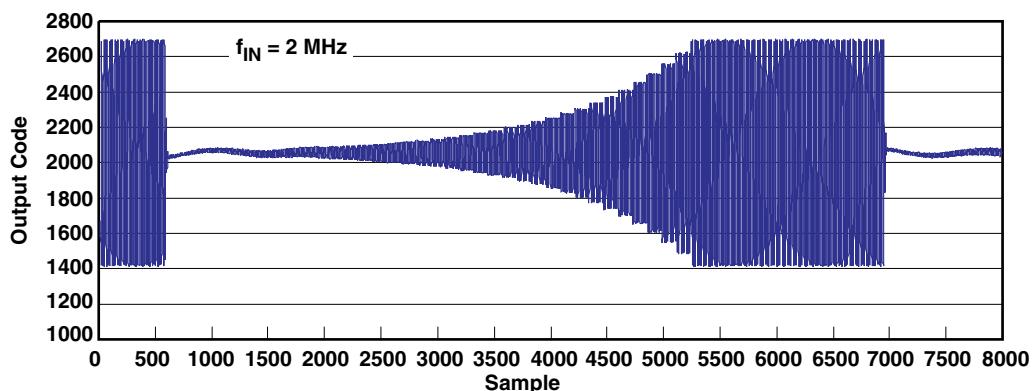

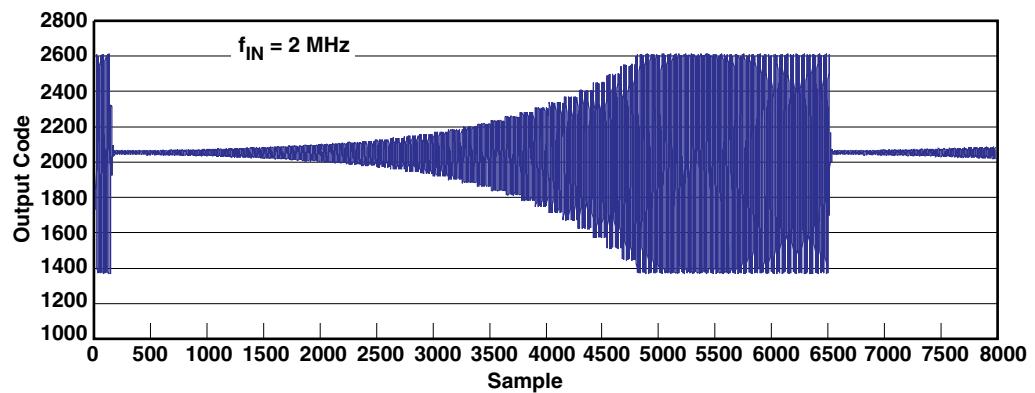

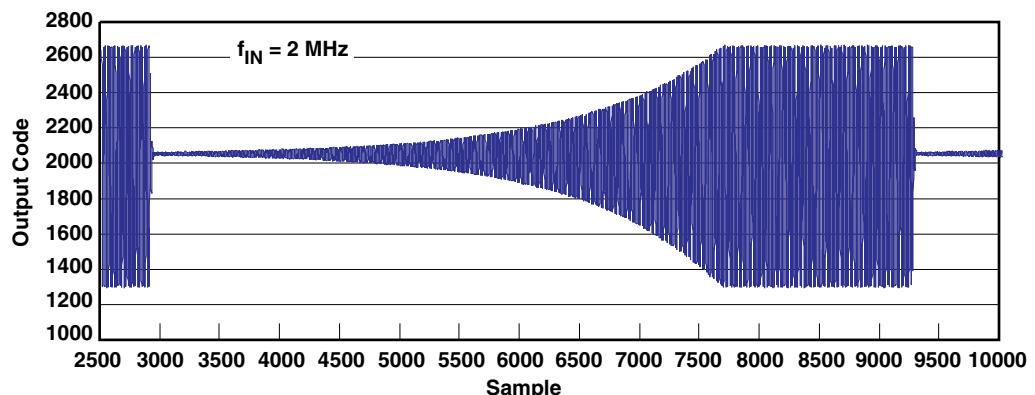

図 25. TGC掃引。補間をディスエーブル、ハイパス・フィルタをイネーブル。

図 26. TGC掃引。補間をディスエーブル、ハイパス・フィルタをディスエーブル。

図 27. TGC掃引。補間をイネーブル、ハイパス・フィルタをディスエーブル。

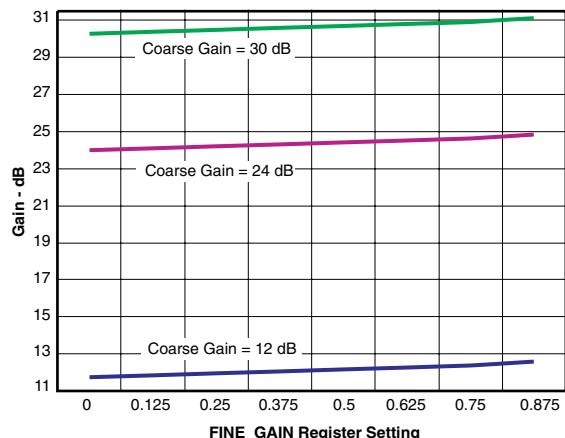

### 代表的特性

すべてのグラフを25°Cで測定、AVDD3 = 3.3V、AVDD18 = DVDD18 = 1.8V、-1dBFSアナログ入力を0.1μFでAC結合、内部リファレンス・モード、最大定格チャネル・サンプリング周波数(32.5 MSPS)、LVCMOS(シングルエンド)クロック、50%デューティ・サイクル、f<sub>IN</sub> = 2MHz、アンチエイリアシング・フィルタを14MHz(3dBコーナー)に設定、出力クランプはディスエーブル、アナログ・ハイパス・フィルタはイネーブルです。

図 28. 相互変調歪

図 29. IRN vs 周波数(ゲイン = 31dB)

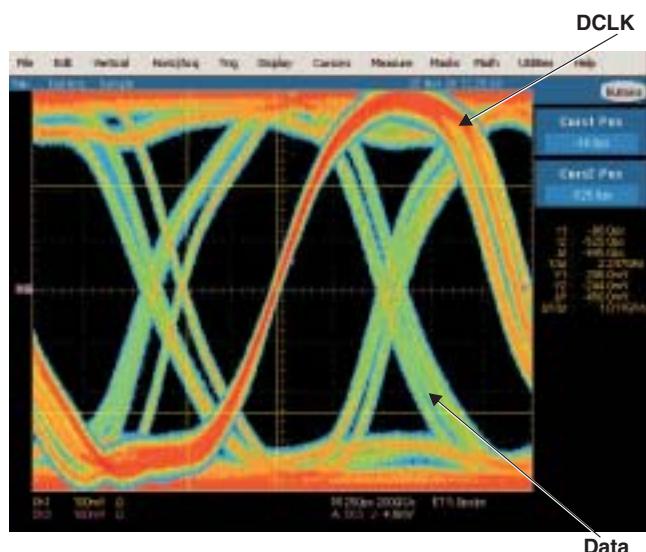

図 30. LVDS アイ・パター

# アプリケーション情報

## 動作原理

AFE5851は、16チャネルの可変ゲイン・アンプ(VGA)を内蔵した低電力CMOSモノリシック・アナログ・フロントエンドであり、スイッチド・キャパシタ・アーキテクチャに基づく8チャネルの12ビット高速パイプラインA/Dコンバータ(ADC)を備えています。

16個のVGAシングルエンド入力はそれぞれバッファリングされ、約1.6VのDCレベル(VCM)を中心に最大1V<sub>PP</sub>の入力振幅を受け付けます。

各VGAのゲイン範囲は-5dB~31dBであり、0.125dBの分解能でデジタル制御されます。時間に対するゲイン曲線(全VGAに共通)は、シリアル・インターフェイス経由でデバイスに内蔵されたメモリに格納できます。

ハードウェア同期入力ピンが用意されています(SYNC)。このピンにパルスが印加されると、デバイス内のすべてのVGAが同じクロック・サイクルで、選択された時間ゲイン曲線に従ってゲインのステップ変化を開始します。この同期は、シリアル・インターフェイスを使ってソフトウェアで開始することもできます。

また、選択可能なアンチエイリアシング・ローパス・フィルタ(AAF)(7.5MHz、10MHz、または14MHzで6dBの減衰)が、クランプ(ディスエーブル可能)とともに内蔵されています。

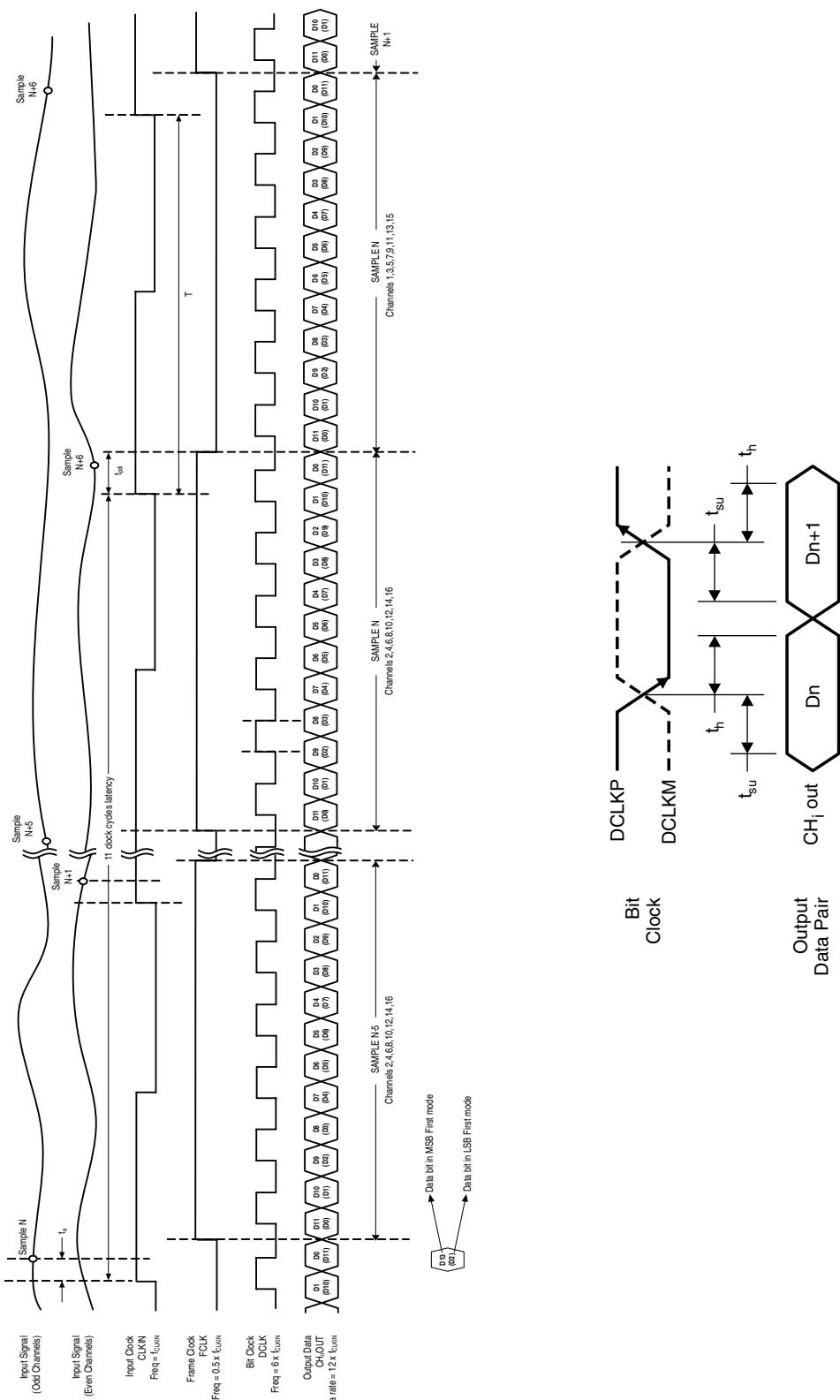

VGA/AAFは、指定された直線性を低下させることなく振幅2V<sub>PP</sub>の差動信号を出力し、12ビットの内蔵ADCを駆動できます。消費電力を最適化するため、各ADCは2つのVGAで共有されます。各VGA出力はクロック・サイクル毎に交互に立ち上がりエッジでサンプリングされ、実効的なサンプリング周波数は入力クロック・レートの1/2となります。例えば、各アナログ・チャネルを30MSPSでサンプリングするには、入力クロック周波数を60MHzにする必要があります。その結果、2つのアナログ・チャネルのサンプリング間に、実質的に1/2(サンプリング)クロックの遅延が生じます。

入力信号がサンプル/ホールド回路でキャプチャされた後、サンプルは一連の低分解能段で連続的に変換されます。それらの出力をデジタル補正ロジック部で結合することにより、最終的な12ビット・ワードが11クロック・サイクルのレイテンシで形成されます(オプションのデジタル信号処理機能で生じる遅延を考慮しない場合)。各チャネルの12ビット・ワードがシリアル化され、ストレート・オフセット・バイナリ形式のLVDSレベルとして出力されます。データ・ストリームに加えて、ビット・クロックとフレーム・クロックも出力されます。フレーム・クロックは、12ビット・ワード境界に揃えられます。

デバイスが正しく動作する(「シリアル・インターフェイス」を参照)ためには、リセット・ピンに正のパルスを印加する必要があります。これにより、内部制御レジスタがゼロに設定されます。ただし、パワーアップ・シーケンスは必要ありません。

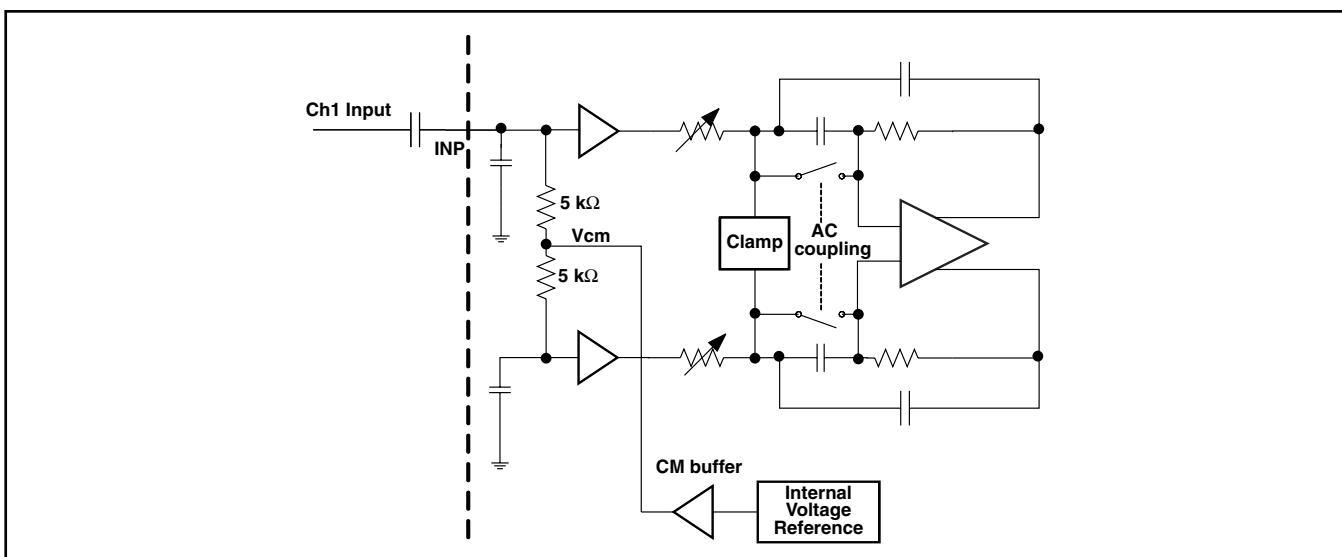

## 入力構成

AFE5851のアナログ入力(図31)は、1.6Vにバイアスされたアナログ・バッファ入力ゲートから構成されています(通常、同相電圧VCMと呼ばれます)。このバイアスは、5kΩの内部抵抗を使用して行われます。適切な動作のためには、入力信号が推奨入力範囲に収まっている必要があります。入力段に歪/飽和が発生しない最大入力振幅は、1V<sub>PP</sub>に制限されています。入力DCレベル(VCM)は約1.6Vであるため、VGAの入力は1.1V~2.1Vの範囲内に維持する必要があります。信号の低周波数における情報が不要である場合は、AC結合を使用できます。入力コンデンサが内部のバイアス抵抗(5kΩ)とともにハイパス・フィルタを形成するので、コンデンサの値は、必要な最低の周波数が最小の減衰で通過できるよう選択する必要があります。超音波で使用される標準的な周波数(>1MHz)の場合は、10nF以上の値を推奨します。DC結合が望ましい場合は、VCM出力ピンをタップして、入力信号のDCレベルを設定できます。VCM出力の駆動能力は限定されているため、高入力インピーダンスの回路に接続してください。選択した入力構成に関わらず、各VCM入力で100nFのコンデンサをAVSSに接続する必要があります。

図 31. 入力等価回路

# シリアル・インターフェイス

## レジスタの初期化

電源投入後、内部レジスタはデフォルト値(ゼロ)に初期化される必要があります。初期化は、次の2つのうちいずれかの方法で実行できます。

1. RESETピンに正パルスを印加することによるハードウェア・リセット

2. シリアル・インターフェイスでSOFTWARE RESETビットを“High”にするソフトウェア・リセット。このビットをセットすると、内部レジスタがそれぞれのデフォルト値(すべてゼロ)に初期化され、その後SOFTWARE RESETビットは“Low”に戻ります。この場合、RESETピンは“Low”(非アクティブ)のまま保持できます。

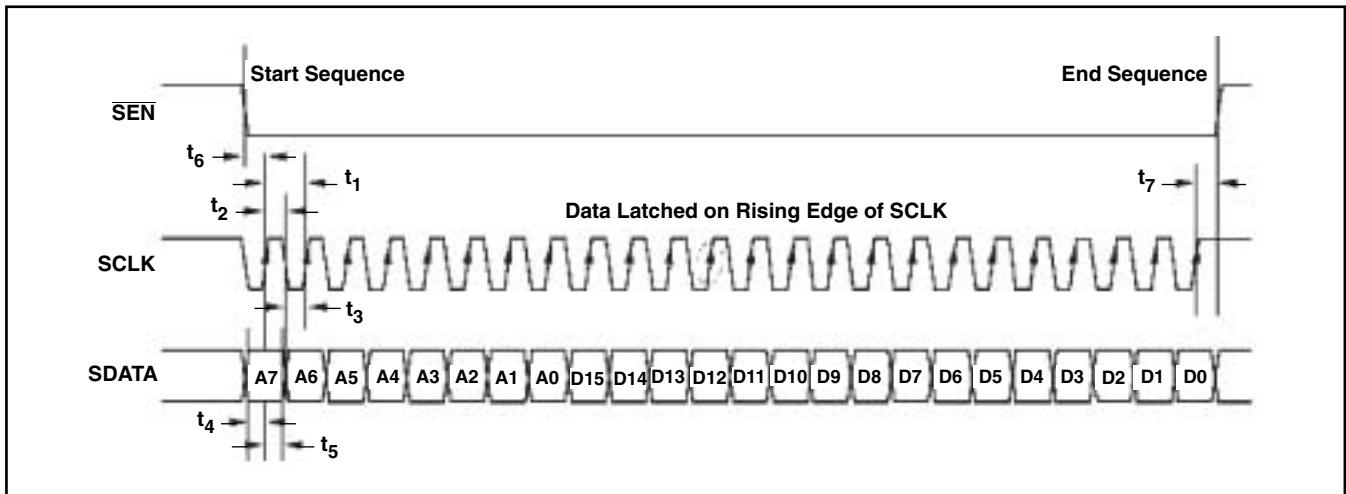

各モードのプログラミングは、 $\overline{\text{SEN}}$ (シリアル・インターフェイス・イネーブル)、SCLK(シリアル・インターフェイス・クロック)、SDATA(シリアル・インターフェイス・データ)、RESETの各ピンから構成されるシリアル・インターフェイスを使用して行えます。SCLKおよびSDATAにはGNDとの間に100kΩのプルダウン抵抗、 $\overline{\text{SEN}}$ にはDVDD18との間に100kΩのプルアップ抵抗があります。 $\overline{\text{SEN}}$ が“Low”的ときに、デバイスへのビットの

シリアル・シフトがイネーブルになります。シリアル・データSDATAは、 $\overline{\text{SEN}}$ がアクティブ(“Low”)のときのSCLKの各立ち上がりエッジでラッチされます。ラッチされたシリアル・データは、 $\overline{\text{SEN}}$ が“Low”的ときのSCLKの24個毎の立ち上がりエッジで、レジスタにロードされます。ワード長が24ビットの倍数より大きい場合、超過するビットは無視されます。1回のアクティブな $\overline{\text{SEN}}$ パルス内で、24ビット・ワードの整数倍のデータをロードできます( $\overline{\text{SEN}}$ の立ち下がりエッジ後に24クロックのグループをカウントする内部カウンタがあります)。このインターフェイスは、20MHz～低速(数Hz)までにわたるSCLK周波数で動作し、デューティ・サイクルが50%以外のSCLKでも動作できます。

データは2つの主要な部分に分けられます。レジスタ・アドレス(8ビット)と、アドレス指定されたレジスタにロードするデータ自体(16ビット)です。未使用ビットのあるレジスタに書き込むときには、それらのビットを0に設定する必要があります。次のタイミング図に、このプロセスを示します。

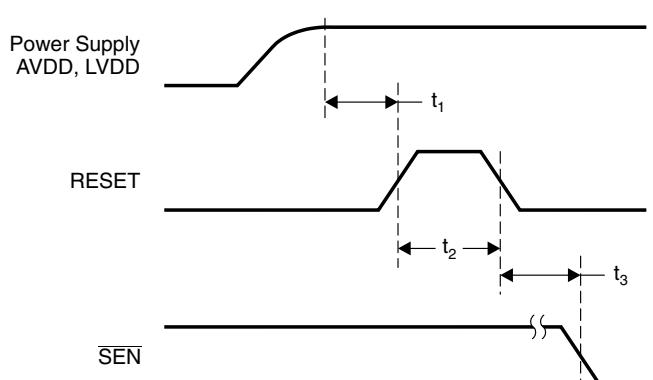

## リセット・タイミング

標準値は25°C、最小値および最大値は $T_{\text{MIN}} = -40^{\circ}\text{C} \sim T_{\text{MAX}} = 85^{\circ}\text{C}$ の全温度範囲、AVDD3 = 3.3V、AVDD18 = DVDD18 = 1.8Vです(特に記述のない限り)。

| パラメータ                         | 測定条件                                         | MIN | TYP | MAX | 単位 |

|-------------------------------|----------------------------------------------|-----|-----|-----|----|

| $t_1$<br>パワーオン遅延時間            | AVDDおよびLVDDのパワーアップからRESETパルスがアクティブになるまでの遅延時間 | 5   |     |     | ms |

| $t_2$<br>リセット・パルス幅            | アクティブなRESET信号のパルス幅                           | 10  |     |     | ns |

| $t_3$<br>レジスタ書き込み遅延時間         | RESETのディスエーブルからSENがアクティブになるまでの遅延時間           | 25  |     |     | ns |

| $t_{\text{PO}}$<br>パワーアップ遅延時間 | AVDDおよびLVDDのパワーアップから出力が安定するまでの遅延時間           |     | 6.5 |     | ms |

図 32. リセット・タイミング図

図 33. シリアル・インターフェイス・レジスタの書き込み

最小値は  $T_{MIN} = -40^{\circ}\text{C}$ ～ $T_{MAX} = 85^{\circ}\text{C}$  の全温度範囲、AVDD3 = 3.3V、AVDD18 = DVDD18 = 1.8V です。

| パラメータ | 説明                             | MIN | TYP | MAX | 単位 |

|-------|--------------------------------|-----|-----|-----|----|

| $t_1$ | SCLK周期                         | 50  |     |     | ns |

| $t_2$ | SCLK “High” 時間                 | 20  |     |     | ns |

| $t_3$ | SCLK “Low” 時間                  | 20  |     |     | ns |

| $t_4$ | データ・セットアップタイム                  | 5   |     |     | ns |

| $t_5$ | データ・ホールドタイム                    | 5   |     |     | ns |

| $t_6$ | SEN立ち下がりからSCLK立ち上がりまで          | 8   |     |     | ns |

| $t_7$ | 最後のSCLK立ち上がりエッジからSEN立ち上がりエッジまで | 8   |     |     | ns |

### 汎用レジスタ・マップ

内部レジスタは、2つのグループに分けることができます。デバイスのすべての汎用機能および設定を制御するレジスタのグループと、TGC/ゲイン曲線動作を制御するレジスタ・バンクです。この2つのレジスタ・セットは、レジスタ・バンクの制御を保持するアドレス0を除き、すべてのアドレス空間で重なり合っています。アドレス0のレジスタ・ビットの1つである

TGC\_REG\_WREN(下の表を参照)を使用して、アクセス対象のレジスタ・セットを選択します。このビットのデフォルト値はゼロであり、汎用レジスタがアクセスされます。TGC制御レジスタ(汎用レジスタの後で説明)は、TGC\_REG\_WRENに1を書き込むことでアクセスできます。

次の表に、汎用レジスタの機能(TGC\_REGISTER\_WRENがデフォルトのゼロの場合)を説明します。各アドレスは、“アドレス[レジスタのビット]”という形式で示されます。

| アドレス     | 機能                              | 説明                                                                                                    |

|----------|---------------------------------|-------------------------------------------------------------------------------------------------------|

| 0[2]     | TGC_REGISTER_WREN               | 0: 汎用レジスタへのアクセス。1: TGCレジスタへのアクセス                                                                      |

| 0[1]     | REGISTER_READOUT_ENABLE         | 1: レジスタの読み出しをイネーブル                                                                                    |

| 0[0]     | SOFTWARE_RESET                  | 1: デバイスをリセットし、ビットは自動的にゼロに戻る                                                                           |

| 1[13]    | EXTERNAL_REFERENCE              | 0: 内部リファレンス 1: 外部リファレンス                                                                               |

| 1[11]    | LOW_FREQUENCY_NOISE_SUPPRESSION | 0: 抑制なし。1: 低周波数でノイズを抑制し、 $f_{channel}/2$ にシフト                                                         |

| 1[10]    | STDBY                           | 0: パワー・アップ。1: スタンバイ(高速パワー・アップ・モード)                                                                    |

| 1[9:2]   | PDN CHANNEL<7:0>                | 各チャネル(VCA+ADC)個別のパワーダウン。LVDSは論理0を出力。                                                                  |

| 1[1]     | OUTPUT_DISABLE                  | 0: 出力をイネーブル。1: 出力をディスエーブル                                                                             |

| 1[0]     | GLOBAL_PDN                      | 0: パワー・アップ。1: グローバル・パワーダウン(低速パワー・アップ・モード)                                                             |

| 2[15:13] | PATTERN_MODE                    | シリアルLVDSのパターン・モード。000: パターンなし。001: 同期。010: デスキュー。011: カスタム・レジスタ。100: オール1。101: トグル。110: オール0。111: ランプ |

| 2[11]    | AVERAGING_ENABLE                | 0: デフォルト(平均化なし)。1: 2つのチャネルを平均化してSNRを向上。                                                               |

| 2[10:3]  | PDN_LVDS                        | 8つのデータ出力LVDSペアをパワーダウン。                                                                                |

| 3[14:13] | SERIALIZED_DATA_RATE            | シリアル化係数。00: 12x、01: 10x、10: 16x、11: 14x                                                               |

| アドレス      | 機能                                                    | 説明                                                                                      |

|-----------|-------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 3[12]     | DIGITAL_GAIN_ENABLE                                   | 0：デフォルト(ゲインなし)。1：以下のレジスタで設定されたデジタル・ゲインを適用。                                              |

| 3[8]      | REGISTER_OFFSET_SUBTRACTION_ENABLE                    | 0：デフォルト(減算なし)。1：対応するレジスタで設定されたオフセット値を減算。                                                |

| 3[7:0]    | INVERT_CHANNEL                                        | 0：デフォルト。1：チャネル出力を反転                                                                     |

| 4[4]      | MSB_FIRST                                             | 0：LSBファースト。1：MSBファースト                                                                   |

| 4[3]      | DFS                                                   | データ形式選択。0：2の補数。1：オフセット・バイナリ                                                             |

| 5[13:0]   | CUSTOM_PATTERN                                        | LVDSのカスタム・パターン・データ (PATTERN_MODE = 011)                                                 |

| 7[10]     | VCA_LOW_NOISE_MODE_(INCREASE_POWER)                   | 0：低電力。1：低ノイズ、ただし電力は増加(チャネル毎に5mW)                                                        |

| 7[8:7]    | SELF_TEST                                             | 00、10：セルフテストなし。01：セルフテストをイネーブル。チャネルの入力に100mVのDCを印加。11：セルフテストをイネーブル。チャネルの入力に150mVのDCを印加。 |

| 7[3:2]    | FILTER_BW                                             | 00：14MHz。01：10MHz。10：7.5MHz。11：未使用。                                                     |

| 7[1]      | INTERNAL_AC_COUPLING                                  | VGAの結合：0：AC結合。1：DC結合                                                                    |

| 13[15:11] | DIG_GAIN1                                             | 0dB～6dB (0.2dBステップ)                                                                     |

| 13[9:2]   | OFFSET_CH1                                            | チャネル1から減算する値                                                                            |

| 14[15:11] | DIG_GAIN2                                             | 0dB～6dB (0.2dBステップ)                                                                     |

| 14[9:2]   | OFFSET_CH2                                            | チャネル2から減算する値                                                                            |

| 15[15:11] | DIG_GAIN3                                             | 0dB～6dB (0.2dBステップ)                                                                     |

| 15[9:2]   | OFFSET_CH3                                            | チャネル3から減算する値                                                                            |

| 16[15:11] | DIG_GAIN4                                             | 0dB～6dB (0.2dBステップ)                                                                     |

| 16[9:2]   | OFFSET_CH4                                            | チャネル4から減算する値                                                                            |

| 17[15:11] | DIG_GAIN5                                             | 0dB～6dB (0.2dBステップ)                                                                     |

| 17[9:2]   | OFFSET_CH5                                            | チャネル5から減算する値                                                                            |

| 18[15:11] | DIG_GAIN6                                             | 0dB～6dB (0.2dBステップ)                                                                     |

| 18[9:2]   | OFFSET_CH6                                            | チャネル6から減算する値                                                                            |

| 19[15:11] | DIG_GAIN7                                             | 0dB～6dB (0.2dBステップ)                                                                     |

| 19[9:2]   | OFFSET_CH7                                            | チャネル7から減算する値                                                                            |

| 20[15:11] | DIG_GAIN8                                             | 0dB～6dB (0.2dBステップ)                                                                     |

| 20[9:2]   | OFFSET_CH8                                            | チャネル8から減算する値                                                                            |

| 21[4:1]   | DIGITAL_HIGH_PASS_FILTER_CORNER_FREQ_FOR_CHANNELS_1~4 | 「汎用レジスタの説明」で示されるハイパス・フィルタのkを設定(k = 2～10)。                                               |

| 21[0]     | DIGITAL_HIGH_PASS_FILTER_ENABLE_FOR_CHANNELS_1~4      | 0：ハイパス・フィルタなし。<br>1：ハイパス・フィルタをイネーブル                                                     |

| 25[15:11] | DIG_GAIN16                                            | 0dB～6dB (0.2dBステップ)                                                                     |

| 25[9:2]   | OFFSET_CH15                                           | チャネル16から減算する値                                                                           |

| 26[15:11] | DIG_GAIN15                                            | 0dB～6dB (0.2dBステップ)                                                                     |

| 26[9:2]   | OFFSET_CH16                                           | チャネル15から減算する値                                                                           |

| 27[15:11] | DIG_GAIN14                                            | 0dB～6dB (0.2dBステップ)                                                                     |

| 27[9:2]   | OFFSET_CH13                                           | チャネル14から減算する値                                                                           |

| 28[15:11] | DIG_GAIN13                                            | 0dB～6dB (0.2dBステップ)                                                                     |

| 28[9:2]   | OFFSET_CH14                                           | チャネル13から減算する値                                                                           |

| 29[15:11] | DIG_GAIN12                                            | 0dB～6dB (0.2dBステップ)                                                                     |

| 29[9:2]   | OFFSET_CH11                                           | チャネル12から減算する値                                                                           |

| 30[15:11] | DIG_GAIN11                                            | 0dB～6dB (0.2dBステップ)                                                                     |

| 30[9:2]   | OFFSET_CH12                                           | チャネル11から減算する値                                                                           |

| 31[15:11] | DIG_GAIN10                                            | 0dB～6dB (0.2dBステップ)                                                                     |

| 31[9:2]   | OFFSET_CH9                                            | チャネル10から減算する値                                                                           |

| 32[15:11] | DIG_GAIN9                                             | 0dB～6dB (0.2dBステップ)                                                                     |

| 32[9:2]   | OFFSET_CH10                                           | チャネル9から減算する値                                                                            |

| 33[4:1]   | DIGITAL_HIGH_PASS_FILTER_CORNER_FREQ_FOR_CHANNELS_5~8 | 「汎用レジスタの説明」で示されるハイパス・フィルタのkを設定(k = 2～10)。                                               |

| 33[0]     | DIGITAL_HIGH_PASS_FILTER_ENABLE_FOR_CHANNELS_5~8      | 0：ハイパス・フィルタなし。<br>1：ハイパス・フィルタをイネーブル                                                     |

| 70[14]    | CLAMP_DISABLE                                         | 0：イネーブル。1：ディスエーブル                                                                       |

## 汎用レジスタの説明

### AVERAGING\_ENABLE

アドレス : 2[11]

1に設定すると、同じペアの2つの異なるチャネルに対応する2つのサンプルが平均されます(チャネル1と3、2と4、5と7、6と8、9と11、10と12、13と15、および14と16)。両方のチャネルの入力が同じである場合は、実効的にSNRが向上します。平均化は次のように行われます。

1. チャネル1とチャネル3の平均がチャネル3のLVDSペアに出力された後、(同じペア上に)チャネル2と4の平均が出力されます。

2. チャネル5とチャネル7の平均がチャネル4のLVDSペアに出力された後、(同じペア上に)チャネル6と8の平均が出力されます。

3. チャネル9とチャネル11の平均がチャネル5のLVDSペアに出力された後、(同じペア上に)チャネル10と12の平均が出力されます。

4. チャネル13とチャネル15の平均がチャネル6のLVDSペアに出力された後、(同じペア上に)チャネル14と16の平均が出力されます。

### CUSTOM\_PATTERN

アドレス : 5[13:0]

このレジスタには、PATTERN\_MODEが‘011’に等しいときに出力されるコードが格納されます。詳細については、PATTERN\_MODEを参照してください。

### DFS

アドレス : 4[3]

DFSは、Data Format Select(データ形式選択)を表しています。デフォルトでは、ADC出力は2の補数モードになります。DFSビットを1にプログラミングすると、MSBが反転し、出力はストレート・オフセット・バイナリ・モードになります。

### DIGITAL\_GAIN\_ENABLE

アドレス : 3[12]

このビットを1に設定すると、各チャネル*i*について、対応するゲインがDIG\_GAIN<sub>i</sub><15:11>で与えられます。実際のゲインは、0dB + 0.2dB\*DIG\_GAIN<sub>i</sub><15:11>となります。例えば、DIG\_GAIN<sub>5</sub><15:11> = 3の場合は、チャネル5のゲインが0.6dB増加します。DIG\_GAIN<sub>i</sub><15:11> = 31の場合は、DIG\_GAIN<sub>i</sub><15:11> = 30と同じ結果となり、チャネル*i*のゲインが6dBに設定されます。

### DIGITAL\_HIGH\_PASS\_FILTERおよび

### DIGITAL\_HIGH\_PASS\_FILTER\_CORNER\_FREQ

アドレス : 21[0]

アドレス : 33[0]

アドレス : 21[4:1]

アドレス : 33[4:1]

この4レジスタのグループは、出力データに適用されるデジタル・ハイパス伝達関数の特性を制御します。これは、 $y(n) = 2^k/(2^k + 1) [x(n) - x(n-1) + y(n-1)]$  という式に従います。Kは、DIGITAL\_HIGH\_PASS\_FILTER\_CORNER\_FREQレジスタ(最初の8チャネルに1つ、次の8チャネルに1つのレジスタ)の項目で説明されるとおりに設定されます。

### EXTERNAL\_REFERENCE

アドレス : 1[13]

内部リファレンス・モード(デフォルト)では、AVDDで使用される電力が約3mW増加します(すべての仕様表に既に含まれています)。EXTERNAL\_REFERENCEを1にプログラミングすることにより、AFE5851は外部リファレンス・モードで動作できます。このモードでは、VREF\_INピンを1.4Vで駆動します。このピンは入力インピーダンスが高いため、特に高い駆動能力は要求されません。外部リファレンス・モードを使用する利点として、複数のAFE5851を同じ外部リファレンスで動作させることにより、デバイス間のゲイン・マッチングなどのパラメータを向上できます。

### FILTER\_BW

アドレス : 7[3:2]

このビットは、アンチエイリアシング・フィルタ(AAF)の3dB減衰周波数を設定します。

### GLOBAL\_PDN

アドレス : 1[0]

グローバルPDNビットは、外部PDNピン(59)の信号とORが取られます。それにより、このビットに1をすると、デバイスが完全にシャットダウンされます。

### INTERNAL\_AC\_COUPLING

アドレス : 7[1]

このビットは、入力バッファとVCAの間に設定された内部ハイパス・フィルタ(図31)を制御します。このフィルタは、入力オフセットがTGCで増幅されるのを防ぐために、オフセットを除去します。別の方法として、DIGITAL\_HIGH\_PASS\_FILTERレジスタ(上記参照)を使用し、ADCの後段のデバイス上、またはADC出力上で、デジタル・ドメインへのオフセットの影響を除外することもできます。

## INVERT\_CHANNEL

アドレス：3[7:0]

INVERT\_CHANNEL<7:0>の対応するビットを設定すると、チャネルの信号/出力データの値が(デジタル的に)反転されます。INVERT\_CHANNEL<0>はチャネル1および2を同時に制御し、INVERT\_CHANNEL<1>はチャネル3および4を同時に制御します(以下、同様)。

## LOW\_FREQUENCY\_NOISE\_SUPPRESSION

アドレス：0[11]

低周波ノイズ抑制モードは、0MHz～1MHz(DC付近)の周波数帯で良好なノイズ特性が求められるようなアプリケーションで特に有用です。このモードを設定すると、AFE5851のADCの低周波ノイズが約 $f_{channel}/2$ までシフトされ、DC付近のノイズフロアがずっと低い値へと低減されます。

## MSB\_FIRST

アドレス：4[4]

デフォルトでは、フレームの最初のビット(DCLKPの立ち上がりエッジ後)はADC出力のLSBです。MSB\_FIRSTモードを設定すると、ワード内のビット順が反転し、DCLKP立ち上がりエッジ後の最初のビットとしてMSBが出力されます。

## OUTPUT\_DISABLE

アドレス：1[1]

このビットを1に設定すると、出力がハイ・インピーダンス状態になります。

## PATTERN\_MODE

アドレス：2[15:13]

AFE5851は、LVDS出力上で各種のテスト・パターンを出力できます。これらのテスト・パターンは、通常のADCデータ出力に代わって出力され、ADCの出力を読み取るデバイスのデバッグや同期に役立ちます。

1. PATTERN\_MODE = '000' がデフォルトであり、テスト・モードはディスエーブルです。つまり、出力データはADCデータと同じです。

2. PATTERN\_MODE = '001' (SYNCモード) では、通常のADCワードが '111111000000' の固定ワードで置き換えられます。

3. PATTERN\_MODE = '010' ではDESKEWモードが設定され、12ビットADC出力D<11:0>が '101010101010' ワードで置き換えられて、データ・ラインに1と0の連続ストリームが生成されます。厳密なシーケンス(最初が0か1か)は、パワーアップの状態によって異なります。このモードでは、0と1が交互に出力されることだけが保証されます。

4. PATTERN\_MODE = '011' の場合は、CUSTOM\_PATTERN<13:0>のビットで設定される固定コードが出力されます。SERIALIZED\_DATA\_RATE(下記参照)の値に応じて、出力ビットは以下の規則に従います。

- a. デフォルト(SERIALIZED\_DATA\_RATE = '00')の場合は、出力の12ビットADCデータとして、サンプル・データの代わりにCUSTOM\_PATTERN<13:2>が使用されます。この出力は、通常のADCデータと同様に、LSBファーストおよびMSBファースト・モードによって制御されます。

- b. SERIALIZED\_DATA\_RATE = '01' の場合は、10ビット出力モードが選択され、ビットCUSTOM\_PATTERN<13:4>が使用されます。

- c. SERIALIZED\_DATA\_RATE = '10' の場合は、16ビット出力モードが選択されます。この場合、上位14ビットにCUSTOM\_PATTERN<13:0>が使用され、下位2ビットはゼロとなります。

- d. SERIALIZED\_DATA\_RATE = '11' の場合は、14ビット・モードが選択され、CUSTOM\_PATTERN<13:0>が出力ワードとして使用されます。

5. PATTERN\_MODE = '100' の場合、出力が常に '1' となります。PATTERN\_MODE = '110' に設定すると、出力が常に '0' となります。

6. PATTERN\_MODE = '101' の場合、デバイスの出力がオール0とオール1の間で切り替わります。n番目のサンプル・クロックでデータが '000000000000' とすると、n+1番目のサンプル・クロックではデータが '111111111111' となります。

7. PATTERN\_MODE = '111' の場合、すべてのチャネルで、繰り返しフルスケール・ランプ・パターンが出力されます。このパターンは、ゼロ・コードからフルスケール・コードまで、クロック・サイクル毎に1LSBステップで上昇します。フルスケール・コードに達すると、ゼロ・コードに戻って再び上昇を開始します。

## PDN\_Channel <7:0>

アドレス：1[9:2]

各ビットは、(同じADCを共有する)連続するチャネルのペアのパワーダウンを制御します。例えば、PDN\_Channel<0>はチャネル1および2をパワーダウンし、対応するLVDSペアがハイ・インピーダンスになります。DCLKおよびFCLKはパワーダウンされず、100Ωで終端されなければアクティブになります。

## PDN\_LVDS

アドレス：2[10:3]

PDN\_LVDS<7..0>は、どのLVDSペアが非アクティブ(0出力)になるかを選択します。フレームおよびビット・クロックのLVDSストリームは、OUTPUT\_DISABLEまたはGLOBAL\_PDNが設定されたときにのみパワーダウンされます。

## REGISTER\_OFFSET\_SUBTRACTION\_ENABLE

アドレス：3[8]

このビットを1に設定すると、対応するOFFSET\_CHANNEL<sub>i</sub><9:2>の値がADC出力から減算されます。数値は2の補数形式で指定されます。例えば、OFFSET\_CHANNEL<sub>i</sub><9:2> = ‘1000000’の場合は、“-128を減算”を意味します。OFFSET\_CHANNEL<sub>i</sub><9:2> = ‘01111111’の場合は、127が減算されます。したがって、加算と減算の両方を実行できます。

オフセットはデジタル・ゲイン（後述）より前に適用されることに注意してください。実際、デジタル・ゲインは最後のステップであり、内部ではデータ・パス全体が2の補数となっています。DFS = ‘1’（ストレート・バイナリ・オフセット形式）の場合のみ、2の補数のワードが最後にオフセット・バイナリに変換されます。

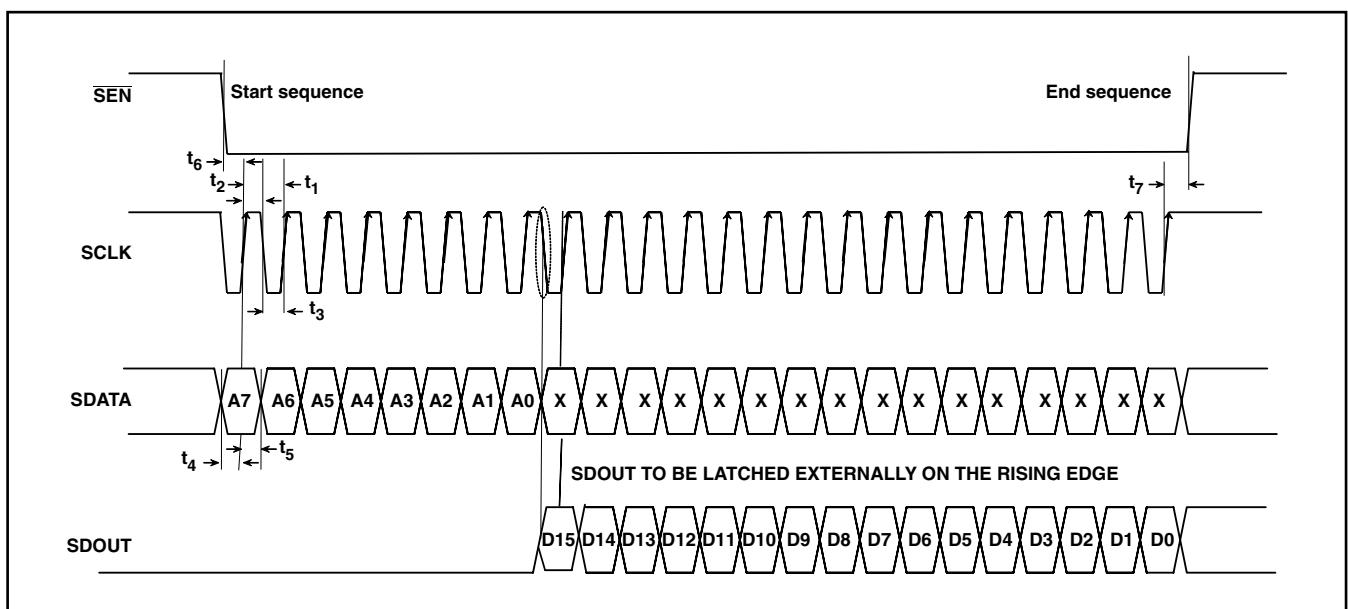

## REGISTER\_READOUT\_ENABLE

アドレス：0[1]

デバイスには、内部レジスタの内容を読み出すためのオプションが用意されています。これは、外部のコントローラとAFEとの間のシリアル・インターフェイス通信を検査する診断機能として利用できます。まず、<REGISTER READOUT ENABLE>ビットを1に設定する必要があります。次に、内容を読み出すレジスタのアドレス（A7-A0）を指定して、シリアル・インターフェイス・サイクルを開始します。データ・ビットは任意です。デバイスは、選択されたレジスタの内容（D15-D0）をSDOUTピンに出力します。外部コントローラは、SCLKの立ち上がりエッジで内容をラッチできます。シリアル・レジスタの書き込みをイネーブルにするには、<REGISTER READOUT ENABLE>ビットを再び0に設定します。次のタイミング図に、この動作を示します（タイミング仕様は、シリアル・インターフェイス・レジスタ書き込みの表に示したのと同じ情報に従っています）。

## SERIALIZED\_DATA\_RATE

アドレス：3[14:13]

この2つのビットは、データ・ワードの長さ（つまり、FCLK周期あたりのDCLK数）を制御します。例えば、12ビットADCで16ビットのデータ・ストリームを出力することも可能です。この場合、下位4ビットにはゼロが埋められます。ただし、高い分解能から低いシリアル化へのパスはサポートされていません。つまり、12ビットADCで10ビット・ストリームを選択することはできません。

## TGC\_REGISTER\_WREN

アドレス：0[2]

TGCテーブルにアクセスするには、このビットを1に設定します。汎用レジスタ・テーブルにアクセスするには、このビットを0（リセット後のデフォルト）に設定します。前に説明したように、同じアドレスがいずれか一方のレジスタ・バンクを示します。ただし、TGC\_REGISTER\_WRENの値に関係なく、汎用レジスタのレジスタ0は常にアクセス可能です。TGCテーブルは、アドレス1から開始されます。

## VCA\_LOW\_NOISE\_MODE

アドレス：7[10]

このビットを1に設定すると、消費電力の増加（5mW/チャネル）と引き換えに、チャネルの等価入力ノイズが $5\text{nV}/\sqrt{\text{Hz}}$ （ゲインが31dBの場合）に減少します。

| アドレス        | D[15:7] | D[8]               | D[7]       | D[6]        | D[5]              | D[4]       | D[3]      | D[2] | D[1] | D[0] |  |  |

|-------------|---------|--------------------|------------|-------------|-------------------|------------|-----------|------|------|------|--|--|

| 0x01...0x94 |         |                    | REG_VALUES |             |                   |            |           |      |      |      |  |  |

| 0x95        | 未使用     | START_INDEX        |            |             |                   |            |           |      |      |      |  |  |

| 0x96        |         | STOP_INDEX         |            |             |                   |            |           |      |      |      |  |  |

| 0x97        |         | INTERP_ENABLE      | 0          | START_GAIN  |                   |            |           |      |      |      |  |  |

| 0x98        |         | HOLD_GAIN_TIME     |            |             |                   |            |           |      |      |      |  |  |

| 0x99        |         | 0                  | 0          | SOFT SYNC   | UNIFORM GAIN MODE | STATIC PGA | FINE_GAIN |      |      |      |  |  |

| 0x9A        |         | 0                  | 0          | COARSE_GAIN |                   |            |           |      |      |      |  |  |

| 0x9B        |         | UNIFORM_GAIN_SLOPE |            |             |                   |            |           |      |      |      |  |  |

## TGC制御レジスタ・マップ

TGCの動作は、後述の「VGA/TGCの動作」で説明されています。ここでは、TGC\_REG\_WRENビットに1を書き込むことでアクセスできるTGC制御レジスタについて説明します。次の表に、TGCの動作に関わるすべてのレジスタのレジスタ・マップを示します。

### REG\_VALUE

アドレス：0x01[8:0]～0x94[8:0]

これらの各9ビット・レジスタ(計148個)には、ゲイン上昇中に所定のゲイン設定に保持される時間が格納されます。各レジスタの最上位ビット(REG\_VALUE<8>)は、現在のゲイン値からの増加または減少のいずれかを示します。他の8ビット(REG\_VALUE<7:0>)は、ゲインがCURRENT\_GAINからCURRENT\_GAIN±1dB (REG\_VALUE<8>に応じて)まで変化するのにかかる時間(8×Tclkの倍数。Tclkはチャネル・サンプリング・クロック=デバイスの入力クロック周期の2倍)を示します。この1dBのゲイン変化の最速上昇(最短時間)は、REG\_VALUE<7:0> = 0x00によって設定され、8×Tclkとなります。この1dBのゲイン変化の最も遅い上昇(最長時間)は、REG\_VALUE<7:0> = 0xFFによって設定され、255×8×Tclkとなります(後述のVGA動作を参照)。

### START\_INDEX

アドレス：0x95[7:0]

この8ビット・レジスタは、TGC曲線の最初のREG\_VALUEレジスタ(曲線の開始部分)を指定し、1～148(10進)の値を使用できます。

### STOP\_INDEX

アドレス：0x96[7:0]

この8ビット・レジスタは、TGC曲線の最後のREG\_VALUEレジスタ(曲線の終了部分)を指定し、1～148(10進)の値を使用できます。

### START\_GAIN

アドレス：0x97 [5:0]

この6ビット・レジスタは、-5dB～31dBの開始ゲイン値を指定します。

$$\text{START_GAIN} = [-5 + \text{REG_VALUE}] \text{ dB}$$

| REG_VALUE | GAIN  |

|-----------|-------|

| 0x0       | -5 dB |

| 0x1       | -4 dB |

| 0x24      | 31 dB |

### STOP\_GAIN

(プログラミング可能なレジスタではなく、内部で計算される値)

ケース1：

INTERP\_ENABLE = 1、

$$\text{STOP_GAIN} = \text{START_GAIN} + (\text{STOP_INDEX} - \text{START_INDEX}) - (2 * \text{減少ステップ数}) + 0.875\text{dB}$$

ケース2：

INTERP\_ENABLE = 0、

$$\text{STOP_GAIN} = \text{START_GAIN} + (\text{STOP_INDEX} - \text{START_INDEX}) - (2 * \text{減少ステップ数})$$

### HOLD\_GAIN\_TIME

アドレス：0x98[7:0]

この8ビット・レジスタは、前述のように計算されたSTOP\_GAIN値に達するか、または最大/最小ゲインに到達した後で、STOP\_GAINを保持する時間を指定します。この時間の経過後、TGCは、Tclk毎に1dBのステップでSTART\_GAIN値への降下を開始します。STOP\_GAIN値は、次のクロック数だけ保持されます。

$$\text{HOLD_GAIN_TIME} = [33 * \text{REG_VALUE}] \text{ Tclk}$$

ここで、Tclkはチャネル・サンプリング・クロックです。

| REG_VALUE | HOLD_GAIN_TIME |

|-----------|----------------|

| 0x0       | 0 Tclks        |

| 0x1       | 33 Tclks       |

| 0xFF      | 8415 Tclks     |

#### **INTERP\_ENABLE**

アドレス : 0x97 [7]

この8ビット・レジスタは、上昇レートを設定します。INTERP\_ENABLE = 1のとき、上昇レートは、REG\_VALUEに格納されているクロック数毎に、0.125dBとなります。

| <b>REG_VALUE</b> | 勾配                |

|------------------|-------------------|

| 0x0              | Tclk毎に0.125dB     |

| 0x1              | Tclk毎に0.125dB     |

| 0x2              | 2*Tclk毎に0.125dB   |

| 0xFF             | 255*Tclk毎に0.125dB |

INTERP\_ENABLE = 0のとき、上昇レートは、REG\_VALUEに格納されているクロック数×8毎に、1dBとなります。

| <b>REG_VALUE</b> | 勾配                  |

|------------------|---------------------|

| 0x0              | 8 × Tclk毎に1dB       |

| 0x1              | 8 × Tclk毎に1dB       |

| 0x2              | 16 × Tclk毎に1dB      |

| 0xFF             | 255 × 8 × Tclk毎に1dB |

#### **STATIC\_PGA**

アドレス : 0x99 [3]

このビットを1に設定すると、TGCエンジンがディスエーブルになります。COARSE\_GAINおよびFINE\_GAINによって、時間とは独立にゲイン値が制御されます。

#### **COARSE\_GAIN**

アドレス : 0x9A [5:0]

この6ビット・レジスタは、-5dB～31dBの範囲内で、ゲインを1dBの粗い間隔で指定(粗調)します。0x00～0x24の値だけが有効であることに注意してください。COARSE\_GAINレジスタで0x24より大きい値を設定すると、0x24を設定した場合と同じになります。

$$\text{COARSE_GAIN} = [-5 + \text{REG\_VALUE}] \text{ dB}$$

| <b>REG_VALUE</b> | <b>GAIN</b> |

|------------------|-------------|

| 0x0              | -5dB        |

| 0x1              | -4dB        |

| 0x24             | 31dB        |

#### **SOFT\_SYNC**

アドレス : 0x99 [5]

SOFT\_SYNCビットを1に設定すると、所定のTGC曲線に統いてTGCエンジンが周期的に実行され、SYNCピンに“High”パルス信号が不要になります(詳細は下記参照)。

#### **UNIFORM\_GAIN\_MODE**

アドレス : 0x99 [4]

このビットを0(デフォルト)に設定すると、TGCエンジンは任意のゲイン対時間曲線に従います。このビットを1に設定すると、ゲインはUNIFORM\_GAIN\_SLOPEレジスタで設定された勾配によって上昇します。(詳細は下記参照)

#### **UNIFORM\_GAIN\_SLOPE**

アドレス : 0x9B [7:0]

後述の「ゲイン一様増加モード」を参照してください。

#### **FINE\_GAIN**

アドレス : 0x99 [2:0]

この3ビット・レジスタは、0dB～0.875dBの範囲内で、ゲインを0.125dBの微細な間隔で指定(微調)します。

$$\text{FINE_GAIN} = [0.125 \times \text{REG\_VALUE}] \text{ dB}$$

| <b>REG_VALUE</b> | <b>GAIN</b> |

|------------------|-------------|

| 0x0              | 0dB         |

| 0x1              | 0.125dB     |

| 0x7              | 0.875dB     |

## VGA/TGCの動作

可変ゲイン・アンプ(VGA)の対時間のゲイン変化は、TGC関数と呼ばれ、AFE5851ではデジタル制御されます。ゲインはスイッチド・ネットワークによって実現され、ゲインを制御するスイッチをADCのサンプリング・タイミングと同期することで、出力データ上のグリッチを最小限に抑えています。ゲイン設定は、ユーザーが選択した動作モードによって異なります。可能な動作モードは、ゲイン非一様モード、ゲイン一様モード、静的モードの3つです。以降の節で、各モードを詳しく説明します。

### ゲイン非一様増加モード

ゲイン非一様ゲイン増加モードでは、ユーザーが任意の形状のゲイン対時間曲線を設定します。所定の時間/サンプリング・タイミングに対して、内部メモリの148個の位置/レジスタ(REG\_VALUE)からデジタル・ゲイン設定が取得されます。各レジスタは9ビット長で、シリアル・ポートを通じてユーザーが値をロードします(「シリアル・インターフェイス」を参照)。TGC\_REGISTER\_WREN = 1のときに、アドレス1~148を使用してこれらのレジスタにアクセスできます。

前述のとおり、各レジスタの最上位ビット(REG\_VALUE<8>)は、現在のゲイン値からの増加または減少のいずれかを示します。他の8ビット(REG\_VALUE<7:0>)は、ゲインがCURRENT\_GAINからCURRENT\_GAIN±1dB(REG\_VALUE<8>に応じて)まで変化するのにかかる時間(8×Tclkの倍数。Tclkはサンプリング・クロック)を示します。この1dBのゲイン変化の最速上昇(最短時間)は、REG\_VALUE<7:0> = 0x00によって設定され、8×Tclkとなります。この1dBのゲイン変化の最も遅い上昇(最長時間)は、REG\_VALUE<7:0> = 0xFFによって設定され、255×8×Tclkとなります。

INTERP\_ENABLEは、ゲインがどのように増加/減少するかを設定します。デフォルトでは、ゲインの変化は1dBのステップで実行されます(INTERP\_ENABLE = 0)。INTERP\_ENABLE = 1の場合、実際の1dBゲイン・ステップが $0.125\text{dB} \times 8$ ステップで実現されます。

148個のREG\_VALUEレジスタを使用して、1つまたは複数のTGC曲線を格納できます。START\_INDEXレジスタは、TGC曲線を開始するREG\_VALUEレジスタを指定し、STOP\_INDEXレジスタはTGC曲線を終了するREG\_VALUEレジスタを指定します。START\_INDEXおよびSTOP\_INDEXレジスタを使用して、目的のTGC曲線を選択できます。

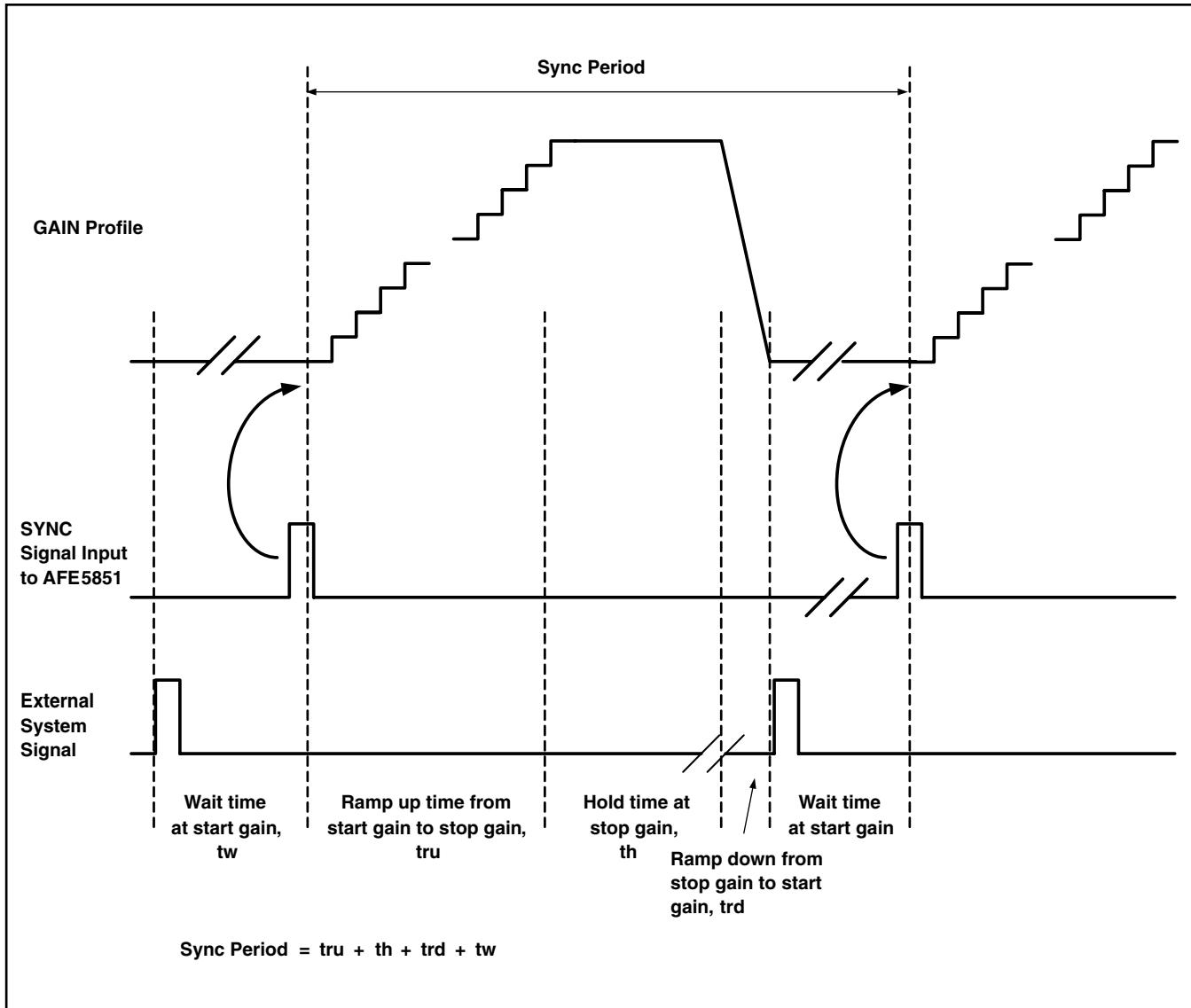

図 34. SYNC周期

図34に示されるように、SYNCピンに“High”パルス信号を印加すると、TGC曲線の開始ゲイン値がSTART\_GAINレジスタの値に設定され、START\_INDEXから開始して各REG\_VALUEが順番に使用されます。SYNCパルスの受信後にゲインのステップ開始を遅延させるオプションはないことに注意してください。その後、STOP\_INDEXに達するか、または最大/最小ゲインを超えるまで、ゲインのステップ変化が継続されます。その後は、HOLD\_GAIN\_TIMEレジスタで設定される追加クロック数の間、最後の有効なゲイン値が保持されます。

HOLD\_GAIN\_TIMEレジスタで指定されるクロック数が経過すると、TGCは、次のTGCプロファイルの準備のために、Tclk(チャネル・サンプリング・クロック)毎に1dBのステップでSTART\_GAINへの降下(または上昇)を開始します。SYNCピンに新しい“High”パルスが印加されると、TGCは再度REG\_VALUEを更新し、その値に従って変化を開始します。

SYNC信号は、チャネル・サンプリング・クロックの立ち上がりエッジでラッチされます。つまり、ゲインは、チャネル・サンプリング・クロックの立ち上がりエッジで増加します。立ち上がりエッジのセットアップ・タイムは7ns、ホールド・タイムは4nsです。

## SOFT\_SYNC

TGCは、SYNCピンに“High”パルス信号を入力する必要なしに、所定のTGC曲線に従って周期的に実行することもできます。これは、SOFT\_SYNCビットを1に設定することで行います。このビットを設定すると、イベントのシーケンスが、固定接続されたSYNCパルスの場合と同じになります。TGC曲線は、START\_INDEXからSTOP\_INDEXまで更新されます。STOP\_INDEXまたは最大/最小ゲインに達すると、STOP\_GAINの値がHOLD\_VALUE\_TIMEの時間だけ保持されてから、ゲインがSTART\_GAINまで上昇または降下します。その後、TGCの更新が再び自動的に開始され、SOFT\_SYNCビットがゼロになるまでの間、上記のステップを周期的に繰り返します。

レジスタ書き込みによるSYNCプロセスは、レジスタが書き込まれたときのシリアル・クロック・エッジで実行されます。シリアル・クロックとサンプル・クロック(チャネル・サンプリング・クロック)が同期している場合は、固定接続SYNCの項で示した関係が適用され、チャネル・サンプリング・クロックの立ち上がりエッジでSYNCビットがラッチされます。ここで、立ち上がりエッジのセットアップ・タイムは7ns、ホールド・タイムは4nsです。サンプル・クロックとシリアル・クロックが同期していない場合は、この関係が適用されず、最も近いサンプル・クロックの立ち上がりエッジに対して±1サンプルのクロック不確定性が生じます。

例1: 次のゲイン非一様モードの例では、148個のレジスタがすべてロードされます。ただし、TGCの開始アドレス(START\_INDEX)は2に設定され、停止アドレス(STOP\_INDEX)は7に設定されます。START\_GAINは6、HOLD\_GAIN\_TIMEは4に設定されます。

SYNCピンに“High”パルスを印加すると、ゲインが1dB(START\_GAIN = 0x06)から開始されます。1dBから2dBへの上昇は、(INTERP\_ENABLEが1に設定されているため)8回の0.125dBステップ(各15Tclk)を使用して120Tclkで実行されます。2dBから3dBへの上昇は、やはり0.125dBステップを使用して64Tclkで実行されます。3dBから4dBへの上昇は、40Tclkで実行されます。4dBから3dBへの降下は、64Tclkです。3dBから4dBへのゲイン上昇は56Tclkであり、4dBから4.875dBへは80Tclkです。

INTERP\_ENABLE = 1の場合、STOP\_GAIN = START\_GAIN + (STOP\_INDEX - START\_INDEX) - (2 \* 減少ステップ数) + 0.875dBとなります。INTERP\_ENABLE = 0の場合は、STOP\_GAIN = START\_GAIN + (STOP\_INDEX - START\_INDEX) - (2 \* 減少ステップ数)となります。これは、INTERP\_ENABLE = 1のときには補間エンジンによってゲインが増加または減少し続けるのに対し、INTERP\_ENABLE = 0のときにはゲインの値が保持されるためです。

| TGC REG INDEX | REG_VALUE[8:0] | Tclk数               | ゲインの変化する方向 |

|---------------|----------------|---------------------|------------|

| 1             | 0x004          | $4 \times 8 = 32$   | 増加         |

| 2             | 0x00F          | $15 \times 8 = 120$ | 増加         |

| 3             | 0x008          | $8 \times 8 = 64$   | 増加         |

| 4             | 0x005          | $5 \times 8 = 40$   | 増加         |

| 5             | 0x108          | $8 \times 8 = 64$   | 減少         |

| 6             | 0x007          | $7 \times 8 = 56$   | 増加         |

| 7             | 0x00A          | $10 \times 8 = 80$  | 増加         |

| ...           | ...            | ...                 | ...        |

| 147           | 0x00F          | $15 \times 8 = 120$ | 増加         |

| 148           | 0x00F          | $15 \times 8 = 120$ | 増加         |

| 名前                | 値    |

|-------------------|------|

| START_INDEX       | 0x02 |

| STOP_INDEX        | 0x07 |

| START_GAIN        | 0x06 |

| HOLD_GAIN_TIME    | 0x04 |

| INTERP_ENABLE     | 1    |

| UNIFORM_GAIN_MODE | 0    |

## ゲイン一様増加モード

UNIFORM\_GAIN\_MODEを1に設定することにより、TGCエンジンをゲイン一様増加モードに設定して、ゲインをSTART\_GAIN値からSTOP\_GAINまで、UNIFORM\_GAIN\_SLOPEレジスタで設定された一定勾配で上昇させることができます。注：STOP\_GAINはプログラミング可能なレジスタではなく、START\_GAIN、UNIFORM\_GAIN\_SLOPE、START\_INDEX、STOP\_INDEXから内部で計算される値です。

INTERP\_ENABLE = 1の場合、UNIFORM\_GAIN\_SLOPEは、0.125dBだけ増加または減少する前に所定のゲインを保持するTclk(チャネル・サンプリング・クロック)数を設定します。INTERP\_ENABLE = 0の場合、このレジスタは、1dBだけ増加または減少する前に所定のゲインを保持する $8 * Tclk$ (サンプリング・クロック8周期分)の数を設定します。どちらの場合も、1dB増加するのにかかる時間は同じです。INTERP\_ENABLE = 0の場合は、指定された時間にわたってゲインが同じ設定に維持されますが、INTERP\_ENABLE = 1の場合は、ゲインが細かいステップ(0.125dB)を重ねながら1dB分増加します。

INTERP\_ENABLEが0のとき、STOP\_GAINは $START_GAIN + (STOP_INDEX - START_INDEX)$ として計算されます。一方、INTERP\_ENABLEが1のときには、STOP\_GAINは $START_GAIN + (STOP_INDEX - START_INDEX) + 0.875dB$ に等しくなります。これは基本的に、後者の場合には補間エンジンによってゲインが増加または減少し続けるのに対し、前者ではゲインの値が保持されるためです。この場合、START\_INDEXおよびSTOP\_INDEXは、REG\_VALUEテーブルへのポインタとして使われているのではないことに注意してください。この2つの値の差だけが、STOP\_GAINを計算するために重要となります。そのため、START\_INDEXはゼロに設定してもよく、その場合STOP\_INDEXには $(STOP_GAIN - START_GAIN)$ が格納されます。正勾配(上昇)だけが可能であることに注意してください。

例1：START\_GAIN = 0x2(-3dB)、START\_INDEX = 0x00、STOP\_INDEX = 0x06、INTERP\_ENABLE = 0、およびUNIFORM\_GAIN\_SLOPE = 0x8に設定すると、ゲインは $8 \times 8 \times Tclk$ にわたって-3dBに設定され、その後64Tclkにわたって-2dBとなり、以下同様に、-1、0、1、2、3dBと変化します。64 × Tclkにわたって3dBに保持された後、ゲインはHOLD\_GAIN\_TIMEの時間が経過するまで同じ値に留まってから、1Tclk毎に1dBの割合でSTART\_GAINまで降下を開始します。

例2：START\_GAIN = 0x2(-3dB)、START\_INDEX = 0x00、STOP\_INDEX = 0x06、およびUNIFORM\_GAIN\_SLOPE = 0x8の同じ設定で、INTERP\_ENABLE = 1に設定すると、ゲインは8Tclkにわたって-3dB、次の8Tclkにわたって-2.875dB、次に-2.750dB、以降同様で3dBまで増加します。この時点で、INTERP\_ENABLE = 0の例1ではゲインがさらに64Tclk保持されました。この例では、3.875dBに達するまで、8Tclk毎に0.125dBステップの割合でゲインが引き続き増加します。その後8Tclk経過し、さらにHOLD\_GAIN\_TIME時間だけ待ってから、ゲインの降下が開始されます。

例3：START\_GAIN = 0x2(-3dB)、START\_INDEX = 0x00、STOP\_INDEX = 0x06、INTERP\_ENABLE = 1、およびUNIFORM\_GAIN\_SLOPE = 0x1に設定すると、ゲインは-3dB、-2.875、-2.75、-2.625、-2.5、-2.375、-2.25、-2.125の順に変化し、各値に1クロック・サイクルだけ留まります(合計8クロック・サイクル)。その後、-2.125dBでHOLD\_GAIN\_TIMEの時間だけ保持されてから、再び-3dBまで降下を開始します。

例4：例3と同じ設定で、INTERP\_ENABLE = 0とすると、単純にVGAゲインが8クロック・サイクルにわって-3dBに保持されてから、HOLD\_GAIN\_TIMEの時間だけ待ちます。

## 静的PGAモード

第3の動作モードは、実際には、STATIC\_PGAビットに1を書き込んでTGCエンジンをディスエーブルにするモードです。これにより、固定ゲイン・モードが使用可能になり、ゲインは粗調ゲインと微調ゲインとの合計で求められます。粗調ゲインは、COARSE\_GAINレジスタ(0x00～0x24の6ビット・ワード)を使用して、-5dBから31dBまで1dBステップで設定できます。COARSE\_GAINレジスタで0x24より大きい値を設定すると、0x24を設定した場合と同じになります。微調ゲインは、FINE\_GAINレジスタ(0x00～0x07の3ビット・ワード)を使用して、0dBから0.875dBまで0.125dBステップで設定できます。両方のレジスタをそれぞれ最大値に設定したときの最大ゲインは、31.875dBとなります。

## アンチエイリアシング・フィルタ(AAF)

AFE5851には、16チャネルのそれぞれについて選択可能な3次ローパス・フィルタが内蔵されています。カットオフ周波数は、シリアル・インターフェイスを使用して、全チャネル同時に3つの可能な設定(7.5MHz、10MHz、14MHz)から選択できます(汎用レジスタ表のFILTER\_BWレジスタを参照)。図19に、これらの各設定での周波数応答を示しています。フィルタ特性は、受動部品によって設定され、プロセスおよび温度によって変動します。周波数特性には標準で±5%の変動が想定されています。

## クランプ回路と過負荷回復

AFE5851は、フロントエンド・デバイスが過負荷状態からごく短時間で回復することが求められる超音波アプリケーション向けに設計されています。そのような過負荷は、VGAおよびADCの過負荷につながる送信パルスのフィードスルーや強力なエコーによって発生します。

AFE5851には、デフォルトでインエーブルとなっているクランプ回路が内蔵され、チャネル全体の過負荷回復動作をさらに最適化しています(図31を参照)。この回路は、汎用レジスタ・マップのアドレス70(10進数)のビット14に1を書き込むことで、ディスエーブルにできます。クランプは、ADCのフルスケール(2Vpp)を3dB超える信号を制限するよう設定されています。

## クロック入力

16個のチャネルは、単一のクロック入力で動作します。アパー チャ遅延およびジッタがすべてのチャネルで同じになるよう に、AFE5851ではクロック・ツリー・ネットワークを使用して各 チャネルへ個別のサンプリング・クロックを生成しています。 クロック・ソースのポイントから8個の内部ADCそれぞれのサン プリング回路まで、すべてのチャネルのクロック・チャネルが マッチングされています。この遅延時間の変動については、「出力インターフェイス・タイミング」の「アパー チャ遅延」パ ラメータに記載されています。時間に対する変動は、同じ表の 「アパー チャ・ジッタ」に示されています。入力クロックの立ち 上がりエッジを使用して、1つの入力クロック周期で偶数チャ ネルをサンプリングし、次の入力クロック周期で奇数チャネル をサンプリングしています。チャネル・サンプリング・クロック の2倍のレートの入力クロックを使用することで、偶数チャネル と奇数チャネルの間のサンプリング・タイミングが厳密に1入力クロック周期だけ離れ、デューティ・サイクルに依存しない ことが保証されます。

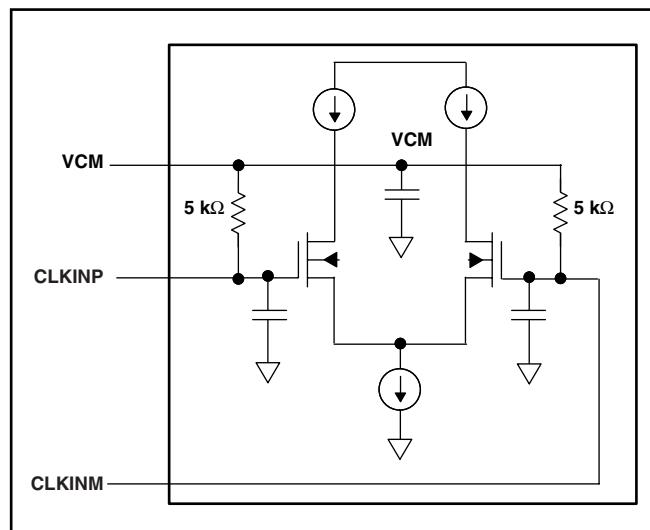

AFE5851のクロック入力は、差動(正弦波、LVPECLまたは LVDS)またはシングルエンド(LVCMOS)で駆動できます。デ バイスのクロック入力には、内部にバッファ/クロック・アンプ が備えられています(図35を参照)。これは、供給されるクロック の種類に応じて、自動的にイネーブルまたはディスエーブル になります(自動検出機能)。イネーブルになると、デバイスは AVDD18電源レールから6mWだけ多くの電力を消費しますが、 より小さな振幅の差動またはシングルエンド入力を受け付けら れるようになります。

図35. 差動クロック・モードの内部クロック・バッファ

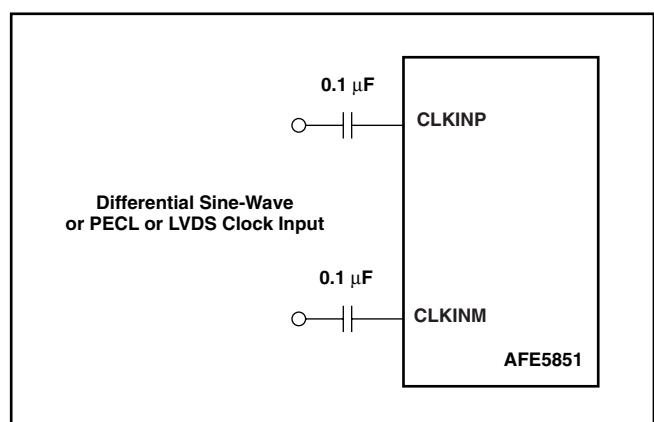

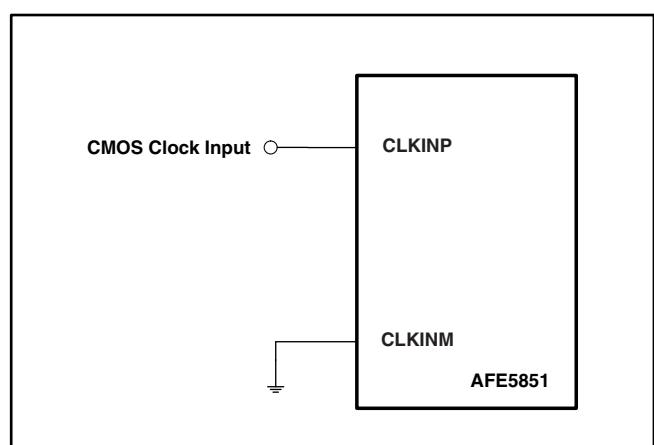

デバイスに使用するクロック方式がシングルエンドである場 合は、CLKINMピンをグランドに接続する必要があります。つ まり、直接AVSSに接続します(図37を参照)。この場合、自動 検出機能によって、内部クロック・バッファがシャットダウン され、デバイスは自動的にシングルエンド・クロック入力とな ります。ユーザーはシングルエンド・クロック・ソース源を直 接(デカップリングなしで)CLKINPピンに接続する必要がありま

す。このピンが、デバイスの唯一のクロック入力となります。 その場合には、低ジッタの方形波信号(LVCMOSレベル、振幅 1.8V)でADCを駆動することを推奨します(理論の詳細につい ては、SLYT075を参照してください)。

シングルエンドの正弦波クロック、または差動クロック (LVPECL、LVDS,...)の場合は、クロック・アンプをイネーブル にする必要があります。その場合、図36の接続方式を使用し ます。クロック・ソースの同相電圧は、AFE5851のクロック入 力の同相電圧(VCM)と一致する必要があります。VCMは、図 35に示すように、5kΩの抵抗を使用して内部で設定されていま す。これを保証するための最も簡単な方法は、図36に示すよう に入力をAC結合することです。クロックがシングルエンドでも、 振幅が小さいか、エッジが鋭くない場合(例えば、正弦波 シングルエンド・クロック)には、同じ方式を適用できます。こ の場合、入力信号は(図36のように)コンデンサを使用してCLK- INPに接続しますが、CLKINMもコンデンサを通してグランド に接続(つまり、AVSSにAC結合)する必要があります。

図36. 差動クロック駆動回路

トランスを使用して2次側をフローティングにする場合(例え ば、シングルエンドから差動に変換する場合)には、100nFの直 列コンデンサを使用せずに、クロック入力に直接接続できます。

図37. シングルエンド・クロック駆動回路

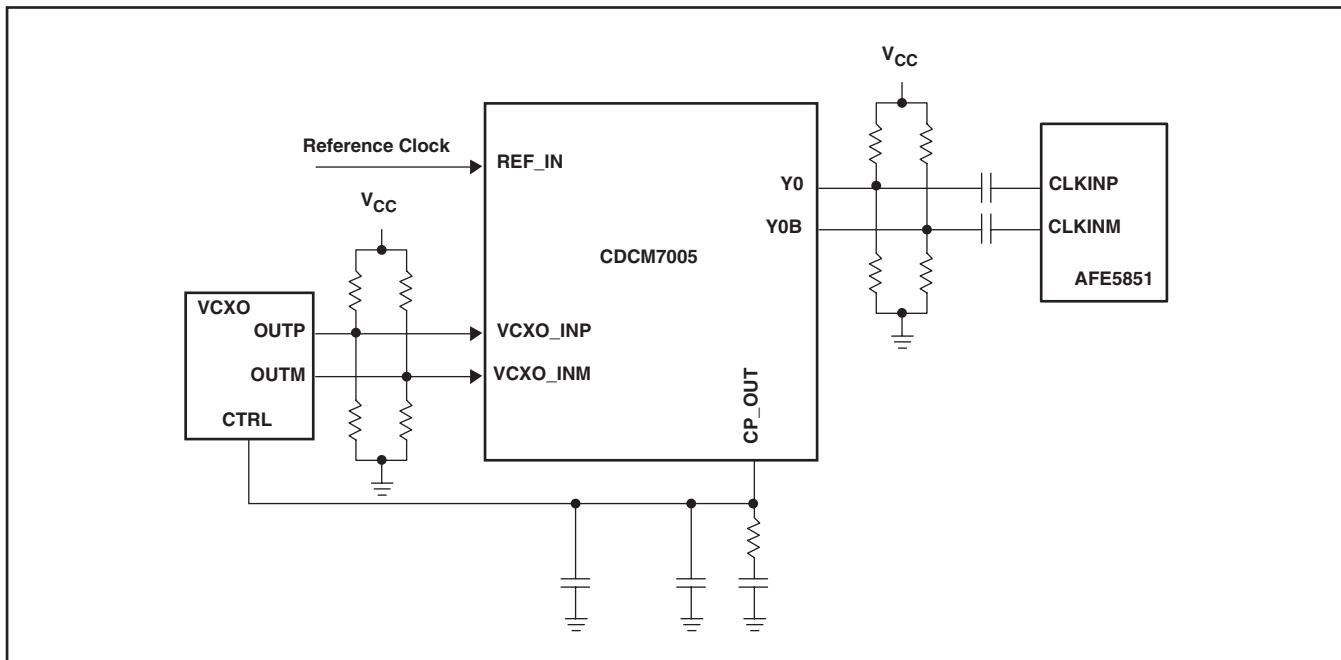

図38. CDCM7005を使用したPECLクロック駆動

最後に、差動クロック構成について、CDCM7005を使用して AFE5851のクロック信号を生成する例を図38に示します。

## デジタル出力

8個のADCからの変換結果はシリアル化され、ADC毎に1つのLVDSデータ・ペアを使用して、デバイス入力クロック・レートの12倍の速さで出力されます。それ以外に、ADC出力を読み取る回路とのインターフェイスを容易にするため、もう2つのLVDSペアが使用されます。一方の側では、チャネル・レート(入力クロック・レートの1/2)で動作するリファレンス・フレームLVDS信号が、サンプル・ワードの開始と終了を示します。それに加えて、デバイスは入力クロック・レートの6倍のレートで動作するリファレンス・クロックを出力し、その立ち上がりおよび立ち下がり時間は個々のビットに揃えられています。タイミング図の説明、およびタイミング・マージンの詳細について

は、「出力インターフェイス・タイミング」を参照してください。

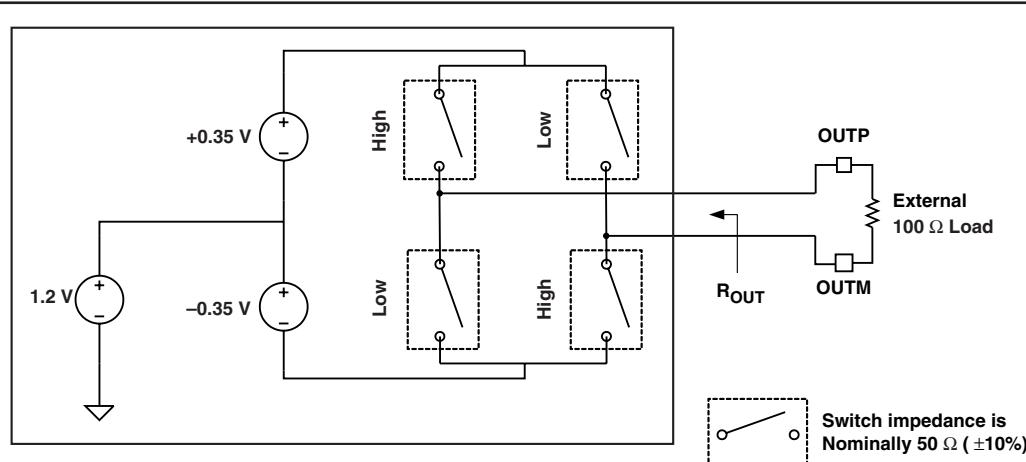

図39に、デバイスのLVDS出力回路を示します。LVDS出力が “High” (OUTP = 1.375V、OUTM = 1.025V) のときに、“High” 側スイッチが閉じて “Low” 側スイッチが開くことがわかります。LVDS出力が “Low” (OUTP = 1.025V、OUTM = 1.375V) のときは、“Low” 側スイッチが閉じ、“High” 側スイッチが開きます。“High” 側および “Low” 側のスイッチはR<sub>ON</sub>の公称値が50Ω±10%であるため、この2つの構成 (“High” 側が閉じる、または “Low” 側の閉じる) のいずれの場合も、出力インピーダンスは公称100Ωとなります。

## 外部/内部リファレンス

「汎用レジスタの説明」のEXTERNAL\_REFERENCEレジスタの説明を参照してください。

図39. LVDS出力回路

## 電源

適切にデカッピングした低ノイズ電源の使用を推奨します。リニア電源が第1の選択肢です。スイッチング電源の場合、AFE5851に結合されるノイズ成分が増加する傾向にあります。

パワーアップ・シーケンスは特に必要ありませんが、電源が安定状態と判断されてからRESETピンに正パルスを印加する必要があります（「シリアル・インターフェイス」を参照）。

パワーダウン・モードにはいくつかの種類があります。スタンバイ・モードでは、リファレンス発生器を除くすべての回路がパワーダウンされます。これにより、パワーダウンからフル動作への高速復帰が可能です。フル・パワーダウン・モードでは、すべてのブロックがパワーダウンされます（一部のデジタル回路を除く）。この場合、節電効果は大きいですが、パワーアップが遅くなります（詳細は仕様表を参照）。また、PDN\_Channel<7:0>を使用して（同じADCに対応する）チャネルのペアをパワーダウンしたり、PDN\_LVDSを使用してLVDS出力をパワーダウンすることも可能です。

最後に、パッケージ底面の金属ヒート・シンクもアナログ・グランドに接続されることに注意してください。

## レイアウト情報

評価ボードは、AFE5851の性能を最大限に活かすための基板レイアウト方法に関して、優れたガイドラインを提供します。多層基板の使用、アナログおよびデジタルADCグランドの両方に対する单一グランド・プレーンの使用、セラミック・チップ・コンデンサによるローカル・デカッピングなど、一般的な設計規則を適用する必要があります。入力パターンは、すべての外部干渉源およびノイズ源（デジタル出力およびクロック・パターンを含む）から分離します。また、入力信号の周波数が低い場合はクロックのジッタ条件が緩和されますが、クロックは他の信号から分離する必要があります。

適切なLVDSタイミングを維持するために、すべてのLVDSパターンは、制御されたインピーダンス設計（例えば、 $100\Omega$ 差動）に従ってください。さらに、すべてのLVDSパターン長を等しく、対称的にする必要があります。パターン長のばらつきは150mil（0.150インチまたは3.81mm）未満に抑えることを推奨します。

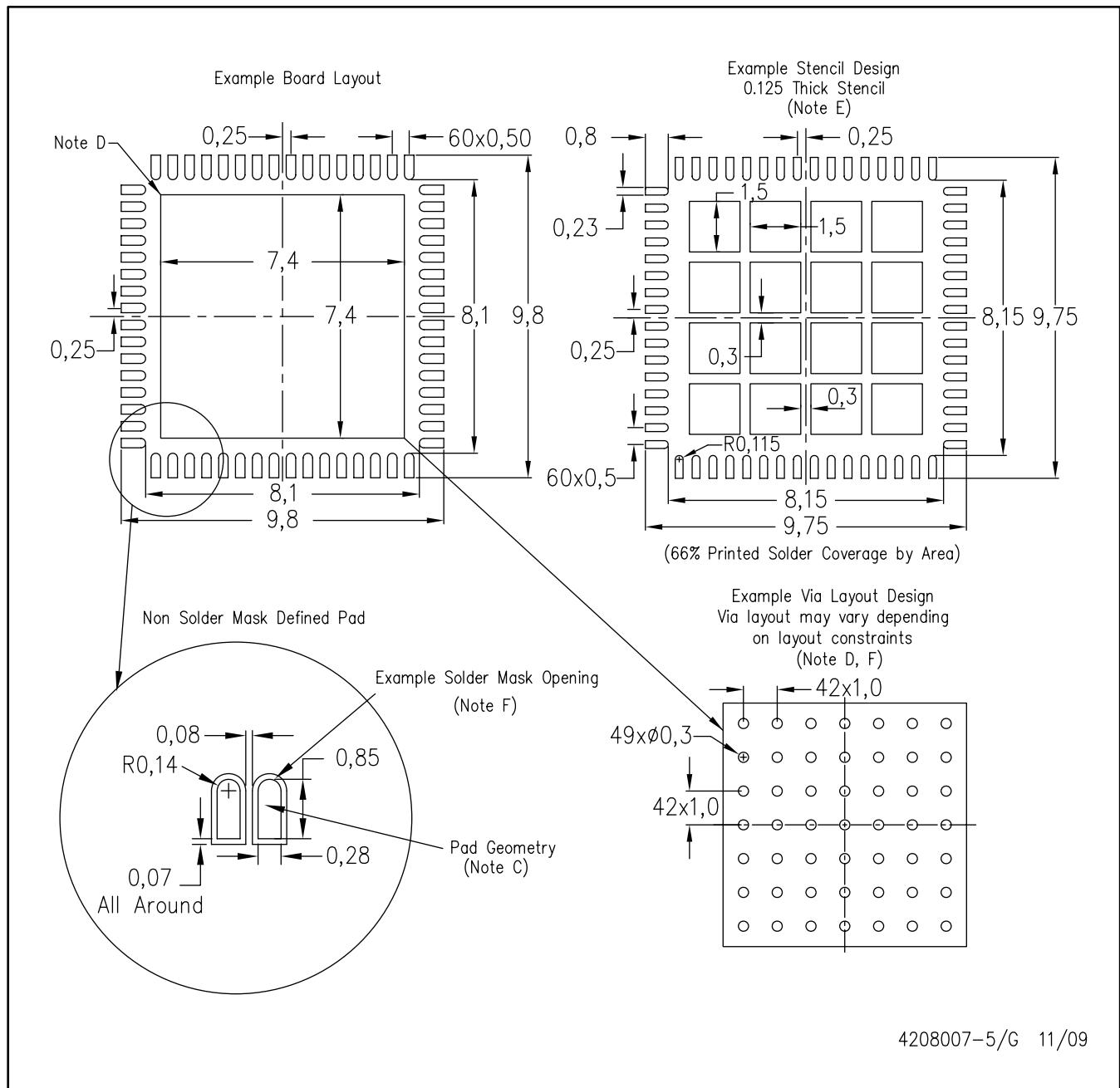

最高の熱特性を得るには、パッケージ底面の露出したパッドをグランド・プレーンに半田付けする必要があります。詳細については、アプリケーション・ノート『QFN Layout Guidelines』（SLOA122A）および『QFN/SON PCB Attachment』（SLUA271A）を参照してください。

## 仕様の定義

**アナログ帯域幅** — 低周波での出力値と比較して基本波の出力が3dB低下するアナログ入力周波数。

**アパー・チャ・遅延** — 入力サンプリング・クロックの立ち上がりまたは立ち下がりエッジ（チャネルによって異なる）から、実際にサンプリングが行われるまでの遅延時間。この遅延時間は、チャネル間で異なります。最大の変動は、アパー・チャ・遅延変動（チャネル間）として仕様に規定されています。

**アパー・チャ・不確定性（ジッタ）** — サンプル間でのアパー・チャ・遅延の変動。

**クロック・パルス幅/デューティ・サイクル** — クロック信号のデューティ・サイクルは、クロック信号の周期に対する、クロック信号が“High”に保持される時間（クロック・パルス幅）の割合。一般に、デューティ・サイクルは、パーセンテージで表されます。完全な差動正弦波クロックでは、デューティ・サイクルが50%になります。

**最大変換レート** — 適正な動作が行われる最大のサンプリング・レート。特に記述のない限り、すべてのパラメータ測定はこのサンプリング・レートで行われます。

**最小変換レート** — ADCが動作する最小のサンプリング・レート。

**微分非直線性（DNL）** — 理想的なADCでは、厳密に1LSBずつ離れたアナログ入力値でコード遷移が起こります。DNLは、任意の1ステップにおけるこの理想的な値からの偏差であり、 LSB単位で測定されます。

**積分非直線性（INL）** — INLは、ADCの伝達関数が、その伝達関数の最小二乗曲線によって決定される最もフィットするラインから、どれだけ離れているかを示す値であり、LSB単位で測定されます。

**ゲイン誤差** — チャネルの実際のゲインとその理想値（理論値）との差。つまり、チャネルの絶対ゲインの誤差です。

**ゲイン・マッチング** — 理論的なゲイン設定が同じである2つのチャネル間のゲインの差。完全なマッチングでは、差がゼロになります。このデバイスの場合、ゲイン・マッチングは2つの異なる方法で得られます。

1. 仕様表の値は、システム上の任意の2チャネル間のゲイン・マッチングの期待値を表しています。ゲインは、任意の温度において、各デバイスの各チャネルで、与えられたゲイン設定に対して測定されます。最大測定ゲインと最小測定ゲインの差が、そのゲイン設定でのゲイン・マッチングを表します。すべてのゲイン設定に対して同じ手順を実行し、任意のゲイン設定での最大の差が表に記載されます。

2. ゲイン・マッチングのヒストグラムは、同じデバイス内でのチャネル間のマッチングを示しています。これは、同じデバイスの任意の2チャネル間で予測される最大のゲイン差、つまり、デバイスのすべてのチャネルにわたる絶対ゲインのピーク・ツー・ピーク変動です。（デバイス全体に対して共通と仮定される任意の温度において）そのデバイスの全チャネルに特定のゲイン設定を適用した場合の、ゲインが最大のチャネルと最小のチャネルとの差が、1カウントを表します。同じ手順を、すべてのデバイスに対して3つの温度（-40°C、25°C、85°C）で行います。1つの温度での1デバイスの各測定が、1カウントを表します。

**オフセット誤差** — オフセット誤差は、ADCの実際の平均アイドル・チャネル出力コードと、理想的な平均アイドル・チャネル出力コードとの差（mV単位）です。

**温度ドリフト** — 温度ドリフト係数(ゲイン誤差およびオフセット誤差について)は、T<sub>MIN</sub>からT<sub>MAX</sub>までの摂氏1度あたりのパラメータの変化を規定します。これは、T<sub>MIN</sub>からT<sub>MAX</sub>までの範囲にわたるパラメータの最大偏差をT<sub>MAX</sub> – T<sub>MIN</sub>の差で割ることにより求められます。

**信号対雑音比(SNR)** — SNRは、ノイズフロア電力(P<sub>N</sub>)に対する基本波電力(P<sub>S</sub>)の比であり、DCおよび最初の9個の高調波の電力は除かれます。

$$SNR = 10 \log_{10} \frac{P_S}{P_N} \quad (1)$$

SNRは、基本波の絶対電力を基準とする場合にはdBc(搬送波に対するdB)、基本波の電力をコンバータのフルスケール範囲に外挿する場合にはdBFS(フルスケールに対するdB)で表されます。

**信号対雑音+歪(SINAD)** — SINADは、ノイズ(P<sub>N</sub>)および歪み(P<sub>D</sub>)を含む他のすべてのスペクトル成分(DCは除く)に対する基本波電力(P<sub>S</sub>)の比です。

$$SINAD = 10 \log_{10} \frac{P_S}{P_N + P_D} \quad (2)$$

SINADは、基本波の絶対電力を基準とする場合にはdBc(搬送波に対するdB)、基本波の電力をコンバータのフルスケール範囲に外挿する場合にはdBFS(フルスケールに対するdB)で表されます。

**有効ビット数(ENOB)** — ENOBは、量子化ノイズに基づく理論的リミットと比較した、コンバータの性能の指標です。

$$ENOB = \frac{SINAD - 1.76}{6.02} \quad (3)$$

**スピリアスフリー・ダイナミック・レンジ(SFDR)** — SFDRは、DCを除いた最大のFFT成分(高調波またはそれ以外)に対する基本波電力(P<sub>S</sub>)の比です。一般に、SFDRはdBc(搬送波に対するdB)単位で表されます。

**2次高調波歪(HD2)** — HD2は、2次高調波に対する基本波電力(P<sub>S</sub>)の比であり、一般にdBc(搬送波に対するdB)単位で表されます。

**3次高調波歪(HD3)** — HD3は、3次高調波に対する基本波電力(P<sub>S</sub>)の比であり、一般にdBc(搬送波に対するdB)単位で表されます。

**全高調波歪(THD)** — THDは、最初の9個の高調波の電力(P<sub>D</sub>)に対する基本波電力(P<sub>S</sub>)の比です。

$$THD = 10 \log_{10} \frac{P_S}{P_D} \quad (4)$$

一般に、THDはdBc(搬送波に対するdB)単位で表されます。

**AC電源除去比(AC PSRR)** - 電源電圧の変動に対するデバイスの耐性の指標です。このデータシートでは、ΔV<sub>SUP</sub>を電源電圧の変化、ΔV<sub>OUT</sub>を結果のADC出力コードの変化(入力を基準)とすると、次の式で表されます。

$$PSRR = 20 \log \left( \frac{\Delta V_{out}}{\Delta V_{sup}} \right) \quad (5)$$

## パッケージ・マテリアル情報

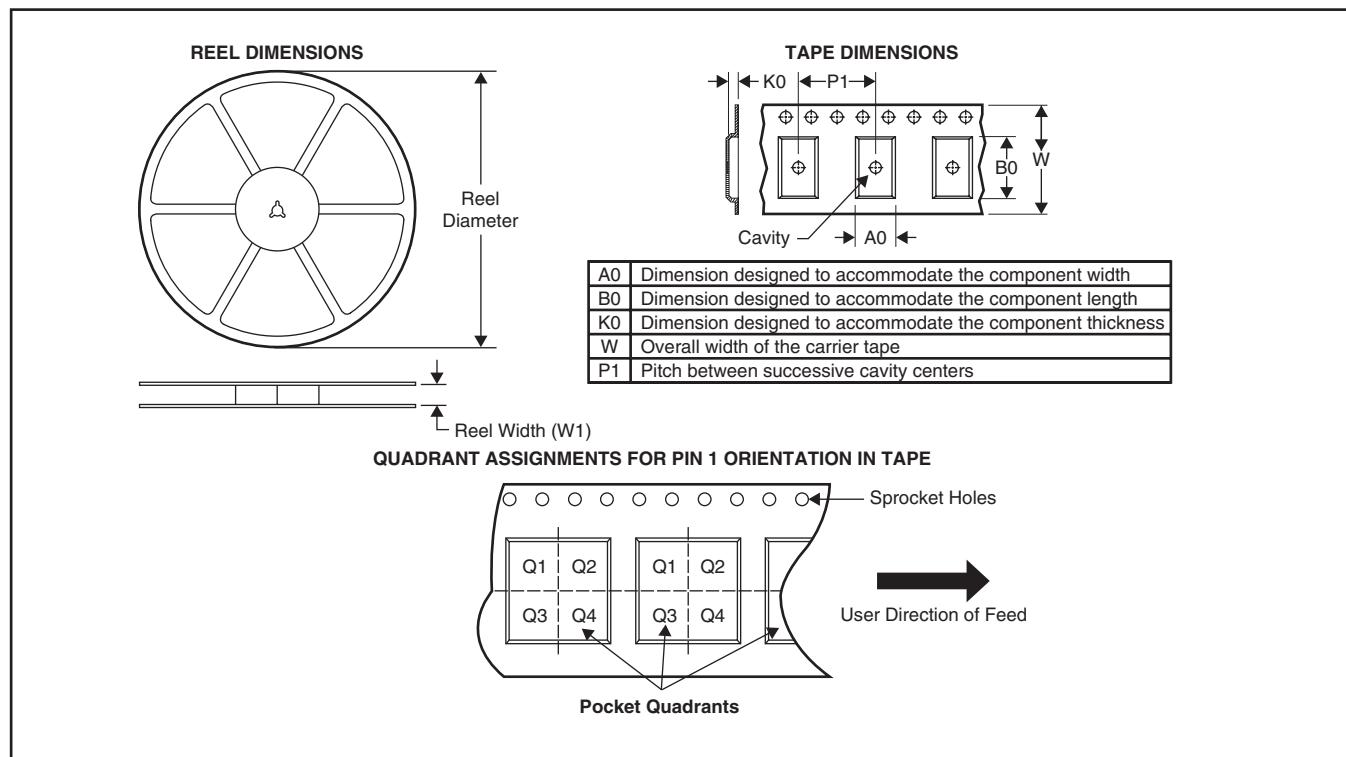

### テープおよびリール・ボックス情報

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| AFE5851IRGCR | VQFN         | RGC             | 64   | 2000 | 330.0              | 16.4               | 9.3     | 9.3     | 1.5     | 12.0    | 16.0   | Q2            |

| AFE5851IRGCT | VQFN         | RGC             | 64   | 250  | 330.0              | 16.4               | 9.3     | 9.3     | 1.5     | 12.0    | 16.0   | Q2            |

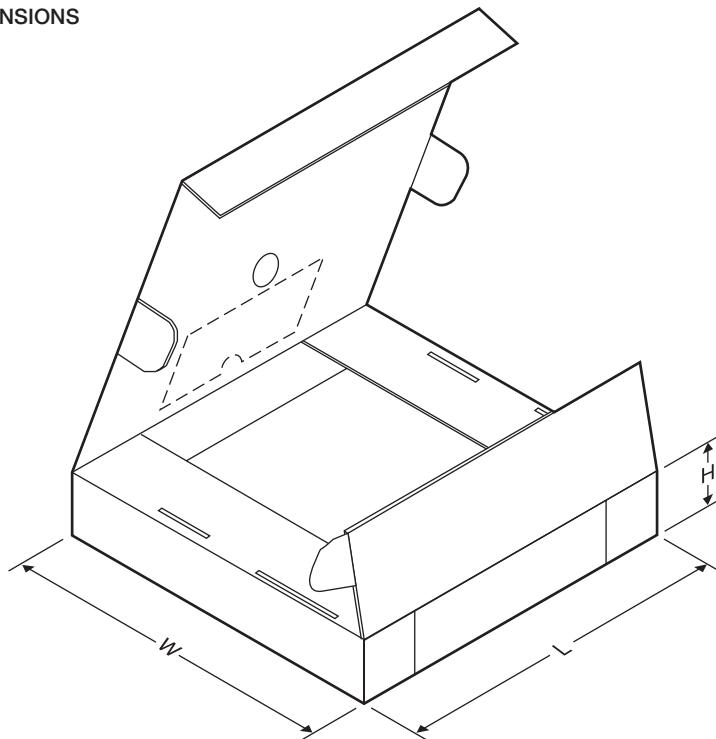

## パッケージ・マテリアル情報

TAPE AND REEL BOX DIMENSIONS

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| AFE5851IRGCR | VQFN         | RGC             | 64   | 2000 | 333.2       | 345.9      | 28.6        |

| AFE5851IRGCT | VQFN         | RGC             | 64   | 250  | 333.2       | 345.9      | 28.6        |

# メカニカル・データ

RGC (S-PVQFN-N64)

CUSTOM DEVICE PLASTIC QUAD FLATPACK NO-LEAD

注：A. 直線寸法はすべてミリメートル単位です。寸法および許容誤差は、ASME Y14.5M-1994によります。

B. 本図は予告なしに変更することがあります。

C. QFN(クワード・フラットパック・ノーリード)パッケージ構造。

△ パッケージのサーマルパッドは、熱的および機構的特性を得るために基板に半田付けする必要があります。

露出サーマルパッドの寸法に関する詳細は、製品データシートをご覧ください。

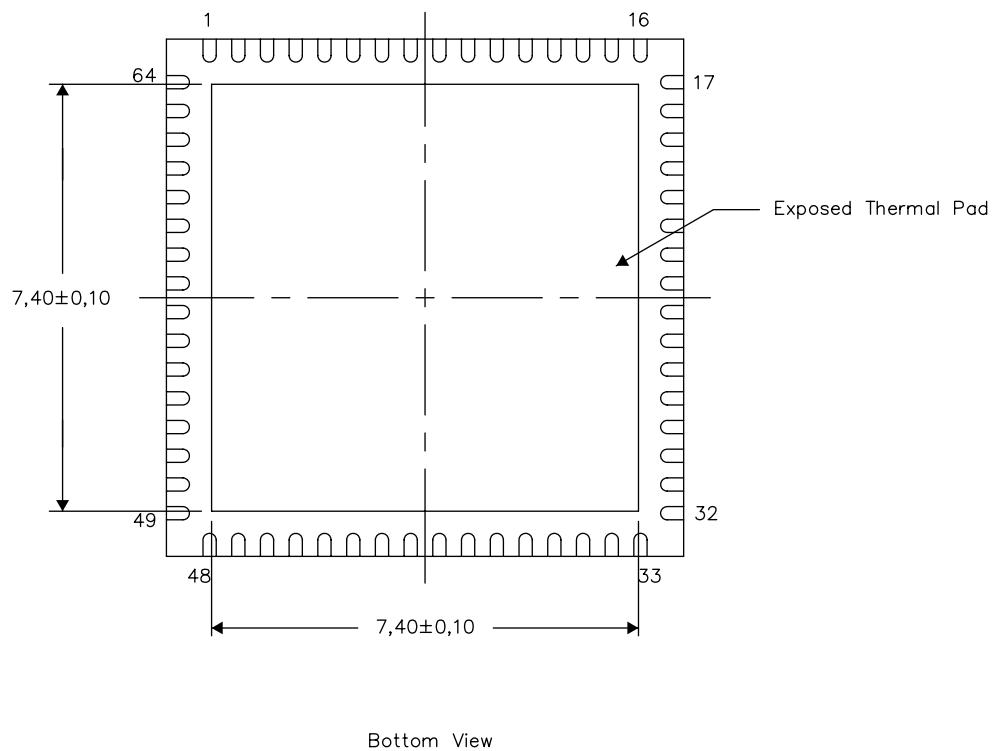

# サーマルパッド・メカニカル・データ

RGC (S-PVQFN-N64)

## 熱的特性に関する資料

このパッケージは外部のヒートシンクに直接接続できるよう設計された露出したサーマル・パッドをもっています。サーマル・パッドはプリント回路基板(PCB)に直接はんだ付けされなければなりません。はんだ付けされることにより、PCBはヒートシンクとして使用できます。さらに、サーマル・ビアを使用することにより、サーマル・パッドはグランドまたは電源プレーン(どちらか当てはまる方)、またはもう1つの方法としてPCBに設計された特別なヒートシンク構造に直接接続することができます。この設計により、集積回路(IC)からの熱の移動が最適化されます。

クワッド・フラットパック・ノーリード(QFN)パッケージとその利点についての情報はアプリケーション・レポート“Quad Flatpack No-Lead Logic Packages” TI文献番号SLUA271を参照してください。この文献はホームページwww.ti.comで入手できます。

このパッケージのサーマル・パッドの寸法は以下の図に示されています。

注：全ての線寸法の単位はミリメートルです。

サーマル・パッド寸法図

# ランド・パターン

RGC (S-PVQFN-N64)

注：A. 全ての線寸法の単位はミリメートルです。

B. 図は予告なく変更することがあります。

C. 代替設計については、資料IPC-7351を推奨します。

D. このパッケージは、基板上のサーマル・パッドに半田付けされるように設計されています。熱に関する具体的な情報、ビア要件、および推奨基板レイアウトについては、アプリケーション・ノート『Quad Flat-Pack Packages』(TI文献番号SLUA271)および製品データシートを参照してください。これらのドキュメントは、ホームページwww.ti.comで入手できます。

E. レーザ切断開口部の壁面を台形にし、角に丸みを付けることで、ペーストの離れがよくなります。ステンシル設計要件については、基板組み立て拠点にお問い合わせください。ステンシル設計上の考慮事項については、IPC 7525を参照してください。

F. 半田マスクの許容差については、基板組み立て拠点にお問い合わせください。

(SLOS574A)

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| AFE5851IRGCR          | Active        | Production           | VQFN (RGC)   64 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 85    | AFE5851             |

| AFE5851IRGCR.A        | Active        | Production           | VQFN (RGC)   64 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 85    | AFE5851             |

| AFE5851IRGCT          | Active        | Production           | VQFN (RGC)   64 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 85    | AFE5851             |

| AFE5851IRGCT.A        | Active        | Production           | VQFN (RGC)   64 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 85    | AFE5851             |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。