## Application Note

## MCU+SDK 用の xSPI カスタム フラッシュ デバッグ ガイド

Vaibhav Kumar, Nikhil Jain

## 概要

本アプリケーション ノートでは、MCU+SDK を使用して TI Sitara™ プロセッサ上でカスタム フラッシュ部品を起動するためのガイダンスを提供します。この文書では、TI の評価基板 (EVM) で利用できるものとは異なるフラッシュ部品を使用するカスタム ボードの開発者が直面する課題について取り上げます。

本文書では、新しいフラッシュ部品を統合、構成、検証し、TI のソフトウェア エコシステムを使用して信頼性の高い動作を検証するために必要な手順を概説しています。ターゲット オーディエンスには、カスタム ハードウェアを設計しており、SPI/QSPI/OSPI インターフェイス経由でフラッシュ通信を有効にする必要のあるエンジニアと開発者が含まれます。

このアプリケーション ノートに従うと、起動時間を短縮でき、一般的な統合の問題を最小限に抑えられることで、カスタム フラッシュ構成の開発とデバッグを迅速化できます。

## 目次

|                                           |    |

|-------------------------------------------|----|

| 1はじめに.....                                | 2  |

| 2用語.....                                  | 2  |

| 3ブートモードとフラッシュの互換性について.....                | 2  |

| 4フラッシュの統合と SysConfig のセットアップ.....         | 3  |

| 4.1 FLASH のパラメータ.....                     | 4  |

| 4.2 OSPI のパラメータ.....                      | 9  |

| 5起動に関する一般的な問題とデバッグ.....                   | 10 |

| 5.1 ブート エラー.....                          | 10 |

| 5.2 既知のエラッタ.....                          | 10 |

| 5.3 フラッシュ初期化エラー.....                      | 10 |

| 5.4 フラッシュの読み取りエラー.....                    | 11 |

| 5.5 フラッシュ プログラム エラー.....                  | 11 |

| 6OSPI および FLASH のサポートを要求するためのチェックリスト..... | 12 |

| 7まとめ.....                                 | 12 |

| 8参考資料.....                                | 12 |

## 商標

Sitara™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

組込みシステムでは、ブートローダーとアプリケーションコードの格納のために、外部フラッシュメモリが広く使用されています。AM64x、AM62x、AM62P、AM62DxなどのSitaraプロセッサは、外部NOR/NANDフラッシュデバイスを接続するための、OSPIやQSPIなどの複数のシリアルインターフェイスをサポートしています。MCU+SDKを使用したカスタムボードの起動時に、ユーザーは多くの場合、新しいフラッシュデバイスの接続において課題に直面します。たとえば、SysConfigパラメータの構成、デバイスIDの読み取り、PHYモードの有効化などです。

このアプリケーションノートでは、SysConfigを使用してフラッシュパラメータを構成する方法、一般的なエラーログの解釈、フラッシュの識別とPHYの有効化時の問題の解決方法について説明します。

## 2 用語

QSPI: クワッドシリアルペリフェラルインターフェイス

OSPI: オクタルシリアルペリフェラルインターフェイス

xSPI: 拡張シリアルペリフェラルインターフェイス

NVCR: 不揮発性構成レジスタ

VCR: 挥発性構成レジスタ

DDR: デュアルデータレート

SDR: シングルデータレート

QE: クワッドイネーブルビット

DAC: ダイレクトアクセスコントローラ

## 3 ブートモードとフラッシュの互換性について

ROMでサポートされているシリアルNOR/NANDフラッシュ用の各種ブートモードについては、[こちら](#)のテクニカルリファレンスマニュアルを参照してください。それぞれのブートモードでは、読み取りコマンドの発行に使用するプロトコルROMが記述されています。プロトコルはブートモードごとに異なります。たとえば、SPI(プロトコル1S-1S-1S)ブートモードの場合、ROMは読み取りコマンド0x03(8ビット)を発行し、それに続いて3バイト(24ビット)のアドレスを発行します。ダミーサイクルは発行しません。

ブートモードの記述に従っている場合、フラッシュはブート対応とみなされます。フラッシュは、次のパラメータをサポートしています。

1. プロトコル。

2. 読み取りコマンド。

3. 読み取りコマンドおよびアドレスのバイト数(3バイト/4バイト)。

4. 読み取りのダミーサイクル数。

カスタムフラッシュの場合、これらの値を取得するには、フラッシュ固有のデータシートを参照してください。フラッシュデータシートでは、これらの値は「コマンドセット」、「コマンドテーブル」、「命令セット」、「命令テーブル」、「トランザクションセット」、「トランザクションテーブル」というセクションに記載されています。

## 4 フラッシュの統合と **SysConfig** のセットアップ

**SysConfig** は、ハードウェアとソフトウェアの構成に関する課題の簡素化と、ソフトウェア開発の迅速化に役立つ設計を採用した構成ツールです。

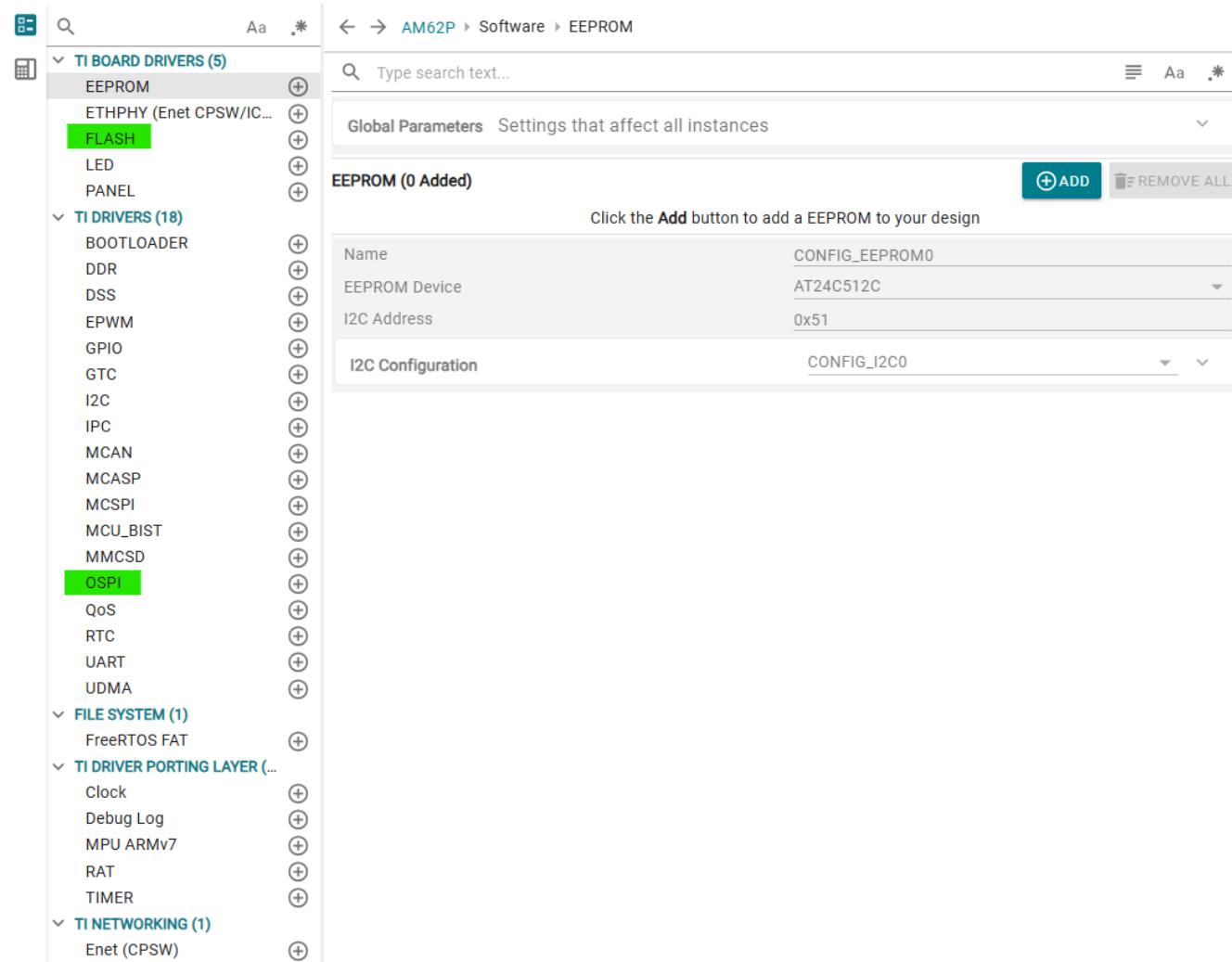

MCU+SDKにおいて、カスタム フラッシュの場合に変更が必要なセクションを図 4-1 に示します。

図 4-1. FLASH および OSPI セクションを示す **SysConfig** GUI

カスタム フラッシュ構成値を取得するには、[こちら](#)のガイドに従ってください。このガイドは現在、シリアル NOR フラッシュで機能します。シリアル NAND フラッシュの場合、構成値はフラッシュのデータシートから取得する必要があります。

値を取得するときは、FLASH セクションに取得した値を書き込むことができます。これらの値は、手動で入力するか、JSON 形式でアップロードできます。フラッシュのデータシートに記載されている値を使用して OSPI フラッシュ診断の例を実行して、得られた値を検証します。以下のセクションでは、FLASH および OSPI セクションの各種パラメータを示します。

## 4.1 FLASH のパラメータ

各パラメータについて、? をクリックすると記述について学ぶことができます。

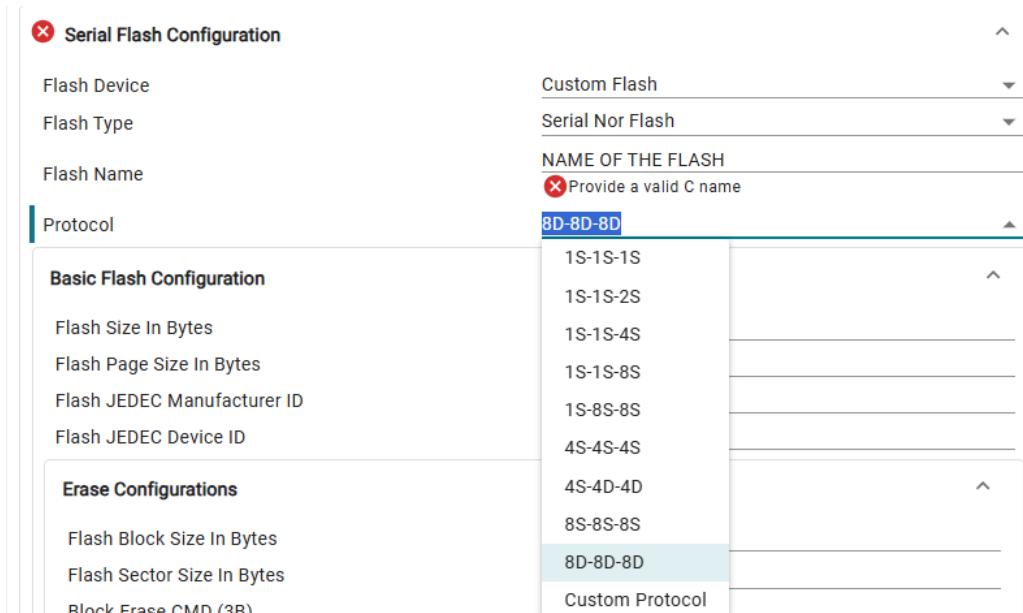

図 4-2 の説明:

1. **フラッシュ デバイス:** TI 評価基板のデフォルト フラッシュのいずれでもない場合は、カスタム フラッシュを選択します。

2. **フラッシュ名:** 使用中のフラッシュの名前 (*W25Q512JV* など) を書き込みます。

3. **プロトコル:** フラッシュがサポートしているプロトコルのいずれかを選択します。これにより、それぞれコマンド、アドレス、およびデータに使用する行数が設定されます。また、データレート (DDR (デュアル データレート) または SDR (シングル データレート)) も指定します。たとえば、**4S-4D-4D** は、コマンド、アドレス、およびデータにそれぞれ 4 ラインが使用されることを意味します。コマンドでは、データは立ち上がりエッジ / 立ち下がりエッジのいずれかでラッピングされますが、アドレスとデータでは、データは立ち上がりエッジと立ち下がりエッジの両方でラッピングされます。

図 4-2. 基本フラッシュ設定

図 4-3 の説明:

1. **フラッシュ JEDEC メーカー ID:** この値は、特定のメーカーで同じです。

2. **フラッシュ JEDEC デバイス ID:** この値は、同じメーカーのフラッシュ バリエントによって異なります。たとえば、Winbond フラッシュは、それぞれ 1.8V と 3.6V で動作するフラッシュのデバイス ID が異なります。フラッシュ部品が変動する他のパラメータもあり、フラッシュのデータシートに記載されています。

3. **ダミー クロック (CMD) とダミー クロック (読み取り):** ダミー クロックは、フラッシュ読み取りの同期に使用されます。これらの値は、フラッシュのデータシートからも取得できます。「ダミー サイクル」「ダミー クロック」というセクションを参照してください。なお、このフィールドには、OSPI コントローラの終端で設定される値が指定されます。フラッシュの終了時にダミー サイクル / クロック値を設定するには、フラッシュ構成レジスタに書き込む必要があります。ダミー サイクルの構成フィールドを参照してください。

4. **クワッド イネーブル タイプ:** 一部の QSPI フラッシュには、QE (クワッド イネーブル) ビットがあります。1S-1S-4S、4S-4S-4S、4S-4D-4D などのプロトコルでは、このビットを有効にする必要があります。

5. **QPI シーケンスと OPI シーケンス:** 4-4-4 モードと 8-8-8 モードをそれぞれ有効にするには、これらのフィールドを使用します。

6. フラッシュのブロック サイズとセクタ サイズについては、フラッシュのデータシートを参照してください。同じコマンドは診断ログから取得できますが、データシートから確認することをお勧めします。

7. **SysConfig** を使用すると、ユーザーはセクタ サイズとブロック サイズを設定できます。フラッシュが異なるセクタ / ブロック サイズをサポートしている場合、ユーザーはアプリケーションに基づいて特定のセクタ / ブロック サイズを指定できます。

8. (3B) および (4B) とは、フラッシュの 3 バイトと 4 バイトのアドレッシング モードを指します。これは基本的に、送信が必要なアドレス バイトの数を指定します。16MB 未満のフラッシュの場合、フラッシュ領域全体に対応するのに十分なアドレッシングは 3 バイトだけです。

| Basic Flash Configuration     |          |

|-------------------------------|----------|

| Flash Size In Bytes           | 67108864 |

| Flash Page Size In Bytes      | 256      |

| Flash JEDEC Manufacturer ID   | 0x34     |

| Flash JEDEC Device ID         | 0x5B1A   |

| Erase Configurations          |          |

| Flash Block Size In Bytes     | 262144   |

| Flash Sector Size In Bytes    | 4096     |

| Block Erase CMD (3B)          | 0xDC     |

| Block Erase CMD (4B)          | 0xDC     |

| Sector Erase CMD (3B)         | 0x21     |

| Sector Erase CMD (4B)         | 0x21     |

| Protocol Enable Configuration |          |

| Read Command                  | 0xEE     |

| Write/Page Program Command    | 0x12     |

| Mode Clocks (CMD)             | 0        |

| Mode Clocks (READ)            | 0        |

| Dummy Clocks (CMD)            | 4        |

| Dummy Clocks (READ)           | 21       |

| Quad Enable Type              | 0        |

| Octal Enable Type             | 0        |

| QPI Sequence                  | 0x00     |

| OPI Sequence                  | 0x00     |

図 4-3. 基本的なフラッシュ消去とプロトコル構成

図 4-4 の説明:

- プロトコル構成:** プロトコルは通常、コマンド、アドレス、データに使用される行数を指定します。特定のプロトコルでフラッシュを動作させるには、このセクションに記入する必要があります。

- ダミー サイクル構成:** フラッシュが特定のプロトコルで動作するには、フラッシュ構成レジスタでダミー サイクルを構成する必要があります。これはフラッシュのサイド設定であり、**OSPI** コントローラの設定はフィールドの **ダミー クロック (読み取り)** で定義されます。

- STR/DTR の構成:** これは、フラッシュを **SDR/DDR** モードで動作させるために設定できます。

**Protocol Configuration**

|                               |                                     |

|-------------------------------|-------------------------------------|

| Config Is Using Addressed Reg | <input checked="" type="checkbox"/> |

| Address Of Config Reg         | 0x00800006                          |

| CMD To Read Config Reg        | 0x65                                |

| CMD To Write To Config Reg    | 0x71                                |

**Register Data**

**Dummy Cycle Configuration**

**STR/DTR Configuration**

図 4-4. プロトコル、ダミー サイクル、STR/DTR 構成

図 4-5 の説明:

よく理解しましょう。構成レジスタの値は 10111101b とします。ビット [5:2] を 1001b で更新する必要がある場合、データシフトビット、データバイナリマスク、書き込むデータの値は、それぞれ 2、0x3C、9 になります。元の値 10111101b では、ロジック (値 & ~ (データバイナリマスク)) でマスク操作が行われます。この結果、値は 10000001b となります。これで、シフト動作が (値 | (書き込むデータ << データシフトビット)) として実行されます。最終的な値は 10100101b になり、構成レジスタに書き込まれます。

**Register Data**

|                    |      |

|--------------------|------|

| Data Shift Bits    | 0    |

| Data Binary Mask   | 0x01 |

| Data To Be Written | 1    |

図 4-5. レジスタ データ フィールドの構成

図 4-6 の説明:

フィールドは自明です。フラッシュのデータシートは、正しい値の設定を参照してください。

**Advanced Flash Configuration**

**Flash Reset Type** ②

**Description**

Flashes support different types of software reset sequences to return the device to its default power-on state. Here 'x' can be 0 or 1.

000000 : Soft Reset Not Supported xxxx1 : Drive 0x0F on all 4 data wires for 8 clocks xxxx1x : Drive 0x0F on all 4 data wires for 10 clocks if device is in 4 byte addressing xxx1xx : Drive 0x0F on all 4 data wires for 16 clocks xx1xxx : Issue instruction 0xF0 x1xxxx : Issue 0x66 for reset enable, and 0x99 for reset

**Flash Device Busy Type** ②

**Description**

Flashes support different ways to poll the device's busy status. Two main ways supported as per JESD216D are:

- 1. Polling bit 7 of flag status register using 0x70 read command, bit value = 1 means ready

- 2. Legacy method of polling the status register RDSR bit 0 (WIP bit), bit value = 0 means ready

Choose the appropriate option for your flash. For most flashes it is option 2.

**図 4-6. 高度なフラッシュ構成**

**図 4-7 の説明:**

これらの値はすべて、フラッシュのデータシートに記載されています。フラッシュ データシートの「読み取りデバイス ID/ 読み取りメーカー ID トランザクション テーブル」を参照してください。

**JEDEC ID Read Configuration**

|                                      |                                   |

|--------------------------------------|-----------------------------------|

| Read ID CMD                          | <input type="text" value="0x9F"/> |

| Number Of Bytes To Read              | <input type="text" value="3"/>    |

| Number Of Dummy Cycles In Quad Mode  | <input type="text" value="0"/>    |

| Number Of Dummy Cycles In Octal Mode | <input type="text" value="4"/>    |

**図 4-7. JEDEC ID 読み取り構成**

**図 4-8 の説明:**

1. **WIP ビットおよび WEL ビット:**これらのビットは、フラッシュステータスレジスタの書き込み中および書き込みイネーブル ラッチ ビットを指します。

2. **4 バイトアドレッシング:**すでに説明したように、これはフラッシュのサイズが 16MB より大きい場合に必要であり、(4B)アドレッシング用の特定のコマンドをサポートしています。

3. **コマンド拡張タイプ:**送信されるコマンドが 0x9F と仮定します。したがって、次の場合:

- a. NONE: 0x9F が送信されます。

- b. REPEAT: 0x9F、0x9F が送信されます。

- c. INVERSE: 0x9F、0x60 (0x9F の逆数) が送信されます。

4. **Quirks 関数:**フラッシュの構成レジスタに追加の変更を実行するカスタム API を定義するために使用されます。現在、これは *Flash\_quirkSpanionUNHYSADisable* として定義されています。この機能は、基本的に、TI の評価基板に搭載されているフラッシュのハイブリッド モード (S28HS512T) を無効化します。

|                                                                                                                          |                                               |

|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Write Enable CMD                                                                                                         | 0x06                                          |

| Read Status Register CMD                                                                                                 | 0x05                                          |

| WIP Bit                                                                                                                  | 0                                             |

| WEL Bit                                                                                                                  | 1                                             |

| WIP Read CMD (xSPI)                                                                                                      | 0x65                                          |

| WIP Status Reg Addr (xSPI)                                                                                               | 0x00800000                                    |

| WIP Bit (xSPI)                                                                                                           | 0                                             |

| Chip Erase Command                                                                                                       | 0xC7                                          |

| Flash Busy Timeout                                                                                                       | 256000000                                     |

| Page Program Timeout                                                                                                     | 512                                           |

| Enable 4 Byte Addressing                                                                                                 | <input checked="" type="checkbox"/>           |

| <b>Four Byte Addressing</b>             |                                               |

| Supported Addressing Modes                                                                                               | 1                                             |

| 4 Byte Addressing Enable Sequence                                                                                        | 0xA1                                          |

| Command Extension Type                                                                                                   | REPEAT                                        |

| <b>Automatically Configure Flash</b>  |                                               |

| Load Flash Config From JSON                                                                                              | <input type="button" value="LOAD FROM JSON"/> |

| Quirks Function                                                                                                          | Flash_quirkSpansionUNHYSADisable              |

図 4-8. 高度なフラッシュ構成 (続き)

#### 4.1.1 推奨アプローチ

**MCU+ SDK** にはデフォルト例が含まれおり、以下のパスで確認できます: **MCU\_PLUS\_SDK\_INSTALL\_PATH/examples/drivers/ospi**。上記の例の 1 つが **OSPI フラッシュ IO** です。この例の詳細については、[こちら](#)を参照してください。

この例を正常に実行すると、消去、書き込み、読み取りというすべての基本的なフラッシュ動作が正しく機能していることを確認できます。また、コントローラとフラッシュ デバイスとの間のプロトコル構成が適切に設定されており、**SysConfig** で構成されたフラッシュ パラメータが期待どおりに動作していることも確認できます。

**OSPI フラッシュ IO** 例を使用して、フラッシュ パラメータとプロトコルの特定の組み合わせを検証した後、これらの検証済み設定は、**UART Uniflash**、**ブートローダー (SBL OSPI など)**、および類似のプロジェクトなど、他のアプリケーションで再利用できます。

要約すると、**OSPI フラッシュ IO** 例は、フラッシュ パラメータのテストおよび構成における信頼性の高いリファレンス ポイントとして機能し、このパラメータは複数のアプリケーションに適用できます。

## 4.2 OSPI のパラメータ

各パラメータについて、? をクリックすると記述について学ぶことができます。

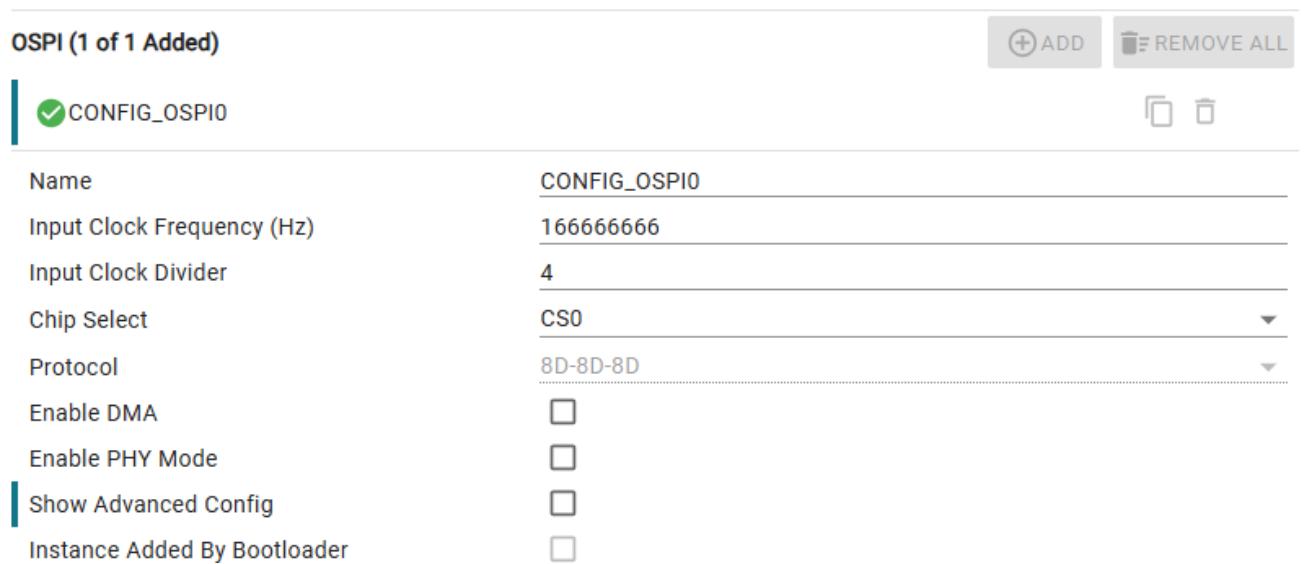

図 4-9 の説明:

1. **入力クロック周波数 (Hz):** これはリファレンス クロック周波数 (RCLK) です。

2. **入力クロック分周器:** これは、リファレンス クロック周波数を分周する分周器です。OSPI 出力クロック = 入力クロック周波数 / 入力クロック分周器。

3. **チップ セレクト:** デフォルトでは、CS0 は OSPI コントローラによって使用されます。

4. **プロトコル:** このフィールドは、FLASH セクションのプロトコルから入力されます。

5. **DMA の有効化:** DMA 転送は、トランザクション サイズが 1KB を超える場合に発生します。

6. **PHY モードの有効化:** PHY モードを有効化します (50MHz を超えるクロックの場合)。オフにすると、TAP モードが使用されます。

OSPI (1 of 1 Added)

CONFIG\_OSPI0

|                              |                          |

|------------------------------|--------------------------|

| Name                         | CONFIG_OSPI0             |

| Input Clock Frequency (Hz)   | 166666666                |

| Input Clock Divider          | 4                        |

| Chip Select                  | CS0                      |

| Protocol                     | 8D-8D-8D                 |

| Enable DMA                   | <input type="checkbox"/> |

| Enable PHY Mode              | <input type="checkbox"/> |

| Show Advanced Config         | <input type="checkbox"/> |

| Instance Added By Bootloader | <input type="checkbox"/> |

図 4-9. OSPI の構成

## 5 起動に関する一般的な問題とデバッグ

MCU+SDK を使用した FLASH 使用時の一般的な問題は、以下のとおりです。

### 5.1 ブート エラー

ROM が 3 バイトのアドレスを発行する際にブート エラーが発生し、フラッシュが 4 バイト アドレッシング モードのままになることがよく発生します。この詳細については、AM62P TRM の図 5-1 を参照してください。

**When using a OSPI\xSPI\QSPI\SPI flash device greater than 128Mb which supports 3-byte and 4-byte addressing modes, a flash device package with a RESET signal must be used. The reason is that the ROM only uses 3 byte addressing mode (address is 24bits). To address the full memory address range, software will typically switch to 4-byte addressing mode. If a reset to the processor occurs (eg, due to a warm reset), the ROM will execute expecting 3-byte addressing mode, but the flash will have been left in 4-byte addressing mode. In order for the flash device to return to 3-byte addressing mode, it must be reset using this signal. This typically can be achieved by using the RESET signal on the flash memory device. The ROM does not issue a software reset command.**

図 5-1. RESET 信号に関する AM62P TRM セクション

一部のシリアル NAND フラッシュは、フラッシュ内のパラメータ ページがオフセット 0x1 に存在しないため、シリアル NAND ブート モードで起動できません。シリアル NAND フラッシュの場合、シリアル NAND ブート モードで正常に起動するには、パラメータ ページがオフセット 0x1 に存在している必要があります。パラメータ ページのオフセットに関する情報は、フラッシュのデータシートから取得できます。

シリアル NOR フラッシュの場合は、必ずブート モードの記述にあるコマンドを確認してください。これについては、「[ブート モードとフラッシュの互換性について](#)」で説明しています。

QSPI NOR フラッシュを使用する場合、起動するための一般的なブート モードは、QSPI ブート モードです。なお、QSPI ブート モードの場合は、ブート モードの記述とフラッシュのデータシートに一致すること以外は、QE ビットをチェックする必要があります。QE はクワッド イネーブル ビットです。ROM が 1S-1S-4S を正しく発行するには、ROM がこのビットを設定していないため、QSPI フラッシュに QE ビットがすでに設定されている必要があります。QSPI フラッシュがあり、このフラッシュには工場出荷時にデフォルトで QE ビットが設定されています。QE ビットが設定されていないフラッシュの場合は、QSPI ブート モードで起動する前に QE ビットを設定することを TI は推奨します。

### 5.2 既知のエラッタ

TI の Sitara プロセッサの一部には、ブートとフラッシュ書き込みに関する既知のエラッタがあります。プロセッサ固有のエラッタへのリンクについては、[参考資料](#)を参照してください。

1. i2351: すべての TI Sitara™ プロセッサ。

2. i2307: AM64x, AM62x プロセッサ。

3. i2366: AM62Ax, AM64x, AM62Dx, AM62x プロセッサ。

4. i2420: AM62Ax, AM64x, AM62Dx, AM62x プロセッサ。

5. i2189: すべての TI Sitara プロセッサ。

6. i2249: すべての TI Sitara プロセッサ。

7. i2383: すべての TI Sitara プロセッサ。

### 5.3 フラッシュ初期化エラー

場合によっては、Flash\_norOspiOpen 関数内でハングが発生することがあります、ほとんどの場合、**FLASH open failed for instance 0 !!!** というログが出力されます。これは、フラッシュが正しく初期化されていないことを示します。この手順を実行するには、次のヒントを参照してください。

#### 5.3.1 FLASH と OSPI の SysConfig の値

OSPI および FLASH の値を再度参照し、値が誤って書き込まれているかどうかを確認します。

### 5.3.2 フラッシュ デバイスとメーカー ID の読み取りエラー

読み取り ID エラーをデバッグするには、次の [FAQ \(よくある質問\)](#) を参照してください。

### 5.3.3 PHY エラー

PHY チューニングには 2 種類の障害があります。[Enable PHY Mode \(PHY モードの有効化\)](#)をチェックすると、これら 2 つの障害が発生するおそれがあります。この作業を開始する前に、[OSPI PHY チューニング](#)と [PHY チューニングの攻撃ベクトル](#)について説明します。

1 つ目は「PHY enabling failed!!! Continuing without PHY...」エラー、2 つ目は、OTP (最適チューニング ポイント) の計算エラーです。1 つ目は、攻撃ベクトルがフラッシュ書き込みされたものの、正しく読み取れない場合に発生します。したがって、この場合はセクション [5.3.1](#) と [5.3.2](#) のポイントに戻ります。2 つ目のは、PHY チューニング アルゴリズムがエラーを返す場合に発生します。これをデバッグするには、次の手順を検討します。

1. デフォルトでは、`flash_nor_ospi.c` ファイルでは `OSPI_phyTuneDDR` が呼び出されます。使用するプロトコルが STR で構成されている場合は、関数 `OSPI_phyTuneSDR` を呼び出す必要があります。

2. PHY チューニング エラーをデバッグするために、TI は PHY チューニング グラフを生成することを推奨します。[こちらにある FAQ \(よくある質問\)](#) を参照してください。PHY 障害時に、このグラフを基準として使用することで OTP ポイントのマーキングが行われている場所を確認できます。

### 5.4 フラッシュの読み取りエラー

フラッシュの読み取りエラーが発生する場合があります。これらの利点は以下のとおりです。

1. OSPI コントローラが DAC 状態のときに、特定のアドレス範囲を使用してフラッシュの内容をマッピングします。利用可能なアドレス範囲を [図 5-2](#) に示します。デフォルトでは `0x60000000` が選択されています。読み取りエラーは、MPU 領域 `0x60000000` が **cached** (キャッシュ済み) としてマークされている場合に発生します。これは、フラッシュの直接メモリ マッピングに使用される領域です。ソフトウェアでこれを実現するには、レジスタ `0xFC40000` の 7<sup>th</sup> ビット、DAC ビットを 1 に設定します。その結果、`0x60000000` を「**Cached**」としてマークする必要はありません。

2. 構成済みのプロトコルに対する **SysConfig** で設定された読み取りコマンドは正しくありません。一部のフラッシュでは、3 バイトと 4 バイトのアドレッシングに対して異なる読み取りコマンドがあります。

3. フラッシュ上のデータが `00h 01h 02h 03h...`、バッファ内の読み取り値が `01h 02h 03h 04h...` であるとします。これは、セクション [5.3.1](#) で、読み取り用のダミー クロックが値 1 でオフになっていることを示します。

4. DMA 関連の問題には、読み取りバッファがキャッシュ アライメントされていないためにデータが正しく読み取れないことが含まれます。

| Address Range                          | Size   | Description                      |

|----------------------------------------|--------|----------------------------------|

| <code>0x400000000 - 0x4FFFFFFF</code>  | 4 GB   | External Memory Space (Region 0) |

| <code>0x060000000 - 0x067FFFFFF</code> | 128 MB | Boot Space (Region 1)            |

| <code>0x500000000 - 0x5FFFFFFF</code>  | 4 GB   | External Memory Space (Region 3) |

図 5-2. FSS メモリ領域

### 5.5 フラッシュ プログラム エラー

フラッシュの消去および書き込みエラーは、次の理由で発生します。

1. 書き込み動作が発行されるセクタまたはブロックは、書き込み動作の前に消去されません。

2. 構成済みのプロトコルに対する **SysConfig** で設定された書き込み / 消去コマンドは正しくありません。一部のフラッシュには、3 バイトと 4 バイトのアドレッシングに対して異なるコマンドがあります。

3. フラッシュ プログラムとフラッシュ ビジー タイムアウトの定義が低すぎます。

4. [図 5-2](#) で説明したように、デフォルトで選択されたアドレス範囲 `0x60000000` は、**Cached** (キャッシュ済み) でなく、**Strongly Ordered** (厳密な順序付け) としてマークされている必要があります。領域を **Cached** としてマークすると、書き込みに失敗します。

## 6 OSPI および FLASH のサポートを要求するためのチェックリスト

OSPI/FLASH 関連の質問を [TI E2E™ フォーラム](#) に投稿する前に、以下の質問を確認すると参考になります。

1. どの TI プロセッサを使用していますか？

2. どの MCU+SDK バージョンを使用していますか？

3. カスタム ボードと TI の評価基板のどちらでテストを実施しましたか？

4. カスタム フラッシュ部品に名前を付け、データシートを添付してください。

5. SysConfig の値は、フラッシュ データシートで検証済みですか？

6. [こちら](#)のデバッグ ガイドに従って、エラー ログまたはエラー ポイントを共有してください。

7. このアプリケーション ノートから、テスト基板で観測されたエラーに類似する特定のセクションを指摘してください。

## 7 まとめ

本アプリケーション ノートは、MCU+ SDK を使用して、カスタム xSPI フラッシュ デバイスを TI Sitara プロセッサに統合する開発者向けの実用的なデバッグ リファレンスを提供します。この資料では、ブート エラー、フラッシュの読み取り / 書き込み / 消去に関する問題、デバイスの起動に関する全体的な課題を診断および解決するための体系的な方法について概要を説明しています。ステップバイステップのチェック、構成ガイドライン、および検証のヒントが記載されており、エンジニアが根本原因を迅速に特定し、カスタム DUT でシステムを立ち上げるのに役立ちます。本ガイドは、一般的なエラーシナリオと実証済みのデバッグ ワークフローを整理することで、統合に対する労力を削減し、カスタム NOR または NAND フラッシュの信頼性の高い動作を実現することを目的としています。

## 8 参考資料

1. テキサス インスツルメンツ、『[AM62Px Sitara プロセッサ](#)』データシート。

2. テキサス インスツルメンツ、『[AM62Px MCU+ SDK](#)』。

3. インフィニオン テクノロジーズ、『[S28HS512T](#)』データシート。

4. テキサス インスツルメンツ、『[AM62Px Sitara プロセッサ テクニカルリファレンス マニュアル](#)』テクニカルリファレンスマニュアル。

5. テキサス インスツルメンツ、『[AM62x プロセッサ シリコン](#)』エラッタ。

6. テキサス インスツルメンツ、『[AM62Dx Sitara プロセッサ シリコン エラッタ](#)』エラッタ。

7. テキサス インスツルメンツ、『[AM64x/AM243x プロセッサ シリコン](#)』エラッタ。

8. テキサス インスツルメンツ、『[AM62L Sitara プロセッサ シリコン エラッタ](#)』エラッタ。

9. テキサス インスツルメンツ、『[AM62A プロセッサ シリコン エラッタ](#)』エラッタ。

10. テキサス インスツルメンツ、『[AM62P Sitara プロセッサ シリコン エラッタ](#)』エラッタ。

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月