*Application Note***AM62x オーディオシステムの設計ガイド****概要**

テキサス インスツルメンツのプレミアムオーディオアプリケーション向けオーディオ DSP SoC は、マルチチャネルオーディオシリアルポート (McASP) を搭載しています。McASP の構成オプションは非常に柔軟で、各種のマルチゾーンおよびマルチチャネルオーディオシステムを実現できます。この資料では、デジタルオーディオ形式、McASP 構成オプション、一般的なシステム実装の概要を説明します。

**この資料の使い方**

この資料は、オーディオデータの送信、TI のオーディオペリフェラル、これらのペリフェラルをマルチゾーンオーディオシステムで使用する方法に関する基本レベルの情報を提供することを目的としています。この資料はオーディオシステム設計の基礎について説明しています。最初に、デジタルオーディオの送受信方法、およびさまざまなシステムの使用事例を実現する McASP 構成について詳細に説明しています。

| 章の概要                                             | 章のリンク                   |

|--------------------------------------------------|-------------------------|

| McASP でサポートされるデジタルオーディオ形式の基本的な説明                 | <a href="#">セクション 1</a> |

| McASP ペリフェラルの基本的概要と、使用可能なさまざまな構成オプション            | <a href="#">セクション 2</a> |

| さまざまな使用事例における McASP インスタンスの AM62x 固有の実装に関する詳細な説明 | <a href="#">セクション 3</a> |

| McASP のレイアウト設計に関する 2 つの最大の検討事項の説明                | <a href="#">セクション 4</a> |

| 外部コンポーネントを含む実用的な使用事例における McASP のさまざまな構成例         | <a href="#">セクション 5</a> |

| 主なオーディオシステム設計の考慮事項                               | <a href="#">セクション 6</a> |

**目次**

|                                                       |    |

|-------------------------------------------------------|----|

| この資料の使い方.....                                         | 1  |

| 1 デジタルオーディオ形式.....                                    | 2  |

| 1.1 I <sup>2</sup> S.....                             | 3  |

| 1.2 TDM.....                                          | 3  |

| 2 McASP の概要.....                                      | 4  |

| 3 AM62x デバイスに対する McASP 接続.....                        | 6  |

| 3.1 McASP の一般的な構成.....                                | 7  |

| 3.1.1 クロックコントローラとしての McASP.....                       | 8  |

| 3.1.2 クロックペリフェラルとしての McASP.....                       | 10 |

| 4 McASP レイアウトの考慮事項.....                               | 11 |

| 4.1 ブートモードロジックと共有される McASP 信号.....                    | 11 |

| 4.2 シングルクロックドメイン内の複数デバイスの McASP トポロジ.....             | 12 |

| 5 McASP の実例.....                                      | 13 |

| 5.1 2 つのクロックドメインで AUDIO_EXT_REFCLK を使用したオーディオ再生 ..... | 13 |

| 5.2 外部クロックソースと McASP SYNC モードを使用するオーディオ再生.....        | 14 |

| 6 主なオーディオシステム設計の考慮事項.....                             | 15 |

| 7 参考資料.....                                           | 16 |

**商標**

すべての商標は、それぞれの所有者に帰属します。

## 1 デジタルオーディオ形式

デジタルオーディオデータは3線形式で通信されます。オーディオ転送に必要な3つの信号は、ビットクロック、フレーム同期、シリアルオーディオデータです。複数のオーディオスロットがデータのフレームに含まれています。单一のバスでマルチチャネルオーディオを送信するため、オーディオチャネルは固有のスロットに割り当てられます。单一のオーディオデータフレームには、転送される各チャネルのための单一のサンプルが含まれています。さまざまなデジタルオーディオ形式により、オーディオデータのフレームがデバイス間で編成および転送される方法が定義されます。一般に、すべてのオーディオフレーム形式は以下の特性によって定義されます：

- フレーム同期の立ち下がりまたは立ち上がりエッジがフレームの開始を示す

- フレーム同期エッジとデータ転送間の遅延

- フレーム同期幅

- フレームあたりの固有のオーディオチャネル数

- チャネルあたりのスロットサイズ(ビット単位)

- スロットあたりのワード深度(ビット単位)

- ビットストリームの順序(MSBまたはLSBファースト)

- サンプリングオーディオデータ用ビットクロック極性

### 注

デジタルオーディオの信号には多くの一般的な名称があります。フレーム同期(FS)はLRCLK、WCLK、またはワード選択とも呼ばれます。ビットクロックはシリアルクロックまたはオーディオクロックとも呼ばれます。この資料では、フレーム同期とビットクロックの標準的な名称を使用しています。

オーディオのスロットには、合計スロットビット幅より小さいワードが含まれる場合があります。ワード深度がスロットサイズより小さい場合、ワードはスロットの左側またはスロットの右側に整列される場合があります。整列オプションが異なるため、オーディオデータを解釈するためにビットをパディングする方法を完全に理解することが重要です。

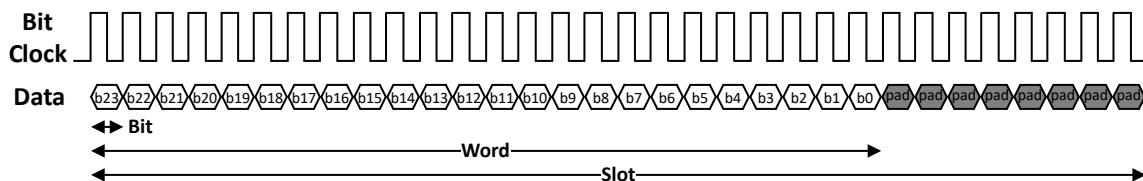

図1-1は、MSBファーストのシリアルビットストリーム、24ビットのワード深度(左に整列)、32ビットのスロットサイズを持つ、オーディオスロットの例を示しています。

図1-1. フレーム内のビット、ワード、スロット

## 1.1 I<sup>2</sup>S

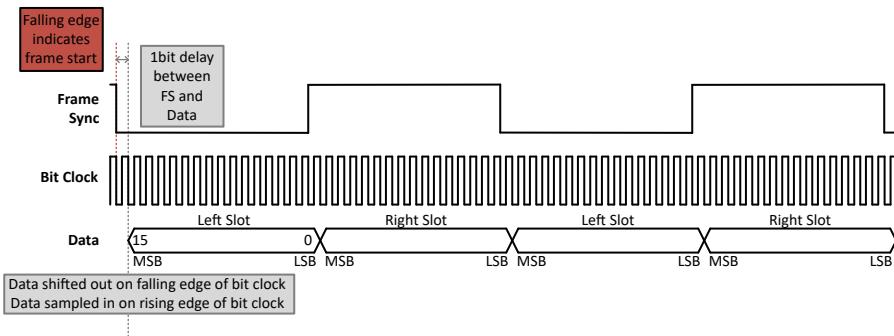

IC 間サウンド (I<sup>2</sup>S) は、ステレオオーディオ専用に定義された標準的なデジタルオーディオプロトコルです。ステレオオーディオとは、各デジタルオーディオフレームが左右の 2 つのチャンネルで構成されることを意味します。I<sup>2</sup>S フレームは次の特性で定義されます：

- フレーム同期の立ち下がりエッジがフレームの開始を示す

- フレーム同期立ち下がりエッジとデータ転送間の 1 ビットクロックサイクルの遅延

- シングルワードフレームの同期幅

- フレームごとに 2 チャンネル

- MSB ファーストのシリアルビットストリームの順序

- ビットクロック立ち下がりエッジでのデータシフトアウト

- ビットクロック立ち上がりエッジでのデータサンプリング

図 1-2. I<sup>2</sup>S タイミング図

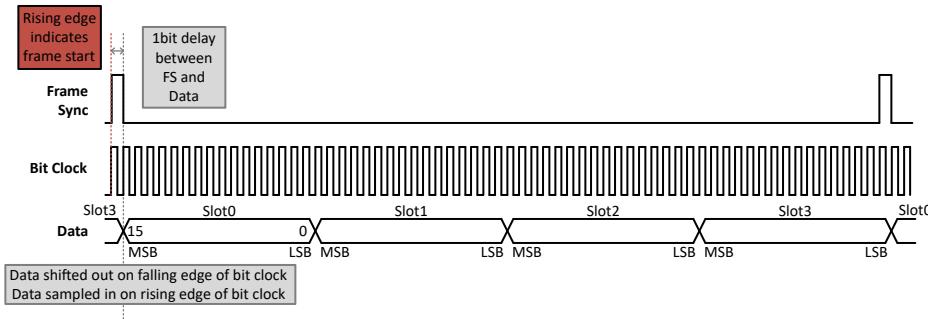

## 1.2 TDM

時分割多重 (TDM) は、マルチチャネルオーディオ転送の標準デジタルオーディオプロトコルです。通常、TDM の後に TDM4 などのオーディオフレームごとのチャネル数を示す数値が続きます。TDM には標準形式がありませんが、標準的な TDM フレームは以下の特性で定義されます：

- フレーム同期の立ち上がりエッジがフレームの開始を示す

- フレーム同期立ち上がりエッジとデータ転送間の 1 ビットクロックサイクルの遅延

- シングルビットフレームの同期幅

- MSB ファーストのシリアルビットストリームの順序

- ビットクロック立ち下がりエッジでのデータシフトアウト

- ビットクロック立ち上がりエッジでのデータサンプリング

図 1-3. TDM4 タイミング図

## 2 McASP の概要

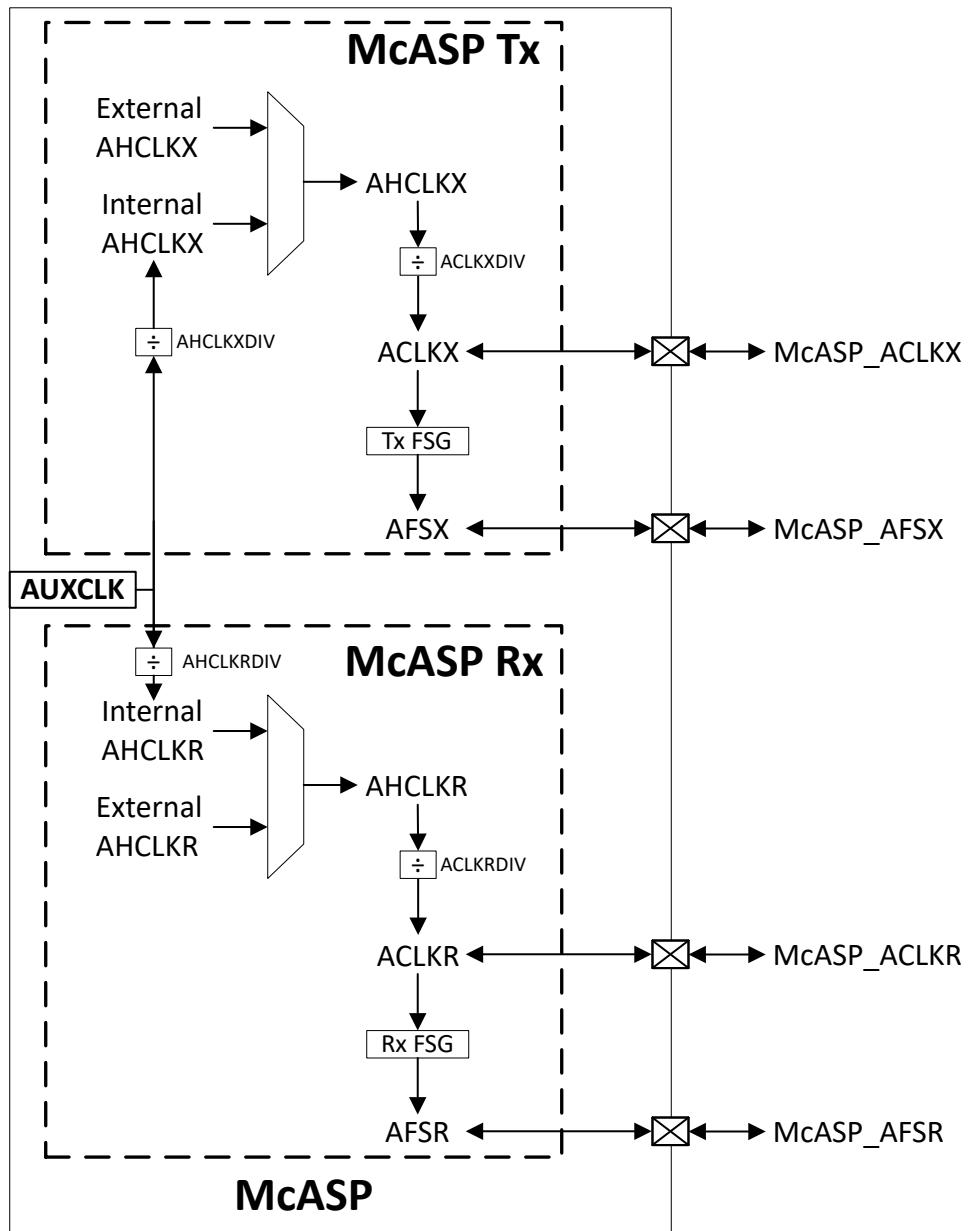

マルチチャネルオーディオシリアルポート (McASP) は、マルチチャネルおよびマルチゾーンのオーディオ通信を最適化するために設計されました。McASP ペリフェラルは、送信および受信のビットクロック (ACLK[X/R]) の信号、送信および受信フレーム同期 (AFS[X/R])、最大 16 のオーディオ送信/受信シリアルライザ (AXR) で構成されます。McASP にはルートクロックを供給するための内部バスとプログラマブル分周器が搭載され、ビットクロックとフレーム同期の適切な周波数を生成するために使用できます。McASP には 1 つの AUXCLK があり、内部送信の生成および高周波クロック (AHCLK[X/R]) の受信に使用できます。高周波クロックは、ビットクロックとフレーム同期を内部生成するために使用されます。または、外部ソースからビットクロックおよび/またはフレーム同期を受信するように McASP を構成できます。

図 2-1. McASP の一般的な概要

各 McASP は以下の機能をサポートしています：

- 独立したクロックゾーンを使用するオーディオデータの送受信

- オーディオ送受信 (AXR) のための最大 16 のシリアルライザ

- McASP インスタンスごとのシリアルライザ数は、SoC の実装に応じて異なります。

- たとえば、AM62x では、McASP2 は 16 のシリアルライザすべてを使用できますが、McASP0 は 4 つのシリアルライザのみ使用できます。

- 送信および受信動作用シリアルライザごとの 32 ビットバッファ

- クロック損失検出

- オーディオフレーム形式の構成オプション

- スロット数

- スロットサイズ (ビット)

- スロットサイズより小さいアクティブワード深度のビットマスク

- アクティブスロットのマスキング

- ビットクロックサイクルに関するデータ遅延に対するフレーム同期

- フレーム同期の極性および幅

- ビットクロックの極性

- シリアルデータビットストリームの順序

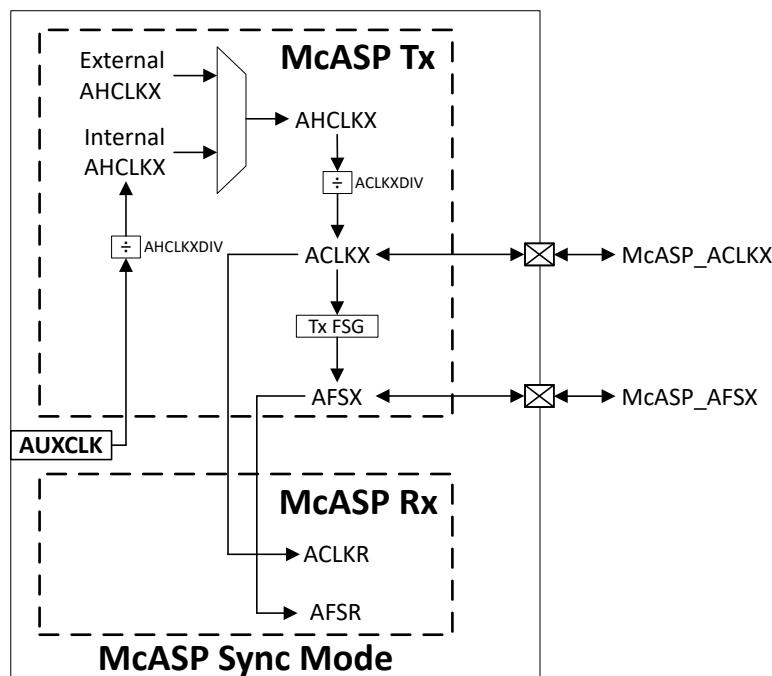

各 McASP は、ACLKX と AFSX が ACLKR と AFSR に内部配線される同期モードでも動作します。同期モードでは、データの送受信用のクロックドメインが 1 つのコードックなどの使用事例を実現できます。

McASP が非同期モードである場合、シリアルライザの IO 方向によって、オーディオデータフレームの解釈に使用するビットクロックとフレーム同期が決定されます。

図 2-2. McASP 同期モード

### 3 AM62x デバイスに対する McASP 接続

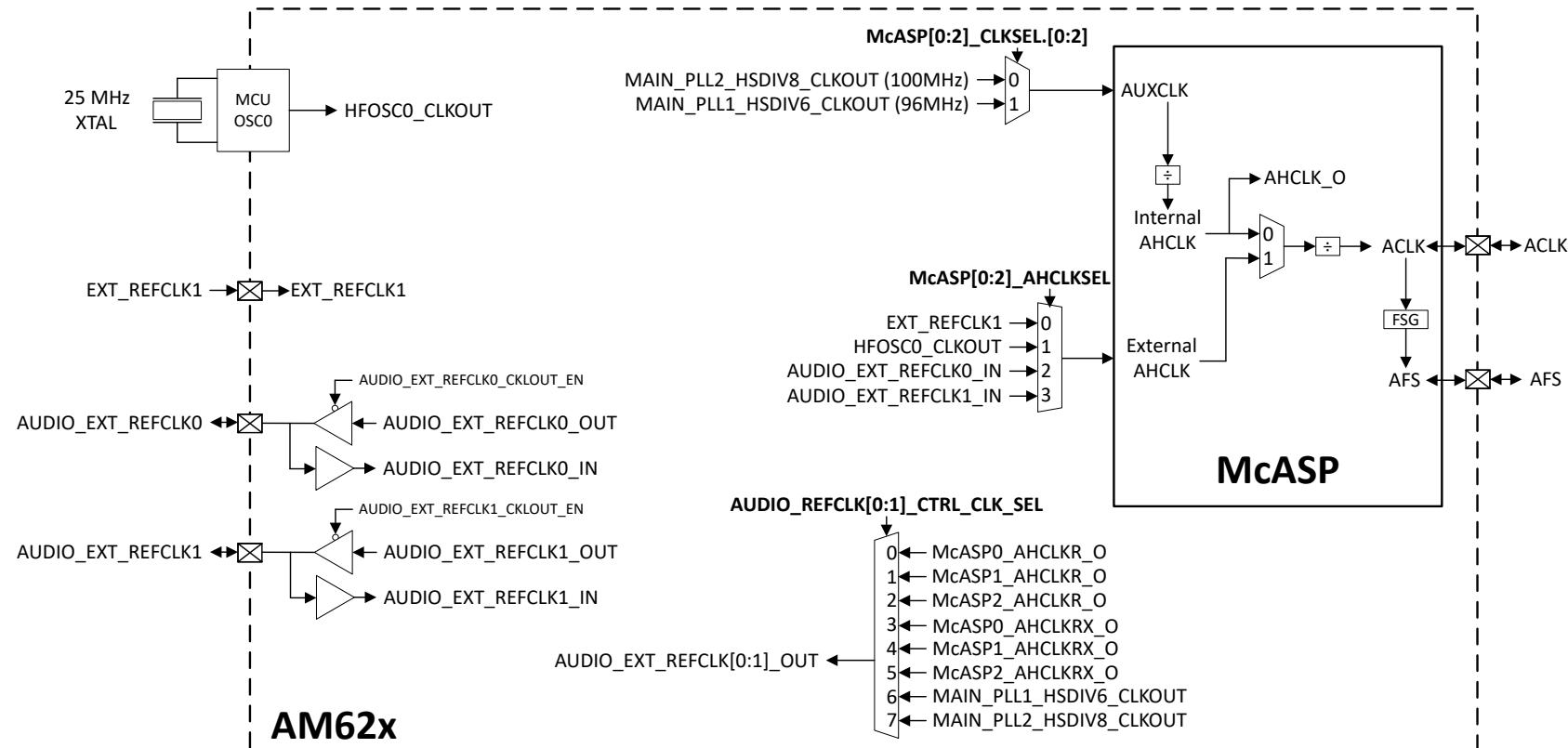

AM62x は、オーディオアプリケーション用の 3 つの固有の McASP を搭載した Arm ベースプロセッサファミリです。図 3-1 は、AM62x デバイス上の McASP のための内部接続の全体的なマッピングを示しています。

注

各 McASP には送信および受信クロックゾーンに独立した ACLK と AFS がありますが、AUXCLK は 1 つのみです。

図 3-1. AM62x McASP の接続

### 3.1 McASP の一般的な構成

McASP ビットクロック (ACLK) とフレーム同期 (AFS) はどちらも双方方向であり、McASP はクロックコントローラまたはクロックペリフェラルのいずれかにすることが可能です。以下のセクションでは、各クロック構成で利用できる、すべてのオプションについて詳しく説明します。

表 3-1 は、McASP の構成で最も一般的な使用事例を示しています。AM62x SoC には、オーディオデータフレーム形式用クロックの、生成、ソース、受信のための多くのオプションがあります。

注

ビットクロックとフレーム同期では、**内部生成**とは McASP クロックコントローラアプリケーションのために SoC レベルで出力される内部リファレンス信号を意味し、**外部生成**とは McASP クロックペリフェラルアプリケーションのために SoC レベルの入力として信号が構成されることを意味します。

表 3-1. McASP 使用事例の行列

| 説明                                     | AHCLK                                                             | ビット クロック | フレーム同期 | McASP                         | 例                     |

|----------------------------------------|-------------------------------------------------------------------|----------|--------|-------------------------------|-----------------------|

| オーディオ PLL リファレンス内蔵 McASP クロックコントローラ    | AM62x デバイスには、オーディオビットクロックとフレーム同期周波数生成用のオーディオ PLL リファレンスを内蔵していません。 |          |        |                               |                       |

| 外部 AUXCLK リファレンスを使用する McASP クロックコントローラ | AM62x デバイスには、外部クロックソースを McASP AUXCLK に配線するオプションがあります              |          |        |                               |                       |

| 外部 AHCLK リファレンスを使用する McASP クロックコントローラ  | 外部生成                                                              | 内部生成     | 内部生成   | <a href="#">セクション 3.1.1.1</a> | <a href="#">図 5-1</a> |

| McASP クロックペリフェラル                       |                                                                   | 外部生成     | 外部生成   | <a href="#">セクション 3.1.2</a>   | <a href="#">図 5-2</a> |

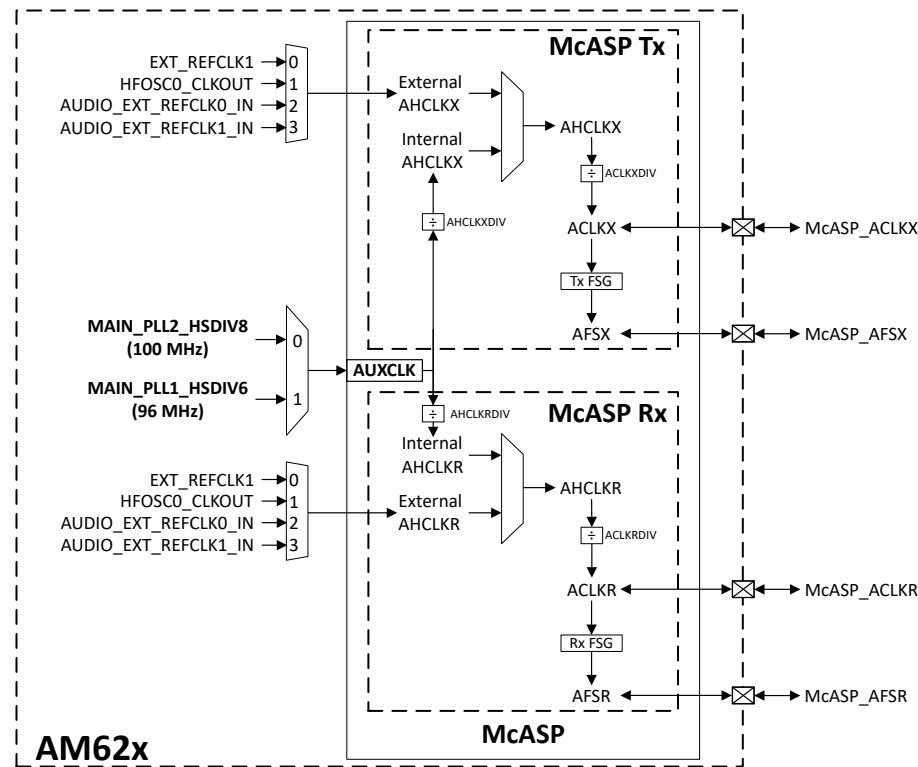

図 3-2 は使用可能なオプションの詳細を示しています。

図 3-2. McASP の詳細の概要

### 3.1.1 クロックコントローラとしての McASP

McASP をクロックコントローラとして構成する場合、ビットクロック信号とフレーム同期信号は出力として構成されます。ソースが内部生成に設定されるとき、SDK ドライバはビットクロックとフレーム同期を出力として定義します。つまり、ビットクロックが High クロックから内部生成され、ビットクロックに基づいてフレーム同期が生成されます。TX または RX ドメインの High クロックには、オーディオシステム要件に最適な多くのオプションが搭載されています。

AUXCLK は、TX と RX 両方のドメインに供給できる單一クロックリファレンスです。AM62x デバイスの McASP AUXCLK 入力は、100MHz および 96MHz 用の内部 PLL 出力に接続されます。

**注**

AM62x AUXCLK 入力にはオーディオ周波数入力がないため、AM62x デバイスでは AUXCLK (および内部生成の AHCLK) を使用しないでください。

AHCLK が内部生成される場合は、AHCLK を高周波リファレンス用の AUDIO\_EXT\_REFCLK ピンのいずれかの出力として配線できます。

**注**

AHCLK を AUDIO\_EXT\_REFCLK の出力として使用するには、AUXCLK をリファレンスとして AHCLK を内部生成するように AHCLK を構成する必要があります。そのため、大半のアプリケーションでは、AHCLK を AM62x デバイスの AUDIO\_EXT\_REFCLK の出力として選択できません。

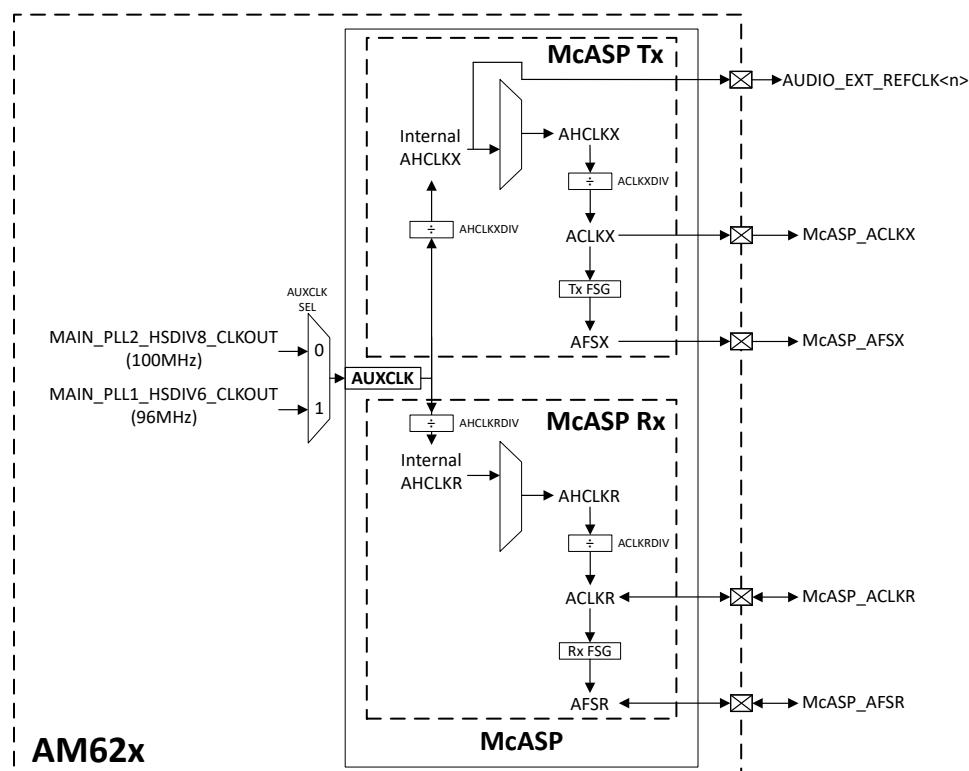

図 3-3. AUXCLK ソースを使用する McASP コントローラ

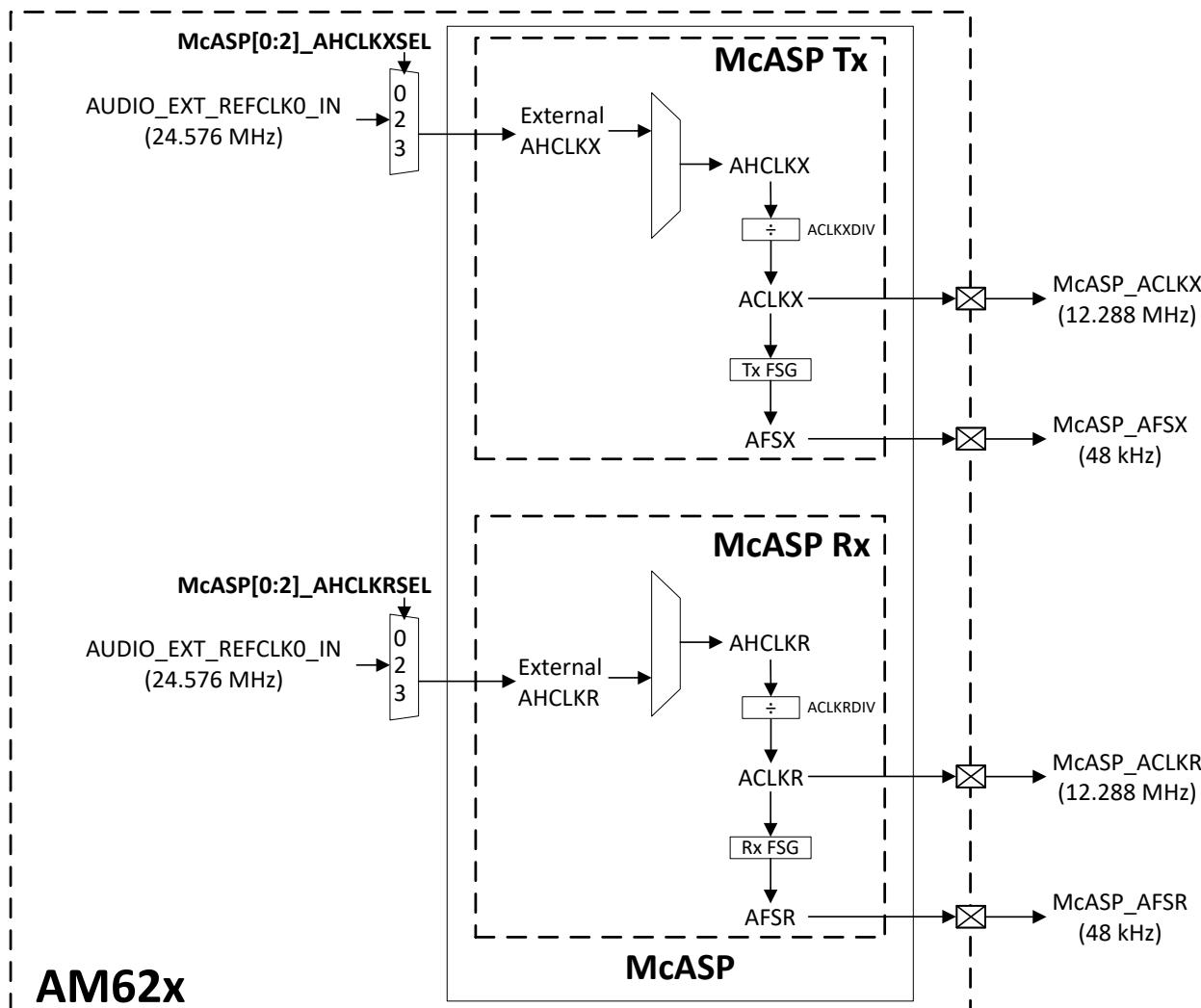

### 3.1.1.1 AUDIO\_EXT\_REFCLK AHCLK ソースを使用して生成されるクロック

以下のセクションでは、McASP のセットアップ例について詳しく説明しています。ビットクロックとフレーム同期は、出力として構成され、AUDIO\_EXT\_REFCLK を介した外部ソースを使用して AHCLK に対する直接のリファレンスクロックとして生成されます。

| 説明                                      | AHCLK | ビット クロック | フレーム同期 |

|-----------------------------------------|-------|----------|--------|

| 外部 AHCLK 入力リファレンスを使用する McASP クロックコントローラ | 外部生成  | 内部生成     | 内部生成   |

この例では、McASP は 48kHz フレーム同期と 32 ビットワードの TDM8 フレーム形式に構成されており、12.288MHz のビットクロック周波数が得られます。AHCLK が外部生成されるように構成されている場合、AUXCLK は考慮されません。各 AHCLK には、異なる外部ソースを選択するための固有のマルチプレクサがあります。AHCLK マルチプレクサは、外部ドライバからの AUDIO\_EXT\_REFCLK0 ソース 24.576MHz を指定するように構成されています。SDK ドライバは、スロット数、フレーム同期周波数、フレーム同期と AHCLK の間の比率に基づいて ACLK 分周器を設定します。

AHCLK が外部生成される場合、AHCLK は AUDIO\_EXT\_REFCLK に出力できません。

図 3-4. AUDIO\_EXT\_REFCLK0 AHCLK リファレンスを使用する McASP クロックコントローラ

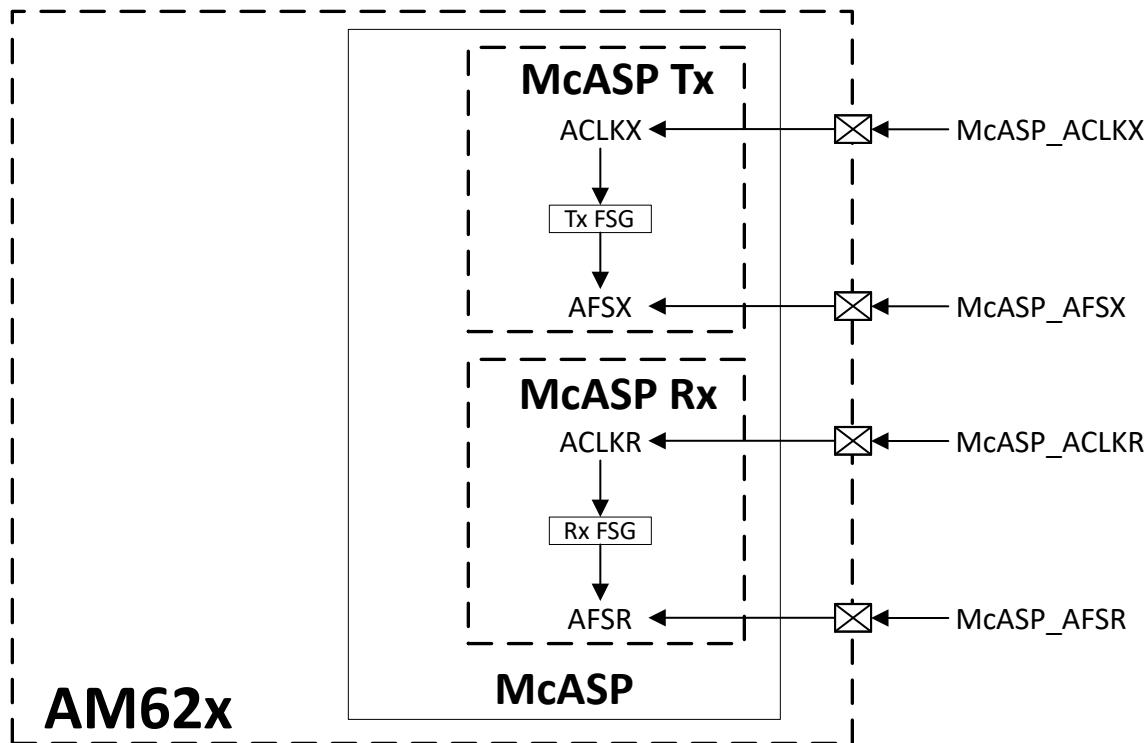

### 3.1.2 クロックペリフェラルとしての McASP

以下のセクションでは、ビットクロックとフレーム同期を入力として構成する McASP のセットアップ例について詳しく説明します。

| 説明               | AHCLK | ビット クロック | フレーム 同期 |

|------------------|-------|----------|---------|

| McASP クロックペリフェラル |       | 外部生成     | 外部生成    |

この例では、McASP は 48kHz フレーム同期と 32 ビットワードの TDM8 フレーム形式に構成されており、12.288MHz のビットクロック周波数が得られます。この場合、AHCLK 設定は重要ではありません。オーディオデータを適切に転送するには、ビットクロックとフレーム同期の想定周波数を表すように SDK ドライバを構成する必要があります。

図 3-5. McASP クロックペリフェラル

## 4 McASP レイアウトの考慮事項

McASP は、単一のクロックドメインを使用して複数のオーディオデバイスと同時に接続できるように設計されています。ただし、レイアウトの実装方法に応じて、クロック信号とデータ信号の信号品質が影響を受けることがあります。この章では、AM62x デバイス上の McASP における、2 つの非常に重要なレイアウト上の考慮事項について説明します。

### 注

レイアウトの実装パラメータにかかわらず、McASP 信号レイアウトのシミュレーションを常に実行して、クロック信号とデータ信号がデータシートのタイミング要件を満たしていることを確認する必要があります。

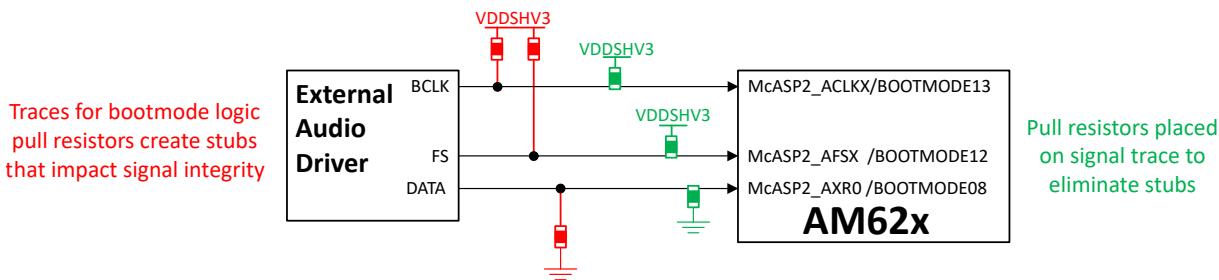

### 4.1 ブートモードロジックと共有される McASP 信号

AM62x には 16 のブートモード信号があり、ブートや他のブート構成パラメータに使用するペリフェラルを決定するため、ROM で使用されます。16 のブートモード信号は SoC の特定のパッドに接続され、AM62x はブートモードパッド用の McASP2 インターフェイスパッドの大半を使用します。

各ブートモードのパッドには、電源投入シーケンス中に関連するブートモード信号のデジタルロジック High または Low 状態を定義する、外部プルアップまたはプルダウン抵抗が必要です。

McASP2 信号はブートモードロジックと共有されるため、以下の内容を確認することは非常に重要です：

- McASP2 インターフェイスに接続されるオーディオデバイスには、最初の電源投入時またはリセット時にブートモード信号を駆動できません。たとえば、AM62x に PORz がアサートされる場合、ブートシーケンスが完了するまで McASP2 オーディオデバイスもリセット状態に保持する必要があります。

- 電源投入時またはリセット時にブートモードロジックに外部ドライバが存在すると、予測不能なブートモード状態が発生します。

- 外付けプル抵抗を信号パターンと直列に配置して、スタブを取り込まないようにする必要があります。[図 4-1](#) はパターンスタブがある、またはない場合のプル抵抗の例を示しています。設計時には、緑色の実装を再現する必要があります。

- スタブによって信号反射が発生するとタイミング誤差や信号歪みが生じる可能性があるため、信号パターン上のスタブ、特にビットクロックはオーディオデータの信頼性に影響を及ぼします。

図 4-1. McASP 信号パターンのスタブ

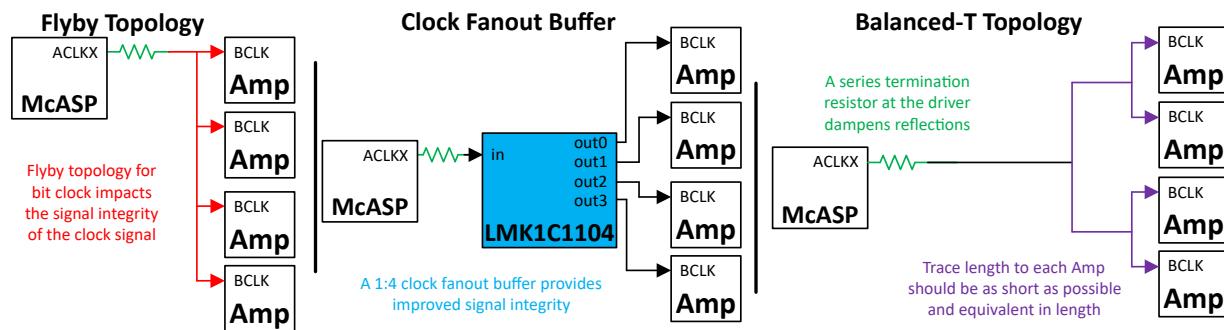

## 4.2 シングルクロックドメイン内の複数デバイスの McASP トポロジ

多くのオーディオデバイスが单一のクロックドメインを共有するシステムでは、多くの場合 McASP が設計されます。たとえば、TAS6754 は TDM16 をサポート可能な 4 チャネルアンプです。つまり、单一の McASP のビットクロック、フレーム同期、データピンを最大 4 つのアンプで共有できます。これら 3 つの信号のレイアウト設計は、インターフェイスの性能と信頼性に影響を与えます。

図 4-2 は、ビットクロック信号を 4 つの異なるアンプに接続する 3 つの異なる信号トポロジを示しています。

- フライバイトポロジを使用する場合、バス上の各ドロップで作成するパターンスタブは、長さを統一して、反射を低減するためだけ短くする必要があります。クロック周波数とパターン長によっては、このトポロジでは信号品質の問題が発生する可能性があります

- 複数のデバイスでクロック信号を共有するには、LMK1C1104 などのクロックファンアウトバッファの使用を推奨します。クロックをリドライブすると、ファンアウトバッファにより、ポイントツーポイントパターンの性能に近い信号品質のクロック信号が生成されます。

- 平衡 T またはスタートポロジでは、各デバイスの長さが等しくなるよう単一バスを分岐させます。作成される分岐は、デバイスに対して作成されたスタブの長さを等しくして、できるだけ短くする必要があります。

### 注

トポロジにかかわらず、信号の反射を抑制して信号品質を維持するために、すべての McASP 信号の直列終端抵抗をドライバの近くに配置することが推奨されています。

図 4-2. マルチデバイスオーディオシステム向けクロックトポロジ

## 5 McASP の実例

### 5.1 2つのクロックドメインで AUDIO\_EXT\_REFCLK を使用したオーディオ再生

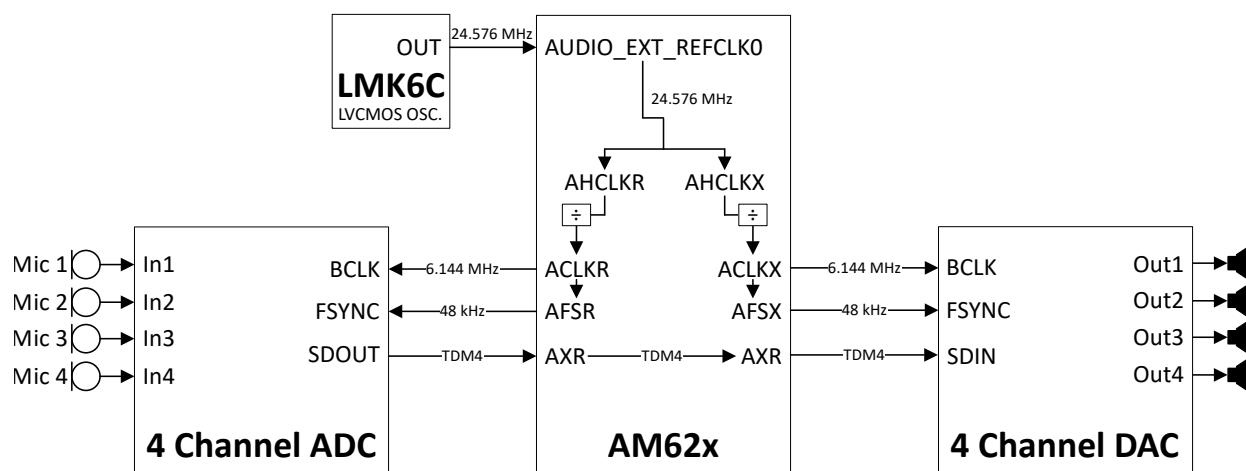

図 5-1 に、McASP で单一の内部リファレンスを使用し複数のドメイン間でオーディオデータを送受信する方法の簡単な例を示します。McASP は非同期モードで動作しますが、送信ドメインと受信ドメインのルートクロックソースが同じであるため、(入力と出力でオーディオデータフレームの形式が同じである限り) バッファのオーバーランまたはアンダーランのリスクがありません。

このシステムでは、外部 LVC MOS 発振器 (LMK6CE024576 など) を使用して 24.576MHz のオーディオクロック周波数を生成します。この場合、TX ドメインと RX ドメインの両方で、AHCLK が (AUDIO\_EXT\_REFCLK0 から) 外部生成されるように構成されており、ACLK と AFS は内部生成されるように構成されています。

オーディオデータフレームは単一の TDM4 ストリーム用の 4 つのオーディオチャネルで、ワード深度が 32 ビットであると仮定すると、 $48\text{kHz} = 4 * 32 * 48,000 = 6.144\text{MHz}$  でサンプリングされる、32 ビットワードの 4 チャネルの積に基づきビットクロックを計算できます。

図 5-1. ADC DAC のオーディオ再生

## 5.2 外部クロックソースと McASP SYNC モードを使用するオーディオ再生

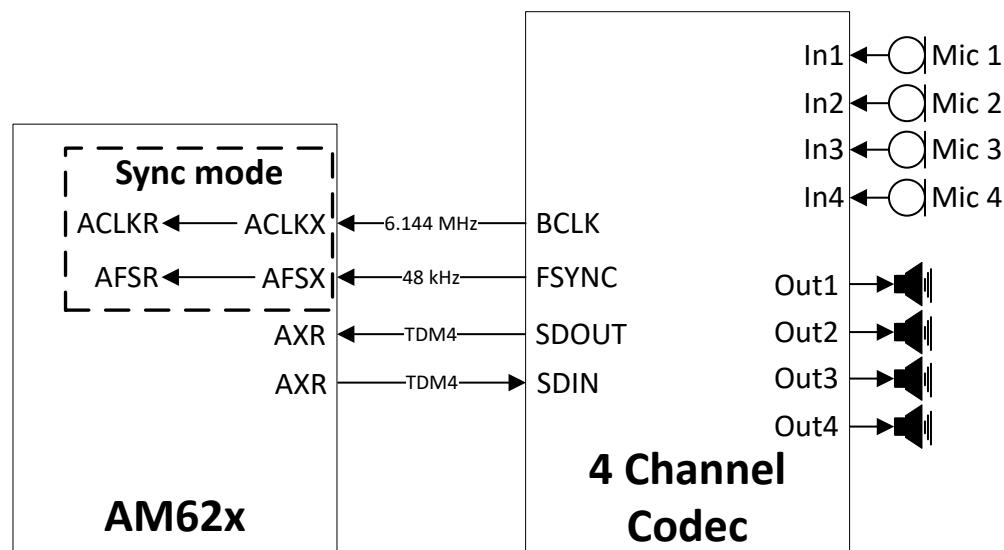

図 5-2 に、McASP が单一クロックリフレンスのみでオーディオデータを送受信する簡単な例を示します。McASP は同期モードで動作しています。つまり、送信ビットのクロックとフレーム同期はそれぞれ受信ビットのクロックとフレーム同期に内部で配線されます。RX ドメインの内部配線を使用すると、すべてのオーディオデータストリームのフレーム形式が同じである限り、単一の McASP インスタンスでオーディオデータの入力および出力用シリアルライザを使用できます。

このシステムでは、4 チャネルコーデックがビットクロックとフレーム同期の両方のクロックコントローラとなります。TX と RX のドメインは SYNC モードで、ACLK と AFS が外部生成されるように構成しています。ビットクロックとフレーム同期が外部生成される場合、AHCLK は動作に必須でないため、「無視できる」値を考えることができます。

オーディオデータフレームは単一の TDM4 ストリーム用の 4 つのオーディオチャネルで、ワード深度が 32 ビットであると仮定すると、 $48\text{kHz} = 4 * 32 * 48,000 = 6.144\text{MHz}$  でサンプリングされる、32 ビットワードの 4 チャネルの積に基づきビットクロックを計算できます。

図 5-2. 同期モードのクロックペリフェラルとして McASP を使用するコーデック再生

## 6 主なオーディオシステム設計の考慮事項

- McASP にはクロック同期用の以下の 2 つの動作モードがあります:

- 同期モード: ACLKX と AFSX の信号は ACLKR と AFSR に内部で配線され、すべてのオーディオデータは单一クロックドメインで送受信されます。

- 非同期モード: TX と RX のクロックドメインは互いに独立しており、オーディオデータのクロックドメインはシリアルアイザの IO 方向により決定されます。

- マルチゾーンオーディオシステムは、オーディオデータのバッファリングに関連する問題を防ぐため、生成されるすべてのビットクロックとフレーム同期に最適な 1 つのクロックリファレンスを備えています。AM62x デバイスでは、クロックリファレンスを外部ソースから供給する必要があります。

- McASP は、AUDIO\_EXT\_REFCLK 入力を内部リファレンスとするよう構成、またはビットクロックとフレーム同期を外部生成するよう構成する必要があります。

- 外部ソースにデバイスレベルの高周波数リファレンスがない場合は、同じリファレンスを使用する他の McASP インスタンスをイネーブルするために、ビットクロックも AUDIO\_EXT\_REFCLK 入力に配線する必要があります。

- McASP 信号と共有しているすべてのブートモード信号を注意深く確認し、クロック信号ラインまたはデータ信号ラインに不要なパターンスタブが導入されないことを確認します。

- 複数のデバイスでクロック信号とデータ信号を共有している場合は、レイアウトポロジが信号の性能に影響しないようにしてください。

- 常に提案されたレイアウトポロジで信号をシミュレーションして、オーディオデータ転送の信頼性と整合性を確保します。

## 7 参考資料

- [AM62D-Q1 信号処理マイクロプロセッサ](#)

- [AM62D-Q1 信号処理マイクロプロセッサデータシート](#)

- [AM62D-Q1 信号処理マイクロプロセッサテクニカルリファレンスマニュアル](#)

- [AM620-Q1 信号処理マイクロプロセッサ](#)

- [AM620-Q1 信号処理マイクロプロセッサデータシート](#)

- [AM620-Q1 信号処理マイクロプロセッサテクニカルリファレンスマニュアル](#)

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月