*Application Note***AM275x オーディオ システムの設計ガイド**

Erik Friedel

**概要**

プレミアム オーディオ アプリケーション向けの TI のオーディオ DSP SoC は、マルチチャネル オーディオ シリアル ポート (McASP) を搭載しています。McASP は非常に柔軟な構成オプションにより、各種のマルチゾーンおよびマルチチャネル オーディオ システムを実現できます。このドキュメントでは、デジタル オーディオ フォーマット、McASP 構成オプション、一般的なシステム実装の概要を説明します。

**このドキュメントの使い方**

このドキュメントは、オーディオ データ送信、TI オーディオ ペリフェラル、これらのペリフェラルをマルチゾーン オーディオ システムで使用する方法を基本レベルで理解することを目的としています。このドキュメントでは、オーディオ システム設計の基礎を説明します。最初に、デジタル オーディオの送受信方法を詳細に説明し、それを McASP と ASRC 構成に適用して、さまざまなシステムの使用事例を取り上げます。

| 章の概要                                             | 章のリンク                   |

|--------------------------------------------------|-------------------------|

| McASP でサポートされているデジタル オーディオ フォーマットの基本的な説明         | <a href="#">セクション 1</a> |

| McASP ペリフェラルの基本的な概要および使用可能なさまざまな構成オプション          | <a href="#">セクション 2</a> |

| 各種の使用事例における AM275x 固有の McASP インスタンスの実装に関する詳細な説明  | <a href="#">セクション 3</a> |

| McASP のレイアウト設計における 2 つの最も重要な検討事項                 | <a href="#">セクション 4</a> |

| 柔軟性の向上を目的としたモジュール実装における ASRC モジュールの基本概要          | <a href="#">セクション 5</a> |

| 外部コンポーネントを扱う実際の使用事例における McASP および ASRC のさまざまな構成例 | <a href="#">セクション 6</a> |

| オーディオ システムの設計に関する重要ポイント                          | <a href="#">セクション 7</a> |

**目次**

|                                                |    |

|------------------------------------------------|----|

| このドキュメントの使い方.....                              | 1  |

| 1 デジタル オーディオ フォーマット.....                       | 2  |

| 1.1 I <sup>2</sup> S.....                      | 3  |

| 1.2 TDM.....                                   | 3  |

| 2 McASP の概要.....                               | 4  |

| 3 AM275x の McASP 接続.....                       | 6  |

| 3.1 一般的な McASP 構成.....                         | 6  |

| 3.1.1 クロック コントローラとしての McASP.....               | 8  |

| 3.1.2 クロック ペリフェラルとしての McASP.....               | 12 |

| 4 McASP レイアウトに関する検討事項.....                     | 14 |

| 4.1 ブート モード ロジックと共有される McASP 信号.....           | 14 |

| 4.2 単一のクロック ドメインの複数のデバイスでの McASP トポロジ.....     | 15 |

| 5 ASRC の概要.....                                | 16 |

| 6 McASP の実例.....                               | 18 |

| 6.1 2 つのクロック ドメイン用の内部オーディオ PLL によるオーディオ再生..... | 18 |

| 6.2 外部クロック ソースと McASP 同期モードによるオーディオ再生.....     | 19 |

| 6.3 2 つのクロック ドメインをブリッジする ASRC によるオーディオ再生.....  | 20 |

| 7 オーディオ システムの設計に関する重要ポイント.....                 | 21 |

| 8 参考資料.....                                    | 22 |

**商標**

すべての商標は、それぞれの所有者に帰属します。

## 1 デジタルオーディオフォーマット

デジタルオーディオデータは3線式の形式通信されます。オーディオ送信に必要な3つの信号は、ビットクロック、フレーム同期、シリアルオーディオデータです。複数のオーディオスロットが、1フレームのデータに含まれています。オーディオチャネルは、1つのバスでマルチチャネルオーディオを送信するために、固有のスロットに割り当てられます。単一のオーディオデータフレームには、転送される各チャネルに1つのサンプルが含まれています。さまざまなデジタルオーディオフォーマットは、オーディオデータフレームがデバイス間でどのように編成され転送されるかを定義します。一般的に、すべてのオーディオフレームフォーマットは次の特性によって定義されます。

- フレーム開始を示すフレーム同期の立ち下がりエッジまたは立ち上がりエッジ

- フレーム同期エッジとデータ送信の間の遅延

- フレーム同期幅

- フレームあたりの固有オーディオチャネル数

- チャネルあたりのビット数のスロットサイズ

- ワード深度(スロットあたりのビット数)

- ビットストリーム順序(MSBまたはLSBファースト)

- オーディオデータサンプリング用のビットクロック極性

### 注

デジタルオーディオの信号には多くの一般名があります。フレーム同期(FS)は、LRCLK、WCLK、ワード選択とも呼ばれます。ビットクロックは、シリアルクロックまたはオーディオクロックとも呼ばれます。このドキュメントでは、フレーム同期とビットクロックの標準的な名称を使用します。

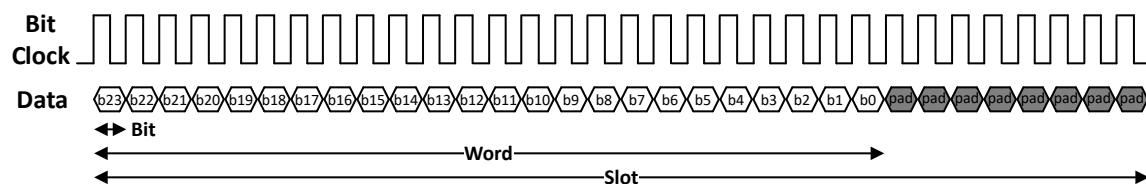

オーディオのスロットには、合計スロットビット幅よりも小さいワードを含めることができます。ワード深度がスロットサイズより小さい場合、ワードはスロットの左側またはスロットの右側に整列できます。整列オプションが異なるため、オーディオデータを解釈するためにビットがどのようにパディングされるかを完全に理解することが重要です。

図1-1に、MSBファーストシリアルビットストリーム、24ビットのワード深度(左揃え)、および32ビットのスロットサイズを持つオーディオスロットの例を示します。

図1-1. フレームのビット、ワード、スロット

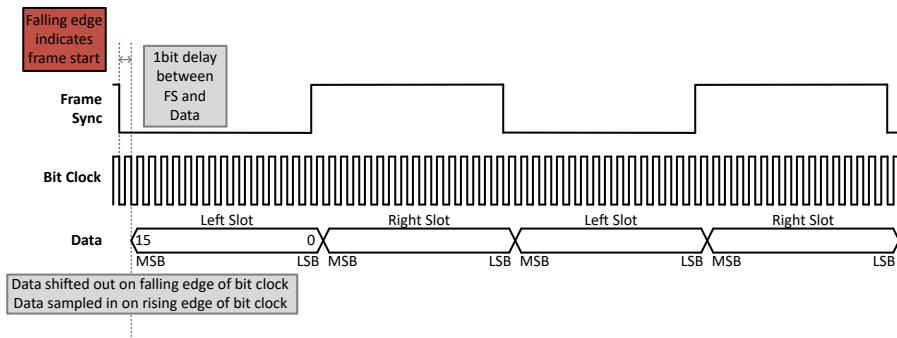

## 1.1 I<sup>2</sup>S

インタ IC サウンド (I<sup>2</sup>S) は、ステレオ オーディオ専用に定義された標準的なデジタル オーディオ プロトコルです。ステレオ オーディオとは、各デジタル オーディオ フレームが左右 2 つのチャンネルで構成されていることを意味します。I<sup>2</sup>S フレームは、次の特性で定義されます。

- フレーム開始を示すフレーム同期の立ち下がりエッジ

- フレーム同期立ち下がりエッジからデータ送信までの 1 ビットクロック サイクル遅延

- シングル ワード フレーム同期幅

- フレームごとに 2 チャンネル

- MSB ファーストシリアルビットストリームの順序

- ビットクロックの立ち下がりエッジでのデータのシフトアウト

- ビットクロックの立ち上がりエッジでサンプリングされるデータ

図 1-2. I<sup>2</sup>S タイミング図

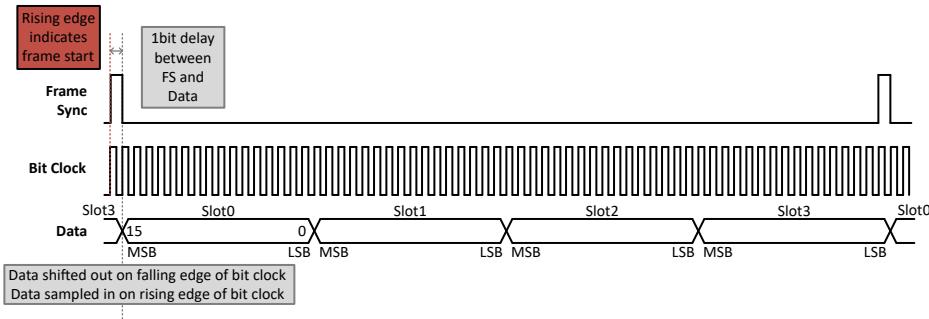

## 1.2 TDM

時分割多重 (TDM) は、マルチチャネル オーディオ転送用の標準的なデジタル オーディオ プロトコルです。通常、TDM の後には、TDM4 などのオーディオ フレームごとのチャネル数を示す数値が続きます。TDM は標準化されたフォーマットではありませんが、標準的な TDM フレームは以下の特性で定義されます。

- フレーム開始を示すフレーム同期の立ち上りエッジ

- フレーム同期立ち上がりエッジからデータ送信までの 1 ビットクロック サイクル遅延

- シングル ビット フレーム同期幅

- MSB ファーストシリアルビットストリームの順序

- ビットクロックの立ち下がりエッジでのデータのシフトアウト

- ビットクロックの立ち上がりエッジでサンプリングされるデータ

図 1-3. TDM4 タイミング図

## 2 McASP の概要

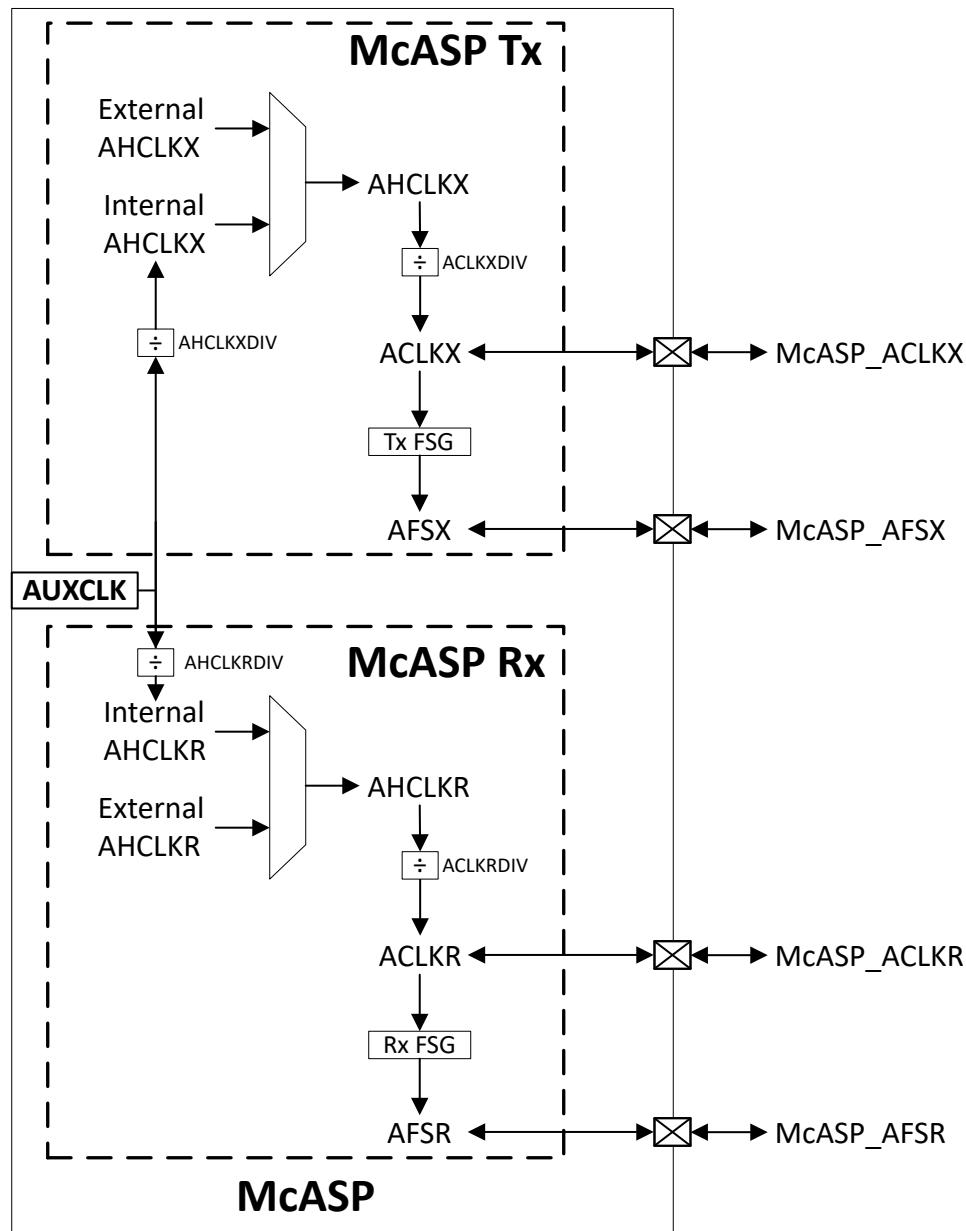

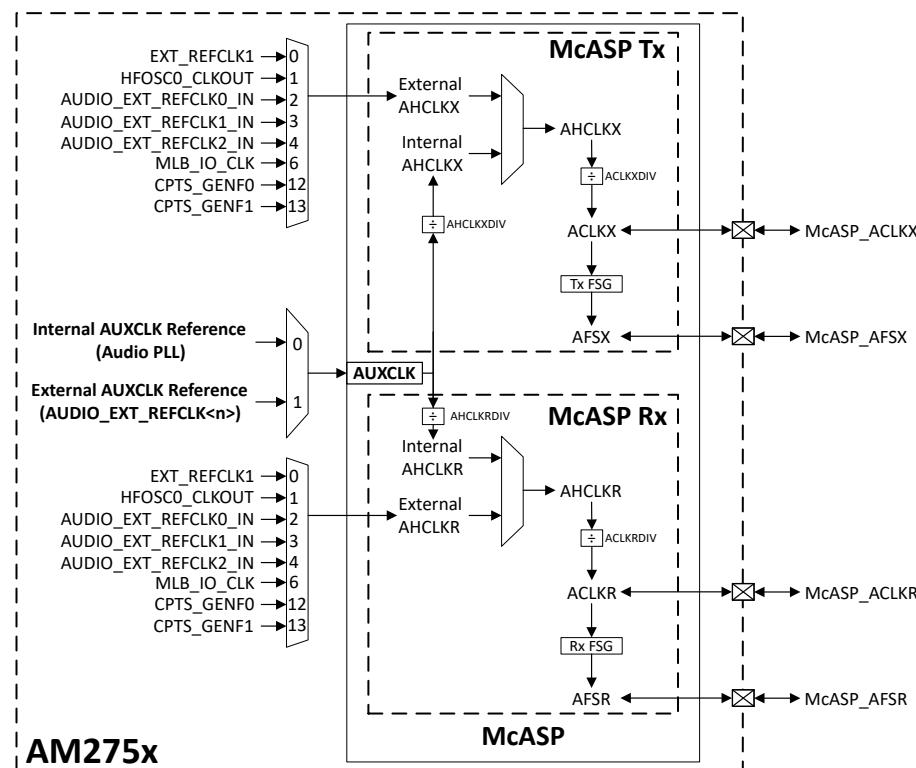

マルチチャネル オーディオシリアルポート (McASP) は、マルチチャネルおよびマルチゾーンのオーディオ通信を最適化するように設計されています。McASP ペリフェラルは、送信と受信ビットクロック (ACLK[X/R]) の信号、送信と受信フレーム同期 (AFS[X/R])、および最大 16 個のオーディオ送信 / 受信シリアルライザ (AXR) で構成されています。McASP には、ルートクロックを供給するための内部パスとプログラマブル分周器もあり、ビットクロックとフレーム同期の適切な周波数を生成するために使用できます。McASP には 1 つの AUXCLK があり、内部送信および受信高周波クロック (AHCLK[X/R]) の生成に使用できます。高周波クロックは、ビットクロックとフレーム同期を内部で生成するために使用されます。または、McASP を外部ソースからビットクロックやフレーム同期を受信するように構成することもできます。

図 2-1. McASP の一般的な概要

各 McASP は以下の機能をサポートしています。

- 独立したクロックゾーンによるオーディオデータの送受信

- オーディオ送受信(AXR)用の最大16個のシリアルライザ

- McASPインスタンスごとのシリアルライザ数は、SoCの実装によって異なります。

- たとえば、AM275xでは、McASP0は16個のシリアルライザをすべて使用できますが、McASP4では6個のシリアルライザのみを使用できます。

- 送信と受信動作用のシリアルライザごとの32ビットバッファ

- クロック損失検出

- オーディオフレームフォーマットの構成オプション

- スロット数

- スロットサイズ(ビット単位)

- スロットサイズより小さいアクティブワード深度のビットマスキング

- アクティブスロットマスキング

- ビットクロックサイクルによるフレーム同期からデータまでの遅延

- フレーム同期極性と幅

- ビットクロック極性

- シリアルデータビットストリームの順序

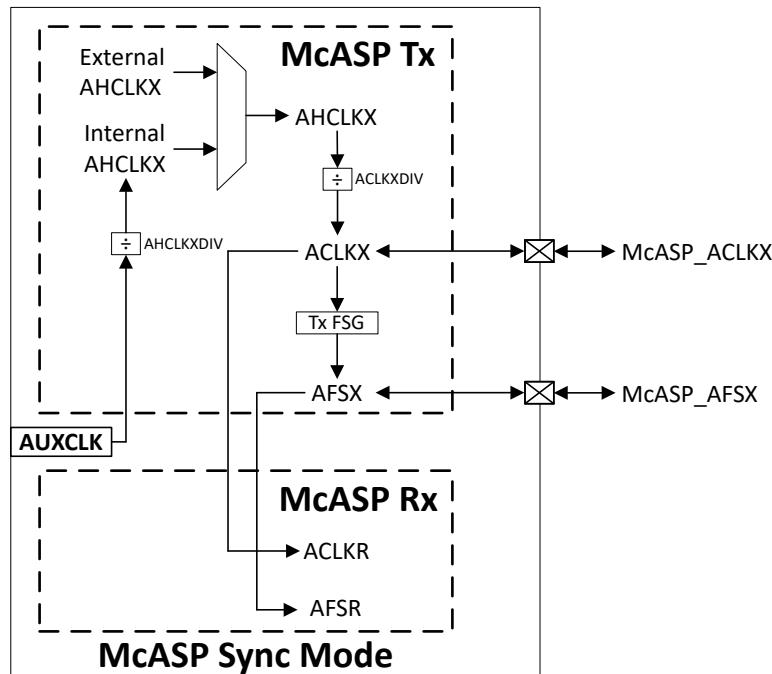

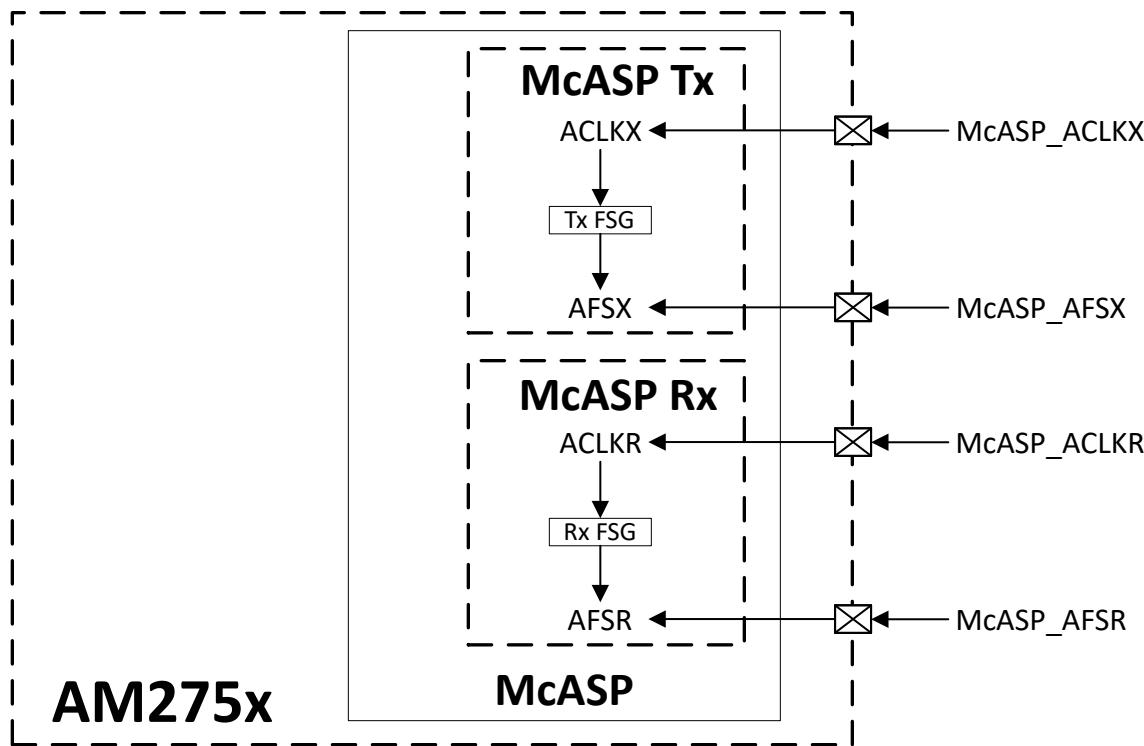

各McASPは、ACLKXとAFSXがACLRとAFSRに内部で配線される同期モードでも動作できます。同期モードは、データの送受信用に1つのクロックドメインを持つコーデックなどの使用事例を可能にします。

McASPが非同期モードの場合、シリアルライザのIO方向によって、オーディオデータフレームの解釈に使用されるビットクロックとフレーム同期が決定されます。

図 2-2. McASP 同期モード

### 3 AM275x の McASP 接続

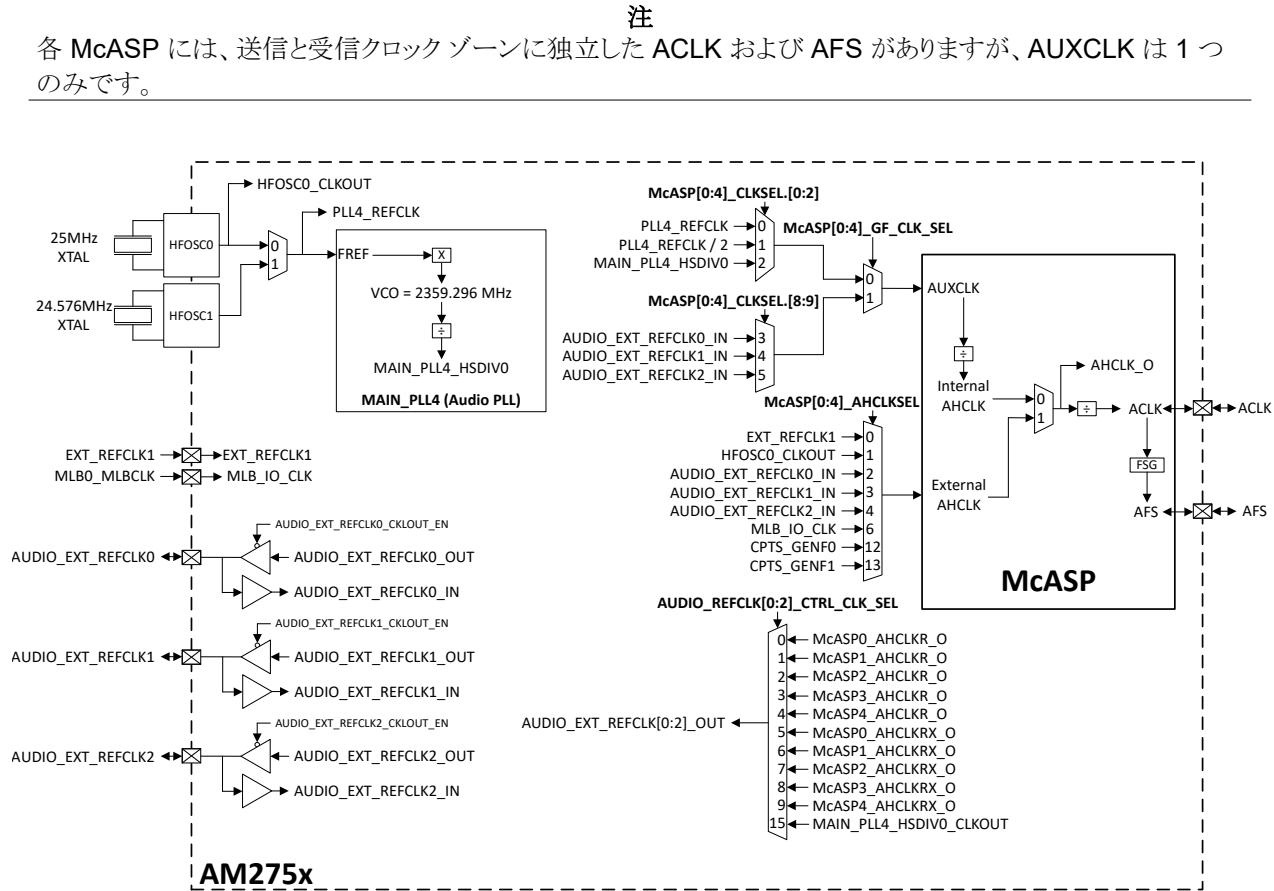

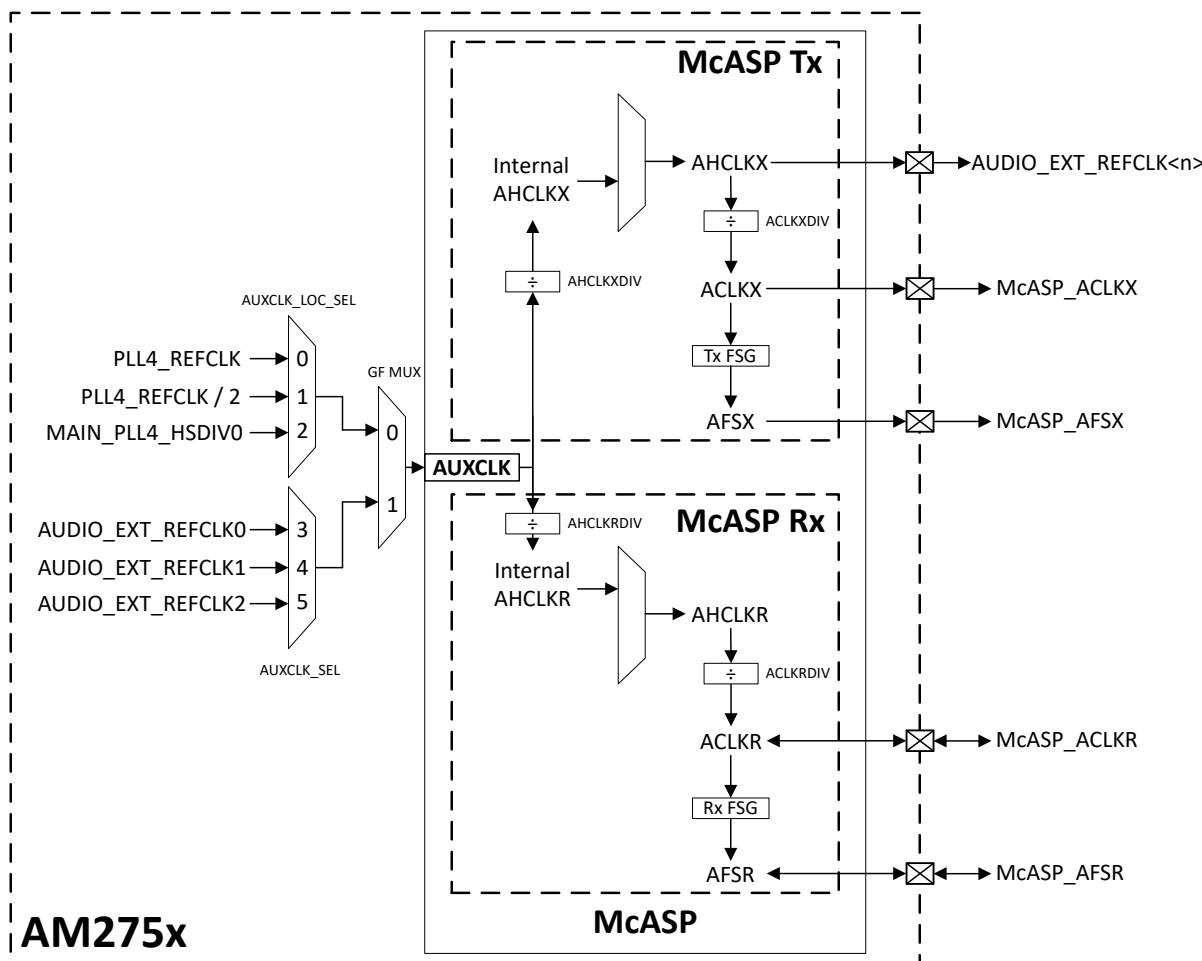

AM275x は、5 つの固有の McASP とさまざまな内部接続を備えた Arm ベースのプロセッサで、各種のクロック シナリオを実現できます。図 3-1 に、内部接続のマッピング全体を示します。

図 3-1. AM275x の McASP 接続

#### 3.1 一般的な McASP 構成

図 3-2. High レベル McASP 図

**注**

各 McASP には、送信 (TX) および受信 (RX) ドメインがあります。図 3-2 に、TX または RX ドメインのいずれかを表す単一のクロック ドメインを示します。

McASP ビットクロック (ACLK) とフレーム同期 (AFS) はどちらも双方方向であり、McASP はクロックコントローラにもクロックペリフェラルにもできます。以下のセクションでは、各クロック構成で利用可能なすべてのオプションについて詳しく説明します。

表 3-1 に、McASP の構成で最も一般的な使用事例を示します。AM275x SoC には、オーディオデータフレームフォーマット用のクロックを生成、供給、受信するための多くのオプションがあります。

### 注

ビットクロックとフレーム同期の場合、**内部生成**とは、McASP クロックコントローラアプリケーションの SoC レベルで出力される内部リファレンス信号を指しています。一方、**外部生成**とは、信号が McASP クロックペリフェラルアプリケーションの SoC レベルで入力として構成されることを意味します。

表 3-1. McASP 使用事例マトリクス

| 説明                                  | GF マルチプレクサ AUXCLK ソース | AHCLK | ビットクロック | フレーム同期 | McASP                 | 例                     |

|-------------------------------------|-----------------------|-------|---------|--------|-----------------------|-----------------------|

| オーディオ PLL リファレンス付き McASP クロックコントローラ | 内蔵オーディオ PLL           | 内部生成  | 内部生成    | 内部生成   | <a href="#">図 3-5</a> | <a href="#">図 6-1</a> |

| 外部 AUXCLK リファレンス付き McASP クロックコントローラ | AUDIO_EXT_REFCLK<n>   | 内部生成  | 内部生成    | 内部生成   | <a href="#">図 3-6</a> |                       |

| 外部 AHCLK リファレンス付き McASP クロックコントローラ  |                       | 外部生成  | 内部生成    | 内部生成   | <a href="#">図 3-7</a> |                       |

| McASP クロックペリフェラル                    |                       |       | 外部生成    | 外部生成   | <a href="#">図 3-8</a> |                       |

| 外部 AUXCLK リファレンス付き McASP クロックペリフェラル | AUDIO_EXT_REFCLK<n>   | 内部生成  | 外部生成    | 外部生成   | <a href="#">図 3-9</a> | <a href="#">図 6-2</a> |

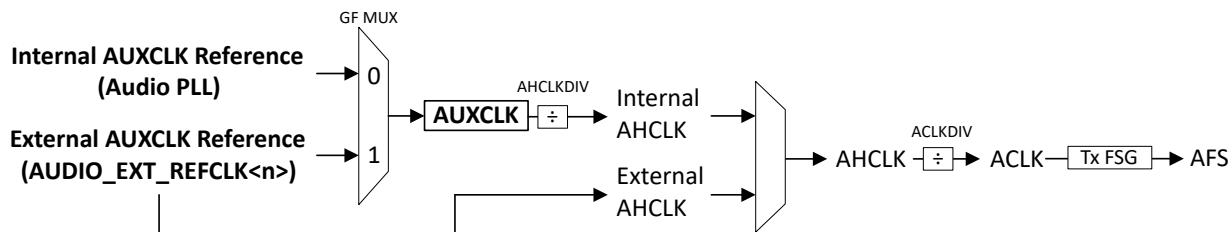

図 3-2 に、McASP クロックのさまざまな構成オプションの概要を示します。また、図 3-3 に、利用可能なオプションの詳細な図を示します。

図 3-3. McASP の詳細概要

### 3.1.1 クロック コントローラとしての McASP

McASP がクロック コントローラとして構成されている場合、ビット クロック信号とフレーム同期信号は出力として構成されます。SDK ドライバは、ソースが内部生成に設定されているとき、ビット クロックとフレーム同期を出力として定義します。つまり、ビット クロックが High クロックから内部的に生成され、ビット クロックに基づいてフレーム同期が生成されることを意味します。TX または RX ドメインの High クロックと McASP AUXCLK には、オーディオ システム要件に最適な多くのオプションが用意されています。

AUXCLK は、TX ドメインと RX ドメインの両方に供給できる単一のクロックリファレンスです。AM275x については、各 McASP AUXCLK 入力がグリッチ フリー (GF) クロック マルチプレクサに接続されており、ローカル クロックと外部クロック リファレンスを選択できます。AUXCLK のローカル リファレンスは、オーディオ PLL (PLL4) クロック入力、または PLL の高速分周器出力のいずれかです。外部クロック リファレンスは、AUDIO\_EXT\_REFCLK 入力のいずれかです。

AHCLK が内部生成される場合、AHCLK は高周波リファレンス用の AUDIO\_EXT\_REFCLK ピンのいずれかの出力として配線できます。

#### 注

SDK は、AUXCLK が AHCLK の生成に使用されているときに内部で生成される High クロック ソース (AHCLK) を指します。GF マルチプレクサが AUDIO\_EXT\_REFCLK マルチプレクサのリファレンス オプションに構成されている場合、AUXCLK 入力には外部を生成するオプションがあるため、これが紛らわしい場合があります。

図 3-4. AUXCLK ソース付き McASP コントローラ

### 3.1.1.1 内部オーディオ PLL を使用して生成されるクロック

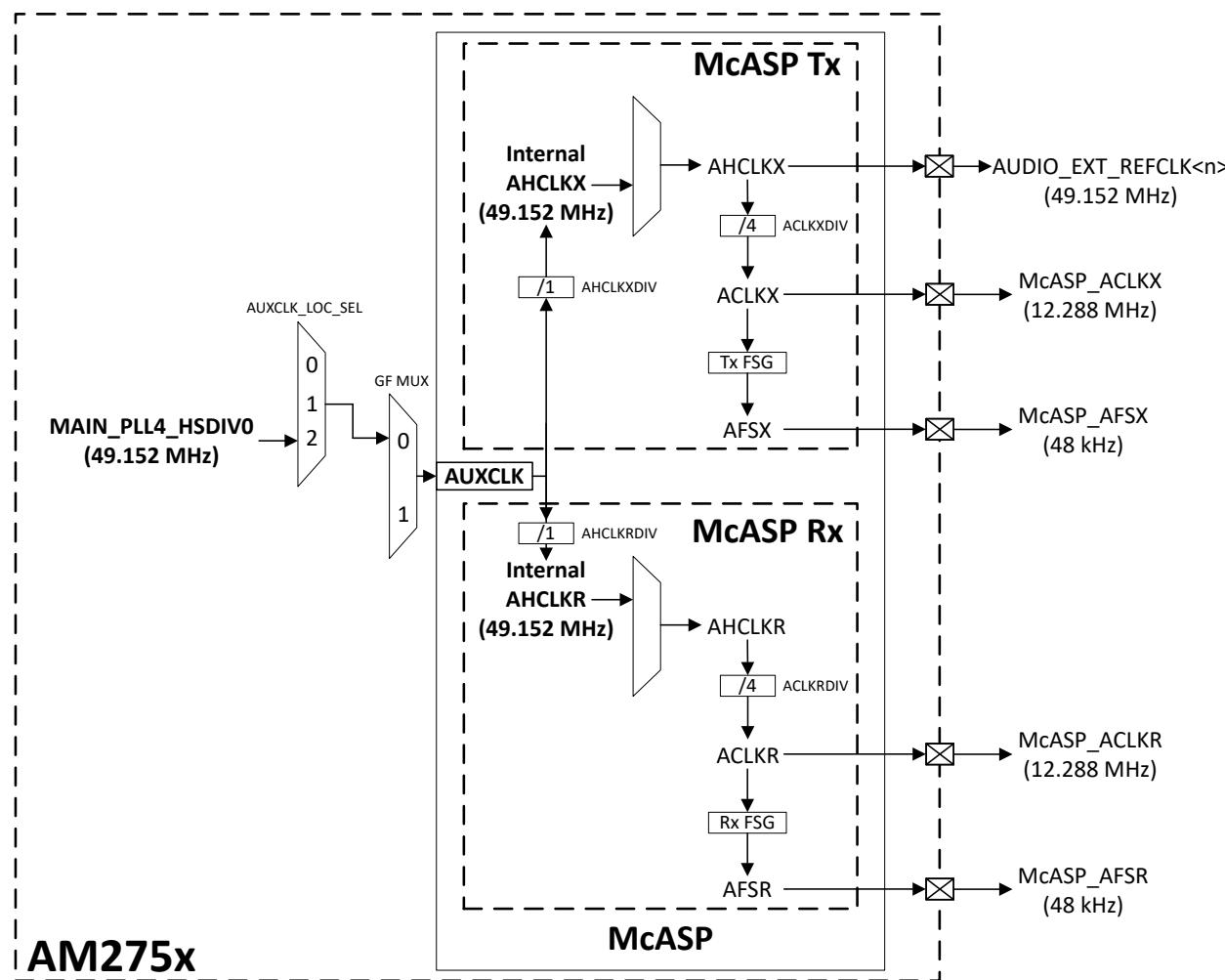

以下のセクションでは、McASP のセットアップ例について詳しく説明します。ビット クロックとフレーム同期は出力として構成され、内部オーディオ PLL をクロック リファレンスとして使用して生成されます。

| 説明                                   | GF マルチプレクサ AUXCLK ソース | AHCLK | ビット クロック | フレーム 同期 |

|--------------------------------------|-----------------------|-------|----------|---------|

| オーディオ PLL リファレンス付き McASP クロック コントローラ | 内蔵オーディオ PLL           | 内部生成  | 内部生成     | 内部生成    |

この例では、McASP は 48kHz フレーム同期と 32 ビットワードの TDM8 フレームフォーマットに構成されており、その結果、12.288MHz のビットクロック周波数が得られます。GF マルチプレクサは、ローカルリファレンスマルチプレクサを指すように構成されています。これは、MAIN\_PLL4\_HSDIV0 を選択します。デフォルトでは、MAIN\_PLL4\_HSDIV0 は 49.152MHz に設定されています。このSDKドライバは、スロット数、フレーム同期周波数、フレーム同期と AHCLK の比率に基づいて、AHCLK および ACLK の分周器を設定します。

AHCLK が内部生成される際に、システムクロックリファレンス出力を供給するために、オプションとして AUDIO\_EXT\_REFCLK ピンのいずれかに AHCLK を出力することもできます。

また、内部生成された AHCLK で McASP のクロック損失検出機能が有効になります。McASP のクロック損失検出の詳細については、『AM275x テクニカルリファレンスマニュアル』の『MCASP エラー報告』セクションにある『クロック障害検出』の章を参照してください。

図 3-5. オーディオ PLL リファレンス付き McASP クロック コントローラ

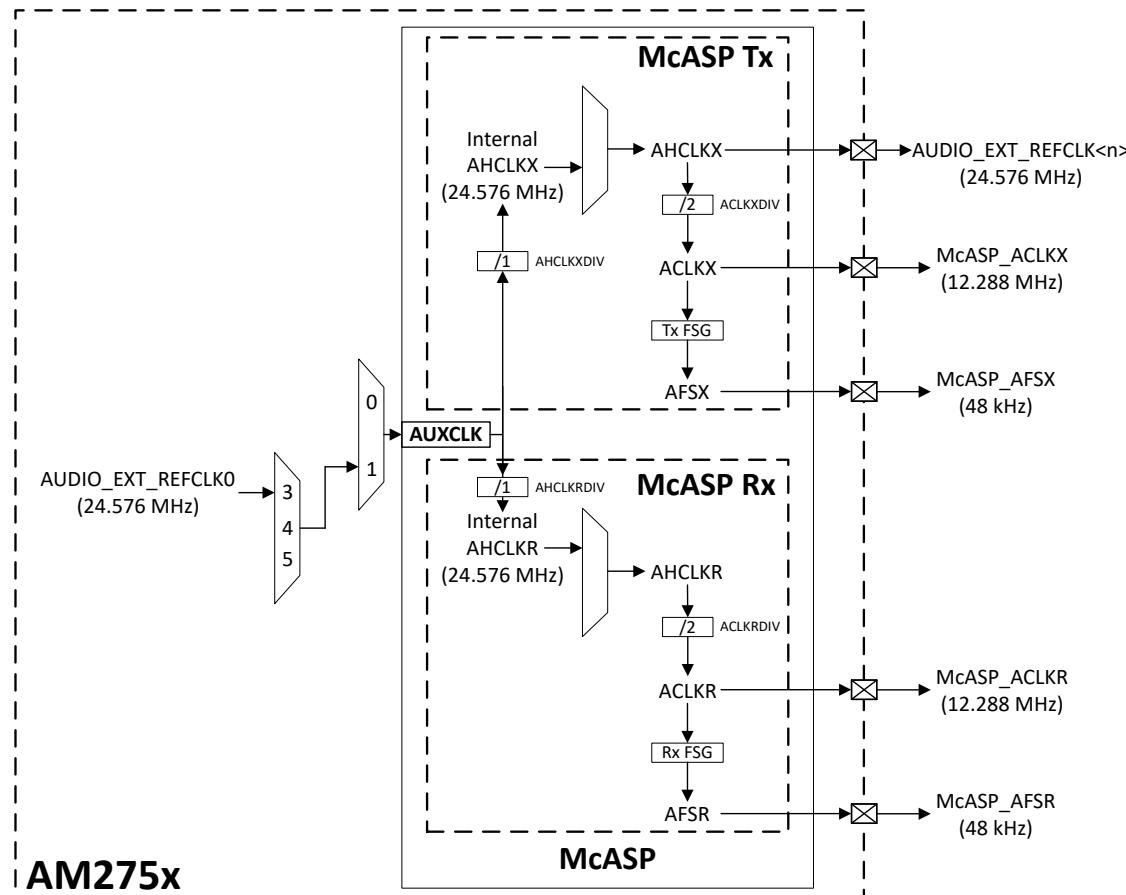

### 3.1.1.2 AUDIO\_EXT\_REFCLK AUXCLK ソースを使用して生成されるクロック

以下のセクションでは、McASP のセットアップ例について詳しく説明します。ビット クロックとフレーム同期は出力として構成され、AUDIO\_EXT\_REFCLK 経由で外部ソースを使用してクロック リファレンスとして生成されます。

| 説明                             | GF マルチプレクサ AUXCLK ソース | AHCLK | ビット クロック | フレーム 同期 |

|--------------------------------|-----------------------|-------|----------|---------|

| 外部入力リファレンス付き McASP クロック コントローラ | AUDIO_EXT_REFCLK<n>   | 内部生成  | 内部生成     | 内部生成    |

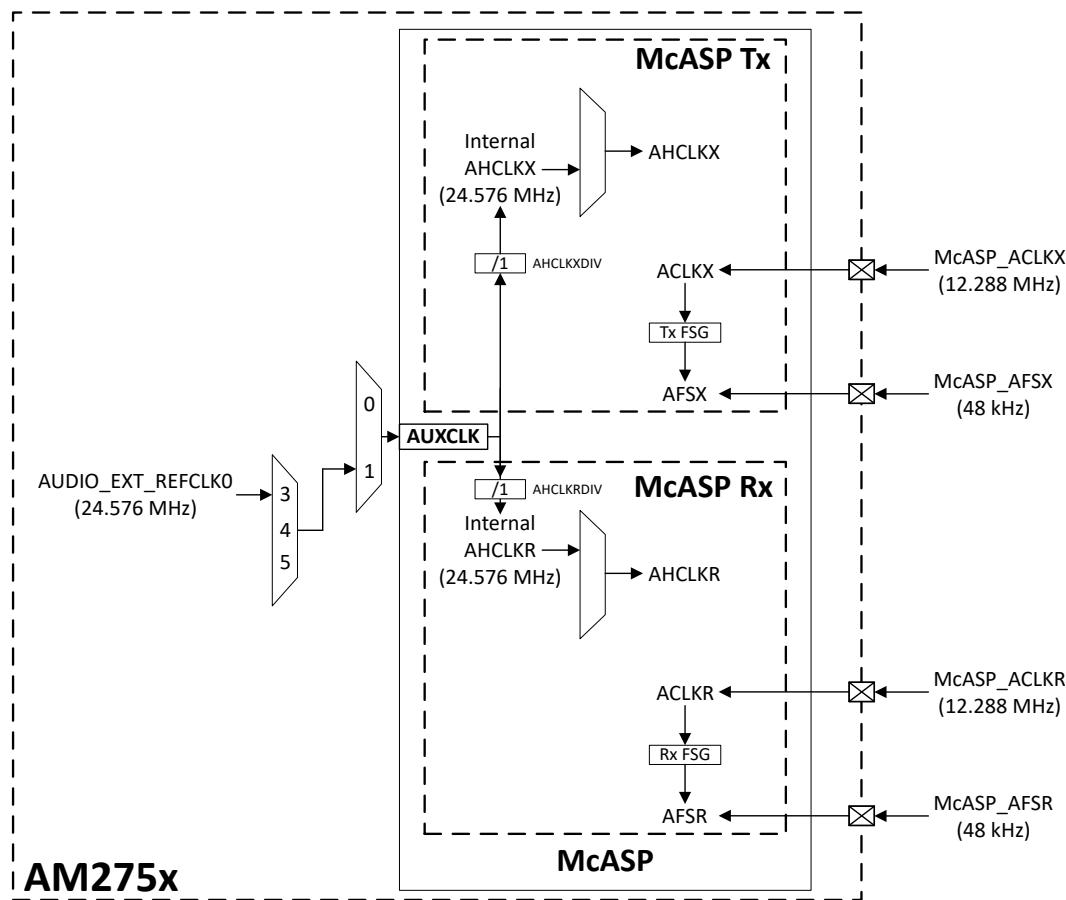

この例では、McASP は 48kHz フレーム同期と 32 ビットワードの TDM8 フレームフォーマットに構成されており、その結果、12.288MHz のビット クロック周波数が得られます。GF マルチプレクサは、外部リファレンス マルチプレクサを指すように構成されています。このマルチプレクサは、外部ドライバからの 24.576MHz である AUDIO\_EXT\_REFCLK0 ソースを選択します。この SDK ドライバは、スロット数、フレーム同期周波数、フレーム同期と AHCLK の比率に基づいて、AHCLK および ACLK の分周器を設定します。

AHCLK が内部生成される際に、システム クロック リファレンス出力を供給するために、オプションとして AUDIO\_EXT\_REFCLK ピンのいずれかに AHCLK を出力することもできます。

また、内部生成された AHCLK で McASP のクロック損失検出機能が有効になります。McASP のクロック損失検出の詳細については、『AM275x テクニカルリファレンスマニュアル』の『MCASP エラー報告』セクションにある『クロック障害検出』の章を参照してください。

図 3-6. AUDIO\_EXT\_REFCLK0 AUXCLK リファレンス付き McASP クロック コントローラ

### 3.1.1.3 AUDIO\_EXT\_REFCLK AHCLK ソースを使用して生成されるクロック

以下のセクションでは、McASP のセットアップ例について詳しく説明します。ビット クロックとフレーム同期は出力として構成され、AUDIO\_EXT\_REFCLK 経由で外部ソースを使用して AHCLK への直接的なクロック リファレンスとして生成されます。

| 説明                                    | GF マルチプレクサ AUXCLK ソース | AHCLK | ビット クロック | フレーム 同期 |

|---------------------------------------|-----------------------|-------|----------|---------|

| 外部 AHCLK 入力リファレンス付き McASP クロック コントローラ |                       | 外部生成  | 内部生成     | 内部生成    |

この例では、McASP は 48kHz フレーム同期と 32 ビットワードの TDM8 フレームフォーマットに構成されており、その結果、12.288MHz のビット クロック周波数が得られます。AHCLK が外部で生成されるように構成されている場合、GF マルチプレクサおよび AUXCLK は考慮されません。各 AHCLK には、異なる外部ソースを選択するための独自のマルチプレクサがあります。AHCLK マルチプレクサは、外部ドライバからの 24.576MHz である AUDIO\_EXT\_REFCLK0 ソースを指すように構成されています。SDK ドライバは、スロット数、フレーム同期周波数、フレーム同期と AHCLK の比率に基づいて、ACLK 分周器を設定します。

AHCLK が外部生成される場合、AHCLK を AUDIO\_EXT\_REFCLK に出力することはできません。

AHCLK が外部生成される場合、McASP ではクロック損失検出は使用できません。

図 3-7. AUDIO\_EXT\_REFCLK0 AHCLK リファレンス付き McASP クロック コントローラ

### 3.1.2 クロック ペリフェラルとしての McASP

以下のセクションでは、ビット クロックとフレーム同期が入力として構成された McASP のセットアップ例について詳しく説明します。

| 説明                | GF マルチプレクサ AUXCLK ソース | AHCLK | ビット クロック | フレーム同期 |

|-------------------|-----------------------|-------|----------|--------|

| McASP クロック ペリフェラル |                       |       | 外部生成     | 外部生成   |

この例では、McASP は 48kHz フレーム同期と 32 ビットワードの TDM8 フレームフォーマットに構成されており、その結果、12.288MHz のビット クロック周波数が得られます。この場合、GF マルチプレクサと AHCLK の設定は重要ではありません。SDK ドライバは、オーディオ データを適切に送信するために、ビット クロックとフレーム同期の想定される周波数を表すように構成する必要があります。

セクション 3.1.2.1 に詳述されているように、AUDIO\_EXT\_REFCLK が使用されない限り、McASP ではクロック損失検出は使用できません。

図 3-8. McASP クロック ペリフェラル

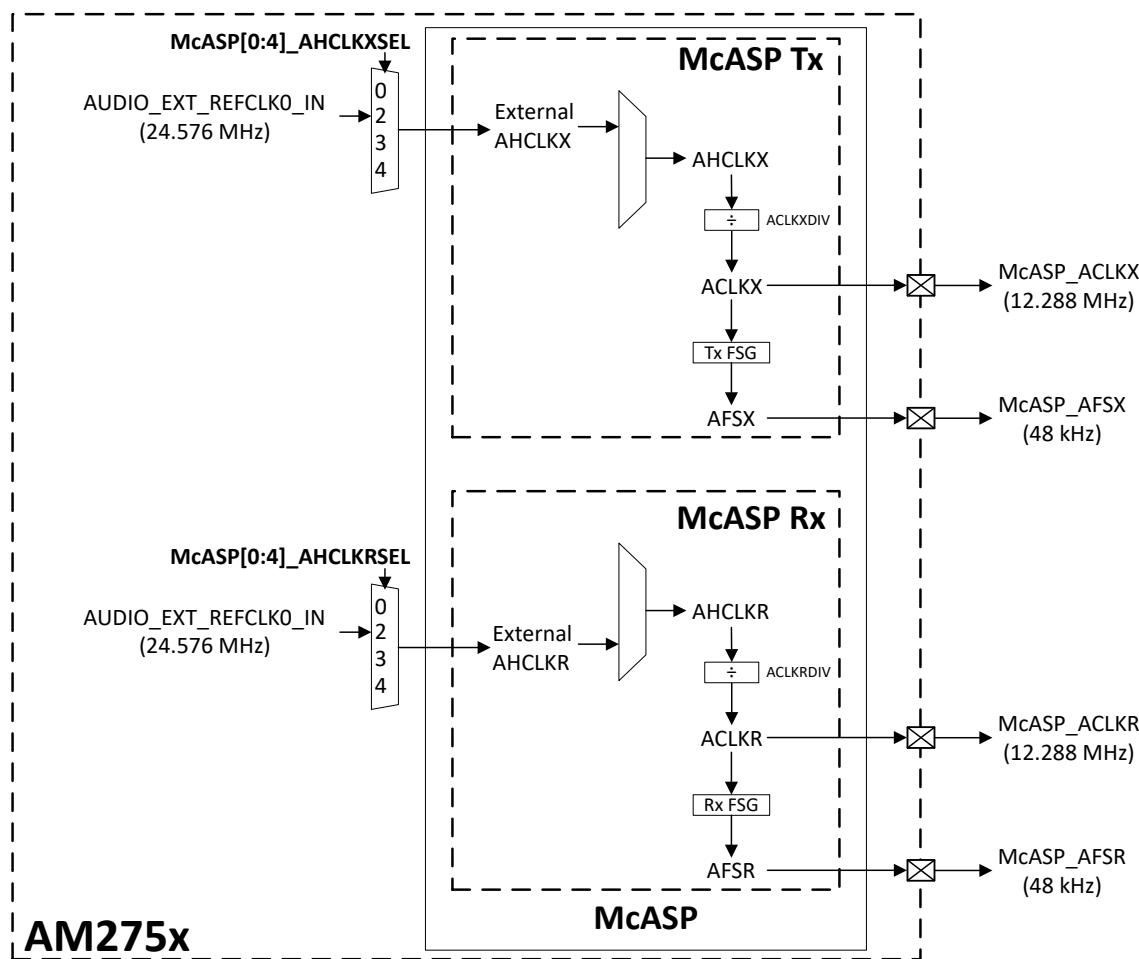

### 3.1.2.1 AUDIO\_EXT\_REFCLK 入力で外部生成されるクロック

以下のセクションでは、ビット クロックとフレーム同期が入力として構成された McASP のセットアップ例について詳しく説明します。

| 説明                                   | GF マルチプレクサ AUXCLK ソース | AHCLK | ビット クロック | フレーム同期 |

|--------------------------------------|-----------------------|-------|----------|--------|

| 外部 AUXCLK リファレンス付き McASP クロック ペリフェラル | AUDIO_EXT_REFCLK<n>   | 外部生成  | 外部生成     | 外部生成   |

この例では、McASP は 48kHz フレーム同期と 32 ビットワードの TDM8 フレームフォーマットに構成されており、その結果、12.288MHz のビット クロック周波数が得られます。GF マルチプレクサは、外部リファレンス マルチプレクサを指すように構成されています。このマルチプレクサは、外部ドライバからの 24.576MHz である AUDIO\_EXT\_REFCLK0 ソースを選択します。SDK ドライバは、AHCLK および ACLK 分周器を設定しますが、ACLK としては使用されず、AFS は外部で駆動されます。

AHCLK が内部生成される際に、システム クロック リファレンス出力を供給するために、オプションとして AUDIO\_EXT\_REFCLK ピンのいずれかに AHCLK を出力することもできます。

また、内部生成された AHCLK で McASP のクロック損失検出機能が有効になります。McASP のクロック損失検出の詳細については、『AM275x テクニカルリファレンスマニュアル』の『MCASP エラー報告』セクションにある『クロック障害検出』の章を参照してください。

図 3-9. AUDIO\_EXT\_REFCLK AUXCLK リファレンス付き McASP クロック ペリフェラル

## 4 McASP レイアウトに関する検討事項

McASP は、単一のクロックドメインを使用して、複数のオーディオ デバイスと同時に接続できます。しかし、レイアウトの実装によっては、クロック信号とデータ信号のシグナル インテグリティが影響を受けることがあります。この章では、AM275x の McASP の最も重要な 2 つのレイアウトに関する検討事項について説明します。

### 注

レイアウトの実装パラメータにかかわらず、McASP 信号レイアウトのシミュレーションを常に行い、クロック信号とデータ信号がデータシートのタイミング要件を満たしていることを確認する必要があります。

### 4.1 ブート モード ロジックと共有される McASP 信号

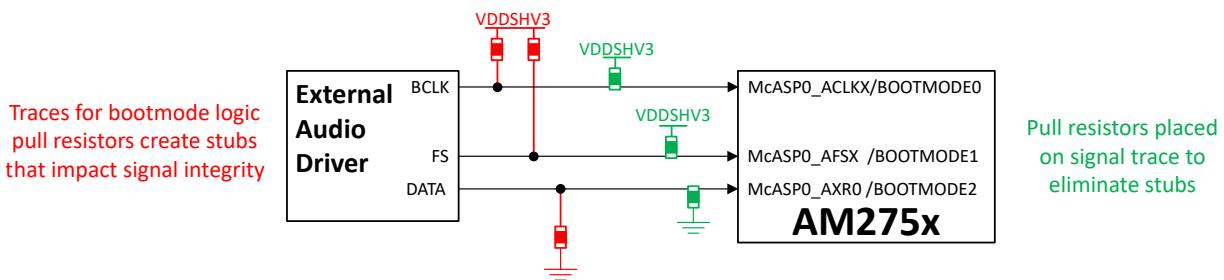

AM275x には 16 のブート モード信号があり、ブートや他のブート構成パラメータに使用されるペリフェラルを決定するために、ROM で使用されます。16 のブート モード信号は SoC の特定のパッドに接続され、AM275x はブート モード パッド用に McASP0 インターフェイス パッドのほとんどを使用します。

各ブート モード パッドは、電源オン シーケンス中に、関連するブート モード信号のデジタル ロジック High または Low 状態を定義するための外部プルアップまたはプルダウン抵抗を必要とします。

McASP0 信号はブート モード ロジックと共有されるため、以下をチェックして保証することが非常に重要です。

- McASP0 インターフェイスに接続されているオーディオ デバイスには、最初の電源投入時またはリセット時にブート モード信号を駆動できません。たとえば、AM275x に対して PORz がアサートされている場合、McASP0 オーディオ デバイスはブート シーケンスが完了するまでリセット状態に保持される必要があります。

- 電源投入時またはリセット時ブート モード ロジックに外部ドライバが存在すると、予測不能なブート モード状態が発生します。

- 外部プル抵抗は信号トレースと直列に配置し、スタブを導入しないようにする必要があります。[図 4-1](#) に、トレース スタブ付きとトレース スタブなしのプル抵抗の例を示します。設計時には、緑色の実装を再現する必要があります。

- 信号トレースのスタブ、特にビットクロックのスタブは、スタブによって生じる信号反射がタイミング誤差や信号歪みにつながる可能性があるため、オーディオ データの信頼性に影響を及ぼします。

図 4-1. McASP 信号トレース スタブ

## 4.2 単一のクロック ドメインの複数のデバイスでの McASP トポロジ

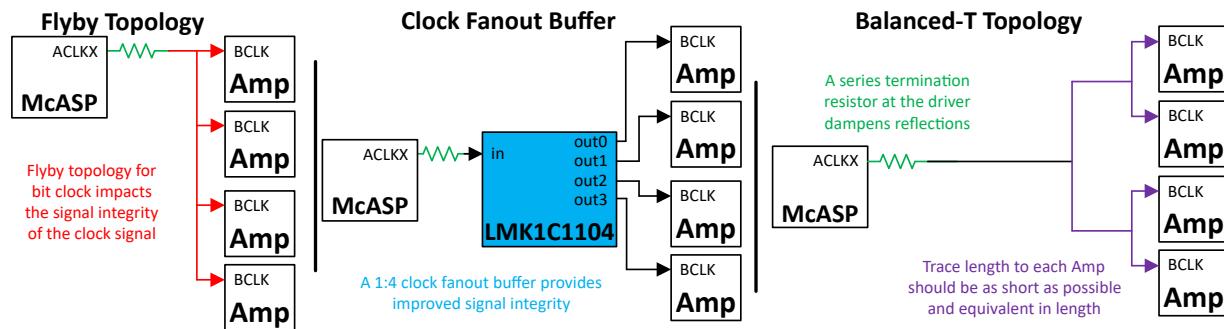

McASP は多くの場合、多くのオーディオ デバイスが单一のクロック ドメインを共有するシステムとして設計されます。たとえば、TAS6754 は TDM16 をサポートできる 4 チャネル アンプです。つまり、単一の McASP のビット クロック、フレーム 同期、およびデータピンを最大 4 つのアンプで共有できるということです。これら 3 つの信号のレイアウト設計は、インターフェイスの性能と信頼性に影響を及ぼします。

図 4-2 に、ビットク ロック信号を 4 つの異なるアンプに接続する 3 種類の信号トポロジを示します。

- フライバイトポロジを使用する場合、バスの各ドロップによって作成されるトレース スタブは、長さが一様で、反射を低減するためにできるだけ短くする必要があります。このトポロジでは、クロック周波数とパターン長によっては、シグナル インテグリティの問題が発生する可能性があります

- 複数のデバイスでクロック信号を共有するには、LMK1C1104 などのクロック ファンアウト バッファを使用することを推奨します。ファンアウト バッファによりクロックをリドライブすることでポイントツー ポイントのトレースの性能に近いシグナル インテグリティのクロック信号が生成されます。

- シリー (T) 型またはスター型トポロジでは、単一のバスを分割して、各デバイスの長さが等価な分岐にします。作成されるブランチは、デバイスの長さが一様になるように作成された各スタブでできる限り短くする必要があります。

### 注

トポロジにかかわらず、信号の反射を抑制し、シグナル インテグリティを維持するため、すべての McASP 信号に直列終端抵抗をドライバの近くに配置することを推奨します。

図 4-2. マルチデバイス オーディオ システム向けのクロックトポロジ

## 5 ASRC の概要

複雑なオーディオ システムは、異なるオーディオ クロックを使用した複数のオーディオ ゾーンを必要とすることがあります。非同期オーディオ サンプル レートコンバータ (ASRC) モジュールは、1 つのクロック ゾーンからサンプルを取得し、オーディオ データを別のクロック ゾーンに変換しながら、高い信号対雑音比を維持し、出力オーディオ品質がさまざまなハイエンド オーディオ アルゴリズムの要件を満たすのに十分な品質であることを保証します。また、ASRC を使用して、異なるルート クロックで同じサンプリング レートを使用して 2 つのクロック ドメイン間で変換を行い、クロックのジッタを除去することもできます。ASRC モジュールの詳細については、『AM275x テクニカル リファレンス マニュアル』の『オーディオ サンプル レート コンバータ』の章を参照してください。

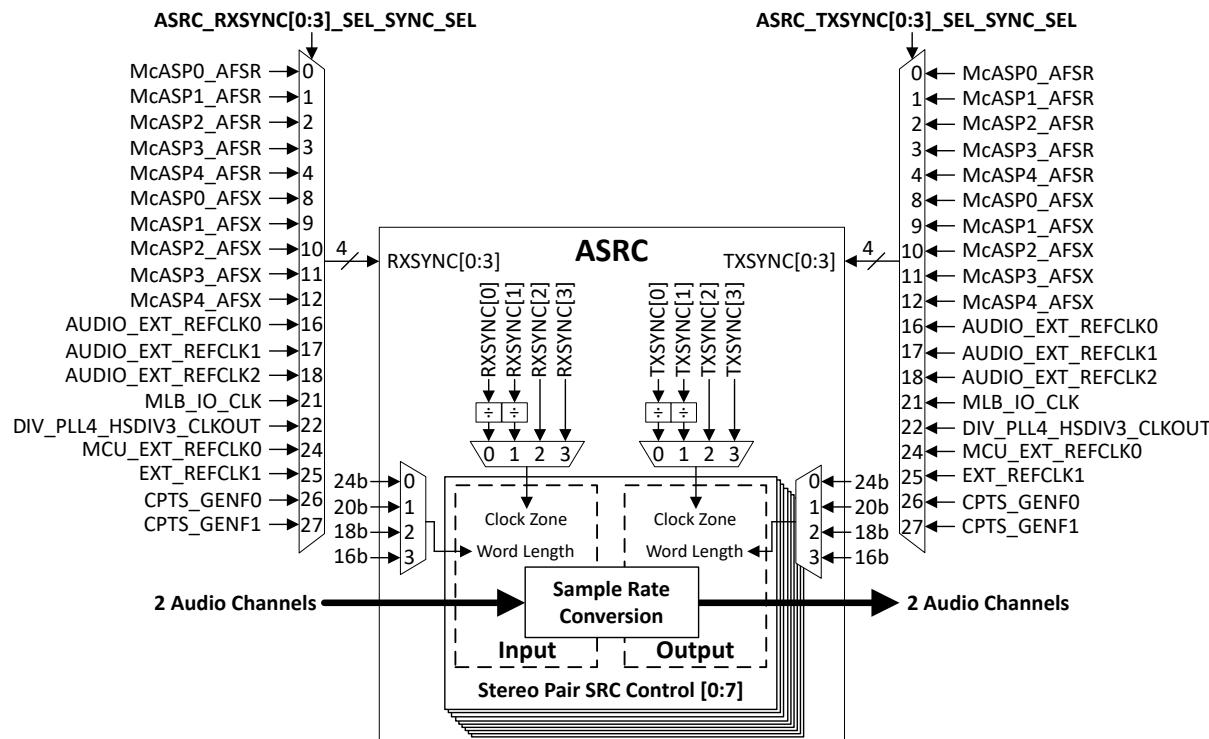

AM275x は 2 つの ASRC モジュールで構成されているため、各 SRC ペアを 2 つのチャネルに使用できると仮定して、最大 32 の独立したオーディオ チャネルで、非同期サンプル レート変換を実行できます。図 6-3 に、オーディオ システムで ASRC を使用する方法の例を示します。

ASRC モジュールには 4 つの入力 (RXSYNC) と 4 つの出力 (TXSYNC) クロック ゾーンがあり、ASRC 同期マルチプロセッサで使用できるさまざまなサンプル レートオプションのいずれかから選択できます。RXSYNC と TXSYNC のクロック ゾーン 0 と 1 のどちらにも、1 ~ 8192 を分周できるオプションの分周器があります。しかし、これらのゾーンに分周器を使用する場合は、入力周波数を 96MHz よりも低くする必要があります。クロック ゾーン分周器を使用しない場合、サンプル レートは 8 ~ 216kHz の範囲にする必要があります。また、任意のサンプル レートのコンバータ ペアの出力クロック ゾーン サンプル レートは、入力クロック ゾーンのサンプル レートに対して 1/16 ~ 16 の比にする必要があります。

各 ASRC モジュールは、8 つのサンプル レート コンバータ ステレオ ペアで構成されています。これらのペアはそれぞれ、4 つの入力および出力クロック ゾーンのいずれかを使用してサンプル レートの変換と、入力および出力ワードの長さをプログラムするように独自に設定できます。各 SRC ペアは、モノラル、ステレオ、またはグループ チャネル タイプに設定できます。2 つのチャネルより大きいオーディオ データストリームの場合、グループ チャネル タイプを使用して、入力と出力の同じタイミング ループで複数の SRC ペアをリンクできます。

---

### 注

TXSYNC/RXSYNC クロック ゾーンの選択、および任意のグループ チャネル構成は、2 つの ASRC モジュール間で独立しています。

---

図 5-1. ASRC のブロック図

## 6 McASP の実例

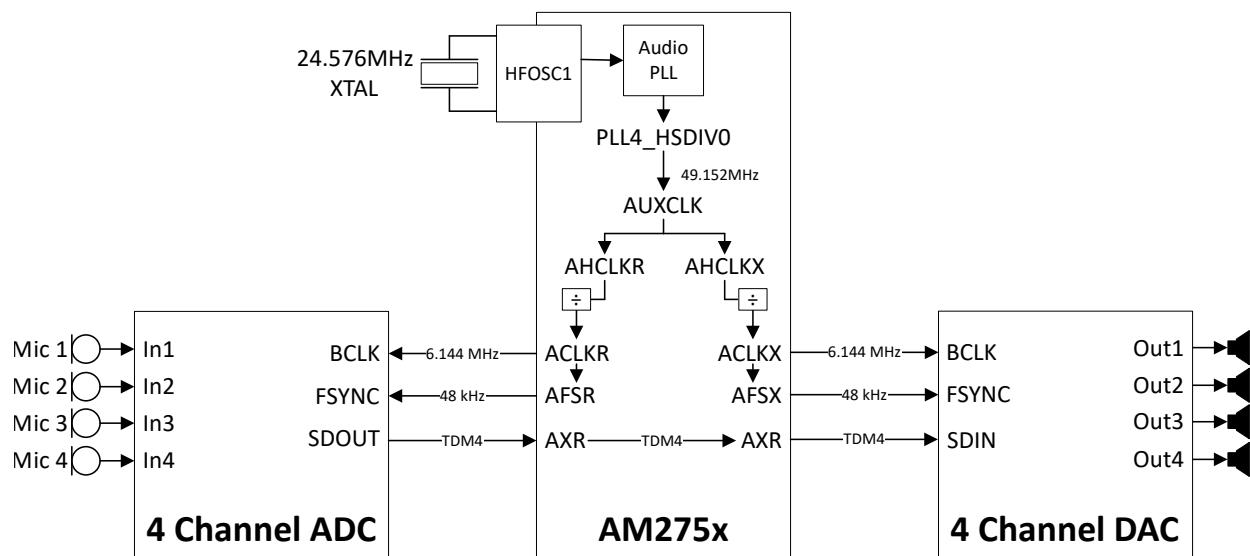

### 6.1 2つのクロックドメイン用の内部オーディオ PLL によるオーディオ再生

図 6-1 に、McASP で单一の内部リファレンスを使用して複数のドメイン間でオーディオ データを送受信する方法の簡単な例を示します。McASP は非同期モードで動作しますが、ルートクロック ソースは送信ドメインと受信ドメインと同じであるため、(オーディオ データフレーム フォーマットが入力と出力で同じである限り) バッファのオーバーランやアンダーランのリスクはありません。

このシステムでは、オーディオ PLL は HFOSC1 を使用して、高周波数のオーディオ クロックリファレンスを生成します。高速分周器 (PLL4\_HSDIV0) は、AUXCLK 入力の高周波リファレンスを 49.152MHz に分周します。この場合、TX および RX ドメインには、AHCLK, ACLK, AFS がすべて内部で生成されるように構成されています。

オーディオ データフレームは、1 つの TDM4 ストリームに対する 4 つのオーディオ チャネルであり、ワード深度が 32 ビットであると想定すると、ビット クロックは、 $48\text{kHz} = 4 \times 32 \times 48,000 = 6.144\text{ MHz}$  でサンプリングされる 32 ビットワードの 4 チャネルの積に基づいて計算できます。

図 6-1. ADC DAC オーディオ再生

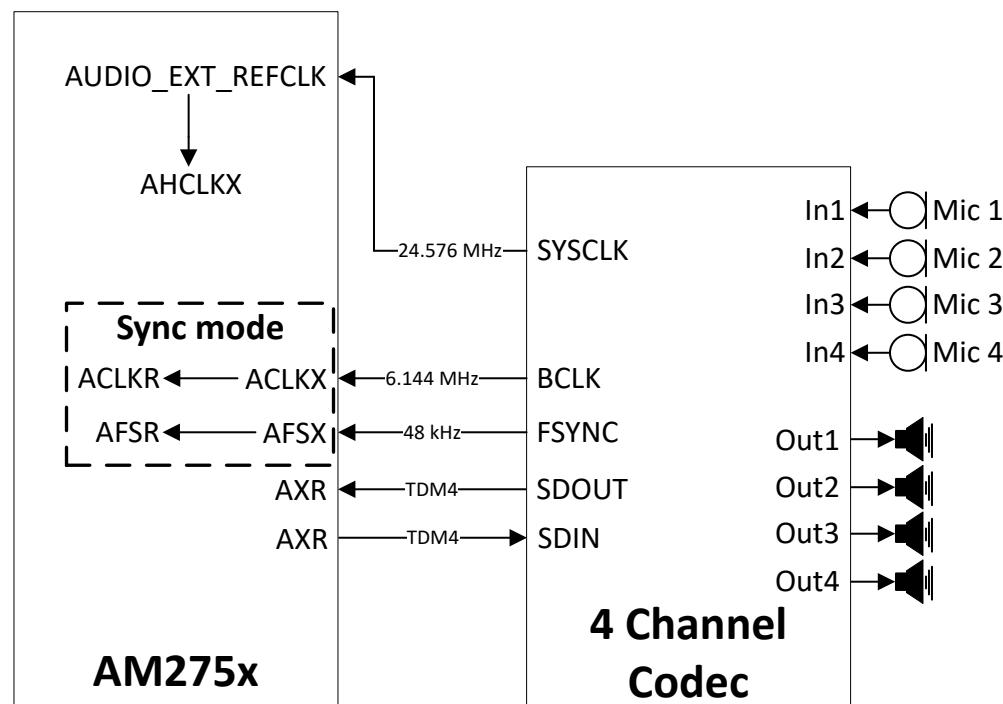

## 6.2 外部クロック ソースと McASP 同期モードによるオーディオ再生

図 6-2 に、McASP が单一のクロック リファレンスのみでオーディオ データを送受信する方法の簡単な例を示します。McASP は同期モードで動作します。つまり、送信ビット クロックとフレーム同期がそれぞれ受信ビット クロックとフレーム同期に内部で配線されます。RX ドメインの内部配線により、すべてのオーディオ データ ストリームが同じフレーム フォーマットを持つ限り、単一の McASP インスタンスでオーディオ データの入力と出力用のシリアル アライザを持つことができます。

このシステムでは、4 チャネルのコーデックがビット クロックとフレーム同期の両方のクロック コントローラとなります。コーデックには、より高い周波数のクロック リファレンスである SYSCLK 出力もあります。これは、他の McASP インスタンスがビット クロックとフレーム同期の生成に使用して、オーディオ システムの単一のルート クロック ソースを維持できます。この場合、TX および RX ドメインは SYNC モードになり、ACLK と AFS が外部で生成されるように構成されます。ビット クロックとフレーム同期が外部で生成された場合、AHCLK は動作に必要ないため、「無効」値と考えることができます。

オーディオ データ フレームは、1 つの TDM4 ストリームに対する 4 つのオーディオ チャネルであり、ワード深度が 32 ビットであると想定すると、ビット クロックは、 $48\text{kHz} = 4 * 32 * 48,000 = 6.144 \text{ MHz}$  でサンプリングされる 32 ビットワードの 4 チャネルの積に基づいて計算できます。

図 6-2. 同期モードのクロック ペリフェラルとしての McASP によるコーデック再生

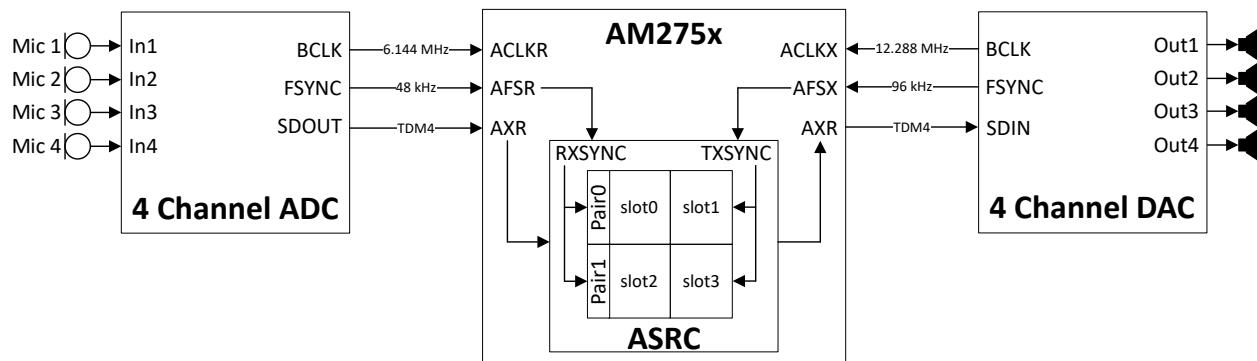

### 6.3 2つのクロック ドメインをブリッジする ASRC によるオーディオ再生

オーディオ システムには、フレーム同期のサンプリング レートが異なり、かつクロック コントローラでなければならない部品がある場合があります。図 6-3 に、ASRC モジュールを使用して 1 つのクロック ドメインから別のクロック ドメインにオーディオ データを変換する方法の簡単な例を示します。送信オーディオ データと受信オーディオ データには異なるクロックがあるため、McASP は非同期モードで動作します。

この場合は、ASRC を使用して、フレーム同期サンプル レートを 48kHz から 96kHz に変換します。この例のフレーム同期サンプル レートが同じ場合、フレーム同期生成用のルート クロックが一致しないため、ASRC が必要です。2 つのルート クロック間のクロックのジッタは、最終的に、バッファのオーバーランまたは McASP でアンダーランが発生します。

このシステムでは、外部 ADC と DAC の両方がクロック コントローラです。ASRC は、SRC ブロックの 2 つのステレオ ペアをグループ化して、4 チャネルのオーディオを 48kHz から 96kHz のサンプリング レートに変換するように構成されています。ASRC モジュール内でグループ化されたチャネルを使用すると、オーディオの 4 チャネルすべてが入力と出力で同じタイミング ループを共有できます。

オーディオ データ フレームは、1 つの TDM4 ストリームに対する 4 つのオーディオ チャネルであり、ワード深度が 32 ビットであると想定すると、ADC のビット クロックは、 $48\text{kHz} = 4 * 32 * 48,000 = 6.144\text{MHz}$  でサンプリングされる 32 ビットワードの 4 チャネルの積に基づいて計算できます。DAC のビット クロックは 12.288MHz です。これは、96kHz のサンプリング レートが、同じチャネル数およびワード深度の ADC サンプリング レート 48kHz の 2 倍の速度であるためです。

図 6-3. ASRC オーディオ再生

## 7 オーディオ システムの設計に関する重要なポイント

- McASP には、クロック同期のための 2 つの動作モードがあります。

- 同期モード: ACLKX 信号と AFSX 信号が ACLKR と AFSR に内部で配線され、すべてのオーディオ データが 単一のクロック ドメインで送受信されます。

- 非同期モード: TX および RX クロック ドメインは互いに独立しており、オーディオ データ クロック ドメインはシリアル イザの IO 方向によって決定されます。

- マルチゾーン オーディオ システムは、オーディオ データのバッファリングに関連する問題を回避するために、生成さ れるすべてのビット クロックとフレーム同期に対して 1 つのクロック リファレンスを理想的に備えています。クロック リフ ァレンスは、内部オーディオ リファレンスまたは外部ソースのどちらかから供給できます。

- AM275x がオーディオ システムの内部リファレンスを提供する場合、McASP がオーディオ PLL を内部的に基準 にするように構成するか、ビット クロックとフレーム同期を生成するためにオーディオ PLL を外部デバイスに供給す る必要があります。

- 外部ソースがオーディオ システム用のオーディオ クロック リファレンスを供給する場合、McASP が AUDIO\_EXT\_REFCLK 入力を内部で基準とするように構成するか、またはビット クロックとフレーム同期を外部で 生成するように構成する必要があります。

- 外部ソースにデバイス レベルの高周波数リファレンスがない場合、同じ基準を持つ他の McASP インスタンスを 有効にするため、ビット クロックも AUDIO\_EXT\_REFCLK 入力に配線する必要があります。

- マルチゾーン オーディオ システムが異なるドメインの複数のオーディオ クロック リファレンスを必要とする場合は、2 つ のクロック ドメイン間でビット クロックとフレーム同期周波数が同じであっても、ASRC を使用する必要があります。 ASRC を使用して異なるリファレンス ソースを持つ 2 つのクロック ドメインをブリッジしない場合、ドメイン間のクロックの ジッタはオーディオ データ バッファのオーバーランまたはアンダーランの問題を引き起こします。

- 各 ASRC モジュールは、最大 16 チャネルのサンプル レートを変換できます。AM275x の ASRC モジュールの数 は、デバイスの性能グレードによって異なります。動作性能ポイント A または B の AM275x は ASRC を 1 つのみ搭 載し、C/D/E/F はすべて 2 つの ASRC モジュールを搭載しています。

- McASP 信号と共有されるすべてのブート モード信号を注意深く確認し、クロック信号ラインやデータ信号ラインに不 必要なトレース スタブが導入されないことを確認します。

- 複数のデバイスで共有されるクロック信号とデータ信号の場合、レイアウトのトポロジが信号の性能に影響しないよう にしてください。

- 常に提案されたレイアウト トポロジで信号をシミュレートし、オーディオ データ転送の信頼性と整合性を確保しま す。

## 8 参考資料

- ・『AM275x 信号処理マイコン』

- ・『AM275x 信号処理マイコン データシート』

- ・『AM275x 信号処理マイコン テクニカルリファレンス マニュアル』

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月