*Application Note***MSPM0 ADC のノイズ解析と応用****概要**

このドキュメントでは、A/D コンバータ (ADC) のノイズ分析について説明し、MSPM0 マイクロコントローラ ADC アプリケーションを紹介します。

**目次**

|                                            |    |

|--------------------------------------------|----|

| <b>1 ADC の概要</b>                           | 2  |

| 1.1 SAR ADC の原理                            | 2  |

| 1.2 ADC のパラメータ                             | 2  |

| <b>2 ADC ノイズ解析</b>                         | 5  |

| 2.1 ADC ノイズ分類                              | 5  |

| 2.2 ノイズを低減する方法                             | 8  |

| <b>3 ADC オーバーサンプリング</b>                    | 10 |

| 3.1 サンプリング レート                             | 10 |

| 3.2 抽出                                     | 10 |

| 3.3 アプリケーションの条件                            | 10 |

| <b>4 MSPM0 をベースとする ADC アプリケーション</b>        | 11 |

| 4.1 MSPM0 の ADC 構成                         | 11 |

| 4.2 MSPM0G3507 ADC EVM 基板を用いた ADC の DC テスト | 13 |

| <b>5 改訂履歴</b>                              | 16 |

**図の一覧**

|                                     |    |

|-------------------------------------|----|

| 図 1-1. CDAC に基づく SAR ADC の原理ブロック図   | 2  |

| 図 1-2. ADC AC テストの図                 | 3  |

| 図 1-3. ADC DC テストの回路図               | 4  |

| 図 2-1. ADC ノイズ源の回路図                 | 6  |

| 図 2-2. 分解能が異なる ADC の量子化ノイズと熱ノイズ     | 7  |

| 図 4-1. ADC クロックの Sysconfig 構成       | 11 |

| 図 4-2. ADC サンプリング モードの Sysconfig 構成 | 11 |

| 図 4-3. ADC 変換メモリ Sysconfig 構成       | 12 |

| 図 4-4. MSPM0G3507 ADC EVM           | 14 |

| 図 4-5. ADC DC テスト ソフトウェア構成          | 15 |

**表の一覧**

|                                 |    |

|---------------------------------|----|

| 表 2-1. さまざまな ADC リファレンス電圧の長所と短所 | 8  |

| 表 4-1. テスト結果                    | 16 |

**商標**

すべての商標は、それぞれの所有者に帰属します。

## 1 ADC の概要

### 1.1 SAR ADC の原理

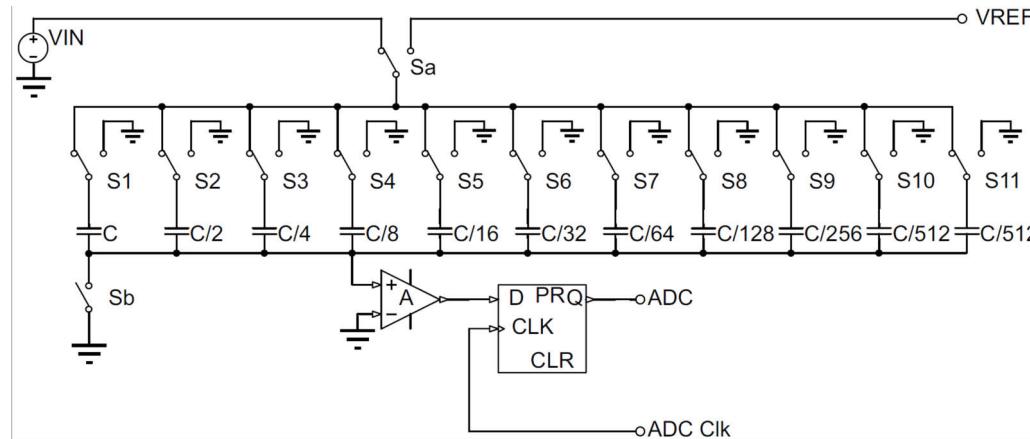

図 1-1 に、SAR ADC のシステム回路図を示します。SAR ADC は複数のスイッチ (この場合は 12 個) を制御し、VREF に対して容量分圧を行うことで、さまざまなアナログ電圧の出力結果を得ます。アナログ電圧を入力サンプリング信号と比較し、コンパレータの出力によってスイッチのオン/オフ状態を調整し、最終的に VREF の分圧で得られる模擬電圧を入力電圧にできるだけ近づけます。実際の比較プロセスは、バイナリ方式を使用して VIN の VREF 分周を近似することで行われるため、データ変換に 12 サイクルが必要です。ADC のトリガ、信号のサンプリングとホールド時間を考慮すると、実際の SAR ADC の変換処理には 12 サイクル以上かかります (MSPM0 G シリーズでは 14 サイクルかかります)。

図 1-1. CDAC に基づく SAR ADC の原理ブロック図

### 1.2 ADC のパラメータ

#### 1.2.1 静的パラメータ

- 微分非線性誤差 (DNL)

微分非直線性誤差とは、ADC の A/D 変換過程において、実際のステップと理想的なステップとの最大偏差のことです。ここで、理想的なステップとは 1LSB を指します。DNL が 1LSB を超えると、ADC のデジタル結果に欠損コードが発生し、特定のデジタルコードが出力結果から消失します。

$$DNL = \text{Actual Step} - 1\text{LSB} \quad (1)$$

- 積分非直線性誤差 (INL)

積分非直線性誤差とは、ADC 変換過程において、ある変換電圧と理想的な変換電圧との偏差のことで、DNL を積分した結果を反映する指標です。この値の測定は、オフセット誤差とゲイン誤差を補償した後で行われました。各デジタルコードの変換電圧を測定することで、各コード点の INL を求めることができます。ADC のデータマニュアルには、最大 INL 値のみが記載されています。

$$INL = \text{the } k^{\text{th}} \text{ actual conversion voltage} - (k - 0.5)\text{LSB} \quad (2)$$

- オフセット誤差 (EO)

オフセット誤差とは、ADC が低電圧から上昇していく際に、最初の実際の変換電圧と最初の理想変換電圧との偏差のことです。最初の変換は、デジタル ADC 出力が 0 から 1 に変化したときに行われます。理想的な ADC では、アナログ入力が 0.5LSB から 1.5LSB の間にあるとき、デジタル出力は 1 になるはずであり、そのため最初の理想変換点は 0.5LSB となります。したがって、オフセット誤差の計算式は次のとおりです：

$$EO = \text{the first actual conversion voltage} - 0.5\text{LSB} \quad (3)$$

- ゲイン誤差 (EG)

ゲイン誤差とは、最後の実際の変換電圧と最後の理想変換電圧との電圧偏差であり、この値はオフセット誤差を補正した後に測定されます。12 ビット ADC を例にとると、出力のデジタル結果が 0xFFE から 0xFFFF に変化したときに最後の実際の変換が発生します。これは  $V_{REF+} - 0.5$  LSB の電圧に対応します。したがって、計算式は次のとおりです：

$$EG = \text{the last actual conversion voltage} - (V_{REF+} - 0.5\text{LSB}) \quad (4)$$

## 1.2.2 動的パラメータ

### 1.2.2.1 AC のパラメータ

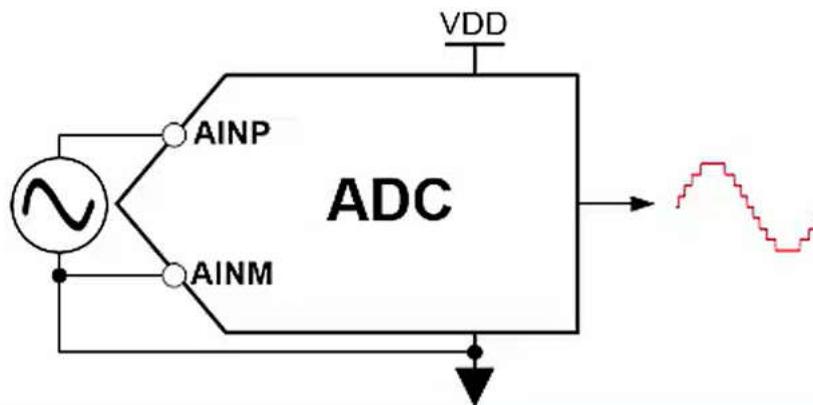

測定条件: ADC の正端子と負端子の間に正弦波の AC 電圧を入力し、ADC のサンプリング出力結果を観察します。フーリエ変換により、出力信号の周波数スペクトルを分析し、信号の基本周波数、高調波、ノイズの各成分を取得します。ADC の動的 AC パラメータは、これらの要素に基づいて算出されます。

図 1-2. ADC AC テストの図

- 全高調波歪み (THD)

全高調波歪みは、AC 信号に含まれるすべての高調波成分の総電力と、基本周波数成分の電力との比を指します。デシベル形式での計算式は以下のとおりです。

$$THD = 20\log_{10}\left(\frac{\sum V_{\text{Harmonics}}}{V_{\text{Signal(RMS)}}}\right)(\text{dB}) \quad (5)$$

ADC の通信パラメータ測定における実験では、THD は ADC の伝達特性曲線の非線形性によって生じます。つまり、サンプリング範囲内で ADC の入力と出力が厳密な線形関係を満たさない (ADC の静的誤差である DNL/ INL/ E<sub>O</sub>/ E<sub>G</sub> によって) ことが原因で、出力信号に高調波成分が発生します。一般的に、高調波次数は計算中に 2 から 10 に求められます。

- 信号対雑音比(SNR)

信号対雑音比は、信号の実効値とノイズの実効値の比です。ここで紹介したノイズは、ADC 量子化ノイズや 1/f ノイズなどの高周波ノイズですが、THD 計算で入力信号の高調波成分は除外されています。計算式は次のとおりです。

$$\text{SNR} = 20\log_{10}\left(\frac{V_{\text{Signal(RMS)}}}{V_{\text{Noise(RMS)}}}\right)\left(\text{dB}\right) \quad (6)$$

- 信号対雑音および歪み(SINAD)

ADC の内部誤差によって信号には常に歪みがあります。SINAD を使用して、信号の高調波とノイズの合計に対する比率を測定し、ADC 出力の実効信号の全体的な比率を示します。

$$\text{SINAD} = 20\log_{10}\left(\frac{V_{\text{Signal(RMS)}}}{\sum(V_{\text{Harmonics}} + V_{\text{Noise(RMS)}})}\right)\left(\text{dB}\right) \quad (7)$$

- 有効ビット数(ENOB)

ENOB は ADC の有効ビット数であり、ADC の実際の分解能と小振幅の信号を区別する能力を表します。この値は、SINAD によって直接計算できます。

上記の式は、入力信号が ADC の最大範囲に割り当てられている場合の ENOB の計算方法を示しています。入力信号が最大範囲を下回る場合、ENOB の計算は次のように調整されます：

$$\text{ENOB} = \frac{\text{SINAD}_{\text{MEASURED}} - 1.76\text{dB} + 20\log_{10}\left(\frac{\text{Fullscale Amplitude}}{\text{Input Amplitude}}\right)}{6.02} \quad (8)$$

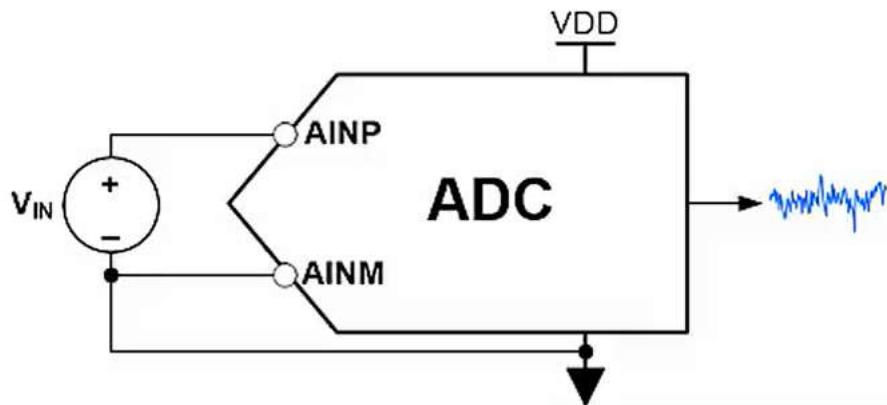

### 1.2.2.2 DC のパラメータ

測定条件: ADC 入力の正端子と負端子の間に一定の DC 電圧を入力し、出力デジタル値の分布を観察します。

図 1-3. ADC DC テストの回路図

理論的には、サンプリングされたデータの量が十分大きい場合、DC 信号に重畠されたノイズは正規分布に近似します。ノイズの実効値は、データサンプルの標準偏差  $\sigma$  です。 $u-3\sigma \sim u+3\sigma$  の範囲内でのデータ分布の確率は 99.73% であるため、DC 信号のピークツーピーク値は約  $6\sigma$  です。

- 有効分解能

DC 入力での ADC の有効分解能は、ADC のフルスケール範囲 (FSR) をノイズの実効値で除算し、対数 2 を取ることで得られます。この分解能は、DC 信号のサンプリングや低周波信号のサンプリングの場面で非常に重要であり、実際のアプリケーションにおいて ADC のデジタル結果がどれだけ有効に使えるかを反映します。

$$\text{Effective resolution} = \log_2 \left( \frac{\text{FSR}}{\text{V}_{N, \text{RMS}}} \right) (\text{bits}) \quad (9)$$

上記の式は、DC 入力がフルスケールの場合の有効分解能の計算方法を表しています。入力がフルスケールでない場合、計算式が次のように変更されます：

$$\text{Effective resolution} = \log_2 \left( \frac{\text{V}_{IN}}{\text{V}_{N, \text{RMS}}} \right) (\text{bits}) \quad (10)$$

つまり、有効分解能は電圧入力に関連しています。理論的には、入力電圧が高いほど、DC の有効分解能は高くなります。したがって、小さい入力信号の場合、通常はプリアンプを経由して FSR に近い値まで増幅し、大きな実効分解能を得ます。1/f ノイズや広帯域ノイズなど、増幅されたノイズを過度に持ち込まないよう注意する必要があります。

- ノイズフリー分解能

ADC のフルレンジをノイズのピークツーピーク値で割り、その比を対数化することで、DC 入力時の ADC のノイズフリーディシジョンを求ることができます。一定の入力で安定性を維持できる桁数ビットを反映します。

$$\text{Noise free resolution} = \log_2 \left( \frac{\text{FSR}}{\text{V}_{N, \text{PP}}} \right) (\text{bits}) \quad (11)$$

## 2 ADC ノイズ解析

### 2.1 ADC ノイズ分類

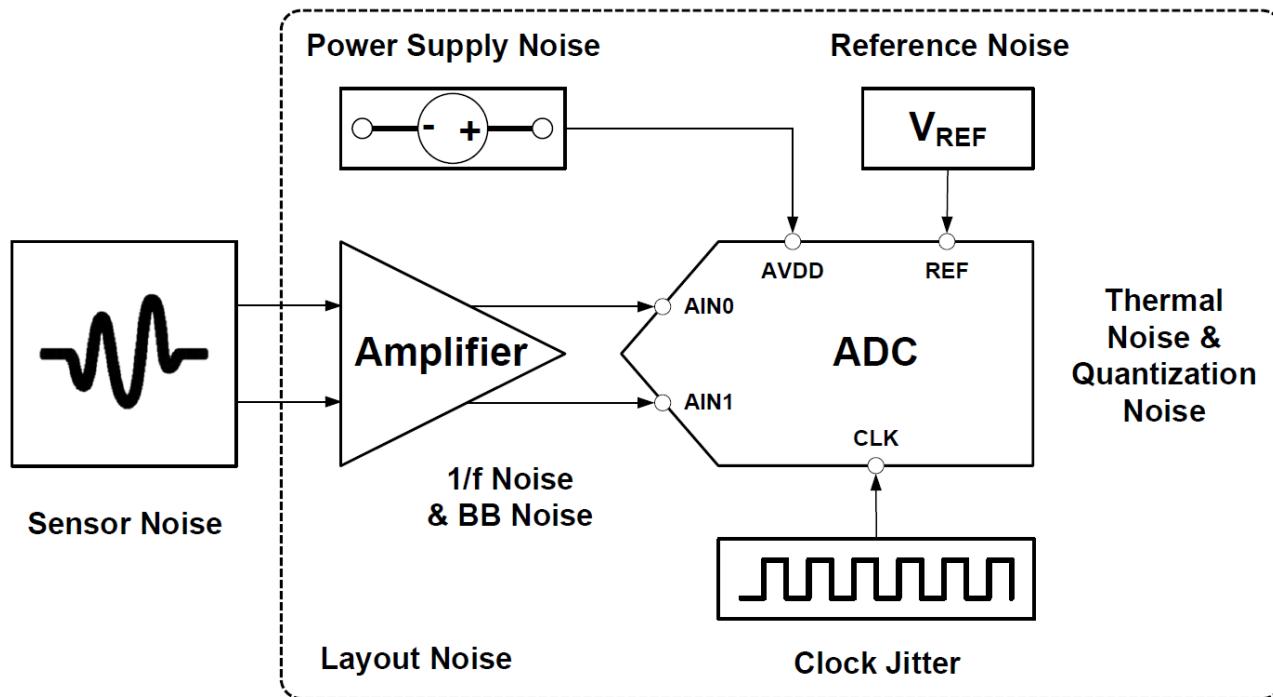

次の図は ADC システムのブロック図を示しており、ADC がサンプリングしたデータのシグナル チェーンと、ADC モジュールの動作に必要な信号入力を表しています。各リンクで ADC システムにノイズが入り込む可能性があるため、ADC システムのノイズ源には、センサノイズ、オペアンプノイズ、ADC 自身のノイズ、電源ノイズ、リファレンス電圧ノイズ、クロックジッタノイズが含まれます。

センサノイズやオペアンプの使い方はアプリケーションの状況によって大きく異なり、レイアウトの影響を強く受けます。この記事では、これらを ADC の入力ノイズとして分類します。図 2-1 は、各段に個別にノイズ発生源を紹介します。

図 2-1. ADC ノイズ源の回路図

### 2.1.1 ADC ノイズ

ADC 内部ノイズには、量子化ノイズと熱ノイズが含まれます。

- 量子化ノイズ

ADC の量子化ノイズとは、入力アナログ信号と出力デジタル信号の間に生じる量子化誤差によって発生するノイズのことです、その大きさは ADC の分解能によって決まります。量子化ノイズのピークツーピーク値は 1LSB であり、ADC の分解能が高いほど、量子化誤差は小さくなります。

- 熱ノイズ

熱ノイズはすべての電気部品に固有の現象であり、ADC 入力がなくても依然として存在します。量子化ノイズを除いた ADC 内部のすべてのノイズの総和は、一般に熱ノイズと呼ばれます。通常、熱ノイズはガウス分布を示し、量子化ノイズとは無関係であるため、ADC 内の総ノイズは二乗和平方根で求めることができます。

$$N_{ADC, Total} = \sqrt{N_{ADC, Thermal}^2 + N_{ADC, Quantization}^2} \quad (12)$$

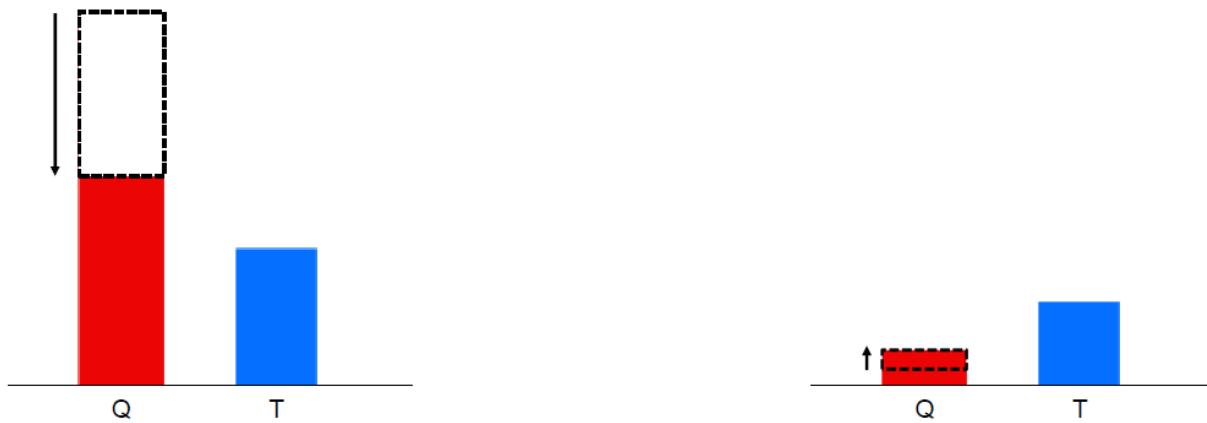

ADC 内部ノイズの計算式から分かるように、ADC の合計ノイズは量子化ノイズと熱ノイズのうち大きい方によって決まります。低分解能 ADC の場合、量子化ノイズは熱ノイズよりもはるかに大きくなります。この場合、ADC ノイズを低減する方法は、量子化ノイズを低減するために、より小さいリファレンス電圧を選択することです。高分解能 ADC では、 LSB が小さく量子化ノイズが低いため、ADC のリファレンス電圧を上げることでフルスケールレンジを広げることができます。これにより、信号中に占める熱ノイズの割合が減少し、信号対雑音比を向上させることができます。

### Lower-resolution ADCs

Resolution is limited by quantization noise

Use **smallest** acceptable reference

(to decrease quantization noise)

### Higher-resolution ADCs

Resolution is limited by thermal noise

Use **largest** acceptable reference

(to increase dynamic range)

図 2-2. 分解能が異なる ADC の量子化ノイズと熱ノイズ

#### 2.1.2 リファレンスノイズ

ADC 出力の通常の計算式は以下の通りです:

したがって、リファレンス電圧に重畠したノイズは、出力電圧に直接影響します。リファレンス電圧ノイズは、出力電圧に蓄積された形式に変換できます:

$$\text{Output Code} = V_{IN(\text{RMS})} * \frac{2^N}{V_{REF} + V_{N, REF(\text{RMS})}} \quad (13)$$

- 分子と分母を  $V_{REF}$  で除算すると、次のが得られます:

$$\text{Output Code} = \frac{V_{IN(\text{RMS})}}{V_{REF}} * \frac{2^N}{1 + \frac{V_{N, REF(\text{RMS})}}{V_{REF}}} \quad (14)$$

- 次の作業を簡素化して取得:

$$\text{Output Code} = \frac{V_{IN(\text{RMS})} * 2^N}{V_{REF}} * \left( 1 - \frac{V_{N, REF(\text{RMS})}}{V_{REF}} \right) \quad (15)$$

- 上記の式を合計形式に分割します:

$$\text{Output Code} = \frac{V_{IN(\text{RMS})} * 2^N}{V_{REF}} - \frac{V_{IN(\text{RMS})} * 2^N * V_{N, REF(\text{RMS})}}{V_{REF}^2} \quad (16)$$

したがって、出力電圧に重畠されるノイズの電圧形態は次のとおりです:

$$V_{N, REF} = \frac{V_{IN(\text{RMS})}}{V_{REF}} * V_{N, REF(\text{RMS})} \quad (17)$$

これは、入力電圧と基準電圧の比率、つまりフルスケールでの使用率に関係します。入力のフルスケール利用率が高いほど、リファレンス電圧ノイズが ADC 出力に重畠される量も大きくなります。

ADC の有効分解能に対するノイズの影響を考えると、リファレンス電圧ノイズによって有効分解能で用いられる  $V_{in}$  が小さくなり、また ADC の内部ノイズは通常一定で ADC の入力電圧とは無関係であるため、ADC ノイズの影響下では ADC の入力電圧を上げることで有効分解能を向上させることができます。しかし、リファレンス電圧ノイズの影響下では、有効分解能を改善することはできません。

リファレンス電圧のノイズを低減する 1 つの方法は、RC フィルタ段を追加してから、ADC にリファレンス電圧を追加し、高周波ノイズをフィルタリングすることです。一方、外部または内部リファレンス電圧を適度に選択することで、リファレンス電圧ノイズの影響を低減できます。

表 2-1 に、いくつかの異なるリファレンス電圧の利点と欠点の比較を示します。

**表 2-1. さまざまな ADC リファレンス電圧の長所と短所**

| 基準電圧 | 利点                                                                                                                                             | 欠点                                                                                                                |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 内部   | <ul style="list-style-type: none"> <li>PCB 面積の削減 + 消費電力とコストの低減</li> <li>多くのアプリケーションに最適</li> </ul>                                              | <ul style="list-style-type: none"> <li>大きい(相対的)ノイズ</li> <li>より大きな(相対的な)ドリフト</li> </ul>                            |

| 外部   | <ul style="list-style-type: none"> <li>リファレンスノイズとドリフトを低減</li> <li>REFN と AIRN を直接接続し、単一点グランドを使用することで、グランドが電源電圧とリファレンス電圧に及ぼす影響を低減します</li> </ul> | <ul style="list-style-type: none"> <li>一般的に大電力</li> <li>コスト増および基板スペースの増加</li> <li>REF と ADC ノイズは相關しません</li> </ul> |

### 2.1.3 電源ノイズ

システムの複数のコンポーネントに電源を供給するために、ADC や他の回路部品 (マイクロコントローラなど) の動作によって電源の電圧変動が発生し、電源ノイズが発生する可能性があります。このノイズは、さまざまな結合方法で ADC の出力結果に影響を及ぼす可能性があります。ロードレギュレーション能力の高い電源を選び、電源出力端およびマイクロコントローラの電源端にデカッピングコンデンサを並列に配置することで、電源の安定性を確保できます。

### 2.1.4 ADC 入力ノイズ

ADC 入力ノイズとは、信号の収集、增幅、伝送の過程で元の信号に重畠され、ADC のアナログ入力端子に到達するまでに加わるノイズのことです。入力ノイズはオシロスコープで測定できます。信号入力には多くのリンクが関わるため、さまざまな干渉を受けやすくなります。入力リンクの設計では、レイアウトや配線を適切に行い、さらに RC フィルタを追加することで、入力信号への干渉を最小限に抑え、高周波ノイズをできるだけ除去できます。

### 2.1.5 クロックジッタ

クロックジッタは、クロックエッジを基準に入力信号をサンプリングする際のサンプリング時点を揺らし、その結果サンプリングされた信号値にもジッタを生じさせます。信号周波数が高いほど、クロックのジッタにより発生するサンプリングされた値のジッタは大きくなります。高周波信号をサンプリングする場合、ADC のサンプリング時間を短縮し、システムに入り込む実効値ジッタを低減するために、電圧スイッチ速度の高いクロックソースを選択する必要があります。

## 2.2 ノイズを低減する方法

一般に、ADC システムの各段におけるノイズは相関していないと考えられています。そのため、ADC システム全体のノイズは実績値で求めます。つまり、各段のノイズを二乗して合計し、その平方根を取る方法です。

したがって、ADC システムのノイズは、実効ノイズ値が最も大きい段に左右されます。システムノイズを効果的に低減するには、測定やデータシート参照によって各段のノイズレベルを評価し、最も大きなノイズ源を抑制することが必要です。

## 2.2.1 RC フィルタリングによる入力ノイズの低減

RC フィルタはローパス フィルタであり、適切なフィルタ帯域幅を選ぶことで ADC 入力の高周波ノイズを除去できます。一方では、高周波ノイズを切り落とすために帯域幅はできるだけ狭いことが望まれますが、他方では、帯域幅を制限しすぎるとサンプリング信号の立ち上がり時間が長くなり、入力信号の歪みを引き起します。したがって、高周波ノイズを除去しつつ、高周波信号に適切に応答できるように、適切な RC 値を設計する必要があります。具体的な参考資料:[「フィルタ RC 選択の理論的計算方法」](#)

## 2.2.2 レイアウトに関する推奨事項

- 電源

- 負荷レギュレーションの優れた LDO またはスイッチング電源を使用し、出力端にフィルタ用コンデンサを並列に配置して、負荷に安定した電源を供給します。

- マイクロコントローラ や ADC チップの電源端子に、大きなコンデンサ(10uF)を並列接続して低周波ノイズを除去し、小さなコンデンサ (0.1uF) を並列接続して高周波ノイズを除去します。

- デジタル電源をアナログ電源から分離し、デジタル グランドをアナログ グランドから分離して、高周波のデジタル信号がアナログ信号入力に影響しないようにします。同時に、相互干渉を最小限に抑えるために、アナログ グランドとデジタル グランドをスター ネットワークで接続することを推奨します。

- リファレンス電圧

- リファレンス電圧の負端子を入力信号の負端子に直接接続し、單一点 (スター接続) でグランドへ落とすことが推奨されます。

- 外部リファレンス電圧を使用する場合は、小さなコンデンサを並列に接続して、電圧の高周波ノイズをフィルタリングします。

## 2.2.3 信号対雑音比の向上

### • 信号増幅

分解能とリファレンス電圧が固定された ADC では、ADC 自身のノイズは一定であり、信号中に占めるノイズの割合を減らすことで ADC の有効分解能を向上させることができます。信号を增幅して ADC のフルレンジにできるだけ近づけることで、有効分解能を向上させることができます。

### • リファレンス電圧の値を削減

信号対雑音比を改善する別の方法は、入力信号の最大値に近い適切なリファレンス電圧を選択することで、量子化ノイズを減らして ADC ノイズを抑え、結果として信号対雑音比を向上させることができます。

## 2.2.4 適切なリファレンス電圧源を選択

- レシオメトリック サンプリングが利用できるアプリケーションでは、外部電圧源を基準電圧として使用することができます。このケースでは、電圧源に乗るノイズは理論上デジタル出力に影響せず、リファレンス電圧のノイズや偏差を非常に小さく抑えることができます。

- 低成本が必要で、高精度を必要としないアプリケーションでは、内部リファレンス電圧を選択できます。

- リファレンス電圧の精度に高い要求がある場合は、高精度かつ低温度ドリフトの外部リファレンス電圧を選択することが推奨されます。

## 2.2.5 ノイズを低減するソフトウェア方式

信号ノイズをソフトウェアで低減する最も直接的な方法は、オーバーサンプリングのためにサンプリング周波数を上げ、必要以上のサンプルを収集し、それらを平均することで信号中のノイズを減らし、有効分解能と信号対雑音比を向上させることです。平均プロセスは、ADC 伝達関数の DNL 誤差を除去するのにも役立ちます。DNL 誤差が大きいことによって ADC 出力で欠落したコードも、平均化を行うことで再び現れることがあります。そのため、オーバーサンプリングを用いることで、ADC のダイナミックレンジを効果的に改善できます。オーバーサンプリングには、次の点に注意する必要があります：

- 1 LSB より高い精度が必要な場合、ハードウェア平均化では実際のサンプル サイズの平均値を取得できません。たとえば、オーバーサンプリングで 16 個のデータポイントを取得しても、ハードウェア上でそのまま 16 ポイントを平均することはできません。その場合、結果は 12 ビット分解能となり、最大量子化誤差は  $\frac{1}{2}$  LSB になります。16 個のサンプルデータのうち 4 個ずつを平均することで、14 ビットの量子化結果を得ることができます。この場合、ソフトウェアによって 12 ビットの浮動小数点データに変換されます。この場合の最大量子化誤差は 1/8 LSB になります。

- 適切なノイズにより、ハードウェア平均化のノイズ低減効果を改善できます。入力信号のノイズが極めて小さい場合 (ノイズのピークツーピーク値が 1LSB 未満)、ADC のハードウェア分解能が 12 ビットしかないため、どれだけオーバーサンプリングしても出力結果は変化しません。そのため、オーバーサンプリングによってより高い分解能を得ることはできません。したがって、1LSB を超える適切な量のノイズを使用すると、平均化の効果が向上します。

- 通常、ノイズが多いほど、高精度を得るために必要なオーバーサンプリング数が増えます。その結果、実際の入力信号に対する有効サンプリング周波数は低くなります。

## 3 ADC オーバーサンプリング

### 3.1 サンプリング レート

ナイキスト定理は、アナログ入力信号を再構成するためには、入力信号の最大周波数成分の 2 倍以上のサンプリング周波数  $f_S$  で信号をサンプリングする必要があることを示しています。ナイキストの定理に従わないと周波数エイリアシングが発生し、入力サンプルからアナログ信号を完全に再構成できなくなります。したがって、ほとんどのアプリケーションでは、サンプリング周波数の半分より高い成分を除去するために、ADC 入力にローパスフィルタが必要になります。さらに、オーバーサンプリングではナイキスト周波数の制限より高い速度でアナログ入力信号をサンプリングし、サンプリング後にデシメーションによってサンプリング レートを低減します。

量子化ノイズがホワイトノイズとして信号に重畠されると仮定すると、その電力密度はナイキスト周波数範囲内に一様に分布し、この電力密度はサンプリング周波数に依存しません。ナイキスト周波数の限界を超えるサンプリングレートでサンプリングすると、量子化ノイズの総電力は一定のままサンプリング帯域幅だけが広がるため、信号帯域内に落ち込むノイズ電力が大幅に減少します。その結果、ADC の信号対雑音比と有効ビット数が向上します。

### 3.2 抽出

従来の平均化の意味は、 $m$  個のサンプルを追加し、結果を  $m$  で除算することです。信号の変動とノイズを減衰させるローパスフィルタを使用した ADC 測定結果からのいくつかのデータを平均化します。 $m$  の  $N$  ビットサンプルの平均は依然として  $N$  ビットの分解能の表現であるため、通常の平均化では変換の分解能は増加しないことに注意してください。抽出は平均化方式で、 $N$  ビットよりも高い分解能を得るには  $m$  未満の数値の平均を必要とします。[ノイズを低減するソフトウェア方式](#)で説明されているように、オーバーサンプリングと組み合わせると、抽出により ADC の分解能が向上します

### 3.3 アプリケーションの条件

オーバーサンプリングと抽出の方法が正しく機能するためには、以下の要件を満たす必要があります:

- 入力信号には、適度なノイズが含まれている必要があります。ノイズは、ホワイトノイズとして近似し、パワースペクトル密度が均一である必要があります。

- ノイズの振幅は、入力信号を量子化ビット間でランダムに遷移させられるだけ十分でなければならず、つまりノイズのピークツーピーク値は少なくとも 1LSB 必要です。そうでない場合、入力サンプルの量子化結果は同じで、合計動作と平均動作によって ADC の有効分解能は増加しません。ほとんどのアプリケーションでは、ADC の内部熱ノイズと入力信号ノイズがこの条件を満たすことができます。

## 4 MSPM0 をベースとする ADC アプリケーション

### 4.1 MSPM0 の ADC 構成

- クロック

Sample Clock Configuration

|                                   |             |

|-----------------------------------|-------------|

| ADC Clock Source                  | ULPCLK      |

| ADC Clock Frequency               | 32.00 MHz   |

| Sample Clock Divider              | Divide by 8 |

| Calculated Sample Clock Frequency | 4.00 MHz    |

図 4-1. ADC クロックの Sysconfig 構成

- ADC クロック (ADCCLK)

- SYSOSC (最大 32MHz)

- HFCLK (最大 48MHz)

- ULPCLK (最大 40MHz, PD0)

- ADC サンプリング クロック (SAMPCLK) : ADCCLK で除算

- 変換クロック (変換クロック) : ADC IP 内部 80MHz 水晶発振器

- 12 ビット ADC データの変換時間は、およそ 14 個の変換クロック サイクルです

- サンプリング モード

Sampling Mode Configuration

|                             |                                |

|-----------------------------|--------------------------------|

| Conversion Mode             | Single                         |

| Conversion Starting Address | 0                              |

| Enable Repeat Mode          | <input type="checkbox"/>       |

| Sampling Mode               | Auto                           |

| Trigger Source              | Software                       |

| Conversion Data Format      | Binary unsigned, right aligned |

図 4-2. ADC サンプリング モードの Sysconfig 構成

- 変換モード

- シングル変換: 各サンプリングおよび変換処理では単一のポイントのみが変換され、使用される MEMCTL 番号は、変換開始アドレス STARTADD を設定することで決まります。

- シーケンス変換: 変換に使用する MEMCTL 番号の開始アドレス STARTADD と終了アドレス ENDADD を設定することで、一連のデータ変換シーケンスを定義できます (MEMCTL0~11 は MEMRES0~11 に対応)。また、各 MEMCTLx ごとに ADC チャネルを個別に設定できます。

- 反復モードをイネーブル

- 非反復モード: 変換の各ラウンドが完了すると、変換イネーブルビット (ENC) は自動的にゼロにリセットされます。

- 反復モード: 変換プロセスは、ソフトウェアによって変換イネーブルビット (ENC) がクリアされるまでイネーブルに継続されます。

- サンプリング トリガ ソース

- ソフトウェア: ソフトウェア設定 CTL1.SC ビット トリガ サンプリング:

- イベント: イベント立ち上がりエッジ トリガ サンプリング:

- サンプリング モード

- 自動サンプリング: サンプリングのトリガ信号が生成されると、サンプリング信号 SAMPLE が自動的に High になります。サンプリング時間は SCOMP によって定義される数個の SAMPCLK サイクルとなります。

- 手動サンプリング (ソフトウェア トリガのみをサポート、反復モードおよびシーケンス変換はサポートせず、ハードウェア オーバーサンプリングはサポートしません) : サンプリング信号サンプルは、ソフトウェア トリガ信号 CTL1.SC と同期してプルアップされます。サンプリング時間は SC のプルアップ時間を決定することで決定され、トリガとサンプリングは同期して完了します。

- トリガ モード

- 繰り返し変換モードおよびシーケンス変換モードでは、次の変換サイクルにトリガ信号が必要かどうかを決めるために、トリガ モード (TRIG) を選択する必要があります。

- 変換メモリの構成

#### ADC Conversion Memory 0 Configuration

|                               |                                                         |

|-------------------------------|---------------------------------------------------------|

| Name                          | 0                                                       |

| Input Channel                 | Channel 2                                               |

| Device Pin Name               | PA25                                                    |

| Reference Voltage             | VREF                                                    |

| VREF Mode                     | Internal                                                |

| Calculated reference voltage  | 1.40 V                                                  |

| Sample Period Source          | Sampling Timer 0                                        |

| <b>Optional Configuration</b> |                                                         |

| Averaging Mode                | <input type="checkbox"/>                                |

| Burn Out Current Source       | <input type="checkbox"/>                                |

| Window Comparator Mode        | <input type="checkbox"/>                                |

| Trigger Mode                  | Trigger will automatically step to next memory conve... |

**図 4-3. ADC 変換メモリ Sysconfig 構成**

- 設定が必要な変換メモリの量は、変換モードで定義された MEMCTL の開始番号と終了番号によって決まります。

- サンプリング入力チャネル

- リファレンス電圧

- VDDA: 内部電源 (3.3V)

- VREF

- 内部: 2.5V/ 1.4V

- 外部: 0 ~ 3.3V

- サンプリング タイマ ソース: 自動サンプリング モードでのサンプリング時間のカウントに使用するタイマを選択します

- その他

- オーバーサンプリング

- サンプリング結果倍数 = サンプリング ポイント数 / 平均分母

- 割り込み

- DMA を使用しない: MEMx の結果読み込み割り込みを有効にし、各サンプリング結果が生成されるたびに、割り込み内でデータを読み取ります。

- DMA の使用方法: DMA 完了割り込みを有効にし、ADC の MEMx 結果のロードをトリガとして DMA データ転送を開始し、DMA 転送データ量を設定します。DMA 転送が完了したら、DMA 割り込みを入力して、ADC サンプリング データを一度に処理します。

- CPU ポーリング

- CPU が MEMx の結果ロードレジスタをポーリングし、ADC の変換が完了して結果が MEMx にロードされると、対応する CPU\_INT\_RIS ビットが 1 に設定されます。

- CPU が ADC ステータス レジスタをポーリングし、ADC の変換が完了すると、ADC ステータスのビザビットがクリアされます。

## 注

以下のデバイスでは、CTL1 レジスタで ADC の開始変換ビットがセットされてから 14 個の ULPCLK サイクル後に、ビジーが設定されます。この 14 ULPCLK 分については、CPU がビジー ビットがセットされるまで待つための遅延を入れる必要があります。その後、CPU はビジー ビットがクリアされるのをポーリングして待つことができます。ADC の変換完了ステータスをポーリングするには、MEMx の結果ロードレジスタを使用することを推奨します。

MSPM0C110x, L1x0x, L111x, L134x, Lx22x, Gx10x, Gx50x, Gx51x, H321x。

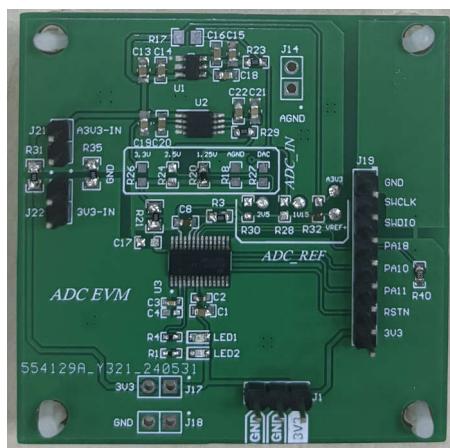

## 4.2 MSPM0G3507 ADC EVM 基板を用いた ADC の DC テスト

MSPM0 G シリーズの ADC 性能を評価し、DC 入力時における異なるリファレンス電圧の精度を比較するため、当社のチームは MSPM0G3507 を用いた ADC EVM 基板を設計し、このテストを実施しました。

### 4.2.1 ソフトウェア/ハードウェアの構成

#### 4.2.1.1 ハードウェア

MSPM0G3507 ADC EVM ボードは、次の 4 つの部分で構成されています：

- マイクロコントローラ 最小システム

マイクロコントローラ は、28 ピン パッケージである MSPM0G3507SDGS28 を採用しています。テストでは、PA25 を ADC 入力として使用し、PA23 を外部リファレンス電圧 VREF+ の入力として使用しています。一方、VREF- は 0R 抵抗を介してグランドに接続されています。

- 2.5V 電圧生成

REF7025QDGKR は、出力電圧が 2.5V の高精度シリーズ電圧リファレンスです。また、ADC の外部リファレンス電圧にも使用できます。

- 1.25V 電圧生成

REF35125QDBVR は 1.25V を生成するために使用され、MSPM0 ADC に安定した DC 入力を供給できます。

- ADC 入力とリファレンス電圧の選択

ADC の入力は 1.25V、2.5V、VDD、GND から選択でき、ADC の外部リファレンス電圧は VDD、2.5V、1.25V の中から 0R 抵抗によって選択できます。

図 4-4. MSPM0G3507 ADC EVM

#### 4.2.1.2 ソフトウェア

テストの方法は次のとおりです：1ms ごとにタイマ イベントで ADC のサンプリングと変換をトリガし、ADC の結果は DMA によって自動的に配列へ転送されます。DMA 転送サイズは 1024 に設定されています。DMA 転送が完了するたびに DMA 割り込みに入り、ADC 結果を解析して、平均値、ピークツーピーク値、標準偏差などの各種パラメータを計算します。その後、上記の進捗を 1000 回繰り返し、各時間の平均値または最大値を取得します。

図 4-5 に、Sysconfig における ADC の基本的な構成を示します。リファレンス電圧の設定とオーバーサンプリングの設定を変更し、さまざまな条件を比較します。

Timer Mode

Desired Timer Period

Actual Timer Period

Start Timer

#### Periodic Down Counting

1 ms

1.00 ms

### Basic Configuration

#### Sample Clock Configuration

ADC Clock Source

ADC Clock Frequency

Force SYSOSC Base Freq In STOP

Force SYSOSC Base Freq In RUN

Sample Clock Divider

Calculated Sample Clock Frequency

SYSOSC

32.00 MHz

Divide by 1

32.00 MHz

#### Sampling Mode Configuration

Conversion Mode

Conversion Starting Address

Enable Repeat Mode

Sampling Mode

Trigger Source

Conversion Data Format

Desired Sample Time 0

Actual Sample Time 0

Desired Sample Time 1

Actual Sample Time 1

Single

0

Auto

Event

Binary unsigned, right aligned

62.5ns

62.50 ns

0 ms

0.00 s

図 4-5. ADC DC テスト ソフトウェア構成

ここでは、ADC の結果に基づいて計算されるいくつかのパラメータについて説明します：

- *ttlAveAnalog (V)* : ADC のデジタル結果と次の式に基づくアナログ計算結果の平均値:

$$N_{ADC} = \left(2^n - 1\right) * \frac{(V_{IN} + 0.5LSB)}{V_{R+}}$$

- *ttlDeltaSample (LSB)* : ADC の 1024 サンプルのデジタル結果について、ピークツーピーク値の平均値:

- *ttlMaxDelta (LSB)* : ADC 1024 の最大値により、デジタル結果のピークツーピーク値をサンプリングします。

- *ttlAveSample (LSB)* : ADC の 1024 サンプルのデジタル結果の平均値。

- *ttlStdErr (LSB)* : ADC の 1024 サンプルのデジタル結果の標準偏差。

- *NoiseStd (V)* : ADC の 1024 サンプルのデジタル結果におけるノイズの RMS 値 (サンプルの電圧標準偏差に相当)。

- *SNR (1)* : ADC の 1024 サンプルのデジタル結果における信号対雑音比の平均値。

#### 4.2.2 テスト結果

表 4-1 に、テスト結果の構成を示します。注意すべき重要なパラメータは *ttlDeltaSample* と SNR です。前者は ADC データのピークツーピーク値の平均レベルを示しており(表でリファレンス電圧に基づいて mV 単位に換算されています)、後者は同じ入力電圧における ADC の全体的な精度を示しています。

**表 4-1. テスト結果**

| 基準電圧    | オーバーサンプリング数 / Den | ttlDeltaSample (mV) に基づくピークツーピーク値 | 有効分解能 (ビット) |

|---------|-------------------|-----------------------------------|-------------|

| 内蔵 VDDA | 1/1               | 10.5                              | 10.598      |

|         | 4/2               | 4.8                               | 11.53       |

|         | 16/4              | 1.6                               | 12.935      |

|         | 128/8             | 0                                 | 16.440      |

| 内部 2.5V | 1/1               | 10.4                              | 10.526      |

| 内部 1.4V | 1/1               | 11.3                              | 9.770       |

| 外部 VDD  | 1/1               | 11.3                              | 11.521      |

| 外部 2.5V | 1/1               | 7.3                               | 10.925      |

#### 4.2.3 結果の分析と結論

- 分析と結論

この情報は、次のテスト結果で確認できます。

- オーバーサンプリングなしで、異なる基準電圧の *ttlDeltaSample* 値に基づくピークツーピーク値を確認すると、「external 2.5」だけが大幅に低く、その他はほぼ同じピークツーピーク電圧となっています。ピークツーピーク電圧は ADC 入力のスペイクにより発生します。その値は ADC の内部ノイズやリファレンスノイズよりもはるかに大きく(さらに、6× 標準偏差で計算したピークツーピーク値よりも大きいため)、基準電圧が異なっても結果が似通ってしまい、リファレンス電圧ごとの性能差を反映できません。

- オーバーサンプリングは、入力ノイズの低減と ADC 出力 SNR の向上を実現できます。オーバーサンプリングで収集するサンプル数が多いほど、SNR は大きくなります。ただし、有効なサンプリング周波数が低下する結果にもなります。

- さまざまリファレンス電圧の有効分解能を比較すると、同じ DC 入力でリファレンスの性能を得ることができます。

#### 外部 VDD 3.3V > 外部 2.5V > 内部 VDDA > 内部 2.5V > 内部 1.4V

- 外部リファレンスは一般的に内部リファレンスより性能が良いものの、その分コストと PCB 面積が増加します。

- 「信号ノイズ > 量子化ノイズ」の場合、より高い基準電圧を用いることで分解能が向上する可能性があります。ここでいう信号ノイズとは、リファレンスノイズ、熱雑音、その他入力信号に加わるノイズを含みます。

- 「信号ノイズ < 量子化ノイズ」の場合、リファレンス電圧を下げる量と量子化ノイズが減少し、分解能と精度の向上につながることがあります。ADC LSB は、ADC の精度の上限を決定します。

- 発言

- 上記のテスト結果は、MSPM0G3507 ADC EVM ボード上での結果のみを反映したものです。お客様のアプリケーションでの実際の ADC 性能は、外部リファレンス電圧の精度やレイアウトに大きく左右されます。上記の結果は再現性が保証されるものではなく、実際の ADC アプリケーション環境では、さらに良い結果が得られる場合もあります。

- 上記の結果は DC 入力での ADC テスト結果のみを反映したものであり、実効分解能は ENOB とは同じ概念ではありません。そのため、デバイス固有のデータシートに記載されている AC パラメータとは一致しません。

- 低精度のリファレンス電圧源を選択したり、レイアウトや配線が不適切な場合、外部リファレンス ADC のサンプリング精度が内部リファレンス電圧ほど高くないことがあります。

## 5 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

**Changes from OCTOBER 31, 2024 to NOVEMBER 30, 2025 (from Revision \* (October 2024) to

Revision A (November 2025))**

|                       | Page |

|-----------------------|------|

| • ADC CPU ポーリング方式を追加。 | 11   |

---

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月