*Application Note***並列接続した低抵抗電流センス抵抗のレイアウトのベスト プラクティス**

Mallika Senthil, Javier Contreras

**概要**

高精度の電流測定は、モーター制御、パワー マネージメント、エネルギー監視システムの基本的な要件です。電流トランス (CT) など従来の検出技法のうち、電流シャントは最も信頼性が高く、コスト効率の優れた直接的な測定アプローチを実現できます。

電流検出には一般的に、数  $\mu\Omega$  または  $m\Omega$  の電流シャント抵抗が使用されます。しかし、抵抗値が数  $\mu\Omega$  程度の低抵抗値を使用した電圧測定は、PCB パターン抵抗、温度係数 (TCR)、および半田抵抗の影響を受ける可能性が高くなります。電流センス抵抗を並列に実装する場合、この効果はさらに困難になります。このアプリケーション ノートは、シャントを並列設計する際のレイアウトのベスト プラクティスと検討事項について説明します。

**目次**

|                                  |    |

|----------------------------------|----|

| 1 はじめに.....                      | 2  |

| 2 レイアウトのベスト プラクティスとシミュレーション..... | 4  |

| 3 結果.....                        | 7  |

| 4 まとめ.....                       | 8  |

| 5 付加.....                        | 8  |

| 6 参考資料.....                      | 10 |

**商標**

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

電流シャント抵抗を並列に配置することは、特に大電流アプリケーションでは一般的な設計方法です。これにより、電流を複数の抵抗に分散するため、電力の増加と放熱性能の改善を実現できます。さらに、比較的安価でより簡単に入手できる、小型のシャントを使用することもできます。

また、シャントを並列に接続すると実効抵抗が低くなるので、シャントの両端での電圧降下が最小限に抑えられ、電力損失が低減され ( $P = I^2R$ )、システム効率の向上につながります。さらに、大電流向けに設計された 1 つのシャント抵抗は物理的なサイズを大きくすることができるため、寄生インダクタンスも大きくなります。複数のより小型の抵抗を並列に使用すると、シャントの全体的なインダクタンスを低減できます。モータードライブや電源など、インダクタンスによって電圧スパイクや測定誤差が発生する可能性のある高速スイッチング回路において、これは特に重要です。

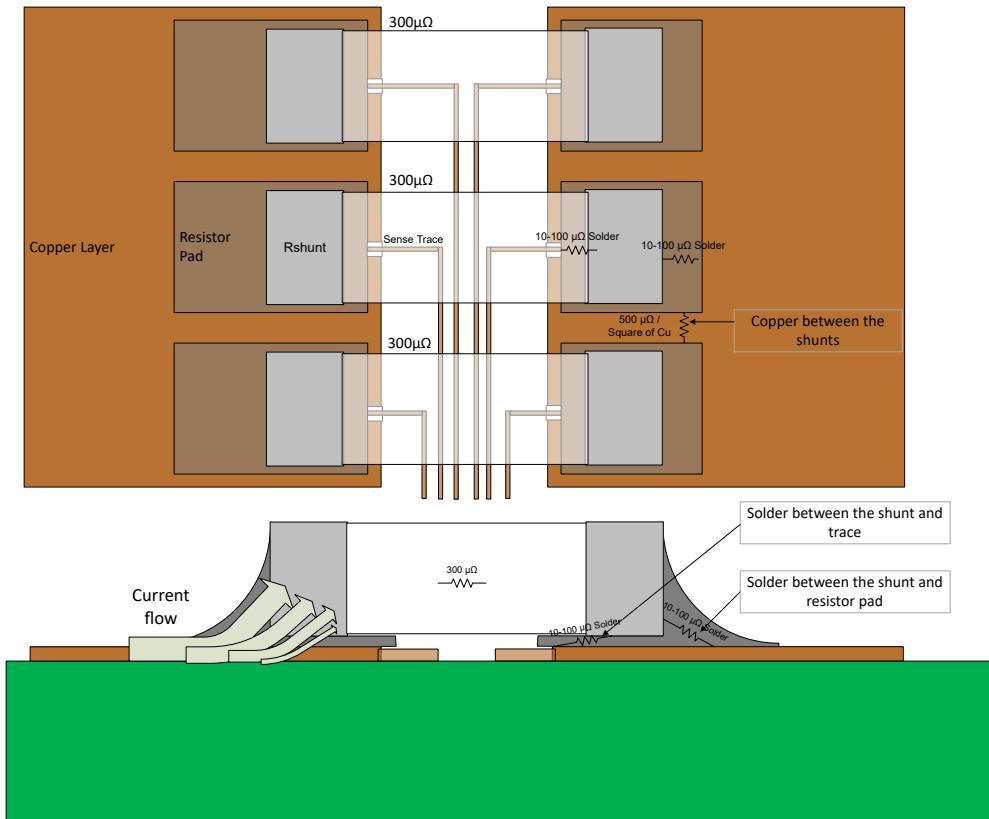

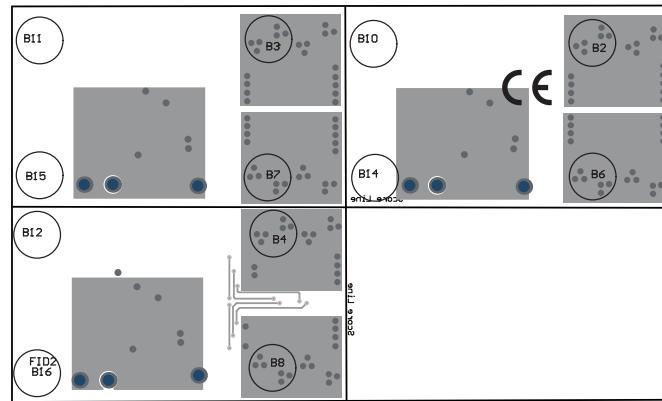

一方、並列シャント設計では、複数の抵抗の間で電流を均等に分割することは困難であるため、電流共有が不均一になることもあります。製造許容誤差に起因する抵抗の変動と、PCB パターンの抵抗の違いにより、各抵抗に生じる電流分布が不均衡になります。これにより、1 つの抵抗が意図した以上に多くの電流を流し、過熱が発生する可能性があります。これによって抵抗が変化し、不均衡がさらに悪化する可能性があります。図 1-1 に、 $\mu\Omega$  の範囲のシャント抵抗を使用すると重要になる可能性のある、さまざまな抵抗源を示します。

シャント抵抗の他に、シャントと抵抗パッドの間の半田付け、シャントとパターンの間の半田付け、シャントの周囲の銅箔などの補助抵抗は、実効抵抗に寄与し、図 1-1 に示すように、それぞれ約  $10 \sim 100\mu\Omega$ 、 $1 \sim 10\mu\Omega$ 、 $500\mu\Omega/\text{平方}$  となります。

図 1-1. 並列シャントレイアウトの抵抗源

高精度の並列シャント設計を行うには、非常に慎重で対称的な PCB レイアウトが必要です。レイアウトでは、銅、半田付け、およびパターン抵抗が確実に補償され、シャント抵抗が全体的なシャント電圧降下に主に寄与するようにする必要があります。電流共有が不均一になる問題を軽減するために、各抵抗に接続するパターンは、長さと幅をできるだけ同一にする必要があります。さらに、電流がセンス パターンを通過するのではなく、シャントを通過するパスを優先するようにする必要があります。

パターン抵抗の影響を最小限に抑える方法の 1 つは、ケルビン接続を使うことです。ただし、並列接続した複数のシャントが関係する場合、中央の対称ポイントから電圧が測定されているか、すべてのシャントに独立したケルビン接続があることを確認することが重要です。そうしないと、測定精度が低下します。

本書では、シャントベースの電流検出における総シャント電圧降下に対する、さまざまな並列抵抗レイアウトの有効性を確認します。この分析は、TINA-TI シミュレーションと PCB 実験測定によって裏付けられています。入力バイアス電流が最大 3nA である TI の超高精度電流センス アンプの 1 つである INA190 を使用して設計する際に、レイアウト手法を実現するための推奨事項が掲載されています。この推奨事項は、複数のシャント間での適切な電流共有を確保するのに役立ちます。このレイアウトは、追加の入力バイアス電流を考慮に入れることで、当社の製品ラインアップ内にある他のデバイスに適用することができます。

## 2 レイアウトのベスト プラクティスとシミュレーション

レイアウトがシャント両端の合計電圧降下に及ぼす影響を示すため、3つのTINA-TIシミュレーションを実行してさまざまな設計アプローチを表しました。以下のセクションでは、パターンの形状とシャント配置が全体的な実効シャント電圧に及ぼす影響について詳しく説明します。

このデザインでは、 $270\mu\Omega$ 、 $300\mu\Omega$ 、 $330\mu\Omega$ の3個のシャント抵抗値を使用しました。これらの値の10%の変動は、実際のアプリケーションで発生するワーストケースの許容誤差や抵抗の変動をシミュレートしています。補助抵抗の影響を最大化するため、 $\mu\Omega$ の範囲内の複数の抵抗が選定されました。これらの抵抗のインピーダンスはシャントの抵抗に匹敵するためです。

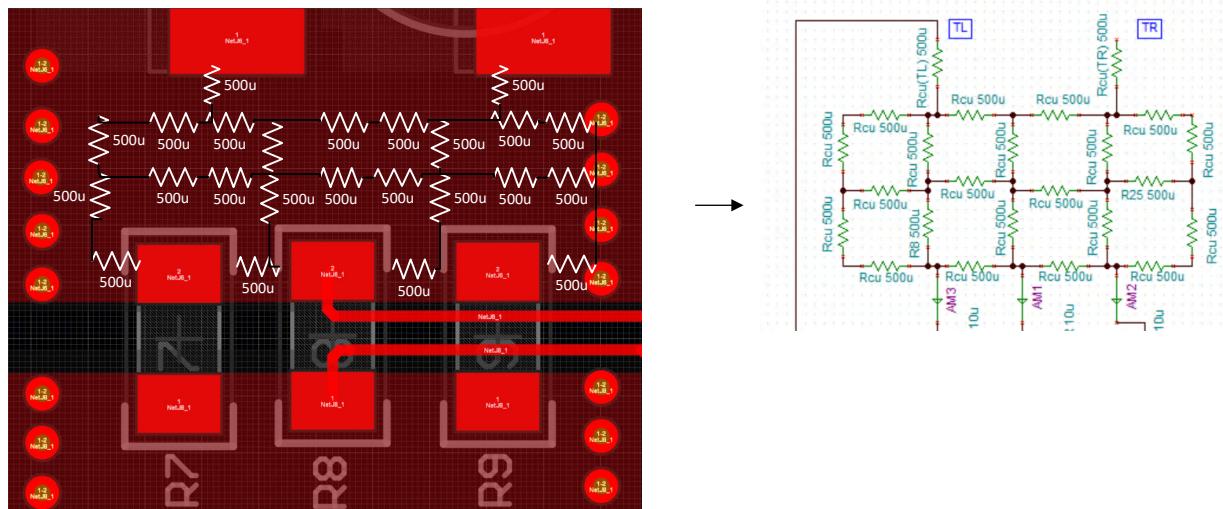

TINA-TIシミュレーションの部品と構成の詳細のリストを以下に示します(図2-1)。

- 3つのアプローチすべてで、シャントに20Aの電流が流れています

- $R_{solder\_SR}$ と $R_{solder\_ST}$ は、それぞれシャント抵抗パッドとシャントパターンの間の半田付け抵抗を表します

- $R_{cu}$ と $R_{trace}$ は、銅層に起因するシャント間のシミュレーション抵抗です

- 出力電圧を上回る電流源(lb)は、INA190の入力バイアス電流(3nA)を表します

- $R_{cu(TL)}$ 、 $R_{cu(TR)}$ 、 $R_{cu(BL)}$ 、 $R_{cu(BR)}$ は、表面実装スペードコネクタに関連する抵抗を表しています

- INA190の理想的なゲインステージをシミュレートするために電圧制御電圧源を使用しており、200V/Vに設定されています

パターン抵抗( $10m\Omega$ 、 $20m\Omega$ 、 $30m\Omega$ )は、Saturn PCB Design Toolkitのパターン抵抗率の計算に基づく、長さに依存する近似値です。銅抵抗は、1オンス銅のシート抵抗が $500\mu\Omega/\text{平方}$ であるという概念に基づいています。シャントの両側に合計2個のスペードコネクタ(図5-4)があり、このコネクタを経由して回路に電流が供給されるため、たとえば5個の接続が可能です。右上から右下(TR-BR)、右上から左下(TR-BL)、左上から右下(TL-BR)、左上から左下(TL-BL)、そして両方(TR-TLからBR-BL)です。

複雑な抵抗ネットワーク(図5-5)では、電流が発生する総抵抗は、取得される特定のパスに大きく依存します。表2-1に、レイアウト2と3のシミュレーション結果を示します。これらのレイアウトでは、電流パスのさまざまな組み合わせを使用しています。

表2-1. 現在のパスの組み合わせ

| 電流パス              | レイアウト2 Vout (mV) | レイアウト3 Vout (mV) |

|-------------------|------------------|------------------|

| TL-BR             | 346.1            | 399.04           |

| TR-BR             | 350.03           | 406.63           |

| TL-BL             | 342.17           | 395.2            |

| TR-BL             | 346.1            | 399.04           |

| 両方(TRTL)-両方(BRBL) | 346.09           | 399.02           |

表2-1から、電流フローの最適な組み合わせは、TL-BR、TR-BL、または両方-両方であると推測します。補足セクションの図5-5は、シミュレーションの抵抗ネットワークがPCBレイアウト用にどのように設計されたかを示しています。

3つのレイアウトは、いずれも確立されたケルビン検出の原理を使用しています。これは、特に、値の小さいシャント抵抗で高精度を実現するうえで非常に重要なことであるためです。さらに、 $270\mu\Omega$ 、 $300\mu\Omega$ 、 $330\mu\Omega$ のRshuntsが並列に配置されると、実効抵抗は $99.3311$ ( $R_{\text{reflective}} = 1/((1/270\mu\Omega) + (1/300\mu\Omega) + (1/330\mu\Omega))$ となり、 $V_{\text{out}}$ は**397.32mV**( $99.3311\mu\Omega \times 20A \times 200V/V$ )と予想されます。次の3つのレイアウトは、期待値にできるだけ近づけようとしています。

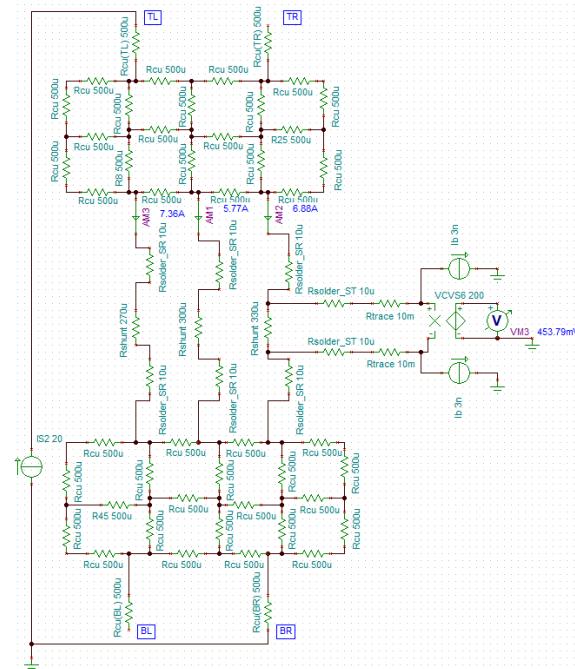

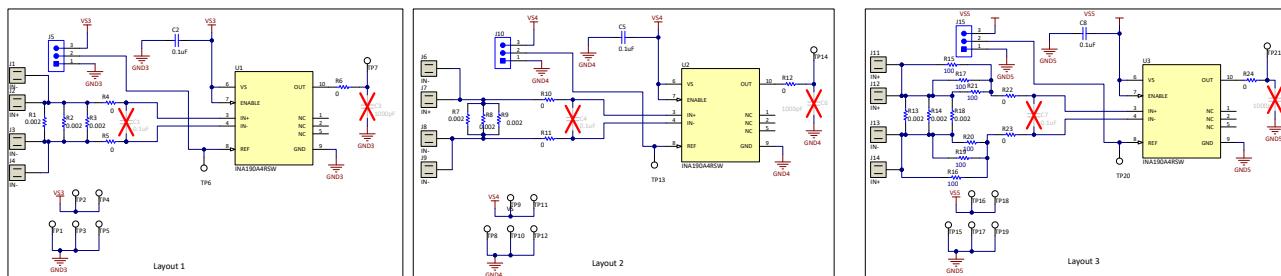

図 2-1. レイアウト 1: シャントからデバイスに最も近いケルビン検出

図 2-1 では、センスパターンは、デバイスに最も近いシャントに接続するように設計されています。センスパターンは大電流パスのさらに下からシャント抵抗をタップするため、実効シャント電圧降下に半田接合部とパターン間の電圧降下が含まれます。

これは、差動測定パスに意図的に最大量の不要な外部寄生抵抗を導入しており、最大出力電圧オフセット (56.47mV)、つまり測定された  $V_{out}$  と予想される  $V_{out}$  の差が最大になるという、悪いレイアウトの例です。

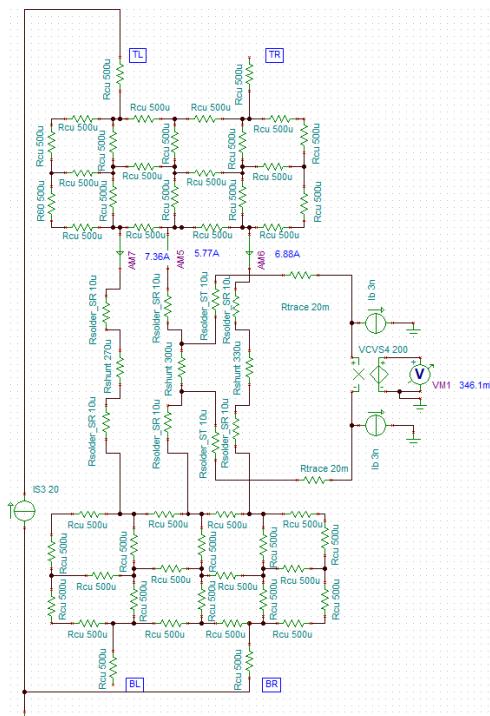

図 2-2. レイアウト 2: 中間シャントからのケルビン検出

レイアウト 2 には、中央のシャントにケルビン接続が設定されています。中間シャントに比べて抵抗の低い並列経路で電流が流れるため、中間シャントを流れる電流は比較的少なくなります (5.77A)。さらに、銅層はシャントではなく電流が流れるための代替経路を多数提供するため、PCB の銅層ではシャント全体の電圧降下よりも大きな電圧降下が発生します。

したがって、センターシャントからのケルビン検出は、51.22mV の出力電圧オフセットになります。

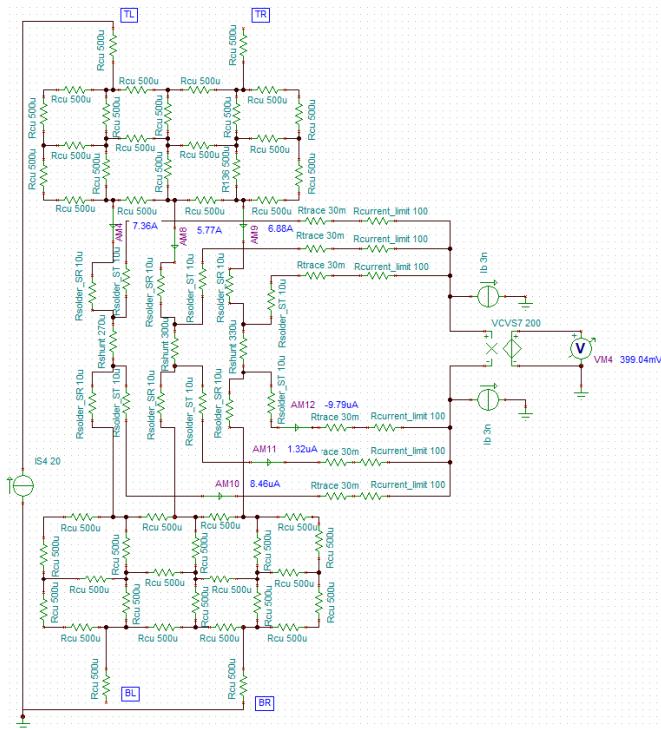

図 2-3. レイアウト 3: 各シャントからのケルビン検出 (ベストケースのレイアウト)

各シャント抵抗からケルビン接続があるため、レイアウト 3 はレイアウトのベストプラクティスと考えられています。個別のケルビン検出ラインにより、パターンと半田の寄生抵抗が総実効シャント電圧に及ぼす影響が最小限に抑えられます。また、3 つのシャント電圧降下すべてを考慮しているため、抵抗間での電流の分割方法に関係なく、正確な出力が得られます。

さらに、複数のケルビン接続を使用すると、パターンが誤って低インピーダンスのループを形成し、不要な電流の循環経路となる可能性があります。したがって、この問題を軽減して測定整合性を維持するため、シャント抵抗よりも 100 倍以上の電流制限抵抗をケルビンパターンと直列に内蔵しています。これらの抵抗がないと、数百ミリアンペアの電流がケルビンパターンで循環し、有害な熱が発生します。より大きな循環電流抑制が必要な場合は、レイアウトに示すように、より大きな制限抵抗を使用してください。これらの抵抗により、各シャント両端の電圧の平均化も可能になるため、精度が向上します。入力バイアス電流が大きいデバイスでは、電流制限抵抗が誤差を引き起こす可能性があることに注意してください。

要約すると、VM4 で測定されるシャントの両端の実効電圧降下は **397.32mV** の計算値に最も近いため、これがレイアウトのベストプラクティスとなります。

### 3 結果

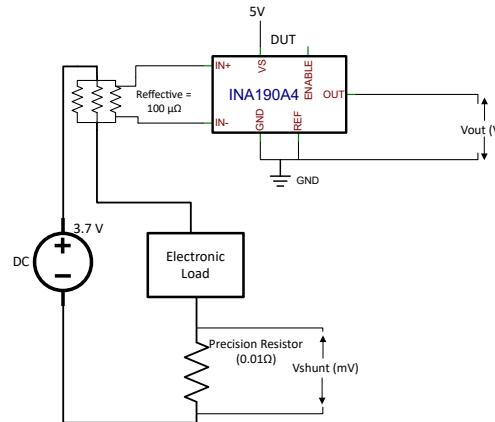

PCB レイアウトをテストするために、最初にテスト対象デバイス (DUT) を図 3-1 に示すように DC 電源 (Xantrex XHR 7.5-80)、電子負荷 (Kikusui PLZ1205W)、および高精度抵抗に接続しました。ベンチ テストで使用するシャントはすべて  $300\mu\Omega$  であるため、 $R_{\text{effective}}$  は  $100\mu\Omega$  と計算されます。TL-BR スペード コネクタの組み合わせを使用して、DUT に電流を流しました。

図 3-1. ベンチ テスト設定の回路図

ベンチ テストでは、回路に流れる負荷電流を正確に決定するため、 $0.01\Omega$  の高精度抵抗を使用しました。ここでは、Keysight 3458A デジタル マルチメータを使用して高精度抵抗 ( $V_{\text{shunt}}$ ) の電圧降下を判定しました。この値を抵抗 ( $0.01\Omega$ ) で割って、負荷電流 ( $I_{\text{load}}$  実数) を計算します。もう 1 つの Keysight 3458A を DUT の OUT ピンとグランドの間に接続し、 $V_{\text{out}}$  を測定しました。

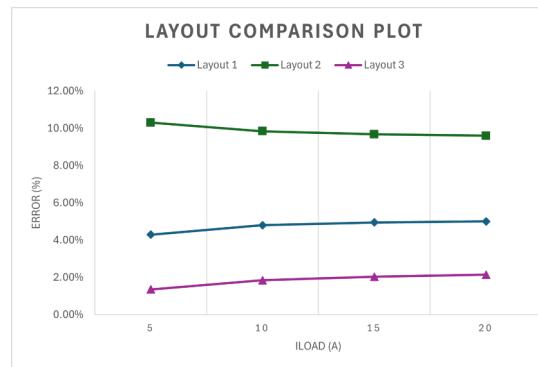

結果を 表 3-1 に示し、負荷電流に対する Error% を 図 3-2 に示します。

$$\text{Error \%} = ((| \text{Expected } V_{\text{out}} - \text{Measured } V_{\text{out}} |) / \text{Expected } V_{\text{out}}) \times 100$$

表 3-1. ベンチ テストの結果

| I <sub>load</sub> (A) | レイアウト 1                  |                         | レイアウト 2                    |                          | レイアウト 3                 |                            | 予想 DUT V <sub>out</sub> (V) |

|-----------------------|--------------------------|-------------------------|----------------------------|--------------------------|-------------------------|----------------------------|-----------------------------|

|                       | DUT V <sub>out</sub> (V) | V <sub>shunt</sub> (mV) | I <sub>load</sub> Real (A) | DUT V <sub>out</sub> (V) | V <sub>shunt</sub> (mV) | I <sub>load</sub> Real (A) |                             |

| 5                     | 0.1042879                | 50.03929                | 5.003929                   | 0.089697                 | 50.02368                | 5.003966                   | 0.1013517                   |

| 10                    | 0.2095919                | 100.0095                | 10.00095                   | 0.180312                 | 100.0349                | 10.004928                  | 0.2036846                   |

| 15                    | 0.3148474                | 150.0678                | 15.00678                   | 0.27096                  | 150.0546                | 15.0068                    | 0.3061003                   |

| 20                    | 0.4200059                | 200.0935                | 20.00935                   | 0.361594                 | 200.0807                | 20.00913                   | 0.4085625                   |

|                       |                          |                         |                            |                          |                         |                            | 20.00807                    |

|                       |                          |                         |                            |                          |                         |                            | 0.400                       |

図 3-2. レイアウトの比較プロット

## 4 まとめ

このホワイトペーパーでは、PCB パターン、半田、銅プレーン抵抗などの寄生効果に対する抵抗値が小さいシャントの課題と、高い感受性について説明しました。これらの問題を軽減するために、本書では TINA-TI シミュレーションとベンチテストデータを通じて、3 つの PCB レイアウトにわたるばらつきについても説明しました。これらの傾向は同様でした。レイアウト 1 のシミュレーションでの出力電圧オフセットは最大ですが、レイアウト 2 で測定された出力オフセットはより大きなものでした。これは、半田抵抗とシャント抵抗の変動が小さいためであると考えられます。レイアウト 1 と 2 で測定された  $V_{out}$  は、シミュレーションの結果を反映します。最後に、シミュレーションとベンチテストの両方で見られるように、レイアウト 3 は  $V_{out}$  のオフセットが最小であるため、最も堅牢性が高く効果的であることが証明されています。

## 5 付加

### 補足図

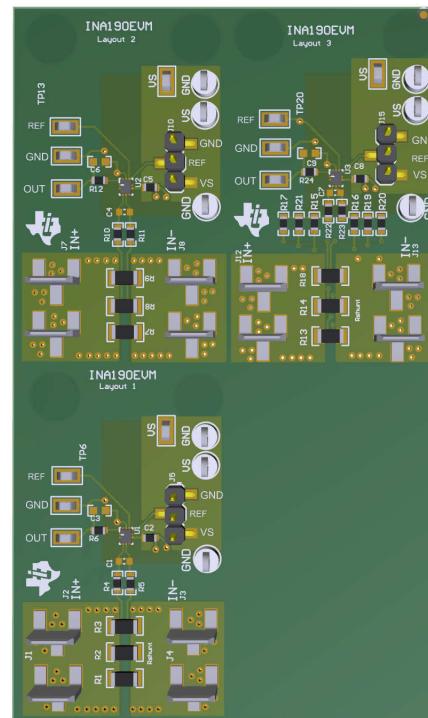

図 5-1. INA190 をベースとする並列シャントの回路図

INA190EVM

Layout 1

INA190EVM

Layout 2

INA190EVM

Layout 3

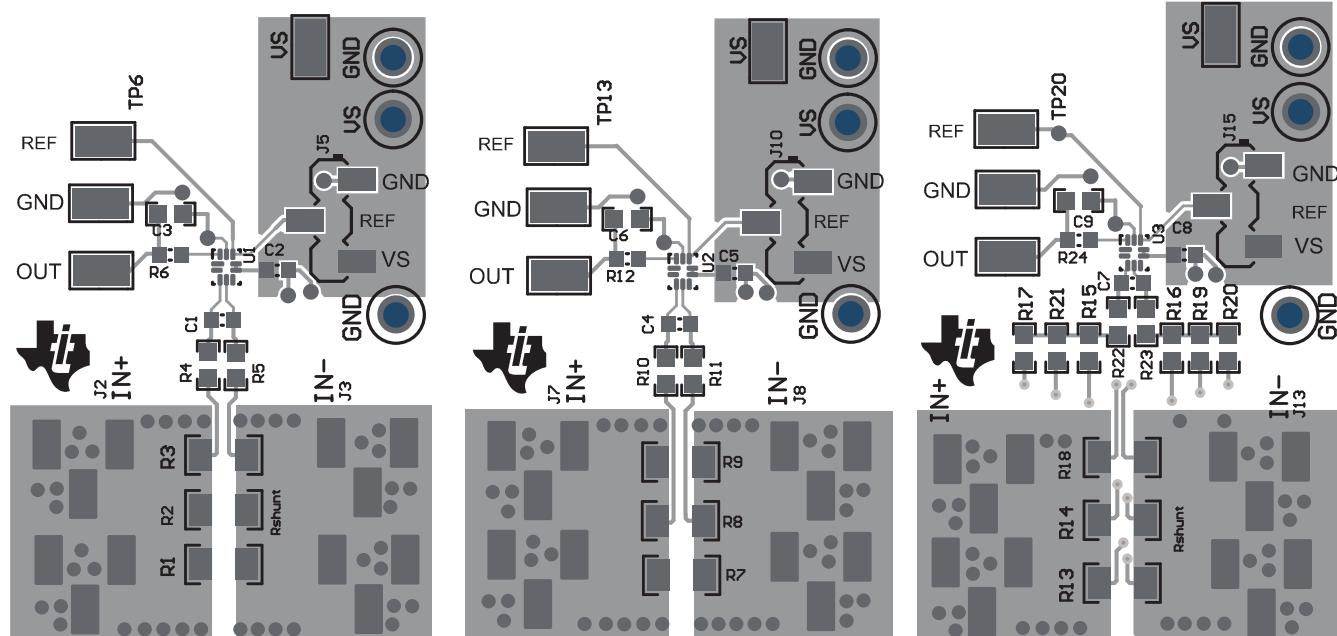

図 5-2. 上面 PCB レイアウト

図 5-3. 底面 PCB レイアウト

図 5-4. PCB レイアウトの 3D ビュー

図 5-5. 抵抗ネットワークの構成

## 6 参考資料

- ・テキサスインスツルメンツおよびDesignSoft、TINA-TI アナログシミュレーションソフトウェア(バージョン X.9.3.200.277 SF-TI)、ソフトウェア。

- ・Voltera チーム。(2018 年 10 月 31 日)。「抵抗、抵抗率、およびシート抵抗」<https://www.voltera.io/blog/resistance-resistivity-and-sheet-resistance>

- ・Gou, X., Tang, Z., Gao, Y., Chen, K., & Wang, H. (2023)。「複数の抵抗を並列に接続した電流検出トポロジとその保護回路。」*応用科学*、13(14)、8382. <https://doi.org/10.3390/app13148382>

- ・KOA Speer Electronics、「電流検出抵抗の並列配置」(TN003-v0100)

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月