*Application Note***UCC33420-Q1 の CISPR25 Class 5 に合格する方法**

*Manuel Alva*

**概要**

UCC33xx0-Q1 は、64MHz スイッチング周波数で動作する統合絶縁型バイアス (IIB) DC/DC モジュールのファミリです。高周波があるため、適切なレイアウトと EMI 部品を使用しない場合、低 EMI を目標とすることは課題になる可能性があります。このアプリケーション ノートでは、UCC33xx0-Q1 ファミリ用の CISPR25 class 5 に合格する方法を説明します。適切なセットアップのためのガイドライン、CISPR 25 規格に適合し、伝導エミッション (CE) と放射エミッション (RE) の両方で低放射を達成するための EMI フィルタ部品の選択および PCB レイアウトについて説明します。CISPR25 の制限に合格することが必要なのは、トラクション インバータ、HEV/EV 充電、バッテリ管理システム (BMS)、オンボード チャージャ (OBC) などの車載アプリケーションです。対象となる読者は、フィールド アプリケーション、システム、アプリケーション エンジニア、および DC/DC コンバータの EMI に関するエンジニアです。

**目次**

|                                      |           |

|--------------------------------------|-----------|

| <b>1 はじめに</b> .....                  | <b>2</b>  |

| <b>2 セットアップ、EMI フィルタ、レイアウト</b> ..... | <b>3</b>  |

| 2.1 構成.....                          | 3         |

| 2.2 EMI フィルタ.....                    | 5         |

| 2.3 PCB レイアウト.....                   | 8         |

| 2.4 フラッデー シールド.....                  | 9         |

| 2.5 回路図.....                         | 9         |

| 2.6 レイアウト.....                       | 10        |

| 2.7 EMI の結果.....                     | 11        |

| 2.8 部品表: BOM.....                    | 13        |

| <b>3 まとめ</b> .....                   | <b>14</b> |

| <b>4 参考資料</b> .....                  | <b>14</b> |

**商標**

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

部品フットプリントが小さく、電力密度が高い IIB モジュールなど、より小型の DC/DC バイアス電源の需要がますます高まっています。高周波電力変換を使用した優れた絶縁技術を採用した IC レベルトランスは、小型 IC パッケージと高い電力密度を実現する主なテクノロジードライバです。UCC33xx0-Q1 デバイス ファミリは次を備えているため、このトレンドの一部となっています: 4x5x1-mm<sup>3</sup>パッケージと 64MHz スイッチング周波数。

1 次側から 2 次側に電力を供給するため、UCC33xx0-Q1 は、負荷条件に応じて 100kHz ~ 500kHz の範囲のバースト周波数を使用します。バースト周波数は低周波数バケットとして説明でき、これらのバケット内でデバイスは 64MHz の高周波でスイッチングします。

エミッションを制限以下に抑えるには、CE と RE を適切に設定することが重要です。LISN を DUT に接続するには、密結合された接続が存在する必要があります。スイッチング周波数 64MHz は CISPR25 CE および RE では VHF 帯域に隣接しています。また、この周波数でエミッションを低減するために、デュアル DM インダクタを使用した HF パイ PI フィルタが設計されました。対数周期アンテナ (LPA) を使用する場合、30 ~ 200MHz の RE に基本 64MHz の HF 高調波が存在します。この場合に、これらの周波数を緩和するため、2 つのフェライトビーズ (FB) が選択されています。最後に、PCB フラーデーシールドを使用した適切なレイアウト、KOZ (キープ アウトゾーン)、DM インダクタと FB の下の銅カット、グランド プレーンの適切な分配により、スイッチング周波数と高調波を制限未満に維持できました。

CISPR25 class 5 は、車載アプリケーション向けの最も厳格な EMI 規格です。

## 2 セットアップ、EMI フィルタ、レイアウト

### 2.1 構成

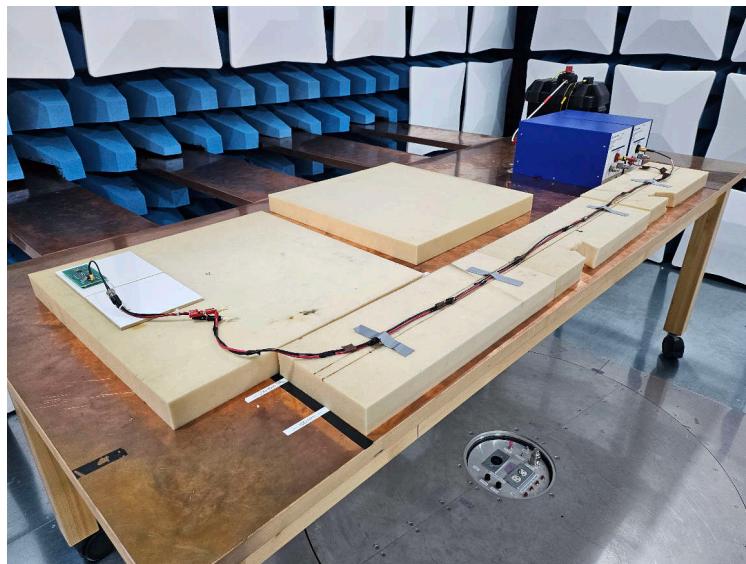

UCC33xx0-Q1 の内蔵トランスから LISN に送られる H 界が結合するのを防止するために、スイッチング ループの正とリターンは密結合して接続することが推奨されます。スイッチング ループは、12V バッテリ電源から開始します。スイッチング ループは LISN を経由し、ループは最終的に DUT PCB の入力に接続します。次の図は、CE と RE のスイッチング ループ全体の密な接続の例を示しています。

図 2-1. CISPR 25 CE 設定

図 2-2. CISPR 25 RE 設定

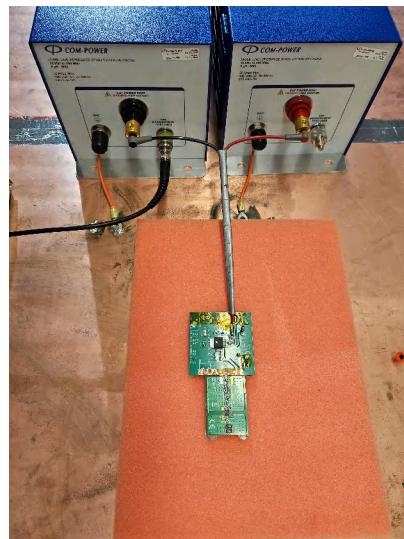

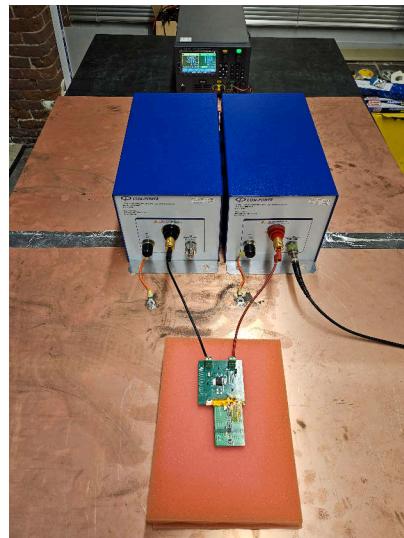

密結合接続とオープン ループ接続の比較。以下の図では、UCC33420-Q1 の CE Pout = 0.5W の密結合接続とオープン ループ接続の違いを示しています。

図 2-3. 密結合リード

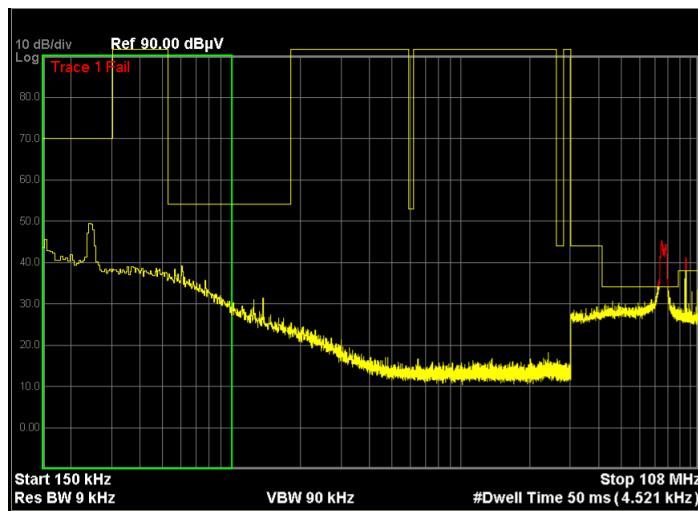

図 2-4. CISPR 25 CE 密結合リード、 $P_{out} = 0.5W$

図 2-5. オープンリード

図 2-6. CISPR 25 CE オープン リード、 $P_{out} = 0.5\text{W}$

## 2.2 EMI フィルタ

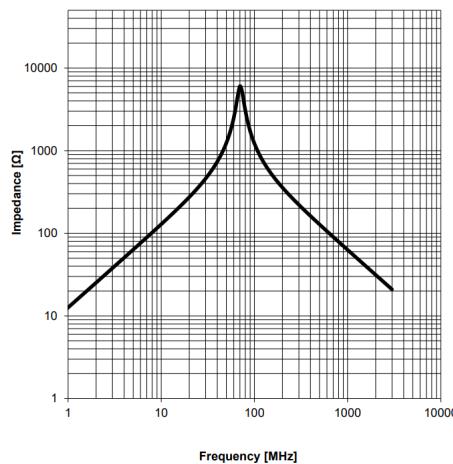

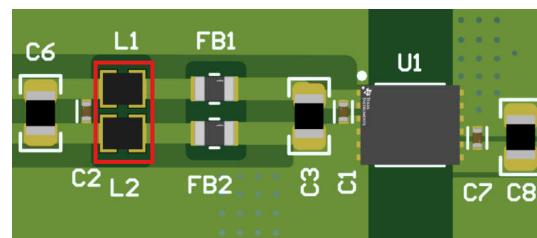

スイッチング周波数  $f_{sw} = 64\text{MHz}$  に起因するノイズを低減するために、デュアル DM インダクタ（上側と下側）を使用したパイフィルタを使用しました。デュアルインダクタの理由は、高い CM ノイズを避けるためのスイッチングループでのインピーダンス整合です。インダクタは、インピーダンスと周波数の比較プロット、シールド、サイズ、電流定格に基づいて選択されました。高 SRF (自己共振周波数) のフルシールド 0806 モールドインダクタを選択しました。表 2-1 に、電力レベルに応じた DM インダクタの選択を示します。

図 2-7. インピーダンスと周波数の関係 - DM インダクタ

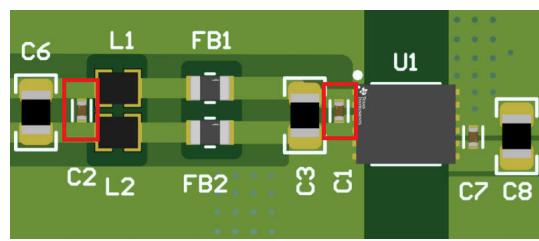

図 2-8. PCB 内のデュアル DM インダクタ

表 2-1. DM インダクタの選択

| パワー レベル | DM インダクタ                        |

|---------|---------------------------------|

| 0.5W    | PN:74479763222、2.2uH、0603、800mA |

**表 2-1. DM インダクタの選択 (続き)**

| パワー レベル | DM インダクタ                                |

|---------|-----------------------------------------|

| 1W      | PN:74438343022, 2.2uH, 2mmx1.6mm, 1.65A |

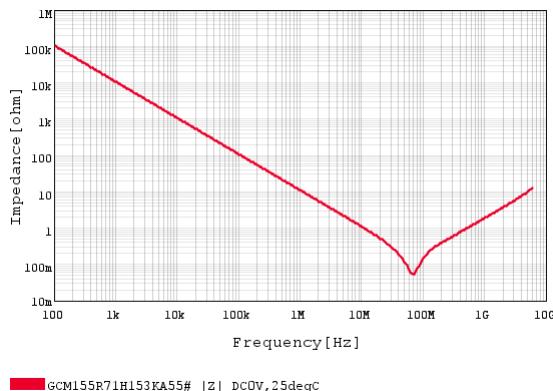

インダクタの左側に、高 SRF の 0402 50V 15nF コンデンサを配置しました。このコンデンサを使用して、インダクタと入力ピンの間に接続された 15nF を使ってパイフィルタを形成しました。

**図 2-9. インピーダンスと周波数との関係 - 0402 15nF****図 2-10. PCB の 0402 15nF コンデンサ**

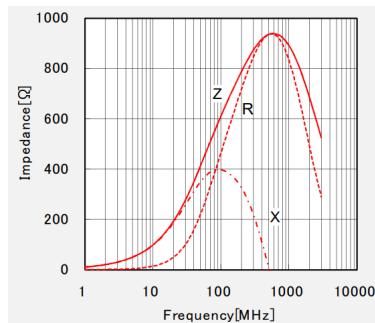

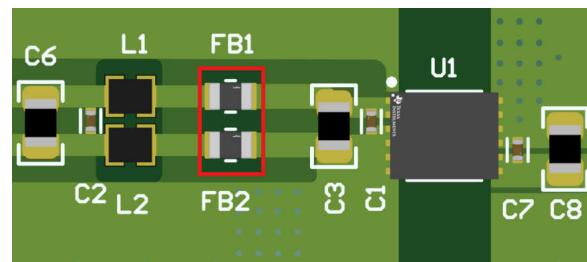

200MHz ~ 1GHz の範囲に存在する HF 電流高調波を低減するために、FB が必要です。0603、800mA フェライトビーズ、インピーダンス 925Ω(600MHz)、フルシールドが選択され、この範囲で低 EMI を実現しています。高い周波数での H 界の軽減を強化するために、これらのフェライトビーズは DUT の隣に配置されています。

**図 2-11. インピーダンスと周波数との関係 - FB**

図 2-12. PCB 内の FB

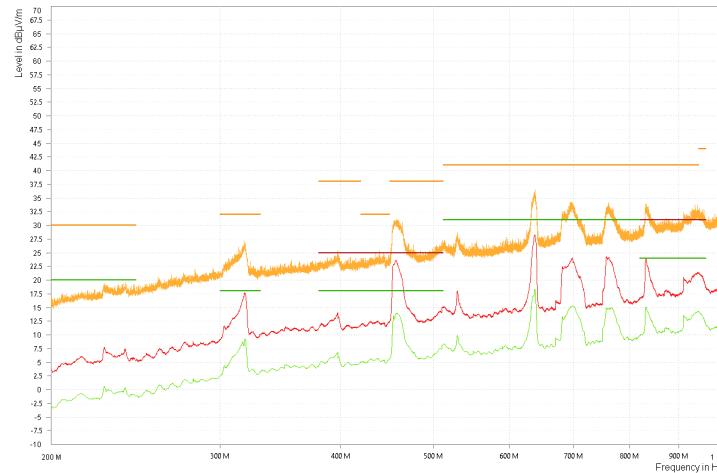

FB ありとなしの比較: 図 2-13 および図 2-14 に、UCC33420-Q1 RE Pout = 0.5W の場合の FB ありとなしの比較を示します。

図 2-13. CISPR25 RE LPA、FB あり、Pout = 0.5W

図 2-14. CISPR25 RE LPA、FB なし、Pout = 0.5W

最後に、スイッチング ループの左側に 0805 10 $\mu$ H のバイパスコンデンサを配置し、DM インダクタおよびデバイスの入力ピンの隣にある 10 $\mu$ F バイパスコンデンサと組み合わせて低周波数パイフィルタを形成しています。目標周波数は、デバイスのバースト周波数で、負荷に応じて 100 ~ 500kHz の範囲です。

## 2.3 PCB レイアウト

グランドプレーンを1次側と2次側の両方に配置することで、デバイスのグランドピンを接続するために使用するときにスイッチングループのリターン側で低インピーダンスになります。さらに、これらのプレーンはファラデー シールドとして機能し、トランジスからのH界を軽減します。この設計で可能な最大の銅の面積を適用します。

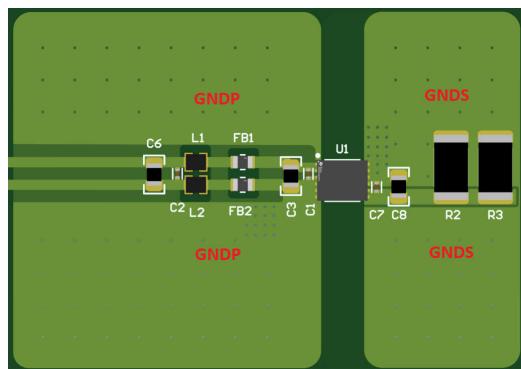

図 2-15. PCB のグランドプレーン

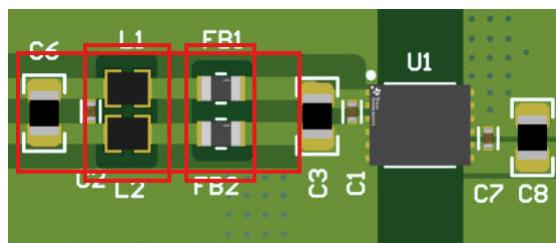

レイアウトの寄生容量を通過する HF 電流のバイパスが発生しないように、DM インダクタと FB の下にある銅を取り除くことが推奨されます。同様の理由から、EMI フィルタ領域の周囲に 1mm の KOZ を配置することをお勧めします。

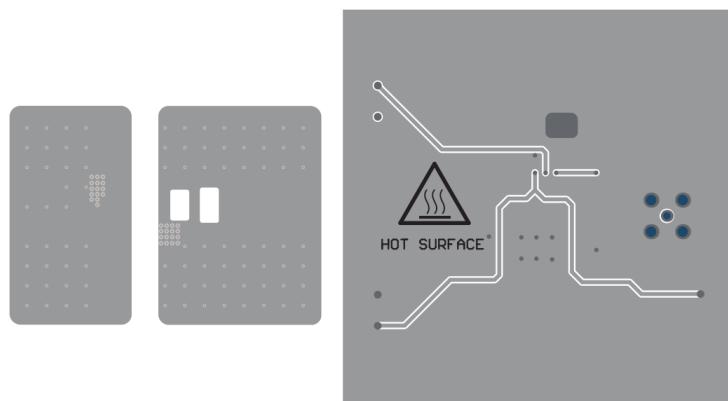

図 2-16. KOZ および DM インダクタと FB の下の銅の切断

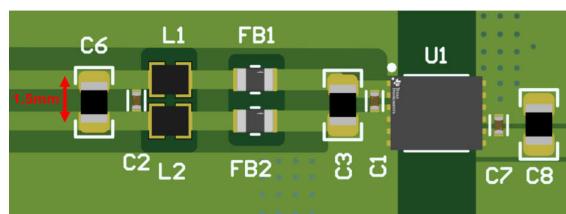

スイッチングループの両側(正とリターン)でのインピーダンス整合により、CM ノイズは最小化され、スイッチングループの距離は LISN での EMI に影響を与えません。このため、小型フットプリントの設計を維持するためにスイッチングループをできるだけ短くすることが推奨されます。ここでは、スイッチングループの距離 1.5mm が選択されています。

図 2-17. スイッチングループの距離

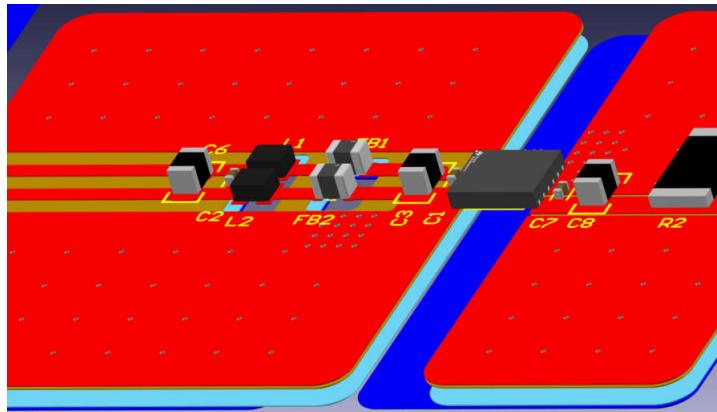

## 2.4 ファラデー シールド

PCB ファラデー シールドは、内蔵トランジスから流入する H 界を低減するために使用する手法です。デバイスの下の内層または最下層から導電性の銅を配置することで構成されます。このファラデー シールドは、元の H 界とは反対方向の H 界を生成する電流を誘導します。これらの誘導電流のバイパスを防止するために、1 次側と 2 次側のグランド プレーンの間に約 4mm の空間距離を配置することも推奨されます。これは、拡張された 2 次側グランド プレーンから 1 次側グランド プレーンを 4 mm 引き出すことで実現できます。2 層 PCB では、絶縁要件を維持するために、この空間距離が必要です。4 層 PCB の場合、ファラデー シールドは内層に配置できますが、4mm の空間距離は必要です。このシールドの周波数目標は、500MHz ~ 1GHz の間です。

図 2-18. ファラデー シールドの 3D ビュー

図 2-19. ファラデー シールドの 2D ビュー

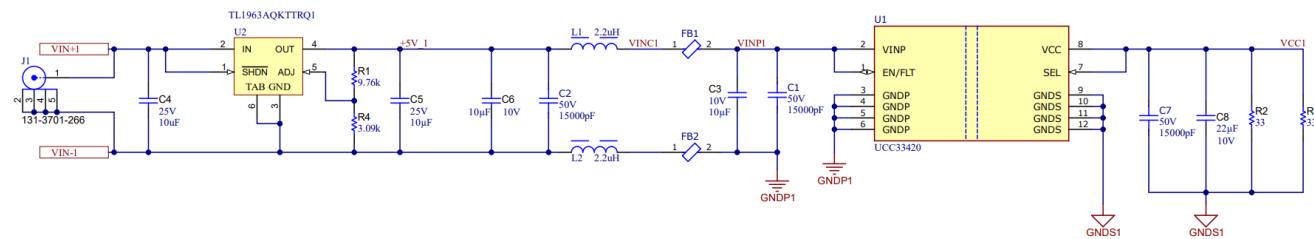

## 2.5 回路図

図 2-20. 回路図 UCC33420-Q1 CISPR 25

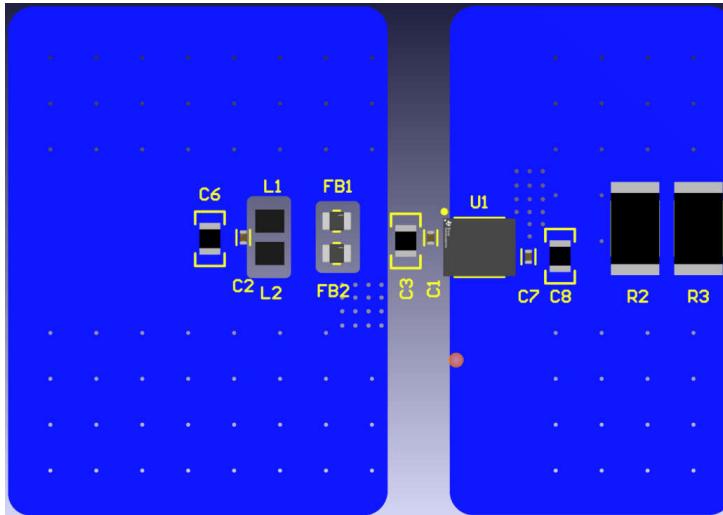

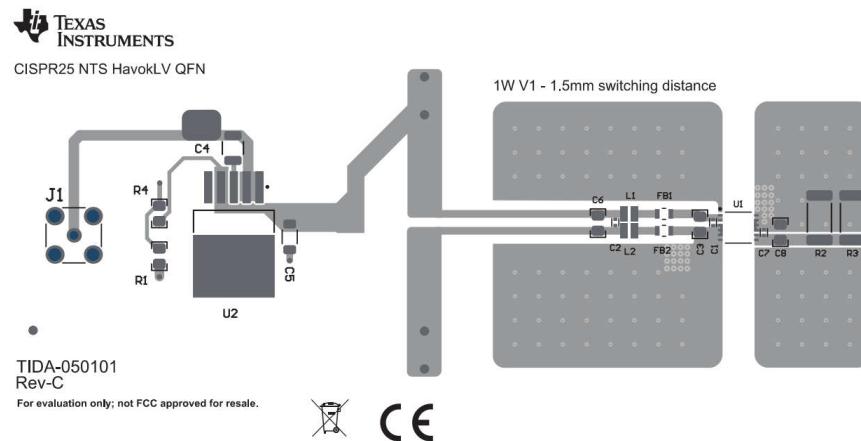

## 2.6 レイアウト

図 2-21. 上層 CISPR 25

図 2-22. 内層 CISPR 25

図 2-23. 最下層 CISPR 25

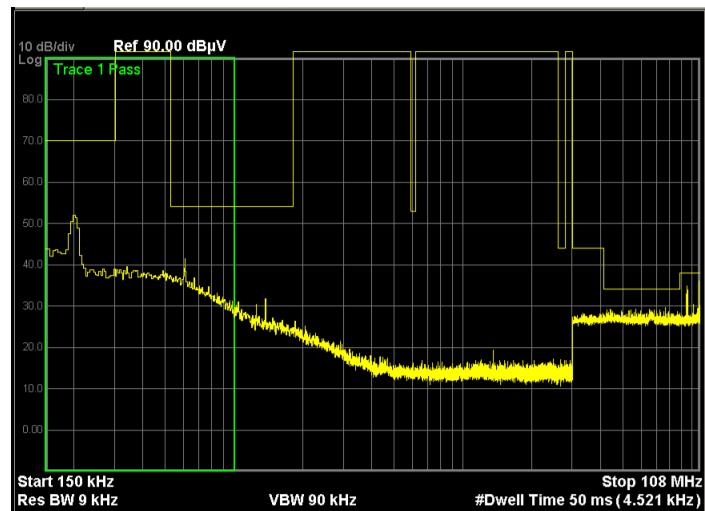

## 2.7 EMI の結果

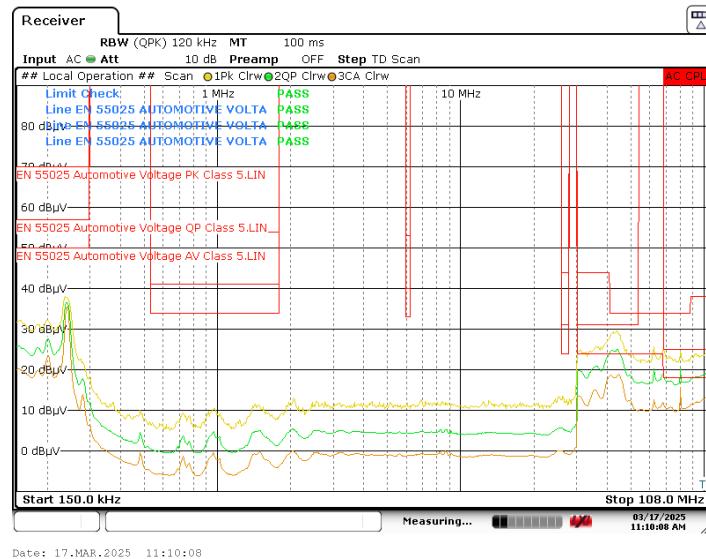

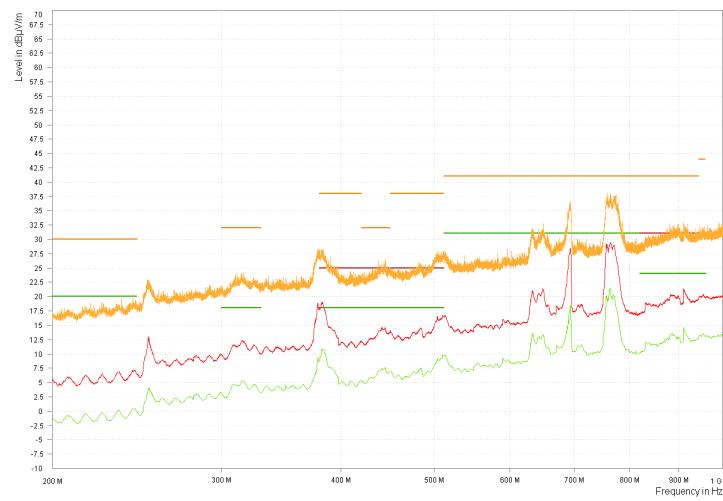

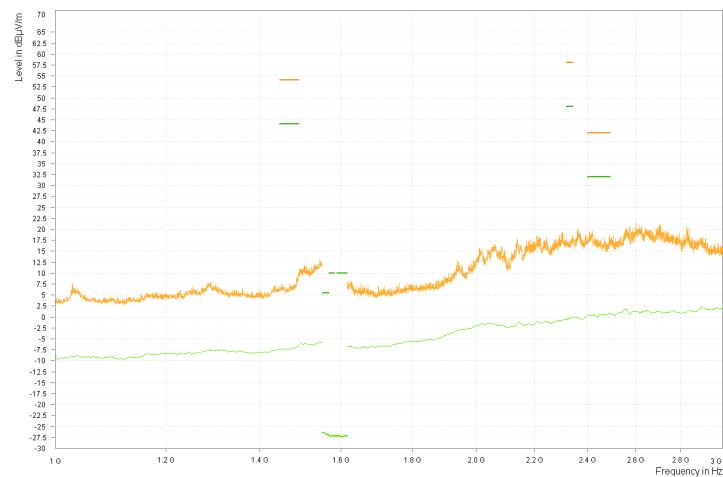

図 2-24. CISPR 25 CE Pout = 1W

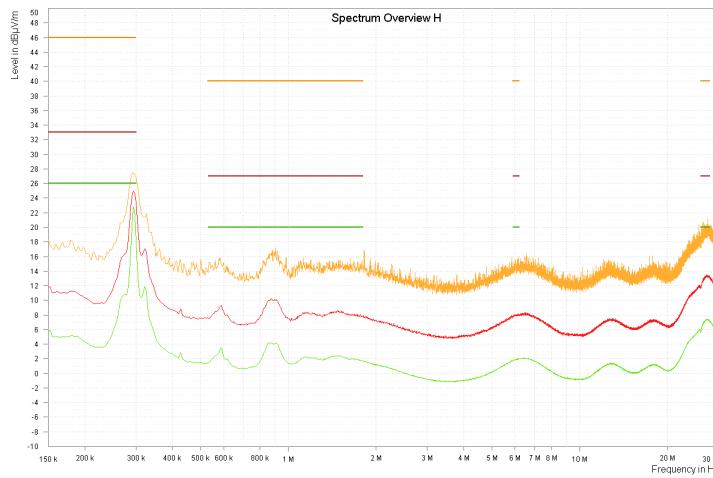

図 2-25. CISPR 25 RE モノポール Pout = 1W

図 2-26. CISPR 25 RE バイコニカル  $P_{out} = 1W$

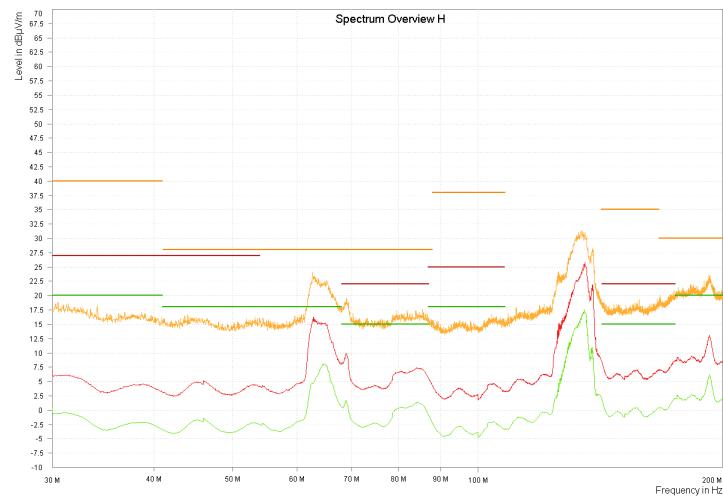

図 2-27. CISPR 25 RE LPA  $P_{out} = 1W$

図 2-28. CISPR 25 RE ホーン  $P_{out} = 1W$

## 2.8 部品表: BOM

表 2-2. 部品表: BOM

| 記号       | 数量 | 部品番号               | メーカー             | 説明                                                                                                          |

|----------|----|--------------------|------------------|-------------------------------------------------------------------------------------------------------------|

| PCB1     | 1  | TIDA-050101        | 任意               | プリント基板                                                                                                      |

| C1、C2、C7 | 3  | GCM155R71H153KA55D | Murata (村田製作所)   | CAP、CERM、0.015μF、50V、±10% X7R 0402 (1005 メートル法)                                                             |

| C3、C6    | 2  | GCJ21BR71A106KE01L | MuRata           | CAP、CERM、10μF、10V、±10%、X7R、AEC-Q200 グレード 1、0805                                                             |

| C4       | 1  | GCM32ER71E106KA57L | MuRata           | CAP、CERM、10μF、25V、± 10%、X7R、AEC-Q200 グレード 1、1210                                                            |

| C5       | 1  | GRM31CR61E106MA12L | MuRata           | CAP、CERM、10μF、25V、±20%、X5R、1206                                                                             |

| C8       | 1  | GRM21BZ71A226ME15L | MuRata           | CAP、CERM、22μF、10V、±20%、X7R、0805                                                                             |

| FB1、FB2  | 2  | LCMGA160808T601RG  | Murata (村田製作所)   | 100MHz において 600Ω、1 電源ライン フェライト ビーズ 0603 (1608 メトリック)、900mA、170mΩ                                            |

| J1       | 1  | 131-3701-266       | Cinch の接続        | コネクタ、SMB、ジャック、50Ω、TH                                                                                        |

| L1、L2    | 2  | 74438343022        | Wurth Elektronik | WE-MAPI SMT パワー インダクタ、サイズ 2010、2.2μH、1.1A、270mΩ                                                             |

| R1       | 1  | RT0805BRD079K76L   | Yageo America    | RES、9.76k、0.1%、0.125W、0805                                                                                  |

| R2、R3    | 2  | CRCW251233R0JNEG   | Vishay-Dale      | RES、33、5%、1W、AEC-Q200 グレード 0、2512                                                                           |

| R4       | 1  | RT0805BRD073K09L   | Yageo America    | RES、3.09k、0.1%、0.125W、0805                                                                                  |

| U1       | 1  | UCC33420QRAQRQ1    | テキサス・インスツルメンツ    | 1.5W、高密度、>3kVRMS、絶縁型 DC/DC コンバータ                                                                            |

| U2       | 1  | TL1963AQKTRQ1      | テキサス・インスツルメンツ    | 単一出力高速過度応答 LDO、1.5A、調整可能な 1.21 ~ 20V 出力、2.1 ~ 20V 入力、5 ピン DDPAK (KTT)、-40° ~ 125°C、グリーン (RoHS 準拠、Sb/Br 非含有) |

### 3 まとめ

UCC33xx0-Q1 ファミリは、適切な EMI フィルタの選択と PCB レイアウトにより、CISPR25 Class 5 に合格します。「T 形」ケーブルを使用した密結合接続と、デュアル DM インダクタを備えた HF パイフィルタを選択しているため、CE が合格しています。RE は、EMI フィルタおよびファラデーシールドなどの PCB レイアウト手法での FB の使用、DM インダクタと FB の下でのグランドプレーン、KOZ、銅カットの使用により合格しています。

### 4 参考資料

1. 国際電気標準会議、[CISPR25 — 国際標準](#)、規格。

2. テキサスインスツルメンツ、[電源の伝導 EMI 仕様の概要](#)、マーケティングホワイトペーパー。

3. テキサス・インスツルメンツ、[UCC33420-Q1](#)、製品ページ

4. テキサスインスツルメンツ、[UCC33420-Q1 の CISPR 32 Class B に合格する方法](#)、アプリケーションノート。

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月