*Application Note***DP83822 ブラブルショーティング ガイド**

Avtar Dhaliwal, Jae Yoon

**概要**

このアプリケーションノートでは、新しいアプリケーションを評価し、予想される機能を確認するための推奨フローを紹介します。ステップバイステップの推奨事項を活用すると、DP83822 を使用した設計のボード立ち上げと初期評価を容易に実施できます。

**目次**

|                                        |    |

|----------------------------------------|----|

| <b>1 DP83822 アプリケーションの概要</b>           | 2  |

| <b>2 PHY アプリケーションのトラブルショーティングを行う</b>   | 3  |

| 2.1 回路図とレイアウトのチェックアウト                  | 3  |

| 2.2 デバイスの正常性チェック                       | 3  |

| 2.2.1 電源ランプシーケンスチェック                   | 3  |

| 2.2.2 電圧チェック                           | 5  |

| 2.2.3 RESET_N 信号をプロープします               | 6  |

| 2.2.4 RBIAS ピンのプロープ                    | 6  |

| 2.2.5 XI クロックをプロープします                  | 7  |

| 2.2.6 初期化中にストラップ ピンをプロープします            | 8  |

| 2.2.7 シリアル管理インターフェース信号のプロープ (MDC、MDIO) | 9  |

| 2.3 MDI ヘルス チェック                       | 12 |

| 2.3.1 磁気                               | 13 |

| 2.3.2 MDI 信号をプロープします                   | 14 |

| 2.3.3 リンク品質チェック                        | 15 |

| 2.3.4 ファイバ接続のデバッグ                      | 16 |

| 2.3.5 フレーム開始検出 (SFD) のデバッグ             | 18 |

| 2.3.6 コンプライアンス                         | 18 |

| 2.4 MII ヘルス チェック                       | 18 |

| 2.4.1 MII チェック                         | 18 |

| 2.4.2 RMII チェック                        | 20 |

| 2.4.3 RGMII チェック                       | 23 |

| 2.5 ループバックと PRBS                       | 26 |

| 2.5.1 ループバック モード                       | 26 |

| 2.5.2 MAC とのパケットの送受信                   | 27 |

| 2.5.3 BIST を使用してパケットを送受信しています          | 28 |

| <b>3 ツールとリファレンス</b>                    | 29 |

| 3.1 DP83822 のレジスタアクセス                  | 29 |

| 3.2 Linux でのソフトウェアおよびドライバのデバッグ         | 30 |

| 3.2.1 一般的な端子出力とソリューション                 | 30 |

| <b>4 まとめ</b>                           | 32 |

| <b>5 参考資料</b>                          | 32 |

| <b>6 改訂履歴</b>                          | 33 |

**商標**

すべての商標は、それぞれの所有者に帰属します。

## 1 DP83822 アプリケーションの概要

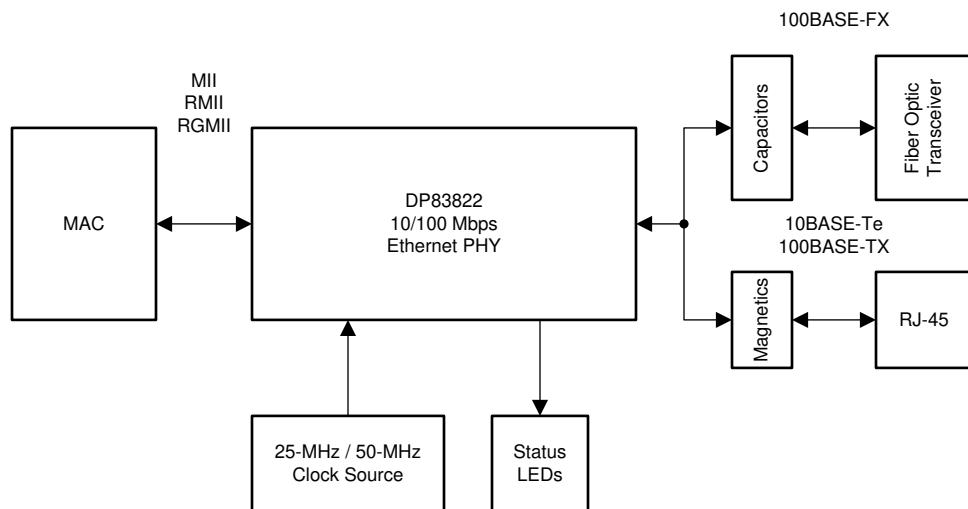

DP83822 は、過酷な産業用環境に設計された、極めて堅牢で低消費電力のシングル ポート 10/100Mbps イーサネット PHY です。DP83822 には、標準のツイストペア ケーブルを介してデータを送受信したり、外部の光ファイバ トランシーバに接続するために必要なすべての物理層機能が搭載されています。さらに、DP83822 は、標準の MII、RMII、RGMII インターフェイスを介して MAC に接続できる柔軟性を提供します。

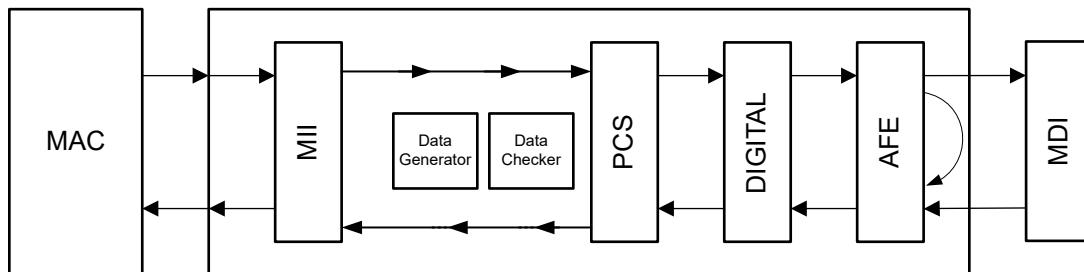

図 1-1 は、代表的な DP83822 のアプリケーションの概略システム ブロック図です。

Copyright © 2016, Texas Instruments Incorporated

図 1-1. DP83822 のブロック図

DP83822 は、Ethernet MAC と MDI に接続します。MDI への接続は、トランスとコネクタ (銅線アプリケーションの場合)、またはコンデンサとトランシーバ (光ファイバアプリケーションの場合) を介して行われます。

## 2 PHY アプリケーションのトラブルシューティングを行う

以下のセクションでは、デバッグを高レベルでアプローチし、まず広範囲に影響を与えるアプリケーション特性から始め、次に設計のより具体的な側面に焦点を当てます。

このドキュメントは、次のような一般的なイーサネットの問題を解決することを目的としています。

- レジスタにアクセスできません

- リンクを取得できない、または間欠的なリンクアップ

- リンクアップしているが、パケットエラーが表示されています

- ping ができない

特に記述のない限り、以下のセクションを順番に読み進めることを推奨します。

### 2.1 回路図とレイアウトのチェックアウト

[DP83822 回路図チェックリスト](#)と [DP838XX レイアウトチェックリスト](#)は、DP83822 の回路図とレイアウトを用いた設計のベストプラクティスを 1 つの使いやすいドキュメントにまとめたファイルです。PHY が機能するために必要な接続とコンポーネントの詳細については、このドキュメントを参照することをお勧めします。

以下のセクションでは、PHY に電源が供給され、正しく初期化された場合に予想される動作を示します。予期される動作から逸脱した場合、不適切なペリフェラル回路によるエラーが原因である可能性があります。

### 2.2 デバイスの正常性チェック

このセクションでは、デバイスの電源が供給され、正しく初期化されていることを確認するデバイスの状態チェックについて説明します。DP83822 が次の場合、このセクションはスキップできます。

- リンクパートナーに接続している場合はリンクアップ状態 (LED 表示またはレジスタステータス)、またはイーサネットケーブルが未接続の場合は FLP 信号を表示し、

- レジスタアクセスに応答する (該当する場合)。

#### 2.2.1 電源ランプシーケンスチェック

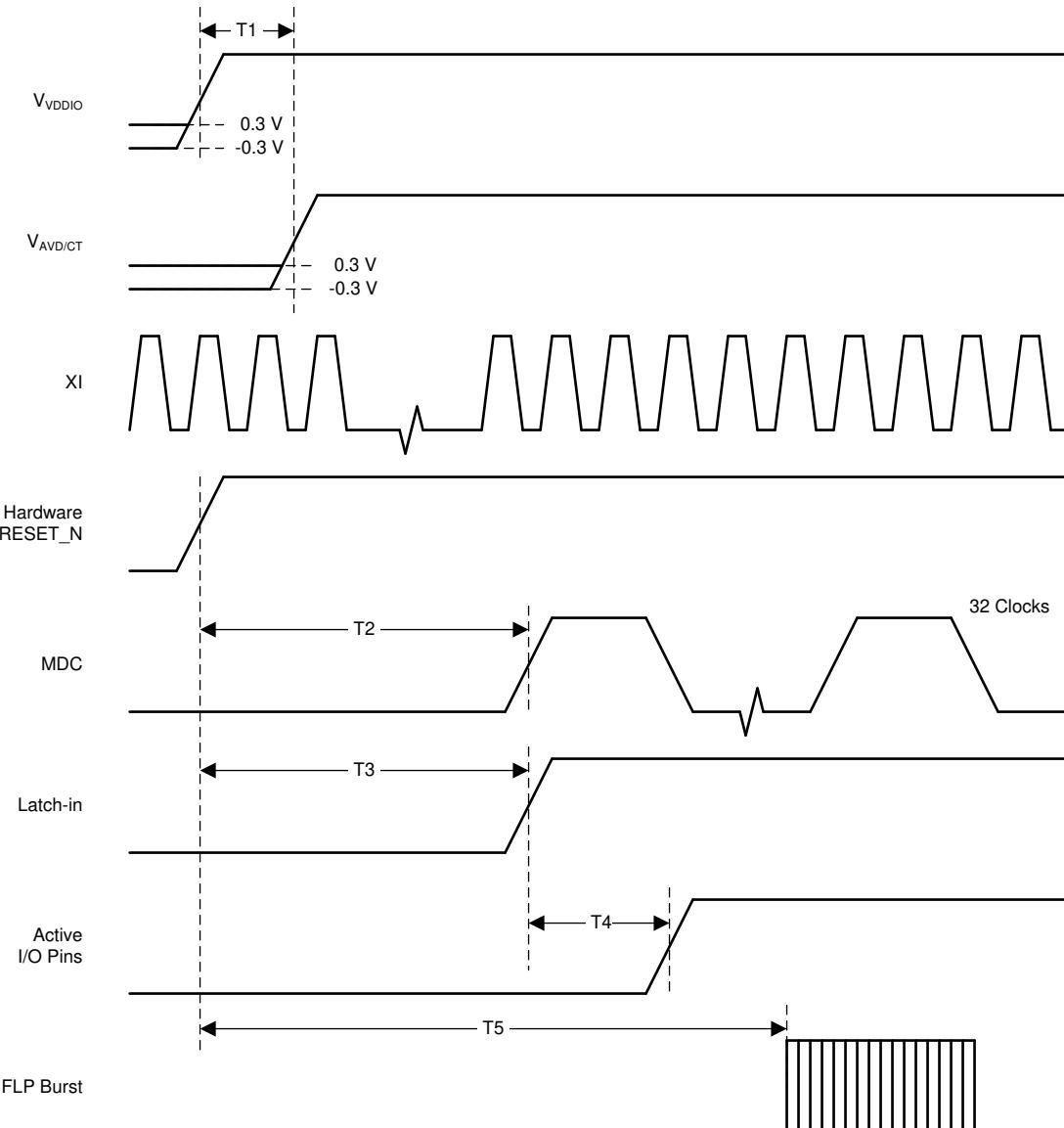

デバイスが推奨電源ランプシーケンスに従って電源供給されていることを確認してください。デバイスの電源を投入し、PHY の電圧レールをプローブして、電圧が表 2-1 で定義された制限値内であることを確認してください。パワーアップ時の電圧パラメータのタイミングが、表 2-2 および図 2-1 で定義された制限値内であることを確認してください。

表 2-1. PHY 電源電圧仕様

|              | 説明                  | 最小値   | 標準値 | 最大値   | 単位 |

|--------------|---------------------|-------|-----|-------|----|

| VDDIO        | 電源電圧: I/O = 1.8V    | 1.71  | 1.8 | 1.89  | V  |

|              | 電源電圧 I/O = 2.5V     | 2.375 | 2.5 | 2.625 |    |

|              | 電源電圧 I/O = 3.3V     | 3.15  | 3.3 | 3.45  |    |

| AVD          | 電源電圧アナログ = 3.3V     | 3.15  | 3.3 | 3.45  | V  |

|              | 電源電圧アナログ = 1.8V     | 1.71  | 1.8 | 1.89  |    |

| センタータップ (CT) | 電源電圧のセンタータップ = 3.3V | 3.15  | 3.3 | 3.45  | V  |

|              | 電源電圧のセンタータップ = 1.8V | 1.71  | 1.8 | 1.89  |    |

表 2-2. タイミング要件: パワーアップのタイミング

|    | パラメータ                                                                                 | テスト条件        | 最小値  | 標準値 | 最大値 | 単位 |

|----|---------------------------------------------------------------------------------------|--------------|------|-----|-----|----|

| T1 | VDDIO (デジタル電源) ランプ後の AVD (アナログ電源) ランプ遅延。電源ランプ開始前の AVD および VDDIO の電位は 0.3V を超えてはなりません。 | 電源ランプ開始からの時間 | -100 | 100 | 100 | ms |

|    | VDDIO ランプ時間                                                                           |              |      |     | 100 | ms |

|    | AVD ランプ時間                                                                             |              |      |     | 100 | ms |

**表 2-2. タイミング要件: パワーアップのタイミング (続き)**

| パラメータ | テスト条件                                                                    | 最小値 | 標準値 | 最大値 | 単位 |

|-------|--------------------------------------------------------------------------|-----|-----|-----|----|

| T2    | レジスタアクセスに対する MDC プレアンプ前のパワーアップ後安定化時間。<br>この最大待機時間後に入力された MDC プリアンプは有効です。 |     |     | 200 | ms |

| T3    | パワーアップ時のハードウェア構成ラッチイン時間                                                  |     |     | 200 | ms |

| T4    | ハードウェア構成のピンの遷移から出力ドライバまで                                                 |     |     | 64  | ns |

| T5    | パワーアップ後の高速リンクパルス転送遅延                                                     |     |     | 1.5 | s  |

**図 2-1. パワーアップのタイミング**

## 注

DP83822 でリンクアップの問題が発生し、AVD が 3.3V で動作している場合は、レジスタ 0x0421 をチェックして、AVD レベルと VDDIO レベルが目的の出力と一致していることを確認してください。レジスタ 0x0421 のビット [2] = 1 の場合、AVD は 3.3V です。レジスタ 0x0421 のビット [1:0] = 11 (3.3V VDDIO の場合) で、レジスタ 0x0421 が目的の結果と一致しない場合は、レジスタ 0x041F に目的の電圧レベルを書き込みます。3.3V AVD の場合はレジスタ 0x041F のビット [12] = 1、3.3V VDDIO の場合はビット [11:10] = 11 を書き込みます。レジスタ 0x0421 および 0x041F は拡張レジスタであり、[拡張レジスタアクセス](#)の手順に従ってください。

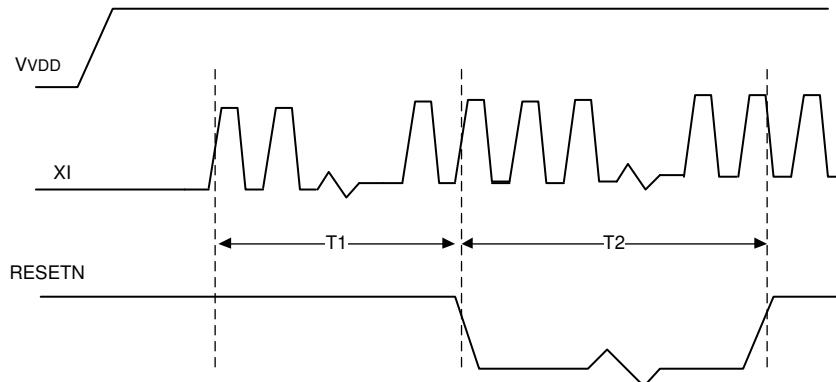

### 2.2.1.1 XI クロックが不安定な場合の電源ランプ

PHY のパワーアップ時に安定した XI クロックが利用できることを確認してください。安定した XI クロックが利用できない場合、PHY は正常に初期化されません。これが不可能な場合は、PHY のパワーアップ後、XI が安定するまで PHY をリセット状態に保持してください。DP83822 のパワーアップ時に XI クロックが不安定であることがプローブで確認された場合、詳細なタイミング要件とタイミング図については、[表 2-3](#) および [図 2-2](#) を参照してください。

**表 2-3. タイミング要件: XI クロックが不安定な状態でのパワーアップ**

| パラメータ                       | 最小値 | 公称値 | 最大値 | 単位 |

|-----------------------------|-----|-----|-----|----|

| T1 XI 安定後にアプリケーションをリセットします。 | 1   |     |     | us |

| T2 パルス幅のリセット                | 10  |     |     | us |

**図 2-2. 不安定な XI 入力でのパワーアップ**

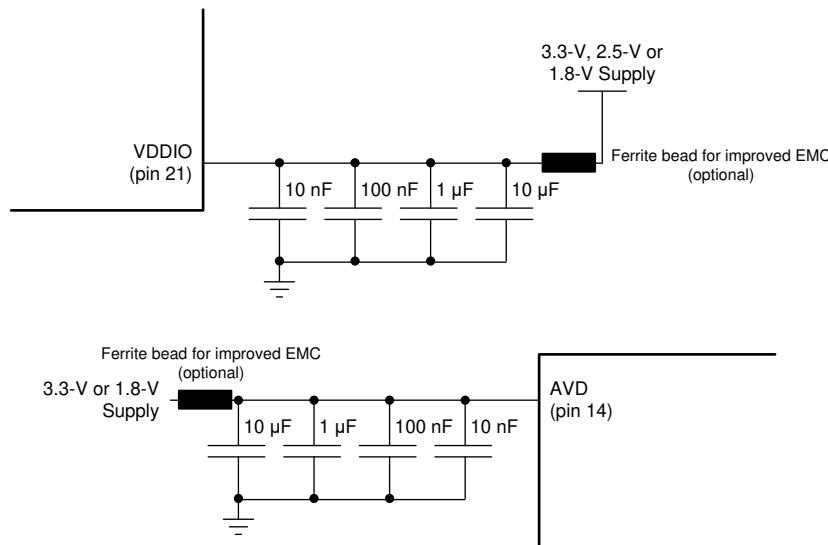

### 2.2.2 電圧チェック

DP83822 には、十分な電力と、デバイスの特性評価が行われた以下のデカップリング方式が必要です。

- レールあたり:

- 1x 10nF、1x 100nF、1x 1uF、1x 10uF

図 2-3. 電源デカップリングに関する推奨事項

### 2.2.3 RESET\_N 信号をプローブします

リセット入力はアクティブ Low です。コントローラーが **RESET\_N** 信号をローに駆動していないことを確認することが重要です。そうでない場合、デバイスはリセット状態のままになり、応答しなくなります。

### 2.2.4 RBIAS ピンのプローブ

**RBIAS** 抵抗は、**PHY** の内部バイアス電流と電圧を生成するために使用されます。**PHY** が最も厳しい IEEE 802.3 仕様を満たすように、1% の許容範囲が指定されています。許容範囲が大きくなる可能性があるため、複数の連続して 1 つの構成部品を使用することをお勧めします。

**RBIAS** 抵抗両端の電圧の DC 値を測定し、電圧が 1V であることを確認します。

基盤をパワーダウンし、RBIAS 抵抗値が  $4.87\text{k}\Omega \pm 1\%$  であることを確認します。

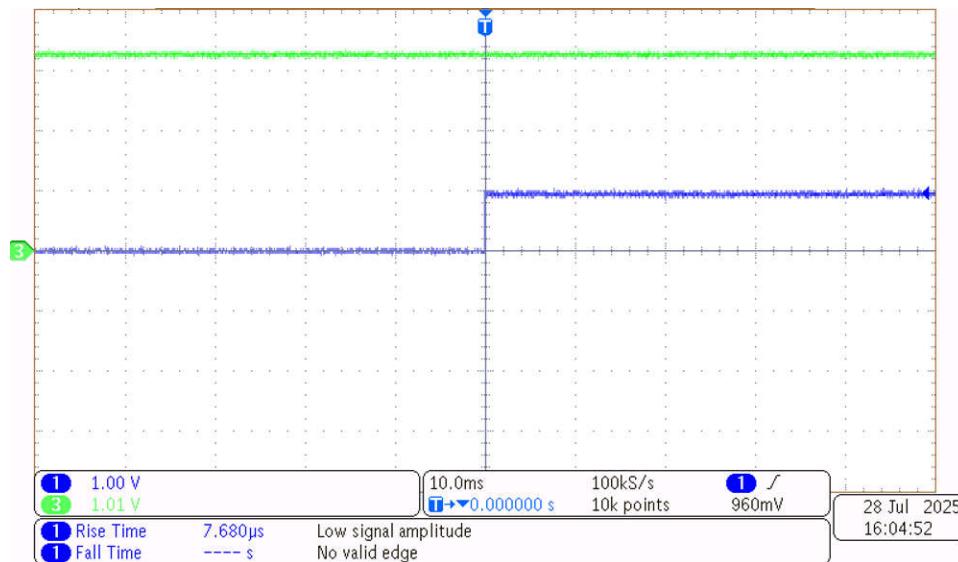

緑は AVD、青は RBIAS を示します。デバイスが適切にランプアップされると、RBIAS は High に遷移し、1V で High を維持することが期待されます。

図 2-4. AVD パワーアップ時の DP83822 RBIAS 信号

## 2.2.5 XI クロックをプロープします

以下のガイドラインは、適合する水晶振動子の参照用の主な仕様です。

表 2-4. 25MHz 水晶振動子の仕様

| パラメータ    | テスト条件             | 最小値  | 標準値 | 最大値 | 単位  |

|----------|-------------------|------|-----|-----|-----|

| 周波数      |                   |      | 25  |     | MHz |

| 周波数の許容誤差 | 動作温度、経年劣化、他の要因を含む | -100 |     | 100 | ppm |

| 負荷容量     |                   | 10   |     | 40  | pF  |

**表 2-5. 25MHz 発振器の仕様**

| パラメータ           | テスト条件             | 最小値  | 標準値 | 最大値 | 単位   |

|-----------------|-------------------|------|-----|-----|------|

| 周波数             |                   |      | 25  |     | MHz  |

| 周波数の許容誤差        | 動作温度、経年劣化、他の要因を含む | -100 |     | 100 | ppm  |

| 立ち上がり / 立ち下がり時間 | 10%~90%           |      |     | 8   | ns 秒 |

| ジッタ (短期)        | サイクル間             |      | 50  | 100 | ps 秒 |

| ジッタ (長期)        | 10 ms 以上の累積       |      |     | 1   | ns 秒 |

| 対称              | デューティ サイクル        | 40   |     | 60  | %    |

| 負荷容量            |                   |      | 15  | 30  | pF   |

**表 2-6. 50MHz 発振器の仕様**

| パラメータ           | テスト条件             | 最小値  | 標準値 | 最大値 | 単位   |

|-----------------|-------------------|------|-----|-----|------|

| 周波数             |                   |      | 50  |     | MHz  |

| 周波数の許容誤差        | 動作温度、経年劣化、他の要因を含む | -100 |     | 100 | ppm  |

| 立ち上がり / 立ち下がり時間 | 10%~90%           |      |     | 8   | ns 秒 |

| ジッタ (短期)        | サイクル間             |      | 50  |     | ps 秒 |

| ジッタ (長期)        | 10 ms 以上の累積       |      |     | 1   | ns 秒 |

| 対称              | デューティ サイクル        | 40   |     | 60  | %    |

| 負荷容量            |                   |      | 15  | 30  | pF   |

周波数とシグナル インテグリティを確認します。リンク整合性を確保するため、リファレンスクロックは以下のモードが推奨されます。

- MII / RGMII および RMII リーダーモード

- 25MHz ±100ppm

- RMII フォローワーモード

- 50MHz ±100ppm

### 2.2.6 初期化中にストラップピンをプロープします

ストラップ構成は、[セクション 2.1](#) で参照されているストラップツールで確認できます。

ストラップ構成は、パワーアップまたはハードウェアリセット時に、RESET ピンまたはレジスタ 0x001F のビット 15 を介してサンプリングされます。

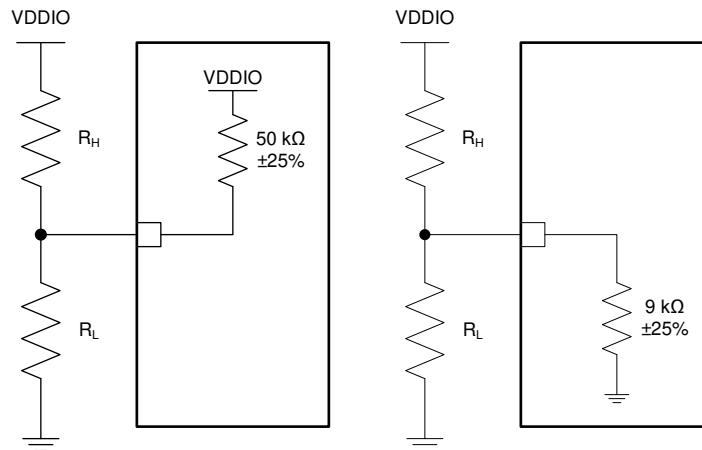

ライン上の他のコンポーネントが、このネットワークによって設定される DC バイアスに影響を与える必要がないことを確認してください。可能なモードの 1 つを選択するには、推奨値のプルアップ抵抗とプルダウン抵抗を使用して、ブートストラップピン入力と電源の電圧比を設定する必要があります。

ただし、場合によっては、ボード上の他のデバイス (MAC など) がこれらのピンを予期せずプルまたは駆動することがあります。ストラップ値はレジスタ 0x467 (SOR1) と 0x468 (SOR2) から読み取ることができます。これらのレジスタは拡張レジスタであり、[拡張レジスタアクセス](#)を使用してのみアクセスできます。

ストラップには次の抵抗を使用することを推奨します。レジスタ値が意図したストラップ構成と一致しない場合は、電源投入時および電源投入後に **RESET\_N** 信号がアサートされたときに測定を行うことができます。

図 2-5. ブートストラップ回路

表 2-7. 推奨される 4 レベルストラップ抵抗比

| モード (1)        | 理想的な $R_H$ (kΩ) | 理想的な $R_L$ (kΩ) |

|----------------|-----------------|-----------------|

| プルダウンピン (9kΩ)  |                 |                 |

| 1 (デフォルト)      | オープン            | オープン            |

| 2              | 10              | 2.49            |

| 3              | 5.76            | 2.49            |

| 4              | 2.49            | オープン            |

| プルアップピン (50kΩ) |                 |                 |

| 1              | オープン            | 1.96            |

| 2              | 13              | 1.96            |

| 3              | 6.2             | 1.96            |

| 4 (デフォルト)      | オープン            | オープン            |

(1) 許容誤差 1% のストラップ抵抗が推奨されます。

### 2.2.7 シリアル管理インターフェース信号のプローブ (MDC、MDIO)

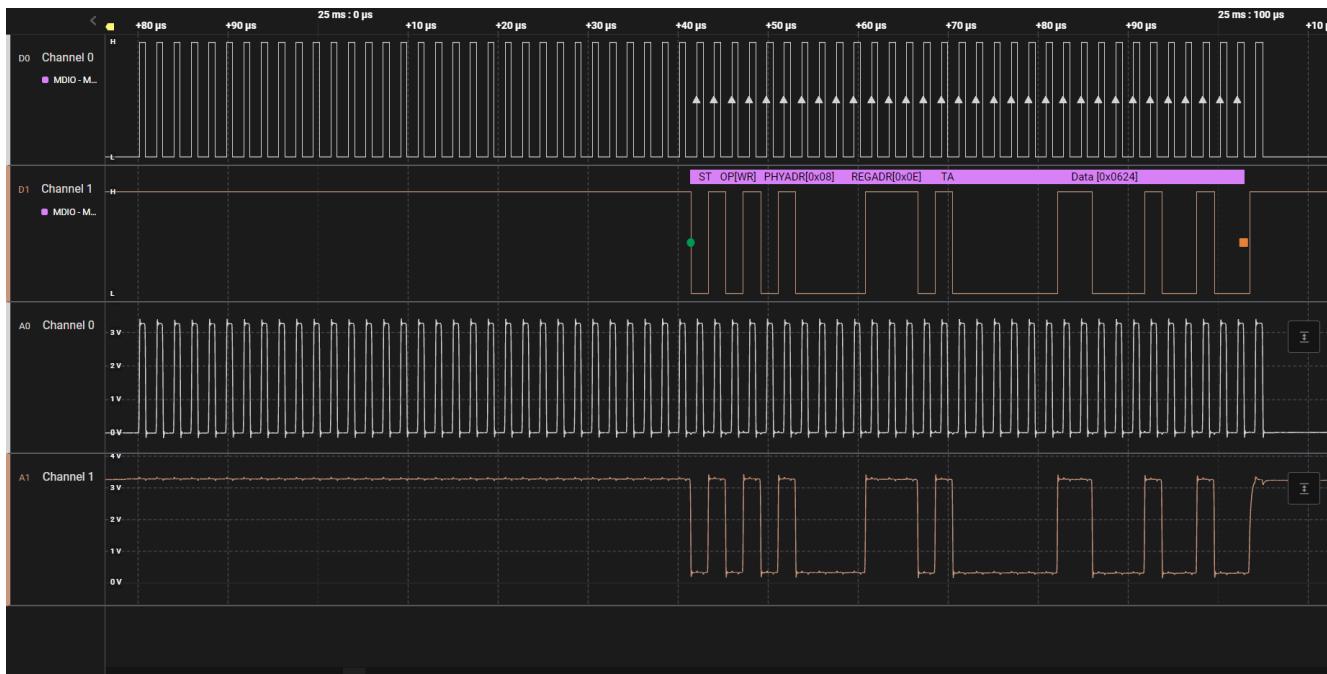

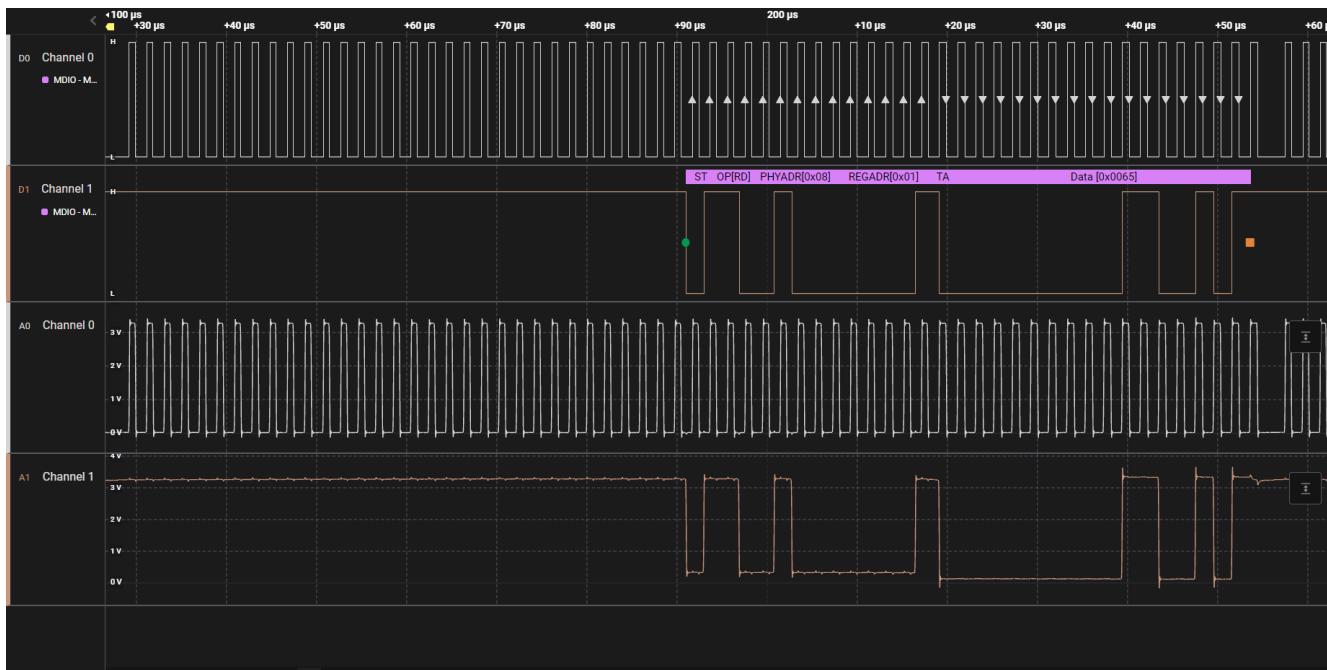

必要に応じて、シリアル管理インターフェースはデバッグ中に重要なステータスフィールドを提供するのに役立ちます。ただし、この通信が正確であることを確認して、複合的な問題を回避してください。MDIO は  $2.2\text{k}\Omega$  のプルアップ抵抗で VDDIO にプルアップする必要があります。MDIO をプローブして、デフォルトの電圧を確認します。

レジスタの書き込みと読み取りを試みます。データシートを参照して MDIO データシーケンスを確認し、MDIO の読み取りアクセスタイミングが正しいことを確認します。

表 2-8. SMI プロトコルの構成

|           |                                                                       |

|-----------|-----------------------------------------------------------------------|

| SMI プロトコル | <idle><start><op code><device addr><reg addr><turnaround><data><idle> |

| 読み取りレジスタ  | <アイドル><01><10><AAAAAA><RRRRRR><Z0><XXXX XXXX XXXX XXXX><アイドル>         |

| 書き込みレジスタ  | <アイドル><01><01><AAAAAA><RRRRRR><10><XXXX XXXX XXXX XXXX><アイドル>         |

図 2-6. MDC / MDIO 書き込みの例

図 2-7. MDC / MDIO 読み取りの例

### 2.2.7.1 レジスタ値の読み出しと確認

SMI バスが正常に動作している場合は、レジスタを読み取り、デバイス固有のデータシートに記載されているデフォルト値を確認してください。

| レジスタ・アドレス | オートネゴシエーションのレジスタ値 |         |

|-----------|-------------------|---------|

|           | 10Mbps            | 100Mbps |

| 0x0000    | 3100              | 3100    |

| 0x0001    | 786D              | 786D    |

| 0x0002    | 2000              | 2000    |

| 0x0003    | A240              | A240    |

| 0x0004    | 0061              | C1E1    |

| 0x0005    | C1E1              | C1E1    |

| 0x0010    | 4117              | 4715    |

| 0x0014    | 0000              | 0000    |

| 0x0015    | 0000              | 0000    |

| 0x0017    | 0041              | 0041    |

| 0x0019    | 8021              | 8C21    |

PHY が所定の速度でリンクされている場合は、これらの値を参考にして、予想される動作との差異を特定します。すべてのレジスタが同じである必要はないことに注意してください。例えば、

- レジスタ 0x0005 の値は、リンクパートナーの機能によって異なります。

- レジスタ 0x0010 の MSB の「4」または「0」の違いは、ビット 14 MDI/MDIX モードによるもので、何も影響しません。重要な違いは LSB の「7」または「5」で、これは速度ステータスを示します。

例: 10 Mbps で PHY に電源を投入してリンクすると、レジスタ 0x0010 は値 0x0017 で読み取られ、ビット 4、2、1、0 がハイであることを意味します。これらのビットは、オートネゴシエーションが完了し、全二重、10Mbps モード、有効なリンクが確立されていることを確認します。

表に示されている予想値とは異なる値に対してこのプロセスを繰り返すと、発生した問題に対する PHY の正確な状態を診断するのに役立ちます。

### 2.2.7.1.1 拡張レジスタアクセス

拡張レジスタ空間でレジスタを読み書きするには、以下の手順を参照してください。

MMD「1F」レジスタの書き込み手順:

`reg<000D> = 0x001F` を書き込みます

`reg<000E> = <address>` を書き込みます

`reg<000D> = 0x401F` を書き込みます

`reg<000E> = <value>` を書き込みます

MMD「1F」レジスタの読み取り手順:

`reg<000D> = 0x001F` を書き込みます

`reg<000E> = <address>` を書き込みます

`reg<000D> = 0x401F` を書き込みます

`reg<000E>` を読み込みます

拡張レジスタ セットのレジスタを書き込み、書き込み動作後にアドレス レジスタをすぐ上の値に自動的にインクリメントするには、次の手順に従います。

MMD「1F」レジスタへの書き込み (ポストインクリメント) 手順:

`reg<000D> = 0x001F` を書き込みます

`reg<000E> = <address>` を書き込みます

`reg<000D> = 0x401F` を書き込みます

`reg<000E> = 0x0C50` を書き込みます

`reg<000E> = <value>` を書き込みます

拡張レジスタ セットのレジスタを読み出し、読み取り動作後にアドレス レジスタをすぐ上の値に自動的にインクリメントするには、次の手順に従います。

MMD「1F」レジスタへの読み取り (ポストインクリメント) 手順:

`reg<000D> = 0x001F` を書き込みます

`reg<000E> = <address>` を書き込みます

`reg<000D> = 0x801F` を書き込みます

`reg<000E>` を読み込みます

`reg<000E>` を読み込みます

#### 注

上記の書き込みおよび読み取り手順は通常、アドレスが `0x001F` より大きいレジスタに使用されますが、一般に任意のアドレスにこの手順を使用することもできます。

## 2.3 MDI ヘルス チェック

このセクションでは、デバイスの MDI セクションが正常に動作していることを確認するデバイス ヘルスチェックについて詳しく説明します。DP83822 が次の場合、このセクションはスキップできます。

- デバイス経由でトラフィックを送信する際に、リンクアップし、Reg `0x15` を通じてパケットエラーを報告していないことを確認してください。

### 2.3.1 磁気

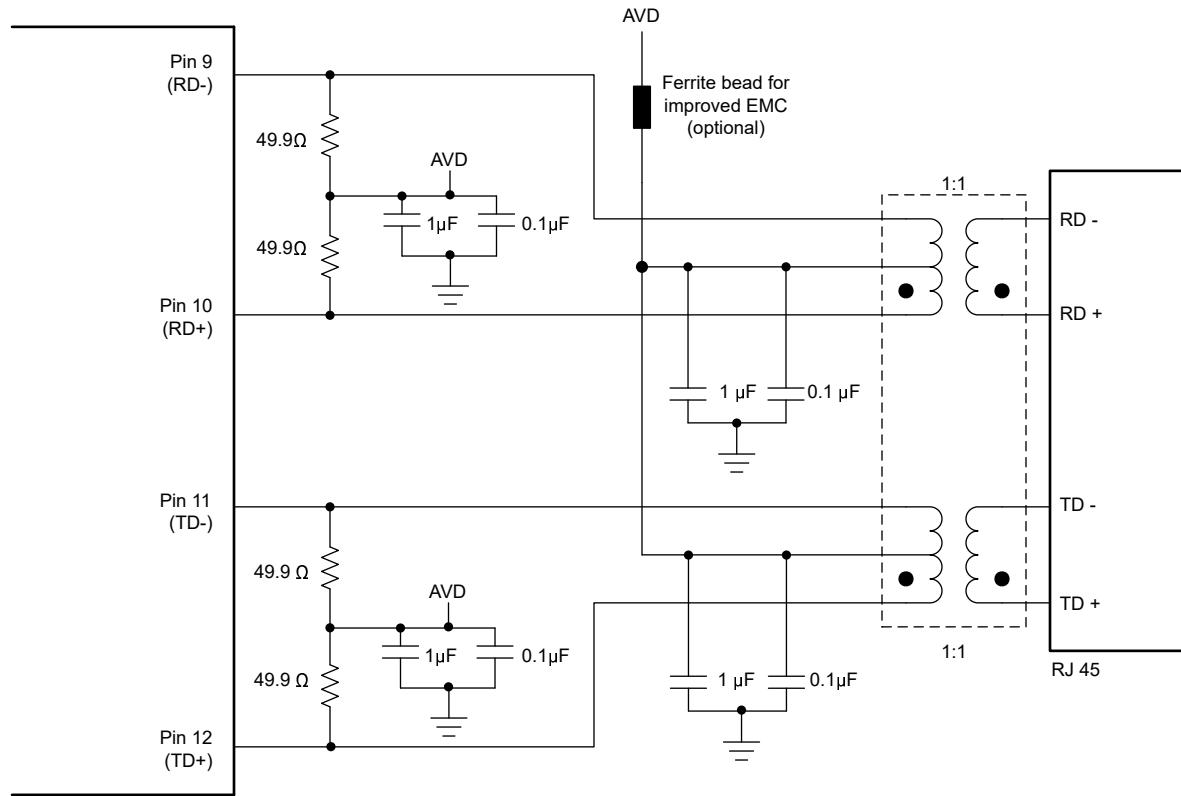

DP83822 は電流モードドライバなので、MDI ラインが  $49.9\Omega$  の抵抗で AVD に接続されていることを確認してください。

図 2-8 を参照

図 2-8. DP83822 TPI ネットワーク回路

以下のガイドラインは、互換性のある磁気素子を参照するための主な仕様を示しています。

表 2-9. 磁気絶縁の要件

| パラメータ        | テスト条件        | 標準値  | 単位   |

|--------------|--------------|------|------|

| 巻数比          | 公差 $\pm 2\%$ | 1:1  | -    |

| 挿入損失         | 1 ~ 100MHz   | -1   | dB   |

| リターン ロス      | 1 ~ 30MHz    | -16  | dB   |

|              | 30 ~ 60MHz   | -12  | dB   |

|              | 60 ~ 80MHz   | -10  | dB   |

| 差動と同相モードの除去比 | 1 ~ 50MHz    | -30  | dB   |

|              | 50Hz~150MHz  | -20  | dB   |

| クロストーク       | 30MHz        | -35  | dB   |

|              | 60MHz        | -30  | dB   |

| 絶縁           | HPOT         | 1500 | Vrms |

これらの正確な要件を満たすことができない場合は、次のような手当を行うことができます。

- 卷数比

- 理想的には 2% ですが、3% は許容できます。

- インダクタンス

- 大きいインダクタンスを推奨します。通常の数は  $350\mu\text{H}$  の周りにあります。

- 挿入損失

- データシートに記載されている各範囲で、指定された値に比べて、可能な限り 0dB に近い値です。仕様が標準値として -1dB である場合は、-1dB、-0.9dB などを持つコンポーネントを見つけることをお勧めします。

- リターンロス

- または、データシートに規定されている振幅より低い値です。標準仕様で -16dB が指定されている場合は、-16dB、-17dB などのコンポーネントを見つけることをお勧めします。

### 2.3.2 MDI 信号をプロープします

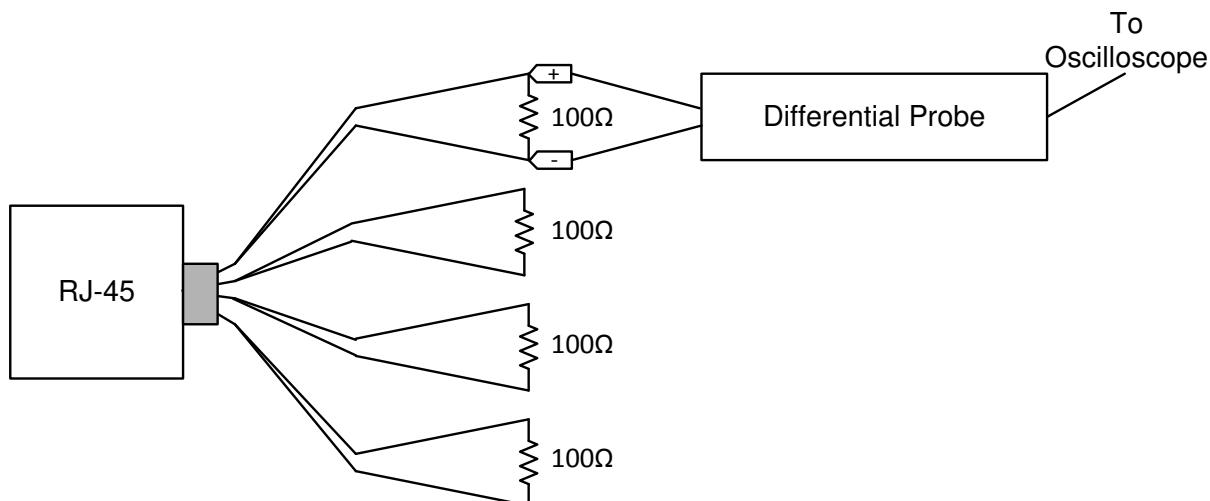

デフォルト設定では、オートネゴシエーションと Auto-MDIX を有効にできます。リンクパルスはチャネル送信 (TD\_P、TD\_M) で確認できる必要があり、受信ペア (RD\_P、RD\_M) に切り替えることもあります。MDI に設定されている場合、このパルスは送信ペアでのみ使用可能ですが、MDI-X に設定されている場合、これは受信ペアでのみ使用可能です。

MDI 信号の測定には、 $100\Omega$  終端を備えた短いイーサネットケーブルを使用できます。図 2-9 に、終端ケーブルを示します。図 2-10 に、終端ケーブルを使用して測定を行うための接続図を示します。

図 2-9. MDI 信号測定用の  $100\Omega$  終端ケーブル

図 2-10. 100M 終端ケーブルの接続図

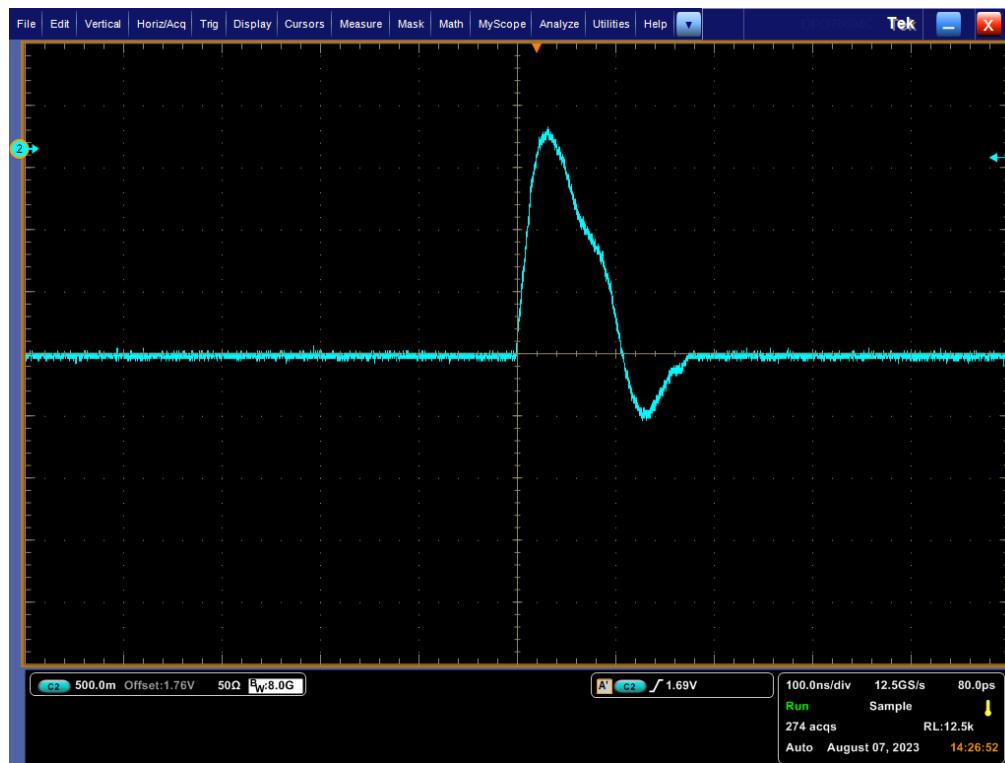

リンクパルスは通常  $100\text{ns}$  幅で、 $16\text{ms}$ ごとに発生します。図 2-11 に、正しいリンクパルスを示します。

図 2-11. DP83822 リンク パルス

### 2.3.3 リンク品質チェック

有効なリンクを確立し、主要なステータス レジスタの値を確認し、リンク LED が点灯していることを目視で確認した後でも、リンクでパケット エラーがまだ発生している可能性があります。

リンクの問題の原因として考えられるものがいくつかあります。

- リンク パートナーの送信に問題があります

- ケーブルの長さと品質

- 25MHz リファレンス クロックのクロック品質

- MDI 信号品質

PHY に電力が供給され、リンク パートナーに接続されている状態では、以下のレジスタを読み取り、リンクの状態を判定できます。

表 2-10. リンク品質 MSE レジスタ

| チャネル | レジスタ・アドレス |

|------|-----------|

| A    | 0x218     |

特定のチャネルについて、レジスタ値を読み取って MSE (平均二乗誤差) を決定し、表 2-11 を参照してリンク品質を判定確認します。

表 2-11. MSE リンク品質範囲

| リンクの品質 | コンテンツの登録    |

|--------|-------------|

| 非常に良好  | < 0x20A     |

| 良好     | 0x20A～0x33B |

| 不良     | > 0x33B     |

PHY 上で時間ドメイン反射率測定 (TDR) テストを実行することで、配線接続の問題や障害発生箇所を検出することができます。さまざまな TDR 構成とテストモード、および PHY 上で TDR テストを実行する方法の詳細については、[DP83822 の TDR 機能の使用方法](#)を参照ください。

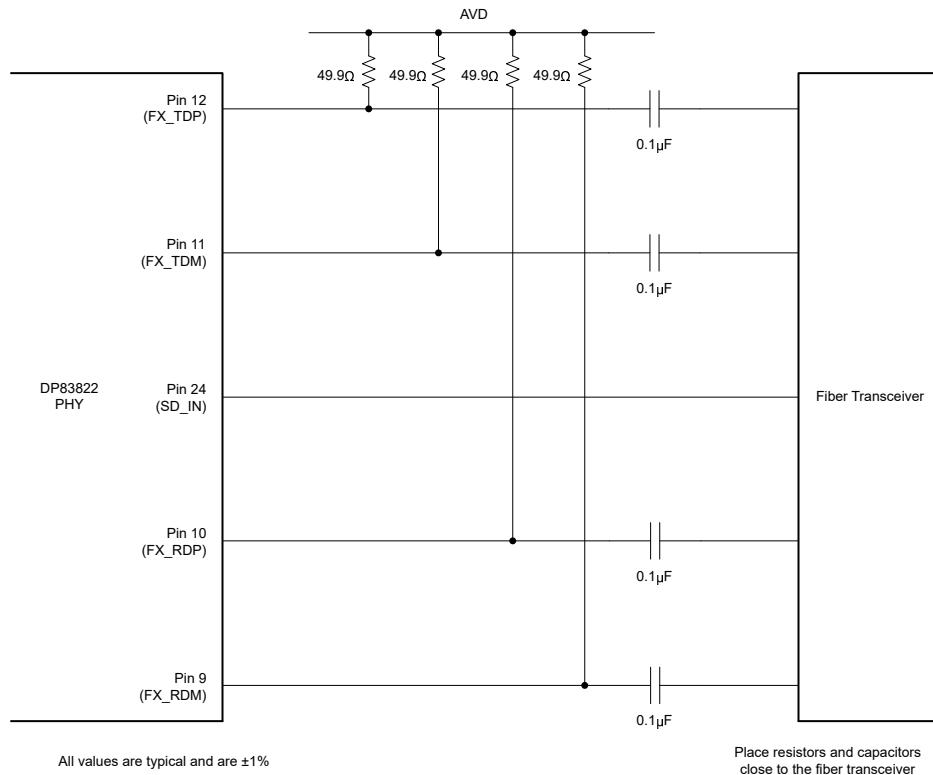

#### 2.3.4 ファイバ接続のデバッグ

ファイバ ネットワーク回路図は、100Mbps ファイバ ネットワークに推奨される回路を示しています。回路が対象アプリケーションの要件を満たしていることを確認してください。

すべての抵抗とコンデンサは、ファイバトランシーバのできるだけ近くに配置してください。

図 2-12. ファイバ ネットワーク回路

#### 注

PECL および LVPECL アプリケーション、および推奨される追加コンデンサと抵抗については、[DP83822 EVM ユーザーズガイド](#)を参照してください。

#### 注

SFP ファイバトランシーバには通常、AC 結合コンデンサが内蔵されています。外付けコンデンサの追加は不要な場合があります。

DP83822 は、IEEE 802.3 準拠の 100BASE-FX 動作を提供します。ハードウェア ブートストラップまたはレジスタ設定を使用して、100BASE-FX 動作を有効にすることができます。

DP83822IF および DP83822HF は、DP83822 の光ファイバー対応モデルです。レジスタ 0x0001[2] は、銅線モードと光ファイバモードの両方の動作におけるリンクステータスを示します。光ファイバモードでは、リンクステータスが変化してもこのビットは切り替わりません。リンクステータスの変化を正しく更新するには、レジスタ 0x0001 を読み取る前にソフトリセット (レジスタ 0x001F を 0x4000 に設定) を実行する必要があります。

DP83822 には信号検出ピンがあります。このピンは業界標準の光ファイバトランシーバーに接続します。FX\_EN ブートストラップを使用して 100BASE-FX 動作を有効にすると、AMDX\_EN ブートストラップは SD\_EN ブートストラップに変わります。光ファイバ ブートストラップの設定については、[表 2-12](#) を参照してください。

## 注

100BASE-FX 信号検出ピン (LED\_1) の極性は、ファイバ一般設定レジスタ (FIBER GENCFG、レジスタ 0x0465) のビット [0] によって制御されます。表 2-13 を参照ください。デフォルトでは、信号検出はアクティブ HIGH 極性です。

## 注

光学素子トランシーバの信号検出ピンを LED\_1 ピンに接続し、100BASE-FX モードでは SD\_EN ブートストラップピンを使用して有効にすることを推奨します。LED\_1 ピンは設計では使用されません。ファイバモジュールと DP83822 間の電気リンクが切断、断線、またはその他の方法で中断された場合、リンクは MDIO / MDC インターフェイスを介してソフトリセットを開始することによってのみ回復します。

**表 2-12. ファイバブートストラップ構成**

| ピン名   | ピン番号 | PU/PD | モード     | 概要                                                                                                                                |

|-------|------|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------|

| COL   | 29   | PU    | 2 または 3 | FX_EN:100BASE-FX を有効にする                                                                                                           |

| RX_ER | 28   | PU    | 3 または 4 | SD_EN:FX_EN が有効な場合、LED_1 を「1」に設定すると、アクティブ HIGH の 100BASE-FX 信号検出が有効になります。極性は、ファイバ一般設定レジスタ (FIBER GENCFG、レジスタ 0x0465) を使用して変更できます。 |

**表 2-13. 0x0465 ファイバ一般設定レジスタ (FIBER GENCFG)**

| ビット | 名称                 | タイプ | デフォルト | 機能                                                                                                                                                                                                                                                               |

|-----|--------------------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 100Base-FX 信号検出の極性 | R/W | 0     | 100Base-FX 信号検出の極性:1 = 信号検出はアクティブ LOW 0 = 信号検出はアクティブ HIGH であり、アクティブ HIGH に設定されていると SD ピンが LOW 状態 (SD =「0」) を検出することにより、リンクドロップが発生します。アクティブ LOW に設定すると、SD ピンが HIGH 状態 (SD =「1」) を検出しリンクドロップが発生します。<br>注:LED_1 (ピン番号 24) で 100BaseFX 信号検出を有効にするには、SD_EN =「1」に設定します。 |

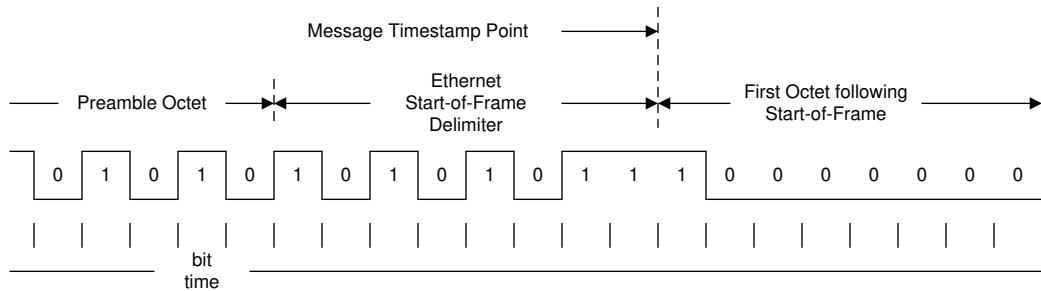

### 2.3.5 フレーム開始検出 (SFD) のデバッグ

SFD における IEEE 1588 表示パルスは、以下のいずれかのピンに出力できます。LED\_0、LED\_1 (GPIO1)、COL (GPIO2)、RX\_D3 (GPIO3)、INT/PWDN\_N、CRS。パルスの正確なタイミングは、レジスタ 0x003F で調整できます。

図 2-13. IEEE 1588 メッセージ タイムスタンプ ポイント

IEEE 1588 送信および受信表示のルーティングを制御する 3 つのレジスタを以下に示します。

1. 0x003E: 送信および受信表示の両方を LED\_0 (GPIO1)、COL (GPIO2)、CRS、および INT/PWDN\_N にルーティングします。

2. 0x0462/0x0463: IO MUX GPIO 制御レジスタ 1/2 により、追加のピン選択と GPIO 制御の集中管理が可能になります。

IOCTRLx レジスタで RX\_SFD ピンと TX\_SFD ピンを有効化 / 設定した後、以下の 2 つのレジスタに書き込みます。

- プログラム (レジスタ 0x0456 = 値 0x000A)

- プログラム (レジスタ 0x04A0 = 値 0x1080)

- レジスタ 0x04A0 は「ビット 7:WOL」を有効化することに注意してください。これは SFD 検出の精度向上に役立ちますが、必須の変更ではありません。Wol 機能には追加のレジスタ設定が必要であるため、この変更によって PHY が WoL パケットを検出することはありません。

---

注

これらのレジスタ値をロードするには、ソフトウェアリセットを実行する必要があります (レジスタ 0x001F = 値 0x4000)。

---

### 2.3.6 コンプライアンス

IEEE 準拠測定は、信号特性を検証するために行うことができます。これらの測定の詳細と適切な設定方法については、アプリケーションノートの [イーサネットコンプライアンステスト用に DP8382x を設定する方法](#) を参照してください。

## 2.4 MII ヘルス チェック

このセクションでは、デバイスの MII セクションが正常に動作していることを確認するデバイスヘルスチェックについて詳しく説明します。

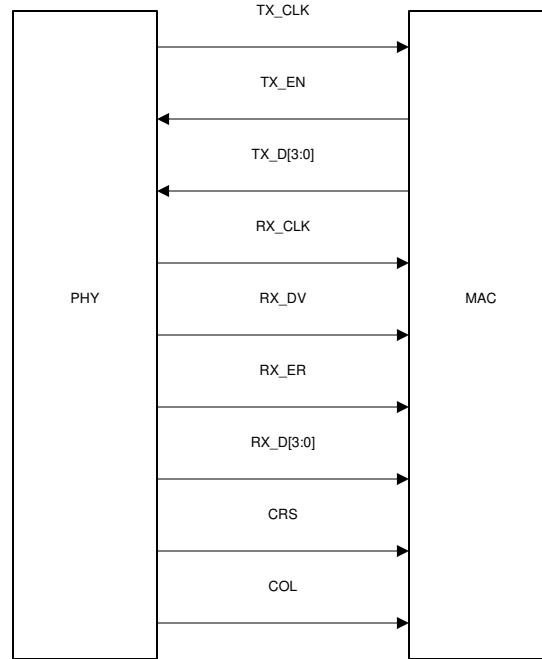

### 2.4.1 MII チェック

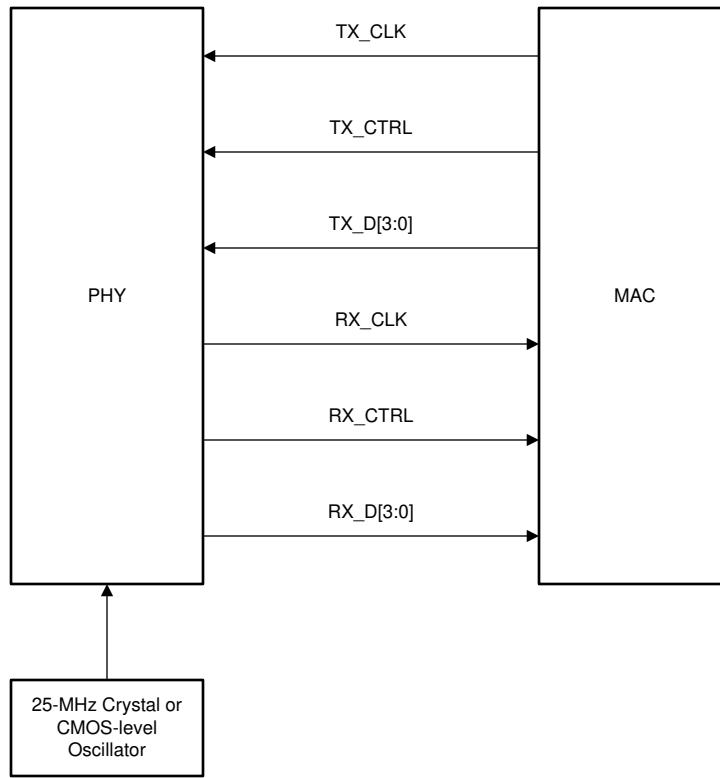

メディア独立インターフェイス (MII) は、PHY を MAC に接続する同期 4 ビット幅のニブル データインターフェイスです。MII は IEEE 802.3-2002 条項 22 に完全準拠しています。

表 2-14 に、MII 信号のまとめを示します。

表 2-14. MII 信号

| 機能     | ピン        |

|--------|-----------|

| データ信号  | TX_D[3:0] |

|        | RX_D[3:0] |

| 信号の送受信 | TX_EN     |

|        | RX_DV     |

表 2-14. MII 信号 (続き)

| 機能          | ピン     |

|-------------|--------|

| ライン ステータス信号 | CRS    |

|             | COL    |

| クロック        | TX_CLK |

|             | RX_CLK |

図 2-14. MII シグナリング

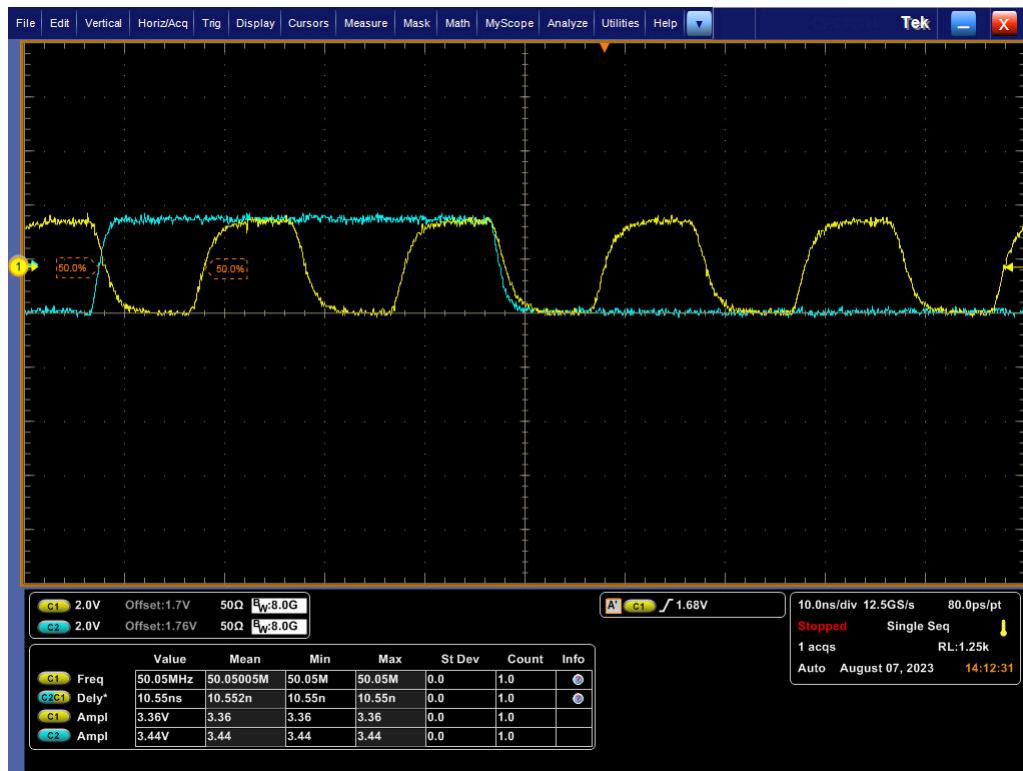

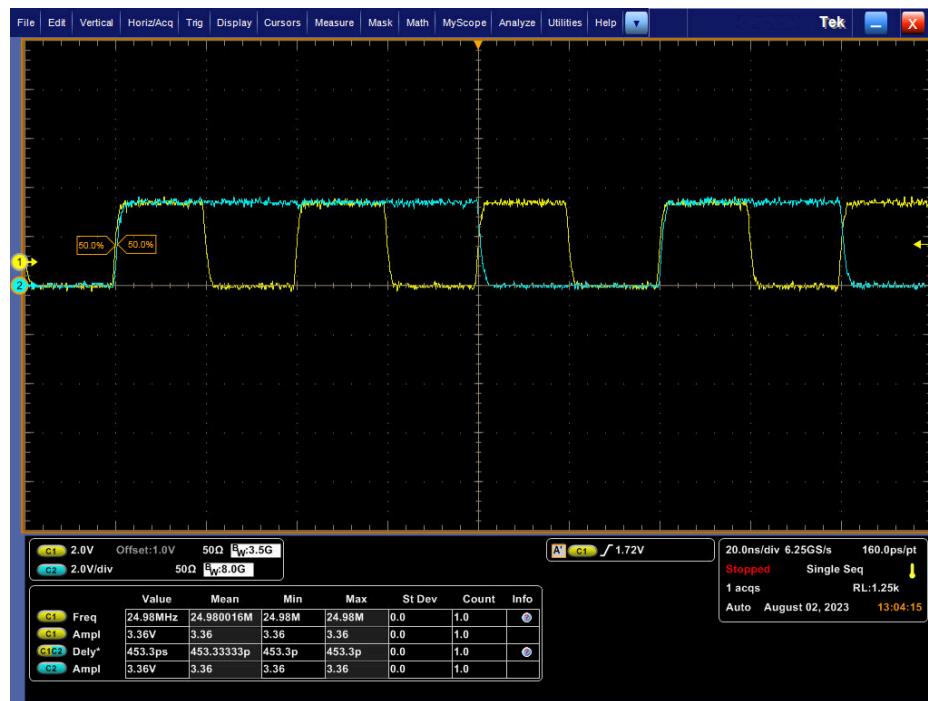

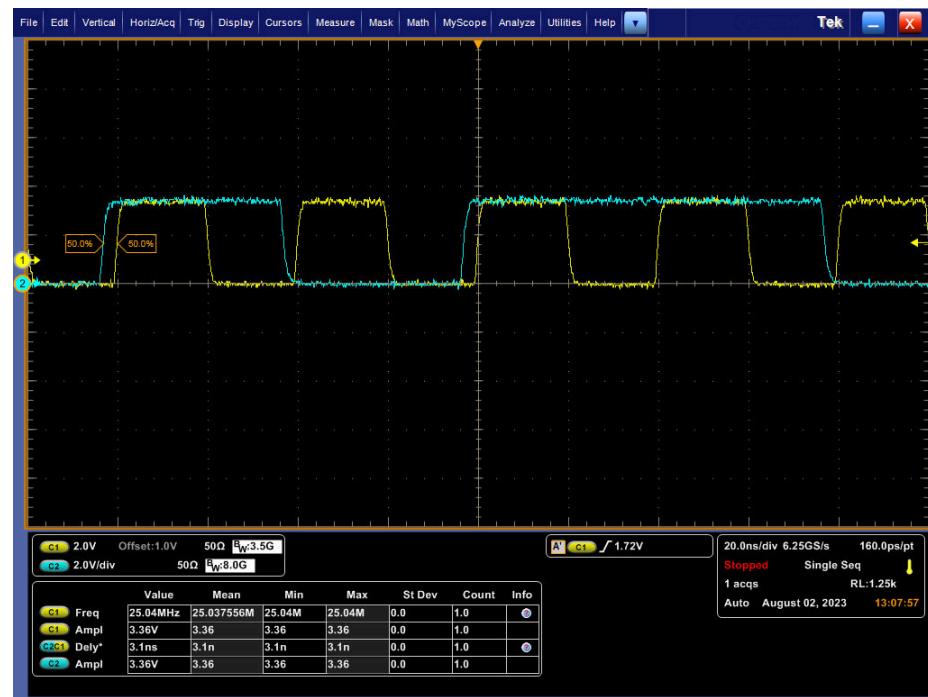

以下の波形を参照して、100BASE-Tx MII モードで予想される MAC データとクロック信号を確認してください。表 2-15 に、波形に示されているデータシートから取得された仕様を示します。PHY が 10Mbps でリンクされていない場合、またはリンクされていない場合は MII 信号を 2.5MHz である必要がありますが、100Mbps でリンクされている場合は 25MHz である必要があります。TX\_CLK と RX\_CLK はどちらも PHY の出力であることに注意してください。

MAC バス (TX または RX) に問題があると思われる場合は、トレースのレシーバ側のラインを調べ、レシーバのセットアップ時間とホールド時間が VIH/VIL と一致することを確認します。これらの仕様に違反する典型的な症状は、PHY がクリントラフィックを示している間に MAC でパケットエラーが発生することです (Reg 0x15)。

表 2-15. 100m MII 受信タイミング

| テスト条件                                     | 最小値 | 標準値 | 最大値 | 単位 |

|-------------------------------------------|-----|-----|-----|----|

| RX_CLK High / Low 時間                      | 16  | 20  | 24  | ns |

| RX_CLK 立ち上がりからの RX_D[3:0]、RX_ER、RX_DV の遅延 | 10  |     | 30  | ns |

表 2-16. 100m MII 送信タイミング

| テスト条件                                    | 最小値 | 標準値 | 最大値 | 単位 |

|------------------------------------------|-----|-----|-----|----|

| TX_CLK High / Low 時間                     | 16  | 20  | 24  | ns |

| TX_CLK までの TX_D[3:0]、TX_ER、TX_EN のセットアップ | 10  |     |     | ns |

| TX_CLK からの TX_D[3:0]、TX_ER、TX_EN のホールド   | 0   |     |     | ns |

**表 2-17. 10m MII 受信タイミング**

| テスト条件                                     | 最小値 | 標準値 | 最大値 | 単位 |

|-------------------------------------------|-----|-----|-----|----|

| RX_CLK High / Low 時間                      | 160 | 200 | 240 | ns |

| RX_CLK 立ち上がりからの RX_D[3:0]、RX_ER、RX_DV の遅延 | 100 |     | 300 | ns |

**表 2-18. 10M MII 送信タイミング**

| テスト条件                                    | 最小値 | 標準値 | 最大値 | 単位 |

|------------------------------------------|-----|-----|-----|----|

| TX_CLK High / Low 時間                     | 190 | 200 | 240 | ns |

| TX_CLK までの TX_D[3:0]、TX_ER、TX_EN のセットアップ | 25  |     |     | ns |

| TX_CLK からの TX_D[3:0]、TX_ER、TX_EN のホールド   | 0   |     |     | ns |

**図 2-15. MII の RX\_CLK と RX\_D0 のタイミング (青波 (チャネル 2) = RX\_CLK、紫波 (チャネル 3) = RX\_D0)**

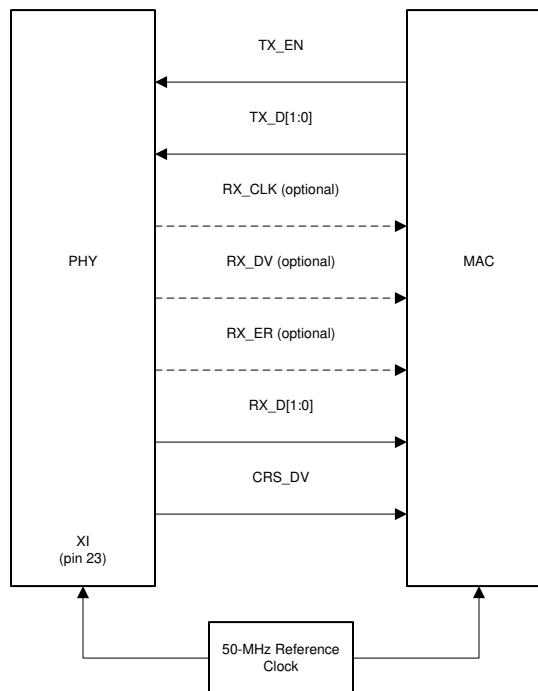

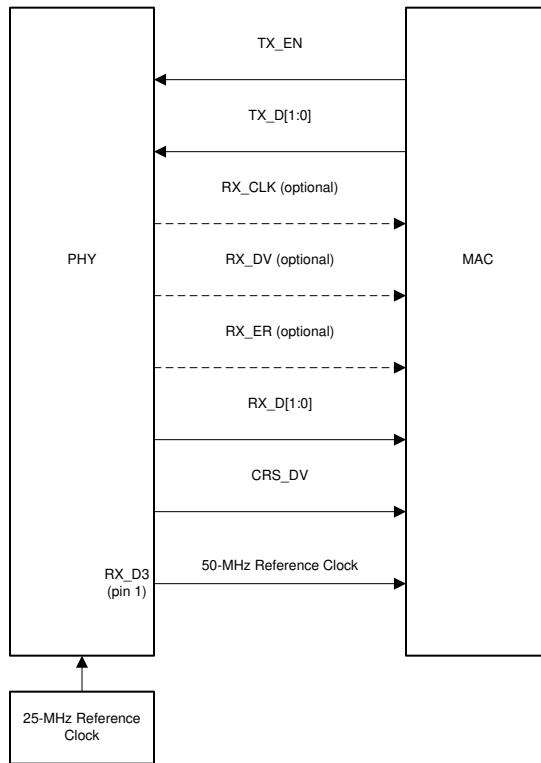

#### 2.4.2 RMII チェック

DP83822 には、RMII コンソーシアムの RMII 仕様で指定されている簡易メディア独立インターフェイス (Reduced Media Independent Interface 以下 RMII) が組み込まれています。アキテクチャとしては、RMII 仕様は MII の両側に追加の整合レイヤを提供しますが、MII がない場合に実装できます。DP83822 には、次の 2 種類の RMII 動作があります: RMII リーダーおよび RMII フォロワー。

RMII リーダー動作では、DP83822 は XI ピンに接続された 25MHz CMOS レベル発振器、または XI ピンと XO ピン間に接続された 25MHz 水晶振動子のいずれかで動作します。

RMII フォロワーアクションでは、DP83822 は XI ピンに接続された 50MHz CMOS レベル発振器で動作し、MAC と同じクロックを共有します。

3つのGPIOのいずれかを基準とする50MHz出力クロックがMACに接続されます。

**注**

RMIIリーダーモードがブートストラップによって設定されている場合、RX\_D3(GPIO3)で50MHz出力クロックが自動的に有効になります。

RMII仕様には、次の特性があります。

- 100BASE-FX、100BASE-TX、10BASE-Teをサポートします。

- MACからPHY(または外部ソース)に供給される単一のクロックリファレンス

- 独立した2ビット幅の送受信データパスを提供

- MIIインターフェイスと同じレベルのCMOS信号レベルを使用

このモードでは、送信バスと受信バスの両方に内部50MHzリファレンスクロックを使用して、クロックサイクルごとに2ビットのデータ転送が行われます。

表2-19に、RMII信号のまとめを示します。

**表 2-19. RMII 信号**

| 機能     | ピン        |

|--------|-----------|

| データ信号  | TX_D[1:0] |

|        | RX_D[1:0] |

| 信号の送受信 | TX_EN     |

|        | CRS_DV    |

**図 2-16. RMII フォロワ信号**

図 2-17. RMII リーダー信号

## 注

DP83822 を RMII リピーター モードで使用する場合は、[DP83822 RMII リピーター モード](#)を参照してください。

表 2-20. RMII 送信タイミング

| テスト条件                                               | 最小値 | 標準値 | 最大値 | 単位 |

|-----------------------------------------------------|-----|-----|-----|----|

| XI クロック周期                                           |     | 20  |     | ns |

| TX_D[1:0] および TX_EN データの XI 立ち上がりまでのセットアップ          | 1.4 |     |     | ns |

| XI 立ち上がりからの TX_D[1:0] と TX_EN データのホールド              | 2   |     |     | ns |

| RMII マスタークロック (RX_D3 クロック) 周期                       |     | 20  |     |    |

| デューティサイクル                                           | 35  |     | 65  | %  |

| TX_D[1:0] および TX_EN データセットアップから RMII リーダークロックの立ち上がり | 4   |     |     | ns |

| TX_D[1:0] および TX_EN データのホールド (RMII リーダークロックの立ち上がり時) | 2   |     |     | ns |

表 2-21. RMII 受信タイミング

| テスト条件                                      | 最小値 | 標準値 | 最大値 | 単位 |

|--------------------------------------------|-----|-----|-----|----|

| XI クロック周期                                  |     | 20  |     | ns |

| TX_D[1:0] および TX_EN データの XI 立ち上がりまでのセットアップ | 1.4 |     |     | ns |

| XI 立ち上がりからの TX_D[1:0] と TX_EN データのホールド     | 2   |     |     | ns |

| RMII マスタークロック (RX_D3 クロック) 周期              |     | 20  |     |    |

| デューティサイクル                                  | 35  |     | 65  | %  |

表 2-21. RMII 受信タイミング (続き)

| テスト条件                                               | 最小値 | 標準値 | 最大値 | 単位 |

|-----------------------------------------------------|-----|-----|-----|----|

| TX_D[1:0] および TX_EN データセットアップから RMII リーダークロックの立ち上がり | 4   |     |     | ns |

| TX_D[1:0] および TX_EN データのホールド (RMII リーダークロックの立ち上がり時) | 2   |     |     | ns |

TX\_D[1:0] のデータは、RMII リーダー モードとフォロワ モードでは、50MHz クロックを基準にして PHY でラッチされます。RX\_D[1:0] のデータは、50MHz クロックを基準として提供されます。さらに、CRS\_DV を RX\_DV 信号として構成することもできます。これにより、受信データを簡単に回復でき、RX\_DV を CRS\_DV 表示から分離する必要もありません。

図 2-18. RMII の RX\_CLK と RX\_D0 のタイミング (黄色の波形 (チャネル 1) = RX\_CLK、青色の波形 (チャネル 2) = RX\_D0)

簡易メディア独立インターフェースの詳細については、[DP83822 堅牢、低消費電力 10/100Mbps イーサネット物理層トランシーバ データシート](#)の簡易メディア独立インターフェース (RMII) セクションを参照してください。

#### 2.4.3 RGMII チェック

表 2-22 に、RGMII 信号のまとめを示します。

表 2-22. RGMII 信号

| 機能     | ピン        |

|--------|-----------|

| データ信号  | TX_D[3:0] |

|        | RX_D[3:0] |

| 信号の送受信 | TX_CTRL   |

|        | RX_CTRL   |

| クロック   | TX_CLK    |

|        | RX_CLK    |

**図 2-19. RGMII シグナリング**

MAC が PHY から正しいデータを送受信できるようにするには、PHY と MAC の両方が TX 側と RX 側で同時にアラインモードまたはシフトモードにならないように、正しい RGMII モードを選択する必要があります。表 2-23 に、正しい RGMII 遅延設定を示します。

RGMII モードで期待される MAC データとクロック信号を確認するには、以下の波形を参照してください。表 2-23 に、波形に示されているデバイス固有のデータシートから取得した仕様を示しています。

**表 2-23. RGMII シフト構成**

| MAC の構成          | 必要な PHY 構成       |

|------------------|------------------|

| RX での RGMII アライン | RX での RGMII シフト  |

| RX での RGMII シフト  | RX での RGMII アライン |

| TX での RGMII アライン | TX での RGMII シフト  |

| TX での RGMII シフト  | TX での RGMII アライン |

図 2-20. RGMII アラインモードにおける RX\_CLK と RX\_D0 のタイミング (黄色の波形 (チャネル 1) = RX\_CLK、青色の波形 (チャネル 2) = RX\_D0)

図 2-21. RGMII RX シフトモードにおける RX\_CLK と RX\_D0 のタイミング (黄色の波形 (チャネル 1) = RX\_CLK、青色の波形 (チャネル 2) = RX\_D0)

RGMII RX シフトモードの場合、RX\_CLK が 3.5 ns シフトされていること、RGMII TX クロックシフトモードの場合、TX\_CLK が 3.5 ns シフトされていることを確認してください。

**表 2-24. RGMII 入力のタイミング仕様**

| パラメータ                     | テスト条件                                      | 最小値 | 標準値 | 最大値 | 単位 |

|---------------------------|--------------------------------------------|-----|-----|-----|----|

| T <sub>cyc</sub>          | TX_CLK および クロックサイクル期間                      | 36  | 40  | 44  | ns |

| T <sub>setup(align)</sub> | TX_D[3:0]、TX_CTRL を TX_CLK にセットアップ (整列モード) | 1   | 2   |     | ns |

| T <sub>hold(align)</sub>  | TX_D[3:0]、TX_CTRL を TX_CLK にホールド (整列モード)   | 1   | 2   |     | ns |

**表 2-25. RGMII 出力タイミング仕様**

| パラメータ                        | テスト条件                                             | 最小値  | 標準値 | 最大値 | 単位 |

|------------------------------|---------------------------------------------------|------|-----|-----|----|

| T <sub>skew(align)</sub>     | RX_D[3:0]、RX_CLK からの RX_CTRL 遅延 (整列モード)           | -500 | 0   |     | ps |

| T <sub>setup(shift)</sub>    | RX_D[3:0]、RX_CLK からの RX_CTRL の遅延 (シフトモード有効、デフォルト) | 1.2  | 2   |     | ns |

| T <sub>cyc</sub>             | RX_CLK および クロックサイクル期間                             | 36   | 40  | 44  | ns |

| Duty_G                       | RX_CLK および デューティサイクル                              | 40   | 50  | 60  | %  |

| T <sub>r/T<sub>f</sub></sub> | RX_CLK および立ち上がり、立ち下がり時間 (20% ~ 80%)               |      |     | 750 | ps |

## 2.5 ループバックと PRBS

### 2.5.1 ループバック モード

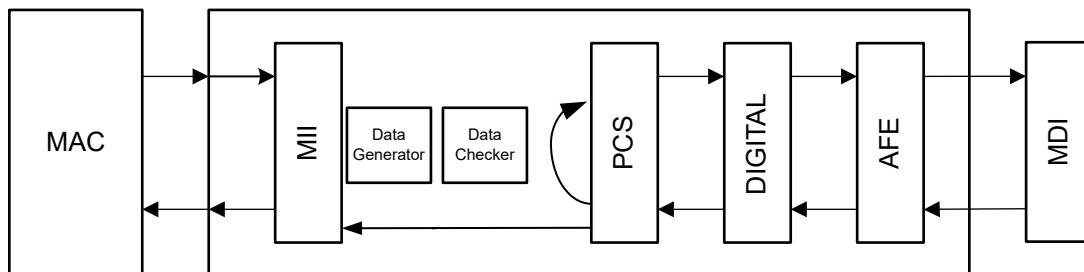

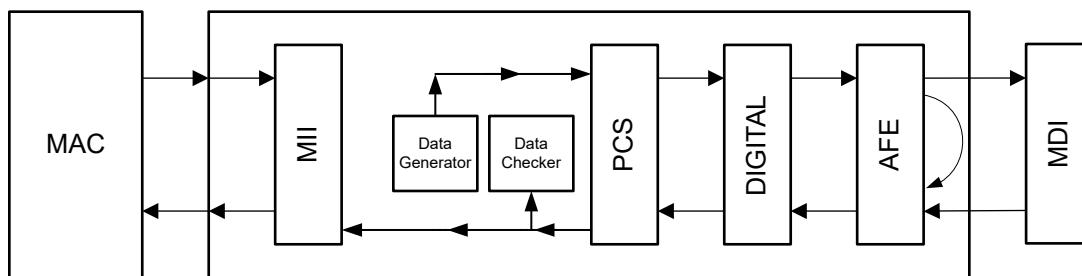

PHY 内の様々な機能ブロックをテストおよび検証するループバックテストには、いくつかのオプションがあります。ループバックモードを有効にすると、xMII / PCS / デジタル / AFE ループバックを使用して MAC と PHY 間の接続を検査できるほか、リバースループバックを使用して PHY と MDI 間の接続を検査できます。

**図 2-22. MAC 側アナログループバックモードの例**

**図 2-23. ブロック図、リバース (ケーブル側) ループバックモード**

MAC と PHY 間のデータパス全体を確認するにはアナログ ループバックが推奨されます。一方、リンクパートナーとリバース ループバックを使用して、PHY と MDI (リンクパートナー) 間のデータパスを検証することもできます。

デバイスには、インサーキットテストや診断に対応する PRBS 内蔵セルフテスト (BIST) 回路も内蔵されています。BIST は、様々なループバックモードを使用して実行でき、可変コンテンツを含むパケット化されたデータを生成することで、データパスの特定の部分における問題を切り分けることができます。データジェネレータとチェック、そして様々なループバックモードを有効にするためのスクリプトが用意されています。

図 2-24. ループバック付きデータジェネレータおよびチェック

### 2.5.2 MAC とのパケットの送受信

MAC を使用してパケットを生成およびチェックできる場合、および PHY にリバース ループバック機能を備えた現用リンクパートナーがある場合は、次のように完全なデータパスを確認します。

1. 電源を供給し、PHY を MAC とワギングリンク パートナーに接続します。

2. リンクパートナーでリバース ループバックを有効にします。

3. MAC から PHY にテスト パケットを送信します。

4. MAC が同じテスト パケットを受信することを確認します。

MAC が問題なく送信された同じテスト パケットを受信する場合、MAC から PHY、リンクパートナー (MDI) を経由するデータパス全体は有効です。このテストに合格しない場合は、アナログ ループバックを実行してデータパス上の問題を切り分けます (アナログ ループバックを実行する前にケーブル側の接続を外してください)。

1. 電源を入れ、PHY を MAC に接続します。

2. PHY でアナログ ループバックを有効にします (レジスタ 0x0016 = 0x0108 を書き込みます)。

3. MAC から PHY にテスト パケットを送信します。

4. MAC が同じテスト パケットを受信することを確認します。

MAC が同じテスト パケットを受信すると、MAC → PHY を経由するデータ パスが有効であり、問題が MDI データ パスに分離されています。このテストに合格しない場合は、MAC インターフェースに問題がある可能性があります。MAC インターフェースを確認するには、MII チェックを参照してください。

以下は、アナログ ループバックを実行するためのレジスタの読み取りと書き込みのシーケンス例です。

```

// Analog Loopback

begin

001F 8000 //Hard Reset

0000 2100 //Disables Auto-Neg, Selects 100 Mbps

0016 0108 //Select Analog Loopback

030B 3380 //This helps PRBS LOCK

0016 3108 //Enables PRBS Checker Config & Packet Generation Enable

//After you write '3108' the register should Read 3b04. (Bit 11 & 9 go high)

001B 807D //Lock Error Counter's value

001B

//after running this test check register 0010 bit 0 should be 1

end

```

### 2.5.3 BIST を使用してパケットを送受信しています

MAC でパケットを生成およびチェックできない場合は、外部パケットジェネレータまたは内部 PRBS パケット生成およびチェック機能を使用してデータパスを検証してください。PRBS および現用リンクパートナーでリバースループバックを実行するには、次の手順を実行します。

1. PHY に電源を供給し、リンクパートナーに接続します。

2. PHY で PRBS パケット生成を有効にします (レジスタ 0x16 を 5000 に書き込みます)。

3. リンクパートナーでリバースループバックを有効にします。

4. 少なくとも 1 秒待ってから、PHY で PRBS ロックステータスを確認します (レジスタ 0x17[11:10] を読み取ります)。

レジスタ 0x17[11] が high の場合、PHY → MDI を経由するデータパスが有効です。このテストに合格しない場合は、PHY の内部データパスまたは MDI に問題がある可能性があります。内部データパスを確認するには、次のスクリプトを使用して、アナログループバックで PRBS を実行します。内部データパスが有効である場合、問題は MDI に切り分けられます (リンクパートナーが動作していると仮定します)。

以下のコードは、2 つの DP83822 PHY を使用して BIST を実行するためのレジスタ読み取りおよび書き込みのシーケンス例です。

```

// Reverse Loopback on PHY

begin

001F 8000 //Hard Reset

0000 2100 //Disables Auto-Neg, Selects 100 Mbps

0016 7100 //Enables PRBS packet generation

0016 // check PRBS lock status on bit 10 high

end

// Reverse Loopback on Link Partner

begin

001F 8000 //Hard Reset

0000 2100 //Disables Auto-Neg, Selects 100 Mbps

0016 0110 //Select Reverse Loopback

end

```

### 3 ツールとリファレンス

#### 3.1 DP83822 のレジスタアクセス

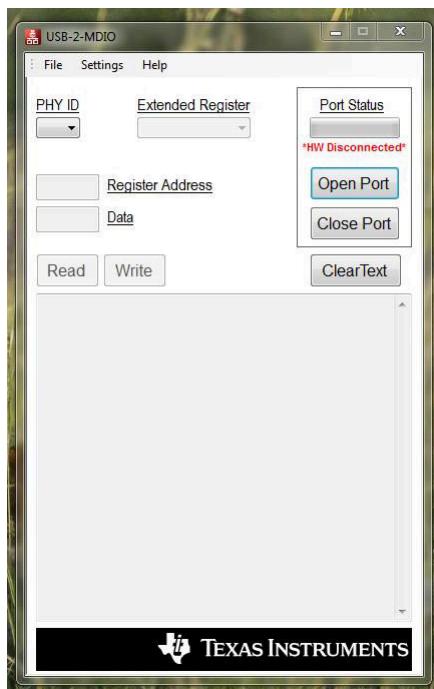

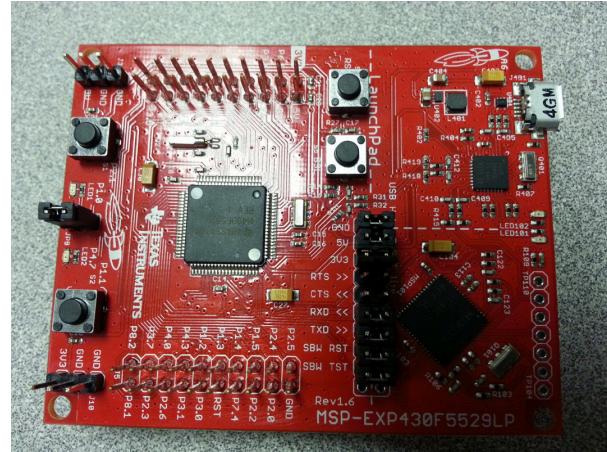

アプリケーションでレジスタアクセスが容易に利用できない場合は、テキサス インストルメンツから USB-2-MDIO GUI が提供されており、eStore で購入可能な MSP430 Launchpad で使用できます。この GUI は、レジスタの読み書きとスクリプトファイルの実行をサポートしています。DP83822 および Ethernet ポートフォリオの他のデバイスで使用できます。USB-2-MDIO ユーザーズガイドと GUI は、<http://www.ti.com/tool/usb-2-mdio> からダウンロードできます。

図 3-1. USB-2-MDIO GUI

図 3-2. MSP430 LaunchPad

以下は、ヘルプメニューの USB-2-MDIO GUI にも表示されるサンプルスクリプトです。

```

// This is how you make a comment. All scripts must start with 'begin'

begin

// To read a register, all you need to do is put down the 4 digit

// HEX value of the registers (from 0000 to FFFF)

// Example to read registers 0001, 000A, and 0017

0001

000A

0017

// To write a register, all you need to do is put down the 4 digit

// HEX value of the register (from 0000 to FFFF) followed by the

// HEX you desire to configure the register to (from 0000 to FFFF)

// Example to write 2100 to register 0000 and

// Example to write 0110 to register 0016

0000 2100

0016 0110

// You must end the script by adding 'end' once you are finished

end

```

IEEE 802.3 で定義されているシリアルマネジメントインターフェース (MDI) は、シングルマスター バスです。MDI クロックは、バスマスター (通常は Ethernet MAC) によって生成されます。USB-2-MDIO GUI を使用するには、MSP430 Launchpad と DP83822 の MDIO ピンおよび MDC ピンを直接接続する必要があります。

- MSP430 ピン 4.2 から PHY の MDIO ピン

- MSP420 ピン 4.1 から PHY の MDC ピン

### 3.2 Linux でのソフトウェアおよびドライバのデバッグ

Linux システムで PHY が機能するために必要な 2 つの必須コンポーネントは、デバイスツリーとドライバーファイルです。DP83822 ドライバーは、[こちら](#)で入手できます。以下に、デバイスツリーの例を示します。

```

mdio0 {

#address-cells = <1>;

#size-cells = <0>;

ethphy0: ethernet-phy@0 {

reg = <0>;

rx-internal-delay-ps = <1>;

tx-internal-delay-ps = <1>;

};

```

---

#### 注

サンプルのバインディングファイルは、以下のリンクから参照ください:[root/Documentation/devicetree/bindings/net/ti,dp83822.yaml](#)

---

#### 3.2.1 一般的な端子出力とソリューション

端子コマンド「dmesg | grep mdio」を使用すると、ソフトウェアの観点から PHY が適切に機能しない原因について、いくつかの手がかりが得られる可能性があります。

```

$ dmesg | grep "mdio"

```

出力例の 1 つを以下に示します。

```

$ mdio_bus xxx.ethernet-x: MDIO device at address 8 is missing

```

このメッセージは、PHY が MDIO バス上に見つかることを示しています。これはいくつかの問題が原因である可能性があります。最も一般的な原因はデバイスツリーの欠落または誤りですが、PHY が機能していない、または SMI 接続が不良であることもあります。

MDIO バス上で PHY が検出されると、次のような一般的なエラーメッセージが表示されます。

```

$ Generic PHY xxx.ethernet-x: attached PHY driver [Generic PHY]

```

このメッセージは、対応する PHY のドライバファイルが正しくロードされていないか、全く存在せず、Linux が PHY で動作しない可能性が高い汎用ドライバをロードしたことを示しています。その場合、ドライバが正常にコンパイルされ、Linux に追加されたことを確認し、使用している PHY のモデルと一致していることを確認してください。

最後に、次のようなメッセージが表示される場合があります。

```

$ am65-cpsw-nuss c000000.ethernet eth3: PHY [c000f00.mdio:05] driver [TI DP83822] (irq=POLL)

```

このメッセージは、PHY に正しいドライバがロードされ、正常に検出されたことを示しています。ifconfig を実行して、ネットワークインターフェースが存在することを確認します。

PHY がネットワークアダプターとして正常に認識された場合の **ifconfig** の出力例を示します。

```

root@j7-evm:~# ifconfig

eth0: flags=4099<UP,BROADCAST,MULTICAST> mtu 1500 metric 1

ether 24:76:25:a2:62:8b txqueuelen 1000 (Ethernet)

RX packets 0 bytes 0 (0.0 B)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 0 bytes 0 (0.0 B)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

lo: flags=73<UP,LOOPBACK,RUNNING> mtu 65536 metric 1

inet 127.0.0.1 netmask 255.0.0.0

inet6 ::1 prefixlen 128 scopeid 0x10<host>

loop txqueuelen 1000 (Local Loopback)

RX packets 82 bytes 6220 (6.0 KiB)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 82 bytes 6220 (6.0 KiB)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

```

次のステップは、データ転送が成功したことを確認することです。

## 4 まとめ

このアプリケーション ノートでは、新しいアプリケーションを評価し、予想される機能を確認するための推奨フローを紹介します。ステップバイステップの推奨事項により、DP83822 設計のボード立ち上げと初期評価が容易になります。

## 5 参考資料

EMC / EMI コンプライアンステストのハードウェアおよびソフトウェア構成については、以下のドキュメントをご覧ください。

テキサス インstrumentツ、*IEEE Ethernet* コンプライアンステストに合格する方法、アプリケーションレポート。

テキサス インstrumentツ、*DP838xx を Ethernet* コンプライアンステスト用に構成する方法、アプリケーションレポート。

## 6 改訂履歴

| Changes from Revision * (December 2023) to Revision A (July 2025) | Page |

|-------------------------------------------------------------------|------|

| ドキュメント全体にわたって表、図、相互参照の採番方法を更新。読みやすさを向上させるためにドキュメント全体の構造を更新しました。   | 1    |

| 電源ランプシーケンスのチェックセクションを追加しました。                                      | 3    |

| セクション 2.2.1.1 を追加                                                 | 5    |

| RBIAS ピンのプローブのセクションを追加しました。RBIAS を 2.7V から 1V に更新。                | 6    |

| セクション 2.3.1 を追加                                                   | 13   |

| MSE リンクの品質範囲表を 10 進数から 16 進数に更新しました。                              | 15   |

| 準拠セクションを追加しました。                                                   | 18   |

| RMII チェックセクションを追加しました。                                            | 20   |

| 「MAC でパケットを送受信する」セクションを追加                                         | 27   |

| 概要セクションを追加しました。                                                   | 32   |

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月