*Application Note***DP83869 ブラブルシューティング ガイド**

Alvaro Reyes

**概要**

DP83869HM は、堅牢でフル機能のギガビット物理レイヤ (PHY) トランシーバです。DP83869 の各種動作モードについて理解するには、DP83869HM の各モードについて詳細に説明しています。このアプリケーションノートは、設計で DP83869HM のトラブルシューティングを支援し、PHY が意図したとおりに動作していない場合に何を確認すべきかを説明するために作成されました。

**目次**

|                                        |    |

|----------------------------------------|----|

| <b>1 DP83869 アプリケーションの概要</b>           | 3  |

| <b>2 アプリケーションのトラブルシューティング</b>          | 4  |

| 2.1 回路図とレイアウトのチェックアウト                  | 4  |

| 2.2 デバイスの正常性チェック                       | 4  |

| 2.2.1 電圧チェック                           | 4  |

| 2.2.2 RESET_N 信号をプロープします               | 6  |

| 2.2.3 RBIAS をプロープします                   | 6  |

| 2.2.4 XI クロックをプロープします                  | 7  |

| 2.2.5 初期化中にストラップ ピンをプロープします            | 8  |

| 2.2.6 シリアル管理インターフェイス信号のプロープ (MDC、MDIO) | 9  |

| 2.3 MDI ヘルス チェック                       | 10 |

| 2.3.1 磁気                               | 11 |

| 2.3.2 MDI 信号をプロープします                   | 11 |

| 2.3.3 リンク品質の確認                         | 13 |

| 2.3.4 コンプライアンス                         | 14 |

| 2.4 MII ヘルス チェック                       | 15 |

| 2.4.1 MII チェック                         | 15 |

| 2.4.2 RGMII チェック                       | 18 |

| 2.4.3 SGMII チェック                       | 24 |

| 2.5 ループバックと PRBS                       | 25 |

| 2.5.1 ループバック モード                       | 25 |

| 2.5.2 MAC とのパケットの送受信                   | 25 |

| 2.5.3 BIST を使用してパケットを送受信しています          | 26 |

| <b>3 動作モードの説明</b>                      | 27 |

| 3.1 ブリッジ モード                           | 27 |

| 3.2 ファイバ構成                             | 28 |

| 3.2.1 ファイバ レジスター                       | 28 |

| 3.2.2 メディアコンバータの LED 動作                | 28 |

| <b>4 ツールおよびリファレンス</b>                  | 29 |

| 4.1 拡張レジスタ アクセス                        | 29 |

| 4.1.1 読み出し (ポスト インクリメントなし) 動作          | 30 |

| 4.1.2 書き込み (ポスト インクリメントなし) 動作          | 30 |

| 4.2 Linux でのソフトウェアおよびドライバ デバッグ         | 31 |

| 4.2.1 共通端子出力                           | 31 |

| <b>5 まとめ</b>                           | 32 |

| <b>6 参考資料</b>                          | 33 |

| <b>7 改訂履歴</b>                          | 34 |

**商標**

MSP430F5529™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 1 DP83869 アプリケーションの概要

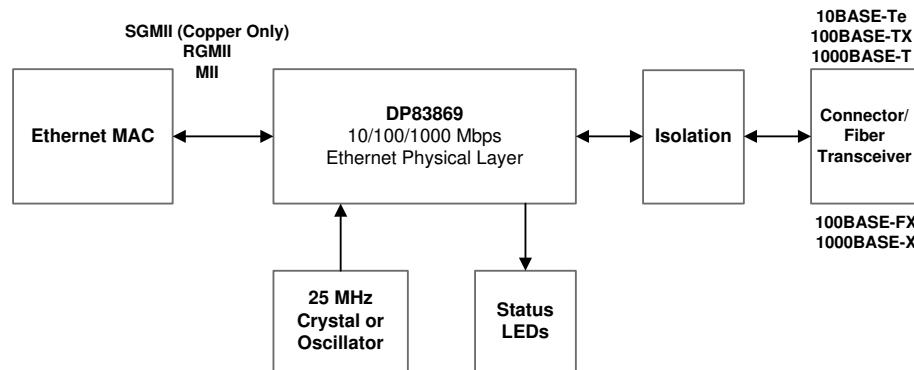

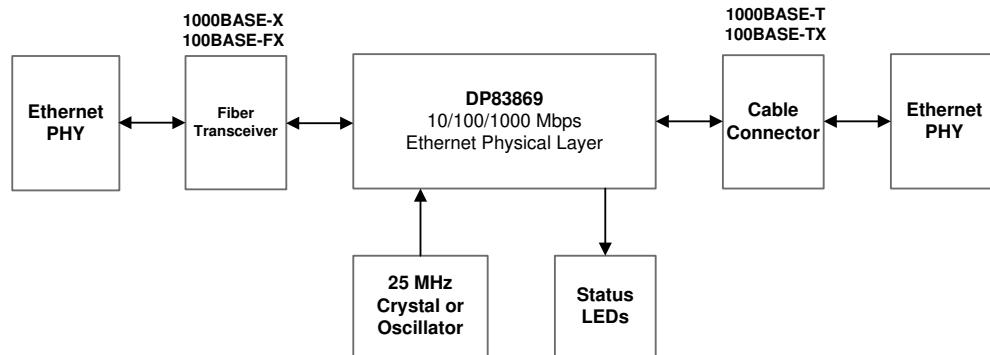

DP83869HM デバイスは、10BASE-T、100BASE-TX、1000BASE-T のイーサネットプロトコルをサポートする、堅牢で完全な機能を備えた、PMD サブレイヤ内蔵型のギガビット物理レイヤ (PHY) トランシーバです。DP83869 では、1000BASE-X および 100BASE-FX のファイバー プロトコルもサポートしています。

図 1-1. 標準的なイーサネットシステムのブロック図

図 1-2. メディア コンバータのシステム ブロック図

## 2 アプリケーションのトラブルシューティング

以下のセクションでは、PHY 設計のサブシステムを切り分けて、サブシステムがアプリケーションの問題に寄与しているかどうかを確認する、ハイレベルで基本的なチェック アプローチからデバッグを行います。このドキュメントは、次のような一般的なイーサネットの問題を解決することを目的としています。

- ping ができない

- リンクを取得できない、または間欠的なリンクアップ

- リンクアップしているが、パケット エラーが表示されています

- レジスタにアクセスできません

特に指定のない限り、以下のセクションを順番に見ていくことをお勧めします。

### 2.1 回路図とレイアウトのチェックアウト

[DP83869 回路図チェックリスト](#) および [DP838XX 産業用レイアウト チェックリスト](#) は、DP83869 を使用した設計のベスト プラクティスを使いやすいドキュメントにまとめたものです。PHY の動作に必要な接続とコンポーネントを詳しく説明するために、このドキュメントを通すことを推奨します。

以下のセクションでは、PHY に電源が供給され、正しく初期化された場合に予想される動作を示します。予期される動作から逸脱した場合、不適切なペリフェラル回路によるエラーが原因である可能性があります。

### 2.2 デバイスの正常性チェック

このセクションでは、デバイスの電源が供給され、正しく初期化されていることを確認するデバイスの状態チェックについて説明します。DP83869 が次の場合、このセクションはスキップできます。

- リンク パートナーに接続されている場合のリンクアップ (LED 表示またはレジスタ ステータス)、またはイーサネット ケーブルが接続されていない場合の FLP 信号を表示します

- レジスタ アクセスに応答 (該当する場合)

#### 2.2.1 電圧チェック

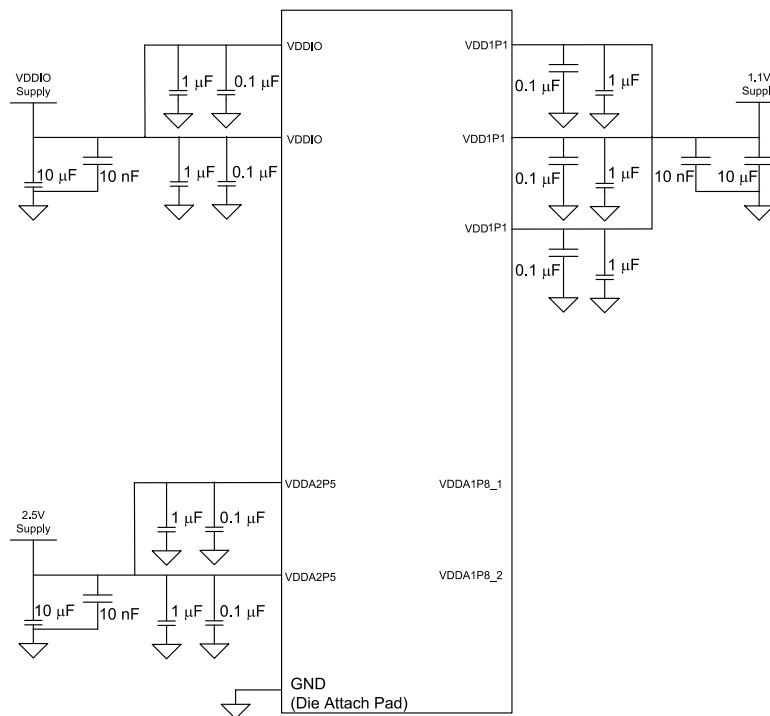

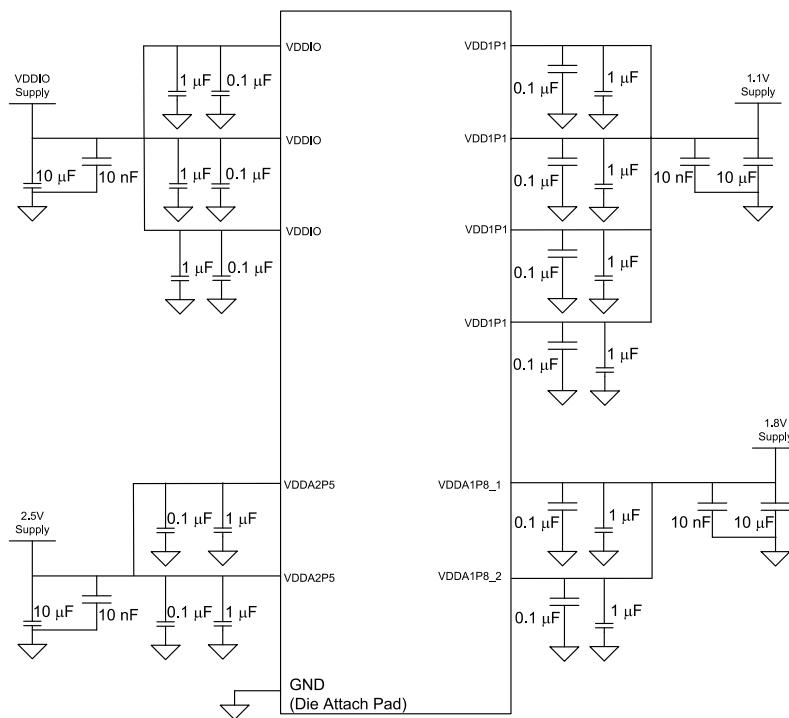

DP83869 には十分な電力と以下が必要です：

- レールごとに 10nF 1 個と 10uF のデカッピング 1 個

- ピンごとに 100nF1 個と 1uF のデカッピング 1 個

DP83869 は、以下の図に示す電源に関して、2 つの構成をサポートしています。

図 2-1.2 電源設定

図 2-2.3 電源設定

3 電源構成で動作する場合、TI は、すべての電源に電力を一緒に供給することを推奨します。すべての電源に同時に電力を供給できない場合、最初に VDD1P1 と VDD2P5 に電力を供給し、50ms 以内に VDDIO と VDD1P8 に電力を供給します。

2 電源構成で動作する場合は、両方の VDDA1P8 ピンを未接続にし、すべての電源に一緒に電力を供給します。すべての電源に同時に電力を供給できない場合、最初に VDDA2P5 と VDD1P1 に電力を供給し、50ms 以内に VDDIO に電力を供給します。

デバイスの電源を投入し、ピンにできるだけ近い場所で DC 測定を行います。各測定値が 表 2-1 で定義されている制限範囲内であることを確認します

**表 2-1. 推奨動作条件**

|              | 最小値 (V) | 標準値 (V) | Max(V) |

|--------------|---------|---------|--------|

| VDDIO (1.8V) | 1.71    | 1.8     | 1.89   |

| VDDIO (2.5V) | 2.375   | 2.5     | 2.625  |

| VDDIO (3.3V) | 3.15    | 3.3     | 3.45   |

| VDD1P1       | 0.99    | 1.1     | 1.21   |

| VDDA1P8      | 1.71    | 1.8     | 1.89   |

| VDDA2P5      | 2.375   | 2.5     | 2.625  |

### 2.2.2 RESET\_N 信号をプロープします

DP83869 のリセット機能はアクティブ low です。このピンには弱い内部プルアップ抵抗があり、未接続のままにするか、外部で駆動しない場合にデフォルト状態になります。

コントローラが RESET\_N 信号を low に駆動していないことを確認します。そうしないと、デバイスはリセット状態に保持され、レジスタ コマンドに応答せず、リンク アップもしません。

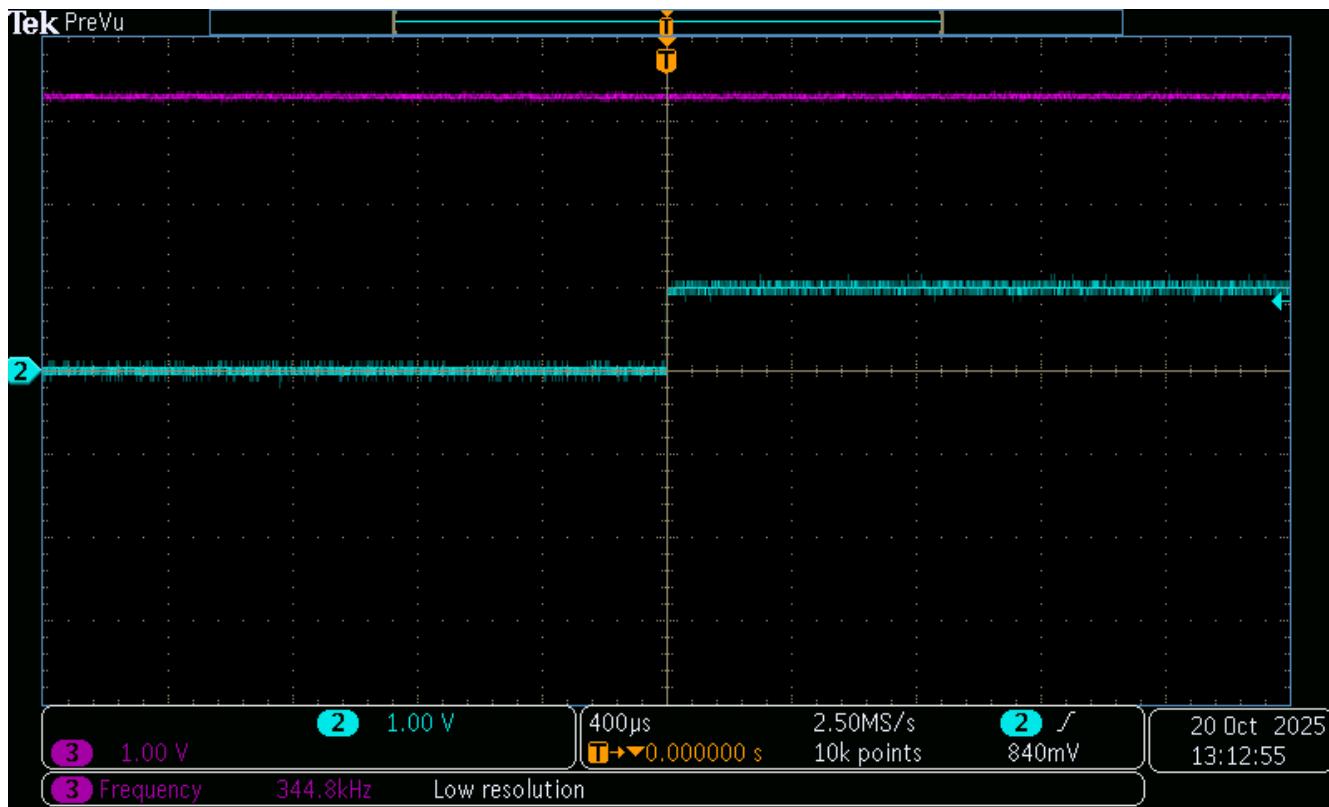

### 2.2.3 RBIAS をプロープします

RBIAS ピンは、DP83869 内の内部基準電流を設定するために使用されます。RBIAS は、公差 1% の 11kΩ 抵抗を使用する必要があります。許容範囲が大きくなる可能性があるため、複数の連続して 1 つの構成部品を使用することをお勧めします。

適切に電力を供給すると、RBIAS ピンをプロープする際に 1V 信号が表示されます。

図 2-3. R<sub>BIAS</sub> 電圧 (青) および V<sub>DDIO</sub> (紫)

#### 2.2.4 XI クロックをプロープします

以下のガイドラインは、互換性のある入力クロックを参照するための主な仕様です：

表 2-2. 25MHz 水晶振動子仕様

| パラメータ    | 最小値  | 標準値 | 最大値 | 単位  |

|----------|------|-----|-----|-----|

| 周波数      |      | 25  |     | MHz |

| 周波数の許容誤差 | -100 |     | 100 | ppm |

| 負荷容量     | 15   |     | 40  | pF  |

| ESR      |      |     | 50  | Ω   |

水晶振動子ノードでプロープを行うと、容量性負荷が変化するため、動作周波数が変化することがあります。水晶振動子をクロックソースとして使用する場合は、CLK\_OUT 信号をプロープします。CLK\_OUT のデフォルト信号は、XI リファレンスのバッファ付きバージョンであり、代表的な測定値を提供します。

表 2-3. 25MHz 発振器の仕様

| パラメータ           | 最小値  | 標準値 | 最大値 | 単位  |

|-----------------|------|-----|-----|-----|

| 周波数             |      | 25  |     | MHz |

| 周波数の許容誤差        | -100 |     | 100 | ppm |

| 立ち上がりまたは立ち下がり時間 |      |     | 5   | ns  |

| デューティサイクル       | 40   |     | 60  | %   |

| ジッタ RMS         |      |     | 11  | ps  |

**注**

水晶振動子ネットワークを使った設計の詳細については、[アプリケーション ノートテキサス インストゥルメンツのイーサネット物理層トランシーバ用水晶振動子の選択と仕様](#)を参照してください。

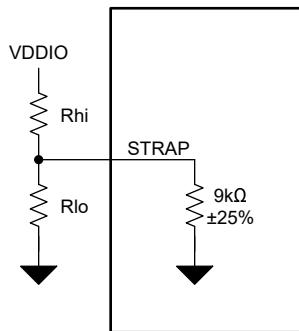

**2.2.5 初期化中にストラップピンをプロープします**

DP83869 にはデバイスをあらかじめ設定されたモードに構成するためのストラップ ピンがあります。これらのストラップ ピンの電圧によって、DP83869 が動作できるモードが決まります。

初期化時に、外部ストラップ ネットワークと内部抵抗により、PHY がサンプリングする分圧器が形成されます。ライン上の他のコンポーネントが、このネットワークで設定される DC バイアスに影響を与えてはなりません。

図 2-4. DP83869 のストラップ回路

図 2-5. DP83869 LED ストラップ回路

場合によっては、ボード上の他のデバイス (MAC など) がこれらのピンを予期せずプルまたは駆動することができます。ストラップ値はレジスタ 0x006E (STRAP\_STS) から読み出すことができます。問題にパワー サイクルの依存性が存在する場合、ストラップが限界的である可能性があり、このレジスタに対してサイクルごとに観測して、PHY が意図しない状態にストラップされているかどうかを判定できます。

測定は、電源オン時および電源オン後に、RESET\_N 信号がアサートされているときに行うことができます。

**注**

レジスタ 0x6E は拡張レジスタであり、直接アクセスすることはできません。[セクション 4.1](#) を参照してください。

**2.2.5.1 正しい動作モードの構成**

DP83869 の動作モードは、OPMODE[0]、OPMODE[1]、OPMODE[2] ストラップにより構成されます。各 OPMODE 構成の概要を表 2-4 に示します。詳細については、[データシートのプログラミングセクション](#)を参照します。

DP83869 の動作モードを確認するには、レジスタ 0x6E を読み出して確認できます。レジスタ 0x6E は読み取り専用であり、このレジスタに書き込んで動作モードを変更することはできません。DP83869 のソフトウェア設定は、レジスタ 0x1DF を使用して行うことができ、このレジスタへの書き込みによって OPMODE を構成できます。一部の動作モードでは、レジスタ 0x1DF だけでなく、より多くのレジスタへの書き込みが必要です。この情報は、[データシート](#)の動作モードのレジスタ構成セクションに記載されています。

注

レジスタ 0x6E および 0x1DF は拡張レジスタであり、直接アクセスすることはできません。[セクション 4.1](#) を参照してください。

表 2-4. 機能モードストラップ表

| ピン名                 | ストラップ名    | ピン番号 | デフォルト | OPMODE[2] | OPMODE[1] | OPMODE[0] | 機能モード                                                |

|---------------------|-----------|------|-------|-----------|-----------|-----------|------------------------------------------------------|

| JTAG_TDO/<br>GPIO_1 | OPMODE[0] | 22   | 0     | 0         | 0         | 0         | RGMII から銅線へ<br>(1000Base-T/100Base-TX/<br>10Base-Te) |

|                     |           |      |       | 0         | 0         | 1         | RGMII から 1000Base-X へ                                |

| RX_D3               | OPMODE[1] | 36   | 0     | 0         | 1         | 0         | RGMII から 100Base-FX へ                                |

|                     |           |      |       | 0         | 1         | 1         | RGMII-SGMII ブリッジ モード                                 |

| RX_D2               | OPMODE[2] | 35   | 0     | 1         | 0         | 0         | 1000Base-T から<br>1000Base-X へ                        |

|                     |           |      |       | 1         | 0         | 1         | 100Base-Tx から 100Base-<br>FX へ                       |

|                     |           |      |       | 1         | 1         | 0         | SGMII から銅線へ<br>(1000Base-T/100Base-TX/<br>10Base-Te) |

|                     |           |      |       | 1         | 1         | 1         | バウンダリ スキャン用 JTAG                                     |

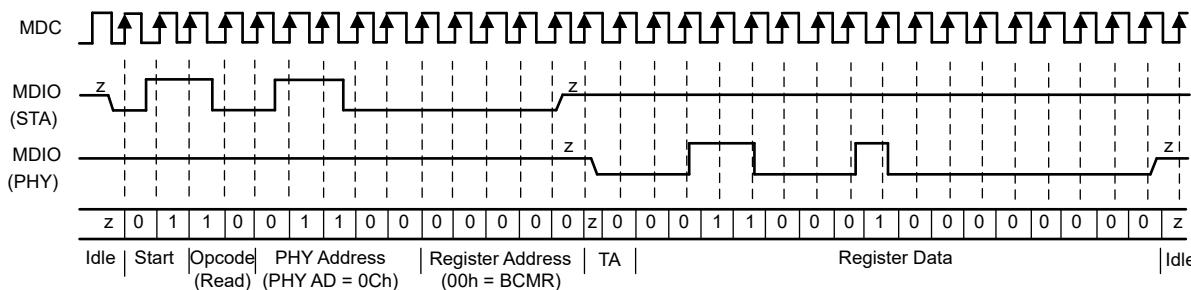

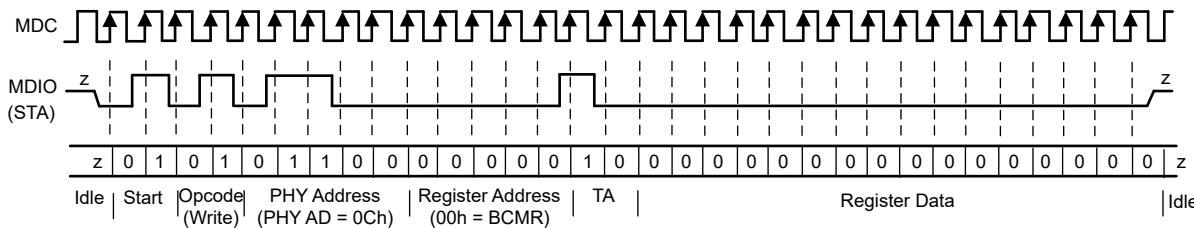

#### 2.2.6 シリアル管理インターフェイス信号のプローブ(MDC、MDIO)

シリアル管理インターフェイス (SMI) は、デバッグ中にステータス フィールドを提供するのに役立ちます。このピンは PHY に対してオープンドレインであるため、MDIO ラインに VDDIO へのプルアップ抵抗が接続されていることを確認します。アイドル時は、電圧を VDDIO にする必要があります。SMI アクセスが次のシーケンスに従っていることを確認します：

図 2-6. SMI 読み取り動作

図 2-7. SMI 書き込み動作

### 2.2.6.1 レジスタ値の読み出しと確認

レジスタを読み出し、データシートに示されているデフォルト値を確認します。一部のレジスタは、ストラップ オプションによって異なる場合があることに注意します。オート ネゴシエーションがイネーブルの場合の PHY の動作と 100/1000Mbps でのリンクに対して予測されるレジスタ値の例を [表 2-5](#) に示します。

**表 2-5. リンクアップ時のレジスタ値の例**

| レジスタ・アドレス | レジスタ値   |          | 備考                                                                                                          |

|-----------|---------|----------|-------------------------------------------------------------------------------------------------------------|

|           | 100Mbps | 1000Mbps |                                                                                                             |

| 0x0000    | 1140    | 1140     | オート ネゴシエーション イネーブル                                                                                          |

| 0x0001    | 796D    | 796D     | リンクが確立されました。オート ネゴシエーション ステータスです                                                                            |

| 0x0004    | 01E1    | 01E1     | 10/100Mbps アドバタイズメント                                                                                        |

| 0x0009    | 0000    | 0300     | 1000Mbps アドバタイズメント                                                                                          |

| 0x0011    | 4F02    | BC02     | リンク プロパティ。PHY が所定の速度でリンクされている場合は、これらの値を参考にして、予想される動作との差異を特定します。この表に示されている値と、すべてのレジスタが同じである必要はないことに注意してください。 |

例:PHY に電源を供給し 1000Mbps でリンクした後、Reg 0x11 には値 0xBC02 が格納されます。これにより、以下が確認されます:

- 1000Mbps モード

- 全二重

- オート ネゴシエーション完了

- リンクが確立されました

アプリケーションでレジスタへのアクセスがすぐに利用できない場合、USB-2-MDIO GUI をテキサス インstrumentツから入手でき、MSP430F5529™ Launchpad と組み合わせて使用して、[TI eStore](#) から購入できます。GUI はレジスタの読み書きやスクリプトファイルの実行に対応しており、DP83869HM や TI のイーサネット製品ラインアップに属する他のデバイスと組み合わせて使用できます。USB-2-MDIO ユーザーズガイドと GUI は、[ダウンロード](#)できます。

### 2.3 MDI ヘルス チェック

このセクションでは、デバイスの MDI セクションが正しく動作していることを確認するデバイスのヘルス チェックについて説明します。DP83869 がリンクアップされており、デバイス経由でトラフィックを送信しているときにレジスタ 0x15 でエラーが報告されない場合、このセクションはスキップできます。

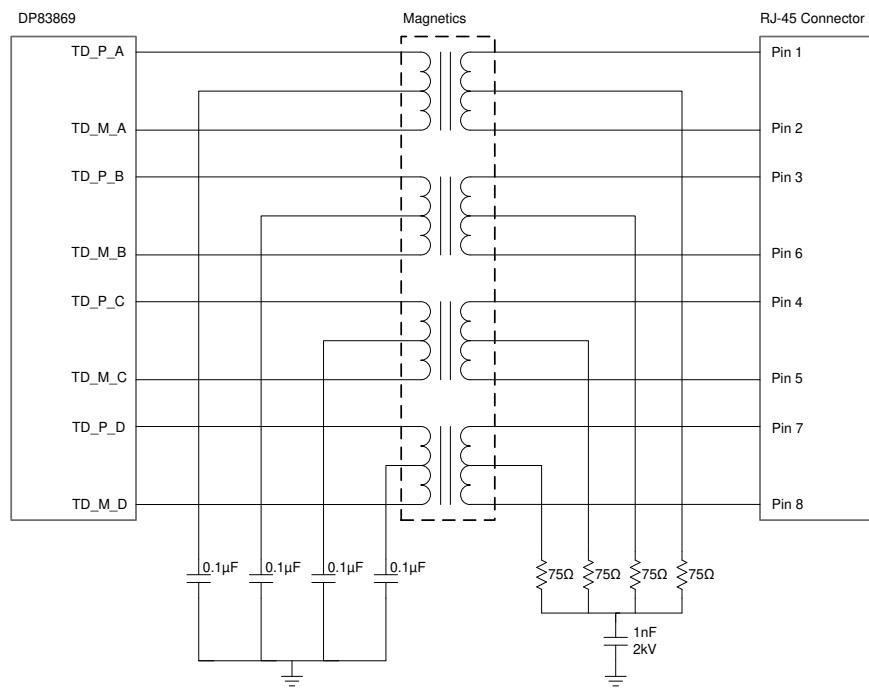

### 2.3.1 磁気

以下のガイドラインは、互換性のある磁気素子を参照するための主な仕様を示しています。

表 2-6. 磁気式絶縁仕様

| パラメータ        | テスト条件       | 標準値  | 単位   |

|--------------|-------------|------|------|

| 巻数比          | 公差 ±2%      | 1:1  | -    |

| 挿入損失         | 1 ~ 100MHz  | -1   | dB   |

| リターン ロス      | 1 ~ 30MHz   | -16  | dB   |

|              | 30 ~ 60MHz  | -12  | dB   |

|              | 60 ~ 80MHz  | -10  | dB   |

|              | 1 ~ 50MHz   | -30  | dB   |

| 差動対コモン モード除去 | 60 ~ 150MHz | -20  | dB   |

|              | 30MHz       | -35  | dB   |

| クロストーク       | 60MHz       | -30  | dB   |

|              | 8mA DC バイアス | 350  | μH   |

| 開路のインダクタンス   | HPOT        | 1500 | Vrms |

| 絶縁           |             |      |      |

これらの正確な要件を満たすことができない場合は、次の許容範囲を適用できます：

- ・巻数比:3% は許容されます

- ・挿入損失:-1 dB または 0dB に近い値

- ・反射(リターン)損失:上記の表の値を満たしますか上回ります。

図 2-8. PHY から RJ45 および磁気部品へ

- ・PHY に接続されている側の各センタータップは互いに絶縁し、デカップリング コンデンサでグランドに接続する必要があります (0.1μF を推奨)。

### 2.3.2 MDI 信号をプロープします

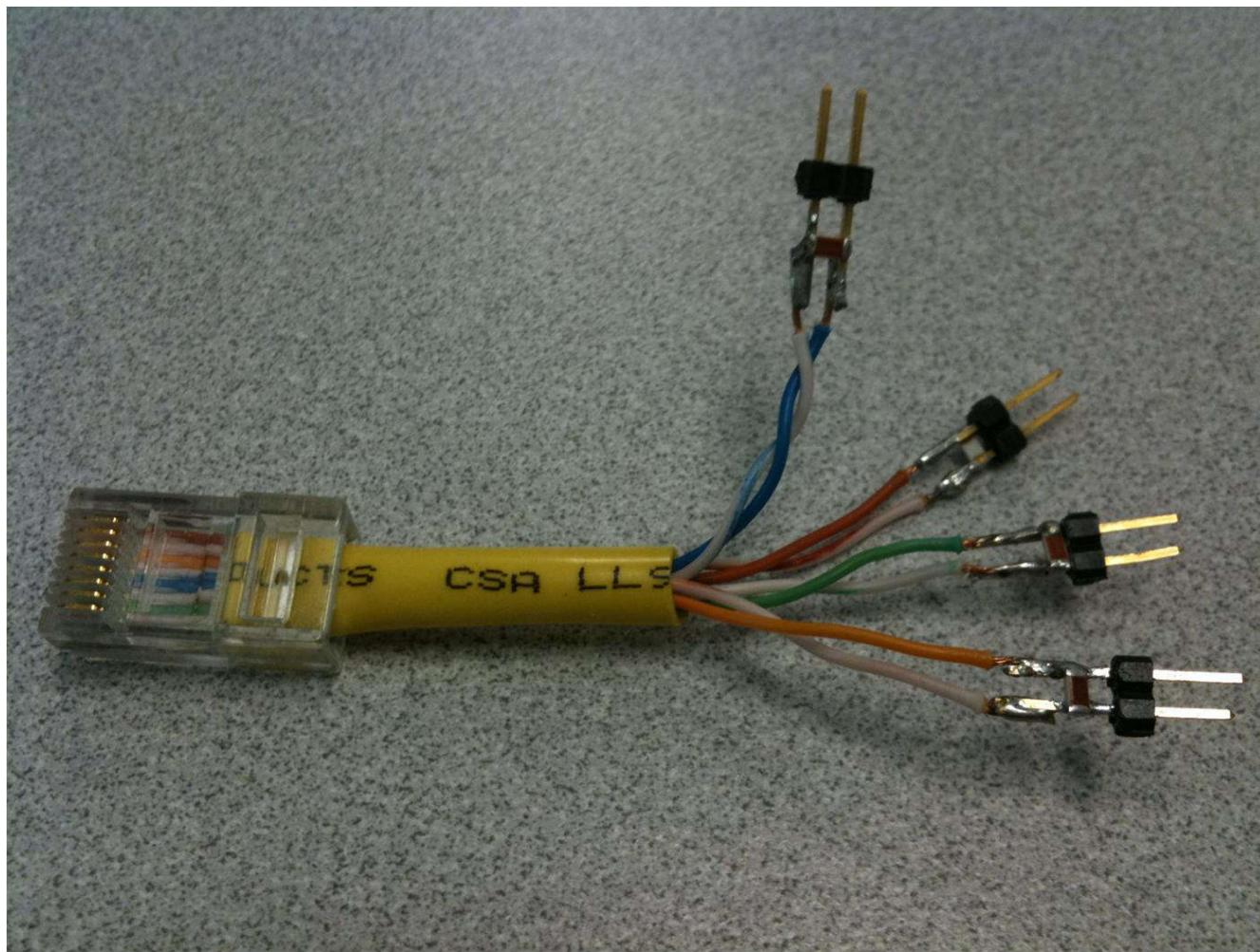

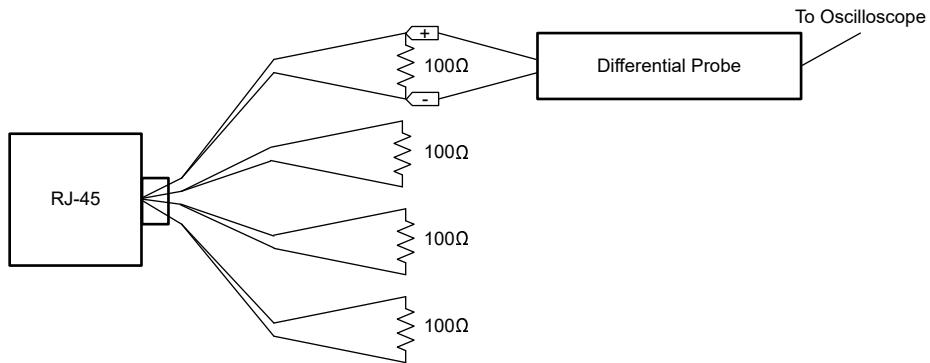

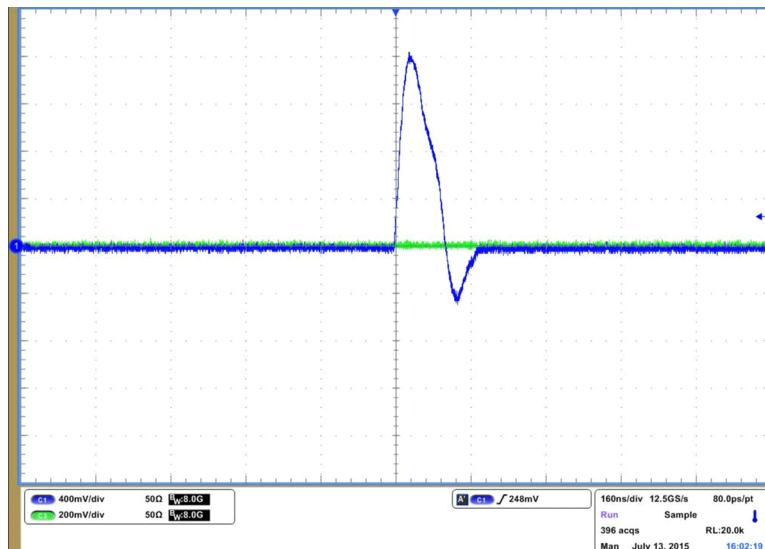

デフォルト設定では、オートネゴシエーションと Auto-MDIX を有効にできます。リンク パルスはチャネル送信 (TD\_P、TD\_M) で確認できる必要があり、受信ペア (RD\_P、RD\_M) に切り替えることもあります。MDI に設定されている場合、こ

のパルスは送信ペアでのみ使用可能ですが、MDI-X に設定されている場合、これは受信ペアでのみ使用可能です。MDI 信号の測定には、 $100\Omega$  の差動で終端された短いイーサネットケーブルを使用する必要があります。終端ケーブルを図 2-7 に示します。終端ケーブルを使用して測定を行うための接続図を Figure 2-8 に示します。

図 2-9.  $100\Omega$  終端ケーブル

図 2-10.  $100\Omega$  終端ケーブルの接続図

オート ネゴテーション リンク パルスの幅は公称  $100\text{ns}$  です。パルスは  $62\mu\text{s}$  または  $125\mu\text{s}$  によって間隔が空けられ、バースト形式で送信されます。バーストは通常  $2\text{ms}$  の持続時間で、 $16\text{ms}$  ごとに発生します。図 2-9 にリンク パルスを示します。

図 2-11. リンク パルスの例

### 2.3.3 リンク品質の確認

有効なリンクを確立し、キー ステータス レジスタの値を確認し、リンク LED が点灯していることを視覚的に確認したら、次のデータ転送デバッグ手順で MDI インターフェイスをチェックします。リンクの問題の原因として考えられるものがいくつかあります。

1. リンク パートナーの送信に問題があります

2. ケーブルの長さと品質

3. 25MHz 基準クロック品質

4. MDI 信号品質

PHY に電源を供給し、リンクパートナーに接続している場合、表 2-6 のレジスタを使用して、平均二乗エラー (MSE) を決定できます。100Mbps 通信については、チャネル A のみを参照してください。MSE 値を使用して、表 2-8 を参照してリンクの品質を確認します：

表 2-7. 1000Mbps 用のリンク品質 MSE レジスタ

| チャネル | レジスタ・アドレス |

|------|-----------|

| A    | 0x0225    |

| B    | 0x0265    |

| C    | 0x02A5    |

| D    | 0x02E5    |

表 2-8. MSE - リンク品質変換

| リンク品質 | MSE 範囲                |

|-------|-----------------------|

| 非常に良好 | 0x020A > MSE          |

| 良好    | 0x033B ≥ MSE > 0x020A |

| 貧乏    | MSE > 0x033B          |

#### 2.3.3.1 ショート ケーブル リンク マージンの改善

DP83869 が長さ 1m 以下の短いケーブルでリンク品質の問題が発生した場合は、以下のセクションを考慮します。

PHY のデジタル信号処理 (DSP) ブロックは、より短い長さで最適でないフィルタ値に収束し、信号対雑音比 (SNR) が低下する可能性があります。以下のレジスタ構成は、DSP が正しく収束しやすくなるようにタイミング帯域幅を調整することで、SNR を改善できます：

```

begin

// Hard Reset

001F 8000

// Threshold for consecutive amount of Idle symbols for Viterbi Idle detector to assert Idle Mode

set to 5

0053 2054

// CAGC DC Compensation Disable

00EF 3840

// Leader Training Timers - increasing time in different training states

0102 7477

0103 7777

0104 4577

// Timing Loop Bandwidth

010C 7777

01C2 7FDE

// Follower Timers - increasing time in different training states

0115 5555

0118 0771

// Timing Loop Bandwidth

011D 6DB2

011E 3FFB

01C3 FFC6

01C4 OFC2

01C5 OFF0

// FFE Fix

012C 0E81

// Soft Reset

001F 4000

end

```

### 2.3.3.2 チャネル間リンク マージンの改善

DP83869 は、AGC ゲイン収束回路 (MDI レシーバの自動ゲイン制御) を使用して、より高速なリンクアップを実現しています。ペア間のリンクアップ時間とゲインミスマッチの間にはトレードオフがあります。パケットエラーが観測されるアプリケーションでは、次のレジスタ書き込みでゲイン収束時間を長くすることで、ゲインマッチングを向上できます：

```

begin

// Hard reset

001F 8000

// Increase time for AGC

0102 7477

// No AGC Re-train

00E4 0080

// Soft reset

001F 4000

end

```

### 2.3.4 コンプライアンス

IEEE 準拠測定は、信号特性を検証するために行うことができます。これらの測定の詳細と PHY を適切に設定する方法については、アプリケーションノート[イーサネットコンプライアンス テスト用に DP8386x を設定する方法](#)を参照してください。

## 2.4 MII ヘルス チェック

このセクションでは、デバイスの MAC インターフェイスが正しく動作していることを確認するデバイスのヘルス チェックについて詳しく説明します。

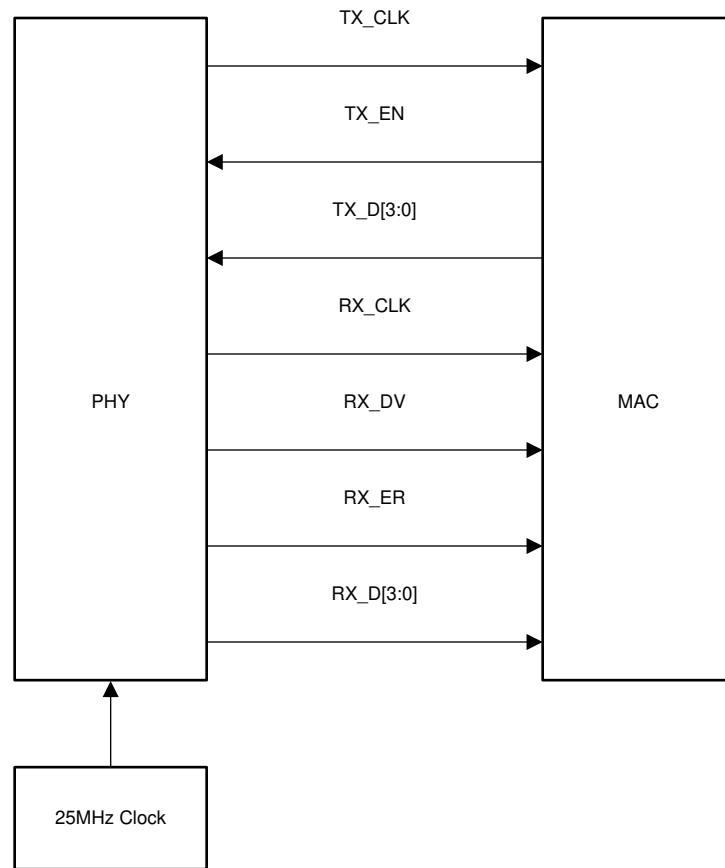

### 2.4.1 MII チェック

メディア独立インターフェース (MII) は、PHY を MAC に接続する同期 4 ビット幅二ブル データ インターフェイスです。MII は IEEE 802.3-2002 条項 22 に完全準拠しています。

MII モードは、ストラップのみを使用してイネーブルにすることはできません。また、レジスタの設定が必要です。次のプロセスを使用して MII モードをイネーブルにします：

1. 銅線 MDI の場合はレジスタ  $0x01DF = 0x0060$ 、ファイバ MDI の場合は  $0x0062$  を書き込みます

2. レジスタ  $0x0018 = 0x000E$  を書き込みます

MII モードでオート ネゴシエーションを使用して MDI 速度を解決する場合、TI は、レジスタ  $0x0009$  を使用してギガビット速度アドバタイズメントを無効にすることを推奨します。

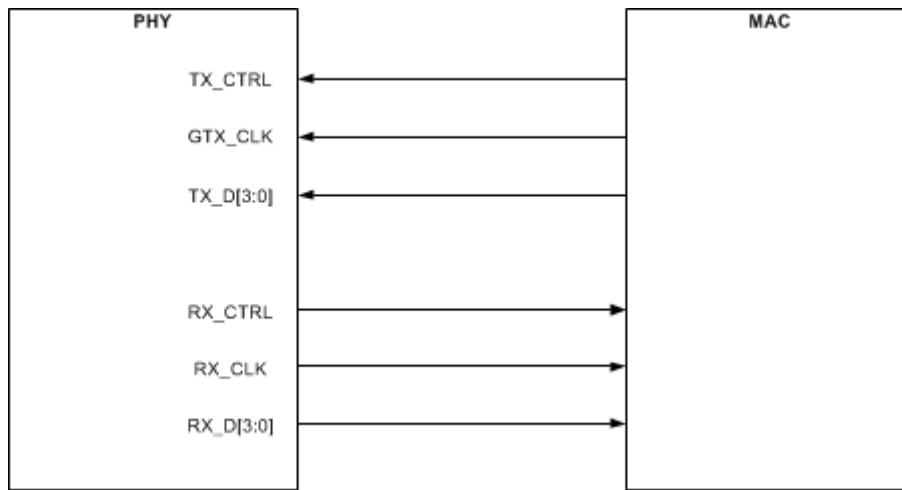

MII 信号の概要は以下の通りです。

**表 2-9. MII 信号**

| 機能     | ピン        |

|--------|-----------|

| データ信号  | TX_D[3:0] |

|        | RX_D[3:0] |

| 信号の送受信 | TX_EN     |

|        | RX_DV     |

| エラー信号  | RX_ER     |

**図 2-12. MII シグナリング**

TX\_D[3:0] のデータは、TX\_CLK を基準として PHY でラッピングされます。RX\_D[3:0] のデータは、RX\_CLK を基準として提供されます。MAC の TX または RX バスに問題があると思われる場合は、トレースのレシーバ側のラインを調べ、レシーバのセットアップ時間とホールド時間が満たされていることを確認します。

**表 2-10. 100M MII のタイミング**

| 仕様                                        | 最小値 | 標準値 | 最大値 | 単位 |

|-------------------------------------------|-----|-----|-----|----|

| TX_CLK High / Low 時間                      | 16  | 20  | 24  | ns |

| TX_CLK までの TX_D[3:0]、TX_EN のセットアップ        | 10  |     |     | ns |

| TX_CLK からの TX_D[3:0]、TX_EN のホールド          | 0   |     |     | ns |

| RX_CLK High / Low 時間                      | 16  | 20  | 24  | ns |

| RX_CLK 立ち上がりからの RX_D[3:0]、RX_ER、RX_DV の遅延 | 10  |     | 30  | ns |

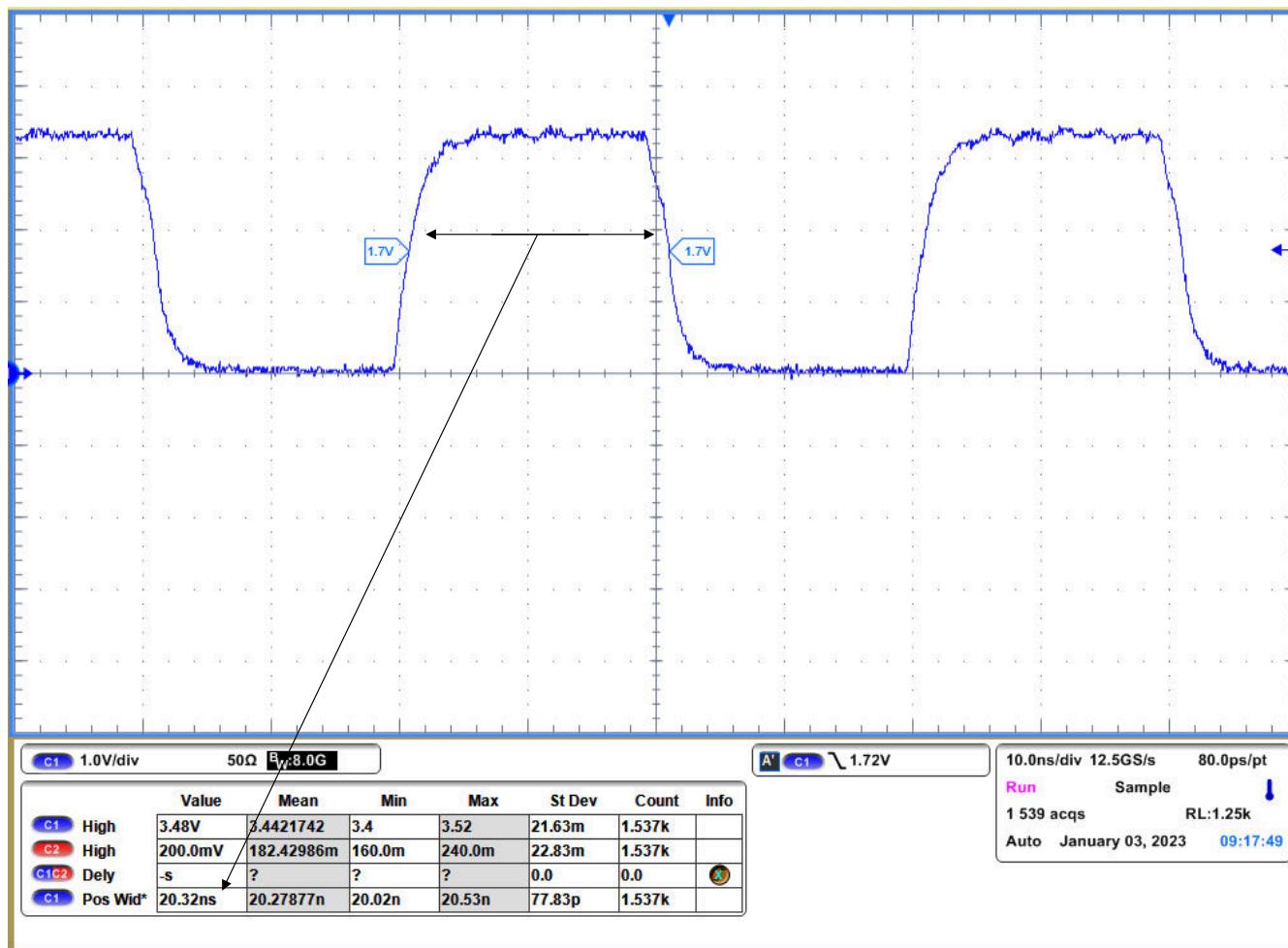

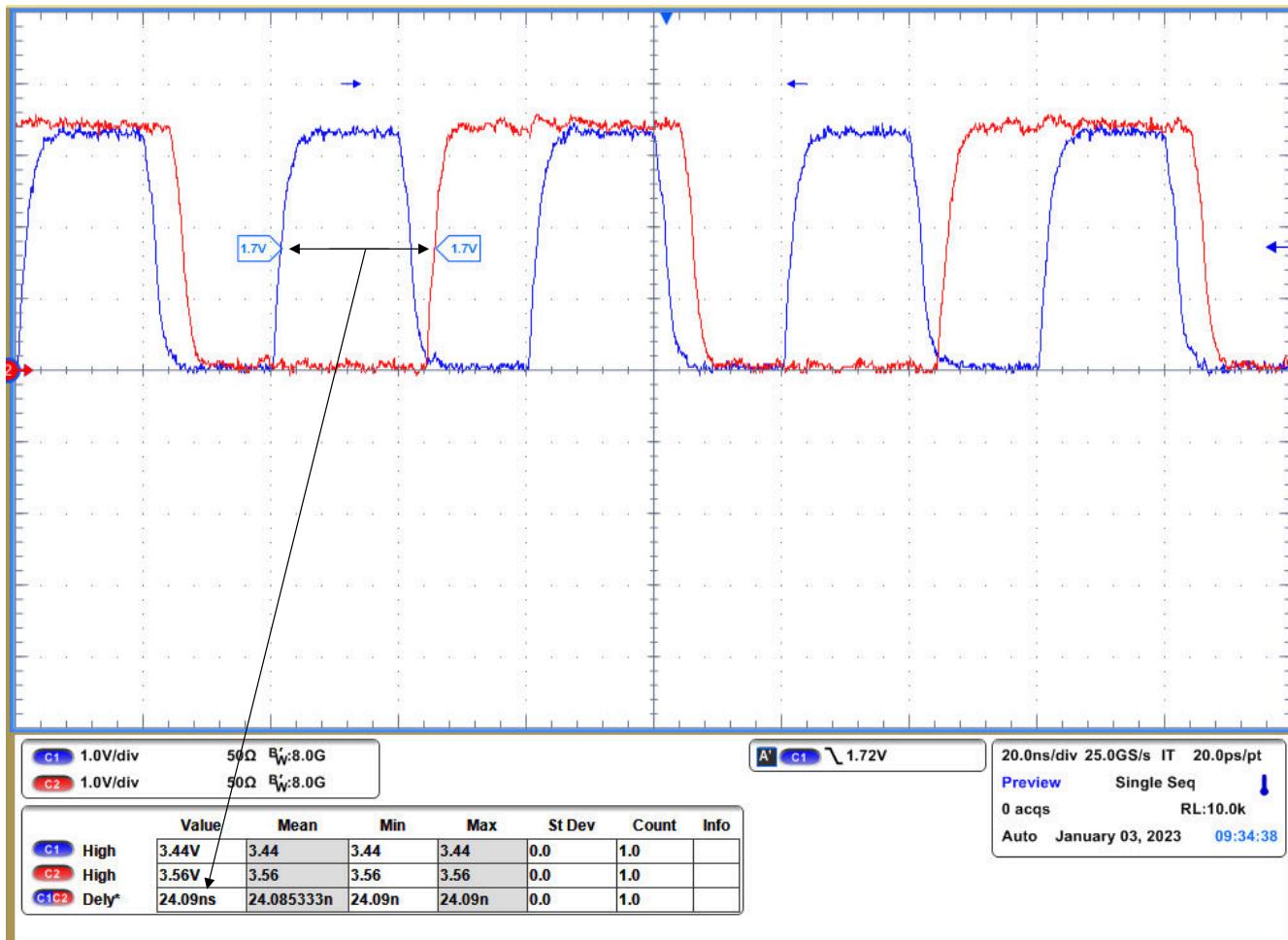

図 2-13. 100M RX\_CLK High 時間

図 2-14. RX\_CLK からの 100m RX\_D1 の遅延

#### 2.4.2 RGMII チェック

リデュースド ギガビット メディア インディペンデント インターフェイス (RGMII) は、4 ビット幅のデータインターフェイスで、PHY と MAC との間で最大 1000Mbps の通信をサポートします。RGMII モードは、OPMODE[2:0] ピンを Low にストラップするか、またはレジスタ 0x01DF[2:0] に「000」を書き込むことでイネーブルにできます。

RGMII 信号の概要は以下の通りです。

表 2-11. RGMII 信号

| 機能     | ピン        |

|--------|-----------|

| データ信号  | TX_D[3:0] |

|        | RX_D[3:0] |

| 信号の送受信 | TX_CTRL   |

|        | RX_CTRL   |

図 2-15. RGMII シグナリング

このセクションの波形を参照して、RGMII のシフト モードおよびアライン モードで予想される MAC データおよびクロック信号を確認してください。データおよびクロック信号をキャプチャするには、レシーバ エンドの近くで測定します。適切な遅延モードを選択する際の以下の要件に注意してください：

表 2-12. 適切な RGMII 遅延モードの選択

| MAC の構成が次の場合：        | 必要な PHY 構成           |

|----------------------|----------------------|

| TX 側の RGMII アライン モード | TX 側の RGMII シフト モード  |

| RX 側の RGMII アライン モード | RX 側の RGMII シフト モード  |

| TX 側の RGMII シフト モード  | TX 側の RGMII アライン モード |

| RX 側の RGMII シフト モード  | RX 側の RGMII アライン モード |

#### RX\_CLK と整列した RX\_D[3:0] データ

10/100Mbps の RX アライン モードに設定された PHY の場合、MAC 側でクロックおよびデータ信号をプローブし、以下に示すリファレンス波形と比較します。

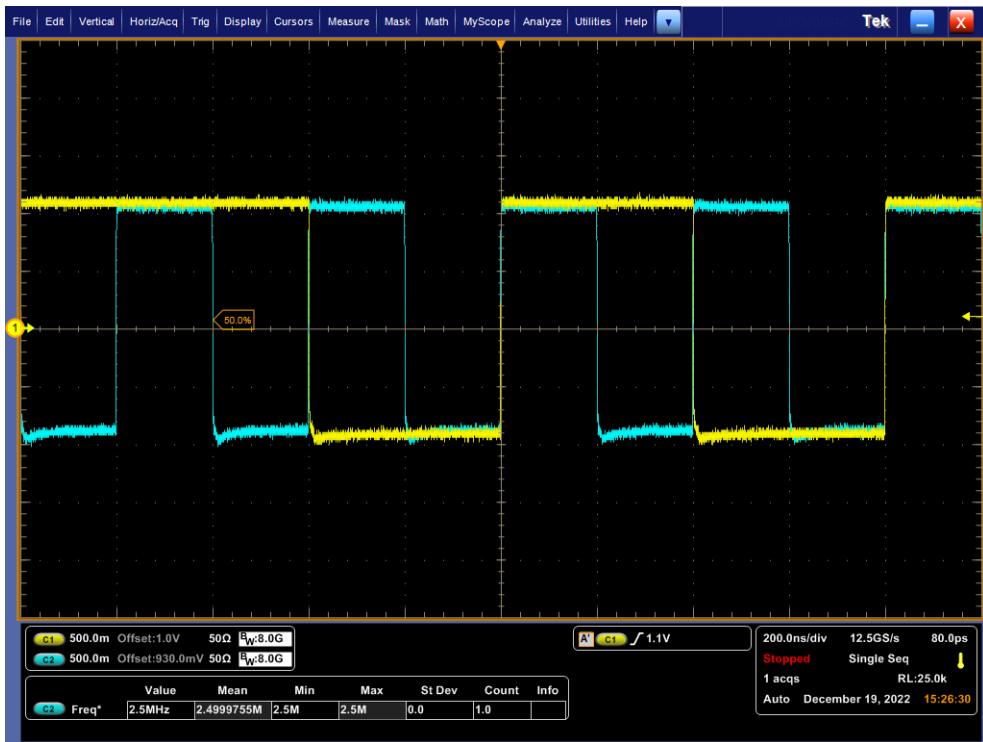

図 2-16. 10Mbps データおよび RX\_CLK の整列

クロック (C2) の周波数が 2.5MHz であること、およびデータ (C1) がクロックの立ち上がりエッジでサンプリングされることを確認します。

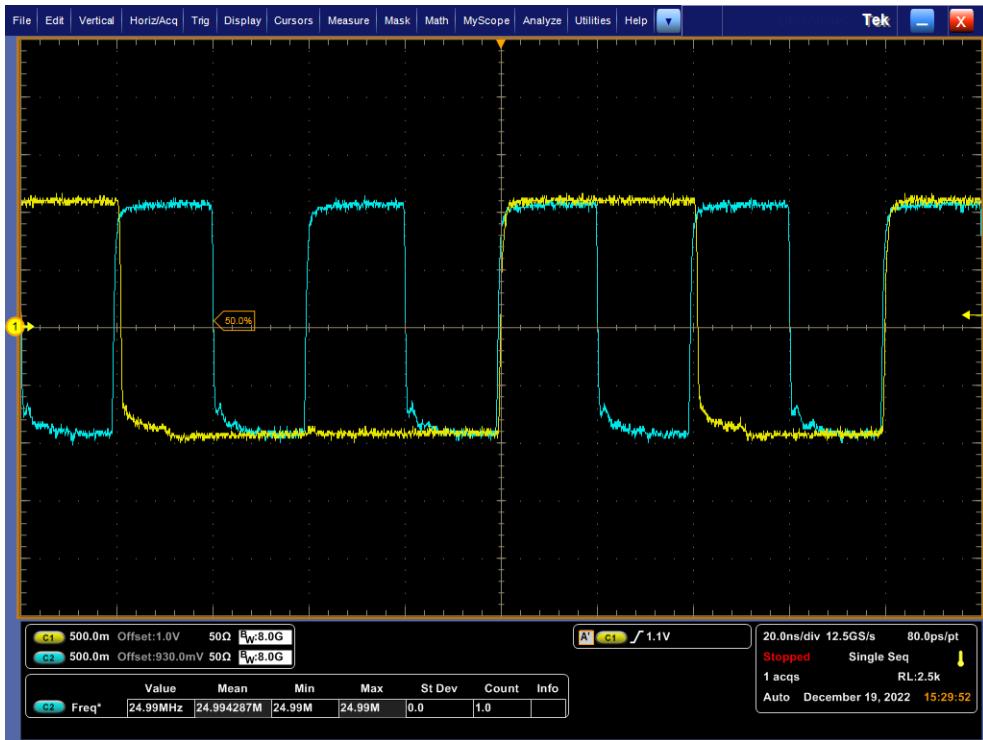

図 2-17. 100Mbps データおよび RX\_CLK の整列

クロック (C2) の周波数が 25MHz であること、およびデータ (C1) がクロックの立ち上がりエッジでサンプリングされることを確認します。

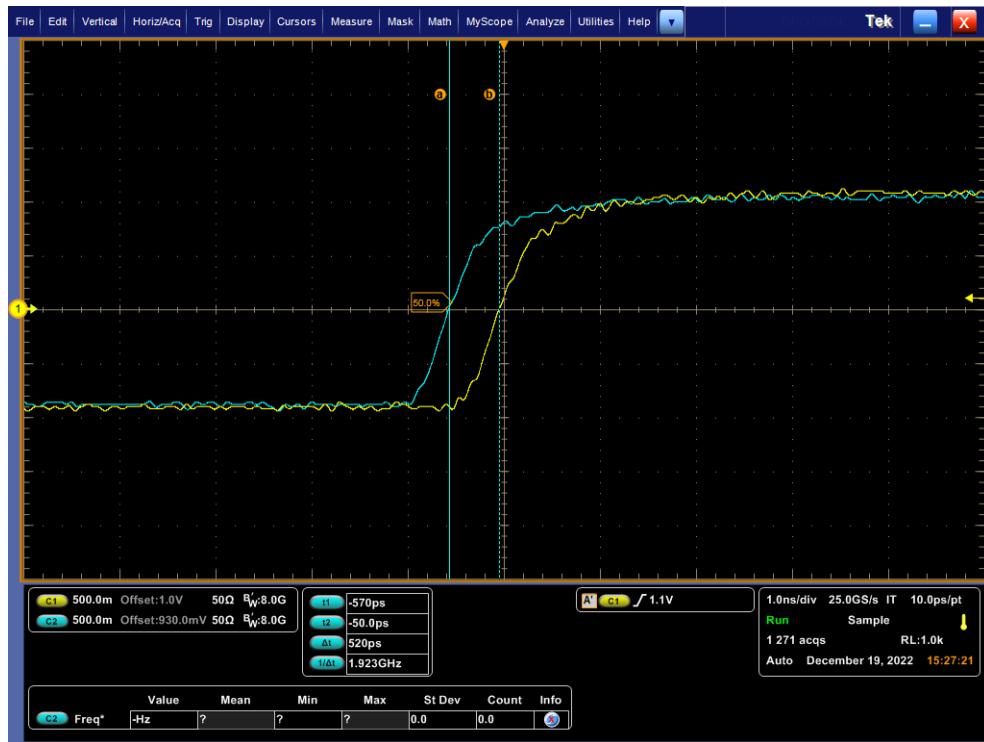

図 2-18. アライン モードでの 10Mbps データおよびクロック遅延

アライン モードで、クロックとデータ間の遅延が 500ps 未満であることを確認します。

#### シフト モードの RX\_D[3:0] データと RX\_CLK

10/100Mbps で RX シフト モード (0x32) に設定された PHY の場合、MAC 側のクロックおよびデータ信号をプローブして、以下のリファレンス波形と比較します。

図 2-19. シフト モードの 10Mbps データおよび RX\_CLK (プログラムされた遅延 4ns)

シフトモードで、クロックとデータ間の遅延が **1ns** を超えることを確認します。プログラムされた遅延は、アラインモードでのクロックの初期位置を基準としています。シフトモードの設定前後のクロック位置の差を測定すると、プログラムされた遅延に近い値が得られます。

### シフトおよびオンライン モードにおける TX\_D[3:0] と TX\_CLK

PHY を TX シフトまたはオンライン モードに設定して、PHY 側のデータおよびクロック信号をプローブし、以下のタイミング要件が満たされていることを確認します：

**表 2-13. RGMII タイミング**

| パラメータ                                                     | 最小値  | 公称値 | 最大値  | 単位 |

|-----------------------------------------------------------|------|-----|------|----|

| $T_{skewT}$<br>データからクロック出力へのスキー<br>(トランスマッタ時)             | -500 | 0   | 500  | ps |

| $T_{skewR}$<br>データからクロックへの入力スキュー<br>(レシーバ時)               | 1    | 1.8 | 2.6  | ns |

| $T_{setupT}$<br>データからクロック出力までのセットアップ<br>(トランスマッタ時 — 内部遅延) | 1.2  | 2   |      | ns |

| $T_{holdT}$<br>クロックからデータ出力までのホールド<br>(トランスマッタ時 — 内部遅延)    | 1.2  | 2   |      | ns |

| $T_{setupR}$<br>データからクロック入力へのセットアップ<br>(レシーバ時 — 内部遅延)     | 1    | 2   |      | ns |

| $T_{holdR}$<br>クロックからデータ入力ホールド<br>(レシーバ時 — 内部遅延)          | 1    | 2   |      | ns |

| $T_{cyc}$<br>クロック周期                                       | 7.2  | 8   | 8.8  | ns |

| Duty_G<br>ギガビットのデューティサイクル                                 | 45   | 50  | 55%  |    |

| Duty_T<br>10/100T のデューティサイクル                              | 40   | 50  | 60%  |    |

| $T_R$<br>立ち上がり時間 (20% ~ 80%)                              |      |     | 0.75 | ns |

| $T_F$<br>立ち下がり時間 (20% ~ 80%)                              |      |     | 0.75 | ns |

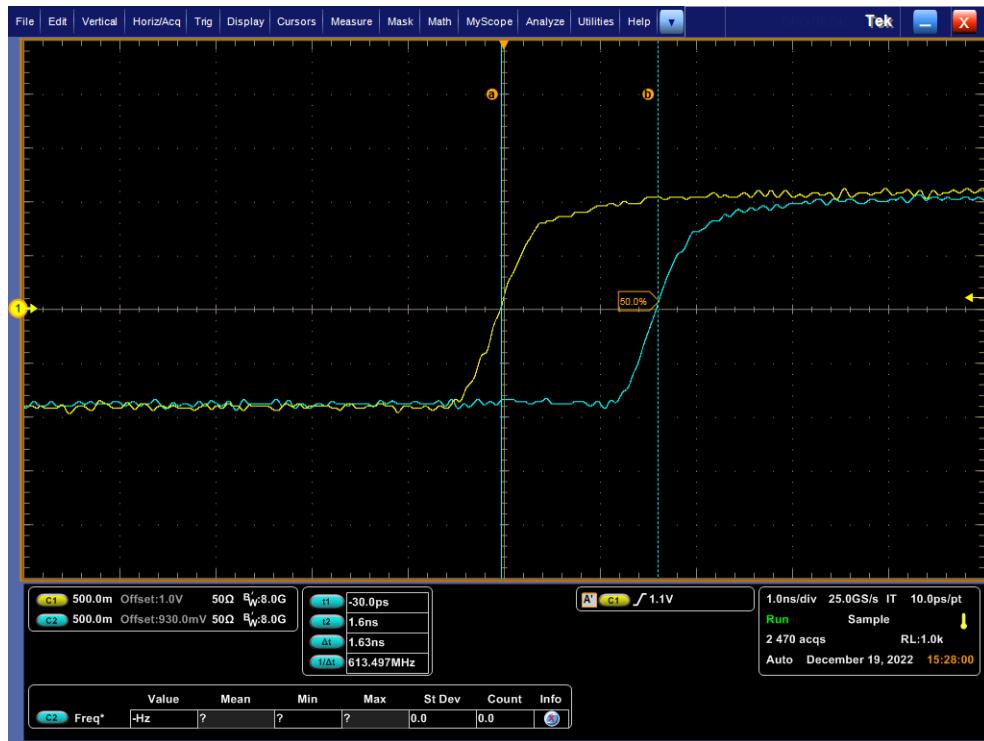

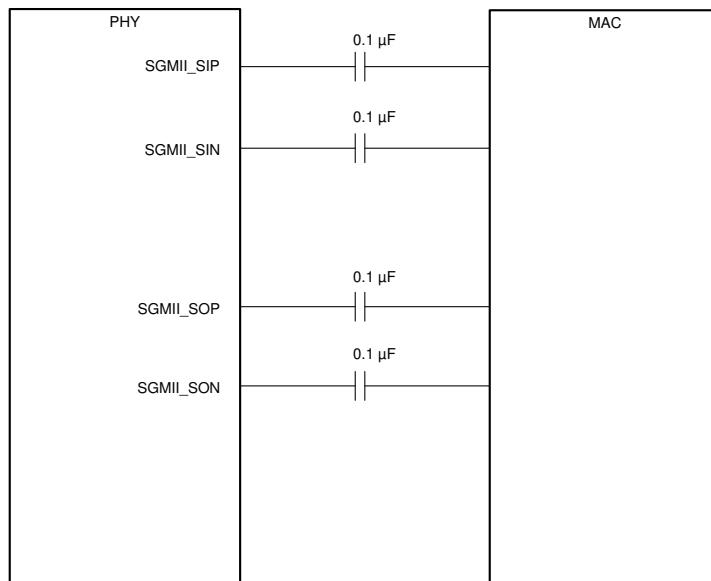

### 2.4.3 SGMII チェック

シリアル ギガビット メディア独立インターフェイス (SGMII) は、100M/1000M PHY と MAC の間で、GMII (24 ピン) または RGMII (12 ピン) に必要な信号ピン数よりも大幅に少ない信号ピン (4 ピンまたは 6 ピン) でネットワークデータとポート速度を伝送する手段を提供します。SGMII インターフェイスは 1.25Gbps の LVDS 差動信号を使用します。この信号は、GMII または RGMII と比較して EMI 放射を低減するという追加の利点があります。

SGMII インターフェイスには、オート ネゴシエーション機能があります。オート ネゴシエーションは、PHY と MAC の間で制御情報を交換するメカニズムを提供します。これにより、MDI 側のメディア速度モード解像度に基づいてインターフェイスを自動構成できます。SGMII オート ネゴシエーションは動作のデフォルト モードですが、レジスタ  $0x14[7]=0$  を書き込むことで無効化することもできます。

データシートに記載されている SGMII 出力仕様には、ピークツーピーク、SO\_P-SO\_N を指す出力差動電圧が記載されています。これは、SO\_P および SO\_N 信号がそれぞれ約  $\pm 0.55V$  であることを意味します。

**表 2-14. SGMII 出力仕様**

| SGMII 出力 |                      | 最小値  | 標準値  | 最大値  | 単位  |

|----------|----------------------|------|------|------|-----|

| 出力差動電圧   | SO_P および SO_N, AC 結合 | 0.95 | 1.00 | 1.05 | Vpp |

すべての SGMII 接続は、 $0.1\mu F$  コンデンサを介して AC 結合する必要があります。

**図 2-20. SGMII 4 ワイヤ接続**

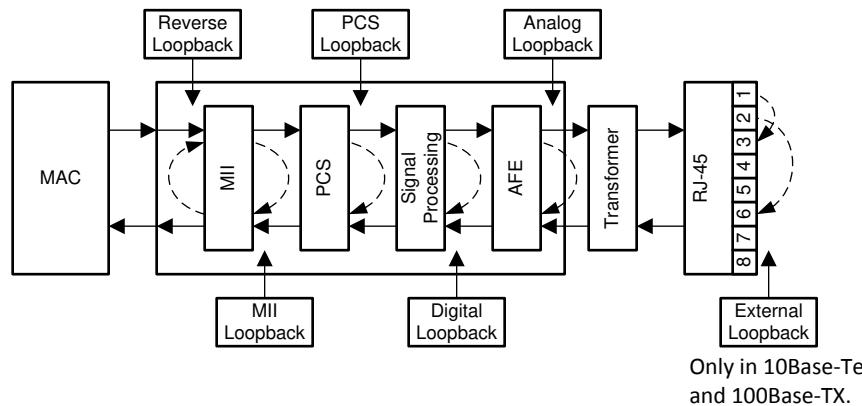

## 2.5 ループバックとPRBS

### 2.5.1 ループバックモード

PHY 内の各種機能ブロックをテストおよび検証するループバックの複数オプションがあります。ループバックモードを有効化すると、MII および MDI データパスのインサーキット テストが可能となります。DP83869 は、ニアエンド (MII) ループバックモードのいずれか、またはリバース (MDI) ループバックモードに構成できます。

図 2-21. ループバック

ループバックの可用性は、PHY の動作モードによって異なります。これらのループバックモードのリンクステータスも、動作モードの影響を受けます。表 2-15 に、ループバックが使用できない例外を示します。

表 2-15. ループバックの可用性の例外

| 動作モード            | ループバック | 例外                     |

|------------------|--------|------------------------|

| 銅                | PCS    | 10M                    |

| ファイバ             | MII    | 100M                   |

|                  | PCS    | 100M                   |

|                  | アナログ   | 100M、1000M             |

|                  | デジタル   | 10M、100M、1000M         |

| SGMII から RGMII へ | PCS    | 10M、100M、1000M         |

|                  | デジタル   | 10M、100M、1000M         |

|                  | アナログ   | 10M、100M、1000M         |

|                  | 外部     | 10M、100M、1000M         |

| RGMII から SGMII へ | PCS    | 10M、100M、1000M         |

|                  | 外部     | 10M、100M、1000M         |

| メディア コンバータ       | MII    | 100M、1000M             |

|                  | アナログ   | ファイバ インターフェイスで 100m    |

|                  | 外部     | ファイバ インターフェイスで 100m    |

|                  |        | 銅線インターフェイスで 100m、1000M |

MII ループバックは通常、MAC インターフェイスの検証に使用できますが、リバース ループバックは、リンク パートナーとともに使用して MDI 上のデータ パスを検証します。

- レジスタ 0x0000[14] を設定すると、MII ループバックがイネーブルになります

- 100Base-TX モードでは、レジスタ 0x0016[3] も設定します

- レジスタ 0x0016[5] を設定することでリバース ループバックがイネーブルになります

### 2.5.2 MAC とのパケットの送受信

MAC を使用してパケットを生成およびチェックできる場合、および PHY にリバース ループバック機能を備えた現用リンクパートナーがある場合は、次のように完全なデータパスを確認します。

1. PHY を MAC および動作しているリンク パートナーに接続します。

2. リンク パートナーでリバース ループバックをイネーブルにします。

3. MAC から PHY にテスト パケットを送信します。

4. MAC が同じテスト パケットを受信することを確認します。

MAC が送信された同じテスト パケットを問題なく受信した場合、MAC → PHY → MDI を経由するフル データ パスが有効です。このテストに合格しない場合は、MII ループバックを実行して、データ パスに沿って問題を切り分けます。

1. 電源を入れ、PHY を MAC に接続します。

2. PHY 上で MII ループバックをイネーブルにします。

3. MAC から PHY にテスト パケットを送信します。

4. MAC が同じテスト パケットを受信することを確認します。

MAC が同じテスト パケットを受信した場合、MAC → PHY データ パスが有効であり、問題は MDI データ パスに切り分けられています。このテストに合格しない場合、問題は MAC インターフェイス上にある可能性があります。MAC インターフェイスを確認するには、このアプリケーション ノートの [セクション 2.4](#) を参照します。PHY 内部データパスを検証するには、アナログループバックモードを使用して上記の手順を実行します。

### 2.5.3 BIST を使用してパケットを送受信しています

本デバイスは、内部 PRBS 内蔵セルフテスト (BIST) 回路を備えて、インサーキット テストまたは診断に適しています。BIST 回路を使用して、送信および受信データ パスの整合性をテストできます。BIST は、さまざまなループバック モードを使用して実行でき、データ パスの特定の部分に問題を切り分けることができます。BIST は、可変コンテンツと IPG を含むパケット化されたデータを生成します。

MAC でパケットを生成および確認できない場合は、PRBS パケット生成およびチェック機能を使用してデータ パスを確認します。PRBS および現用リンク パートナーでリバースループバックを実行するには、次の手順を実行します。

1. PHY に電源を供給し、リンク パートナーに接続します。

2. PHY で PRBS パケット生成をイネーブルします (Reg 0x0016 = 0xF000 を書き込みます)。

3. リンク パートナーでリバース ループバックをイネーブルにします (リンク パートナーが DP83869 の場合、Reg 0x0016 = 0x0020 を書き込みます)。

4. 少なくとも 1 秒待ってから、レジスタ 0x0017[11] を読み出して PHY の PRBS ロック ステータスを確認します。

レジスタ 0x0017[11] が high の場合、PHY → MDI を経由するデータ パスが有効です。このテストに合格しない場合は、PHY の内部データ パスまたは MDI に問題がある可能性があります。内部データ パスを確認するには、次の手順を使用して、アナログ ループバックで PRBS を実行します：

1. レジスタ 0x001F = 0x8000 を書き込みます // PHY リセット

2. レジスタ 0x0000 = 0x0140 を書き込みます // オート ネゴシエーションを無効化し、1000Mbps を強制します

3. レジスタ 0x0016 = 0x0008 を書き込みます // アナログループバックをイネーブルにし、100Ω の MDI 終端を使用します

4. レジスタ 0x0016 = 0xF008 を書き込みます // PRBS ジェネレータをイネーブルにします

5. レジスタ 0x0017[11] を読み出します // PRBS ロック時は High である必要があります

6. レジスタ 0x0072[7:0] を読み出します // エラーがない場合は 0x00 である必要があります

内部データ パスが有効である場合、問題は MDI またはリンク パートナーに切り分けられます。

### 3 動作モードの説明

データシートには十分な情報が記載されていますが、このセクションは、これらのモードの適切な使用方法と構成方法を理解するのに役立つ要約バージョンです。

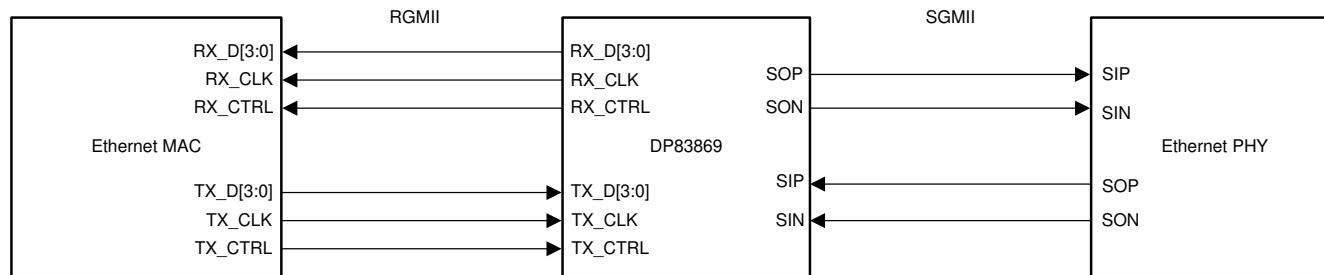

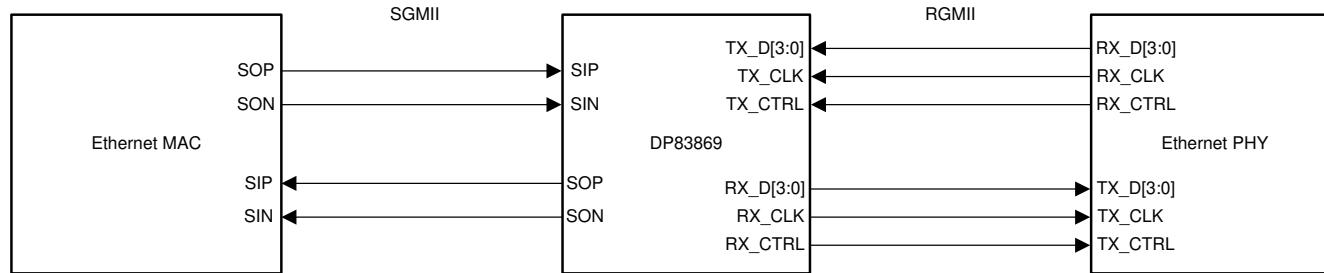

#### 3.1 ブリッジ モード

DP83869HM は、2 種類のブリッジモードをサポートしており、2 種類の MAC インターフェイスタイプ間でデータを変換できます。2 つのタイプを次に示します：

- RGMII-to-SGMII モード

- SGMII-to-RGMII モード

命名規則は MAC-to-PHY を意味し、DP83869HM の機能は選択したモードに応じて変化します。詳細については、[データシート](#)のブリッジモードセクションを参照します。

図 3-1. DP83869HM RGMII-to-SGMII ブリッジ

図 3-2. DP83869HM SGMII-to-RGMII ブリッジ

### 3.2 ファイバ構成

DP83869HM は、100Base-FX および 1000Base-X の光ファイバー通信に対応しています。ファイバーを使用している場合、速度はオートネゴシエーションによって決定されません。リンクの両側を同じ動作速度に設定する必要があります。ファイバに使用されるピンは、SGMII に使用されるピンと同じです：SIP/SIN および SOP/SON。DP83869HM は、SGMII から銅線、RGMII/MII からファイバ、または銅線からファイバのいずれかに設定する必要があります。SGMII とファイバの接続はできません。ファイバインターフェイスのデバッグの詳細については、[イーサネット PHY ファイバデバッグガイド](#)を参照してください。

#### 3.2.1 ファイバレジスタ

DP83869HM にはファイバー関連のレジスタが複数あります。このセクションでは、これらの機能のいくつかを要約し、デバッグ方法を示します。リンクステータスは常にレジスタ 0x01 でチェックできますが、レジスタ 0xC01 はファイバーリンクをチェックします。

表 3-1. レジスタ 0xC01 の動作

| モード           | レジスタ 0xC01 の動作                                                                                                                                                                                                                                                                                 |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RGMII からファイバへ | レジスタ 0x01 と同じ動作をします。レジスタ 0xC01 を読み出すことに伴う利点はありません                                                                                                                                                                                                                                              |

| メディアコンバータモード  | <p>ケース 1: 銅線リンクはダウンしていますが、ファイバリンクはアップしています<br/>レジスタ 0x01 はリンクがダウン（銅線側）であることを示しますが、レジスタ 0xC01 はリンクがアップ（ファイバ側）であることを示します。これは、どのケーブルに障害が発生したかをデバッグするのに役立ちます。</p> <p>ケース 2: 銅線リンクはアップですが、ファイバリンクはダウンしています<br/>レジスタ 0x01 は、リンクがダウンしていることを示します。レジスタ 0xC01 がリンクがダウンしていると表示されると、レジスタ 0x01 もダウンします。</p> |

表 3-1 のケース 2 では、どのリンクがダウンしているかを完全に信頼できません。ファイバ割り込みステータスレジスタ (0xC19) を使用して、フルトルの位置を分離できます。ケース 2 では、0xC19[9] (ファイバ遠端フルトル) および 0xC19[4] (リンクステータス変更) がフラグを立てます。ケース 1 では、0xC19[4] のみがフラグを立てるることができます。

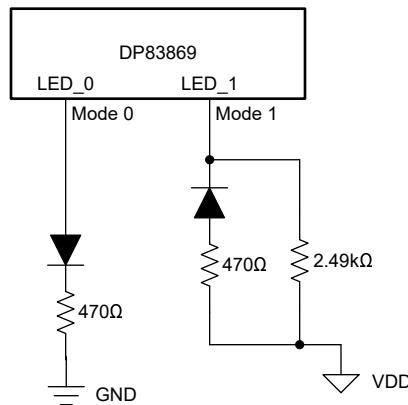

#### 3.2.2 メディアコンバータの LED 動作

DP83869 の LED は、レジスタ 0x0018 により構成できます。LED には 15 の動作モードがあり (0 ~ E)、DP83869 をメディアコンバータとして構成すると、リンクステータスを判定するために以下の LED モードを使用できます：

- モード 0: リンク Ok

- モード 1: RX/TX 動作

- モード 2: TX 動作

- モード 3: RX 動作

- モード 5: 1000Base-T/1000Base-X

- モード 7: 10BT リンク

- モード 8: 10/100BT リンク

- モード 9: 100/1000BT リンク

- モード B: Copper リンク + TX/RX 動作時に点滅

銅線リンクのステータスには、LED モード 0 を使用します。モード 7、8、9 では、銅線リンク速度を区別できます。ファイバリンクのステータスには、LED モード 5 を使用します。LED モード 5 は、1000Base-X と 100Base-X の両方のリンクステータスを追跡します。LED モード 6 を使用してメディアコンバータ動作時のファイバリンクステータスを追跡することはお勧めしません。TX/RX 動作には LED モード 1 を使用します。モード 2 と 3 では TX 動作と RX 動作を区別でき、モード B では LED が動作の時に点滅します。

## 4 ツールおよびリファレンス

次の章では、デバッグに関連するその他のツールと参考資料について説明します。

### 4.1 拡張レジスタ アクセス

DP83869HM の SMI 機能は、レジスタ REGCR (0x0D) および ADDAR (0x0E) を使用し、IEEE 802.3ah Draft の Clause 22 で定義された MDIO 管理可能デバイス (MMD) 間接方式によって Clause 45 の拡張レジスタセットにアクセスするための読み出しおよび書き込みアクセスをサポートしています。

標準のレジスタセット MDIO レジスタ 0～31 には、通常の直接 MDIO アクセスまたは間接方式でアクセスしますが、レジスタ REGCR (0x0D) および ADDAR (0x0E) は別で、通常の MDIO トランザクションでのみアクセスされます。SMI 関数は、これらのレジスタへの間接アクセスを無視します。

REGCR (0x0D) は MMD アクセス制御です。一般に、レジスタ REGCR[4:0] は、ADDAR (0x0E) レジスタのすべてのアクセスを適切な MMD に向けるデバイス アドレス DEVAD です。

PHY は 1 つの MMD デバイスアドレスをサポートします。ベンダ固有のデバイスアドレス DEVAD[4:0] = 11111 は、一般的な MMD レジスタアクセスに使用されます。

レジスタ REGCR および ADDAR によるすべてのアクセスでは、適切な DEVAD を使用する必要があります。その他の DEVAD を使ったトランザクションは無視されます。REGCR[15:14] はアクセス機能を保持します：アドレス (00)、ポストインクリメントなしのデータ (01)、読み出しおよび書き込み時ポスト インクリメントありのデータ (10)、書き込み時のポスト インクリメントありのデータ (11)。

**表 4-1. REGCR DEVAD 関数**

| REGCR[15:14] | 機能                                                                                                                                                   |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00           | レジスタ ADDAR へのアクセスにより、拡張レジスタの「セットアドレス」レジスタが変更されます。拡張レジスタ セット内のいずれのレジスタにアクセスするにも、このアドレス レジスタを必ず初期化する必要があります。                                           |

| 01           | レジスタ ADDAR にアクセスすると、アドレス レジスタの値によって選択された拡張レジスタ セット内のレジスタにアクセスします。                                                                                    |

| 10           | レジスタ ADDAR にアクセスすると、アドレス レジスタの値によって選択された拡張レジスタ セット内のレジスタにアクセスします。そのアクセスが完了した後、読み出しの場合も書き込みの場合も、アドレス レジスタの値がインクリメントされます。                              |

| 11           | レジスタ ADDAR にアクセスすると、アドレス レジスタの値によって選択された拡張レジスタ セット内のレジスタにアクセスします。このアクセスが完了した後、書き込みアクセスの場合のみ、アドレス レジスタの値がインクリメントされます。読み出しアクセスの場合、アドレス レジスタの値は変更されません。 |

以下のセクションでは、レジスタ REGCR および ADDAR を使って拡張レジスタ セットを操作する方法について説明します。これらの説明は、一般的な MMD レジスタ アクセス (DEVAD[4:0] = 11111) のデバイス アドレスを使用します。

#### 4.1.1 読み出し(ポスト インクリメントなし)動作

拡張レジスタ セットのレジスタを読み出すには、次の手順に従います。

| 手順                                                                       | 例:0x0170 を読み出します          |

|--------------------------------------------------------------------------|---------------------------|

| 1.レジスタ REGCR に値 0x001F (機能フィールド = 00 (アドレス)、DEVAD = '31') を書き込む。         | 値 0x001F にレジスタ 0x0D を書き込む |

| 2.レジスタ ADDAR に目的のレジスタ アドレスを書き込む。                                         | 値 0x0170 にレジスタ 0x0E を書き込む |

| 3.レジスタ REGCR に値 0x401F (データ、ポスト インクリメントなし機能フィールド = 01、DEVAD = 31) を書き込む。 | 値 0x401F にレジスタ 0x0D を書き込む |

| 4.レジスタ ADDAR に目的の拡張レジスタ セットレジスタの内容を読みだす。                                 | レジスタ 0x0E を読み出す           |

それ以降、レジスタ ADDAR (ステップ 4) から読み出すと、アドレス レジスタの値によって選択されたレジスタが引き続き読み出されます。

**注**

アドレス レジスタが前もって設定されている場合、ステップ (1) および (2) を飛ばすことができます。

#### 4.1.2 書き込み(ポスト インクリメントなし)動作

拡張レジスタ セット内のレジスタを書き込むには、次の手順に従います。

| 手順                                                                       | 例:レジスタ 0x0170 = 0C50 に設定する |

|--------------------------------------------------------------------------|----------------------------|

| 1.レジスタ REGCR (0x0D) に値 0x001F (アドレス機能フィールド = 00、DEVAD = 31) を書き込む。       | 値 0x001F にレジスタ 0x0D を書き込む  |

| 2.レジスタ ADDAR (0x0E) に目的のレジスタ アドレスを書き込む。                                  | 値 0x0170 にレジスタ 0x0E を書き込む  |

| 3.レジスタ REGCR に値 0x401F (データ、ポスト インクリメントなし機能フィールド = 01、DEVAD = 31) を書き込む。 | 値 0x401F にレジスタ 0x0D を書き込む  |

| 4.レジスタ ADDAR に目的の拡張レジスタ セットレジスタの内容を書き込む。                                 | 値 0x0C50 にレジスタ 0x0E を書き込む  |

それ以降、レジスタ ADDAR (ステップ 4) に書き込むと、そのアドレス レジスタの値によって選択されたレジスタが引き続き書き換えられます。

**注**

アドレス レジスタが前もって設定されている場合、ステップ (1) および (2) を飛ばすことができます。

## 4.2 Linux でのソフトウェアおよびドライバ デバッグ

Linux システムで PHY が機能するために必要な 2 つの重要なコンポーネントは、デバイスツリーとドライバファイルであり、DP83869HM ドライバは[こちら](#)で入手できます。以下に、デバイスツリーの例を示します。これは、`root/Documentation/devicetree/bindings/net/ti` のパスの下にあるすべてのオープンソースカーネルで見つけることができます。

```

#include <dt-bindings/net/ti-dp83869.h>

mdio0 {

#address-cells = <1>;

#size-cells = <0>;

ethphy0: ethernet-phy@0 {

reg = <0>;

tx-fifo-depth = <DP83869_PHYCR_FIFO_DEPTH_4_B_NIB>;

rx-fifo-depth = <DP83869_PHYCR_FIFO_DEPTH_4_B_NIB>;

ti,op-mode = <DP83869_RGMII_COPPER_ETHERNET>;

ti,max-output-impedance;

ti,clk-output-se1 = <DP83869_CLK_O_SEL_CHN_A_RCLK>;

rx-internal-delay-ps = <2000>;

tx-internal-delay-ps = <2000>;

};

};

```

### 4.2.1 共通端子出力

次のセクションでは、ドライバに関連する問題のデバッグに使用できる一般的なターミナルコマンドを提供します。

```

$ dmesg | grep "mdio"

```

出力の 1 つは次のとおりです:

```

$ mdio_bus xxx.ethernet-x: MDIO device at address 8 is missing

```

このメッセージは、MDIO バス上で PHY が見つからないことを示します。これはいくつかの問題が原因で発生する可能性があります。最も一般的なものは、デバイスツリーの欠落または不正ですが、機能しない PHY または SMI 接続の不良が原因である可能性もあります。

MDIO バスで PHY を検出できると、次のような一般的なエラーメッセージがあります:

```

$ Generic PHY xxx.ethernet-x: attached PHY driver [Generic PHY]

```

このメッセージは、対応する PHY のドライバファイルが正しくロードされていないか、まったく存在していないことを示し、Linux が汎用ドライバをロードしましたが、おそらく PHY では動作しません。その場合は、ドライバが正常にコンパイルされ、Linux のビルド時に追加され、ドライバが使用されている PHY のモデルと一致することを確認します。

最後に、次のようなメッセージが表示されます:

```

am65-cpsw-nuss 8000000.ethernet eth1: PHY [mdio_mux-0.1:03] driver [TI DP83869] (irq= POLL)

```

このメッセージは、PHY に正しいドライバがロードされ、正常に検出されたことを示します。*ifconfig* を実行して、ネットワークインターフェイスが存在することを確認します。PHY がネットワークアダプタとして正常に認識された場合の *ifconfig* 出力の例:

```

root@am64xx-evm:~# ifconfig

eth0: flags=4099<UP,BROADCAST,MULTICAST> mtu 1500

ether 34:08:e1:80:b5:f8 txqueuelen 1000 (Ethernet)

RX packets 0 bytes 0 (0.0 B)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 0 bytes 0 (0.0 B)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

eth1: flags=4099<UP,BROADCAST,MULTICAST> mtu 1500

ether 70:ff:76:1e:9e:a6 txqueuelen 1000 (Ethernet)

RX packets 0 bytes 0 (0.0 B)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 0 bytes 0 (0.0 B)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

lo: flags=73<UP,LOOPBACK,RUNNING> mtu 65536

inet 127.0.0.1 netmask 255.0.0.0

loop txqueuelen 1000 (Local Loopback)

RX packets 90 bytes 6824 (6.6 KiB)

RX errors 0 dropped 0 overruns 0 frame 0

TX packets 90 bytes 6824 (6.6 KiB)

TX errors 0 dropped 0 overruns 0 carrier 0 collisions 0

```

## 5 まとめ

このアプリケーションノートでは、新しいアプリケーションを評価し、予想される機能を確認するための推奨フローを紹介します。ステップバイステップの推奨事項を活用すると、DP83869HM を使用した設計のボード立ち上げと初期評価を容易に実施できます。

## 6 参考資料

- テキサス インスツルメンツ、[DP83869HM](#)、製品ページ。

- テキサス インスツルメンツ、[DP83869HM 銅線および光ファイバー インターフェイス対応の高耐性 10/100/1000 イーサネット物理レイヤトランシーバ](#)、データシート。

- テキサス インスツルメンツ、[DP83869HM のさまざまな動作を理解する](#)、アプリケーションノート。

## 7 改訂履歴

| Changes from Revision * (December 2023) to Revision A (October 2025) | Page |

|----------------------------------------------------------------------|------|

| ドキュメント全体にわたって表、図、相互参照の採番方法を更新.....                                   | 1    |

| コンテンツを PHY およびインターフェイスの健全性チェックセクションに再フォーマットしました.....                 | 4    |

| 回路図とレイアウト チェックリストへの参照を追加しました.....                                    | 4    |

| LED ストラップ回路の図を追加しました.....                                            | 8    |

| USB2MDIO の説明セクションを、「レジスタ値の読み取りとチェック」セクションに移動.....                    | 10   |

| MSE レジスタを追加しました.....                                                 | 13   |

| 短いケーブルスクリプトを追加しました.....                                              | 13   |

| AGC ゲインスクリプトを追加しました.....                                             | 14   |

| メディア コンバータ モードでの LED の動作を追加しました.....                                 | 28   |

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](#) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月