## Application Note

## スマート RGB LED 制御用 TPLD デバイス

Gerardo Leyva-Hernandez

## 概要

TPLD2001 は、車載、コンシューマエレクトロニクス、パーソナルエレクトロニクス向けのシーンライティングにおいて、一般的にスマート 24 ビット RGB LED で使用される、時間ベースのロジックでの標準的なロジック値の生成と変換に利用できます。さらに、標準的な I2C または SPI 通信を使用して RGB LED の色を更新するために、TPLD の内部シリアル通信要素を活用できます。1670 万色の RGB LED ソフトウェアレス アプリケーションが、単一のデバイス設計として示されています。

## 目次

|                                 |   |

|---------------------------------|---|

| 1 はじめに.....                     | 2 |

| 2 スマート LED のデータおよびタイミングの理論..... | 2 |

| 3 ロジックシンボルの生成.....              | 3 |

| 4 TPLD ベースのスマート LED コントローラ..... | 4 |

| 5 TPLD シリアル通信.....              | 6 |

| 6 まとめ.....                      | 7 |

| 7 参考資料.....                     | 7 |

## 商標

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

このアプリケーションノートでは、TPLD2001 による時間ベースロジックでの標準ロジック値の生成と変換の方法と、標準 I2C または SPI 通信を使用してスマート RGB LED の色を更新するための TPLD 素子の活用方法を説明します。このようにして、TPLD は、RGB ベースのディスプレイ、視覚信号、またはライティングを最新状態に維持するためのメインコントローラの負荷を最小限に抑えるのに役立ちます。

このアプリケーションノートは、スマート 24 ビット RGB LED を制御するための単一 TPLD デバイス内ソフトウェアレスアプリケーションの設計を提示しています。さらに、このドキュメントでは、複数のタイマ、DFF、FSM、その他の素子を使用して変換を行う方法を示します。

最後に、RGB LED の色を更新するためのシリアル通信モジュールの使用について述べます。

## 2 スマート LED のデータおよびタイミングの理論

スマート LED は、リセット期間後に DIN ピンに存在する 24 ビットカラー フォーマットを待機します。通信はシリアル、ユニポーラ、RZ 通信モードです。図 2-1 に示すように、データの順序は最上位ビットが先頭となる GRB です。

|    |    |    |    |    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|----|----|----|----|

| G7 | G6 | G5 | G4 | G3 | G2 | G1 | G0 | R7 | R6 | R5 | R4 |

| R3 | R2 | R1 | R0 | B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 |

図 2-1. Smart 24 ビット GRB LED のデータ転送順序

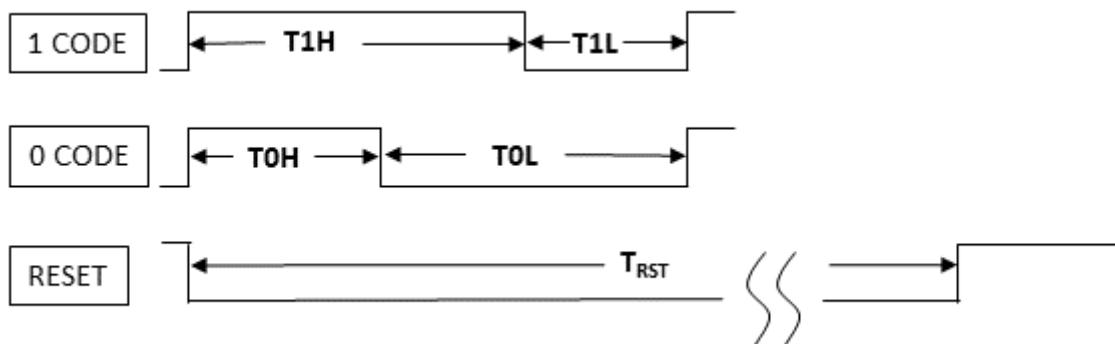

各カラービットのタイミングに関しては、データ信号は High レベルから開始し、パルスの間にゼロに戻ることが期待されます。各カラービットの High 状態の期間により、通常 1200nS 程度にわたる全周期において論理 0 または論理 1 の値が決まります。表 2-1 および図 2-2 に、市場に出ているいくつかのスマート LED モデルについてデータ転送時間を示します。200uS を超える期間は、リセットコードとされます。

表 2-1. データ転送のタイミング

| 名称   | コード周期                   | 最小値   | 精度       |

|------|-------------------------|-------|----------|

| T0H  | ロジック High に対する 0 コードの時間 | 350nS | +/-150nS |

| T0L  | ロジック Low に対する 0 コードの時間  | 800nS | +/-150nS |

| T1H  | ロジック High に対する 1 コードの時間 | 700nS | +/-150nS |

| T1L  | ロジック Low に対する 1 コードの時間  | 600nS | +/-150nS |

| Trst | リセットのロジック Low           | 200uS |          |

図 2-2. 論理記号のタイミング

### 3 ロジックシンボルの生成

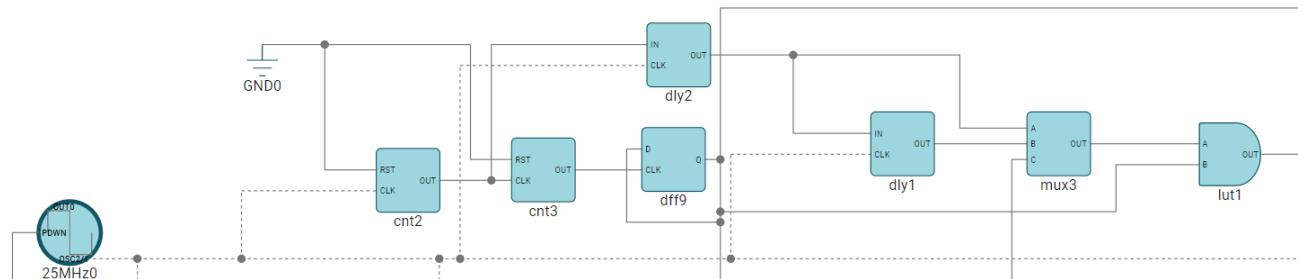

内部の 25MHz OSC は、内部のプリデバイダ OSC/2 によって生成される 12.5MHz を含む必要なすべてのクロック信号を生成します。これをカウンタと組み合わせることで、RGB LED が必要とする 800KHz の時間基準を生成できます。

クロック信号は設計上対称ではないため、TPLD の内部遅延を適切に設定することで、T0H および T1H をそれぞれ 350nS および 800nS で生成できます。必要なシンボル周期が実際に生成されるので、T0L および T1L のタイミングを制御する必要はありません。図 3-1 に、時間基準とロジックシンボルの生成に必要な素子を示します。

図 3-1. TPLD を使用したロジックシンボルの生成

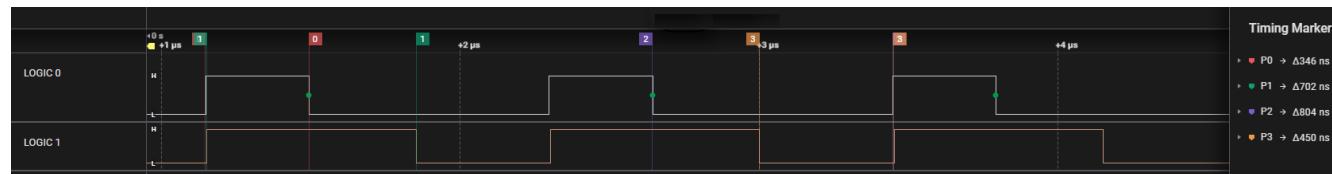

図 3-2 に、ロジックシンボルのタイミングをすべて生成する TPLD デバイスのロジックアナライザ上のスクリーンキャプチャを示します。ロジックマルチプレクサは、両方のシンボルを入力とし、生成する色に応じて他の回路セクションが生成する選択信号を使用します。

図 3-2. ロジック High および Low シンボルのスクリーンショット

## 4 TPLD ベースのスマート LED コントローラ

### TPLD 内の RGB ビットの制御

前述のように特定の RGB カラーを生成するには、RGB LED は 24 ビットを連続して受信する必要があります。さらに、これらの 24 ビットは TPLD 内に内部的に維持され、シリアル通信モジュールを使用して更新できる必要があります。RGB 情報を処理するために内蔵の有限ステートマシン (ASM) が選択されたのは、それぞれ 8 ビット出力を持つ最大 8 つの状態 (合計 64 ビット) を生成でき、各状態値をユーザーが変更可能であり、そのすべてがタスクの実行に十分以上であるためです。

表 4-1 に、ステートマシン出力セクションの GRB コード 0xFF000 を示します。6 つの状態は、OUT3 から OUT0 への 4 ビットを使用して定義されます。RGB ピクセルに対して生成された実際の出力は緑に対応する図 5 に示されています。

表 4-1. ユーザーによって定義された状態と値の ASM レポート

| 状態   | OUT7 | OUT6 | OUT5 | OUT4 | OUT3 | OUT2 | OUT1 | OUT0 |

|------|------|------|------|------|------|------|------|------|

| ST0  | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1    |

| ST1  | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1    |

| ST2  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| ST3  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| ST4  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| ST5  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| ST6  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| ST70 | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

図 4-1. RGB LED の緑色の値 0xFF000 を表す 24 ビット

### パラレル・シリアル・シフトレジスタ

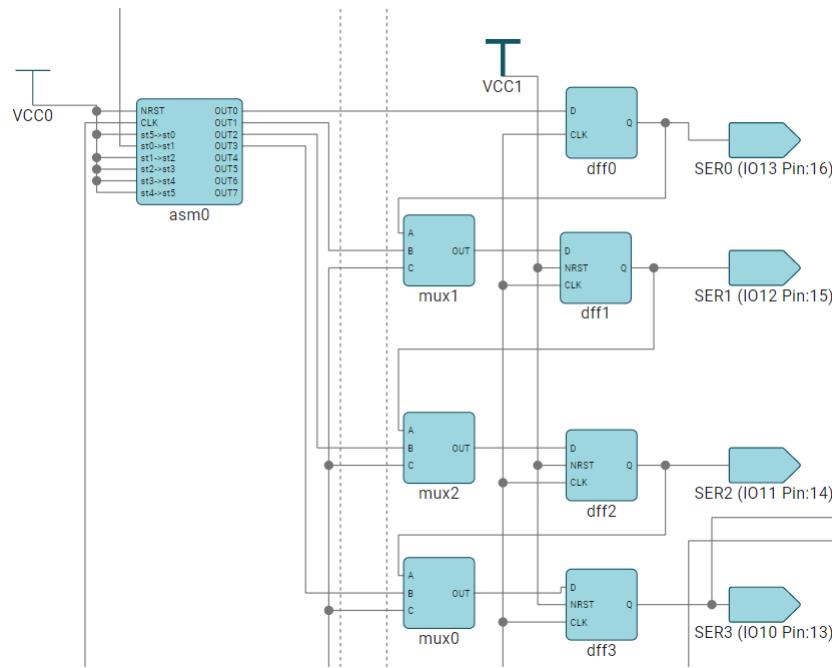

このデバイスセクションは、図 4-2 に示すように、ほとんどの従来型の機能としてデータをシリアル出力 (SER3) にシフトする 4 ビットのパラレル ロード シフトレジスタとして設計されています。データは FSM の出力によって生成され、シフトレジスタにロードされます。最後に、SER3 出力を使用して、RGB LED の 1 ビットであるロジック マルチプレクサを介してロジック値を選択します。

図 4-2. FSM および 4 ビットシフトレジスタ

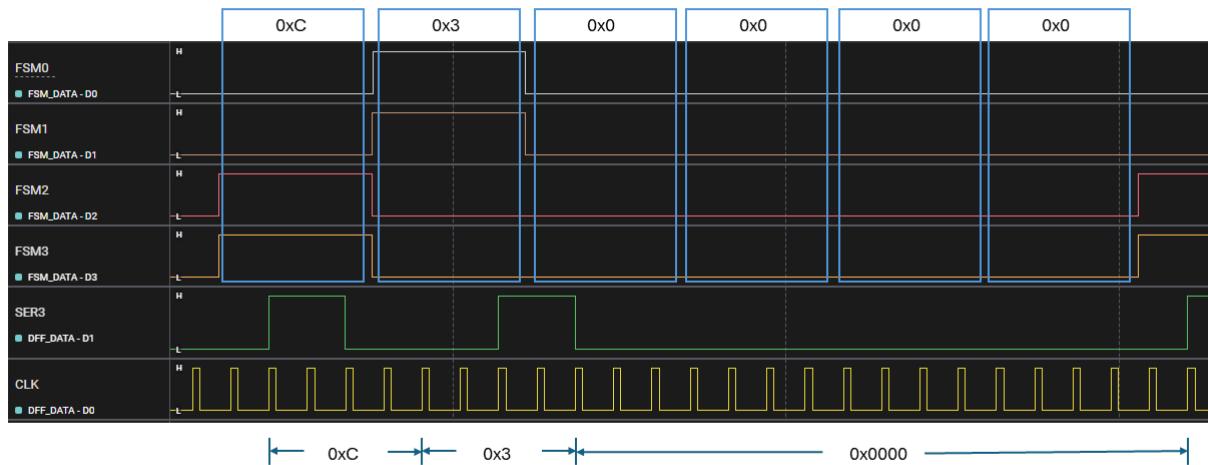

ステートマシンと 4 ビットシフトレジスタの動作を、図 4-3 に示します。16 進数 0xC30000 で表される特定の色に対して、FSM はマシンの各クロックイベントに 4 ビットの番号を生成します。同時に、シフトレジスタは FSM によって生成された新しいデータを内部的にロードし、指定された色を表す 24 ビットのシリアル番号を生成します。シフトレジスタの速度は、FSM の速度の 4 倍です。

図 4-3. FSM および 4 ビットシフトレジスタの動作

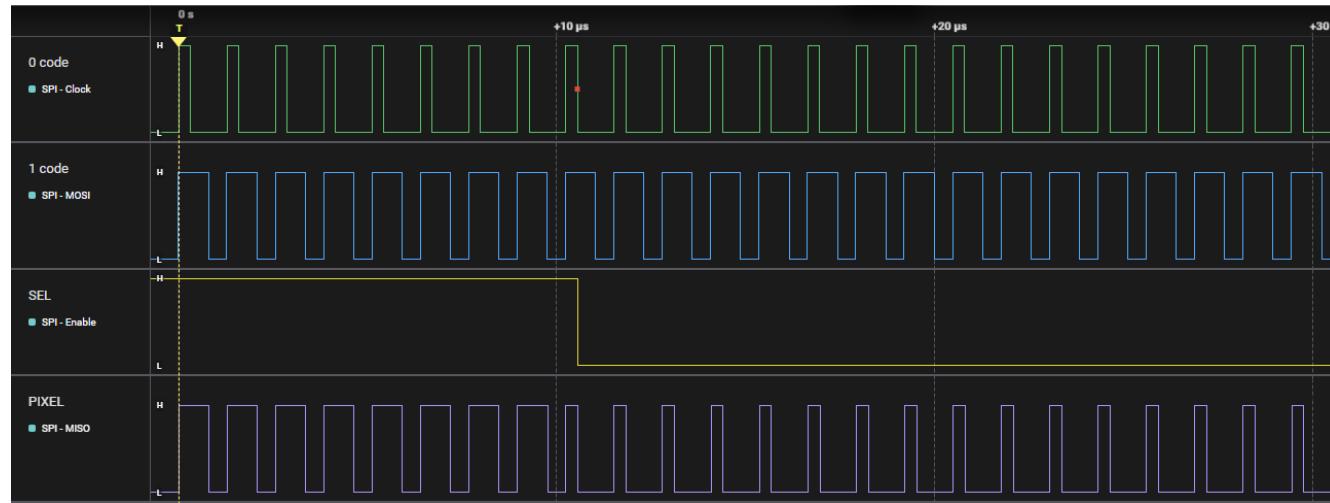

## 5 TPLD シリアル通信

TPLD2001 は、ASM を含むユーザー レジスタ空間の読み書きが可能な I2C シリアル通信モジュールを備えています。ASM へのアクセスは、設計内にシリアル通信素子を配置し、TPLD との通信に使用される I2C ペリフェラル アドレスを設定するだけで構成される、簡単な手順です。内部の電気接続または追加の構成について、それ以外の作業は必要ありません。ASM の内部アドレスは 0x50 ~ 0x58 であり、FSM に関する追加の詳細はすべて、TPLD2001 のデータシートに記載されています。FSM レジスタの値を変更して RGB LED の色を変化させることが可能であり、1670 万色のすべての色を生成できます。

図 5-1 に、I2C モジュールと使用可能なパラメータを示します。この例では、I2C アドレスは 0x7 に設定されています。

### I2C RECEIVER ②

This block is not simulatable

|                                     |                                            |

|-------------------------------------|--------------------------------------------|

| Name                                | i2c0                                       |

| Label                               | ADDR 0x7                                   |

| Peripheral Address                  | 0111                                       |

| Use GPIO Instead of Bits in Address | Use GPIO input rather than bits in address |

| Global Reset Listening              | <input type="checkbox"/>                   |

| Use Virtual Inputs                  | Selected virtual inputs will be used       |

| Device MacroCell Allocated          | SER_COMM                                   |

図 5-1. I2C モジュールとパラメータ

## 6 まとめ

TPLD2001 は、スマート RGB LED で一般的に使用される時間ベースのロジックにおいて、標準ロジック値の生成や変換を支援します。内蔵発振器、D 型フリップフロップ、カウンタ、遅延回路、汎用 I/O、同期型有限ステートマシンなど複数の素子を使用することで、TPLD は、ゼロコストの非反復エンジニアリングで、複雑な設計を单一チップ上に統合することを可能にします。さらに、標準の I2C または SPI 通信を使用して、内部 TPLD 素子の値を更新できます。最後に、設計の例として、单一のデバイス設計におけるソフトウェアレス アプリケーションを示します。

## 7 参考資料

- テキサス・インスツルメンツ、[TPLD](#)、製品ページ。

- テキサス・インスツルメンツ、『[TPLD2001 18 GPIO 搭載、I2C/SPI 選択可能、プログラマブル ロジック デバイス](#)』、データシート。

- テキサス・インスツルメンツ、『[TPLD 内でのシリアル通信の使用](#)』、アプリケーション プリーフ。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月