*Application Note***PSpice-for-TI を使用して、自動 SPICE 設計を作成**

Carolina Walter

**概要**

テキサス インスツルメンツでは、アナログ回路の機能評価に役立つ 2 つの SPICE シミュレーションツール、TINA-TI と PSPICE-FOR-TI を提供しています。TINA-TI は、回路図を迅速に組み立て、回路の応答を解析できる、機敏なプログラムです。PSpice®-for-TI は、エコシステムがすべてのポストプロセッサ設定（複数の複雑なパターンと方程式）を記憶するため、大規模な回路解析向けに設計されています。

このドキュメントは、新規ユーザー向けの情報を提供します。この概要で説明するすべての用語は、後ほど定義します。

シミュレーション問題の手順が確立されると、PSpice-for-TI® は一度セットアップするだけで済みます。回路、シミュレーションプロファイル、プロットとトレースの出力ウィンドウの設定、および主要な測定値は、プロジェクトに保存されます。プロジェクトを再利用すればするほど、初期投資は大きな成果をもたらします。

このアプリケーションノートでは、オペアンプの安定性を評価するための自動 SPICE 設計の作成について説明します。このプロセスは、SPICE に依存し、繰り返し回路解析を必要とするあらゆる評価に再現できます。

**目次**

|                                 |           |

|---------------------------------|-----------|

| <b>1はじめに</b> .....              | <b>2</b>  |

| <b>2再利用可能な回路図</b> .....         | <b>3</b>  |

| <b>3プロジェクトの作成</b> .....         | <b>4</b>  |

| 3.1 プロジェクト階層.....               | 5         |

| <b>4読みやすさを高めた概略図</b> .....      | <b>6</b>  |

| 4.1 受動部品の配置.....                | 6         |

| 4.2 パラメータ.....                  | 8         |

| 4.3 電源装置を設置.....                | 12        |

| 4.4 配線.....                     | 13        |

| 4.5 ユーザーエクスペリエンスを考慮した編成.....    | 14        |

| <b>5シミュレーションプロファイルの設定</b> ..... | <b>16</b> |

| 5.1 収束を支援.....                  | 17        |

| 5.2 強力な後処理.....                 | 19        |

| <b>6まとめ</b> .....               | <b>27</b> |

| <b>7参考資料</b> .....              | <b>29</b> |

**商標**

PSpice®, PSpice-for-TI®, Pspice®, and Pspice-for-TI® are registered trademarks of CADENCE DESIGN SYSTEMS, INC..

is a registered trademark of CADENCE DESIGN SYSTEMS, INC.

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

オペアンプの2つの入力ノードは互いに等しくなければならず、それに応じて出力が変化します。出力応答と反転帰還ノード(IN-)の間に遅延(または位相遅れ)をもたらす部品がある場合、出力は正しい値に落ち着こうと繰り返し試みる不安定な振動応答を示します。

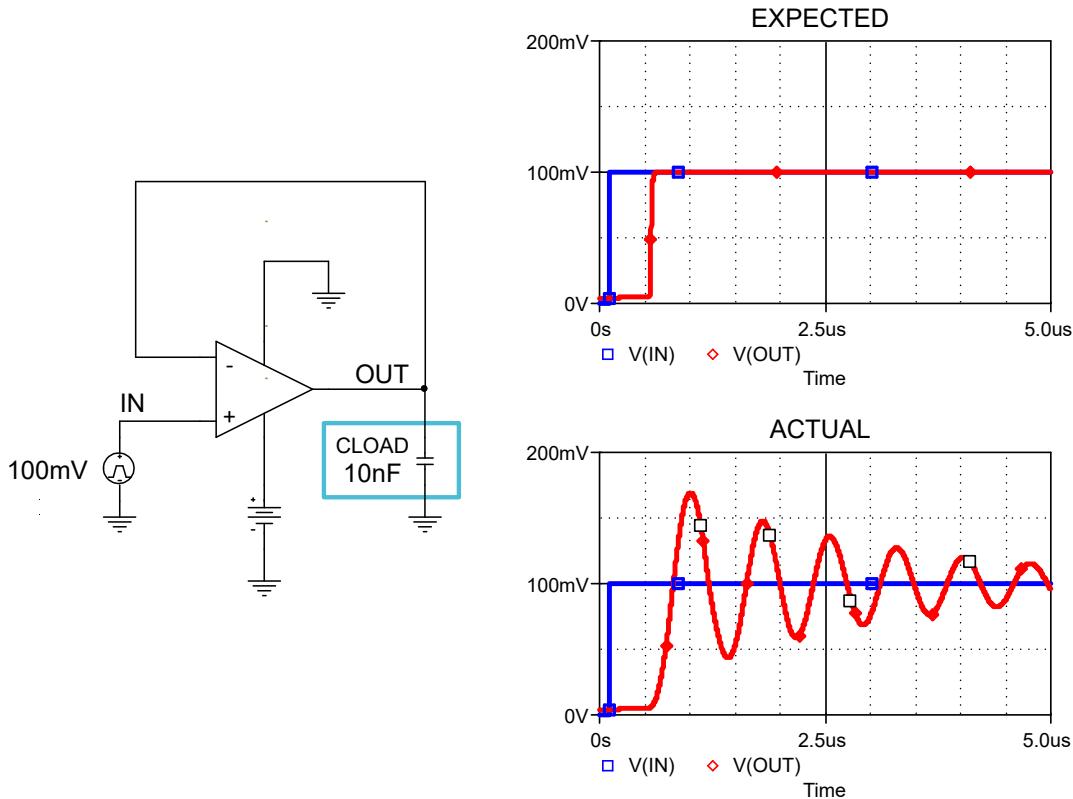

図1-1では、予想される応答は100mVですが、オペアンプの出力は最初にオーバーシュートし、その後オーバー/アンダー補正を行い、結果として出力が振動します。

図1-1. 不安定なオペアンプ回路の応答

帰還ネットワークで位相遅れが生じる一般的な原因としては、オペアンプの出力インピーダンスと容量性負荷、またはオペアンプの入力容量と大きな帰還抵抗などが挙げられます。図1-1に、大きな容量性負荷が不安定性を引き起こす例を示しています。安定性補償理論の詳細については、TIのPrecision Labsトレーニングを [TIPL 安定性ビデオシリーズ](#)をご覧ください。

安定性補償部品は、安定した出力応答(位相マージン $45^\circ \sim 90^\circ$ )を実現するために回路に導入されます。適切な安定性補償値を見つけるには、オペアンプと回路構成ごとに以下の手順を実行する必要があります。

1. 疑似開ループ構成でシミュレーション回路図を作成します。

2. ACスイープを実行します。

3. 回路の開ループゲインと位相をプロットし、位相マージンを測定します。

4. 周波数応答のパラメータを使用して、補償値を計算します。

5. 補償値を実装し、ACスイープを再実行して、目的の位相マージン( $45^\circ \sim 90^\circ$ )が達成されているかどうかを確認します。

この手順では、大量の後処理計算とACスイープの再実行が必要です。PSpice®-for-TIでは、出力ウィンドウプロットの設定、位相マージンなどの主要な測定値、周波数応答と回路図のパラメータを使用して補償値を決定するための式を記憶することで、この手順を簡素化します。このドキュメントでは、PSpice®-for-TIに組み込まれた自動設計を使用して、この再現性のある問題を解決する方法を示します。

## 2 再利用可能な回路図

繰り返し可能な手順が特定されたら、次のステップは、ほとんどの回路構成で機能する回路構成を見つけることです。

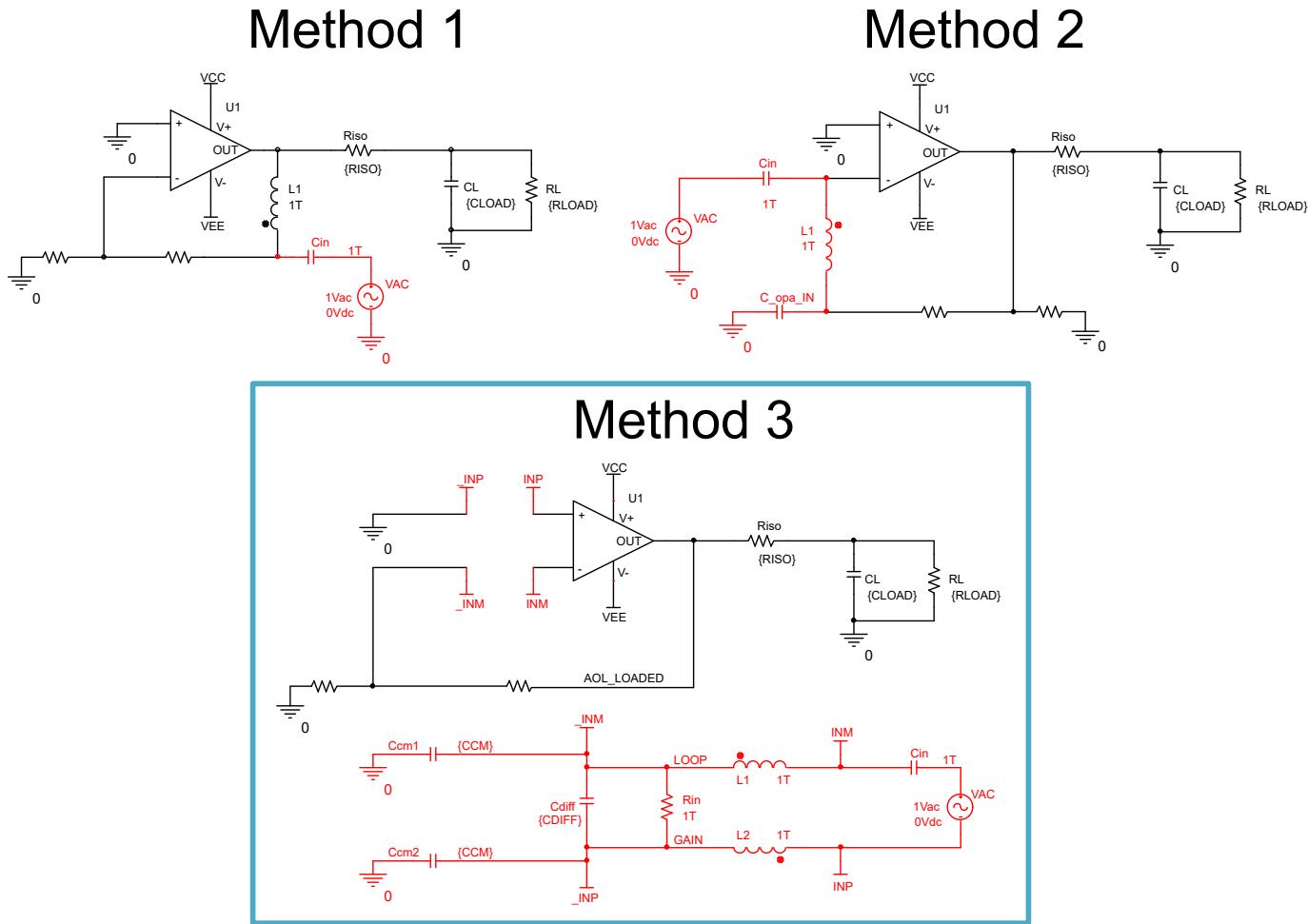

この例では、オペアンプにとって最も堅牢な開ループ構成は、方法 3 に示すダブルブレークです。これは、オペアンプの出力インピーダンスと帰還ネットワーク間の相互作用（方法 1 の欠点）と、帰還ネットワークと入力の寄生インピーダンス間の相互作用（方法 2 の欠点）を考慮しています。

図 2-1. オペアンプ回路の疑似開ループ構成方法

方法 3 は、PSpice®-for-TI の再利用性を高める上で推奨される選択肢ですが、主な欠点はセットアップ時の回路図の複雑さです。この方法の詳細については、[ti.com のビデオ「差動アンプのループを切断する」](#)をご覧ください。

### 3 プロジェクトの作成

このドキュメントでは、ユーザーが ケイデンス環境を初めて使用することを想定して、自動化プロジェクトの作成手順を最初から順に説明します。

ユーザーが以前に PSpice®-for-TI でプロジェクトと回路図を作成したことがある場合は、[セクション 4.5](#) に進むオプションがあります。

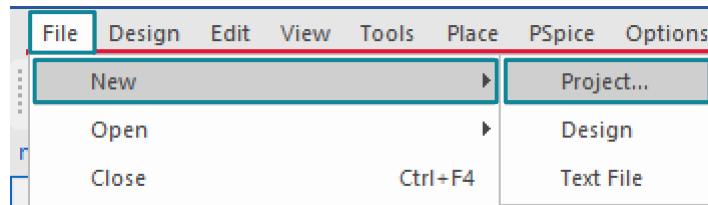

新しいプロジェクトは、ファイル、新規、プロジェクトから作成できます。

図 3-1. 新規プロジェクトの選択

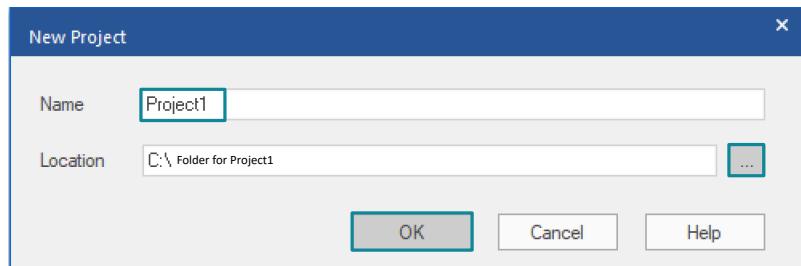

新しいプロジェクトの場所と名前を選択し、OK をクリックして続行します。ベストプラクティスとして、各 PSpice®-for-TI プロジェクトは新しいフォルダに保存されます。

図 3-2. 新規プロジェクト作成

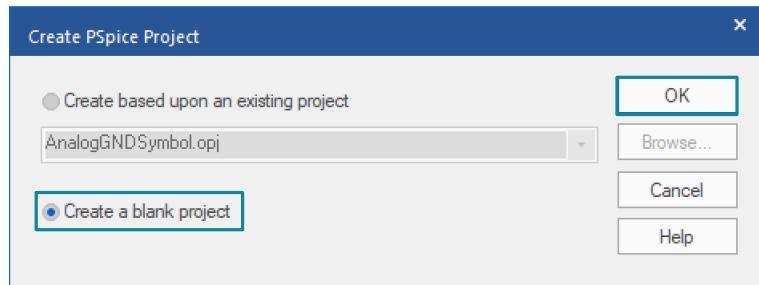

プロンプトが表示されたら、空のプロジェクトを作成を選択し、OK をクリックして継続行します。既存のプロジェクトに基づいて作成する方法は、複数の自動化プロジェクトを開発する場合に役立ちますが、このアプリケーションノートの範囲外です。

図 3-3. プロジェクトテンプレートの選択

### 3.1 プロジェクト階層

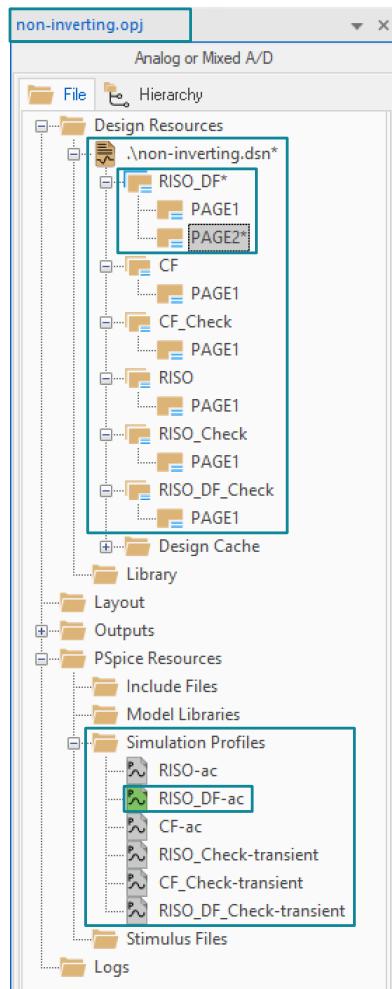

カデンツア環境には、複数の回路図を持つデザイン (.dsn) を含むプロジェクト (.opj) が含まれています。各回路図には複数のページを含めることができ、複数のシミュレーションプロファイルを関連付けることができます。

図 3-4 の例では、*non-inverting.opj* は、設計ファイル *non-inverting.dsn* を含むプロジェクトです。この設計ファイルには 6 つの回路図が含まれており、そのうち *RISO\_DF* には 2 つの回路図ページと、*RISO\_DF\_ac* というラベルの付いた AC シミュレーションプロファイルが 1 つ含まれています。

図 3-4. プロジェクト階層

## 4 読みやすさを高めた概略図

PSpice-for-TI® 回路図エディタには、より幅広いユーザーが簡単に使用できるベストプラクティスが組み込まれています。以下の手順では、複数のユーザーが読みやすく、直感的に操作できる回路図を組み立てるする方法について説明します。

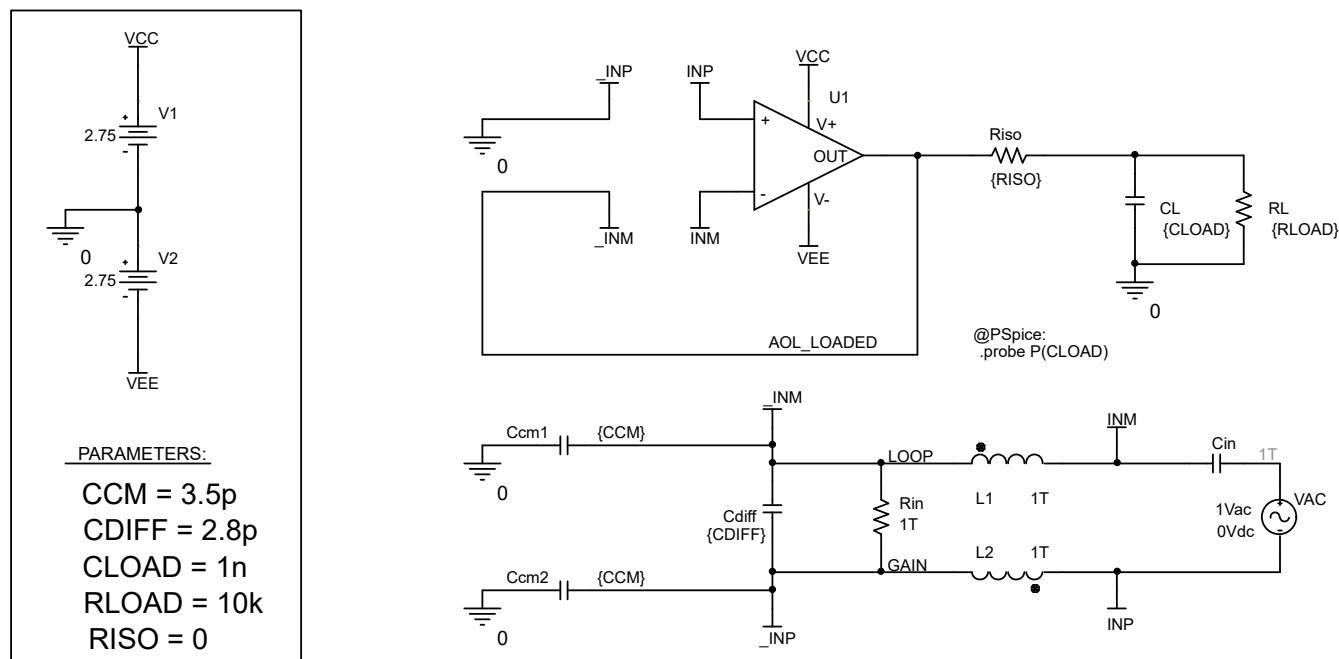

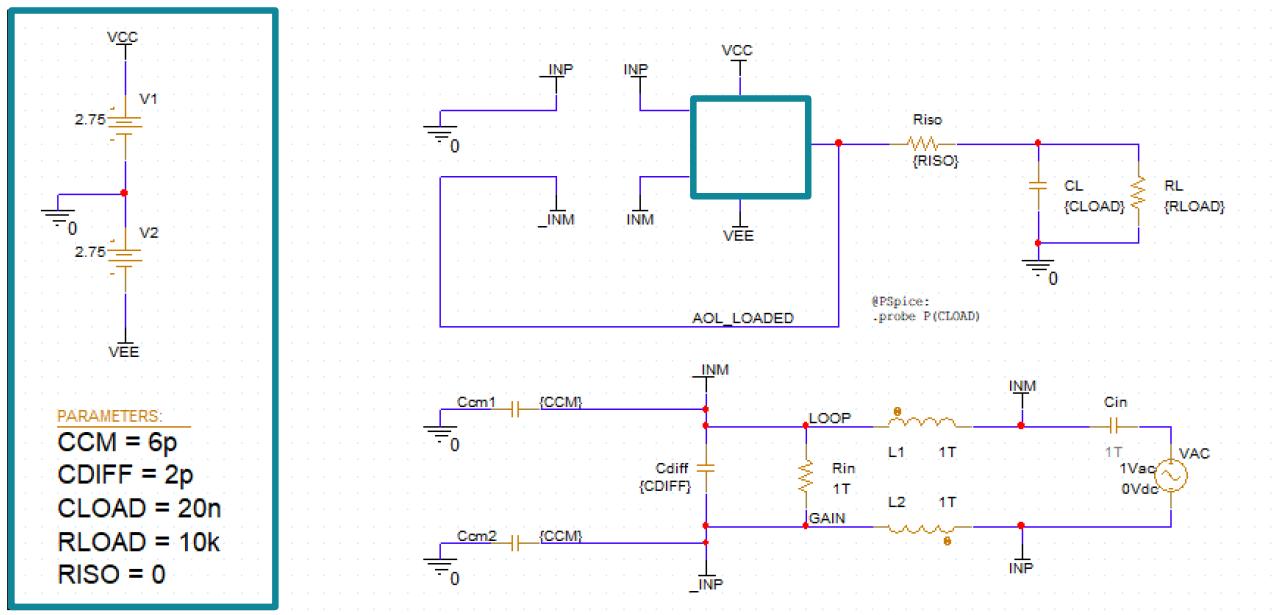

図 4-1. 最終的な回路図

### 4.1 受動部品の配置

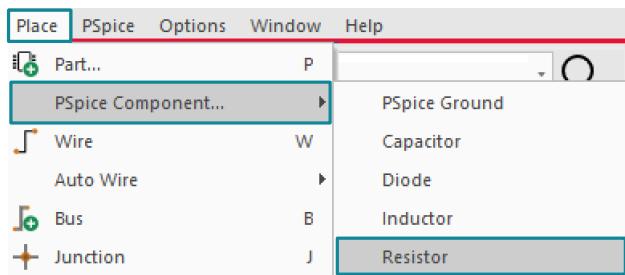

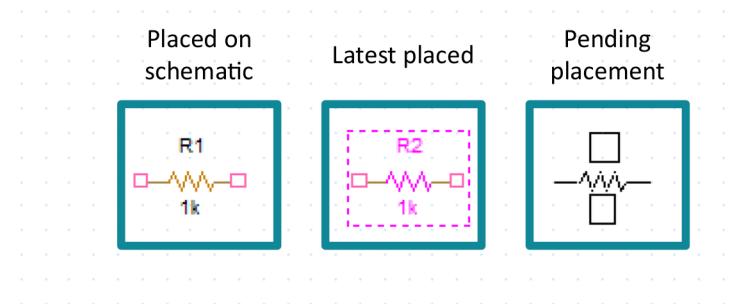

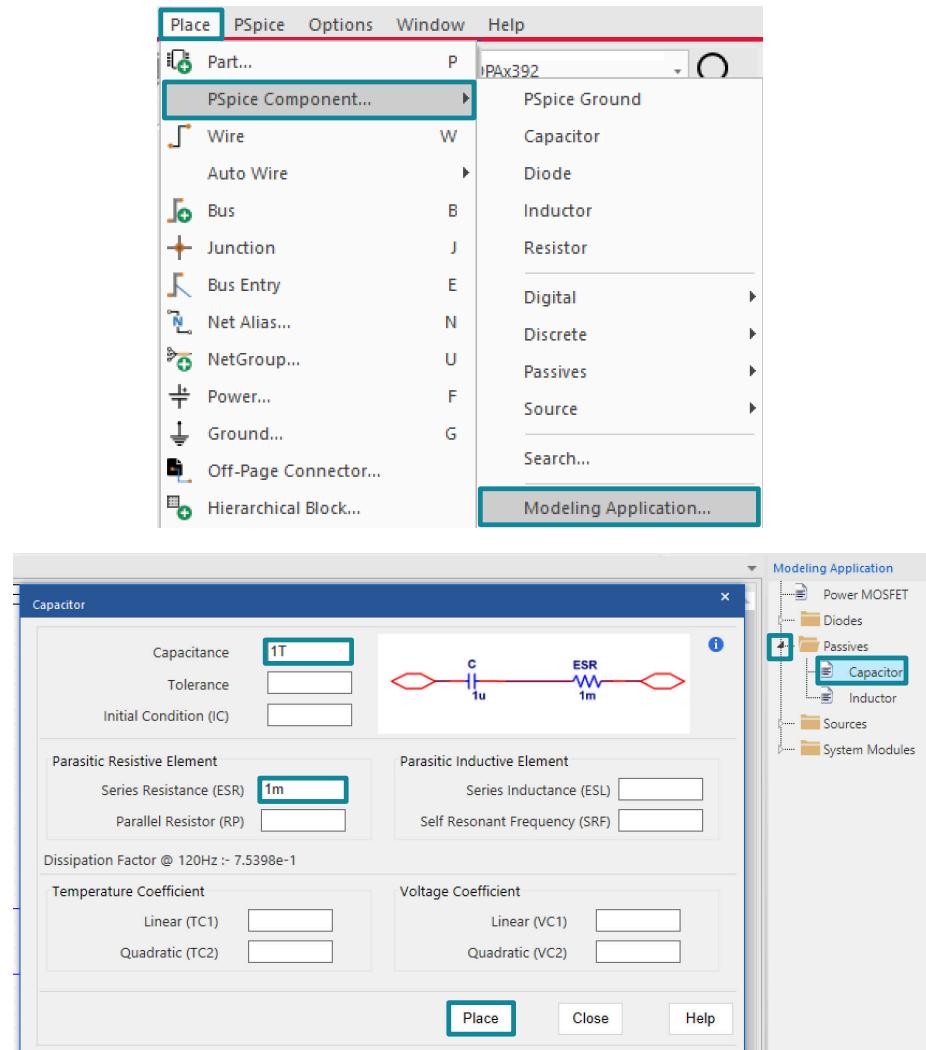

受動部品は、配置から PSpice 部品を順に選択し、該当する部品を選択することで配置できます。図 4-2 に示す例では、抵抗が回路図に配置されています。

図 4-2. 抵抗の配置

図 4-3 に、R1 (以前に配置された部品)、R2 (最後に配置された部品としてピンク色で強調表示)、そしてマウスがある場所にある名前がない部品を示しています。ESC を押して、複数の部品の配置を停止します。

図 4-3. 複数配置

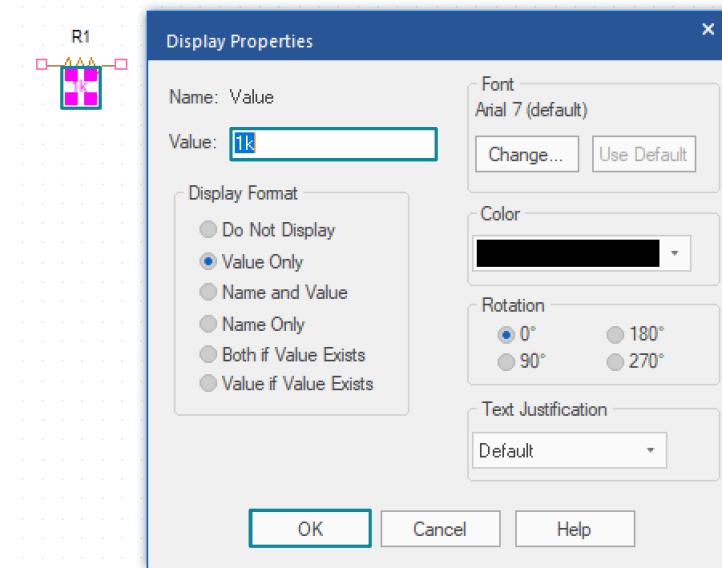

配置後は、部品の値をダブルクリックすることで値を編集できます。

図 4-4. シングルの変更

新しい値を入力し、OKを選択して適用します。

## 4.2 パラメータ

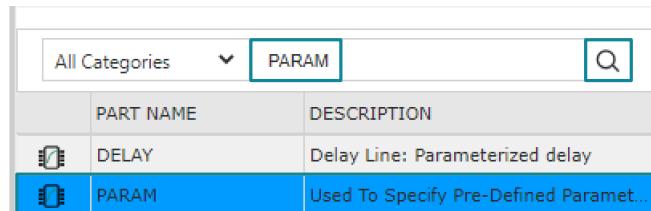

変数が複数の場所で使用されている場合、その変数は回路図にパラメータとして実装できます。PSpice® 部品検索(組み込みライブラリ)は、配置から PSpice 部品、検索を経てアクセスできます。パラメータを検索し、ダブルクリックして回路図に配置します。

図 4-5. パラメータの変数

複数の配置を停止するには、「ESC」を押します。図 4-6 に、回路図に配置されたパラメータ部品を示します。

## PARAMETERS:

図 4-6. 回路図上のパラメータ部品

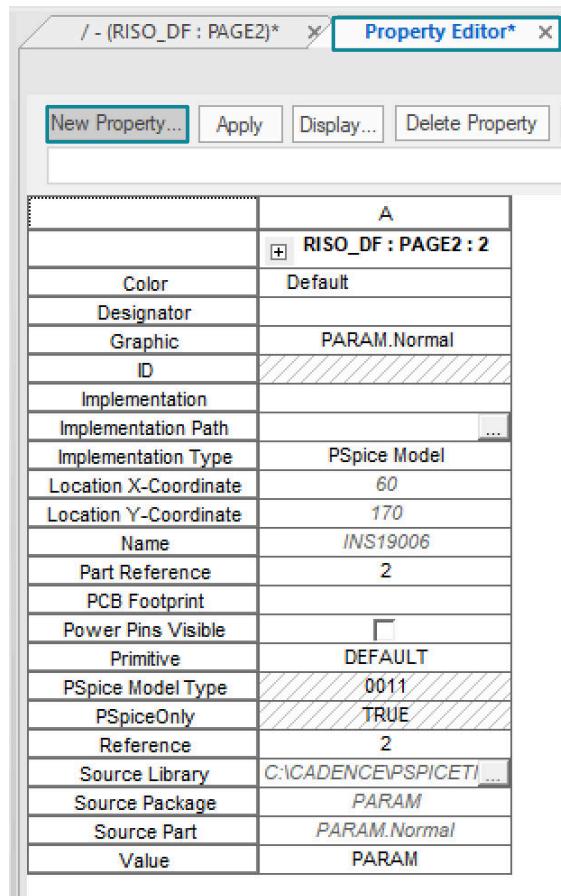

配置後、パラメータ部品をダブルクリックして、別のタブでプロパティエディタを開きます。オプションとして、図 4-7 のようにプロパティを垂直方向に表示するには、ピボットを選択します。

図 4-7. パラメータのプロパティエディタ

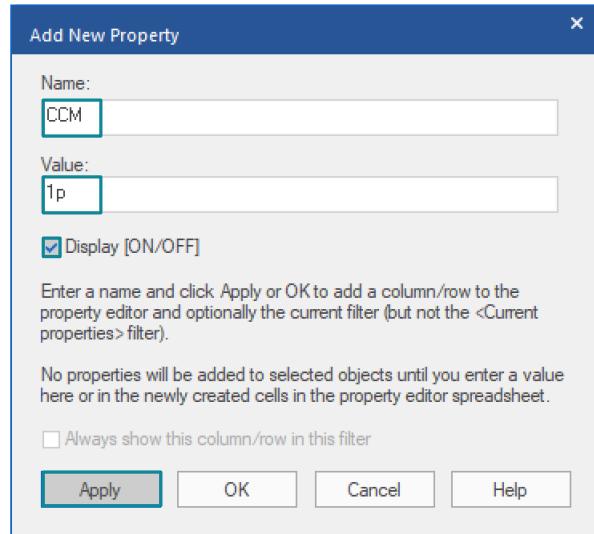

新規プロパティを選択し、図 4-8 のようにパラメータの名前とデフォルト値を選択します。「オン / オフ」表示チェックボックスをオンにすると、回路図に新しいパラメータが表示されます。適用を選択して、複数のパラメータを追加します。OK を選択して、パラメータを 1 つだけ追加します。

図 4-8. パラメータに新しいプロパティを追加します

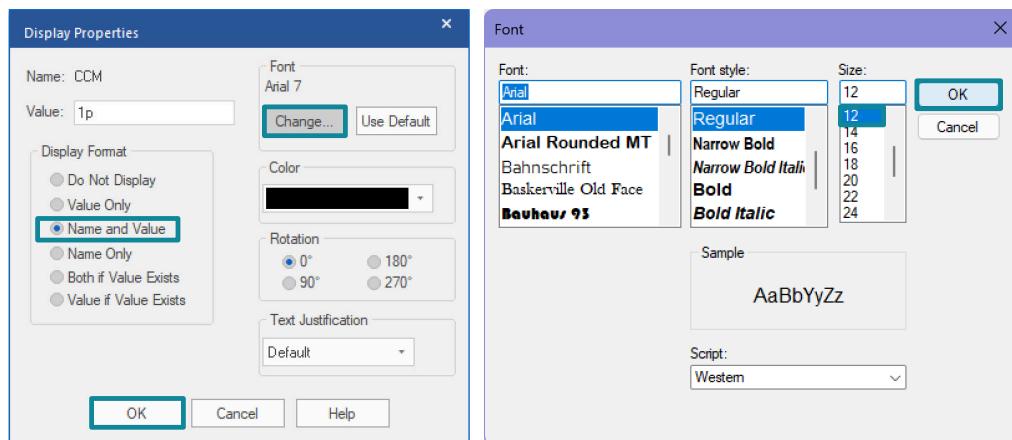

「オン / オフ」の表示を選択すると、表示設定を選択できます。表示形式は名前と値を選択します。デフォルトのフォントとサイズである Arial 7 は、プロジェクトで表示するには小さすぎます。自動化プロジェクトでは、よく使用するパラメータを大きなフォントサイズで実装することで、回路図内で簡単に見つけることができます。図 4-9 の例では、フォントサイズ 12 が選択されています。

図 4-9. パラメータの表示とサイズ設定

前述のように、複数のパラメータを追加する場合は、適用を選択し、プロジェクトに必要な数の新しいパラメータを作成します。図 4-10 に、追加されたさまざまなパラメータと、各パラメータのデフォルト値が表示されます。

### PARAMETERS:

**CCM = 1p**

**CDIFF = 3p**

**CLOAD = 1u**

**RLOAD = 10k**

**RISO = 0**

図 4-10. 複数のパラメータ

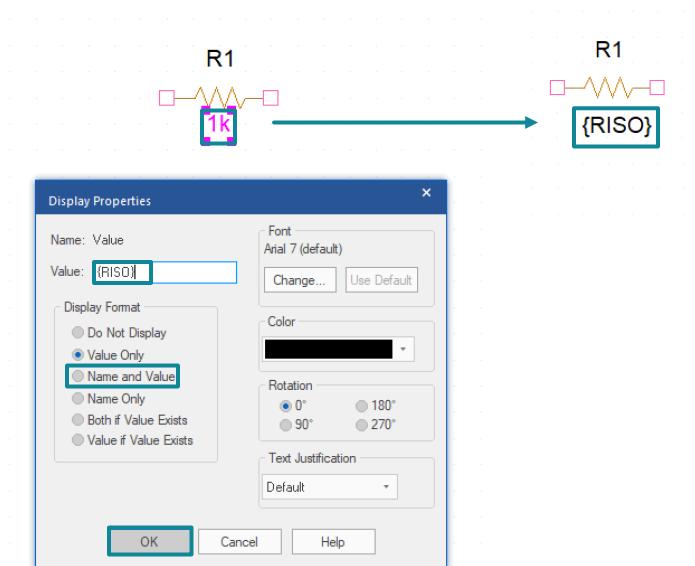

回路図でパラメータが宣言されると、ユーザーは部品の値で名前を中括弧で囲むことでパラメータを呼び出すことができます。図 4-11 では、R1 の値が  $1\text{k}\Omega$  からパラメータ RISO に対応する変数値に変更されます。

図 4-11. 部品値としてパラメータを追加します

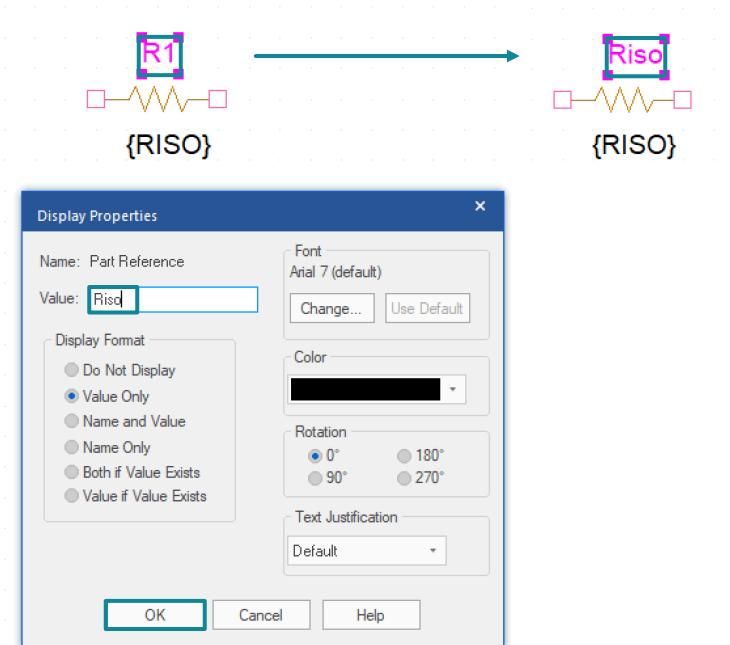

回路内の部品に共通の名前がある場合は、それを反映するように部品リファレンスを変更します。

図 4-12. 部品リファレンスの名前を変更

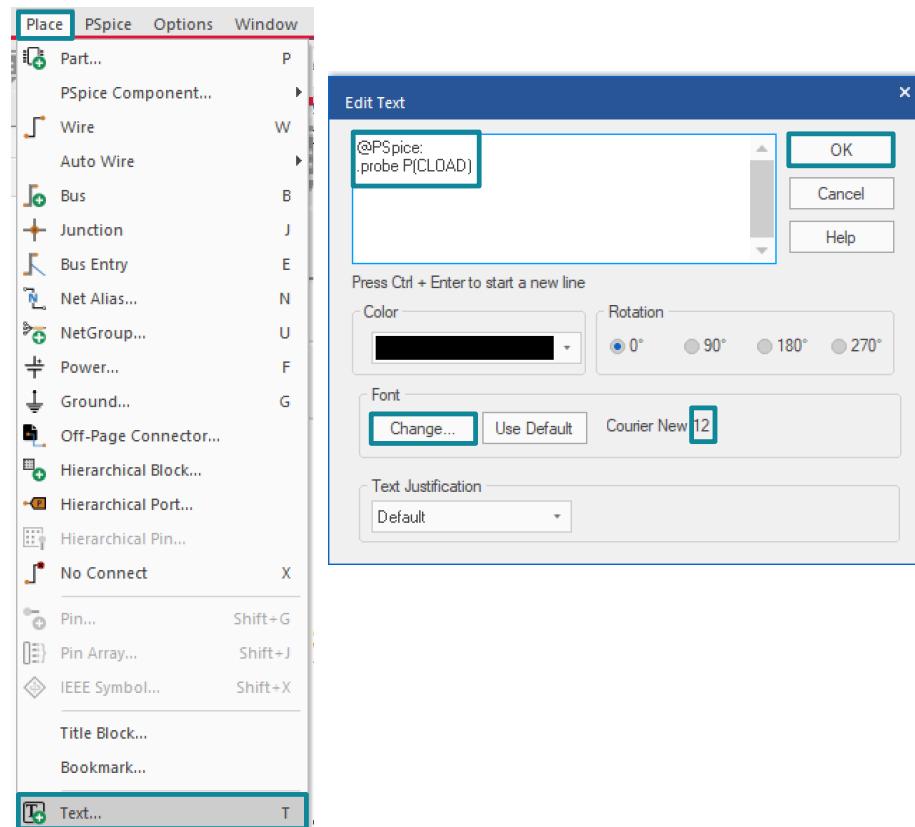

出力シミュレータウインドウで呼び出されるパラメータにプローブが追加されます。パラメータにプローブを追加するには、配置、テキスト、またはキーボードショートカット T, @PSpice を使用して、回路図に次のテキストを追加する必要があります。プローブ P (パラメータ名)。この実装の使用例は、後処理方程式でパラメータが必要な場合です。詳細はセクション 5.2 で説明されています。図 4-13 では、計算に使用されたパラメータは CLOAD でしたが、この手順は必要に応じて複数のパラメータに対して繰り返すことができます。フォントサイズが 12 に拡大されました。

図 4-13. 出力シミュレーションウインドウで使用されるパラメータ

## 4.3 電源装置を設置

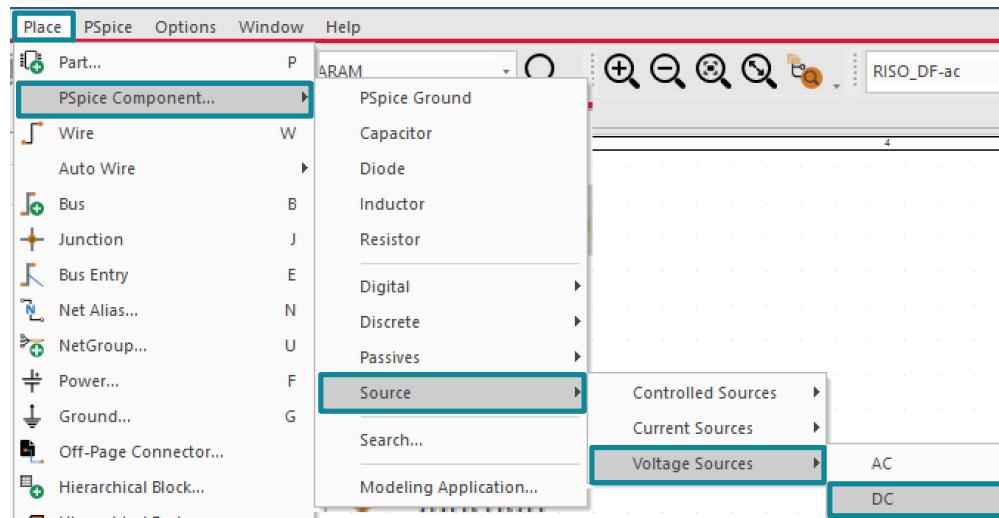

DC 電源は、配置から、*PSpice* 部品、ソース、電圧源、DC を経て配置できます。

図 4-14. DC 電圧の配置

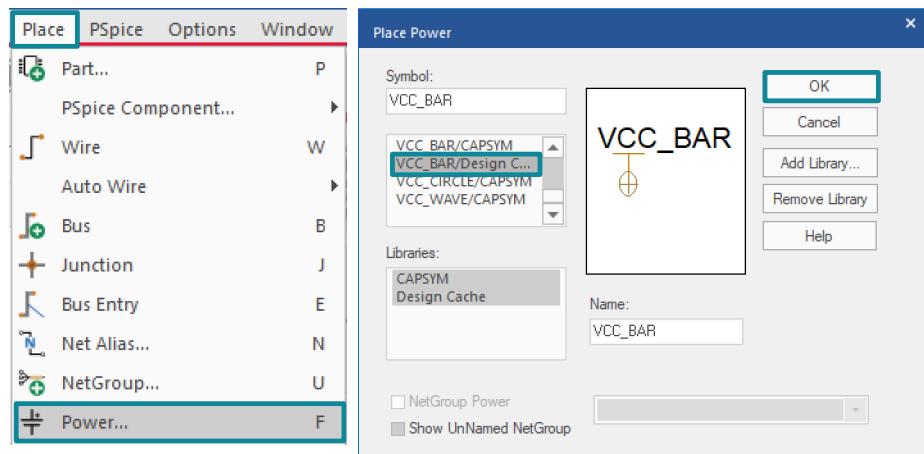

電源の配置後、その電源を使用するために、電源ネットを回路図内の複数の場所に配置できます。電源コンポーネントは、配置から電源、またはキーボードショートカット「F」にあります。複数のシンボルが使用可能で、図 4-15 の例では *VCC\_BAR* を使用しています。

図 4-15. *VCC\_BAR*

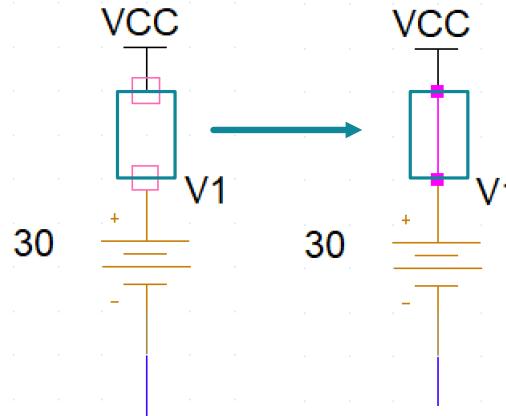

#### 4.4 配線

ワイヤは、配置からワイヤ、またはキーボードショートカット W を使用して配置されます。回路図をクリックしてワイヤの配置を開始し、クリックのたびに方向を変更できます。2つの部品を接続するには、正方形のコネクタをクリックするだけです。

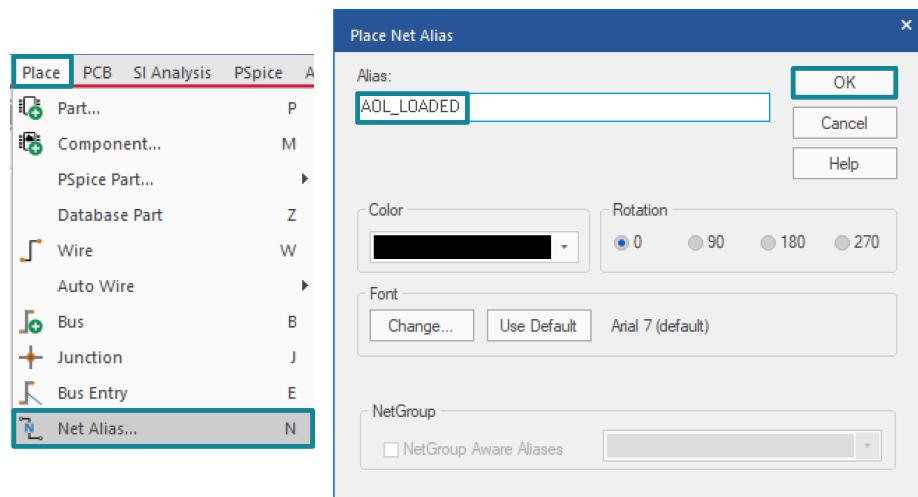

図 4-16. ワイヤの配置

ワイヤが配置されると、PSpice®-for-TI は各ワイヤに英数字のネットエイリアスを割り当てます。重要なワイヤの場合は、ネットエイリアスの名前を認識可能な名前に変更します。ネットエイリアスは、配置からネットエイリアス、またはキーボードショートカット N を使用してエイリアスを入力し、OKを選択して配置します。ネットエイリアスは既存のワイヤ上にのみ配置され、物理的に接続せずに 2つのワイヤを接続するために使用することもできます。

図 4-17. ネットのラベル付け

#### 4.5 ユーザーエクスペリエンスを考慮した編成

すべての部品を配置し、分かりやすい名前を付け、配線したら、ユーザー エクスペリエンスを考慮する必要があります。作者にとって明らかなことも、初心者には分かりにくい場合があります。そのため、プロジェクトの各部分にラベルを付けて分離することで、初心者がスムーズに作業を進めることができます。

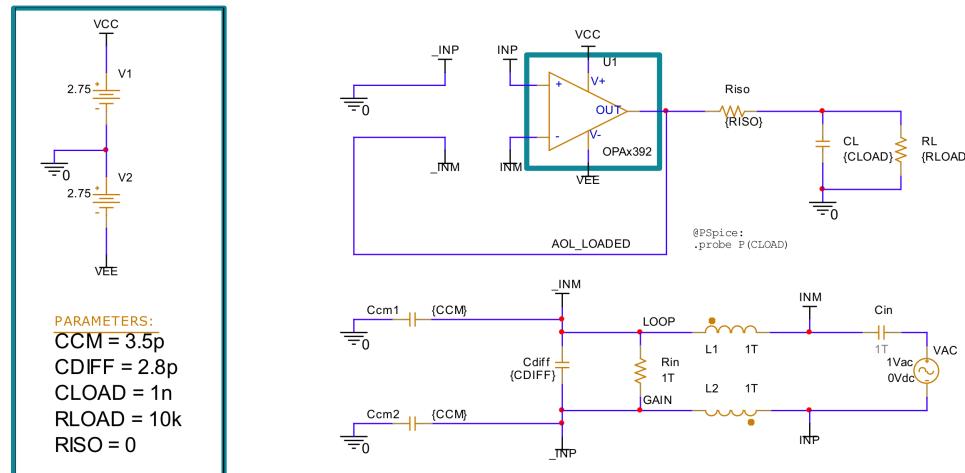

この例では、ユーザーが変更する必要がある変数は、左側図 4-18 のボックス内にのみ配置されています。右側の回路図接続は、ユーザー依存の変数 (パラメータ) と相互作用しますが、実際の回路図で上書きされる可能性は低くなります。

図 4-18. ユーザインタラクションの最小化

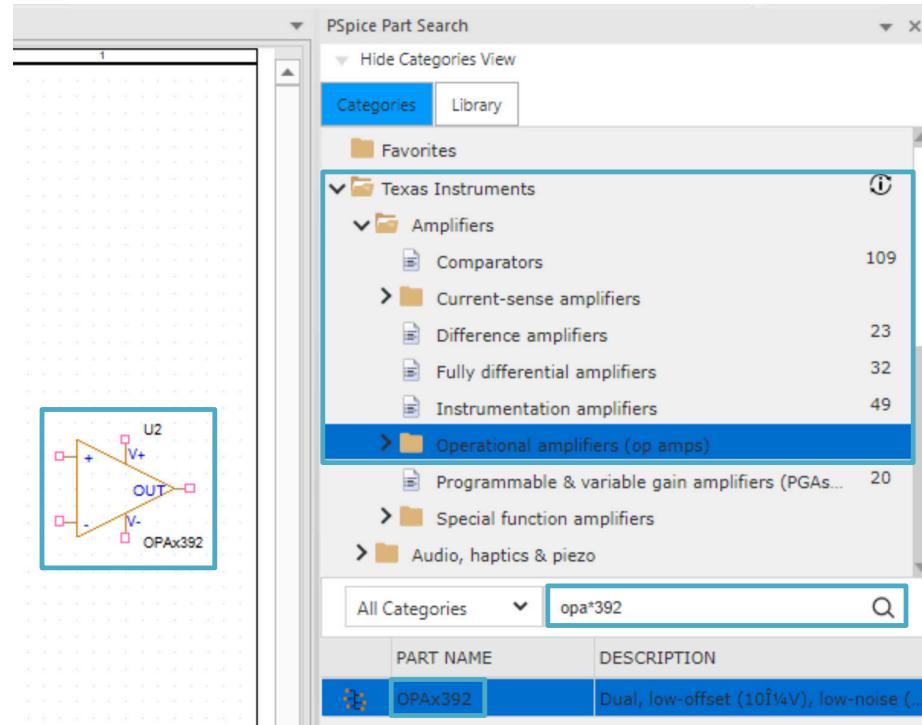

回路図の中央図 4-18 にオペアンプを配置する操作は、この回路図における最後のユーザー インタラクションです。部品は、PSpice® 部品検索 (パラメータと同様に) から配置できます。テキサスインスツルメンツ、アンプ、オペアンプ (オペアンプ) の順で選択するか、検索 (拡大鏡アイコンの付いたすべてのカテゴリドロップダウンメニューの横にあります) から配置できます。検索では、アスタリスク (\*) としてワイルドカードを使用できます。配置すにはダブルクリックしてください。

図 4-19. 統合ライブラリを使用して TI の部品を配置します

TI のオペアンプ製品群の 90% 以上は、図 4-19 に示すピン配置(非反転入力 (IN+) と正電源 (V+) が上向き)で配置されます。この回路図は、図 4-20 に示すように、ユーザーが回転や反転することなく、簡単に配置できるように描かれています。

The screenshot shows a PSpice schematic editor window titled '/ - (RISO : PAGE1)\*'. On the left, there's a component symbol for the OPAx392 op-amp with its pin connections labeled: INP, INM, OUT, V+, VEE, and VCC. Below it, a parameter box lists: CCM = 3.5p, CDIFF = 2.8p, CLOAD = 1n, RLOAD = 10k, and RISO = 0. The main schematic area shows a complex circuit. At the top, there's a voltage source V1 connected to ground through a 2.75 ohm resistor. Another 2.75 ohm resistor connects V1 to the VCC pin of the op-amp. The VEE pin is connected to ground. The OUT pin of the op-amp is connected to a load CL (CLOAD) through a resistor RL (RLOAD). The INP pin is connected to a node labeled 'LOOP' via a capacitor Cdiff (CDIFF). The INM pin is connected to ground. The 'LOOP' node is connected to the INP pin of another op-amp U1, which is also connected to ground. The OUT pin of U1 is connected to the INP pin of the OPAx392. There are other components like resistors Rin, L1, L2, and capacitors Cin, Ccm1, Ccm2, and a voltage source VAC.

図 4-20. ユーザーによる変更のなしの配置

JAJAA68 – OCTOBER 2025

資料に関するフィードバック(ご意見やお問い合わせ)を送信

PSpice-for-TI を使用して、自動 SPICE 設計を作成

15

English Document: SBOA605

Copyright © 2025 Texas Instruments Incorporated

## 5 シミュレーションプロファイルの設定

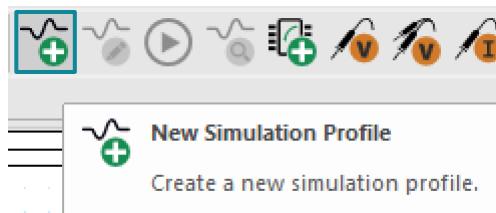

回路図が完成したら、次のステップはシミュレーションプロファイルの作成です。

以前に PSpice®-for-TI でシミュレーションプロファイルを作成したことがある場合は、[セクション 5.1](#) に進んでください。

新規シミュレーションプロファイルを作成するには、**PSpice** から、新規シミュレーションプロファイルを選択するか、[図 5-1](#) に示すタスクバーの新しいシミュレーションプロファイルアイコンをクリックします。

図 5-1. 新規シミュレーションプロファイルアイコン

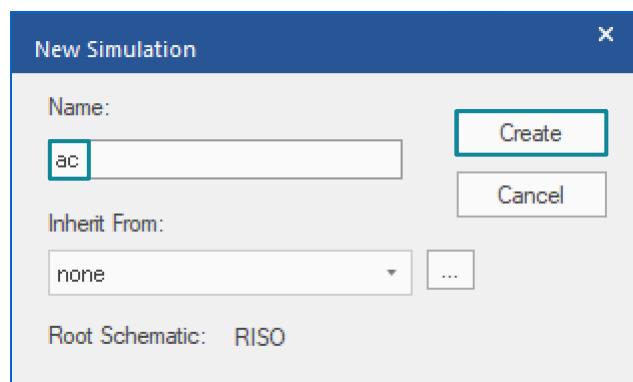

シミュレーションプロファイルには、わかりやすい名前を付けてください。[図 5-2](#) では、シミュレーションは AC スイープを表す **ac** という名前になっています。作成を選択して続行します。

図 5-2. 新規シミュレーションプロファイルの名前付け

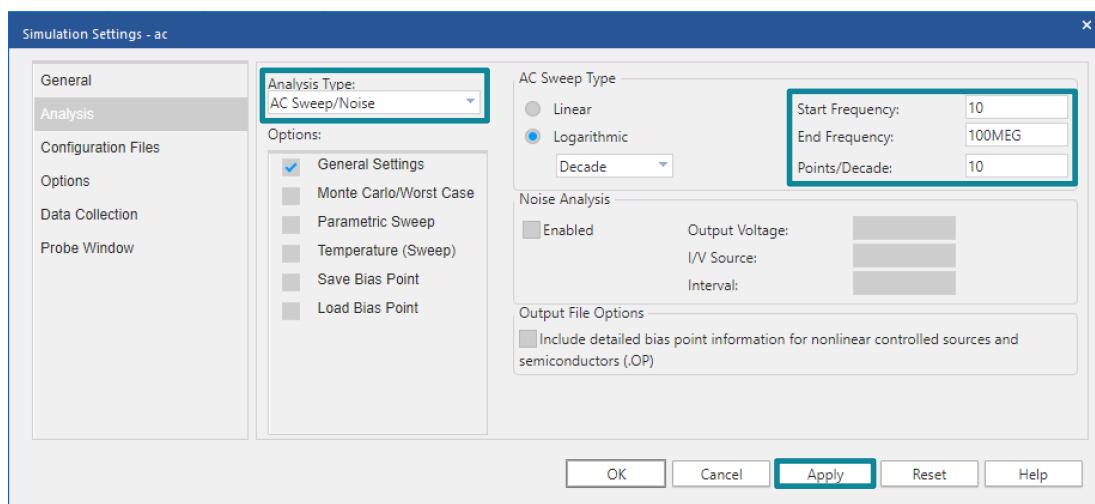

この例では、解析は周波数ドメインで行われるため、解析タブの解析タイプとして AC スイープ/ノイズが選択されています。対象周波数はアンプの帯域幅によって異なります。この例では、10Hz から 100MHz までの周波数スイープがディケードごとに 10 ポイントで実行されます。PSpice®-for-TI では、メガ ( $10^6$ ) を表す **MEG** の宣言が必要で、**M** はミリ ( $10^{-3}$ ) として認識されます。このタブの設定を保存するには、**適用**を選択します。

図 5-3. AC スイープのセットアップ

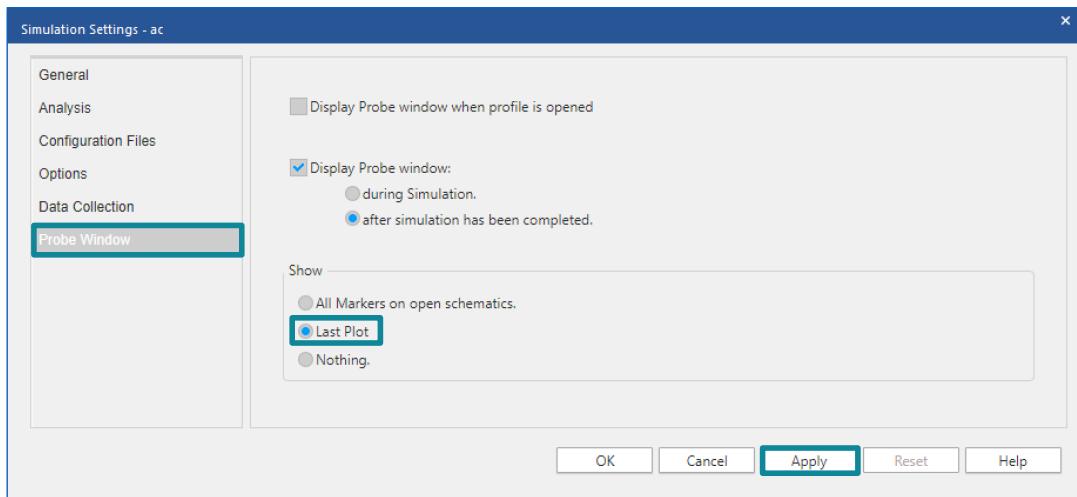

プロープウインドウタブでは、シミュレーションを実行するたびに最後のプロットを表示するように選択します。これにより、シミュレーションプロファイルはプロープウインドウの設定（プロットと方程式）を保存し、毎回の実行に適用されます。**適用**と**OK**を選択して、シミュレーションプロファイルの設定を終了し、ファイル設定を終了します。

図 5-4. 最後のプロット

## 5.1 収束を支援

PSpice®-for-TI は、デフォルトでは自動収束が有効になっていません。収束の問題がある場合は、デバイスのデータシートを確認し、デバイスのリニア動作条件内での設定と動作を確認してください。

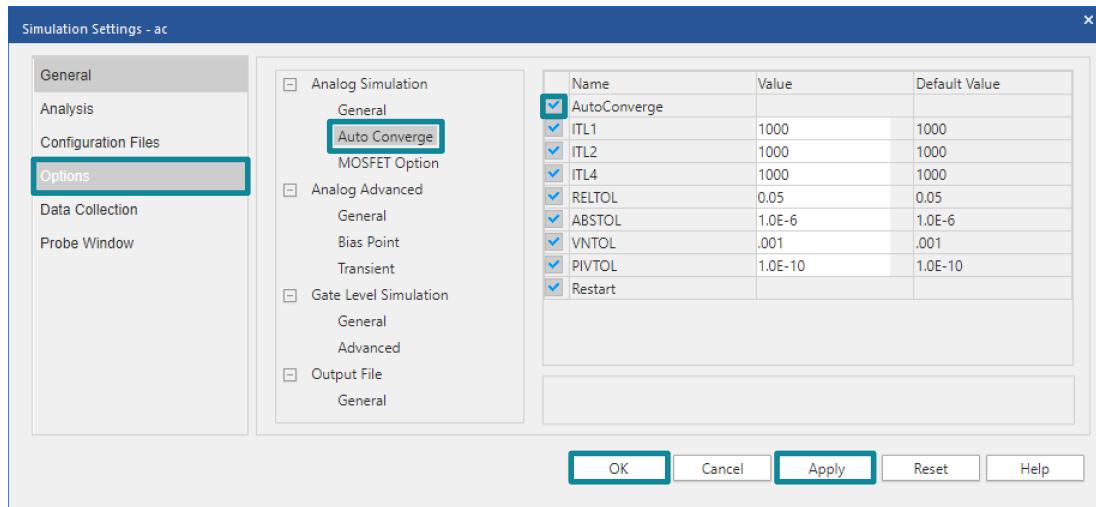

複雑なプロジェクトでは、デバイスのリニア動作条件内であっても、シミュレーションに数分かかることがあります。シミュレーションプロファイル設定で自動収束を有効にすると、シミュレーション時間を短縮できます。オプション、タブ、アナログシミュレーション、自動収束の順で、一番上の自動収束のテキストボックスを選択すると、その下のすべてのオプションが選択されます。

自動収束を有効にすると、プログラムが収束を試みる際に、シミュレーションの精度が低下したり、反復回数が増加したりする可能性があります。

図 5-5. Auto Converge

タブの設定を保存するには**適用**を選択し、**OK**をクリックしてシミュレーションプロファイル全体の編集を終了します。

### 5.1.1 モデリングアプリケーション

プロジェクトによっては、シミュレータがノード電圧と電流を計算する際に数値的な制限に直面することがあります。

この例では、AC 入力の隣にある大きな(1T)コンデンサに、収束を促進するために寄生直列抵抗を追加する必要があります。この小さな直列抵抗は、シミュレータがコンデンサを流れる非常に大きな電流を計算することを避けるために、最小限のコンデンサインピーダンスを提供します。

これを実装するには 2 つの方法があります。一つ目は、コンデンサと直列に抵抗を配置する方法、または二つ目のモデリングアプリケーションを配置から PSpice コンポーネント、モデリングアプリケーションを選び、より洗練されたオプションが利用できます。コンデンサの受動部品で、静電容量を 1T、直列抵抗(ESR)を 1m に設定します。これにより、AC シミュレーションの応答がすべての周波数範囲で滑らかになります。配置されたコンデンサは、変更箇所がわかるように黒ではなく灰色で表示されます。

図 5-6. モデリングアプリケーション

## 5.2 強力な後処理

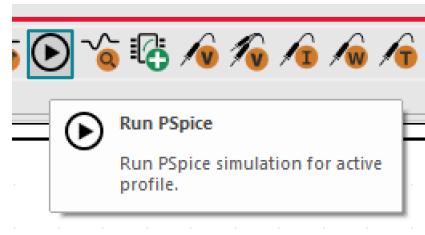

シミュレーションプロファイルが作成されると、デフォルトではシミュレーションプロファイルが階層の最上部に配置され、アクティブとして表示されます。アクティブなシミュレーションプロファイルは、**PSpice** から実行またはキーボードショートカット F11 で評価されます。

図 5-7. PSpice® シミュレーション実行アイコン

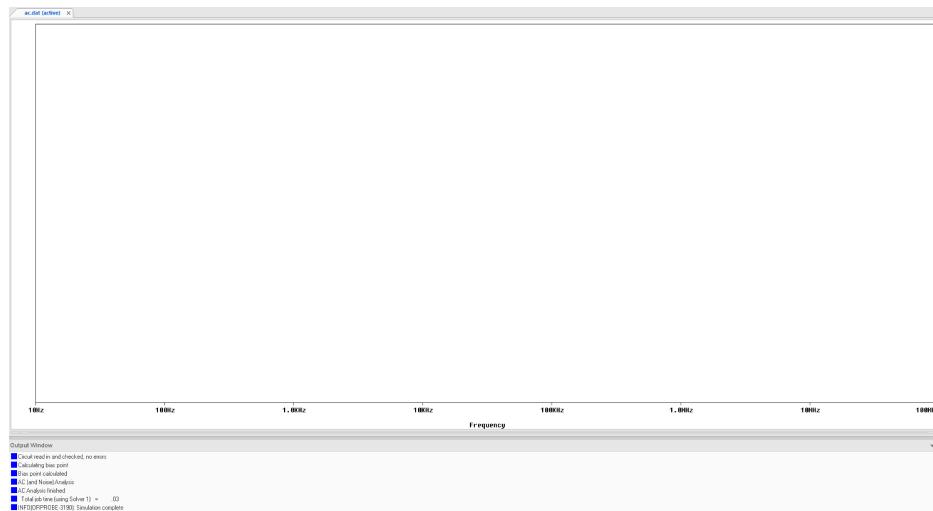

シミュレーションを初めて実行する際は、PSpice®-for-TI が [ti.com](http://ti.com) から最新のライブラリを更新するため、予想よりも長い待機時間が発生することが予想されます。新しいウィンドウが開き、図 5-8 のように空のプロットが表示されます。

図 5-8. 最初の出力は空のプロットです

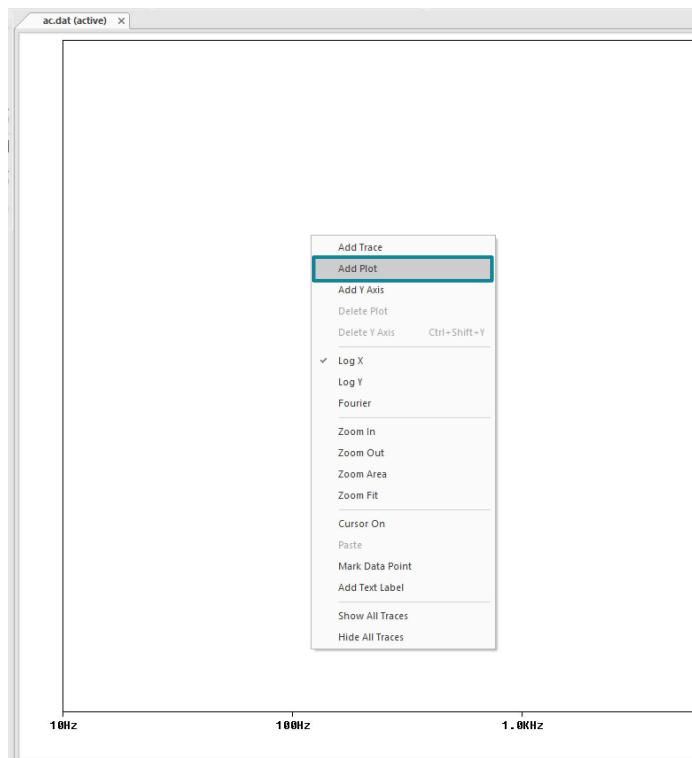

図 5-9 に示すように、プロットを右クリックしてプロットの追加を選択すると、複数のプロットを追加できます。

**図 5-9. プロットを追加します**

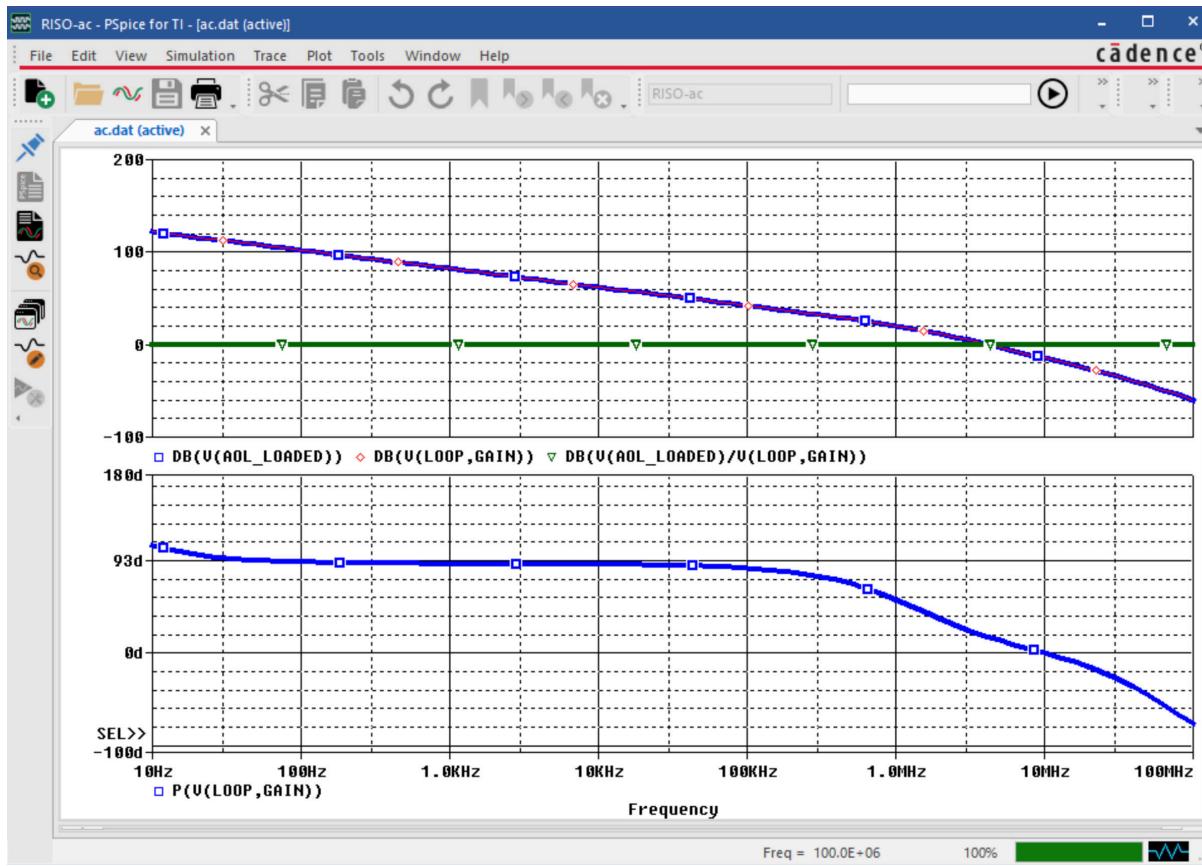

この例では、周波数スイープを実行して回路の開ループ応答を振幅 (dB) と位相 (°) で観測しました。そのため、シミュレータの出力ウィンドウに 2 つのプロットが追加されています。

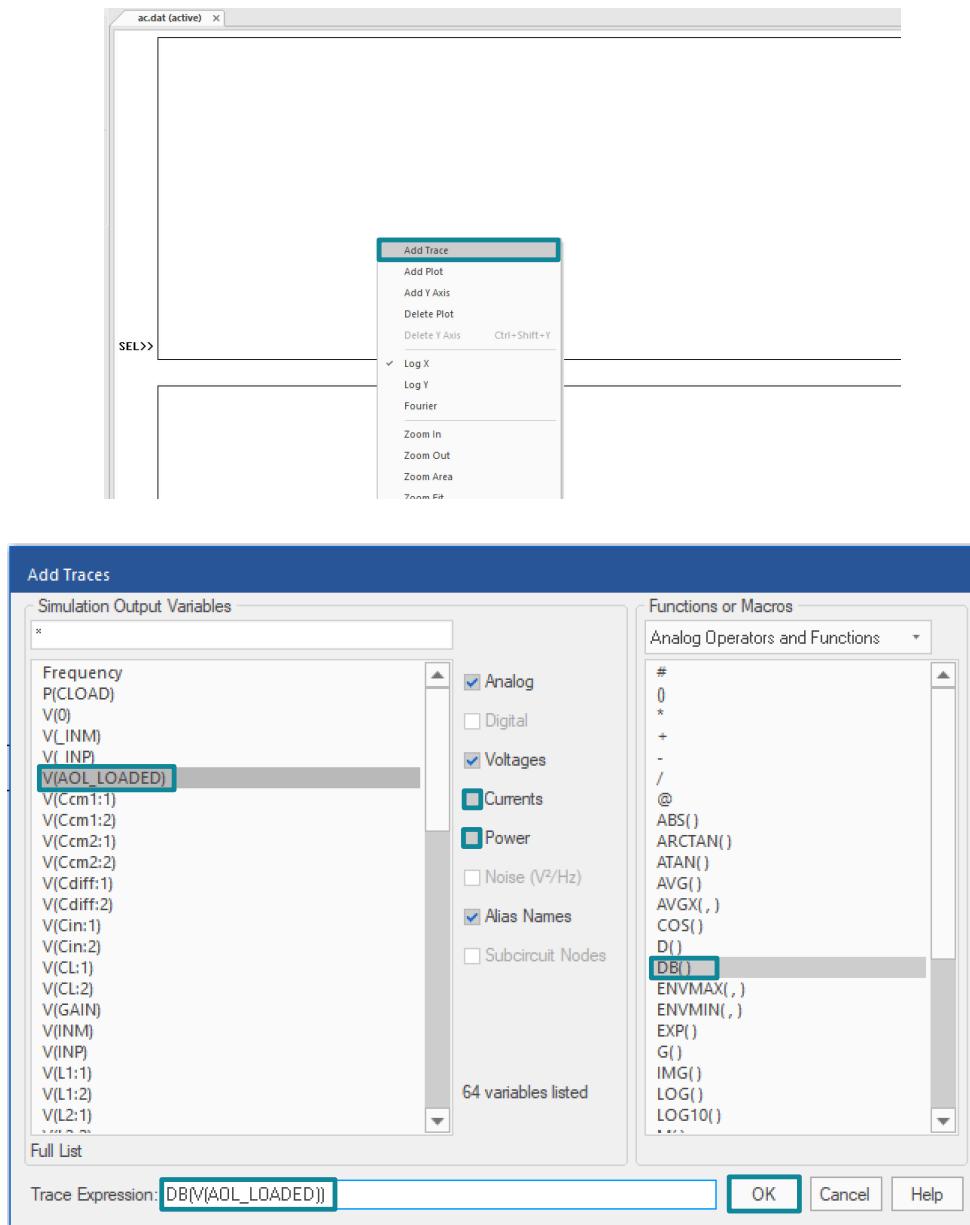

オペアンプの AC 応答では通常、上のプロットが振幅 (dB)、下のプロットが位相 (°) です。関連するネットの振幅 (dB) と位相 (°) を追加するには、トレースを配置する必要があります。これは、図 5-10 に示すように、目的のプロットを右クリックし、トレースの追加を選択することで実行できます。

図 5-10. トレースの追加

ダイアログウィンドウが表示され、シミュレーション出力変数と「関数またはマクロ」を選択できます。

この例では、必要な振幅 (dB) と位相 (°) のトレースが表 5-1 にリストされています。

表 5-1. トレース シンタックス

|              | トレース                                    | 式シンタックス                               |

|--------------|-----------------------------------------|---------------------------------------|

| 負荷に対する開ループ応答 | 負荷を接続したオペアンプ出力の電圧 (dB)                  | DB (V (AOL_LOADED) )                  |

| ループ ゲイン      | 「LOOP」および「GAIN」のラベル付きのネット間の電圧 (dB および度) | DB (V (LOOP, GAIN) )                  |

|              |                                         | P (V (LOOP, GAIN) )                   |

| 1/β          | 負荷とループゲインに対する開ループ応答の比率                  | DB (V (AOL_LOADED) / V (LOOP, GAIN) ) |

トレース式は、図 5-10 に示すように、直接入力するか、使用可能なオプションから選択することができます。あるいは、図 4-17 で前述のようにネットにラベルが付けられている場合は、トレースを表 5-1 からプログラムに直接コピーして貼り付けることもできます。

すべてのトレース式を含む出力シミュレーション ウィンドウを図 5-11 に示します。上のプロットは振幅 (dB) 応答、下のプロットは位相 (°) です。

図 5-11. 出力シミュレーション ウィンドウ

この例では、位相マージンを改善することが目標です。これは、開ループ応答の位相マージンを評価し、回路の AC 応答から補償成分を計算することによって行われます。

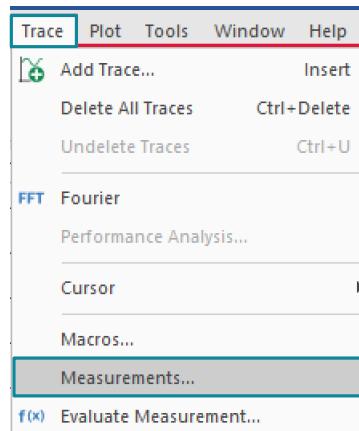

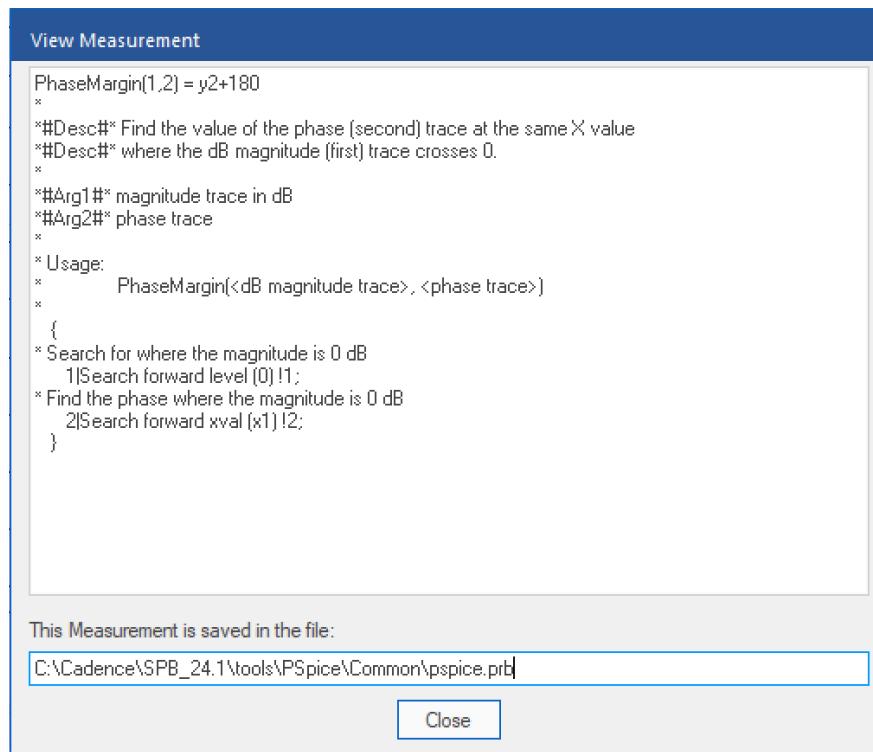

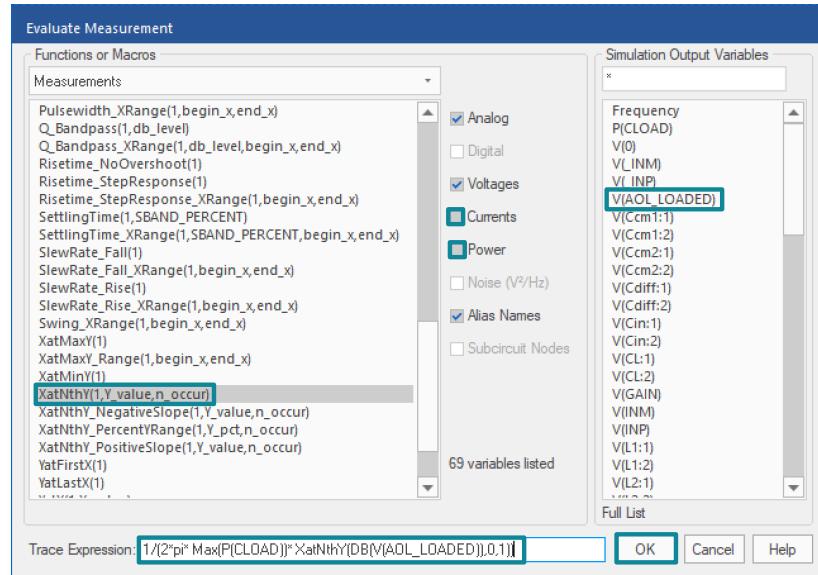

PSpice®-for-TI には数式が組み込まれており、その構文は図 5-12 に示すように、トレースサブメニューの測定オプションにあります。この例では、位相マージン、XatNthY、および 最大の 3 つの測定値が使用されます。

図 5-12. 測定値のシンタックス定義

測定ウィンドウで該当するオプションを選択します。この例では、位相マージンがハイライト表示され、表示が選択されています。

図 5-13. 位相マージンの測定値

選択した測定値、説明、測定引数のシンタックス、およびファイルパスがダイアログボックスに表示されます。

図 5-14. 位相マージン測定値の定義

位相マージン測定値は、振幅が 0dB となる周波数における位相です。PSpice®-for-TI では、トレースの振幅を dB 単位で検索し、値が 0 になるまで x 値(周波数)を記録します。次に、その周波数における位相プロットの y 値を読み取ります。

図 5-14 で定義された測定値では、 $y_2$  によって提供される位相マージンは +180 度でオフセットされますが、これはオペアンプには関係ないため、評価される測定値は -180 度でオフセットされ、 $\text{PhaseMargin (DB (Trace), P (Trace))} - 180$  という式で表されます。

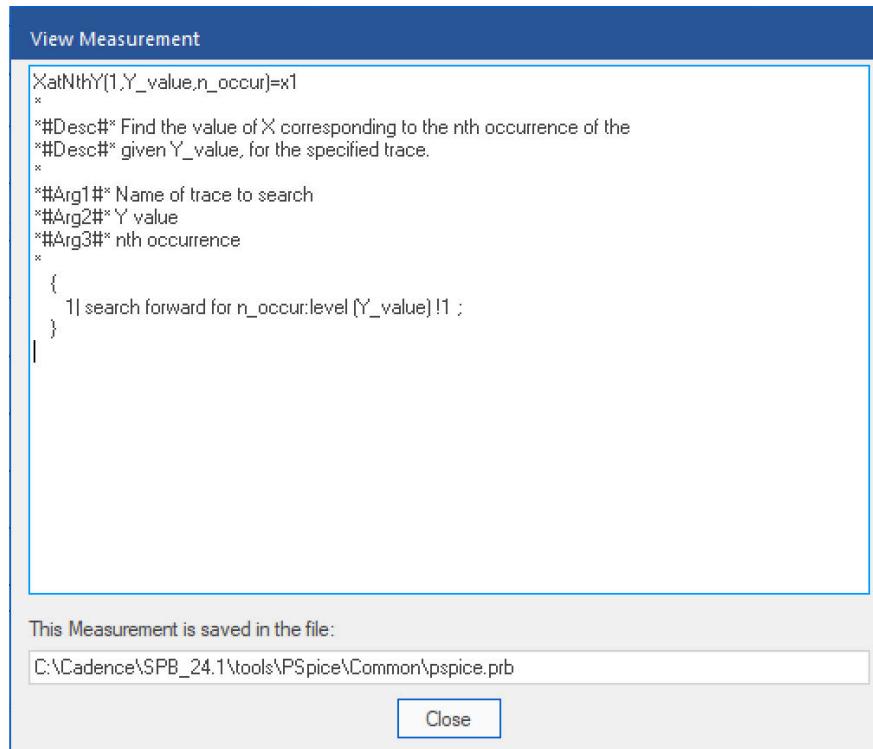

次に、オペアンプの振幅出力が 0dB と 20dB となる周波数を見つけるために、**XatNthY** 測定値を使用します。**XatNthY** 測定値は、図 5-15において、発生時の特定の y 値に対応する x として定義されます。ここで、x は周波数 (Hz)、y は振幅 (dB) です。どちらのシナリオでも、複数回発生することはないと想定され、最初の発生のみが考慮されます。

**図 5-15. XatNthY 測定値の定義**

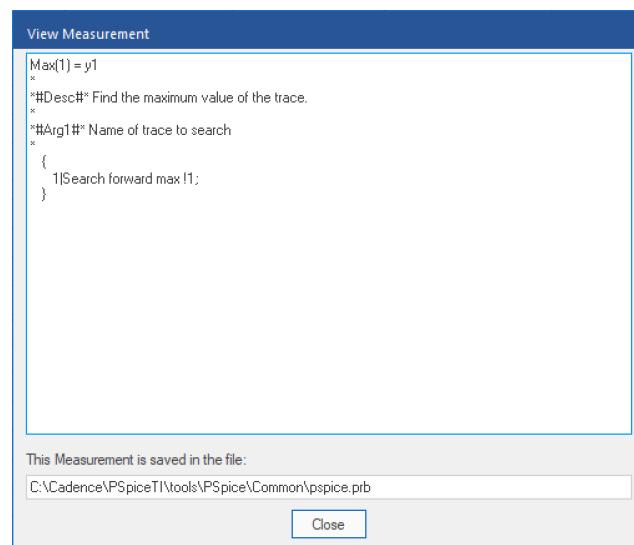

R/ISO 補償を計算するには、容量性負荷の値を回路図から出力シミュレーション ウィンドウに転送する必要があります。この実装については図 4-13 を参照ください。このプローブの **CLOAD** における値 **P(CLOAD)** を評価対象の式に含めるには、パラメータ **CLOAD** でプローブに測定値を適用する必要があります。容量値は周波数によって変化しないことを考慮して、図 5-16 で定義されている最大測定値が使用されます。

**図 5-16. 最大測定値の定義**

表 5-2 に、「位相マージン」、標準的な「RISO」、および保守的な「RISO」値に必要な式シンタックスの概要を示しています。標準的な「RISO」では位相マージンが  $45^\circ$  近くになり、保守的な「RISO」では位相マージンが  $90^\circ$  近くになります。より大きな絶縁抵抗では、電流需要が高くなり（抵抗負荷が小さくなる）出力の電圧が不正確になるというトレードオフが生じます。

$$R_{ISO} \text{ (typical)} = \frac{1}{2\pi \times f_{AOL\_LOADED}} = 0 \text{dB} \times C_{LOAD} \quad (1)$$

$$R_{ISO} \text{ (conservative)} = \frac{1}{2\pi \times f_{AOL\_LOADED}} = 20 \text{dB} \times C_{LOAD} \quad (2)$$

表 5-2. 式の測定値とシンタックス

| 測定時        | 式シンタックス                                                                                                                    |

|------------|----------------------------------------------------------------------------------------------------------------------------|

| 位相マージン     | 位相マージン (DB (V (LOOP, GAIN) ), P (V (LOOP, GAIN) )) -180                                                                    |

| RISO (標準値) | $1 / (2 * \pi * \text{Max} (\text{P} (\text{CLOAD})) * \text{XatNthY} (\text{DB} (\text{V} (\text{AOL\_LOADED})), 0, 1))$  |

| RISO (保守的) | $1 / (2 * \pi * \text{Max} (\text{P} (\text{CLOAD})) * \text{XatNthY} (\text{DB} (\text{V} (\text{AOL\_LOADED})), 20, 1))$ |

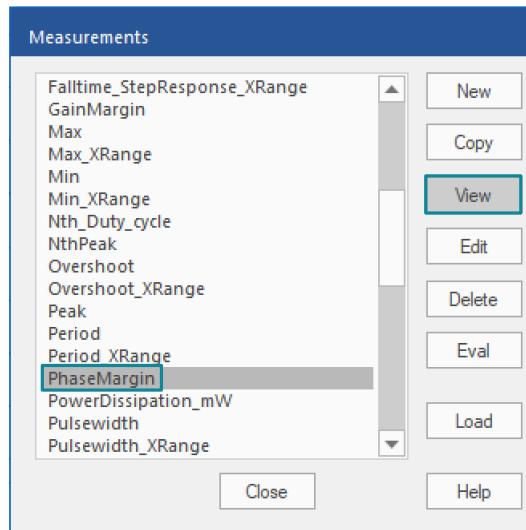

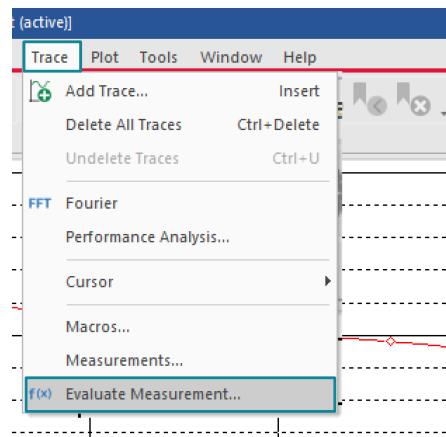

これらの測定値を出力シミュレーション ウィンドウに追加するには、トレースサブメニューから測定値の評価を選択します。

図 5-17. 測定値の評価

トレース式は、直接入力するか、利用可能なオプションから選択するか、または表 5-2 からコピー / ペーストすることができます。

図 5-18. 測定値評価のためのトレース式

測定結果ウィンドウには、図 5-19 で説明した測定結果が表示されます。プロットと測定値を含む出力ウィンドウは、反復処理が実行されるたびに表示されます。

| Evaluate                            | Measurement                                                                                              |                     |

|-------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------|

| <input checked="" type="checkbox"/> | PhaseMargin(DB(V(LOOP,GAIN)),P(V(LOOP,GAIN)))-180                                                        | Phase Margin        |

| <input checked="" type="checkbox"/> | $1/(2\pi \cdot \text{Max}(P(\text{CLOAD})) \cdot \text{XatNthY}(\text{DB}(V(\text{AOL\_LOADED})),0,1))$  | RISO (typical)      |

| <input checked="" type="checkbox"/> | $1/(2\pi \cdot \text{Max}(P(\text{CLOAD})) \cdot \text{XatNthY}(\text{DB}(V(\text{AOL\_LOADED})),20,1))$ | RISO (conservative) |

図 5-19. Pspice®-for-TI シンタックスの式

## 6 まとめ

自動化設計のあらゆる構成要素についてすべて、下記に限定されず、詳細を検討しました。

- 解決すべき問題

- 再利用可能なソリューション

- PSpice-for-TI® プロジェクトの作成方法

- 読みやすさを高めた概略図

- 受動部品の配置

- パラメータの活用

- 電源の配置

- 配線とラベルの方法

- ユーザーエクスペリエンスを考慮した編成

- シミュレーションプロファイルの設定

- 収束を支援

- 強力な後処理

組み立て後、この設計を使用して、複数のデバイスや条件にまたがる問題を迅速に解決できます。本書で説明されている例を実際に示します。

OPAx392 を回路図に配置し、1nF の容量性負荷を駆動します。

図 6-1. OPA392 による 1nF の容量性負荷の駆動補償なし

結果として得られた位相マージンが 16 度であり、これは 45 度から 90 度の間の安定定義から外れています。

| Evaluate                            | Measurement                                              | Value     |

|-------------------------------------|----------------------------------------------------------|-----------|

| <input checked="" type="checkbox"/> | PhaseMargin(DB(V(LOOP,GAIN)),P(V(LOOP,GAIN)))-180        | 16.35200  |

| <input checked="" type="checkbox"/> | 1/(2*pi* Max(P(CLOAD))* XatNthY(DB(V(AOL_LOADED)),0,1))  | 37.92552  |

| <input checked="" type="checkbox"/> | 1/(2*pi* Max(P(CLOAD))* XatNthY(DB(V(AOL_LOADED)),20,1)) | 153.34276 |

図 6-2. 不安定な位相マージンと RISO の推奨値 (標準および保守的)

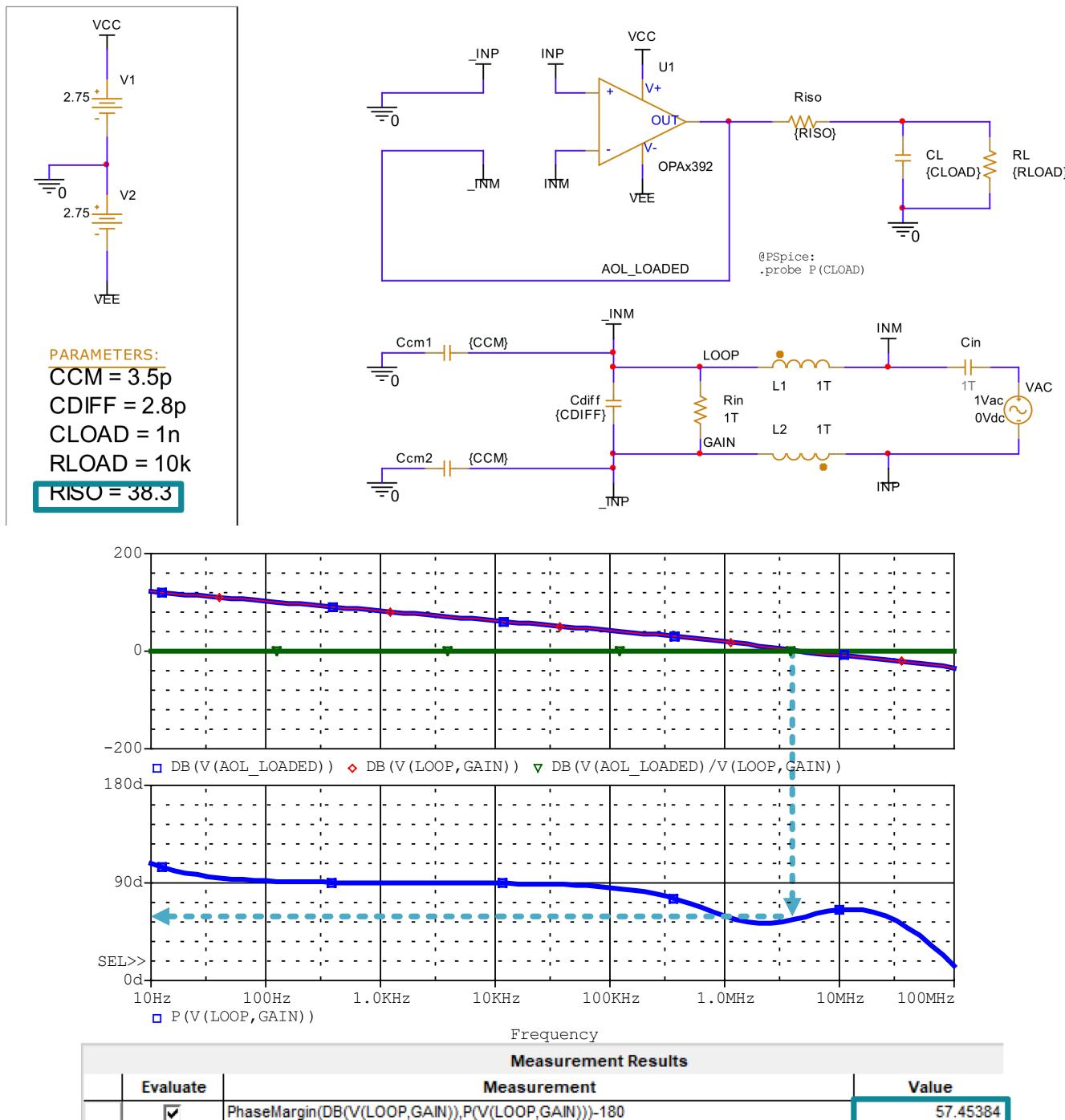

RISO の最小推奨値は 37.9Ω、保守的推奨値は 153.3Ω です。次のシミュレーションでは、RISO として 1% の共通抵抗値である 38.3Ω を使用します。

結果として得られた出力の位相マージンが 57 度であり、これは出力容量性負荷が 38.3Ω の絶縁抵抗によって適切に補償されていることを意味します。

図 6-3. OPA392 による RISO 補償付き 1nF 容量性負荷の駆動

この自動設計は、異なるオペアンプ、異なる容量性負荷、および異なる回路構成に対して繰り返し実行でき、迅速な解決策の実現に役立ちます。このアプリケーションノートで解説されている自動設計例は、こちらからダウンロードできます。

- 0° ~ 60° の安定性の自動化ゲイン 1 (バッファ)

- 0° ~ 60° の安定性の自動化非反転ゲイン

- 0° ~ 60° の安定性の自動化反転ゲイン

- 0° ~ 60° の安定性の自動化差動アンプのゲイン

## 7 参考資料

- テキサス インスツルメンツ、[TINA-TI シミュレーションツール](#)、SPICE ベースのアナログ シミュレーションプログラム。

- [PSPICE-FOR-TI シミュレーションツール](#)、シミュレーションツール。

- プレシジョンラボシリーズ:オペアンプ、ビデオシリーズ。

- 差動アンプのループ遮断、ビデオシリーズ。

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月