## Application Note

非絶縁型ゲートドライバを使用した **SiC MOSFET** の駆動

Rubas Khalid, Sam Wallace, Kevin Ginunas

## 概要

小型フォームファクタでより高い電力密度が求められるようになったことで、シリコンカーバイド (SiC) のようなワイドバンドギャップ半導体技術の普及が進んでいます。これらのスイッチは従来、より大電力 (10kW 超) の設計で使用されてきました。多くの場合、絶縁型ゲートドライバ、特に電気自動車や充電ステーションで使用されていました。SiC テクノロジーがスケール化を継続する中で、低消費電力の非絶縁型アプリケーション向けに SiC テクノロジーを検討する産業用のお客様が増加しています。このアプリケーションノートでは、SiC MOSFET 向けの非絶縁型ローサイド ゲートドライバであるテキサスインスツルメンツ (TI) の製品ラインアップの概要を説明します。適切なシステム設計に関する主な検討事項と、力率補正 (PFC) の設計例も紹介します。

## 目次

|                                       |    |

|---------------------------------------|----|

| 1はじめに.....                            | 2  |

| 2 TI の非絶縁型 SiC MOSFET ゲートドライバの概要..... | 3  |

| 3 SiC MOSFET ゲートドライバ設計の検討事項.....      | 4  |

| 3.1 低電圧誤動作防止 (UVLO).....              | 4  |

| 3.2 負バイアス電源 (バイポーラ駆動).....            | 5  |

| 3.3 短絡保護.....                         | 5  |

| 4 PFC CCM 昇圧ローサイド ゲートドライバの例.....      | 8  |

| 4.1 ゲートドライバの要件.....                   | 9  |

| 4.2 ゲートドライバの選択.....                   | 9  |

| 4.3 ゲートドライバ消費電力.....                  | 10 |

| 5まとめ.....                             | 12 |

| 6参考資料.....                            | 12 |

## 商標

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

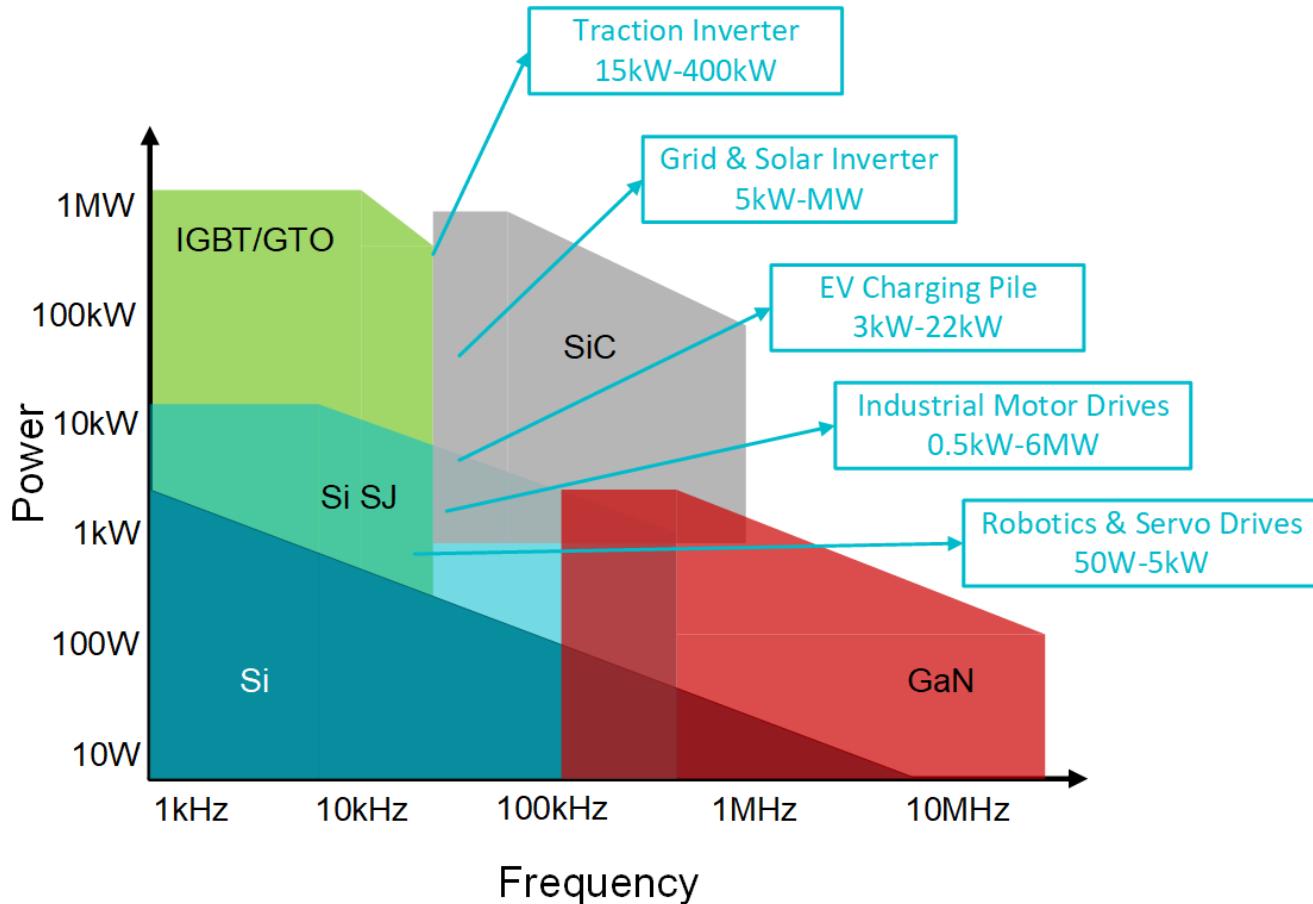

シリコン カーバイド (SiC) パワースイッチは、高スイッチング周波数、高電圧、大電流に対応できることから、産業用途および自動車用途の両方で普及しています。SiC MOSFET の設計は、高周波アプリケーションと大電力アプリケーションの間で適切なバランスを実現します。ゲートドライバは SiC MOSFET を効果的に制御するうえで重要な役割を果たし、SiC MOSFET が安全動作領域内にとどまるかを確認するためには、ゲートドライバのシステム設計を慎重に行うことが不可欠です。

図 1-1. パワースイッチ テクノロジーと一般的なアプリケーション

このアプリケーション ノートでは、テキサス インストゥルメンツの非絶縁ローサイド ゲートドライバ製品について説明し、低電圧ロックアウト (UVLO)、短絡保護、負バイアス供給対応といった機能の設計詳細も含めて解説します。力率補正 (PFC) の連続導通モード (CCM) 昇圧トポロジを目的としたゲートドライバの設計例を提示しています。ゲートドライバの要件は、最大電源電圧 ( $V_{DD}$ ) 定格、ピーク電流能力、UVLO スレッショルド、短絡保護設計、外部ゲート駆動抵抗、消費電力を基準として説明されています。

## 2 TI の非絶縁型 SiC MOSFET ゲートドライバの概要

TI の最新ローサイド ゲートドライバである UCC5710X、UCC5713x、UCC5714x は、TI の非絶縁ドライバとして初めて短絡保護機能を内蔵しています。UCC5710x は DESAT 保護を備えており、UCC5713x は正方向、UCC5714x は負方向の過電流保護 (OCP) をそれぞれ備えています。これらの短絡保護方式は同じ目標を達成していますが、それぞれの方法には次のような利点があります: OCP はカスタマイズ性に優れた実装がよりシンプルですが、DESAT は電力を消費する検出抵抗がないため、本質的に効率的です。

また、UCC5710X、UCC5713x、UCC5714x には追加機能もあり、SiC MOSFET の駆動に適しています。これには、システムの立ち上げ時や電源障害時にスイッチの損傷や電力損失を防ぐための高 UVLO オプション、誤動作オンを防ぐために電源スイッチのゲートを -15V まで保持できる負のバイアス供給機能、そして過温状態が検出された際にドライバをオフにするサーマルシャットダウン機能が含まれます。これらの機能に加えて、負の IN 電圧対応や短い伝搬遅延により、UCC5170x、UCC5713x、UCC5714x は SiC MOSFET を使用するシステムにおいて堅牢で効率的なドライバとなります。表 2-1 に、これらのドライバの詳細な仕様を示します。

**表 2-1. 非絶縁型ローサイド SiC MOSFET ゲートドライバ**

| パラメータ                                   |                                                                          | UCC27614      | UCC27531      | UCC5710x       | UCC5713x / UCC5714x |

|-----------------------------------------|--------------------------------------------------------------------------|---------------|---------------|----------------|---------------------|

| 保護機能                                    | 内蔵保護                                                                     | なし            | なし            | DESAT (脱飽和)    | OCP                 |

| 絶対最大定格                                  | 電源電圧、V <sub>DD</sub>                                                     | 30V           | 35V           | 30V            | 30V                 |

| 推奨動作条件                                  | 電源電圧、V <sub>DD</sub>                                                     | 26V           | 32V           | 26V            | 26V                 |

|                                         | 入力電圧: IN <sub>A</sub> 、IN <sub>B</sub> 、EN <sub>A</sub> 、EN <sub>B</sub> | -10~26V       | -5~25V        | -5~26V         | -5~26V              |

|                                         | 負電源電圧、V <sub>EE</sub>                                                    | 該当なし          | 該当なし          | -15V (B バリアント) | -15V (B バリアント)      |

|                                         | 動作時の接合部温度範囲                                                              | -40°C ~ 150°C | -40°C ~ 150°C | -40°C ~ 150°C  | -40°C ~ 150°C       |

|                                         | UVLO                                                                     | 電源開始スレッショルド   | 4.1V          | 8.9V           | 8.0V/13.5V          |

| 出力                                      | シンク / ソース ピーク電流                                                          | 10A / 10A     | 2.5A / 5A     | 3A / 3A        | 3A / 3A             |

| スイッチング特性<br>(C <sub>Load</sub> = 1.8nF) | 立ち上がり時間、t <sub>R</sub><br>(10% ~ 90%) 立ち下がり時間、t <sub>F</sub> (90% ~ 10%) | 5ns、4ns       | 15ns、7ns      | 8ns、14ns       | 8ns、14ns            |

|                                         | 入力から出力までの伝搬遅延                                                            | 17ns          | 17ns          | 26ns           | 26ns                |

| 追加機能                                    | イネーブル                                                                    | あり            | あり            | W バリアント        | あり                  |

|                                         | 分割出力                                                                     | なし            | あり            | C バリアント        | C バリアント             |

|                                         | ソフトターンオフ                                                                 | なし            | なし            | あり             | なし                  |

### 3 SiC MOSFET ゲートドライバ設計の検討事項

SiC MOSFET は高出力システムで使用され、主に 50kHz を超える高スイッチング周波数を用いるアプリケーションに実装されています。適切で効率的な SiC MOSFET 動作を検証するには、ゲートドライバの設計に関するいくつかの検討事項が必要です。このセクションでは、SiC MOSFET ゲートドライバの最も重要な考慮事項について説明します。

#### 3.1 低電圧誤動作防止 (UVLO)

UVLO はゲートドライバの重要な機能で、バイアス供給電圧が規定値未満になった場合にゲートドライバ出力をオフにすることで、SiC MOSFET を保護します。UVLO なしのゲートドライバのバイアス電源電圧がより低い電圧まで低下した場合、ゲートドライバは SiC MOSFET ゲートソース電圧 ( $V_{GS}$ ) ターンオン レッショルドに達する可能性がある電圧を出力しますが、SiC MOSFET が完全にオンにならないため、大きな導通損失が発生します。

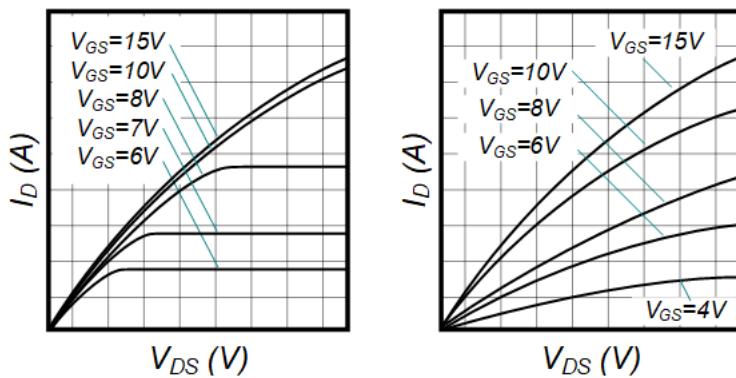

この導通損失は、 $V_{GS}$  に対する SiC MOSFET のドレイン電流 ( $I_D$ ) とドレインソース間電圧 ( $V_{DS}$ ) の I-V 曲線の関係で示すことができます。 $V_{GS}$  が低いと、SiC MOSFET がより早く飽和し、ドレインソース間オン抵抗 ( $R_{DS(on)}$ ) が大きいため MOSFET が完全にオンになることを防止できます。

図 3-1 に、Si MOSFET と SiC MOSFET の標準的な I-V 曲線を示します。 $V_{GS}$  が低い場合は、MOSFET はより速く飽和します。Si MOSFET と SiC MOSFET のどちらも、 $V_{GS} < 10V$  の各曲線には大きなマージンがあり、MOSFET が完全にオンにならないことを示しています。 $V_{GS}$  が小さいと、 $R_{DS(on)}$  が大きくなるため、導通損失が大きくなります。

ただし、 $V_{GS} \geq 10V$  の場合、Si MOSFET と SiC MOSFET の差はより明らかです。Si MOSFET の場合、 $V_{GS} = 10V$ 、 $V_{GS} = 15V$  の曲線はほぼ同じであり、Si MOSFET が  $V_{GS} = 10V$  で完全にオンになっていることを示しています。Si MOSFET の  $V_{GS}$  を 10V を超えて大きくしても、導通損失を低減する効果は最小限です。SiC MOSFET の場合、 $V_{GS} = 10V$  および  $V_{GS} = 15V$  の曲線の間には依然として大きなマージンがあり、対応する Si MOSFET のように  $V_{GS} = 10V$  で SiC MOSFET が完全にオンにならないことを示しています。SiC MOSFET を  $V_{GS} = 10V$  で動作させると、 $V_{GS} = 15V$  での動作に比べて、導通損失が大きくなります。

そのため、バイアス電源のスタートアップまたはシャットダウン時の導通損失を最小限に抑えるために、多くの場合、SiC MOSFET には高い UVLO が求められます。

図 3-1. Si MOSFET の I-V 特性 (左) と SiC MOSFET の I-V 特性 (右)

### 3.2 負バイアス電源 (バイポーラ駆動)

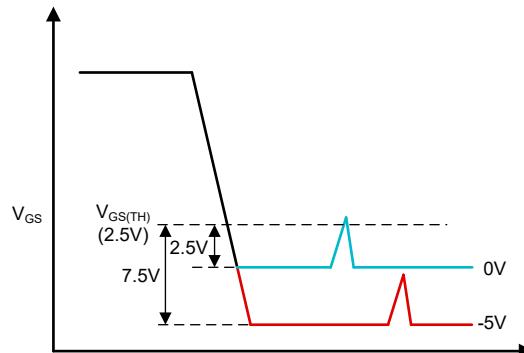

負バイアス電源は、SiC MOSFET を駆動するためのもう 1 つの一般的な要件です。大電力アプリケーションでは、高い  $dv/dt$  が発生し、SiC MOSFET のミラー容量を介して電流が誘導され、SiC MOSFET のゲートが充電される可能性があります。SiC MOSFET が誤ってオンになると、破壊的な結果を招く可能性があります。負のバイアス電圧を使用して、スパイクがターンオン スレッショルドに達しないようにすることで、SiC MOSFET がオフに維持されるようにします (バイポーラ駆動とも呼ばれます)。図 3-2 は、過渡 2.5V スパイクが 2.5V のゲートソーススレッショルドで SiC MOSFET に与える影響を示しています。0V のターンオフを使用すると、誤ってターンオンが発生します。また、-5V ターンオフを使用すると、SiC MOSFET がオフのままであることを確認できます。

図 3-2. ターンオフ レベルの比較

### 3.3 短絡保護

大電力アプリケーションでは短絡が発生するリスクが高く、SiC MOSFET やシステム内の他の部品に深刻な損傷を与える可能性があります。短絡による損傷を軽減するために、高速検出と誤動作の抑制を備えたさまざまな短絡保護方式を実装できます。

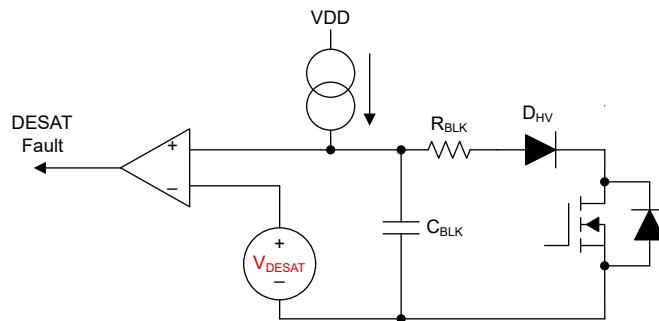

#### 3.3.1 脱饱和保護

脱饱和 (DESAT) 保護機能は、電圧に基づく短絡保護の一種です。代表的な DESAT 回路を 図 3-3 に示します。

通常動作時に SiC MOSFET がオンのとき、 $I_D$  は仕様範囲内になり、ドレイン電圧を低く維持します ( $V_{DS} = I_D \times R_{DS(on)}$ )。これにより、高電圧ブロッキングダイオード ( $D_{HV}$ ) が順バイアスされ、 $I_{CHG}$  ( $V_{DD}$  の下矢印で図に示す) から供給される電流が、ブランкиングコンデンサ ( $C_{BLK}$ ) を充電せずに  $D_{HV}$  を流れるようになります。

短絡が発生すると、 $I_D$  が大きいと、ドレイン電圧は high に上昇します。これにより、 $D_{HV}$  が逆バイアスされ、 $I_{CHG}$  から供給される電流の流れがブロックされます。ここで、充電電流が  $C_{BLK}$  を充電し、 $C_{BLK}$  電圧が内部 DESAT 電圧スレッショルド ( $V_{DESAT}$ ) を超えると、コンパレータは短絡が検出されたことを示します。

コンデンサを充電する時間はブランкиング時間です。この時間は、内部の  $V_{DESAT}$  および  $I_{CHG}$  を使用して式 1 で計算できます。コンデンサの値を小さくすると、DESAT 保護をトリガするまでの時間が短縮できるため、SiC MOSFET アプリケーションに役立ちます。

$$t_{BLK} = \frac{V_{DESAT} \times C_{BLK}}{I_{CHG}} \quad (1)$$

内部  $V_{DESAT}$  は設計上設定されていますが、DESAT 保護をトリガするために必要なドレイン電圧は、DESAT ピンと SiC MOSFET ドレインの間の直列の部品を変更することで調整できます。これは、式 2 で計算できます。 $V_{DESAT(actual)}$  とは、DESAT をトリガするドレイン電圧を指します。

$$V_{DESAT(actual)} = V_{DESAT} - (I_{CHG} \times R_{BLK}) - V_{F(D_{HV})} \quad (2)$$

図 3-3. DESAT 保護回路

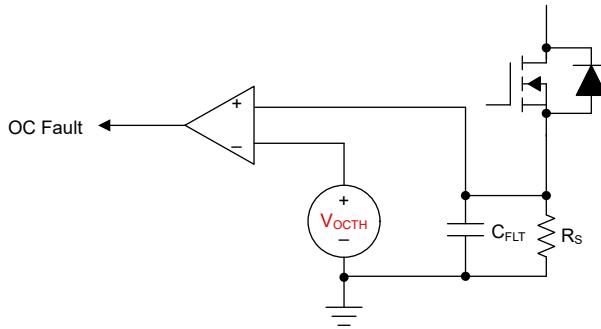

### 3.3.2 過電流保護

過電流保護 (OCP) は、電流をベースにした短絡保護のもう 1 つのタイプです。図 3-4 に、OCP 回路を示します。 $I_D$  の測定にシャント抵抗を使用すると、シャント電圧が得られます。短絡が発生すると、 $I_D$  が大きいとシャント電圧は high に上昇します。シャント電圧が OCP 電圧スレッショルドを上回ると、コンパレータは短絡が検出されたことを示します。

シャント抵抗値は、OCP をトリガるために必要なドレン電流 (通常、SiC MOSFET が処理可能な最大ドレン電流よりわずか小さい) に基づいて選択されます。これは式 3 で計算できます。

$$R_S = V_{OCTH} / I_{D(OC)} \quad (3)$$

図 3-4. OCP 回路

### 3.3.3 ソフト ターンオフ

短絡イベントが検出された後、システムの損傷を最小限に抑えるために、SiC MOSFET を安全にオフにする必要があります。

寄生インダクタンスは、高速  $I_D$  スイッチングと相互作用し、電圧を誘導できます ( $V = L \times \frac{di}{dt}$ ) 両端間で SiC MOSFET を経由します。 $I_D$  が定格制限内の公称イベントでは、通常のターンオフを使用することにより、SiC MOSFET の制限内の電圧が誘導されます。ただし、短絡現象の間、誘導された電圧は致命的なレベルに達し、SiC MOSFET の破損につながる可能性があります。

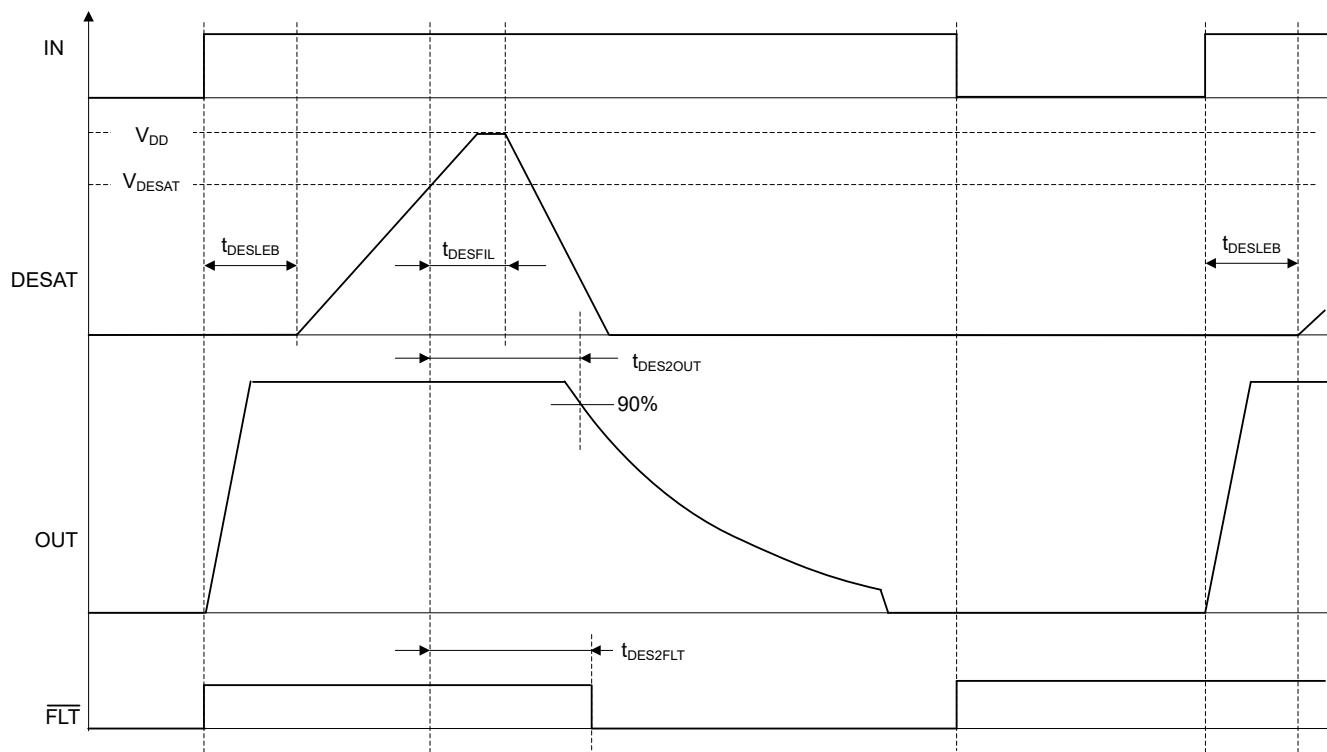

ソフト ターンオフとは、ターンオフ時間を長くする設計であり、SiC MOSFET をオフにする際のスイッチング速度が低下します。これにより、 $di/dt$  が減少し、誘導電圧が最小化されます。図 3-5 に、UCC5710x の DESAT 保護により短絡が検出されたときに、OUT がゆっくりとオフになることを示しています。DESAT 保護に関する概念的なタイミング特性として、 $t_{DESLEB}$  (SiC MOSFET のターンオン過渡による誤動作トリガを防ぐリーディング エッジ ブランкиング時間)、 $t_{DESFIL}$  (SiC MOSFET がオンのときに、ノイズによる誤トリガを防ぐためのデグリッチ フィルタ時間)、 $t_{DES2OUT}$  (DESAT スレッショルド到達から OUT が 90% まで低下するまでの時間)、および  $t_{DES2FLT}$  (スレッショルド到達から  $\overline{FLT}$  が低下するまでの時間) が図に示されています。

図 3-5. ソフト ターンオフ

#### 4 PFC CCM 昇圧ローサイド ゲートドライバの例

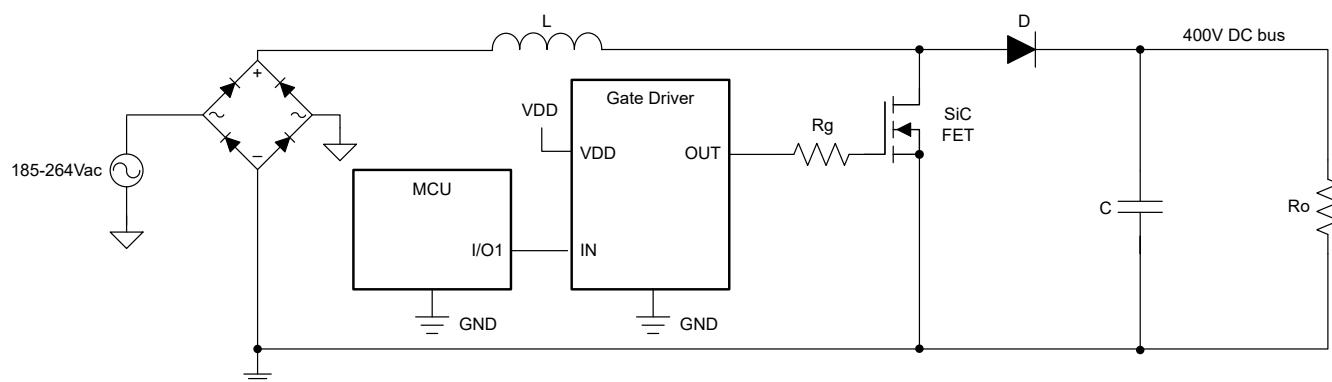

力率補正 (PFC) 連続導通モード (CCM) 昇圧アプリケーションでは、SiC MOSFET に大きな利点があります。SiC MOSFET の導通損失とスイッチング損失が小さいため、1kW を超えるアプリケーションで効率が向上し、電力密度が向上します。SiC テクノロジーを使用すると、より高いスイッチング周波数を実現でき、磁気素子のサイズとコスト削減の機会に寄与します。この例では、3kW PFC CCM 昇圧に関するローサイド ゲートドライバの考慮事項の概要をこのアプリケーション ノートで説明しています。目標設計パラメータを [表 4-1](#) に示します。

表 4-1. 設計パラメータ

| 設計パラメータ             | 数値の例            |

|---------------------|-----------------|

| PFC の入力電圧範囲         | 185-265Vac、60Hz |

| PFC 公称出力電圧          | 400VDC          |

| 最大定常状態出力電力          | 3000W           |

| SiC MOSFET の正バイアス電源 | +20V            |

| SiC MOSFET の負バイアス電源 | -5V             |

| スイッチング周波数           | 60kHz           |

| 切り替え可能なスルーレート       | 20V/ns          |

| 短絡の検出               | あり              |

| 最大周囲温度              | 100°C           |

この例では、選択した SiC MOSFET の定格は次のようにになります: 最大 650V の  $V_{DS}$ 、35A の連続  $I_D$  定格 ( $T_c = 100^\circ\text{C}$  時)、合計  $Q_G$  は 73nC、 $V_{GS} = 20\text{V}$  時の 45mΩ 標準  $R_{DS(\text{on})}$ 。図 4-1 に、一般的な PFC CCM 昇圧アプリケーションに必要な部品を示します。

図 4-1. PFC システムにおけるゲートドライバの代表的なアプリケーション

## 4.1 ゲートドライバの要件

SiC MOSFET 用に適切なゲートドライバを選定する際には、バイアス電圧定格、ピーク電流能力、保護機能、ゲート抵抗、電力損失を慎重に考慮する必要があります。

導通損失を最小化するため、バイアス電圧は 20V に設定し、過渡現象による誤動作オンを防ぐために -5V の負バイアスを設定します。電位差から、ゲートドライバの  $V_{DD}$  要件は 25V 以上になります。

スイッチング損失を最小化するためには、ゲートドライバが目標とするスイッチング速度を達成できるよう、必要なピーク電流を供給することも求められます。スイッチング速度のシステム要件は一般に、スルーレートの観点から記述されます。この例の PFC における要件では、SiC MOSFET は DC バス電圧 400V の下で 20V/ns 以上のスルーレートでターンオンする必要があります。これは、SiC MOSFET のターンオン時の  $V_{DS}$  全体のスイングが 20ns ( $= 400V / 20 \frac{V}{ns}$ ) またはそれ以下。 $V_{DS}$  のスイング中は、SiC MOSFET のミラー電荷 ( $Q_{GD}$  パラメータ、選択した SiC MOSFET の場合 27nC) がゲートドライバのピーク電流によって充電され、ピーク電流は  $Q_{GD}$  を 20ns 以内に充電する必要があります。これにより、必要なピーク電流は 1.35A 以上となります ( $= 27nC / 20ns$ )。

UVLO は、電源障害時に SiC MOSFET への損傷を最小限に抑えるための重要な保護機能です。故障によって  $V_{GS}$  が安全でないレベルに低下すると、SiC MOSFET の導通損失が発生する可能性があります。これにより、SiC MOSFET の効率の低下、発熱の増加、寿命の短縮が可能です。このアプリケーションでは、UVLO 定格が高いゲートドライバが有益です。

SiC MOSFET のもう 1 つの重要な保護機能は、短絡検出の形式を使用することです。SiC MOSFET は、IGBT における飽和領域からアクティブ領域への遷移のように、線形領域から飽和領域への明確な遷移がないため、DESAT 保護のような単一電圧しきい値検出を用いる場合、大幅な改良を行わない限り正確性を確保できません。OCP はより推奨される選択肢であり、シャント抵抗を使用して電流を測定します。

## 4.2 ゲートドライバの選択

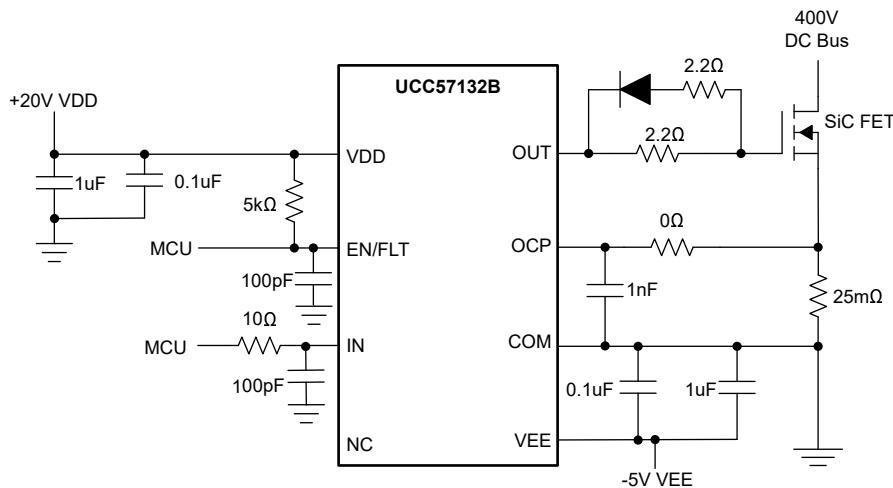

このアプリケーションには UCC57132B を使用することが推奨されます。UCC57132B は、30V ローサイド ゲートドライバで、3A のソース/シンク ピーク電流、OCP、および故障報告機能を備えています。UCC57132B は、負のバイアス入力にも対応し、OCP を故障表示付きで検出でき、典型値 13.5V の高い UVLO スレッショルドを備えています。

UCC57132B をシステムに組み込む際には、バイアス供給用のバイパスコンデンサが重要な部品であることに注意する必要があります。これらのバイパスコンデンサは、ノイズ耐性を高めるために、UCC57132B の VDD/VEE ピンおよび GND ピンにできるだけ近く配置する必要があります。TI は、少なくとも 2 つのバイパスコンデンサを並列に配置することを推奨しています。1 つ目は 0.1 $\mu$ F、2 つ目は 1 $\mu$ F 以上とし、0.1 $\mu$ F のコンデンサを大きいコンデンサより IC に近く配置する必要があります。入力 PWM 信号のノイズ耐性を高めるために、IN ピンに小容量のバイパスコンデンサや RC フィルタを追加することが有効です。

OCP ピンのスレッショルドは 500mV で、このスレッショルドを使用してシャント抵抗値を計算できます。SiC MOSFET の最大連続  $I_D$  定格は、 $T_c = 100C = 35A$  で、マージンを確保する余地があります。シャント抵抗は 25m $\Omega$  と計算できます ( $= 500mV / 20A$ )。OCP ピンの近くに小さな RC フィルタを追加すると、OCP が誤ってトリガされるノイズを低減できます。

故障信号の復帰時間は、EN/FLT ピンの RC フィルタを使用して 式 4 に従って計算されます。 $R_{ENU}$  は、EN/FLT ピンの内部プルアップ抵抗、 $V_{ENH}$  はイネーブル信号の立ち上がりスレッショルドを示します。どちらの値も、UCC57132B データシート ( $R_{ENU} = 2M\Omega$  および  $V_{ENH} = 2.2V$ ) に記載されています。 $R_{FLTC} = 5k\Omega$  および  $C_{FLTC} = 100pF$  を使用すると、故障復帰時間は  $t_{FLTC} = 58ns$  で計算できます。

$$t_{FLTC} = - \left( \frac{R_{FLTC} \times R_{ENU}}{R_{FLTC} + R_{ENU}} \right) \times C_{FLTC} \times \ln \left( 1 - \frac{V_{ENH}}{V_{DD}} \right) \quad (4)$$

外部ゲート抵抗を追加するには、いくつかの利点があります。ゲート抵抗は、出力のターンオンおよびターンオフ時間を制限して EMI を低減するとともに、ゲートチャージに関連する一部の消費電力を吸収します。UCC57132B にはターンオン時間とターンオフ時間を個別に制御する分割出力機能はありませんが、ブロッキングダイオードを使用することで分割出力を擬似的に実現できます。ゲート抵抗の選定にはベンチテストでの実験が必要ですが、出発点としてはターンオンに

2.2Ω、ターンオフに 1.1Ω が適しています (ブロッキング ダイオード使用時は、2.2Ω の抵抗を 2 つ並列にして有効にします)。

UCC57132B の設計パラメータを、図 4-2 に示します。部品の値を検証するためには慎重なテストが必要であり、それに応じて調整が求められる場合があります。

図 4-2. 設計値を用いた UCC57132B

#### 4.3 ゲートドライバ消費電力

選択したゲートドライバの消費電力が仕様範囲内であるかどうかを確認します。ローサイド ゲートドライバの合計消費電力 ( $P_{tot}$ ) は、次の 2 つの部分に分類できます: DC 損失およびスイッチング損失。DC 損失 ( $P_{DC}$ ) は、内部回路のバイアスとして消費されるゲートドライバの静止電流の関数です。スイッチング損失 ( $P_{SW}$ ) は、ゲート電荷、バイアス電圧、スイッチング周波数、パワー スイッチの内部 / 外部ゲート抵抗に依存します。

ゲートドライバのデータシートに記載される熱仕様と推定周囲温度を使用して、ゲートドライバの最大許容消費電力 ( $P_{max}$ ) を推定できます。ゲートドライバを確実に仕様内に収まるように、 $P_{max}$  を計算した  $P_{tot}$  と比較できます。式 5 と式 6 に、UCC57132B の最大消費電力を推定します。

$$P_{max} = \frac{T_J - T_A}{R_{\theta JA}} \quad (5)$$

$$P_{max} = \frac{150^{\circ}C - 100^{\circ}C}{126.6 \frac{{}^{\circ}C}{W}} = 395mW \quad (6)$$

UCC57132B の最大 VDD 静止電流は 1.3mA、最大 VEE 静止電流は 1.1mA です。20V の VDD 電源と -5V VEE 電源では、DC 損失は 31.5mW になります ( $= (1.3mA \times 20V) + (-1.1mA \times -5V)$ )。

スイッチング損失は、式 7 および式 8 を使って推定できます。 $R_{OH\ (eff)}$  は出力ターンオン時の出力構造の有効プルアップ抵抗 (1Ω) を示しており、これは UCC57132B の出力ステージが持つハイブリッド プルアップ構造 (プルアップ NMOS とプルアップ PMOS が並列に配置されている) によるものです。これは、データシートの  $R_{OH}$  パラメータとは異なります。これはプルアップ PMOS のみを表します (過大評価が必要な場合、 $R_{OH\ (eff)}$  ではなく  $R_{OH}$  を使用することは問題ありません)。 $R_{OL}$  は標準的なプルダウン NMOS を指し、データシート (1Ω) に記載されています。 $R_{GATE\ (H)}$  はターンオンの外部ゲート抵抗、 $R_{GATE\ (L)}$  はターンオフの外部ゲート抵抗を表します。 $R_{GATE\ (I)}$  は、選択した SiC MOSFET の固有ゲート抵抗 (2Ω) を表します。

$$P_{SW} = Q_g \times (V_{DD} - V_{EE}) \times f_{sw} \times \frac{1}{2} \left( \frac{R_{OH\ (eff)}}{R_{OH\ (eff)} + R_{GATE\ (H)} + R_{GATE\ (I)}} + \frac{R_{OL}}{R_{OL} + R_{GATE\ (L)} + R_{GATE\ (I)}} \right) \quad (7)$$

$$P_{SW} = 73nC \times (20V - (-5V)) \times 60kHz \times \frac{1}{2} \left( \frac{1\Omega}{1\Omega + 2.2\Omega + 2\Omega} + \frac{1\Omega}{1\Omega + 1.1\Omega + 2\Omega} \right) = 23.9mW \quad (8)$$

パッケージで消費される総電力の推定値は、式 9 と式 10 で計算されます。

$$P_{tot} = P_{DC} + P_{SW} \quad (9)$$

$$P_{tot} = 31.5mW + 23.9mW = 55.4mW \quad (10)$$

初期設計の目的で、計算された  $P_{tot}$  は UCC57132B の推定  $P_{max}$  よりもはるかに小さくなり、デバイスを仕様内に維持しています。適切な冷却を確認するには、設計フェーズ全体を通してさらに熱解析を完了する必要があります。熱解析の詳細については、[半導体およびICパッケージの熱評価基準](#) アプリケーションノートを参照してください。

## 5 まとめ

このアプリケーションノートでは、テキサス インスツルメンツ (TI) のシリコン カーバイド (SiC) スイッチ向け非絶縁ローサイド ゲート ドライバ設計について説明します。TI のゲート ドライバは、必要な保護機能を備えて SiC パワー スイッチを制御でき、産業用および自動車用システムにおいて高電力密度かつ小型フォーム ファクタの設計を可能にします。

## 6 参考資料

- テキサス インスツルメンツ、『シリコンカーバイド MOSFET の短絡保護について』、アプリケーションノート。

- テキサス インスツルメンツ、『安全な IGBT および SiC MOSFET パワー スイッチ動作に高 UVLO が重要な理由』アプリケーションノート。

- テキサス インスツルメンツ、『ゲート ドライバ用の外部ゲート抵抗設計ガイド』アプリケーションノート。

- テキサス インスツルメンツ、ローサイド ゲート ドライバ(バイポーラ駆動)を使用し、負バイアスを使用して SiC FET または IGBT を駆動する方法、E2E™ 設計サポート フォーラム。

- テキサス インスツルメンツ、『SiC ゲート ドライバの基礎』、電子書籍。

- テキサス インスツルメンツ、『ゲート ドライバの電力損失と熱に関する考慮事項』、ビデオ。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月