## Application Brief

## DLP® テクノロジーを活用してパネル レベルの先進的なパッケージングを実現する方法

Karina Bridger

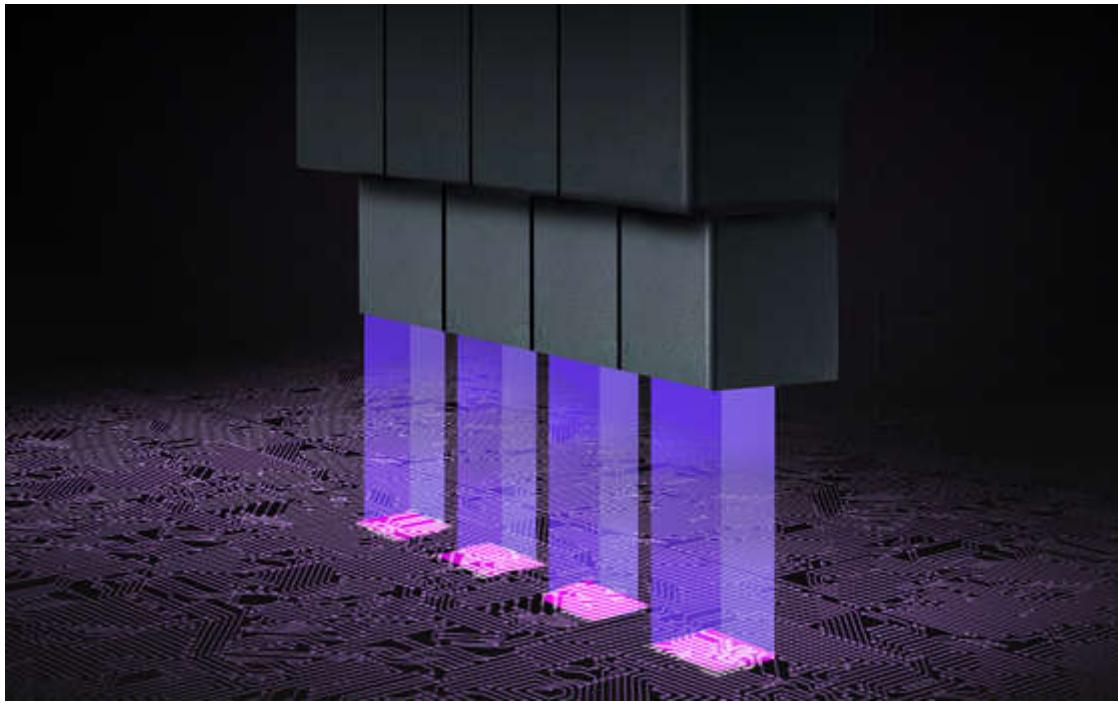

DLP® テクノロジーは、単にプロジェクター向けの業界最先端のディスプレイ技術にとどまりません。鮮明で没入感のある投影を可能にする同じ技術は、先進的なパッケージやパネル レベル パッケージの製造に用いられるデジタル イメージング システム向けのプログラム可能なフォトマスクとしても利用できます。このアプリケーション ブリーフでは、先進パッケージの動向と、DLP テクノロジーがこの製造プロセスの可能性をいかに引き出すかについて説明します。図 1 に、DLP デジタル マイクロミラー デバイス (DMD) によるマスクレス フォトリソグラフィーのレンダリングを示します。

図 1. DLP DMD を使用するマスクレス フォトリソグラフィー

## 高度なパッケージとは？

先進的なパッケージは、新たに登場した製造手法であり、複数の半導体コンポーネントを高密度相互接続で 1 つのパッケージに組み合わせて統合することで、従来のパッケージと比べて性能、電力効率、機能性を向上させます。基本的に、これは複数のダイを内蔵している個別の半導体パッケージを指します。

直接的な比較ではありませんが、先進的なパッケージは、接続、保護、統合を目的として設計された、マイクロン スケールの半導体グレード版 PCB の後継技術と見ることができます。これは同じ原理で動作しますが、チップ スケールにまで縮小されて半導体のパッケージングに使用され、半導体設計者が従来の PCB の制約を克服するのに役立ちます。

PCB は、配線や部品の実装用のシンプルな基板として始まりました。時間の経過とともに、これらの基板はより複雑な電子回路を扱えるよう進化し、層の追加、より細かい配線、ビア、高度な材料が導入されました。この過程を経て、PCB の製造は適応、小型化、高度化され、IC 基板、高密度相互接続 (HDI)、および信号の経路変更に使用される再配線層

(RDL) が生み出されました。そこから技術はさらに小型化と特化を続け、最終的に現在の 3D 先進パッケージへと進化しました。

先進パッケージを用いることで、半導体設計者はより効率的に設計を行い、コストを削減し、相互接続密度を高め、最適な構造を設計できます。このアプローチにより、消費電力を抑えながらシステムの帯域幅を拡大でき、各アプリケーションに合わせた多様な設計が可能になります。先進的なパッケージの可能性が拡大する中で、装置メーカーはこれらのパッケージをより容易に作成する方法を模索しています。DLP テクノロジーを採用すると、従来の障壁を克服できます。

## DMD をフォトリソグラフィーに使用

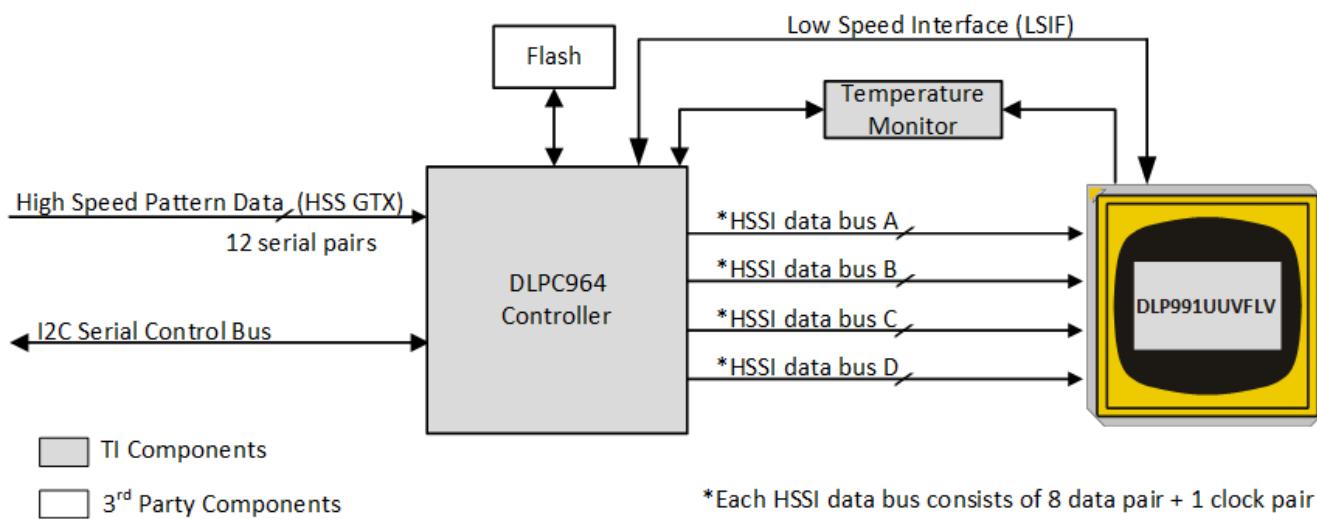

一般的には、[DLP991UUUV \(図 2\)](#) などの DMD は、数百万個の個別にアドレス指定可能なマイクロミラー (ピクセル) で構成されたマイクロ電気機械システム (MEMS) ベースの空間光変調器です。これらの DMD は、343nm から 2500nm までの広い波長範囲と、対角 0.1 インチから 0.99 インチまでのサイズにわたり、ピクセル単位の正確な制御を提供し、システム設計に柔軟性をもたらします。設計者は、これらのデバイスを 3D プリンタや歯科用スキャナからマシンのビジョンやマスクレス露光システムに至るまで、さまざまな産業用途で使用できます。

図 2. DLP991UUUV DMD を採用した概略ブロック図

DMD は、当初、先進パッケージ製造へと用途が拡大する前は、PCB を印刷するためのフォトリソグラフィシステムで使用されていました。プログラム可能なフォトマスクとして機能するこれらの DMD は、物理的なフォトマスクを使用することなく、配線、ビア、半田マスクといったパターンを印刷するために使用されます。PCB は一般的に、有機積層基板と、相互接続用の金属層 (多くの場合は銅) で構成されています。パターンや特長をプリントするために、銅層にフォトレジストを塗布し、ステージ上で位置合わせを行います。その後、フォトリソグラフィ手法を用いてフォトレジストにパターンを印刷し、レジストを現像し、不要な金属レジストを除去することで、回路パターンが形成されます。

DLP テクノロジーを用いたシステムはフォトリソグラフィ工程に用いられ、UV 光を使用してフォトレジストにパターンを印刷します。このステップでは、従来のマスクベースシステムとマスクレスシステムの 2 つの主要なテクノロジーについて説明します。

- マスクベースのシステム:** マスク方式のシステムは、レチクルとも呼ばれるフォトマスクに依存して回路パターンを転写します。これらのマスクは通常、ガラスまたは石英で作られ、特定の材料でコーティングされています。これらの材料は光の透過を遮断し、コーティングされていない部分は透明なままで光を通過させます。UV 光をマスクに照射すると、透過した光がフォトレジストに当たり、マスクで形成されたパターンが硬化します。この技術の課題の一つは、マスク自体ではパターンを変更できず、印刷するパターンを変えるには新しいマスクを作成する必要があることです。

- マスクレスシステム:** マスクレス方式のシステムは、パターンを転写するのに物理的なマスクに依存しません。1 つの方法として、DLP テクノロジーをプログラム可能なフォトマスクとして使用する方法があります。このマスクレス方式では、UV 光を DMD に照射し、DMD 内のマイクロミラーがオンまたはオフに傾くことで光を変調し、PCB のフォトレジスト上に投影されるパターンを生成します。通常、多数の光パルスが DMD に投影され、ミラーが反転しながら、モジュール全体が表面を走査します。光の各パルスが材料を硬化させ、所望のパターンを形成します。これにより、パターンはパ

ルスごとに変更可能となり、反りなどの要因にも対応できます。レジストに投影されるパターンを動的に調整することで、新しいマスクを作成する代わりに、修正されたソフトウェア ファイルや帰還ループを用いてパターンを変更できます。

DLP テクノロジーを使用すると、いつでもデジタル設計を変更し、高いスループットを維持しながら、必要なプリント形状サイズを満たすことができます。また、DMD ベースのシステムは、マスク製造、マスク在庫管理、マスクの再設計など、マスクに関連する費用を削減します。

## 先進的なパッケージングに適した DLP 技術

PCB は、個別の部品やパッケージ化されたチップ間で基板レベルの支持と電気的接続を提供し、比較的広い領域に中程度の密度で信号を配線します。ただし、これらの PCB には配置や形状サイズなど多くのルールがあり、I/O が制限されます。このため、個々のダイを接続して配線する際には、それらの制約を克服する手段として基板やインターポーラが有用となります。先進的なパッケージ基板は、細ピッチのチップ パッドから大きなパッケージ ピンやボールへ信号を分配することで、パッケージ レベルでの I/O 密度を高めます。複数の層により、コンパクトなフットプリントでより多くの接続が可能となり、1 つのパッケージ上に多数のダイを統合することができるようになります。インターポーラは、ダイの間に直接より細かいピッチを提供することで、より高い I/O 密度を実現します。基板やインターポーラを使用することで従来の PCB の制約を回避でき、各ダイに個別のパッケージを用いた場合の PCB と比べて、最終的なサイズをより小さく抑えることが可能になります。これにより、接続が短くなり、PCB への接続数が減少するため、性能と効率が向上します。基本的に、PCB に直接配線するとサイズが大きくなるという問題を克服するために、インターポーラや基板が仲介役として使用されます。DMD は、PCB を印刷するのと同じ方法で、これらの基板やインターポーラ上にパターンを印刷するために使用できます。

ほとんどの基板材料は PCB にも類似し、誘電体と金属の層が交互に配置されています。インターポーラは、一般的に有機材料、ガラス、シリコンの 3 種類の材料に分類されます。DLP テクノロジーを用いたシステムは、特にパネル レベルへ拡張する際に、有機材料とガラスに重点を置くのが一般的です。パネルは、製造効率の向上、取り扱いミスや工具コストの削減、高スループットの実現に役立ちます。パネル レベルの製造は、より多くのトランジスタを 1 つのパッケージに統合することで、面積効率の向上、スケーラビリティ、および柔軟性を実現します。

フォトマスクを使用せずに基板へ直接投影することで、DLP テクノロジーを用いたシステムは、マスク方式のシステムをスケーリングする際によくあるステッピング誤差を最小限に抑えつつ、パネル サイズへの柔軟性とスケーラビリティを高めることができます。DMD ベースのシステムでは、パネル サイズに制限がなく、リアルタイム補正によって反りを考慮することができます。ほとんどの最新 PCB はパネル レベルでプリントされており、これが、DLP テクノロジーを用いた PCB 印刷から、先進的なパッケージ向けの基板、インターポーラ、RDL をパネル レベルで印刷するという自然な進展をさらに裏付けています。

より高い I/O 密度への需要が高まり、先進的なパッケージやパネル レベル パッケージでの層数が増加し続ける中、DLP テクノロジーを搭載したシステムは、高精度かつ高スループットでスケーラビリティの要件を満たしつつ、誤差の蓄積を低減することでシステム メーカーを支援しています。

**DLP991UV** DMD は、先進的なパッケージ市場をサポートするように設計されています。この DMD は最大 110Gbps の高データレートを提供し、最大の露光速度と 1 時間あたりのパネル数でリアルタイム補正を可能にします。

**DLP991UV** は 5.4 $\mu$ m のマイクロミラー ピッチを採用し、対角 0.99 インチのパッケージに 890 万個のマイクロミラーを搭載しています。DLP 製品群の中で最高の解像度を持つこれらのデバイスは、最大限のスループットと露光面積の拡大を可能にしつつ、パターン寸法を縮小して 1 $\mu$ m L/S を実現します。343nm まで規定されているため、**DLP991UV** は G ラインおよび I ライン ツールで使用でき、複数の波長をカスタマイズしてフォトレジスト性能を最適化できます。DMD は、システム メーカーが設計においてより高い精度と微細なパターン寸法を実現できるよう支援し、I/O 密度の向上を可能にすると同時にコスト削減にも貢献します。

## まとめ

DLP テクノロジーを用いたデジタル イメージング製造プロセスにより、システム メーカーは製造コストとサイクルタイムを削減し、パネル レベル パッケージにおけるリアルタイム設計調整を可能にし、歩留まりを改善しながら大規模製造を実現し、複雑な地形上でも高精度を達成できます。

**関連資料**

DLP®テクノロジーの違いについては、[www.DLP.com](http://www.DLP.com)をご覧ください

**商標**

DLP® is a registered trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月