## Application Note

## TAS2x20、TAS257x 内の Y ブリッジ採用による効率向上

Nayeem Mahmud

## 概要

急速に進化するポータブルエレクトロニクスの環境を取り巻く中で、より豊富な機能と性能向上への需要が高まっているため、設計者は消費電力を管理するいっそうスマートな方法を探し求めているようになっています。特にオーディオ品質が非常に重要なデバイスでは、性能を犠牲にせずに電力効率を管理することが難しくなっています。テキサス・インスツルメンツ (TI) は、強化された Class-D オーディオアンプアーキテクチャを活用して、この課題に対応できる優れた設計を開発しました。この最先端の設計により、音質を犠牲にせずに消費電力を最適化でき、ワイヤレススピーカ、小型イヤホン、スマートホームガジェット、モバイルデバイスなどのバッテリ動作デバイスに大きな利点をもたらします。

この記事では、実際の使用事例を詳細に説明し、この技術を活用してバッテリ動作期間を延長し、デバイス性能を向上させる方法を提示します。TI の最適化済みアーキテクチャを採用することで、設計者は音質と効率の境界を引き上げ、現在の消費者のニーズを満たす次世代製品を製作することができます。

## 目次

|                                   |   |

|-----------------------------------|---|

| 1 はじめに.....                       | 2 |

| 2 Y ブリッジとは何か.....                 | 3 |

| 3 Y ブリッジの利点.....                  | 4 |

| 4 Y ブリッジの構成.....                  | 5 |

| 5 Y ブリッジスレッショルドおよびヒステリシスレジスタ..... | 5 |

| 6 1S、2S および外部 PVDD モード.....       | 6 |

| 7 さまざまな使用事例への効率向上.....            | 6 |

| 8 まとめ.....                        | 7 |

| 9 参考資料.....                       | 8 |

| 10 改訂履歴.....                      | 9 |

## 商標

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

従来、オーディオアンプは I/O と内部バイアスに低電圧レール (VDD) を使用し、それに加えて高電圧電源 (PVDD) を電力段のスイッチングと増幅に使用していました。出力信号の電圧レベルが低いとき、電力需要が低くなると、単一の高電圧電源からの不要なヘッドルームにより、効率は多くの場合 20% 未満に低下します。

この非効率に対処するために、テキサス・インスツルメンツは優れた Y ブリッジアーキテクチャを開発しました。このリファレンスデザインにより、アンプは必要な電力レベルに基づいて 2 つの電源間でシームレスにスイッチングでき、低消費電力レベルでアイドル時の消費電力を 90% 低減し、効率を 15~20% 向上させます。しかも、オーディオ性能を損なうことはありません。このアーキテクチャは、テキサス・インスツルメンツの業界最先端アルゴリズムと組み合わせることにより、OEM メーカーが OEM 最終製品の効率を最大化し、バッテリ動作時間を延長するのに役立ちます。

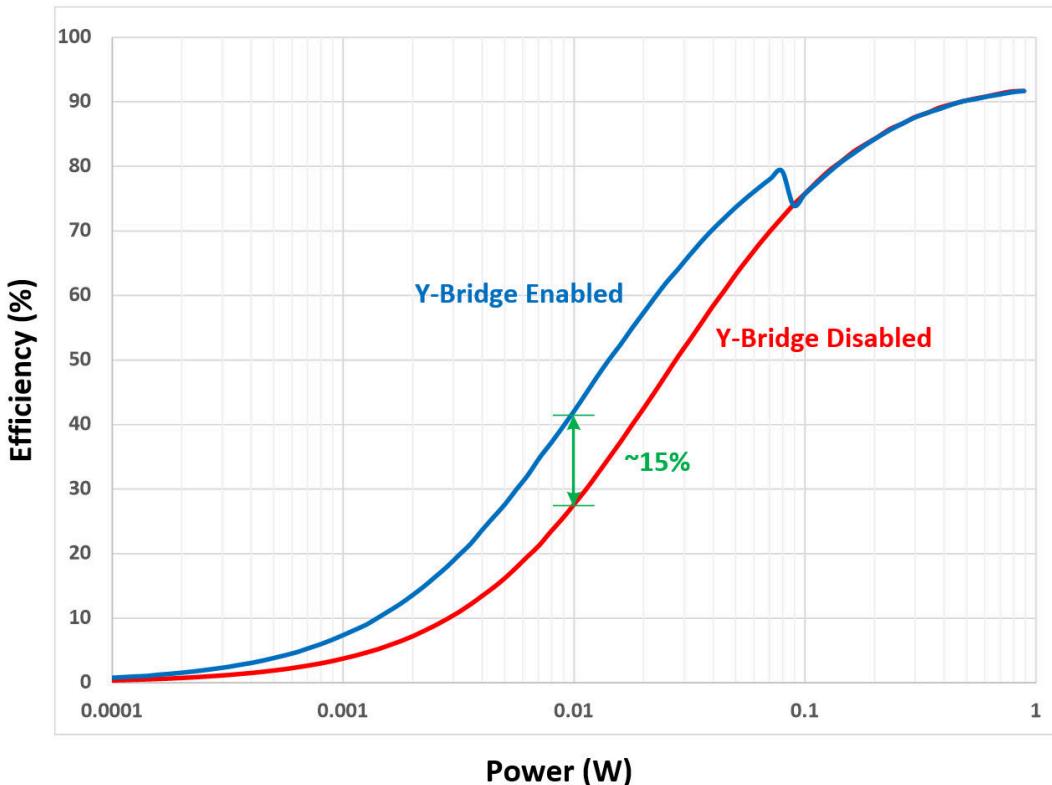

図 1-1 に示すように、Y ブリッジを使用する場合、Y ブリッジを使用しない従来のアンプと比較して、低消費電力 (100mW 未満) で効率が大幅に向上します。

図 1-1. Y ブリッジの有無による EVM での効率測定

## 2 Y ブリッジとは何か

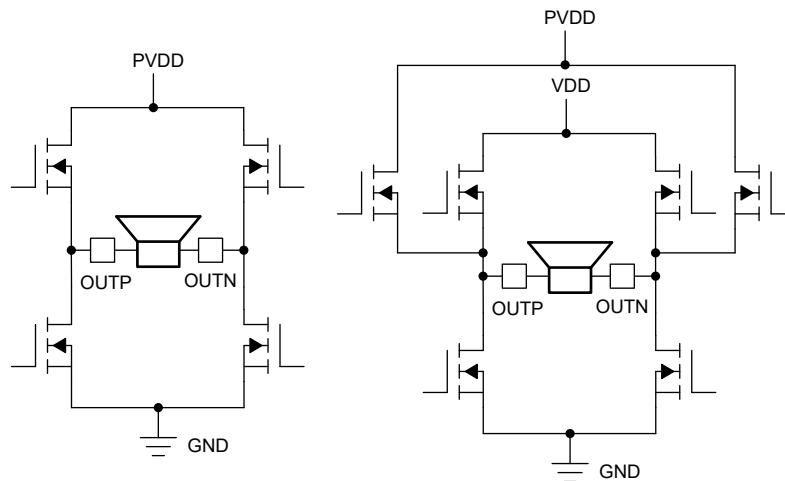

Y ブリッジは、低電力レベルでの効率を最適化し、スタンバイまたはアイドル状態での消費を低減するプログラマブル電力スレッショルドを使用して、電力要求に基づいて 2 つの電源レールを切り替えるように設計されたアンプアーキテクチャです。このアーキテクチャは Y 形状に似ており、従来のリニアハーフブリッジ設計と区別されています。図 2-1 に、従来型の Class-D アンプと Y ブリッジアーキテクチャ採用アンプの違いを示します。

従来のハーフブリッジアーキテクチャの場合、出力段はスイッチングの高電圧電源 (PVDD) のみに依存します。一方、Y ブリッジアーキテクチャは高電圧電源 (PVDD) と固定低電圧レール (VDD) の両方を利用します。低出力電力レベル (ヘッドルームを最小限に抑えるアイドル状態を含む) では、このアンプはクリッピングを発生させずに低電圧レール (VDD) で動作し、効率が大幅に向上します。電力需要が増加し、大きなヘッドルームを必要とする場合、アンプは高電圧電源 (PVDD) にシームレスに切り替わり、Y ブリッジのない標準システムの効率に一致しています。このため、従来の Class-D アンプでは効率が低下しがちな低電力レベルにおいて、Y ブリッジの利点が最も発揮されます。

図 2-1. 従来の Class-D アンプと簡略化した Y ブリッジ アーキテクチャの比較

TAS2120、TAS2320、TAS2572、TAS2574 などの TI の最新オーディオアンプは、Y ブリッジアーキテクチャを採用しています。この機能をイネーブルまたはディセーブルにするようにデバイスを設定できますが、ディセーブルにすると、アンプは PVDD 電源のみに依存します。この場合、これは、クリッピングを防止するために PVDD 電圧が十分に高いことを確認することが不可欠です。

Y ブリッジ機能は、2S~4S バッテリ構成 (7V~14V) のように、高電圧の電力段電源を必要とするシステムにおいて特に有利です。テキサス・インスツルメンツのデバイスでは、このピンは通常 PVDD と呼ばれます。PVDD 電源は、外部電源、外部昇圧回路の出力、または TAS2572、TAS2574、TAS2120 といったデバイスに搭載された内蔵昇圧回路を使って VBAT から内部生成することができます。VDD レールは、システムにすでに存在する低電圧電源も表します。TAS2x20 および TAS257x デバイスファミリでは通常 1.8V です。電力段電源 (PVDD) が 5V 以上の場合、PVDD と 1.8V レールの間でスイッチングすることにより、PVDD が 5V 未満の場合と比べて大きな利点があります。そのため、高電圧出力段を必要とするシステムには、Y ブリッジ機能が最も有利です。

さらに、Y ブリッジ機能は、事前定義されたスレッショルドに基づいて PVDD と VDD を動的に選択します。オーディオ出力信号がプログラムされたスレッショルドを超えると、Class-D 出力は高電圧電源 (PVDD) に切り替わります。このスレッショルドを下回ると、出力は引き続き 1.8V レール (VDD) を使用します。このスレッショルドはユーザー設定可能で、ほとんどの使用事例では通常約 100mW に設定されます。効率プロットは、このスレッショルドまでの効率の向上を示しています。このポイントを超えると、効率は通常、Y ブリッジを使用しないシステムの効率と整合します。

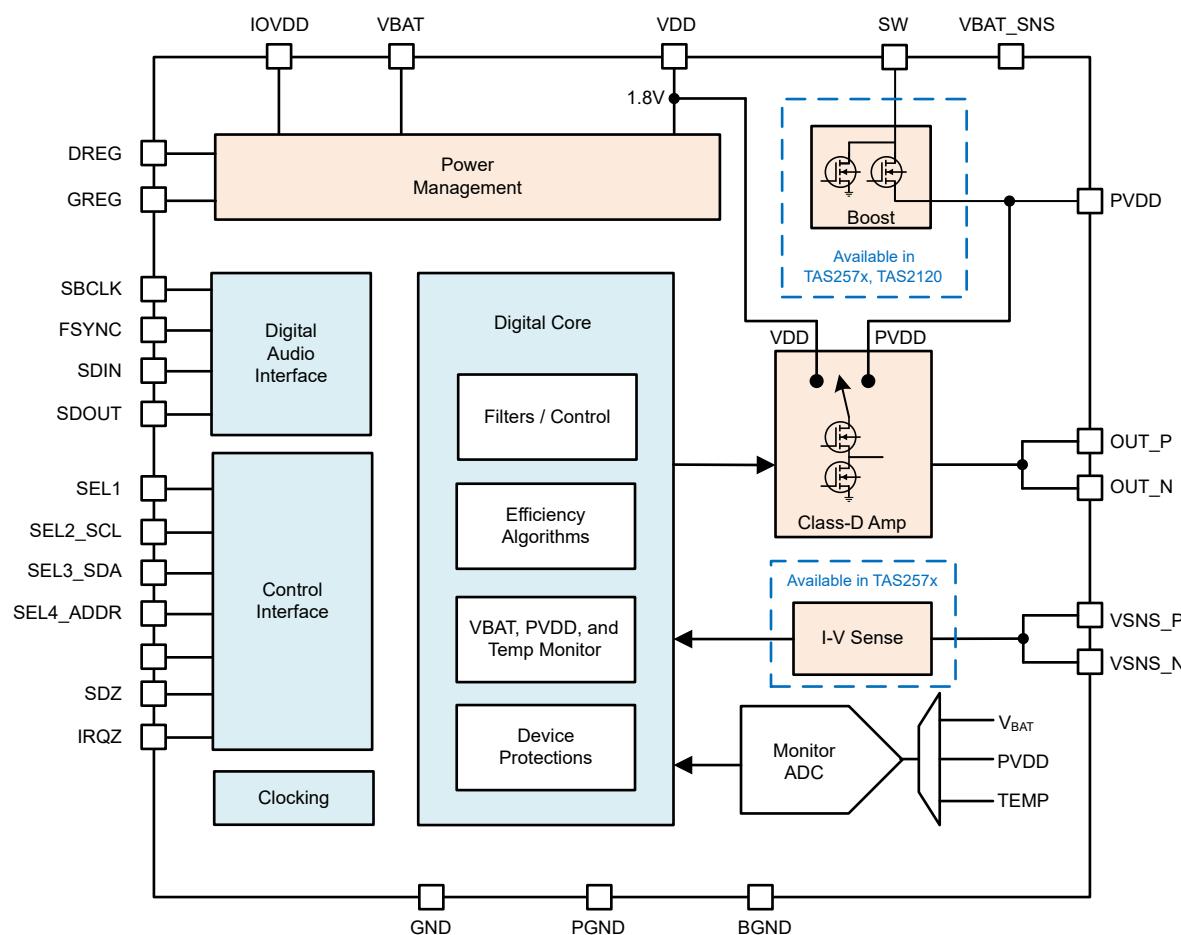

図 3-1 に、Y ブリッジ機能を備えたスマートアンプの機能ブロック図を示します

図 3-1. Y ブリッジ機能を備えたスマートアンプの機能ブロック図

## 4 Y ブリッジの構成

このアプリケーションノートでは、TAS2x20 および TAS257x デバイスファミリの Y ブリッジレジスタを構成するプロセスについて詳しく説明します。どちらのファミリも Y ブリッジ構成を活用して、オーディオ再生中の効率を向上させています。**EN\_Y\_BRIDGE\_MODE** を High に設定してこの機能をイネーブルにすると、デバイスは出力 PWM を自動的にスイッチングできます。

表 4-1. VDD Y ブリッジ モードの構成

| EN_Y_BRIDGE_MODE | 構成                 |

|------------------|--------------------|

| 0                | Y ブリッジ モードはディスエーブル |

| 1 (デフォルト)        | Y ブリッジ モードはイネーブル   |

オーディオ信号レベルが低い場合、出力は 1.8V (VDD) でスイッチングでき、Class-D 出力のスイッチング電圧を低減することで、システム全体の効率を向上させることができます。逆に、オーディオ信号レベルが High になると、必要な出力電力レベルを確実に満たすように PVDD で出力がスイッチングします。

## 5 Y ブリッジスレッショルドおよびヒステリシスレジスタ

このデバイスは、**VDD\_MODE\_THR\_LVL [23:0]** レジスタによって構成された Y ブリッジ モード スレッショルドと比較して、入力オーディオ信号レベルを常時監視します。オーディオ信号がこのスレッショルドを下回ると、内部ヒステリシス タイマがアクティブになります。信号が **YBRIDGE\_HYST\_TIMER [1:0]** レジスタで指定された期間中にスレッショルドを下回ったまま維持されると、デバイスは低電圧 (1.8V) の VDD 電源ベースの PWM スイッチングモードに切り替わります。信号レベルが **VDD\_MODE\_THR\_LVL [23:0]** レジスタと **VDD\_MODE\_HYST [23:0]** レジスタを上回ると、デバイスは信号クリッピングを発生させずに PVDD 電源の出力 PWM 信号のスイッチングを開始します。

**VDD\_MODE\_THR\_LVL [23:0]** レジスタおよび **VDD\_MODE\_HYST [23:0]** レジスタはどちらも、PPC3 ソフトウェアツールを使用して構成できます。

表 5-1. VDD\_MODE\_THR\_LVL レジスタ

| ピット  | フィールド                  | タイプ | リセット    | 説明                                             |

|------|------------------------|-----|---------|------------------------------------------------|

| 23-0 | VDD_MODE_THR_LVL[23:0] | R/W | 50A3D7h | アドレス 0x8~0xA が組み合わされます。PPC3 ソフトウェアを使用して構成できます。 |

表 5-2. VDD\_MODE\_HYST レジスタ

| ピット  | フィールド               | タイプ | リセット  | 説明                                             |

|------|---------------------|-----|-------|------------------------------------------------|

| 23-0 | VDD_MODE_HYST[23:0] | R/W | DA74h | アドレス 0xC~0xE が組み合わされます。PPC3 ソフトウェアを使用して構成できます。 |

表 5-3. VDD Y ブリッジ ヒステリシス タイマ

| YBRIDGE_HYST_TIMER[1:0] | 構成    |

|-------------------------|-------|

| 00                      | 100us |

| 01 (デフォルト)              | 500us |

| 10                      | 5ms   |

| 11                      | 50ms  |

TAS257x ファミリとは異なり、TAS2x20 デバイスはハードウェアピン制御または I<sup>2</sup>C 制御のどちらかを使用して構成できます。ハードウェアピン制御モードでは、Y ブリッジスレッショルドに対して事前定義された 3 つの構成のいずれかを選択できます。一方、I<sup>2</sup>C またはソフトウェア制御モードでは、Y ブリッジスレッショルドは、前述のように **VDD\_MODE\_THR\_LVL** レジスタと **VDD\_MODE\_HYST** レジスタの組み合わせによって定義されます。

表 5-4. SEL4 HW モード構成

| SEL4_ADDR の接続 | 構成                    |

|---------------|-----------------------|

| GND への直接短絡    | 80mW の Y ブリッジ スレッショルド |

| 電源への直接短絡      | 40mW の Y ブリッジ スレッショルド |

表 5-4. SEL4 HW モード構成 (続き)

| SEL4_ADDR の接続 | 構成                   |

|---------------|----------------------|

| 24k で電源に接続    | 1mW の Y ブリッジ スレッショルド |

また、ハードウェアピン制御モードでは、ヒステリシスタイマがデフォルト値の 500 マイクロ秒に設定されています。一方、I<sup>2</sup>C またはソフトウェア制御モードでは、上記のように、YBRIDGE\_HYST\_TIMER レジスタでヒステリシスタイマの値をカスタマイズできます。

## 6 1S, 2S および外部 PVDD モード

TAS2572, TAS2574, TAS2120 デバイスは Class-H 昇圧回路を内蔵しており、1S, 2S、および外部 PVDD モードをサポートしています。その結果、Y ブリッジの PVDD 電圧は、特定の使用事例とアプリケーション回路によって変化する可能性があります。PVDD 電圧は、昇圧電圧の電力が不要な場合 (昇圧バイパスモード)、VBAT ピンの電圧と同一となる場合があります。この電圧は、外部の固定電源から供給することもでき (システムで高電圧レールがすでに利用可能な場合)、あるいは外部の昇圧回路からも供給できます。したがって、1S, 2S、外部 PVDD モードに応じて、PVDD 高電圧が変動する可能性があります。

昇圧が不要な昇圧バイパスモードでは、PVDD 電圧を VBAT 電圧 (2.5V~5.5V の範囲) と同じにできます。この場合、PVDD = VBAT です。

統合昇圧モードでは、PVDD 電圧は内部で生成される昇圧出力によって決定され、VBAT 電源から生成されます。ここでは、PVDD = 内部昇圧出力電圧です。

外部の PVDD モードでは、PVDD 電圧は固定の外部電源、または外部昇圧出力のいずれかから供給されます。このモードは、昇圧回路を内蔵していない TAS2320 デバイスに特に適用できます。

## 7 さまざまな使用事例への効率向上

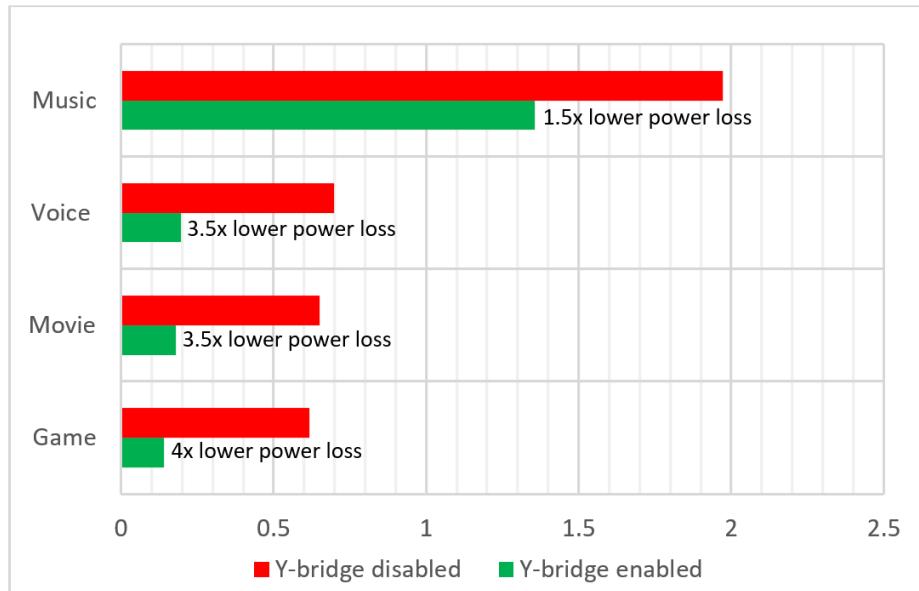

図 7-1 は、Y ブリッジをイネーブルにすることで、無効または未搭載の場合と比較して最大 75% の電力損失削減が可能であることを示しました。具体的な使用事例によって、消費電力の削減量が異なる場合があります。たとえば、サイレントセグメントを持つオーディオトラックは、音楽などの連続オーディオトラックよりも高い省電力性を実現します。このように電力損失が大幅に低減されるため、Y ブリッジアーキテクチャを使用しない従来のアンプと比較した場合、低消費電力モードでの効率が 15~20% 向上します。

図 7-1. ラップトップ スピーカに接続した EVM で測定した電力損失 (W 単位)

## 8 まとめ

バッテリ寿命の延長と高効率のオーディオ設計を実現するため、Yブリッジアーキテクチャを採用したオーディオアンプの使用を推奨します。テキサス・インスツルメンツの最新のオーディオアンプは、このアーキテクチャと、最先端のオーディオ拡張アルゴリズムを組み合わせています。Yブリッジ構成を使用することで、設計者はシステムの消費電力を最適化し、より効率的なパワーマネジメントを実現できます。これは、電力使用量の大幅な削減につながり、最終的にバッテリ動作時間の延長とユーザー エクスペリエンスの向上につながります。

## 9 参考資料

- ・ テキサス・インスツルメンツ、『TAS2572: I/V センス機能搭載、13V の Class-H 昇圧機能内蔵、6.6W、デジタル入力スマートアンプ

- ・ テキサス・インスツルメンツ、『TAS2574: I/V センス機能搭載、15V の Class-H 昇圧機能内蔵、8.5W、デジタル入力スマートアンプ

- ・ テキサス・インスツルメンツ、『TAS2120: 15V Class-H 昇圧機能内蔵、8.2W、モノラル、デジタル入力 Class-D アンプ

- ・ テキサス・インスツルメンツ、『TAS2320: 14V 外部昇圧サポート、15W、モノラル、デジタル入力 Class-D アンプ

## 10 改訂履歴

### Changes from Revision \* (March 2025) to Revision A (September 2025)

### Page

|                                      |   |

|--------------------------------------|---|

| • ドキュメント全体にわたって表、図、相互参照の採番方法を更新..... | 1 |

| • 消費電力を電力損失に変更.....                  | 6 |

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月