## Application Note

# 保護機能付き、低ノイズV-I 合成出力段、アナログ出力の構成要素

Ahmed Noeman

### 概要

このアプリケーションノートでは、電圧出力および電流出力のいずれの出力段としても使用できる汎用性の高い回路を紹介します。この回路はディスエーブル機能付きオペアンプを使用し、保護およびレンジ選択のための必要な回路を追加しています。その結果、産業用アナログ出力を駆動するための魅力的で柔軟かつコスト効率に優れた設計となっています。

### 目次

|                            |    |

|----------------------------|----|

| 1はじめに                      | 2  |

| 2回路の説明                     | 2  |

| 3複数の出力レンジへの対応              | 3  |

| 4抵抗のサイズ選定、M2の選択、その他設計上の留意点 | 3  |

| 5モード/レンジコントロール             | 4  |

| 6電流出力の電源レベル                | 4  |

| 7電圧出力の電源レベル                | 4  |

| 8保護機能                      | 4  |

| 9測定結果                      | 5  |

| 10消費電力                     | 6  |

| 11誤差モンテカルロ分析               | 6  |

| 12立ち上がり時間および立ち下がり時間        | 7  |

| 13マルチチャネル出力の構築             | 8  |

| 14まとめ                      | 9  |

| 15参考資料                     | 9  |

| 16改訂履歴                     | 10 |

### 商標

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

アクチュエータのPLCアナログ制御信号は、通常4~20mAまたは±10Vです。4線式および3線式のセンサトランスマッタについても同様です。一般的な手法は、低電圧DAC(3.3Vまたは5V電源)を使用して出力段(±10Vを超える電力)を駆動することです。同一の出力端子で電圧または電流を駆動できる機能は、PLC出力モジュールやセンサトランスマッタに望ましい柔軟性をもたらします。

この記事では、シャットダウン機能付きオペアンプを使用して、電圧と電流を組み合わせた出力段の効率的な構造を紹します。また、過電圧と過電流から段を保護する方法、およびこのような段で期待される性能についても説明します。さらに、この出力段を使用してマルチチャネルモジュールを構築するプロセスは共有されます。

## 2 回路の説明

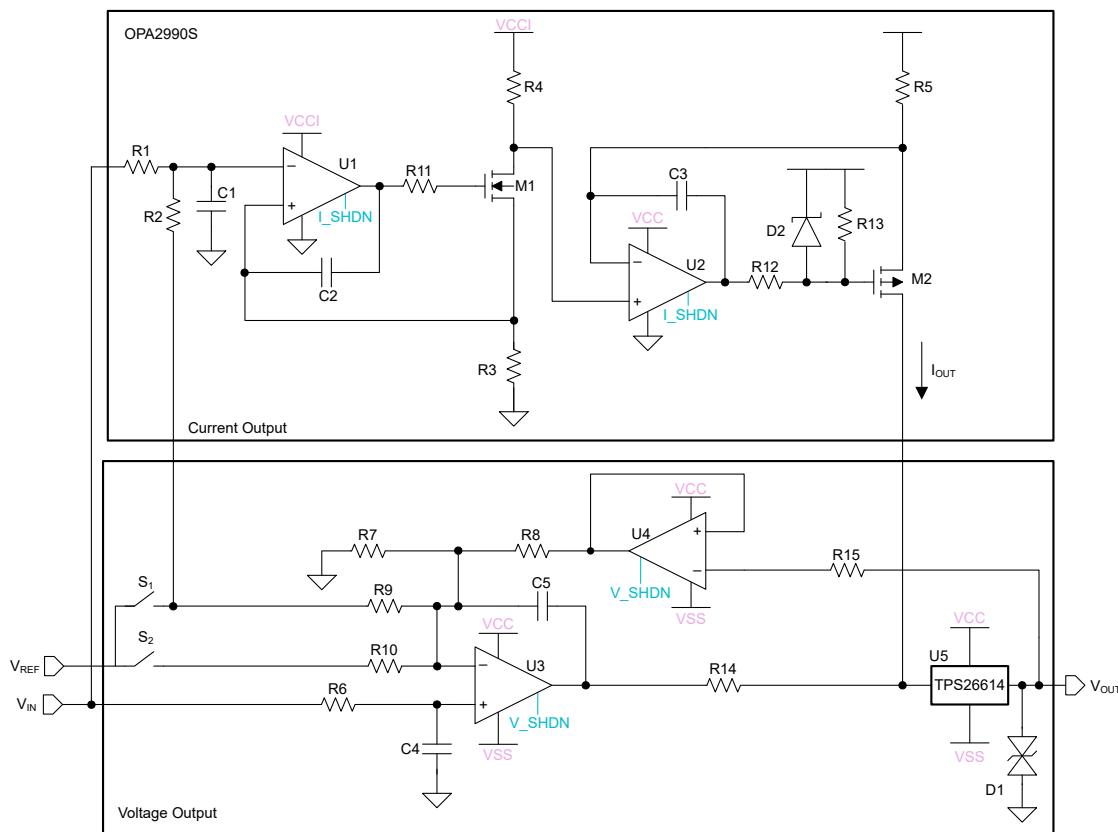

図2-1は合成されたV/I回路を示しています。電流経路はU1とU2によって構成され、電圧経路はU3とU4によって構成されます。

図2-1. V/I結合段の回路図

電流経路は2段構成の電圧-電流コンバータです。伝達関数は容易に導出できます:

$$I_{OUT} = \left[ V_{IN} \times \frac{R_2}{R_1 + R_2} + V_{REF} \times \frac{R_1}{R_1 + R_2} \right] \times \frac{R_5}{R_3 \cdot R_4} \quad (1)$$

VREFI入力がオープン回路の場合、この式は次のように簡略化されます:

$$I_{OUT} = V_{IN} \times \frac{R_5}{R_3 \cdot R_4} \quad (2)$$

電圧バスは非反転アンプで、帰還抵抗は出力ノードに直接接続する代わりに、ユニティゲインバッファで駆動されます。出力をバッファリングすると、帰還抵抗にリークされた電流が減少し、電流出力モードの誤差が低減されます。同様に、電圧出力段の伝達関数は次のように容易に導出できます:

$$V_{OUT} = V_{IN} \times \left[ 1 + \frac{R_8}{R_7} + \frac{R_8}{R_9} \right] - V_{REF} \times \frac{R_8}{R_9} \quad (3)$$

VREF 入力が開放状態であれば、この式は次の形になります

$$V_{OUT} = V_{IN} \times \left[ 1 + \frac{R_8}{R_9} \right] \quad (4)$$

回路が 0~10V または 0~20mA の出力用に設計されている場合、VREF 入力はフローティングのままでし、簡易式が使用されます。VIN = 0~2.5V と仮定すると、Vout 段のゲインは 4V/V に設定する必要があります、電流段のゲインは 8mA/V に設定する必要があります。ゲインは、適切な抵抗値を選択することで設定されます。

オペアンプ U1 と U2、および U3 と U4 は、デュアル パッケージのオペアンプ OPA2990S です。そのため、各パスに異なる電源レールを使用できます。電流経路は VCC1 と GND を電源レールとし、電圧経路は VCC2 と VSS を電源レールとしています。それぞれの経路にはシャットダウン信号があります: ISHDNI、および VSHDN。2 個のデュアル オペアンプの代わりに、OPA4990S を使用することもできます。この場合、電圧と電流の両方のセクションでは 2 つの電源レールのみを使用できます。

### 3 複数の出力レンジへの対応

回路が複数出力レンジに対応する必要がある場合、段のゲインは固定されているため、入力レンジおよびリファレンスレンジを変更することで対応する必要があります。ゲインを調整可能にすると、設計が複雑になり、精度が低下する可能性があります。

表 3-1 に、複数の出力範囲をサポートする同じ段のさまざまな構成を示します。

表 3-1. さまざまな範囲の設定

|           | 0~20mA                              | 4~20mA                        | 0~10                  | 0~5     | -10~10                |

|-----------|-------------------------------------|-------------------------------|-----------------------|---------|-----------------------|

| VREF スイッチ | S1 オープン                             | S1 クローズ                       | S2 オープン               | S2 オープン | S2 クローズ               |

| VIN 範囲    | 0~2.5                               | 0~2.5                         | 0~2.5                 | 0~1.25  | 0~2.5                 |

| R 比       | $\frac{R_5}{R_3 \cdot R_4} = 0.008$ | $\frac{R_1}{R_1 + R_2} = 0.2$ | $\frac{R_8}{R_7} = 3$ |         | $\frac{R_8}{R_9} = 4$ |

表 3-1 は、抵抗比を一定に保ちながら、スイッチと入力レンジを切り替えることで異なる出力レンジを実現できることを示しています。

ステージを駆動するには、2.5V または 1.25V フル スケールの DAC ソースと、2.5V のリファレンスが必要です。

### 4 抵抗のサイズ選定、M2 の選択、その他設計上の留意点

電流経路における抵抗値の選定は R5 から始まります。値を小さくするとヘッドルームは小さくなりますが、同時に U2 の入力が電源に近づき、入力同相モード範囲を逸脱する可能性があります。R5 = 49.9Ω は妥当な選択です。

R4:R5 の比率によって、M1 の電流と M2 の出力電流との比率が決まります。(M1 における) 中間電流を小さくすると消費電流は減少しますが、出力ノイズが増加し、動的性能が劣化します。1:10 の比率が選択され、その結果、R4 = 499Ω となりました。

最大 I (M1) = 2mA が決定された状態で、R3 = 1.24kΩ となります。

R12 = 10kΩ は M2 のゲートをプルアップするために使用され、C2 = C3 = 200pF は U1 と U2 の補償に使用されます。

M2 の選定は最大電力損失によって決まります。24V × 20mA を仮定すると約 0.5W となり、また最大 Vce 電圧を考慮すると、40V を超える耐圧を持つデバイスが必要です。DMP6110SVT-7 は 1.2W、60V 定格の PMOS であり、この回路で使用することができます。M1 の選択はそれほど重要ではありません。PMV88ENEAR は 0.6W、60V 定格の NMOS であり、選定されています。

電圧モードでは、R7、R8、R9 は出力ノイズを増加させることなく消費電力を最小化するように選定されています。R8 = 34kΩ、R7 = 11.3kΩ、R9 = 8.45kΩ が選定されています。

## 5 モード / レンジ コントロール

レンジ制御スイッチ S1 および S2 は、1:1 の SPST スイッチ ペアで実装でき、これは通常データコンバータで利用可能な 2.7V ~ 5V で駆動されます。TMUX1511 はコスト効率の高い選択肢であり、例えば 4 つのスイッチを備えており、2 つの V/I 合成チャネルをサポートできます。TMUX1511 は 1.8V ロジックで制御できます。

OPA2990S オペアンプのシャットダウンは、その負電源を基準としており、ディスエーブル閾値は 0.8V です。GND を基準とする電流経路では、1.8V 以上のロジック信号を使用して U1 および U2 を無効化できます。ただし、U3 と U4 の場合はレベルシフタが必要です。シンプルな P MOSFET レベルシフタを使用できます。

## 6 電流出力の電源レベル

電流出力段にはユニポーラ電源 VCCI があります。OPA2990S は、2.7V までの低電源電圧で動作可能です。最大出力が  $V_{out(max)} = V_{CCI} - 1.5V$  に達する可能性があると仮定します。電流出力の最大負荷は、 $R_{Load(max)} = V_{out(max)} / 20mA$  です。これらの式により、特定の最大負荷を対象とした場合に必要となる最小電源電圧を求めることができます。一般的な値である  $R_{Load} = 600\Omega$  の場合、最小電源電圧レベルは約 13.5V です。ただし、1kΩ の負荷を駆動するには代わりに 22V が必要です。20% の過電流 (24mA) を使用する場合、20% 高い電源電圧が必要となります。

## 7 電圧出力の電源レベル

電圧出力段は VCC、VSS の両電源を備えています。OPA2990S はレールツーレールのオペアンプであり、出力電流に応じて電源レールから約 150~300mV のヘッドルームしか必要としません。バイポーラ出力の場合、電源は最大の正出力より少なくとも +0.5V 高く、最小出力より少なくとも -0.5V 低く設定します。

ユニポーラ出力が 0~5V および 0~10V の場合、真のゼロ出力を実現するために、VSS を生成する簡易的な負のチャージポンプを使用できます。LM7705 は低ノイズ、低コストのチャージポンプで、-0.23V を生成でき、最大 26mA をシンクする能力を備えています。そのため、ユニポーラ出力の場合に VSS を生成する用途には LM7705 が適した選択肢となります。

電圧モードにおける最小負荷は  $R_{Load(min)} = V_{out(max)} / I_{out(max)}$  で表されます。電圧出力が 20mA 出力用に設計されていると仮定すると、±10V 出力範囲の場合、 $R_{Load(min)} = 500\Omega$  となります。

## 8 保護機能

図 2-1 の回路には独自の保護デバイス U5、TPS26614 があり、過電圧保護と過電流保護の両方を備え、自動リトライ機能を特徴としています。電流出力モードでは、出力ノードが VSS または VCCI を超えた場合にデバイスが電流経路を遮断し、出力段を逆電流から保護します。電圧出力モードでは、電流が 30mA を超えると TPS26614 が遮断し、U3 を過負荷や短絡から保護します。また、デバイスは電圧が VCCI または VSS を超えた場合にもスイッチオフすることができます。電圧出力段を適切に保護するためには、VCC と VCCI を同一に保つことが推奨されます。

出力トランジスタ M2 のゲートは、出力がオープン回路の場合に  $V_{gs(M2)}$  電圧を制限するため、ツェナー D2 によって保護されています。この場合、U2 は  $V_{g(M2)}$  をプルダウンすることができ、選択されたトランジスタのゲート電圧動作限界の 20V を超える可能性があります。このようなイベントが発生した場合、R12 は D2 の電流を制限できます。R13 は  $V_{g(M2)}$  をプルアップしており、M2 が起動時に確実にオフになるようにしています。

TVS ダイオード D1 は出力ピンをサージや EFT 事象から保護し、これらの事象発生時に出力ピンの電圧を制限します。R14 は、電流を制限することで U4 の入力を保護します。R1、R6、および R9 は同様に U1 と U3 の入力を保護しており、特に未給電状態のデバイスに入力が加えられた場合に有効です。

## 9 測定結果

提案回路のプロトタイプを製作し、性能を評価するためにいくつかの測定を実施しました。以下のセクションでその結果を詳細に示します。

条件:  $\pm 12V$  電源レール、 $1k\Omega$  負荷、出力は  $8k$  サンプルで平均化されます。**表 9-1** は、測定された出力、mA 単位の電源電流、 $\mu V$  単位の rms ノイズ、さらに対応する有効分解能 (ビット) を示しています。このテストでは、低ノイズ源によって入力と  $V_{ref} = 2.5V$  の両方を生成しています。

**表 9-1. バイポーラ  $\pm 10V$  電圧モード**

| vin   | vout      | I(vcc) | I(vss)  | rms ノイズ | 分解能  |

|-------|-----------|--------|---------|---------|------|

| 0     | -10.09124 | 0.232  | -10.592 | 0.345   | 17.1 |

| 0.625 | -5.03302  | 0.233  | -5.418  | 0.366   | 17.1 |

| 1.25  | 13.63853m | 0.274  | 0.297   | 0.365   | 17.1 |

| 1.875 | 5.06036   | 5.373  | 0.238   | 0.369   | 17.0 |

| 2.5   | 10.10703  | 10.533 | 0.24    | 0.374   | 17.0 |

条件:  $\pm 12V$  電源レール、 $1k\Omega$  負荷、出力は  $8k$  サンプルで平均化されます。**表 9-2** は、測定された出力、mA 単位の電源電流、 $\mu V$  単位の rms ノイズ、さらに対応する有効分解能 (ビット) を示しています。

**表 9-2. ユニポーラ 0 ~ 5V 電圧モード**

| vin   | vout     | I(vcc) | rms ノイズ | 分解能  |

|-------|----------|--------|---------|------|

| 0     | -0.739mV | 0.221  | 0.109   | 17.5 |

| 0.625 | 2.51609  | 2.791  | 0.112   | 17.4 |

| 1.25  | 5.04145  | 5.369  | 0.14    | 17.1 |

条件:  $+24V$  電源、 $1k\Omega$  負荷、出力は  $8k$  を超えるサンプルを平均化されます。**表 9-3** は、測定された出力、mA 単位の電源電流、nA 単位の rms ノイズ、さらに対応する有効分解能 (ビット) を示しています。

**表 9-3. 0 ~ 20mA 電流モード**

| vin  | iout     | I(vcc) | rms ノイズ | 分解能  |

|------|----------|--------|---------|------|

| 0    | 1.37077u | 0.253  | 207     | 18.9 |

| 1.25 | 10.08287 | 11.73  | 283     | 18.4 |

| 2.5  | 20.16957 | 22.919 | 279     | 18.4 |

4 ~ 20mA モードが有効化されている場合、**表 9-4** にゼロ入力の状況を示します

**表 9-4. 4 ~ 20mA 電流モード**

| vin | iout    | I(vcc) | rms ノイズ | 分解能  |

|-----|---------|--------|---------|------|

| 0   | 4.07328 | 5      | 276.8   | 18.5 |

## 10 消費電力

出力段の効率を算出するために、電圧モードおよび電流モードの両方について( $VCC = 24V$ 、 $VSS = -12V$ を使用)、電圧モードは無負荷条件とし、回路各部の消費電力を以下の表に示します。

**表 10-1. 電流出力モードでの消費電力**

| 出力   | U1 および U2 | I(M1) | TPS26614 | U3 および U4 | 合計 (mA) |

|------|-----------|-------|----------|-----------|---------|

| 4mA  | 0.55      | 0.4   | 0.8      | 0.03      | 1.78    |

| 20mA | 0.7       | 2     | 0.8      | 0.03      | 3.53    |

**表 10-2. 電圧出力モードでの消費電力**

| 出力  | U1 および U2 | I(M1) | TPS26614 | U3 および U4<br>VCC、VSS | 合計 (mA) VCC、VSS |

|-----|-----------|-------|----------|----------------------|-----------------|

| -10 | 0.03      | 0     | 0.8      | 0.23、-0.59           | 1.06、-0.59      |

| 0   | 0.03      | 0     | 0.8      | 0.23、-0.24           | 1.06、-0.24      |

| 10  | 0.03      | 0     | 0.8      | 0.53、-0.24           | 1.36、-0.24      |

## 11 誤差モンテカルロ分析

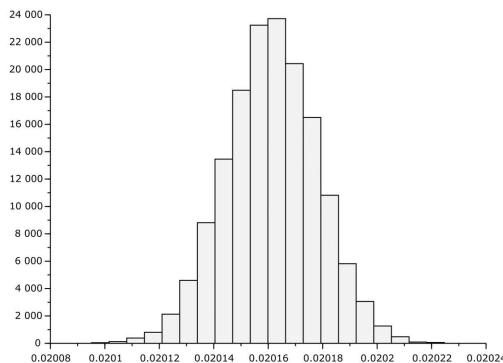

プロトタイプでの測定では、抵抗の許容差による誤差分布の全体像を把握することはできません。モンテカルロ解析を実施し、所定の抵抗許容差およびオペアンプのオフセット分布とドリフトに対する誤差分布を評価しました。

表 11-1 は、特定の許容誤差を持つ抵抗を使用した場合の予測誤差 (その場合はゲイン誤差で調整されていません) を示しています。R1 ~ R5 のみが電流出力バスの精度に寄与することに注意してください。

**表 11-1. 抵抗の許容誤差に対する誤差の依存性**

| 抵抗の誤差    | 1%    | 0.5%  | 0.1%  | 理想的な抵抗 |

|----------|-------|-------|-------|--------|

| ±3 シグマ誤差 | 1.73% | 0.87% | 0.25% | 0.18%  |

| 最大誤差     | 2.3%  | 1%    | 0.3%  | 0.25%  |

**図 11-1. 2.5V 入力、0.5% 抵抗に対する出力電流ヒストグラム**

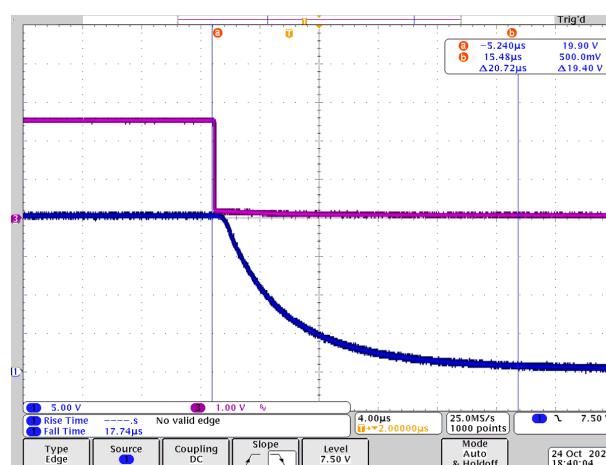

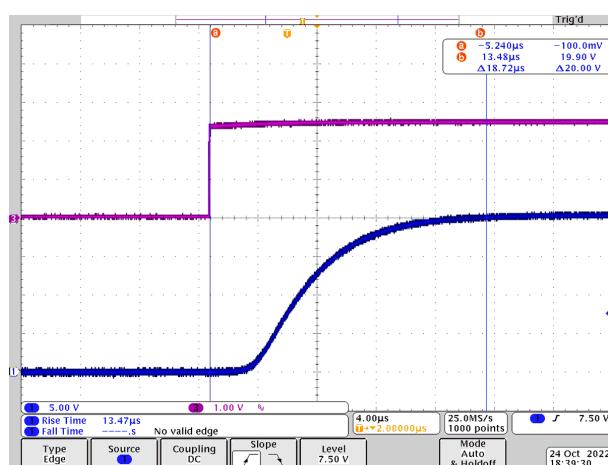

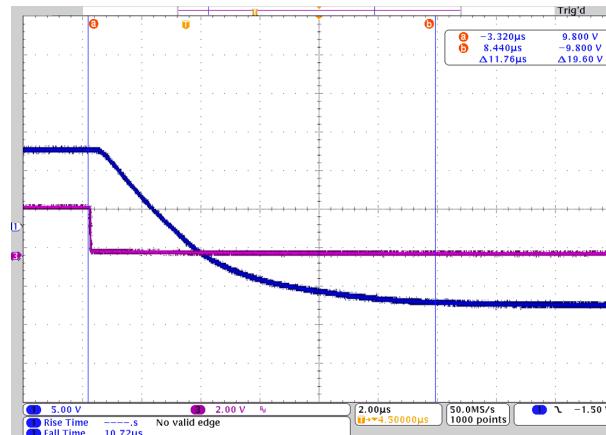

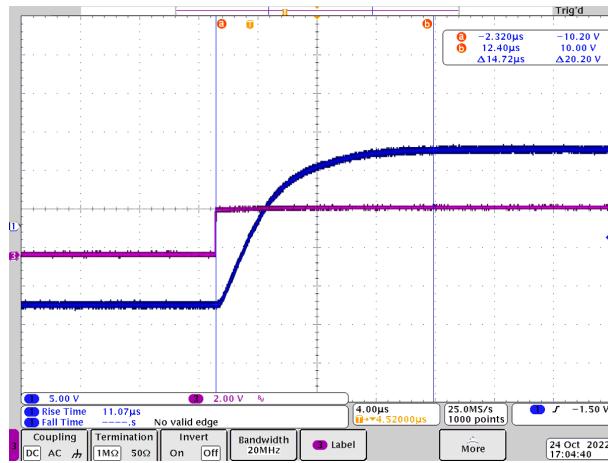

## 12 立ち上がり時間および立ち下がり時間

図 12-1 に示すように、バイポーラ電圧出力のフルスケールの立ち上がり時間および立ち下がり時間は 15 $\mu$ s 未満です。電流モードにおける立ち上がり時間および立ち下がり時間は、0~20mA モードおよび 4~20mA モードのいずれにおいても 20 $\mu$ s 未満であり、その結果を以下の図に示します。

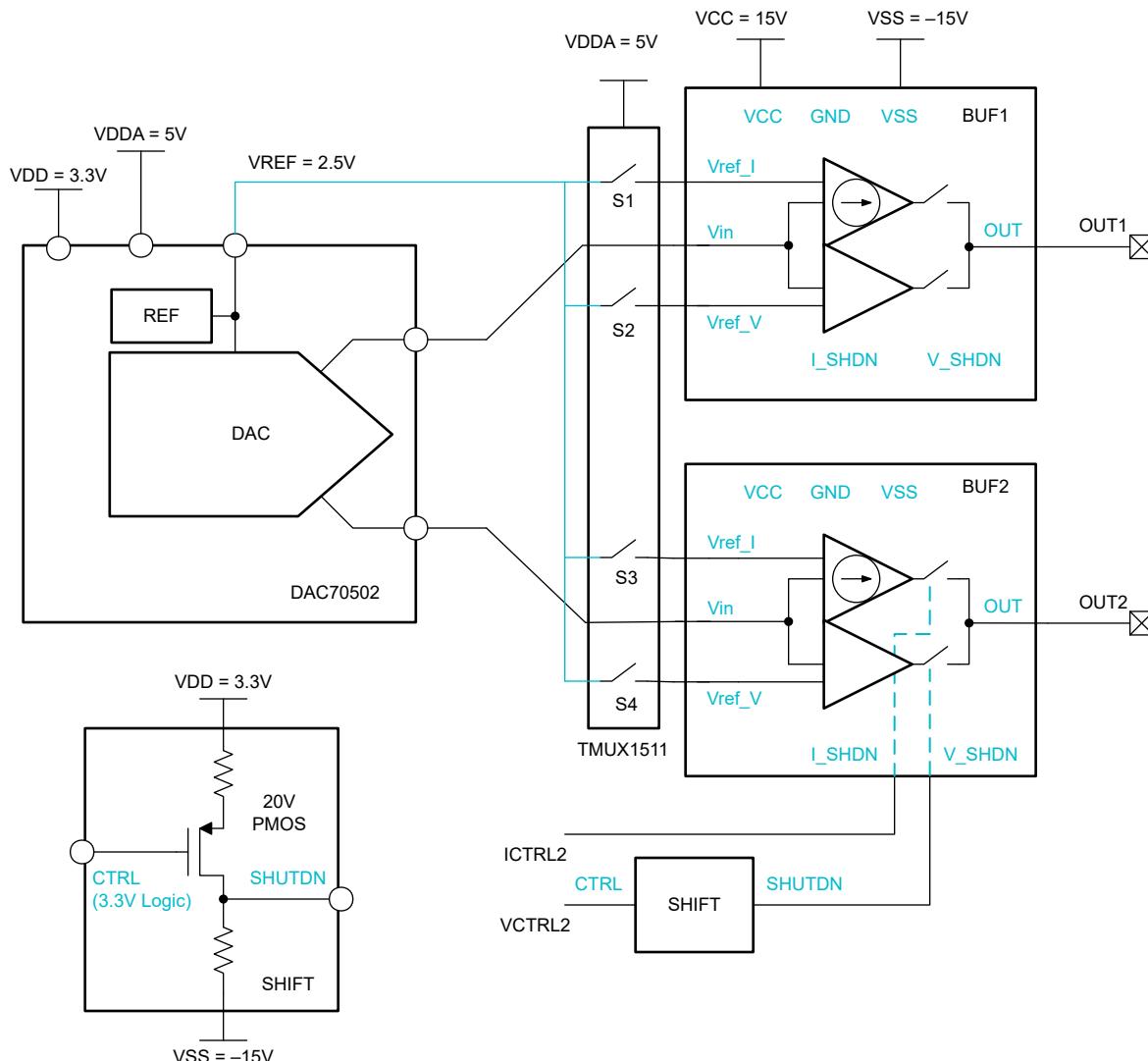

## 13 マルチチャネル出力の構築

V/I 合成回路は標準的な DAC に接続でき、構成可能なマルチチャネル出力モジュールを構築できます。DAC8050x ファミリはこれに最適です。このデバイスファミリは 1 ~ 8 チャネルを提供し、16b の分解能、1LSB の INL、およびバッファ付き電圧出力を備えています。このファミリには、12 ビットおよび 14 ビットの対応品 (DAC6050x および DAC7050x) もあります。DAC には 2.5V のリファレンスが内蔵されており、外部ピンで利用できます。

DAC の出力範囲は 2.5V または 1.25V に調整可能であり、DAC GAIN を  $x1$  または  $x2$  に設定することで、DAC は容易に 0~5V の出力範囲を実現できます。

図 13-1 は、2 チャネル構成可能レンジ AOUT の簡略ブロック図を示しています。BUF1 および BUF2 は、それぞれ提案された V/I 回路を表しています。

図 13-1.2 チャネル出力のブロック図

## 14 まとめ

可変出力レンジと完全な保護機能を備えた柔軟な V/I 合成出力段を紹介します。表 14-1 に、出力段の標準的性能を示します

表 14-1. 性能仕様の概要

| モード            | サポートされているモード                  |

|----------------|-------------------------------|

|                | 電圧: 0~5V, 0~10V, ±10V         |

|                | 電流: 0~20mA, 4~20mA            |

| 有効分解能          | 電圧モード: 17b<br>電流モード: 18b      |

| 未調整誤差          | 0.5%、25ppm の抵抗については 0.87% FSR |

| 電源             | VCC-VSS = 5V~40V              |

| 温度             | -40~125 °C                    |

| セトリング タイム (FS) | 20us の抵抗性負荷                   |

| 保護             | サーボ、OV、UV、OC                  |

## 15 参考資料

- テキサス インスツルメンツ、[ユニポーラ DAC からバイポーラ ±10V 出力、産業電圧ドライバ用](#)設計ガイド。

- テキサス インスツルメンツ、[産業用アプリケーション向けのハイサイド電流源](#)アナログ設計ジャーナル。

- 電子製品、[プログラマブル アナログ出力回路](#)により、産業システムの柔軟性を最大化。

## 16 改訂履歴

| Changes from Revision * (August 2024) to Revision A (September 2025) | Page |

|----------------------------------------------------------------------|------|

| • ドキュメント全体にわたって表、図、相互参照の採番方法を更新.....                                 | 1    |

| • <a href="#">図 2-1</a> を更新.....                                     | 2    |

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月