*Application Note***AFE11612-SEP を使用した航空宇宙アプリケーションにおける

GaN および LDMOS RF パワー アンプのバイアス供給**

Erin Bowrie

**概要**

このアプリケーション ノートでは、宇宙規格対応アプリケーションにおける高周波パワー アンプの電圧バイアスに関して、AFE11612-SEP の基本的な機能と利点を詳しく説明します。このレポートでは、パワー アンプのバイアスとそれを支える回路の基本について解説します。

**目次**

|                                    |    |

|------------------------------------|----|

| 1 LDMOS および GaN パワー アンプ FET PA の基礎 | 3  |

| 2 $V_{GS}$ 補償                      | 4  |

| 3 シーケンシング                          | 5  |

| 4 統合型 PA バイアスソリューション               | 6  |

| 5 GaN PA の負バイアス印加                  | 6  |

| 6 TDD アプリケーション向けの高速スイッチング          | 8  |

| 7 $V_{DRAIN}$ スイッチング回路             | 8  |

| 8 制御されたゲートシーケンス回路                  | 9  |

| 9 $V_{DRAIN}$ 監視                   | 10 |

| 10 外部負電源監視                         | 10 |

| 11 PA 温度のモニタリング                    | 11 |

| 12 まとめ                             | 11 |

| 13 参考資料                            | 12 |

| 14 改訂履歴                            | 13 |

**図の一覧**

|                                                           |    |

|-----------------------------------------------------------|----|

| 図 1-1. GaN と LDMOS FET                                    | 3  |

| 図 1-2. FET $V_{DRAIN}$ , $I_{DS}$ , および $V_{GS}$ の動作      | 3  |

| 図 2-1. GaN PA $V_{GS}$ バイアス電圧と温度との関係により、一定の $I_{DS}$ を維持し | 4  |

| 図 3-1. GaN 電源シーケンス                                        | 5  |

| 図 4-1. AFE11612-SEP の代表的なアプリケーション                         | 6  |

| 図 5-1. 差動オペアンプ回路                                          | 6  |

| 図 5-2. 差動オペアンプ出力                                          | 7  |

| 図 6-1. ゲートスイッチング回路                                        | 8  |

| 図 7-1. $V_{DRAIN}$ イネーブル回路                                | 8  |

| 図 7-2. $V_{DRAIN}$ イネーブルプロット                              | 8  |

| 図 8-1. PA_ON AND ゲート                                      | 9  |

| 図 8-2. PA_ON 電力シーケンス制御                                    | 9  |

| 図 9-1. $V_{DRAIN}$ 監視回路                                   | 10 |

| 図 10-1. $V_{SS}$ 監視回路                                     | 10 |

| 図 11-1. リモート温度回路                                          | 11 |

**表の一覧**

|                    |    |

|--------------------|----|

| 表 8-1. PA_ON の真理値表 | 9  |

| 表 12-1. 推奨デバイス     | 11 |

**商標**

すべての商標は、それぞれの所有者に帰属します。

## 1 LDMOS および GaN パワー アンプ FET PA の基礎

ほとんどの高周波 (RF) アンテナシステムは、RF トランミッタ設計にパワー アンプ (PA) を備えています。多くの航空宇宙および宇宙アプリケーションには、以下のようなアンテナ システムが含まれます：

- レーダー

- レーダー画像処理ペイロード

- 通信ペイロード

- 遠隔測定

PA バイアス回路は、2 つの目的を確実にするために RF アンテナ システムに実装されています。1 つ目は、アンプの出力電力を把握し適切に制御すること、2 つ目は、PA を損傷しないようシステムを安全にオン/オフすることです。PA は一般的に窒化ガリウム (GaN)、ガリウムヒ素 (GaAs)、または横拡散 MOSFET (LDMOS) ランジスタを使用して設計されています。GaN および LDMOS FET (電界効果トランジスタ) の出力電力は、ドレインからソースへ流れる電流 ( $I_{DS}$ ) に依存します。

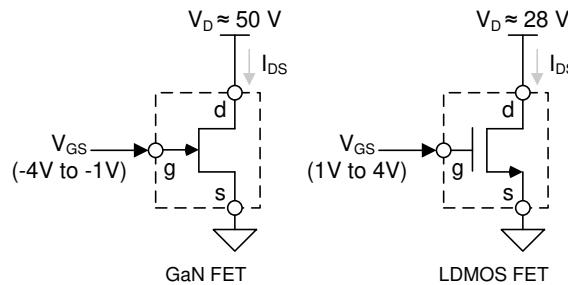

図 1-1. GaN と LDMOS FET

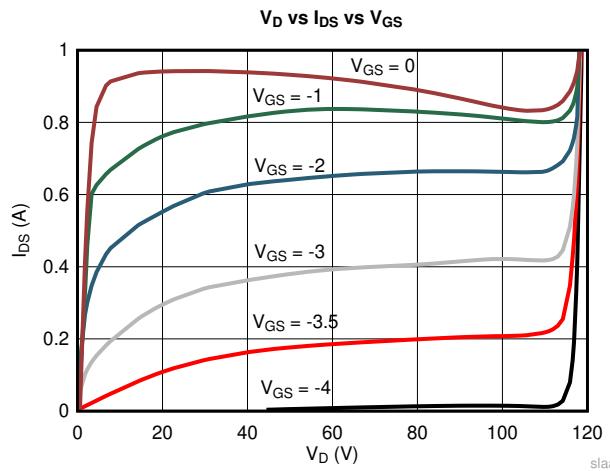

$I_{DS}$  は、ドレイン電圧 ( $V_{DRAIN}$ )、ゲート電圧 ( $V_{GS}$ )、および温度のいくつかの変数によって決まります。図 1-2 は、GaN PA における一部の  $V_{GS}$  電圧に対する  $I_{DS}$  値と  $V_{DRAIN}$  の関係例を示しています。 $V_{GS}$  電圧が高いほど、 $I_{DS}$  が大きくなり、アンプからの電力が増加します。 $V_{GS}$  が十分に低い場合、PA では実質的に  $I_{DS}$  電流がゼロになります。この  $V_{GS}$  電圧をピンチオフ電圧と呼びます。 $I_{DS}$  は  $V_{DRAIN}$  にも依存しますが、ほとんどの設計者は  $V_{DRAIN}$  を変化させていません。代わりに、設計者は目的の電力レベルに最適化された  $V_{DRAIN}$  電圧を使用します。 $V_{DRAIN}$  値は通常、GaN PA では約 50V、LDMOS PA では 28V です。

図 1-2. FET  $V_{DRAIN}$ 、 $I_{DS}$ 、および  $V_{GS}$  の動作

## 2 $V_{GS}$ 補償

$I_{DS}$  は PA の温度に依存します。温度ドリフトによる  $I_{DS}$  の変動により、システム内の他の 2 つの変数の 1 つを調整して PA を補償する必要が生じます:  $V_{DRAIN}$  または  $V_{GS}$  です。 $V_{DRAIN}$  の調整がさまざまな RF アプリケーションで実装される理由は多数ありますが、出力電力の応答は、図 1-2 に示すように、 $V_{DRAIN}$  電圧の変化に比べて最小限です。 $V_{GS}$  を調整することで、応答時間が短くなり、出力電力の合計振幅となるため、温度補償やその他のアプリケーションにもっと実用的に使えます。

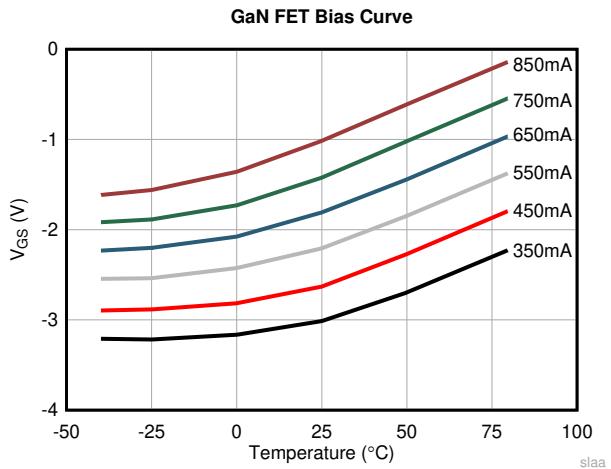

図 2-1. GaN PA  $V_{GS}$  バイアス電圧と温度との関係により、一定の  $I_{DS}$  を維持し

図 2-1 は、熱ドリフトにより  $I_{DS}$  を安定させるために  $V_{GS}$  を調整する必要があることを示しています。これらの PA を利用するアプリケーションでは、アンテナ システムの出力が厳密に制御されるよう、この種の補償を実装する必要があります。 $V_{GS}$  補償は、PA の温度を測定するか、電流シャントを使用して  $I_{DS}$  を測定し、それに応じて  $V_{GS}$  を調整することで実装できます。

### 3 シーケンシング

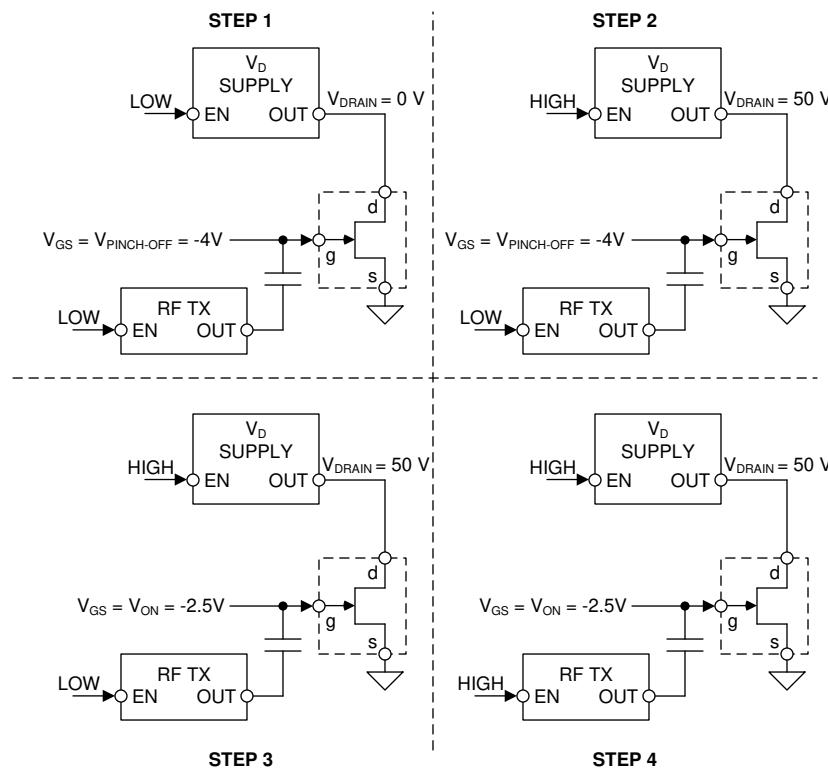

$V_{DRAIN}$  が印加された際に  $V_{GS}$  電圧が過大にならないようにするために、PA の電源を制御された手順でオン/オフする必要があります。このような状態になると、PA が飽和動作し、PA 自体または実装されている基板に熱的損傷を与える可能性があります。PA の電源をオンにするには、以下の手順が必要です：

1. まず、 $V_{GS}$  信号を PA に印加します。 $V_{GS}$  電圧は、 $V_{GS}$  ピンチオフ電圧またはそれ以下の電圧に遷移する必要があります。これにより、 $V_{DRAIN}$  電圧が印加されたときに、ゲートはすでに Low になっています。

2. 次に、ドレイン電圧電源を有効にし、 $V_{DRAIN}$  に公称値（たとえば 50V）に電力を供給できるようにします。 $V_{GS}$  はピンチオフ電圧のときのため、 $I_{DS}$  は最小限にする必要があります。

3.  $V_{DRAIN}$  を印加した後で、 $V_{GS}$  bias 電圧を上げて、PA の目的の電力出力を設定します。

4. 最後に、RF 信号を有効にします。これにより、PA は信号を送信できます。

図 3-1. GaN 電源シーケンス

電源投入手順を逆にすることで、PA を安全にシャットダウンできます。

1. PA からの RF 信号を無効にします。

2.  $V_{GS}$  電圧をピンチオフ値まで下げて、PA の出力電力を不要にします。

3. ドレイン電源にディスエーブル信号を送信して、 $V_{DRAIN}$  電圧をディスエーブルにします。

4. 最後に、PA が完全に無効化されるため、 $V_{GS}$  電圧がグランドまで落ちることがあります。

## 4 統合型 PA バイアスソリューション

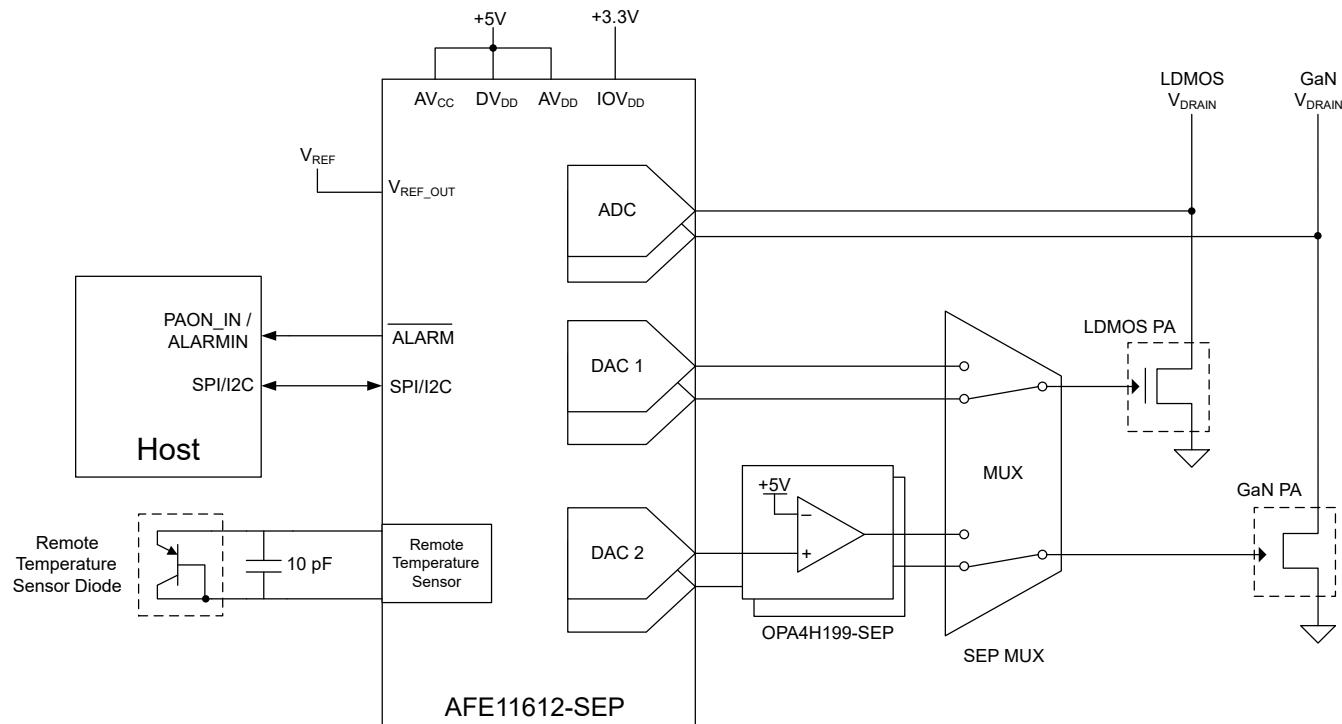

図 4-1. AFE11612-SEP の代表的なアプリケーション

AFE11612-SEP は、12 ビット高精度 DAC を 12 チャネル、16 入力 12 ビット ADC、2 組のリモート温度センサ入力を備えた、統合型パワーインプーティングバイアスソリューションです。DAC 出力により、最大 12 個の LDMOS PA の  $V_{GS}$  制御が可能です。追加の回路で GaN PA をサポートできます。また、このデバイスは 2 つのリモート温度センサおよび 4 つの ADC 入力に対してプログラマブル スレッショルドを備えた、堅牢な PA モニタリングと保護機能も備えています。

## 5 GaN PA の負バイアス印加

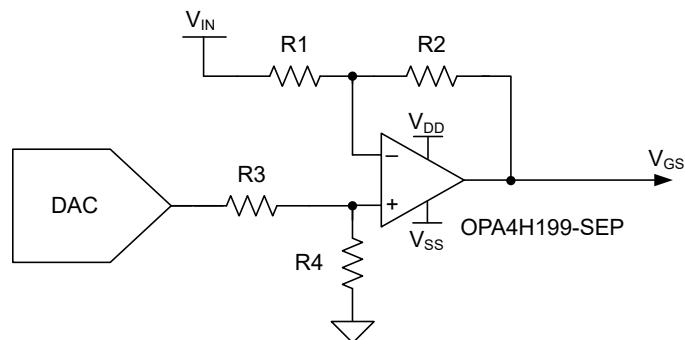

AFE11612-SEP は内部に 2.5V リファレンスを備えており、DAC 出力範囲を 0V ~ 5V にスケーリングします。GaN PA は適切にバイアスするために負のゲート電圧を必要とし、ピンチオフ電圧はオン電圧よりも負側になります。DAC 出力は、差動オペアンプ回路を使用することで負電圧にシフトできます。図 5-1 の回路例では、放射線耐性を強化したオペアンプ OPA4H199-SEP を使用して、DAC 出力を負範囲にオフセットおよびスケーリングしています。アラームシャットダウン時に PA を保護するために、差動オペアンプ回路が使用されます。アラーム状態では、DAC は電圧を 0V に駆動します。差動回路は GaN ゲートに最も負の電圧を出力し、GaN PA がオフになることを保証します。

図 5-1. 差動オペアンプ回路

抵抗値は、目的のオペアンプ出力、 $V_{IN}$ 、DAC の範囲に基づいて選択されます。以下の式は、抵抗値を選定する際の指針を示します：

$$V_{GS} = -\left(V_{IN} \times \frac{R2}{R1}\right) + DAC \times \left(\frac{R4}{R4+R3}\right) \times \left(\frac{R1+R2}{R1}\right) \quad (1)$$

DAC = 0V の場合：

$$V_{GS}(\text{MIN}) = -\left(V_{IN} \times \frac{R2}{R1}\right) \quad (2)$$

$V_{GS}$  (MIN) は  $-7.5V$  に設定され、 $V_{IN}$  は  $5V$  に設定されます。

$$-7.5V = -\left(5 \times \frac{R2}{R1}\right) \quad (3)$$

$$\frac{R2}{R1} = 1.5 \quad (4)$$

この比率に従って R2 と R1 の値を選択します。この例では、 $R1 = 10k\Omega$ 、 $R2 = 15k\Omega$  です。R3 および R4 を計算するには、目標とする最大 DAC 値と  $V_{GS}$  値を使用します。この例では、DAC = 5V、 $V_{GS}$  (MAX) = 0V です。

$$V_{GS}(\text{MAX}) = -\left(V_{IN} \times \frac{R2}{R1}\right) + DAC \times \left(\frac{R4}{R4+R3}\right) \left(\frac{R1+R2}{R1}\right) \quad (5)$$

$$0 = -\left(5 \times \frac{15k}{10k}\right) + 5 \times \left(\frac{R4}{R4+R3}\right) \times \left(\frac{10k+15k}{10k}\right) \quad (6)$$

$$7.5 = 12.5 \times \left(\frac{R4}{R4+R3}\right) \quad (7)$$

この式を下げるとき、式 8 の抵抗比が得られます。

$$\frac{R4}{R3} = 1.5 \quad (8)$$

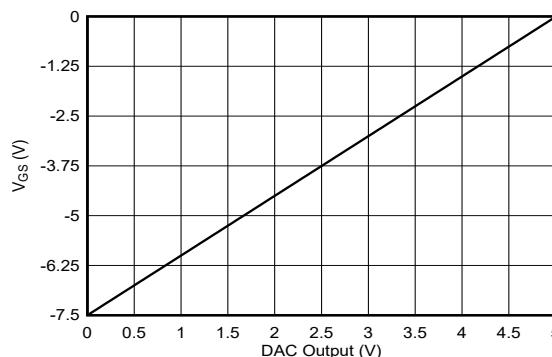

これは  $R2/R1$  と同じ比率であるため、R3 と R4 にも同じ値を使用します： $R3 = 10k\Omega$  および  $R4 = 15k\Omega$ 。図 5-2 に、これらの抵抗値による DAC と  $V_{GS}$  出力の関係を示します。

図 5-2. 差動オペアンプ出力

## 6 TDD アプリケーション向けの高速スイッチング

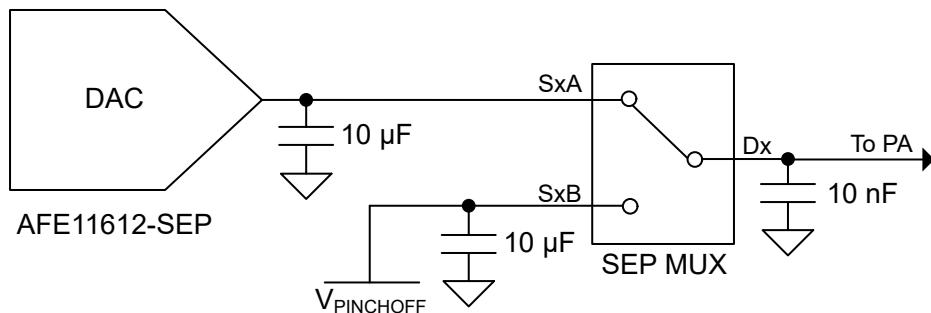

時分割の両面印刷など一部の PA バイアス アプリケーションでは、高速なオン/オフ ゲートスイッチングが必要です。高速ゲートスイッチングは、低抵抗の宇宙用マルチプレクサと容量性電荷シェアリングを使用することで実現されます。

容量性電荷共有を使用すると、高速な出力スイッチングを実現できます。図 6-1 は、入力コンデンサおよび出力コンデンサの推奨容量を示しています。2 つの入力電圧には大容量コンデンサを使用し、出力には小容量コンデンサを使用する必要があります。マルチプレクサがスイッチすると、入力コンデンサが小容量の出力コンデンサをすばやく充電し、必要な高速スイッチングを実現します。

図 6-1. ゲートスイッチング回路

## 7 $V_{DRAIN}$ スイッチング回路

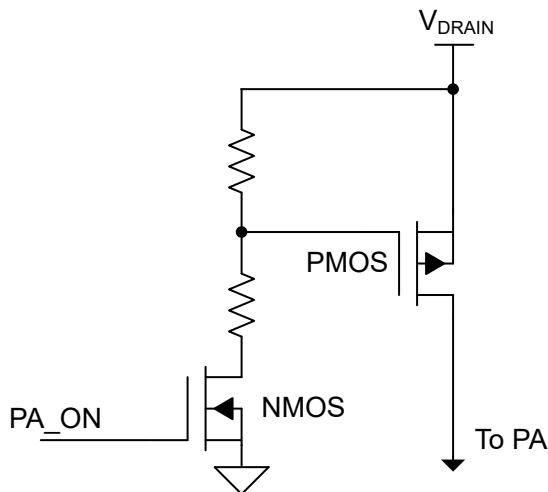

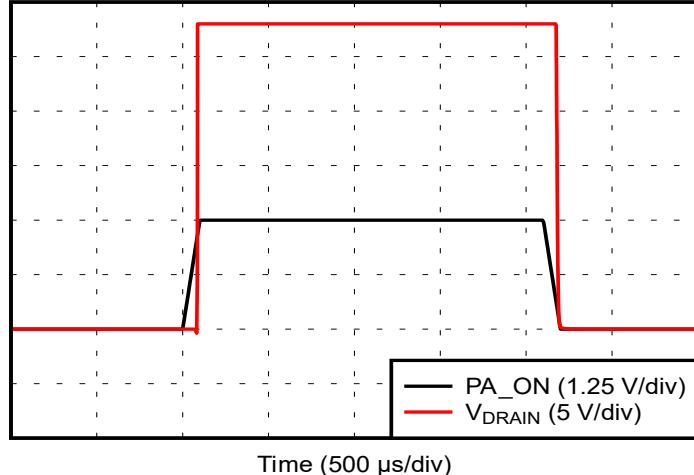

$V_{DRAIN}$  保護回路は、NMOS および PMOS ランジスタを使用して、PA ドレインに印加される電圧をディスエーブルにします。この PA\_ON 回路は高電圧スイッチとして機能します。起動、シャットダウン、アラームイベント中は、キー タイムに  $V_{DRAIN}$  をディスエーブルにする必要があります。この設計では、NMOS および PMOS 回路により、これを実現しています。NMOS ゲートに PA\_ON 電圧を印加すると、回路がオンになり、 $V_{DRAIN}$  を PMOS 経由で流れます。

図 7-1.  $V_{DRAIN}$  イネーブル回路

図 7-2.  $V_{DRAIN}$  イネーブルプロット

## 8 制御されたゲートシーケンス回路

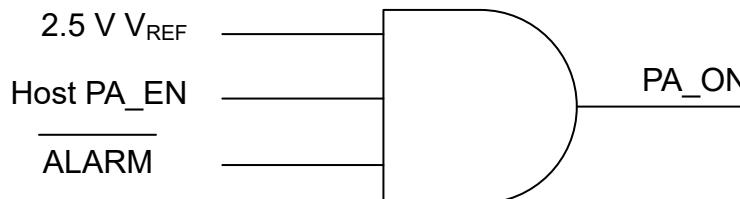

これらのイベント中に PA が損傷しないように、スタートアップ、シャットダウン、アラーム状態の間 PA を制御することが重要です。これは、主要な信号を入力とする 3 入力論理 AND ゲートを作成することで実現されます:  $V_{REF}$ 、ホスト PA\_EN、ALARM。

図 8-1. PA\_ON AND ゲート

$V_{REF}$  は、PA\_ON 出力のデバイスグッド信号として使用されます。これにより、AFE11612-SEP のスタートアップ後にホストコントローラによって  $V_{REF}$  をイネーブルにする必要があるため、PA のスタートアップ時にドレイン電圧が印加されないようにします。AFE11612-SEP がアラームを検出した場合、AFE11612-SEP 回路からの ALARM 信号は、PA\_ON を強制的に 0V することができます。最後に、ホストマイコンは PA\_ON をオフにするオプションを備えています。表 8-1 に、すべてのデジタル出力と PA\_ON との相互作用を示します。

表 8-1. PA\_ON の真理値表

| V <sub>REF</sub> | PA_EN | ALARM | PA_ON |

|------------------|-------|-------|-------|

| 0V               | X     | X     | 低     |

| X                | 0V    | X     | 低     |

| X                | X     | 0V    | 低     |

| 2.5V             | 高     | 高     | 高     |

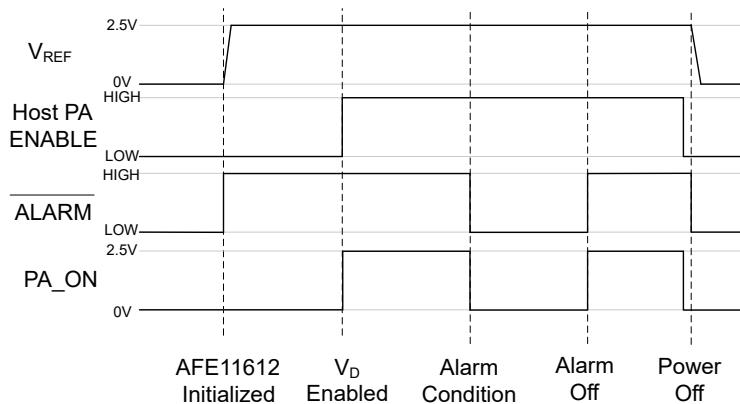

PA\_ON 電源オンシーケンスの例を以下に示します:

- AFE11612-SEP が初期化されます。ホストは  $V_{REF}$  をオンにするためのコマンドを送信します。起動時にアラーム状態がない状態で、ALARM ピンはハイインピーダンスになります。ホストは PA\_EN を Low に維持して、PA をオフに維持します。

- 次に、ドレイン電力がオンになります。ホストが PA\_EN を High に設定して、PA\_ON 信号をイネーブルにします。

- 3 番目に、アラーム条件が表示されています。ALARM は 0V になり、PA\_ON をオフにすることで PA をオフにして、PA を保護します。

- 4 番目に、アラーム状態はクリアされます。ALARM はハイインピーダンスに戻り、PA\_ON がオンになります。

- 最後に、本デバイスの電源がオフになる前に、PA\_EN を無効にして PA\_ON をオフにします。AFE11612-SEP の電源をオフにします。

図 8-2. PA\_ON 電力シーケンス制御

## 9 $V_{DRAIN}$ 監視

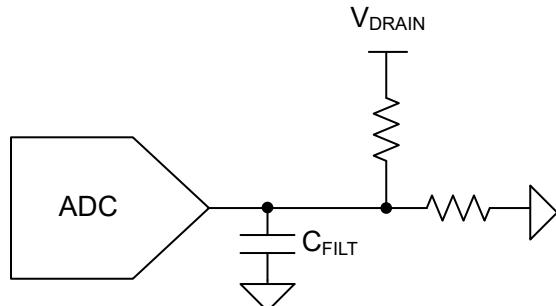

PA ドレイン電源が期待どおりの電圧で動作していることを確認するために、 $V_{DRAIN}$  電圧を監視することが重要です。これは、AFE11612-SEP に内蔵された ADC を使用して実行できます。 $V_{DRAIN}$  電圧を 5V の ADC 範囲に適切にスケーリングするには、分圧抵抗が必要です。サンプリングコンデンサを十分に充電できるように、抵抗分圧回路のインピーダンスは制限し、理想的には  $10\text{k}\Omega$  未満とする必要があります。ADC サンプリングコンデンサをすばやく充電するには、約  $1\text{nF}$  の外付けコンデンサ ( $C_{FILT}$ ) が必要です。

図 9-1.  $V_{DRAIN}$  監視回路

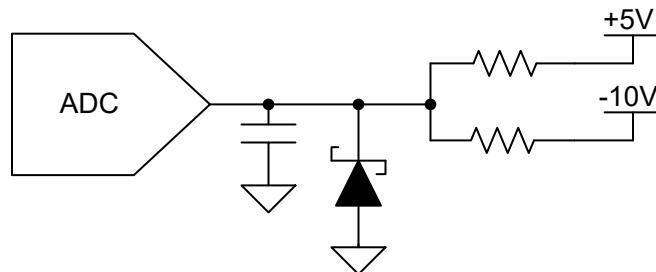

## 10 外部負電源監視

$V_{GS}$  の電位が大きすぎると、GaN PA が損傷する可能性があり、その結果、PA が飽和する可能性があります。 $V_{SS}$  電源が低下すると、差動オペアンプの出力は 0V まで下降します。したがって、電圧低下事象が発生していないか  $V_{SS}$  電源を監視することが重要です。監視は、デバイスのアナログ電源に使われる 5V などの外部リファレンス電圧をバイアスとした単純な抵抗分圧回路で実現できます。外部 5V 電源が失われた際の保護強化のために、ツェナーダイオードを挿入することができます。

図 10-1.  $V_{SS}$  監視回路

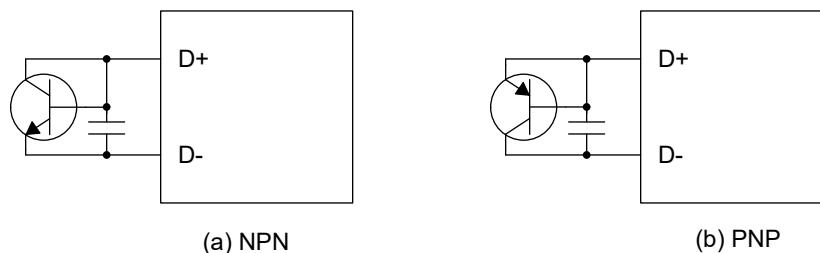

## 11 PA 温度のモニタリング

AFE11612-SEP には 2 系統のリモート温度センサ入力があり、PA 付近に配置されたダイオード接続トランジスタ 2 個の温度を監視するために使用できます。2 つの温度センサにはプログラム可能なアラーム スレッショルドがあり、アラーム状態をトリガして DAC 出力を無効化できます。

図 11-1. リモート温度回路

## 12 まとめ

パワー アンプの動作に関するニュアンスにより、ディスクリート  $V_{GS}$  補償ソリューションは複雑でコストがかかります。AFE11612-SEP はソリューションを簡素化するとともに、ゲート監視、 $V_{DRAIN}$  監視、温度監視、スタートアップおよびシャットダウン シーケンス制御用の電源電圧低下検出などの有益な機能を追加して、このデバイスに非常に優れた価値をもたらします。

表 12-1. 推奨デバイス

| デバイス         | 最適化されるパラメータ                                             | 総電離線量 (TID) 特性評価済み | シングル イベント ラッチアップ (SEL) 特性評価済み               |

|--------------|---------------------------------------------------------|--------------------|---------------------------------------------|

| AFE11612-SEP | 宇宙用途向けに強化された 12 個の 12 ビット DAC と 16 個の 12 ビット ADC 入力を搭載。 | 20krad(SI)         | 125°C において 43MeV-cm <sup>2</sup> /mg に耐性あり  |

| OPA4H199-SEP | 宇宙用途向けに強化された高電圧 4 出力オペアンプ。                              | 30krad(SI)         | 125°C 環境下で 43MeV-cm <sup>2</sup> / mg に耐性あり |

## 13 参考資料

- テキサス インスツルメンツ、[AFE11612-SEP](#) マルチチャネルの ADC、DAC、および温度センサ搭載放射線耐性のあるアナログモニタおよびコントローラデータシート。

- テキサス インスツルメンツ、[OPA4H199-SEP 40V](#)、放射線耐性強化、レールツー レール入出力、低オフセット電圧、低ノイズオペアンプ、宇宙向け強化プラスチック封止

- テキサス インスツルメンツ、[パワー アンプ FET バイアス電圧の温度補償](#)アプリケーションノート。

## 14 改訂履歴

### Changes from Revision \* (June 2023) to Revision A (September 2025)

|                                      | Page |

|--------------------------------------|------|

| • ドキュメント全体にわたって表、図、相互参照の採番方法を更新..... | 1    |

| • 未リリース製品への参照を削除.....                | 1    |

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](#) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月