*Application Note*

## プロセッサの高速パラレルインターフェイスのためのカスタム基板設計およびシミュレーションのガイドライン

**概要**

本アプリケーション ノートでは、高速パラレルインターフェース向けのカスタム基板設計およびシミュレーションに適用可能な設計ガイドラインについて説明します。

**目次**

|                                                      |    |

|------------------------------------------------------|----|

| <b>概要</b>                                            | 1  |

| <b>1 はじめに</b>                                        | 2  |

| <b>2 基板の設計およびレイアウトのガイドライン</b>                        | 2  |

| 2.1 一般的な基板設計ガイド                                      | 2  |

| 2.2 信号完全性向上のための基板設計ガイド                               | 2  |

| 2.3 カスタム基板設計シミュレーション例の説明                             | 4  |

| <b>3 カスタム基板設計シミュレーション</b>                            | 5  |

| 3.1 基板モデルの抽出                                         | 5  |

| 3.2 シミュレーションの設定                                      | 6  |

| <b>4 回路および例を含むカスタム基板設計の例</b>                         | 7  |

| 4.1 シミュレーション用語                                       | 7  |

| 4.2 さまざまなユースケースにおける OSPI インターフェイスのシミュレーション例          | 7  |

| 4.3 さまざまなユース ケースにおける RGMII インターフェイス送信データ信号のシミュレーション例 | 12 |

| <b>5 まとめ</b>                                         | 14 |

| <b>6 参考資料</b>                                        | 14 |

| <b>7 改訂履歴</b>                                        | 14 |

**商標**

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

本書には、高速パラレル インターフェイス用カスタム基板設計シミュレーションに適用可能な設計ガイドラインが含まれています。これらのインターフェイスは、さまざまなバッファタイプ (例:LVC MOS、SDIO、eMMCPHY、その他のバッファタイプ) サポートしており、端子 (ピン) に関連付けられる電気的特性を決定します。サポートされているバッファタイプについては、該当プロセッサのデータシートの『ピン属性』セクション、サポートされている動作速度については「タイミングおよびスイッチング特性」セクションを参照してください。

本ガイドラインは、eMMC (最大 HS200)、MMC SD カード、MMC SDIO、OSPI、QSPI、および RGMII (イーサネットインターフェイス) など、一般的にシミュレーション対象となる周辺装置に適用が可能です。本シミュレーションアプローチは、DPI、GPMC、SPI、その他のオンボードのペリフェラルインターフェイスにも適用が可能です。多くの周辺装置における高速パラレルインターフェイスの仕様は、JEDEC 規格に基づいています。

## 2 基板の設計およびレイアウトのガイドライン

### 2.1 一般的な基板設計ガイドライン

最適な信号 (信号完全性) の性能を実現するため、以下に示す一般的な基板設計ガイドラインに従ってください。

- すべての信号にグランドリファレンス (両側に強く推奨) が必要です。

- 信号基準プレーン内でプレーンの分割が交差しないようにします。

- デカップリングコンデンサと電源ピンをつなぐ配線は、可能な限り最大のトレース幅とすることが推奨されます。

- トレースインピーダンスをマッチングさせることにより、符号間干渉 (ISI) を最小限に抑えます (SoC または接続デバイスの推奨事項を参照)

- クロック信号やストローブ信号などの感度の高い信号を絶縁し、適切な PCB スタックアップを選択することで、クロストークを最小限に抑えます。

- 信号が層やリファレンスプレーンを切り替える際には、ステイッキングビアを追加し、帰路の不連続を回避します。

- 信号トレースと電源トレースを絶縁し、デカップリングコンデンサを使用することで、電源レールのノイズを最小限に抑えます。

- 信号接続のスタブ長は可能な限り短くします。

- クロック信号とストローブ信号の配線間隔は、クロストークを最小限に抑えるために定められたガイドラインに従ってください。

- 全ての信号線やコンデンサ (バイパス、デカップリングコンデンサ) に対して、共通のグランド (一般に GND と呼ばれる) 基準を維持します。

- マイクロストリップラインのトレースとストリップラインのトレースでは、伝搬遅延に差がある場合があります。カスタム基板設計者が、タイミング解析またはトレースのルーティングを行う際には、伝搬遅延の差を考慮することが推奨されます。

- ビアからビアへの結合は、PCB レベルのクロストークの重要な要因となる可能性があります。ビアの寸法とビア間のピッチが重要です。高速インターフェイスでは、ビア間の結合を最小限に抑えるために、グランドにシールドされたビアの使用を検討します。

- ビアスタブは信号品質に影響を及ぼす可能性があります。ユースケースに応じて、信号品質を向上させるためにビアのバックドリルを検討します。

### 2.2 信号完全性向上のための基板設計ガイドライン

信号完全性に関連する問題には、さまざまな要因が関与しています。カスタム基板レベルの信号完全性を向上させるためには、システムレベルでの解析および最適化が推奨されます。

カスタム基板の信号完全性 (信号品質) を向上させるためには、いくつかの対策オプションを検討することができます。推奨されるオプションの一部を以下に示します。

**表 2-1. 信号品質向上のためのアプローチオプション**

| オプション | 推奨事項               | 推奨事項の効果やメリット                                               |

|-------|--------------------|------------------------------------------------------------|

| A     | 直列抵抗を追加            | 信号の反射を低減し、信号品質を向上できます                                      |

| B     | コンデンサを追加 (負荷付近に配置) | リターン信号の反射を低減できます。両端にバランスを取ったコンデンサを配置することで、全体の反射をさらに抑制できます。 |

| C     | 信号トレース長を延長         | 信号が遷移中でも、位相の異なる反射が入射信号に与える影響を低減できます。                       |

表 2-1. 信号品質向上のためのアプローチオプション (続き)

| オプション | 推奨事項                       | 推奨事項の効果やメリット                                                        |

|-------|----------------------------|---------------------------------------------------------------------|

| D     | 高速駆動強度を設定し、A、B、C の組み合わせを使用 | 信号の立ち上がり/立ち下がりを向上し、アイバターン全体を向上します。また、A、B、C の組み合わせによる信号反射低減効果も得られます。 |

以下の図は、信号完全性向上のための一般的なガイドラインです。

図 2-1. データ ラインに直列抵抗を追加

図 2-2. クロックラインに負荷コンデンサを追加

図 2-3. データ ライン上でオプション A とオプション B を組み合わせ

## セットアップおよび測定に関する注意事項:

- プロセッサおよび接続デバイス(デバイスとも呼ばれます)のIBISモデルが使用されています

- .SOPファイル(SIシミュレーションを実施するために、抽出ツールを用いてカスタム基板から抽出したファイル)

- 信号完全性分析ツール(2.5D)

- アイパターンプロットツール

## 注

表示のアイダイアグラムは、接続デバイスのBGAパッドで測定した結果をプロットしたものです。

この解析と例は書き込み操作のためのものです。読み取り操作のシミュレーションにも同じガイドラインを適用できます。

## 2.3 カスタム基板設計シミュレーション例の説明

本セクションでは、カスタム基板設計者が信号品質を向上させるためのガイドラインを示します。

$C_{LOAD}$ は、接続デバイスの総容量性負荷(書き込みのシミュレーションの場合は周辺装置の入力ピンで測定、読み取りの場合はSoCの入力ピンで測定)を示します。

例: $C_{LOAD}$ が約3pFの場合:

オプション1:トレース長を短く保つ(約0.5インチ~0.6インチ)とともに、信号トレースの中点に低抵抗値(10Ωまたは22Ω)の直列抵抗を追加(挿入)します。

オプション2:トレース長が1インチ以上、5インチ未満の場合は、以下のオプションを考慮してください。

A:オプション1と同様に、トレース中点に抵抗を追加します。

B:接続デバイスのBGAパッド付近に、低容量の集中コンデンサを追加します(必要容量に近い標準値、例:2pF、3pFを使用)。

オプション3:オプション1と2が実施困難な場合は、接続デバイス仕様で許容される最大トレース長まで延長します(例:6インチ)。トレース長の延長に加えて、さらにオプション2-Bと同様の小容量集中コンデンサも使用可能です。

## 注

上記に示したオプションは、信号品質向上のために考えられる一例です。オプション1は、全体的な信号品質を向上させることが予想されます。カスタム基板の設計者は、シミュレーションを実行し、説明されているオプションのうち、特定のシステムレベルのユースケースに対してどのオプションが最適か評価することが推奨されます。

## 3 カスタム基板設計シミュレーション

### 3.1 基板モデルの抽出

以下に示す基板モデル抽出のガイドラインは、あらゆる EDA 抽出ツールで利用できるように意図されており、特定のツールに依存するものではありません。S パラメータの抽出完了後は、[セクション 3.2](#) に記載されている手順に従います。シミュレーションを実行する前に、カスタム基板設計が以下の手順に従っていることを確認することが推奨されます。

- 信号抽出には、2.5D 抽出ツールを使用できます

- カスタム基板層スタックアップの場合は、推奨される層の厚さと PCB 基板材料に従ってください。

- シミュレーション時間を短縮する目的で、基板レイアウトの必要な部分を抽出前にクリップする場合、信号および電源トレイスから少なくとも 0.25 インチ以上離れた位置でクリップ境界を定義することが推奨されます。

- サプライヤ提供の S パラメータまたは RLC パッケージモデルを使用し、シミュレーションを続行します。

#### 3.1.1 IBIS モデルおよび抽出された基板モデルを用いたシミュレーション

高速パラレルインターフェースのシミュレーションを実施するためのガイドラインは、以下のセクションに示します。チャネル(グループ)のシミュレーション(例:データライン)は、IBIS モデルおよび抽出済み基板モデルを用いて、ターゲットとなるデータパターンに基づいて実施され、信号波形およびアイパターンを生成します。シミュレーション結果については、接続デバイスのデータシートに定義されたセットアップ/ホールド時間、スルーレート、クロックの high/Low、その他のパラメータを確認することが推奨されます。VIH/VIL 電圧レベルに関するリングバックの追加チェックを実施することも推奨されます。

### 3.2 シミュレーションの設定

以下の手順で IBIS シミュレーションをセットアップします:

- TI.com の SoC 固有の製品ページにある SoC IBIS モデルを入手して使用し、接続デバイス (メモリ、EPHY) の IBIS モデルについてはサプライヤーに依頼してください。IBIS モデルには、パッケージ RLC モデルが含まれることが想定されています。

- カスタム基板上の信号の S パラメータファイルを抽出します。

- 3D 抽出ツールの使用が推奨されます。シミュレーション中に実行時間の制限があるため、3D 抽出ツールを使用できない場合があります。実行時間が問題の場合は、2.5D 抽出ツールを使用することが推奨されます。

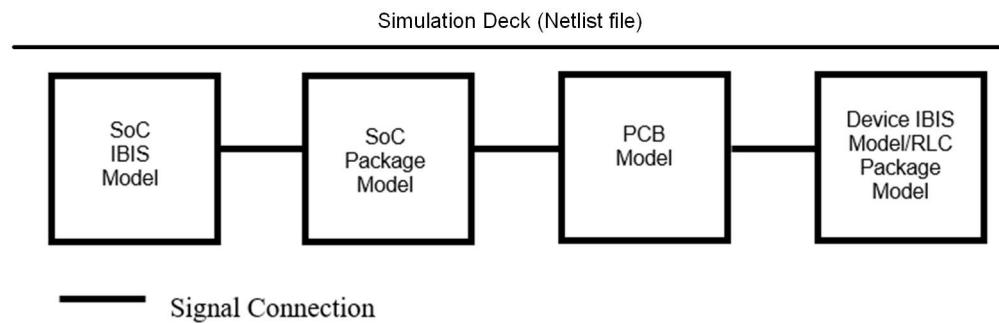

- 使用するシミュレーションツールのガイドラインに従って、シミュレーション ネットリストを構築します

- SoC IBIS モデル、基板モデル、接続デバイスの IBIS モデルを設定します (シミュレーションデッキを構成します)

- シミュレーションが必要なプロセス、電圧、温度の各コーナー条件を設定します。

SoC の IBIS モデルでサポートされるすべてのプロセス、電圧、温度条件にわたってシミュレーションを行うことが推奨されます。

- 標準値

- 最小値

- 最大値

- シミュレーション結果を波形解析ツールで確認し、接続デバイスのデータシートに示された合否判定基準 (仕様) を使用します。

図 3-1. システムレベル シミュレーションの設定手順

## 4 回路および例を含むカスタム基板設計の例

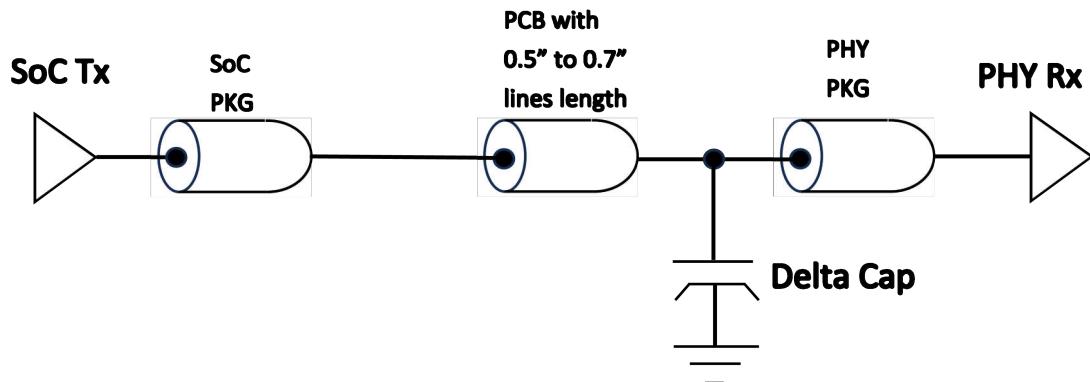

基板の変更には、データ信号およびクロック信号に対して、グラウンドに接続される追加のコンデンサ（デルタコンデンサと呼ばれます）を配置する変更が含まれます。SoC と接続デバイスの IBIS モデルに含まれる C\_Comp 値と、SoC と接続デバイスのピン容量値の合計の差が、デルタコンデンサの値となります（計算例を以下の表に示します）。信号ラインとクロックラインにデルタコンデンサを追加することで、信号の反射を低減し、リングバック違反を最小限に抑えることができます。

C\_Comp (典型 (Typ) 値) を用いたデルタコンデンサ値の計算例：

| SoC IBIS モデル |                 | 接続デバイス (デバイス) IBIS モデル |            |                 |            |            |

|--------------|-----------------|------------------------|------------|-----------------|------------|------------|

| C_pin (pF)   | C_Comp (Typ) pF | C Total pF             | C_pin (pF) | C_Comp (Typ) pF | C Total pF | C Delta pF |

| 1.582        | 4.812           | 6.394                  | 1.076      | 1.72            | 2.796      | 3.598      |

### 4.1 シミュレーション用語

C\_COMP — バッファダイのピン容量で、各バッファのタイプごとに固有の値

リングバック波形のリングング、オーバーシュート/アンダーシュート

### 4.2 さまざまなユース ケースにおける OSPI インターフェイスのシミュレーション例

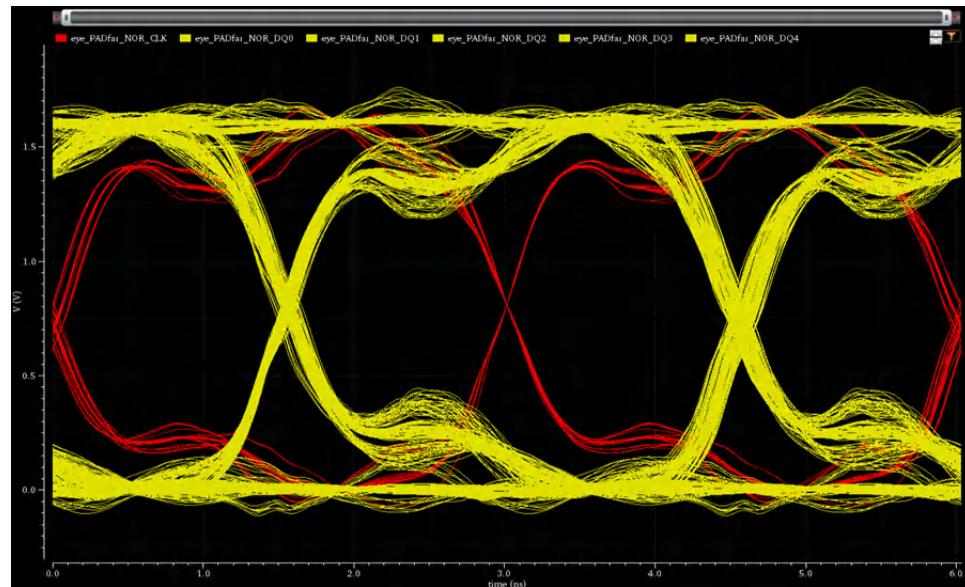

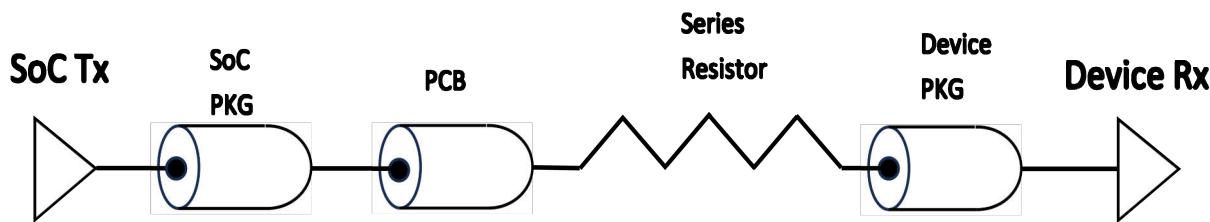

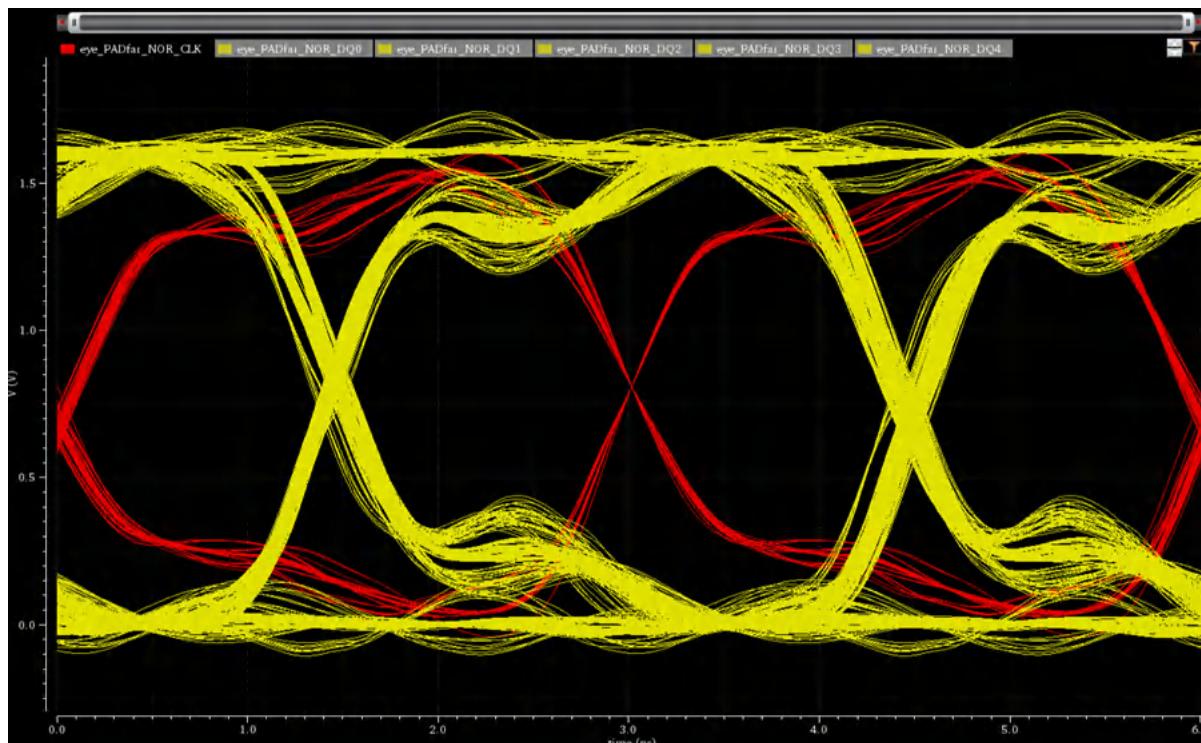

**事例 1：**下図は、ベースラインシステムの解析結果を示しています。ベースラインシステムは、接続メモリデバイスのデータシートに定められているセットアップ時間とホールド時間（タイミング）の要件を満たしておらず、データラインとクロックラインにリングバックが発生しています。

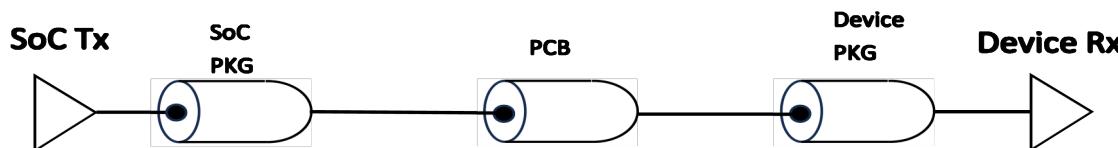

図 4-1. ベースラインシステムの回路図

図 4-2. ベースラインシステム解析の波形

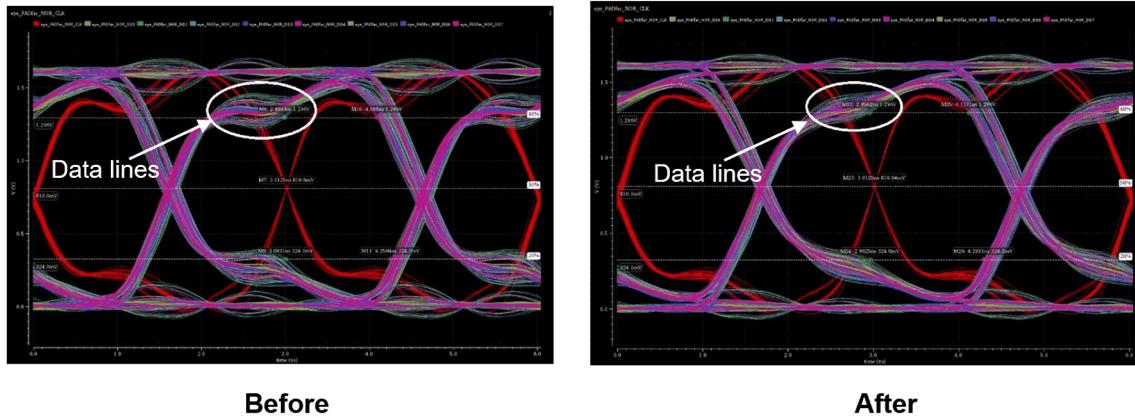

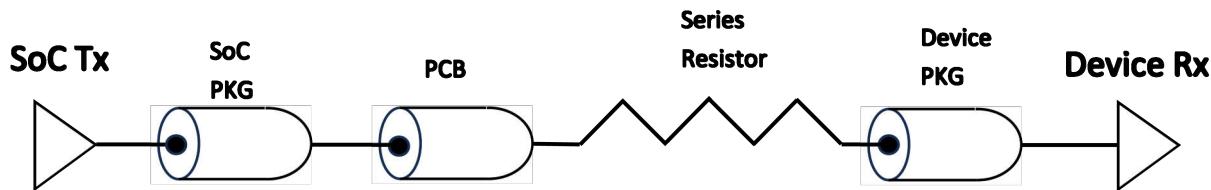

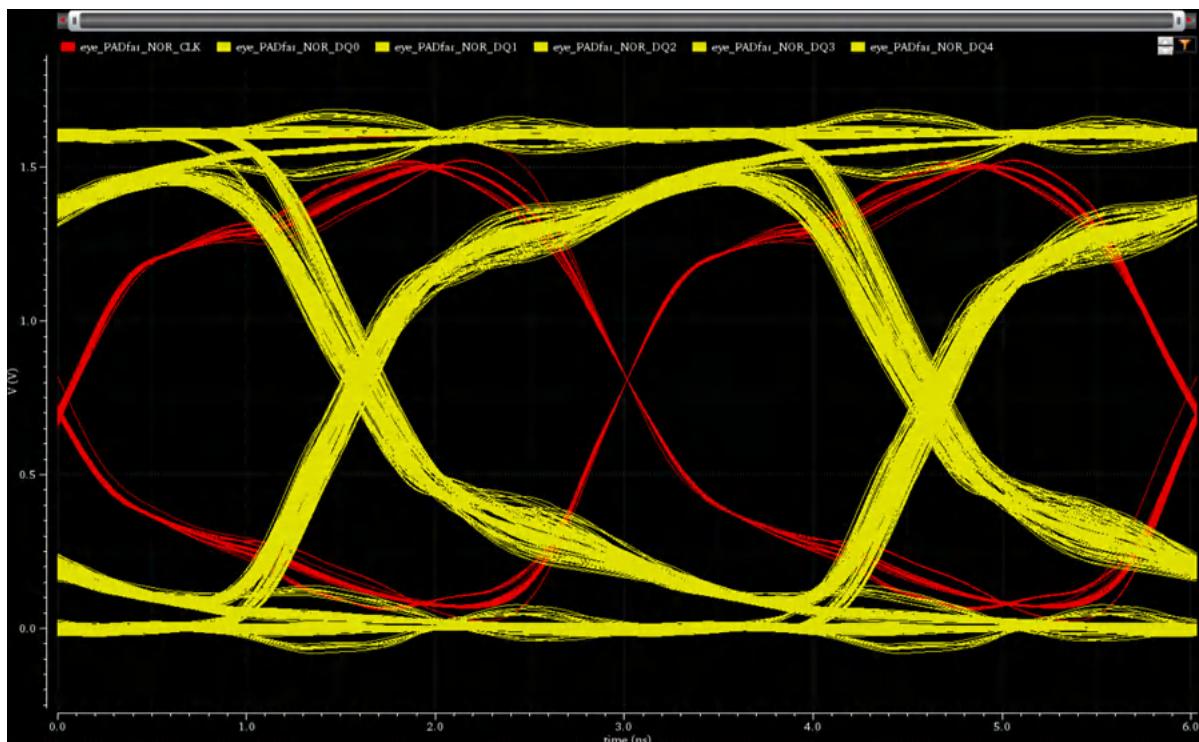

**事例 2:** 下図は、SoC と接続メモリデバイス間のデータインターフェイス信号に、SoC 側付近で  $10\Omega$  の直列抵抗を追加した場合の解析結果を示しています。データライン上のリングバックが低減され、信号品質が向上しています。

図 4-3. ベースラインシステムのデータラインに直列抵抗を追加した回路図

図 4-4. ベースラインシステムのデータラインに追加された直列抵抗の波形

**事例 3:** 下図は、SoC と接続メモリデバイス間のクロック信号に、SoC 側付近で  $10\Omega$  の直列抵抗を追加した場合の解析結果を示しています。クロック信号上のリングバックが低減され、信号品質が向上しています。

図 4-5. ベースラインシステムのクロックラインに直列抵抗を追加した回路図

図 4-6. ベースラインシステムのクロック信号に追加された直列抵抗の波形

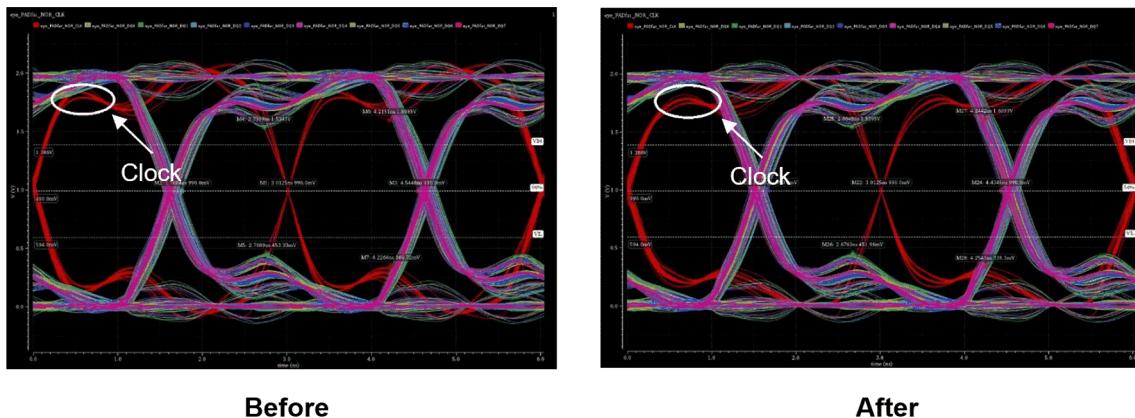

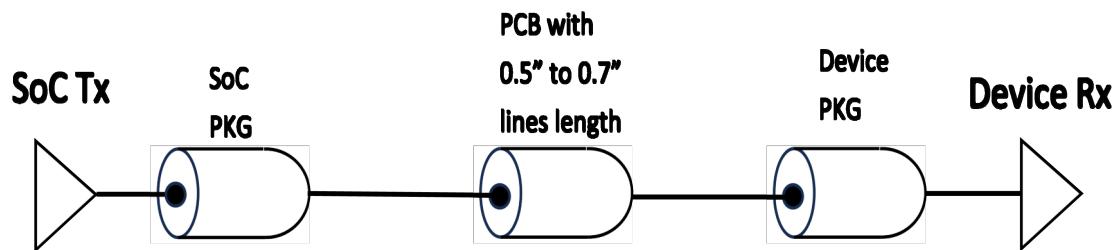

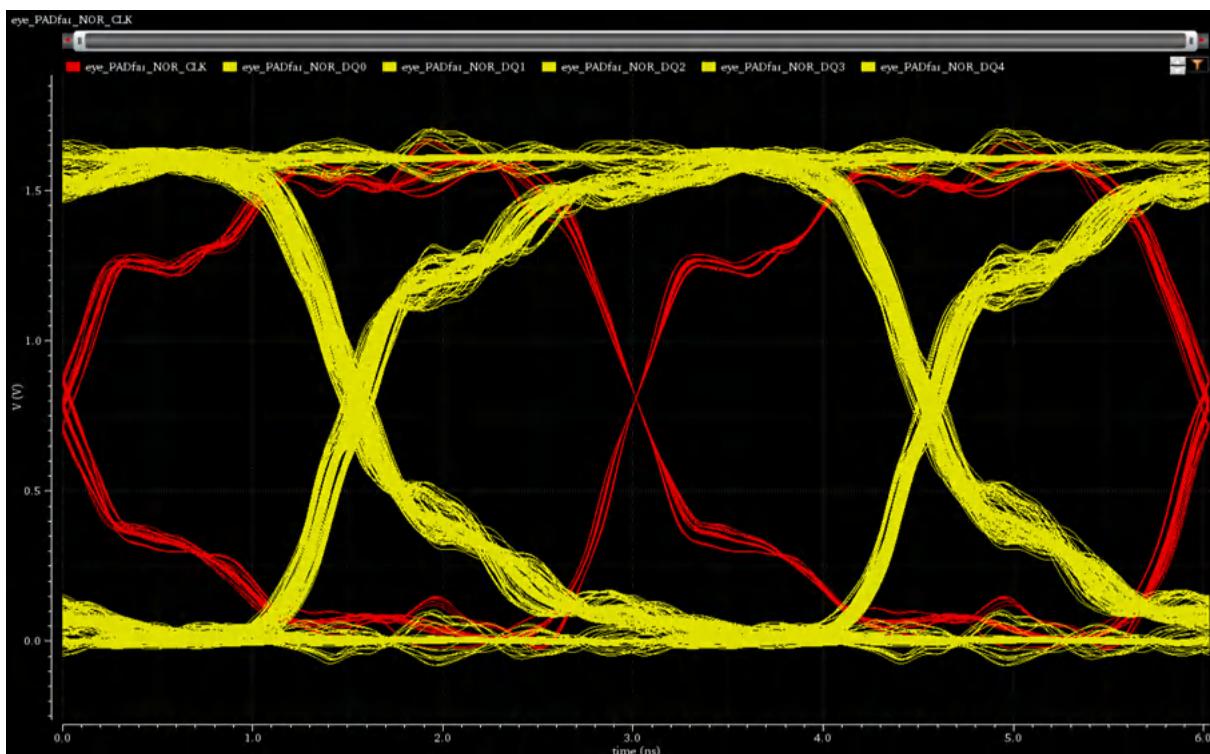

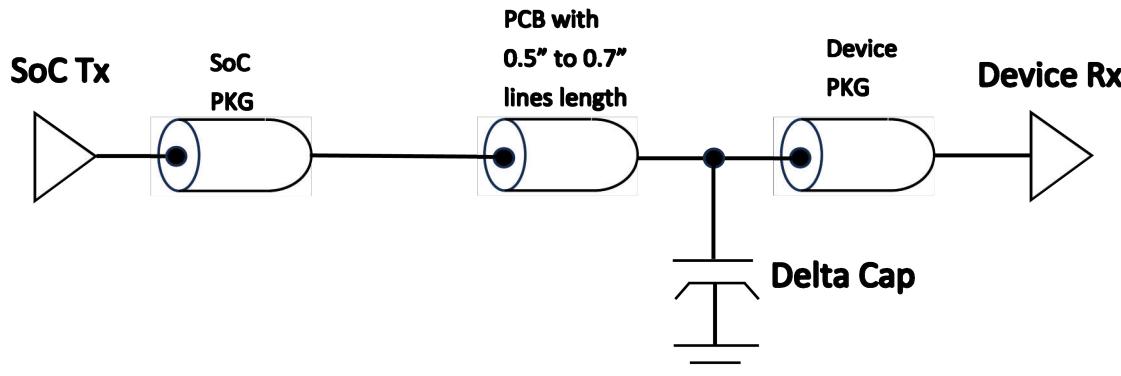

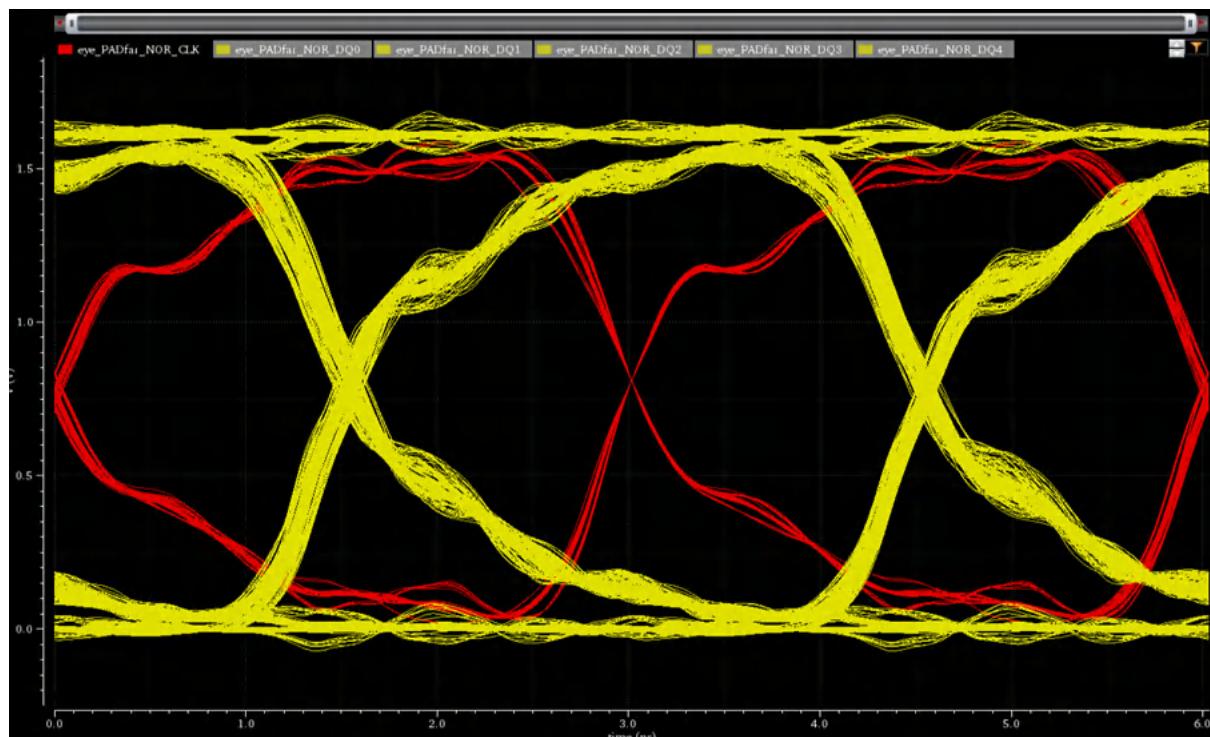

**事例 4:** 下図は、すべてのデータラインとクロックラインのトレース長を 0.5 インチ ~ 0.7 インチに短縮した場合の解析結果を示しています。変更後の回路は、接続メモリデバイスのデータシートに定められているセットアップ時間とホールド時間の要件を満たしています。また、この構成では、データラインおよびクロックライン上の信号反射が低減されています。

図 4-7. 0.5 インチ ~ 0.7 インチのトレース長にした回路図

図 4-8. 0.5 インチ ~ 0.7 インチのトレース長にした場合の波形

**事例 5:** 下図は、データラインにおいて、SoC と接続メモリデバイス (OSPI メモリ) 間のトレース長を 0.5 インチ ~ 0.7 インチに短縮し、デルタコンデンサ **c\_comp** を追加した場合の解析結果を示しています。デルタコンデンサは、接続デバイスの BGA パッド付近にできるだけ近接して配置することが推奨されます。

この構成では、仕様に定められたセットアップ時間とホールド時間の要件を満たしていません。

図 4-9. PCB 上の BGA パッド付近 (接続メモリのデータラインおよびクロックライン) にデルタ C\_Comp コンデンサを追加し、トレース長を 0.5 インチ ~ 0.7 インチとしたベースラインシステムの回路図

図 4-10. PCB 上の BGA パッド付近 (接続メモリのデータラインおよびクロックライン) にデルタ C\_Comp コンデンサを追加し、トレース長 0.5 インチ ~ 0.7 インチとした場合の波形

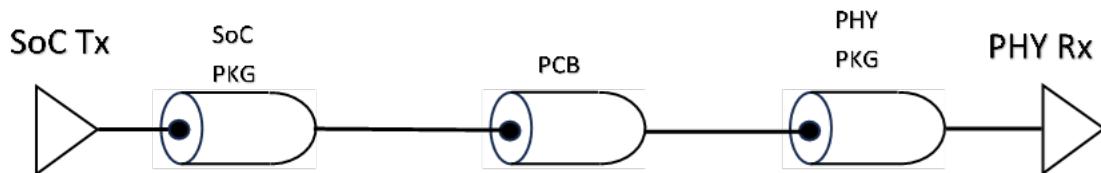

#### 4.3 さまざまなユース ケースにおける RGMII インターフェイス送信データ信号のシミュレーション例

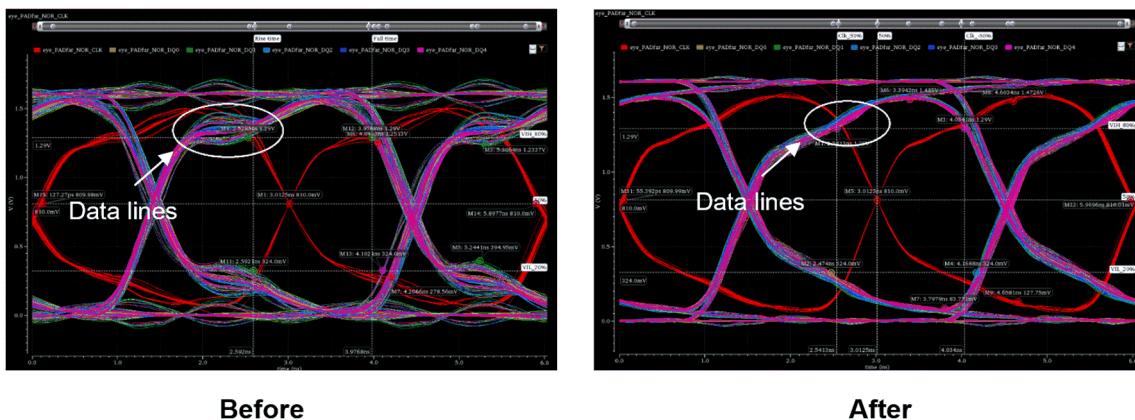

**事例 1:** 下図はベースライン解析の結果を示しています。ベースライン解析は、RGMII 仕様に定められたセットアップ時間とホールド時間の要件を満たしています。波形には、データラインとクロックライン上に反射が見られます。

図 4-11. ベースラインシステムの回路図

図 4-12. ベースラインシステム解析の波形

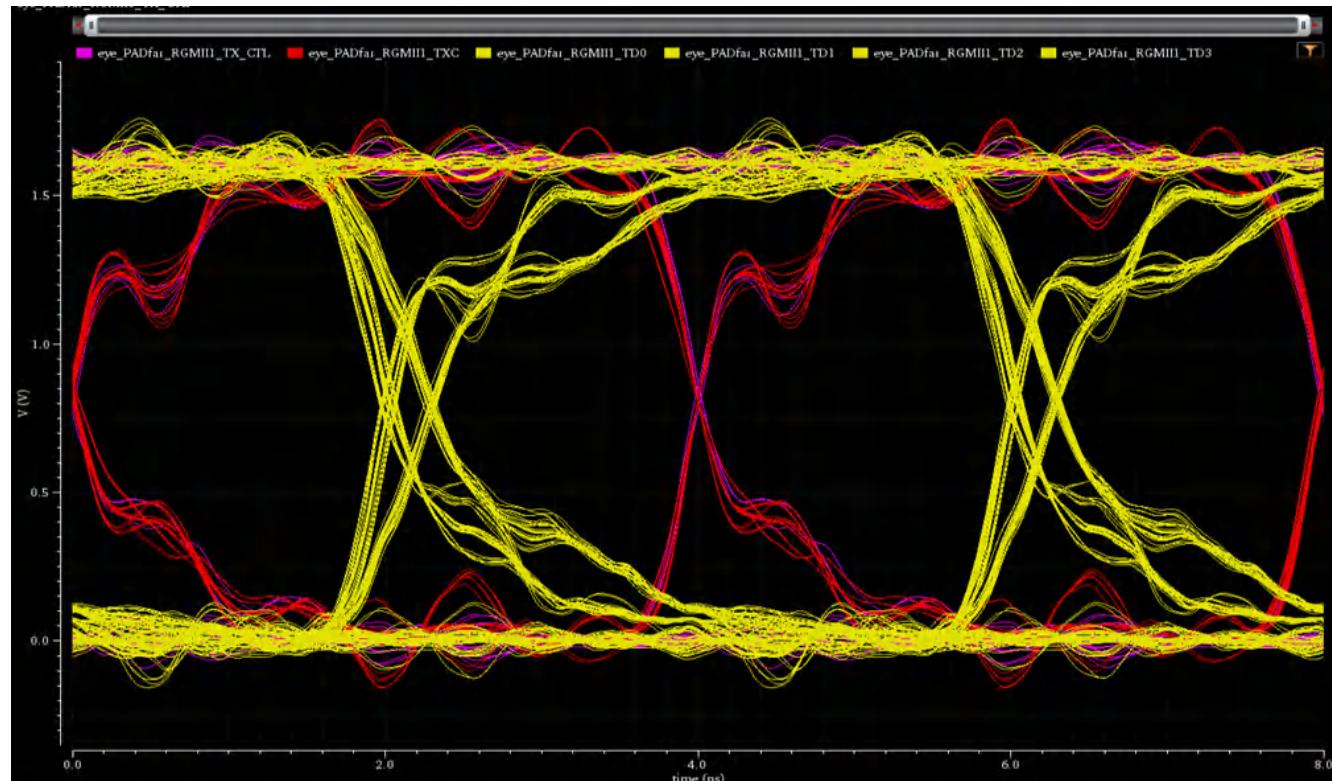

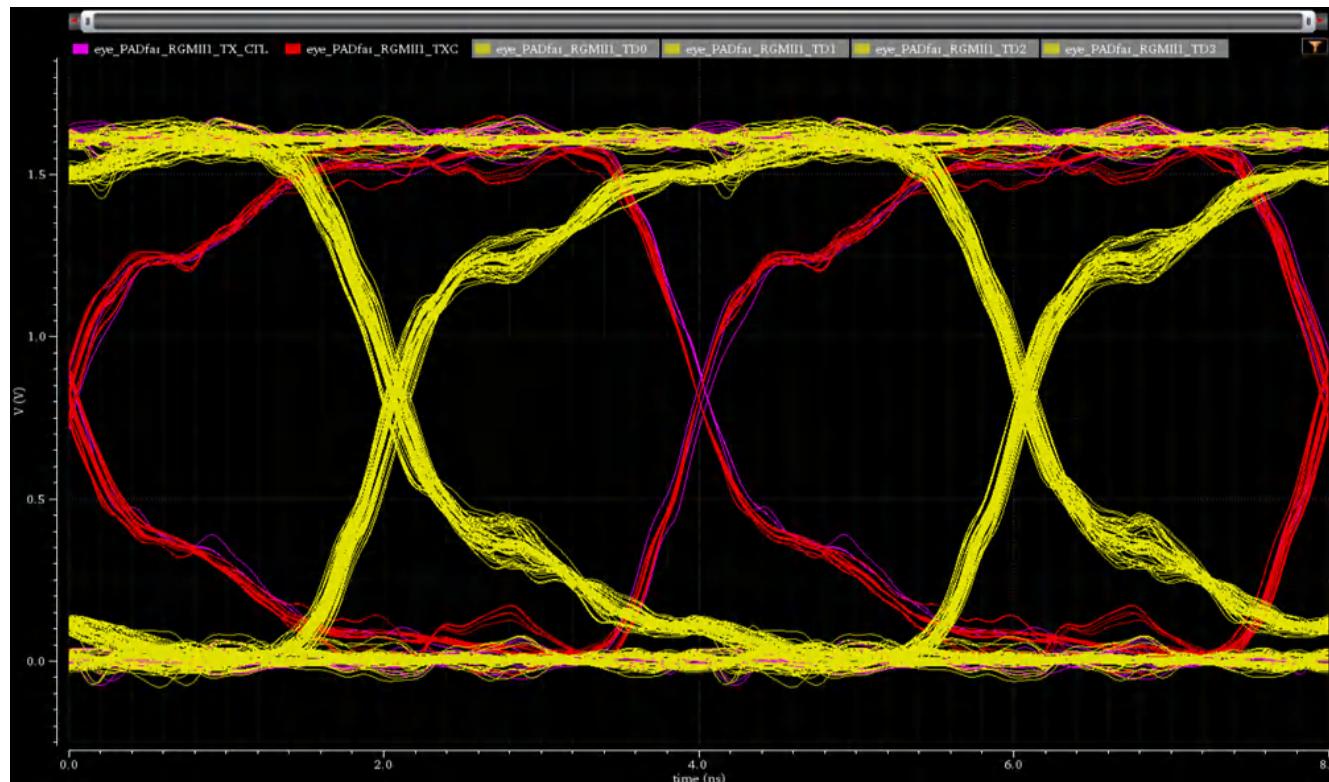

**事例 2:** 下図は、SoC と接続デバイス (EPHY) の間のすべての送信データ信号 (TD0, TD1, TD2, TD3) および送信クロック信号にデルタコンデンサ **c\_comp** を追加した場合の解析結果を示しています。デルタコンデンサは、接続デバイスの BGA パッド付近にできるだけ近接して配置することが推奨されます。コンデンサを追加により、信号反射が低減され、信号品質が向上しています。

図 4-13. PCB 上の接続デバイス BGA パッド付近 (データラインおよびクロックライン) にデルタ C\_Comp コンデンサを追加したベースラインシステムの回路図

図 4-14. ベースラインシステムにおいて、PCB 上の接続デバイス BGA パッド付近 (データラインおよびクロックライン) にデルタ C\_Comp コンデンサ (4.7pF) を追加した場合の波形

## 5 まとめ

本アプリケーションレポートでは、高速パラレルインターフェースを正常に動作させるためのカスタム基板レイアウトの計画、配線、およびシミュレーション方法について説明します。カスタム基板設計者は、対象システムのユースケースに最適な構成を選定するため、シミュレーションを実施し、各種シミュレーションオプションを評価することを推奨します。

## 6 参考資料

1. テキサスインスツルメンツ [AM62Px eMMC HS400 基板の設計およびシミュレーションのガイドライン](#) アプリケーションノート。

2. 縮小ギガビットメディア非依存インターフェース (RGMII) - EIA/JESD 8-6 1995。

3. [AM625/AM623/AM620-Q1/AM62L/AM64x/AM243x \(ALV\)/AM62Ax/AM62D-Q1/AM62Px の基板レイアウト](#) 一般的な高速レイアウトガイドライン関連文書へのリンク

4. [高速インターフェイスレイアウト ガイドライン](#)

## 7 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

### Changes from SEPTEMBER 30, 2025 to FEBRUARY 28, 2026 (from Revision \* (September 2025) to Revision A (February 2026))

|                                                | Page |

|------------------------------------------------|------|

| • タイトルを更新。                                     | 0    |

| • 『はじめに』セクションを更新。                              | 2    |

| • 『一般的な基板設計ガイドライン』セクションを更新。                    | 2    |

| • 『信号完全性向上のための基板設計ガイドライン』セクションを更新。             | 2    |

| • 『カスタム基板設計シミュレーション例の説明』セクションを更新。              | 4    |

| • 『基板モデルの抽出』セクションを更新。                          | 5    |

| • 『IBIS モデルおよび抽出された基板モデルを用いたシミュレーション』セクションを更新。 | 5    |

| • 『シミュレーションの設定』セクションを更新。                       | 6    |

| • 『回路および例を含むカスタム基板設計の例』セクションを追加。               | 7    |

| • 『参照資料』セクションを更新。                              | 14   |

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](#) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2026, Texas Instruments Incorporated

最終更新日：2025 年 10 月