# Application Note

## AM62Lx の電源実装

Brenda Diaz

### 概要

このアプリケーションノートでは、さまざまな使用事例と低消費電力モードに対応する AM62L 電源の実装について説明します。このドキュメントの電力供給ネットワーク (PDN) は、テキサスインスツルメンツ AM62L Sitara プロセッサを使用するアプリケーションに PMIC または個別の電源設計を統合するためのガイドとして使用できます。設計プロセスを支援するために、サンプル供給とデジタル図が提供されます。設計プロセスを支援するために必要なご質問や技術サポートについては、[TI E2E™ 設計サポートフォーラム](#)をご利用ください。

### 目次

|                                   |    |

|-----------------------------------|----|

| 1はじめに                             | 3  |

| 2パワー マネージメント IC (PMIC) の概要        | 4  |

| 3低消費電力モードと電源最適化                   | 5  |

| 3.1 PDN#1: BOM サイズとコストに最適化された電源設計 | 6  |

| 3.2 PDN#2: 中断電力を最小限に抑え最適化された電源設計  | 9  |

| 3.3 PDN#3: 完全に柔軟な電源設計             | 12 |

| 3.4 PDN#4: DDR4 の電源実装             | 14 |

| 4パワーアップ シーケンス                     | 17 |

| 5電源オフ シーケンス                       | 18 |

| 6まとめ                              | 19 |

| 7参考資料                             | 19 |

| A付録 A: PDN#1 のディスクリート電源実装         | 20 |

| B改訂履歴                             | 22 |

### 図の一覧

|                                           |    |

|-------------------------------------------|----|

| 図 2-1. TPS65214 の機能ブロック図                  | 4  |

| 図 3-1. BOM サイズとコストに最適化された AM62L PDN       | 6  |

| 図 3-2. PDN#1 の SoC - PMIC デジタル接続          | 7  |

| 図 3-3. PMIC BOM の例                        | 8  |

| 図 3-4. 中断電力を最小限に抑えるように最適化された AM62L PDN    | 9  |

| 図 3-5. PDN#2 の SoC - PMIC デジタル接続          | 10 |

| 図 3-6. AM62L 完全に柔軟な PDN                   | 12 |

| 図 3-7. PDN#3 の SoC - PMIC デジタル接続          | 13 |

| 図 3-8. DDR4 の電源実装                         | 14 |

| 図 3-9. DDR4 用デジタル接続の使用事例                  | 15 |

| 図 4-1. AM62L のパワーアップ シーケンス                | 17 |

| 図 5-1. AM62L のパワーダウン シーケンス                | 18 |

| 図 A-1. BOM サイズおよびコストのディスクリート実装に最適化された PDN | 20 |

| 図 A-2. ディスクリート BOM の例                     | 21 |

| 図 A-3. ロジックの実装の例                          | 21 |

### 表の一覧

|                               |    |

|-------------------------------|----|

| 表 1-1. AM62L のパワー アーキテクチャ機能   | 3  |

| 表 3-1. AM62L 電源供給ネットワーク (PDN) | 5  |

| 表 3-2. TPS6521401 デジタル構成      | 11 |

| 表 3-3. TPS6521402 デジタル構成      | 16 |

TI E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

AM62L Arm ベース プロセッサは、幅広い産業用および汎用アプリケーション向けに設計された低コストで電力効率に優れたシステムオンチップ (SoC) です。AM62L プロセッサは 2 つの ARM Cortex-A53 コアを搭載し、セキュア ブートなどの必要なセキュリティ機能を備えた堅牢なコンピューティングを提供します。このデバイスは、スケーラブルなソフトウェア開発キット (SDK)、オープンソース ハードウェア、設計ツールを使用した迅速かつ効率的な開発を可能にします。この SoC は、スマートメーター、EV 充電、IOT ゲートウェイ、産業用 HMI、患者モニタリングなど向けに設計されています。

AM62L は、消費電力の低減、BOM コストの削減、柔軟な電源設計を可能にするパワー マネージメントアーキテクチャを使用して開発されました。このパワー アーキテクチャでは、メイン CORE (VDD\_CORE)、RAM (VDDR\_CORE)、DDR PHY IO (VDDS\_DDR)、VDDA アナログ電源 (適切なフィルタリングにより 1.8V の IO と組み合わせることも可能)、および 1.8V / 3.3V の IO 電源に電力を供給するために 4 ~ 5 個の外部レギュレータが必要です。表 1-1 に、SoC パワー アーキテクチャの利点のいくつかを示します。

### 注

ユーザー ガイド、アプリケーション レポート、またはその他の参考資料の間に矛盾がある場合は、データ シートの仕様が最終的な情報源となります。

**表 1-1. AM62L のパワー アーキテクチャ機能**

| パワー アーキテクチャの特長 | 利点                                                                                                                                               |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| ✓ 低消費電力モード     | 4 つの低消費電力モード (RTC のみ、RTC + IO + DDR、DeepSleep、スタンバイ) により、消費電力が大幅に削減され、電力効率が向上し、バッテリー寿命が長くなります。                                                   |

| ✓ アクティブ電源      | 低いアクティブ電源と OS アイドルにより、アクティビティの少ない使用時に電力を削減できます。                                                                                                  |

| ✓ CORE 電圧      | 0.75V 固定 CORE 電圧供給による差別化された低消費電力機能により、最大 1.25GHz デュアル A53 をサポートします。                                                                              |

| ✓ 電圧ドメイン       | シングル CORE 電圧ドメインにより、低コストの電力設計とパワー マネージメントのためのよりシンプルなソフトウェア制御が可能になります。                                                                            |

| ✓ 内部デュアル電圧 LDO | 1.8V に切り替えて SD カード インターフェイスに電源を供給し、UHS-I 速度をサポートできる 3.3V LDO (SDIO) を統合しています。この内部 LDO により、設計者は外部デュアル電圧 LDO が不要になり、BOM サイズとコストを削減できます。            |

| ✓ 電源の実装        | 柔軟な電源シーケンスと電源統合により、PMIC または個別電源の実装が簡素化され、BOM サイズとコストを削減する最適化が可能になります。                                                                            |

| ✓ コンパニオン PMIC  | TPS65214 は、AM62L に電力を供給するために開発された、3.5mm x 3.5mm のコストとスペースが最適化されたパワー マネージメント IC (PMIC) です。これは統合されたスーパーバイザとシーケンサであり、すべての電源レールを監視し、シーケンスを完全に制御できます。 |

## 2 パワー マネージメント IC (PMIC) の概要

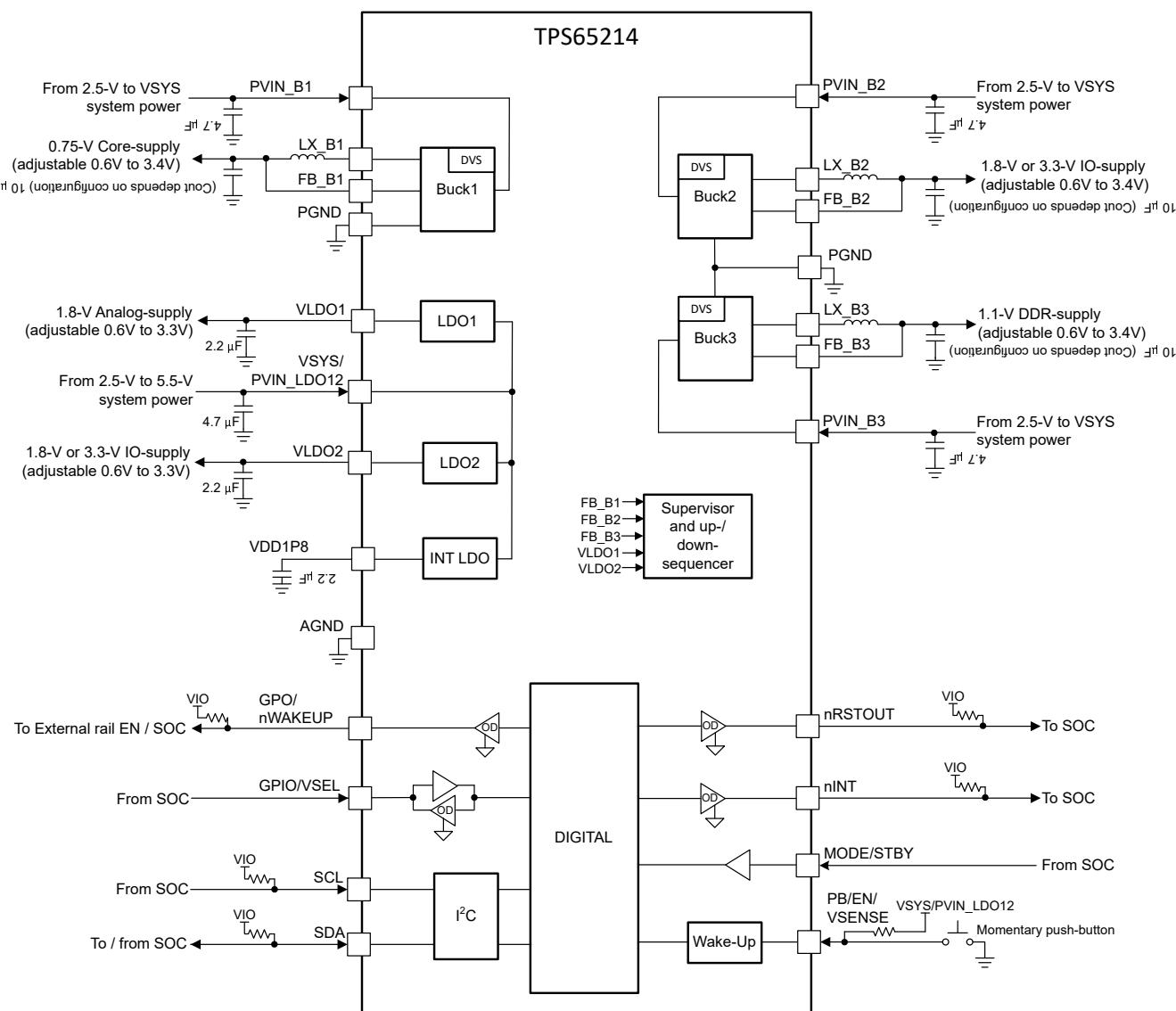

TPS65214 PMIC には、3 つの Buck レギュレータと 2 つの Low ドロップアウト レギュレータ (LDO) の 5 つのレギュレータが含まれています。Buck コンバータは、Buck1 で最大 2A、その他の降圧レギュレータでそれぞれ 1A をサポートします。LDO1 は最大 300mA の出力電流をサポートし、LDO2 は最大 500mA の出力電流をサポートします。両方の LDO は、負荷スイッチとして構成することもできます。この PMIC は VIN 範囲が 2.5V ~ 5.5V と広く、3.3V または 5V の一般的なシステム電圧をサポートします。図 2-1 に、各アナログリソースの電圧および電流能力の概要を示します。

TPS65214 PMIC は、I<sup>2</sup>C インターフェイス、2 つの GPIO ピン、および 3 つの多機能ピンを備え、AM62L SoC と主要ペリフェラルに電力を供給するため 最大出力パッケージを提供します。

TPS65214 デバイスには、さまざまなアプリケーションのユースケースをサポートするために、独自の OTP 設定を備えたさまざまな注文可能な型番 (OPN) があります。各 TPS65214 デバイスは、型番と TI\_DEV\_ID/NVM\_ID レジスタフィールドで区別されます。型番の 9 - 10 行目は、デフォルトの OTP 設定を表します。たとえば、TPS6521401 には AM62L SoC の電圧およびシーケンシング要件をサポートするための独自の OTP 設定があります。

### 注

TPS6521401 は、[AM62L EVM](#) で使用されます。

図 2-1. TPS65214 の機能ブロック図

### 3 低消費電力モードと電源最適化

AM62L には、以下の低消費電力モードがあります。RTC のみ、RTC + IO + DDR、ディープスリープおよびスタンバイを提供します。各低消費電力モードとサポートされているウェークアップ源の詳細については、**AM62L テクニカルリファレンスマニュアル**の電源セクションを参照してください。高レベルでは、RTC のみの設定では、RTC レール (VDDS\_RTC / VDD\_RTC) がオンのままであり、残りの電源レールはオフになります。RTC + IO + DDR の設定では、メインコア (VDD\_CORE) と 1.8V アナログ (VDDA) はオフになり、残りのレールはオンのままであります。これに対して、ディープスリープおよびスタンバイをサポートする場合、すべての外部電源レールはオンのままであります。**表 3-1** に、必要な低電力モードに基づいて AM62L + LPDDR4 に電力を供給するための、異なる電力最適化を実現する 3 つの PDN を示します。この表には、DDR4 を使用した電源実装の PDN も含まれています。

低消費電力モードを使用しないアプリケーションの場合: 合計 3.3V の IO 電流が 500mA よりも低い場合は、PDN#1 を推奨します。合計 3.3V の IO 電流が 500mA よりも大きい場合は、PDN#2 を推奨します。

**表 3-1. AM62L 電源供給ネットワーク (PDN)**

| 電源の最適化                                | メモリ    | サポートされる低消費電力モード |                |          |       |

|---------------------------------------|--------|-----------------|----------------|----------|-------|

|                                       |        | RTC のみ          | RTC + IO + DDR | ディープスリープ | スタンバイ |

| 最小 BOM サイズとコスト (PDN#1) <sup>(1)</sup> | LPDDR4 |                 |                | ✓        | ✓     |

| 最小中断電力 (PDN#2) <sup>(2)</sup>         | LPDDR4 |                 | ✓              | ✓        | ✓     |

| 完全に柔軟な設計 (PDN#3) <sup>(2)</sup>       | LPDDR4 | ✓               | ✓              | ✓        | ✓     |

| DDR4 の電源図 (PDN#4) <sup>(3)</sup>      | DDR4   | ✓               | ✓              | ✓        | ✓     |

(1) PDN#1 では、大量生産アプリケーションへのリクエストに応じて利用可能なカスタム PMIC 構成を使用しています。

(2) PDN#2 および PDN#3 では、TPS6521401 PMIC 構成を使用します。

(3) PDN#4 では、TPS6521402 PMIC 構成を使用します。

### 3.1 PDN#1: BOM サイズとコストに最適化された電源設計

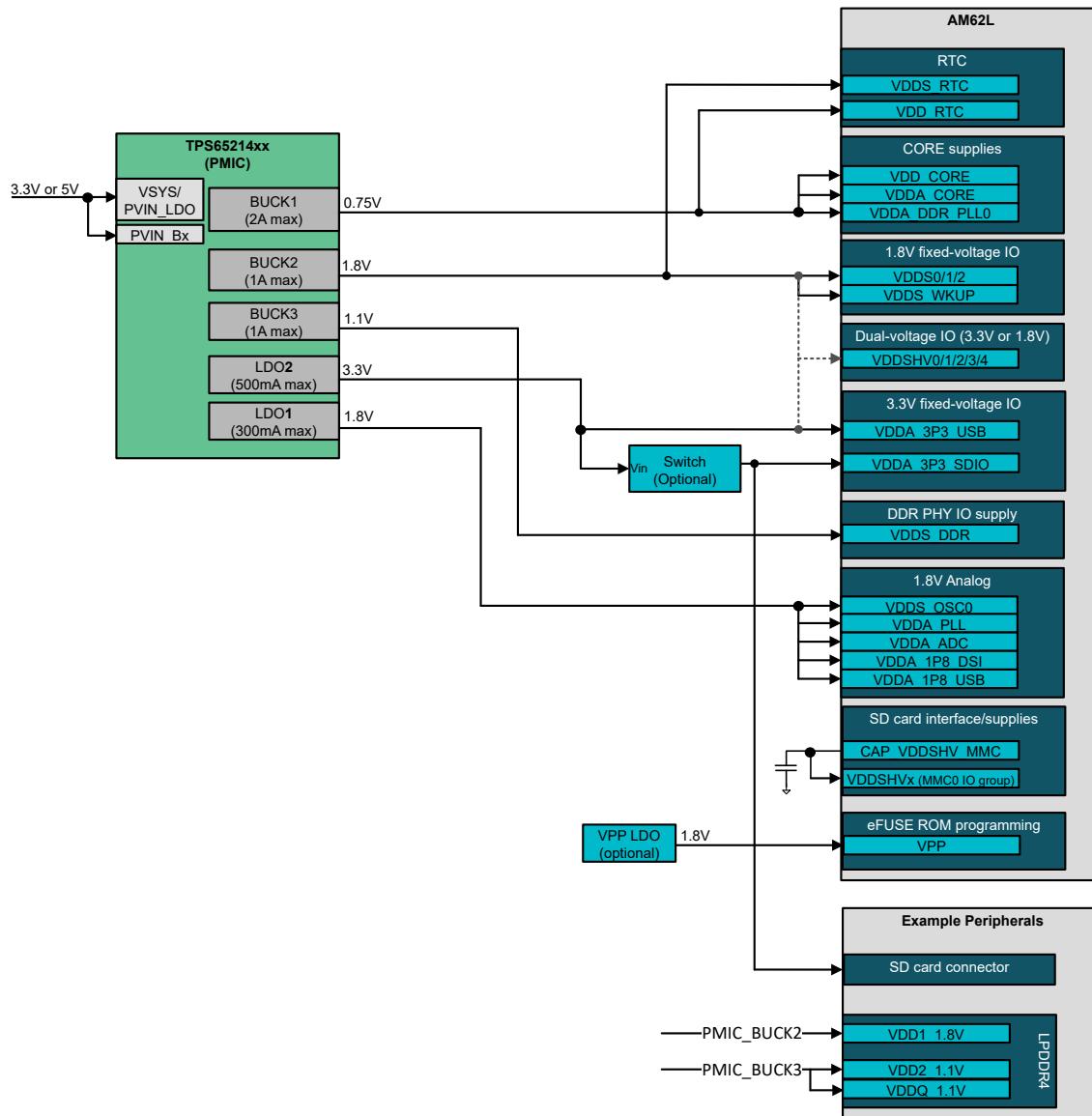

このセクションで説明する電力供給ネットワーク (PDN) は、BOM サイズの縮小とコストの削減に最適化された電源設計を提供します。この設計では、単一の 3.5mm × 3.5mm パワー マネージメント IC (PMIC) を使用して、すべての SoC 電源ドメインに電力を供給します。または、個別の部品を使用して電源設計を実装することもできます。図 3-1 は PMIC の実装を示します。この PDN は、RTC のみを使用しないアプリケーションや RTC + IO + DDR 低消費電力モードに使用できます。

#### 特長:

- 推定 BOM サイズ: **36.97mm<sup>2</sup>** (PCB 空間距離を含まない)。

- 3.3V IO (AM62L + ペリフェラルを含む) の合計電流が 500mA 未満の場合、すべての SoC 電圧ドメインには単一の PMIC が供給されます。

- 3.3V IO (AM62L + ペリフェラルを含む) の合計電流が 500mA を超える場合は、[セクション 3.2](#) を参照してください。

- 3.3V 入力電源 (最小の消費電力) を使用する場合、PMIC LDO2 は 3.3V 負荷スイッチとして構成されます。

- 4V ~ 5V 入力電源を使用する場合、PMIC LDO2 は 3.3V LDO として構成されます。

図 3-1. BOM サイズとコストに最適化された AM62L PDN

注

VDDA\_3P3\_SDIO に接続されたパワースイッチはオプションであり、アプリケーションが SD カードを使用する場合にのみ必要です。VPP 1.8V LDO はオプションであり、オンボード eFuse プログラミングが必要な場合にのみ必要です。ディスクリート実装の例については、[Appendix A](#) を参照してください。

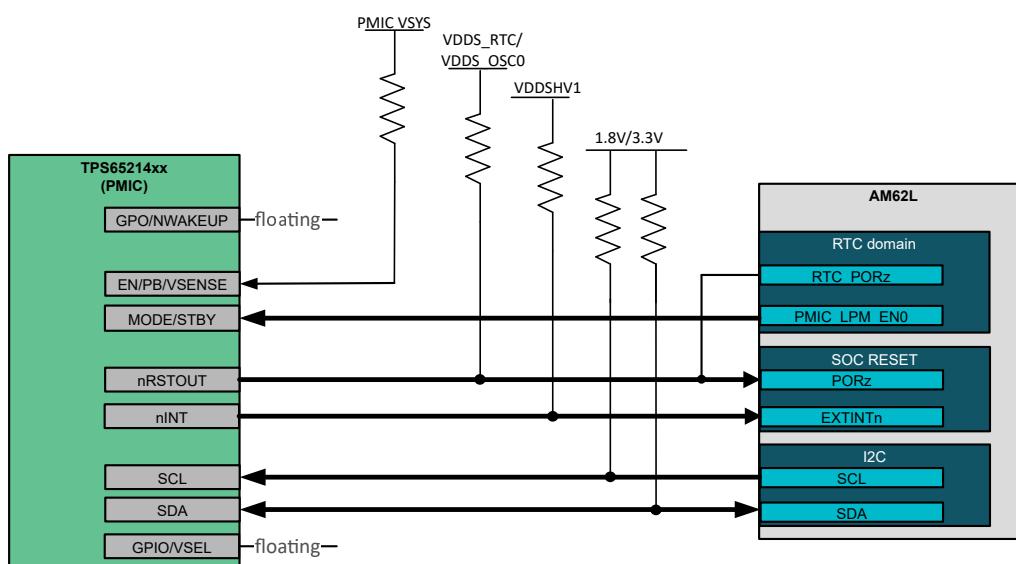

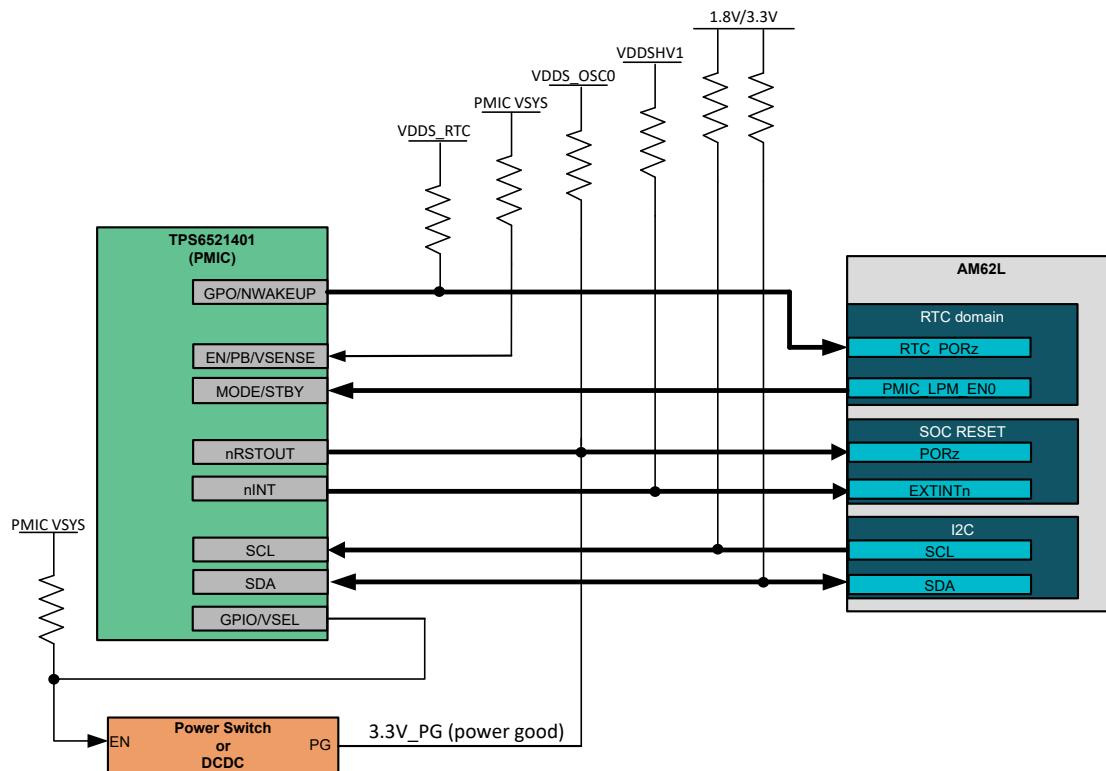

図 3-2 に、PDN#1 の SoC と PMIC のデジタル接続を示します。この画像には、外部プルアップ抵抗を必要とするデジタルピンも示しています。PMIC イネーブルピン (EN / PB / VSENSE) は、プリレギュレータのパワーグッド信号で駆動できます。または、プリレギュレータがパワーグッド信号を統合しない場合は、この信号を PMIC\_VSYS にプルアップすることができます。PMIC\_nRSTOUT は、RTC パワーオンリセット (RTC\_PORz) および SoC メインリセット (PORz) を駆動します。これは、RTC のみおよび RTC + IO + DDR 低消費電力モードをサポートしていない場合に許可されます。PMIC\_LPM\_EN0 は PMIC MODE/STBY ピンを駆動して、DCDC スイッチング モードを強制 PWM から自動 PFM に切り替え、DeepSleep およびスタンバイ/OS アイドル 低消費電力モード中の電力効率を向上させます。これはオプションであり、PMIC MODE/STBY ピンを「MODE」として構成する必要があります。

図 3-2. PDN#1 の SoC - PMIC デジタル接続

注

PMIC\_LPM\_EN0 は、外部プルアップ抵抗を必要としません。SoC には、VDDS\_RTC が電源投入されている場合に信号をハイに駆動する内部プルアップ抵抗があります。PORz は 3.3V 耐性があり、VDDS\_OSC0 に電源が供給されている限り、外部プルアップ抵抗を 1.8V 電源または 3.3V 電源に接続できます。

| AM62L     | Power Supply        | Qty             | Example component          | Component Value      | Length (mm) | Width (mm) | Area (mm <sup>2</sup> ) |  |

|-----------|---------------------|-----------------|----------------------------|----------------------|-------------|------------|-------------------------|--|

| NA        | PMIC rails          | PMIC IC package | 1                          | TPS65214             | N/A         | 3.5        | 3.5                     |  |

|           |                     | VSYS/PVIN_LDO   | 1                          | C1608X7S1A475K080AC  | 4.7uF       | 1.6        | 0.8                     |  |

|           |                     | VDD1P8 - Cout   | 1                          | C1005X7S1A225K050BC  | 2.2uF       | 1          | 0.5                     |  |

|           |                     | BUCK1-L         | 1                          | TFM201208BLE-R47MTCF | 0.47μH      | 2          | 1.2                     |  |

|           |                     | BUCK1-Cin       | 1                          | C1608X7S1A475K080AC  | 4.7μF       | 1.6        | 0.8                     |  |

|           |                     | BUCK1-Cout      | 2                          | GRM21BZ71A226ME15L   | 22μF        | 2          | 1.25                    |  |

|           |                     | BUCK3-L         | 1                          | TFM201208BLE-R47MTCF | 0.47μH      | 2          | 1.2                     |  |

|           |                     | BUCK3-Cin       | 1                          | C1608X7S1A475K080AC  | 4.7μF       | 1.6        | 0.8                     |  |

|           |                     | BUCK3-Cout      | 1                          | GRM21BZ71A226ME15L   | 22μF        | 2          | 1.25                    |  |

|           |                     | BUCK2-L         | 1                          | TFM201208BLE-R47MTCF | 0.47μH      | 2          | 1.2                     |  |

| 1.8V IO   |                     | BUCK2-Cin       | 1                          | C1608X7S1A475K080AC  | 4.7μF       | 1.6        | 0.8                     |  |

|           |                     | BUCK2-Cout      | 1                          | GRM21BZ71A226ME15L   | 22μF        | 2          | 1.25                    |  |

|           |                     | LDO1-Cin        | 0                          | shares Cin with VSYS | NA          | 0          | 0                       |  |

|           |                     | LDO1-Cout       | 1                          | C1005X7S1A225K050BC  | 2.2μF       | 1          | 0.5                     |  |

| 3.3V IO   |                     | LDO2-Cin        | 0                          | shares Cin with VSYS | NA          | 0          | 0                       |  |

|           |                     | LDO2-Cout       | 1                          | C1005X7S1A225K050BC  | 2.2uF       | 1          | 0.5                     |  |

| Resistors | Digital Pull-up Res | 5               | Example: 0201 10K pull-ups | NA                   |             | 0.6        | 0.3                     |  |

|           |                     |                 |                            |                      |             |            | Total Size 36.97        |  |

図 3-3. PMIC BOM の例

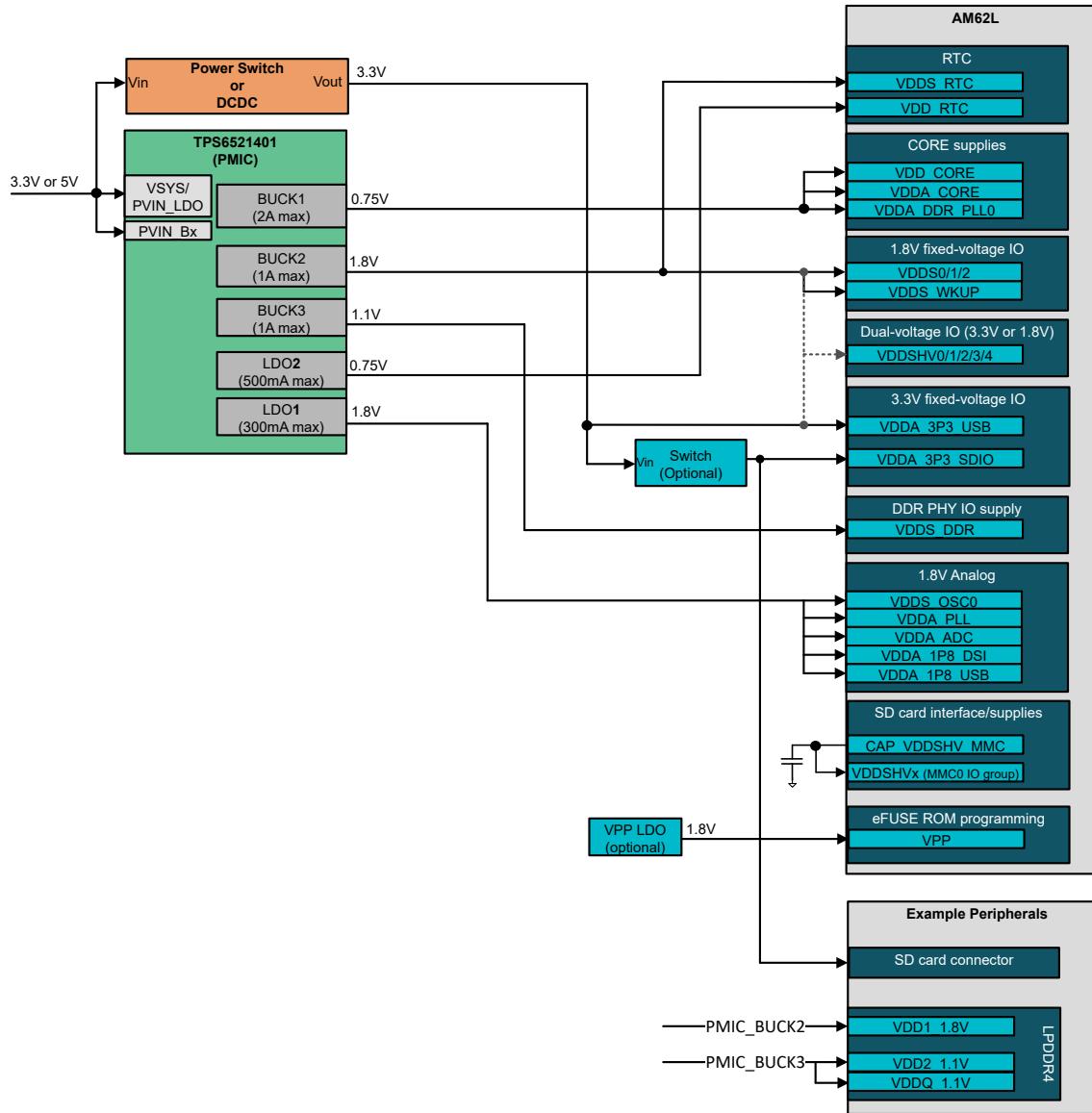

### 3.2 PDN#2: 中断電力を最小限に抑え最適化された電源設計

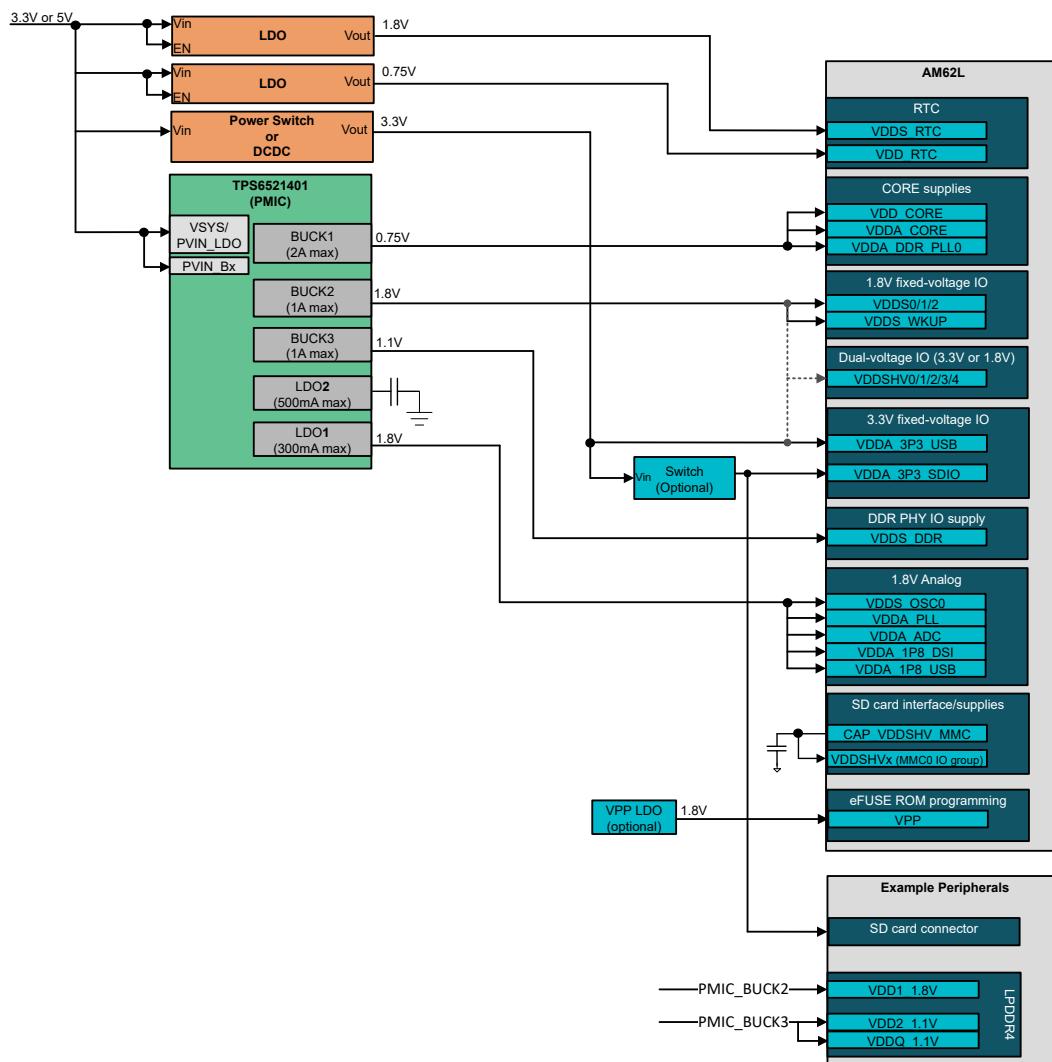

このセクションで説明する電力供給ネットワーク (PDN) は、最も低い中断電力に最適化されており、RTC モードのみを除くすべての低消費電力モードをサポートします。PDN は、3.5mm x 3.5mm PMIC と外部 3.3V ディスクリートレギュレータを使用して、すべての SoC 電源ドメインに電力を供給します。この PDN は、RTC + IO + DDR 低消費電力モードを使用するアプリケーション、または 3.3V IO で 500mA 以上の電流を必要とするアプリケーションに推奨されます。この PDN は、RTC + IO + DDR 低消費電力モードに入るときに VDD\_CORE と VDDA をオフにして消費電力を削減するように設計されています。図 3-4 は TPS6521401 構成を使用した PMIC 実装を示します。

#### 特長:

- TPS6521401 PMIC を使用。この PMIC 構成は、AM62L EVM で使用されています。ハードウェア設計ファイルが利用可能です。

- 3.3V 入力電源 (PMIC + 3.3V 電源スイッチ) の推定 BOM サイ: **41.69mm<sup>2</sup>** (PCB 空間距離を含まない)。パワースイッチの例: TPS22954 の詳細を示します。

- 4V ~ 5V 入力電源 (PMIC + 3.3V Buck) 推定 BOM サイ: **58.68mm<sup>2</sup>** (PCB 空間距離を含まない)。Buck の例: TPS62A01 の詳細を示します。

- 外部 3.3V ディスクリートは、3.3V IO (SoC + ペリフェラルを含む) に必要な合計電流に基づいて拡張可能です。

図 3-4. 中断電力を最小限に抑えるように最適化された AM62L PDN

**注**

VDDA\_3P3\_SDIO に接続されたパワースイッチはオプションであり、アプリケーションが SD カードを使用する場合にのみ必要です。VPP 1.8V LDO はオプションであり、オンボード eFuse プログラミングが必要な場合にのみ必要です。

図 3-5 に、PDN#2 の SoC と PMIC の間のデジタル接続を示します。この画像は、外付けプルアップ抵抗が必要なデジタル信号も示しています。PMIC イネーブルピン (EN / PB / VSENSE) は、プリレギュレータのパワーグッド信号で駆動できます。または、プリレギュレータがパワーグッド信号を統合しない場合は、この信号を PMIC\_VSYS にプルアップすることができます。PMIC nRSTOUT と 3.3V IO のパワーグッド信号が、メイン SoC リセット (PORz) を駆動します。PMIC GPO は、RTC レール (BUCK2 および LDO2) のパワーグッド信号として動作し、RTC パワーオンリセット (RTC\_PORz) を駆動します。PMIC\_LPM\_EN0 は、「RTC + IO + DDR」低消費電力モードに入力すると、PMIC MODE/STBY ピンを駆動して PORz を Low にし、VDD\_CORE (BUCK1) と VDDA (LDO1) をオフにします。

図 3-5. PDN#2 の SoC - PMIC デジタル接続

**注**

PMIC\_LPM\_EN0 は、外部プルアップ抵抗を必要としません。SoC には、VDDA\_RTC が電源投入されている場合に信号をハイに駆動する内部プルアップ抵抗があります。PORz は 3.3V 耐性があり、VDDA\_OSC0 に電源が供給されている限り、外部プルアップ抵抗を 1.8V 電源または 3.3V 電源に接続できます。

**表 3-2. TPS6521401 デジタル構成**

|                | OTP 構成       | 極性                                                                                                                                                                                   |

|----------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EN/PB/VSENSE   | イネーブルとして構成   | <ul style="list-style-type: none"> <li>High: PMIC はパワーオン シーケンスを実行します。</li> <li>Low: PMIC はパワーダウン シーケンスを実行します。</li> </ul>                                                             |

| モード/スタンバイ      | モードおよびスタンバイ  | <ul style="list-style-type: none"> <li>High: アクティブ状態の PMIC 電流。すべてのレールが有効。Buck は強制 PWM で動作します。</li> <li>Low: PMIC はスタンバイ状態です。Buck1 および LDO1 はオフになります。Buck は自動 PFM で動作します。</li> </ul>  |

| GPIO / nWAKEUP | オープンドレイン GPO | <ul style="list-style-type: none"> <li>Buck2 および LDO2 のパワーグッド信号として機能するように構成されています。このデジタルピンは RTC_PORZ を駆動し、PMIC がスタンバイ状態に入ると high/Z のままになり、AM62L RTC+DDR 低消費電力モードをサポートします。</li> </ul> |

| GPIO/VSEL      | オープンドレイン GPO | <ul style="list-style-type: none"> <li>外部 3.3V ディスクリートデバイスをイネーブル/ディセーブルするように構成する。</li> </ul>                                                                                         |

**注**

デフォルトの PMIC OTP レジスタ設定の全リストについては、[TPS6521401 テクニカルリファレンスマニュアル](#)を参照してください。

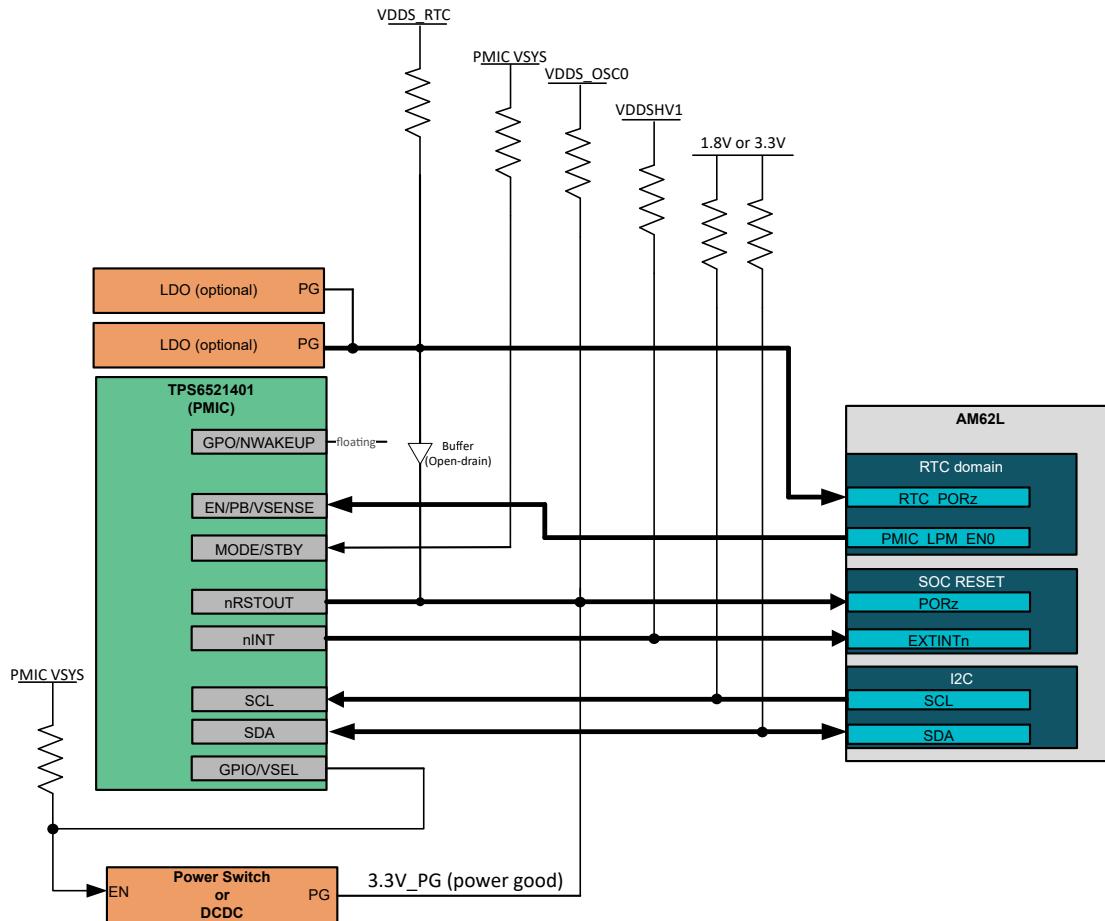

### 3.3 PDN#3: 完全に柔軟な電源設計

このセクションで説明する電力供給ネットワーク (PDN) は、すべての SoC 低消費電力モードをサポートできる柔軟な PMIC + ディスクリート電源設計を提供します。この PDN は、VDDS\_RTC (1.8V) と VDD\_RTC (0.75V) を残りの電源レールから絶縁することにより、RTC のみの低消費電力モードをサポートします。RTC ドメインに常時オンのディスクリートデバイスを供給すると、RTC レールのみをオンのままにして PMIC 全体と外部 3.3V ディスクリートをオフにすることで、RTC のみの消費電力モード中の消費電力を大幅に削減できます。RTC のみの低消費電力モードに移行すると、AM62L PMIC\_LPM\_EN 信号は PMIC イネーブルピンを Low に駆動します。図 3-6 に、PMIC + ディスクリート電源の実装を示します。

#### 特長:

- この PDN は、TPS6521401 PMIC (AM62L EVM で使用される PMIC OTP 構成) を使用して実装できます。

- すべての AM62L 低消費電力モードをサポートしています。

- BOM のサイズは、RTC レールと 3.3 IO に選択したディスクリートデバイスによって大きく依存します。

- 3.3V 入力電源 (低消費電力) を使用する場合は、外部 3.3V パワースイッチを使用します。IC の例: TPS22954 の詳細を示します。

- 4V ~ 5V 入力電源を使用する場合は、外部 3.3V DCDC を使用します。IC の例: TPS62A01 の詳細を示します。

- 外部 3.3V ディスクリート電流定格は、3.3V の IO に必要な合計電流に基づいて拡張可能です。

図 3-6. AM62L 完全に柔軟な PDN

注

VDDA\_3P3\_SDIO に接続されたパワースイッチはオプションであり、アプリケーションが SD カードを使用する場合にのみ必要です。VPP 1.8V LDO はオプションであり、オンボード eFuse プログラミングが必要な場合にのみ必要です。

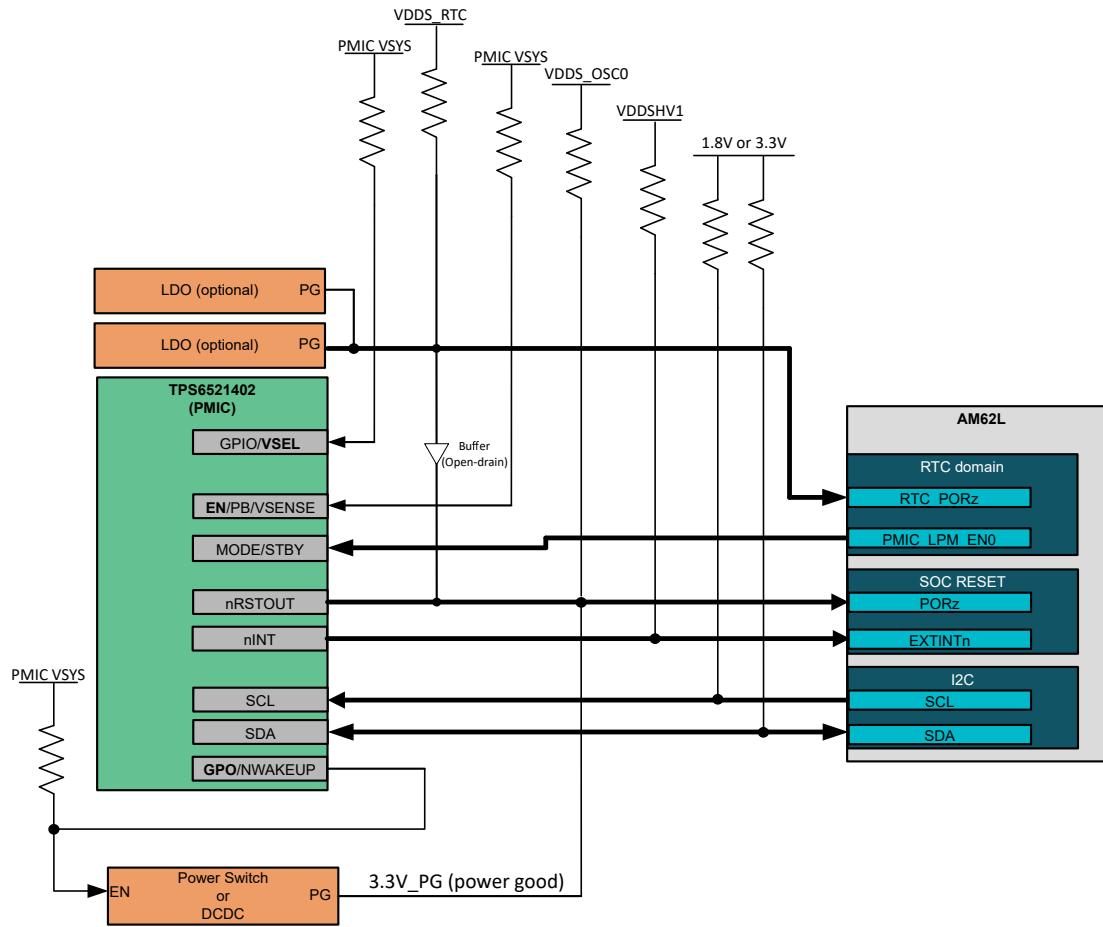

図 3-7 に、PDN#3 の SoC と PMIC 間のデジタル接続を示します。この画像は、外付けプルアップ抵抗が必要なデジタル信号も示しています。SoC PMIC\_LPM\_EN0 は、RTC のみの低消費電力モードに移行するときに PMIC イネーブルピン (EN / PB / VSENSE) を駆動して PMIC をオフにします。RTC レールに電力を供給する個別の LDO の結合されたパワーグッド信号が RTC\_PORz を駆動します。さらに、2 つのパワーオンリセット間のオープンドレイン バッファにより、外部のディスクリート LDO で故障が検出された場合に PORz を低く引き下げ、SoC をリセット状態に保つことができます。PMIC nRSTOUT、3.3V の IO のパワーグッド信号、およびオープンドレイン バッファの出力は、メイン SoC リセット (PORz) を駆動します。

図 3-7. PDN#3 の SoC - PMIC デジタル接続

注

PMIC\_LPM\_EN0 は、外部プルアップ抵抗を必要としません。SoC には、VDDS\_RTC が電源投入されている場合に信号をハイに駆動する内部プルアップ抵抗があります。PORz は 3.3V 耐性があり、VDDSHV1 に電源が供給されている限り、外部プルアップ抵抗を 1.8V 電源または 3.3V 電源に接続できます。

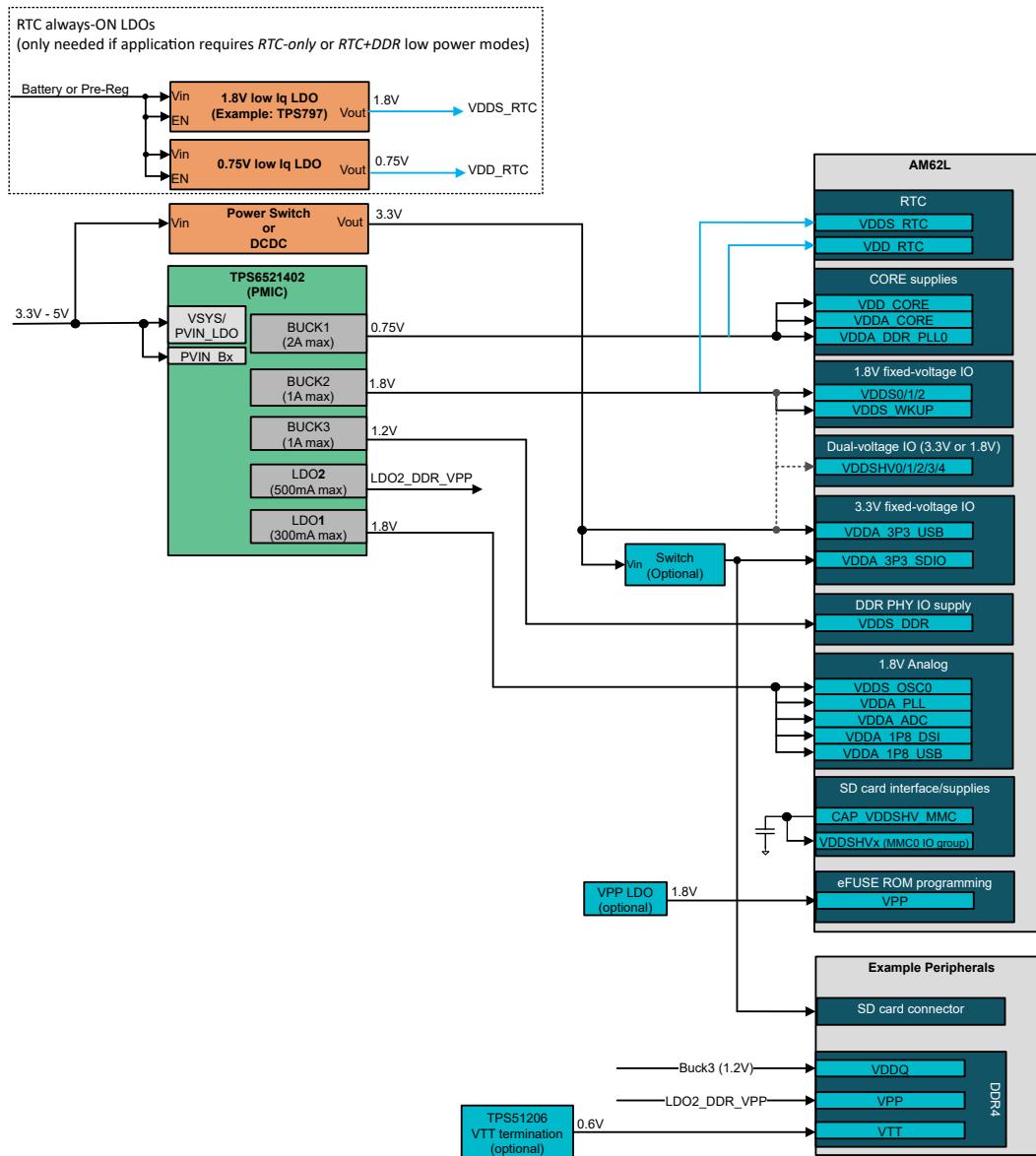

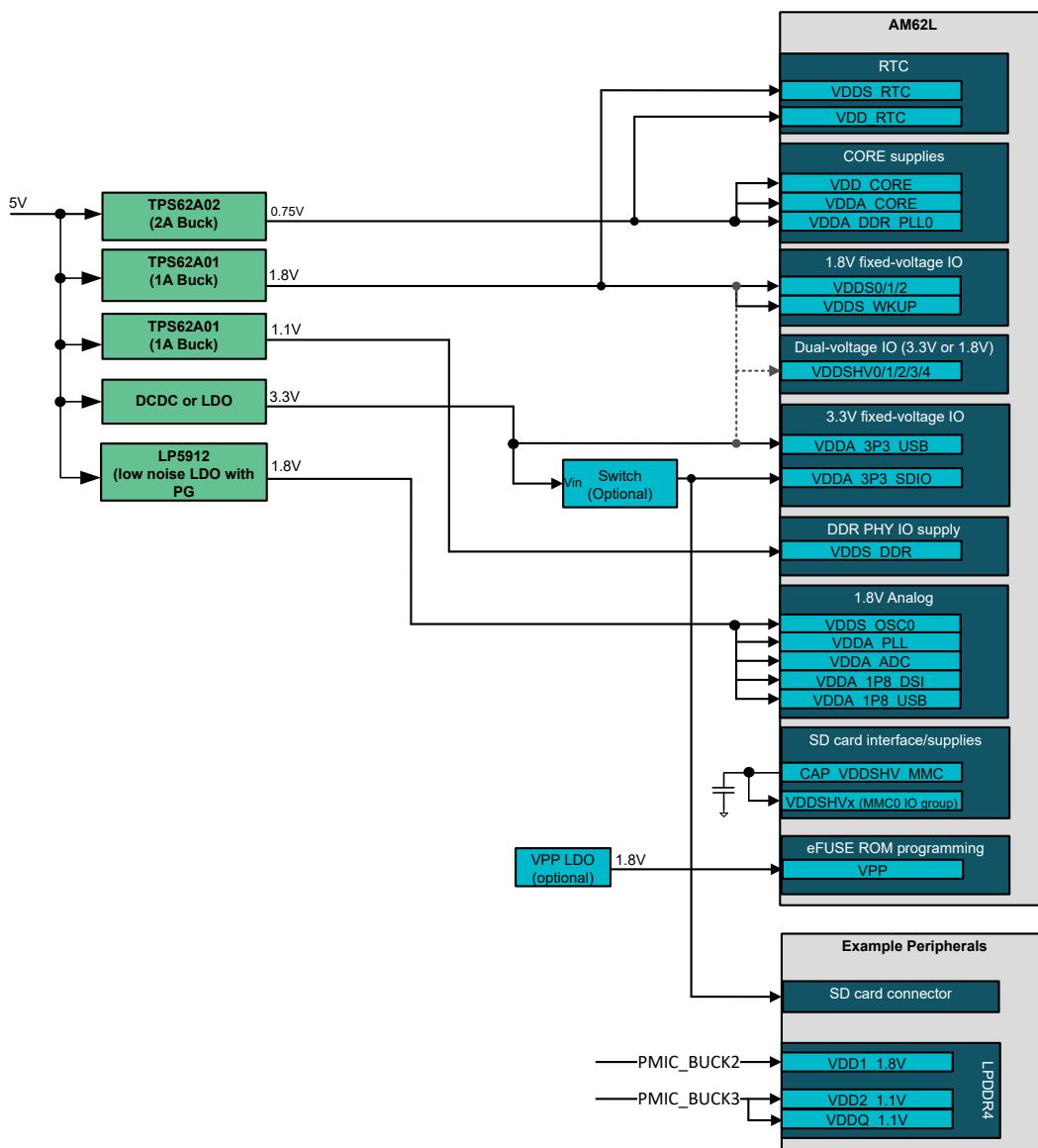

### 3.4 PDN#4: DDR4 の電源実装

このセクションで説明する電力供給ネットワーク (PDN) は、AM62L + DDR4 をサポートしています。RTC のみまたは RTC + IO + DDR 低消費電力モードが必要ない場合、VDD\_RTC を VDD\_CORE (Buck1) に接続し、VDDDS\_RTC を 1.8V IO (Buck2) に接続することができます。図 3-8 は TPS6521402 構成を使用した PMIC 実装を示します。

#### 特長:

- TPS6521402 PMIC を使用。

- 2 つの外部 1.8V/0.75V ディスクリート LDO は、アプリケーションが RTC のみまたは RTC + IO + DDR 低消費電力モードを使用する場合のみ必要です。

- BOM のサイズは、RTC レールと 3.3 IO に選択したディスクリートデバイスによって大きく依存します。

- 3.3V 入力電源 (低消費電力) を使用する場合は、外部 3.3V パワースイッチを使用します。IC の例: TPS22954 の詳細を示します。

- 4V ~ 5V 入力電源を使用する場合は、外部 3.3V DCDC を使用します。IC の例: TPS62A01 の詳細を示します。

- 外部 3.3V ディスクリート電流定格は、3.3V の IO に必要な合計電流に基づいて拡張可能です。

図 3-8. DDR4 の電源実装

注

VDDA\_3P3\_SDIO に接続されたパワースイッチはオプションであり、アプリケーションが SD カードを使用する場合にのみ必要です。VPP 1.8V LDO はオプションであり、オンボード eFuse プログラミングが必要な場合にのみ必要です。外部電源のターンオフを必要とする低消費電力モード (RTC のみ、または RTC + DDR 低消費電力モード) をアプリケーションで使用する場合、VDDS\_RTC と VDD\_RTC は、ディスクリートの常時オンレギュレータから供給する必要があります。これは、AM62L + DDR4 PDN の要件です。

図 3-9 に、SoC と PMIC の間のデジタル接続と必要なプルアップ抵抗を示します。SoC PMIC\_LPM\_EN0 は、RTC のみの低電力モードをサポートするときに、PMIC イネーブルピン (EN/PB/VSENSE) を駆動します。それ以外の場合、この信号は PMIC MODE/STBY ピンを駆動します。

図 3-9. DDR4 用デジタル接続の使用事例

**表 3-3. TPS6521402 デジタル構成**

|                | OTP 構成       | 極性                                                                                                                                                                                  |

|----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EN/PB/VSENSE   | イネーブルとして構成   | <ul style="list-style-type: none"> <li>High: PMIC はパワーオン シーケンスを実行します。</li> <li>Low: PMIC はパワーダウン シーケンスを実行します。</li> </ul>                                                            |

| モード/スタンバイ      | モードおよびスタンバイ  | <ul style="list-style-type: none"> <li>High: アクティブ状態の PMIC 電流。すべてのレールが有効。Buck は強制 PWM で動作します。</li> <li>Low: PMIC はスタンバイ状態です。Buck1 および LDO1 はオフになります。Buck は自動 PFM で動作します。</li> </ul> |

| GPIO / nWAKEUP | オープンドレイン GPO | <ul style="list-style-type: none"> <li>外部 3.3V ディスクリートデバイスをイネーブル/ディセーブルするように構成する。</li> </ul>                                                                                        |

| GPIO/VSEL      | オープンドレイン GPO | <ul style="list-style-type: none"> <li>このピンは BUCK3 の電圧を設定するよう構成されており、DDR4 に 1.2V を出力するにはプルアップが必要です。</li> </ul>                                                                      |

**注**

デフォルトの PMIC OTP レジスタ設定の全リストについては、[TPS6521402 テクニカルリファレンスマニュアル](#)を参照してください。

## 4 パワーアップ シーケンス

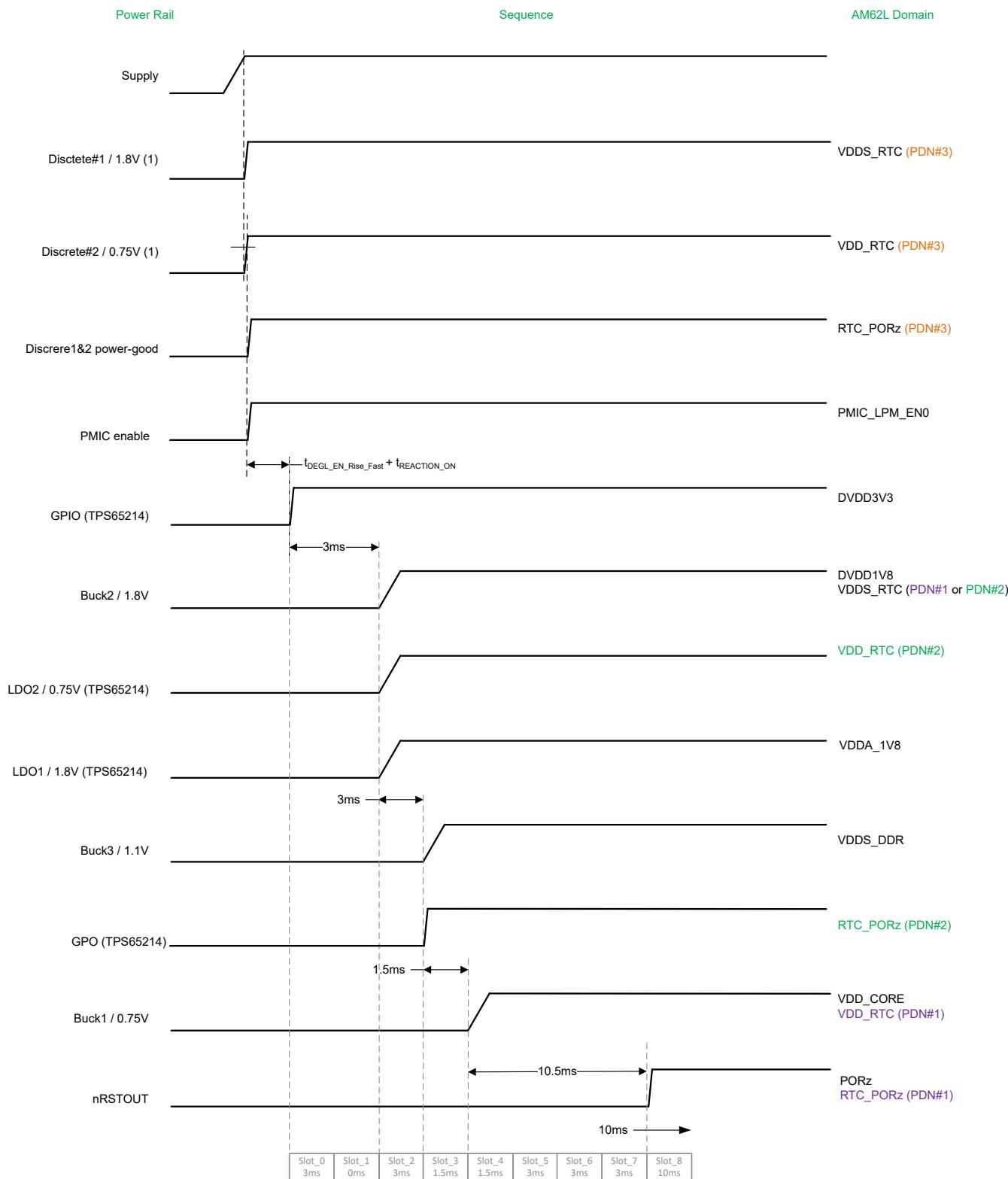

図 4-1 に、TPS6521401 OTP 構成をリファレンスとして使用するパワーアップ シーケンスを示します。シーケンシング波形と要件の詳細については、AM62L のデータシートを参照してください。

図 4-1. AM62L のパワーアップ シーケンス

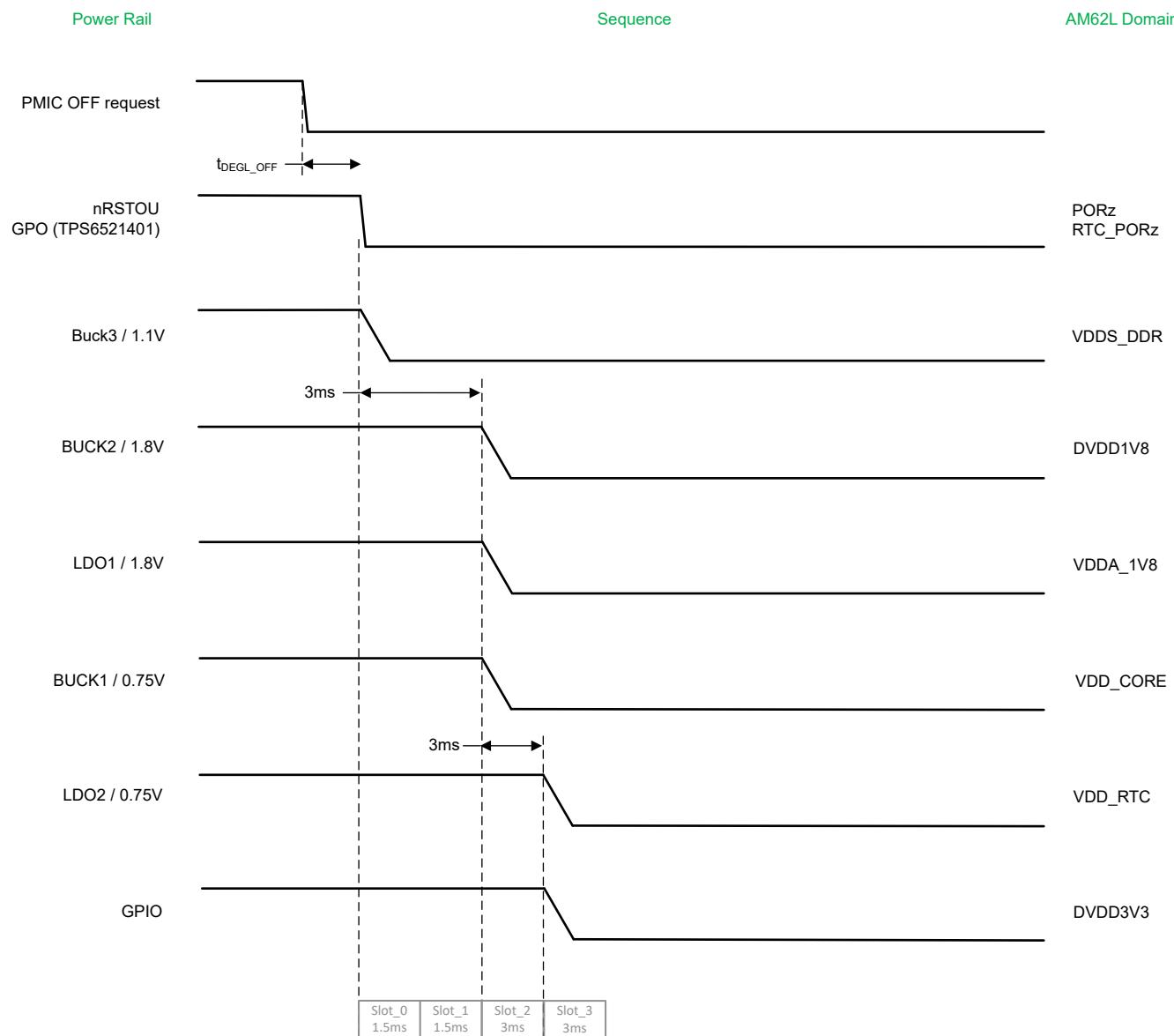

## 5 電源オフシーケンス

図 5-1 は、TPS6521401 OTP 構成を基準として使用するパワーダウンシーケンスを示します。このパワーダウンシーケンスでは、起動から低消費電力モードへの SoC のシーケンシングはカバーされません。この図は、ハードウェア (イネーブルピンを Low にする) またはソフトウェア (I2C オフ要求) によってオフ要求が PMIC に送信された場合の電源オフシーケンスのみを表しています。シーケンシング波形と要件の詳細については、AM62L のデータシートを参照してください。

図 5-1. AM62L のパワーダウンシーケンス

## 6 まとめ

AM62L 電源アーキテクチャは、設計者が消費電力だけでなく、BOM 面積とコストも削減できるようにする機能を備えて開発されました。このアプリケーションノートで説明している 3 つの電力供給ネットワーク (PDN) は、BOM 面積の削減、コスト、低消費電力時の消費電力の低減など、システムレベルの要件を満たすように電源設計を最適化する方法の例を示します。

## 7 参考資料

- テキサス インスツルメンツ、[AM62Lx Sitara™ プロセッサデータシート](#)。

- テキサス インスツルメンツ、[『AM62L テクニカルリファレンス マニュアル』](#)、テクニカル リファレンス マニュアル。

- テキサス・インスツルメンツ、[TPS65214 統合パワー マネージメント IC プロセッサ データシート](#)。

- テキサス インスツルメンツ、[『TPS6521401 テクニカルリファレンス マニュアル』](#)、テクニカル リファレンス マニュアル。

- テキサス インスツルメンツ、[『TPS6521402 テクニカルリファレンス マニュアル』](#)、テクニカル リファレンス マニュアル。

このセクションでは、PDN#1 のディスクリート電源実装について説明します。BOM サイズとコストに最適化された電源ソリューションは、以下にリストされているデバイスと同等の属性を持つ個別な部品を使用して実装することもできます。図 A-1 に、5V 入力電源と LPDDR4 の使用事例の電源図例を示します。

- VDD\_CORE (0.75V): TPS62A02

- VDDS\_DDR (1.1V): TPS62A01

- VDDSHV (3.3V IO / 1.8V IO)

- 合計電流が 500mA より大きい場合: TPS62A01 (DCDC)

- 合計電流が 500mA 未満の場合: TPS74501 (LDO)

- VDDA (1.8V アナログ): LP5912 (低ノイズ LDO)

注

このディスクリート PDN は供給実装例であり、テキサス・インスツルメンツはそのテストや検証を行っていません。

図 A-1. BOM サイズおよびコストのディスクリート実装に最適化された PDN

## 注

VDDA\_3P3\_SDIO に接続されたパワースイッチはオプションであり、アプリケーションが SD カードを使用する場合にのみ必要です。VPP 1.8V LDO はオプションであり、オンボード eFuse プログラミングが必要な場合にのみ必要です。

| AM62L               | Discrete Power | Qty | Example component         | Component Value   | Length (mm) | Width (mm) | Area (mm <sup>2</sup> ) |

|---------------------|----------------|-----|---------------------------|-------------------|-------------|------------|-------------------------|

| VDD_CORE<br>VDD_RTC | Buck IC        | 1   | TPS62A02DRLR              | 2A Buck           | 1.6         | 1.6        | 2.56                    |

|                     | BUCK1-L        | 1   | XGL3520-102MEC            | 1.0uH             | 3.5         | 3.2        | 11.2                    |

|                     | BUCK1-Cin      | 1   | GRM21BR71A475KA73L        | 4.7uF             | 2           | 1.25       | 2.5                     |

|                     | BUCK1-Cout     | 2   | GRM21BZ71A226KE15L        | 22uF              | 2           | 1.25       | 5                       |

|                     | Resistors      | 3   | Resistor, Chip, 0.1 W, 1% | 0603 std resistor | 1.6         | 0.8        | 3.84                    |

| VDDS_DDR            | Buck IC        | 1   | TPS62A01DRLR              | 1A Buck           | 1.6         | 1.6        | 2.56                    |

|                     | BUCK3-L        | 1   | DFE252012F-1R0M           | 1.0uH             | 3.5         | 3.2        | 11.2                    |

|                     | BUCK3-Cin      | 1   | GRM21BR71A475KA73L        | 4.7uF             | 2           | 1.25       | 2.5                     |

|                     | BUCK3-Cout     | 1   | GRM21BZ71A226KE15L        | 22uF              | 2           | 1.25       | 2.5                     |

|                     | Resistors      | 3   | Resistor, Chip, 0.1 W, 1% | 0603 std resistor | 1.6         | 0.8        | 3.84                    |

| 1.8V IO             | Buck IC        | 1   | TPS62A01DRLR              | 1A Buck           | 1.6         | 1.6        | 2.56                    |

|                     | BUCK2-L        | 1   | DFE252012F-1R0M           | 1.0uH             | 3.5         | 3.2        | 11.2                    |

|                     | BUCK2-Cin      | 1   | GRM21BR71A475KA73L        | 4.7uF             | 2           | 1.25       | 2.5                     |

|                     | BUCK2-Cout     | 1   | GRM21BZ71A226KE15L        | 22uF              | 2           | 1.25       | 2.5                     |

|                     | Resistors      | 3   | Resistor, Chip, 0.1 W, 1% | 0603 std resistor | 1.6         | 0.8        | 3.84                    |

| 3.3V IO             | Buck IC        | 1   | TPS62A01DRLR              | 1A Buck           | 1.6         | 1.6        | 2.56                    |

|                     | BUCK2-L        | 1   | DFE252012F-1R0M           | 1.0uH             | 3.5         | 3.2        | 11.2                    |

|                     | BUCK2-Cin      | 1   | GRM21BR71A475KA73L        | 4.7uF             | 2           | 1.25       | 2.5                     |

|                     | BUCK2-Cout     | 1   | GRM21BZ71A226KE15L        | 22uF              | 2           | 1.25       | 2.5                     |

|                     | Resistors      | 3   | Resistor, Chip, 0.1 W, 1% | 0603 std resistor | 1.6         | 0.8        | 3.84                    |

| VDDA (1.8V analog)  | IC             | 1   | LP5912                    | low noise LDO     | 2           | 2          | 4                       |

|                     | LDO - Cin      | 1   | GRT033C81A105ME13D        | 1uF               | 0.6         | 0.3        | 0.18                    |

|                     | LDO - Cout     | 1   | GRT033C81A105ME13D        | 1uF               | 0.6         | 0.3        | 0.18                    |

|                     |                |     |                           |                   |             | Total Size | 97.26                   |

図 A-2. ディスクリート BOM の例

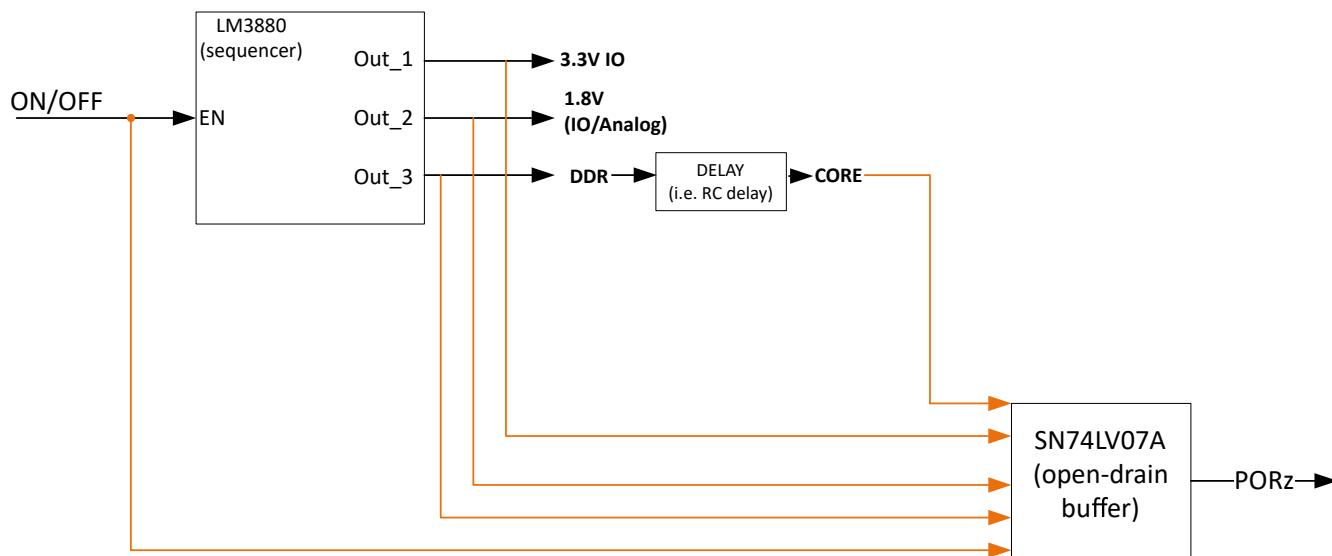

SoC のシーケンス要件とリセットアーキテクチャを満たすには、適切なロジック実装が必要です。図 A-3 は LM3380 シーケンサーと 6 チャンネル オープンドレイン バッファを使用した例を示します。オレンジ色で強調表示された接続は、SoC レールとシステム電源を供給するデバイスのパワーグッド信号を表します。

図 A-3. ロジックの実装の例

## 9 改訂履歴

| <b>Changes from Revision A (September 2025) to Revision B (October 2025)</b> | <b>Page</b> |

|------------------------------------------------------------------------------|-------------|

| • DDR4 をサポートするための電源実装を追加.....                                                | 5           |

| • TPS6521401 TRM へのリンクを修正。.....                                              | 9           |

| <b>Changes from Revision * (March 2025) to Revision A (September 2025)</b> | <b>Page</b> |

|----------------------------------------------------------------------------|-------------|

| • ドキュメント全体にわたって表、図、相互参照の採番方法を更新.....                                       | 1           |

| • デバイスファミリを含めるため、タイトルのデバイスに「x」を追加します。.....                                 | 1           |

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月