# Application Note

# DP83826 から DP83826A へのハードウェア ロールオーバ ドキュメント

#### David Liu

## 概要

テキサス インスツルメンツはさまざまなイーサネット PHY トランシーバを提供しており、複数の最終製品の使用事例に対応する設計を実現します。このアプリケーション ノートでは、10/100Mbps 製品ラインアップ内の 2 つの PHY (DP83826x (1) と DP83826Ax (2)) の違いと、DP83826x を使用した既存の設計を変換して DP83826Ax を使用する方法を紹介しています。

- DP83826x は DP83826E と DP83826I を指します。

- DP83826Ax は DP83826AI を指します。

# 目次

| 1 はじめに                      | <mark>2</mark> |

|-----------------------------|----------------|

| 2 DP83826x と DP83826Ax の違い  | 3              |

| 2.1 高速リンクドロップ (FLD) ストラップ構成 |                |

| 2.2 EMC 性能                  |                |

| 3 まとめ                       |                |

| 4 参考資料                      | 7              |

| > \\                        |                |

#### 商標

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

DP83826x および DP83826Ax は、IEEE802.3 10BASE-Te および 100BASE-TX 規格に準拠したシングル ポートの 物理層トランシーバです。 DP83826x および DP83826Ax は、厳格な産業用フィールド バス アプリケーションの要件を 満たすように設計されており、非常に低いレイテンシ、レイテンシの確定的な変動 (リセット、電源サイクル全体)、XI と TX\_CLK 間の固定位相、低消費電力、高速リンク アップを実現するハードウェア ブートストラップを使用した構成を提供 します。

このデバイスは、MAC (媒体アクセス制御) に直接接続するための標準の MII および RMII (リーダー モードおよびフォロワ モード) をサポートしています。このデバイス専用の CLKOUT ピンを使用して、システム上の他のモジュールをクロック駆動できます。 さらに、PWRDN ピンはパワーオン リセット (POR) から DP83826x と DP83826Ax のリンク アップを制御し、DP83826x と DP83826Ax の非同期パワーアップおよびホスト SoC (システム オン チップ) または FPGA (フィールドプログラマブル ゲートアレイ) コントローラの設計に有用です。デバイスは 3.3V 単一電源で動作し、LDO を内蔵しているので、内部ブロックに必要な電圧レールを供給できます。

このデバイスは 3.3V または 1.8V の I/O 電圧インターフェイスに対応しており、I/O 電圧が 3.3V の場合は単一電源 PHY として、I/O 電圧が 1.8V の場合はデュアル電源 PHY として DP83826x と DP83826Ax を動作させることができます。 DP83826x と DP83826Ax 内の自動電源構成により、追加の構成設定を必要とせずに、VDDIO 電源を自由に組み合わせて使用できます。 DP83826x と DP83826Ax は、ミックスド シグナル処理機能により、イコライゼーション、データの回復、誤り訂正を行い、CAT5e ツイストペア ケーブル上で信頼性の高い動作を実現します。

# 2 DP83826x と DP83826Ax の違い

# 2.1 高速リンクドロップ (FLD) ストラップ構成

DP83826x と DP83826Ax は、高速リンクドロップ (FLD) とも呼ばれる拡張リンクドロップ メカニズムをサポートしており、リンクを判定するための観測ウィンドウを短縮できます。リンク ステータスを決定する方法は複数あり、ユーザの好みに応じて有効化または無効化することができます。

#### 2.1.1 ベーシック モード

DP83826x BASIC モードでは、高速リンクドロップがデフォルトで有効化されています。RX エラーおよび信号およびエネルギー損失カウントでは、高速リンクドロップが有効になります。

DP83826Ax BASIC モードでは、高速リンクドロップがデフォルトで有効化されています。BASIC モードでの追加の FLD メカニズムは、表 2-1 に示すように、Strap11 によって決定できます。

#### 表 2-1. DP83826Ax Basic モード FLD 構成

| ストラップ構成                    | RX エラー カウン<br>ト | <b>MLT3</b> エラー カウン<br>ト | 低信号対雑音比スレッ<br>ショルド | 信号およびエネルギー損<br>失 | デスクランブラリンク損失 |

|----------------------------|-----------------|--------------------------|--------------------|------------------|--------------|

| ストラップ 11 = Low (デフォ<br>ルト) | イネーブル           | イネーブル                    | ディセーブル             | イネーブル            | ディセーブル       |

| ストラップ 11 = High            | ディセーブル          | ディセーブル                   |                    |                  |              |

DP83826x と DP83826Ax のいずれの場合も、追加構成は制御レジスタ 3 (CR3、レジスタ アドレス 0x000B) を使用してプログラムできます。 ビット [3:0] およびビット [10] を使用すると、各種 FLD 状態を有効化することができます。

#### 2.1.2 拡張モード

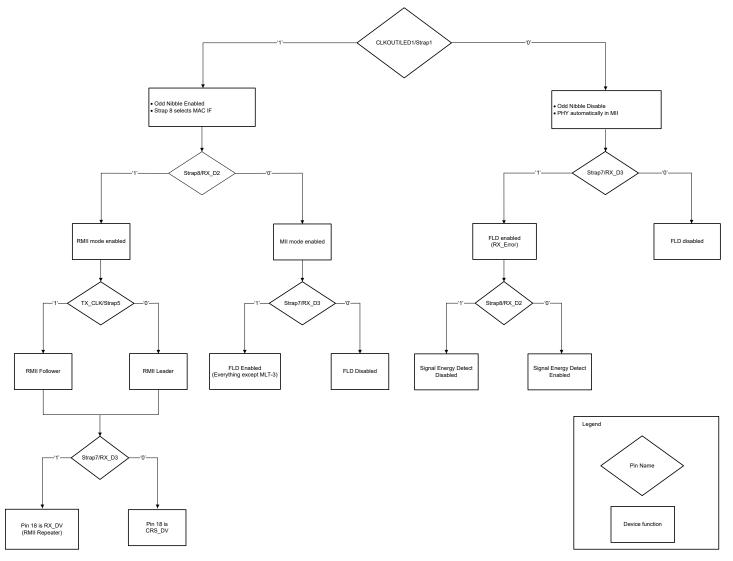

表 2-2 および図 2-1 に、DP83826x FLD 検出モード構成を示します。 Strap7 = High、Strap1 = High/Low、Strap8 = High/Low の場合、MLT3 エラー カウントは無効化されることに注意してください。

表 2-2. ブートストラップ構成による DP83826x FLD 検出モード

| ストラップ構成                                             | RX エラー カウント | MLT3 エラー カウント | 低信号対雑音比スレッ<br>ショルド | 信号 / エネルギー損失 | デスクランブラ リンク <b>損</b><br>失 |

|-----------------------------------------------------|-------------|---------------|--------------------|--------------|---------------------------|

| (デフォルト)<br>Strap7 = LOW<br>Strap1 = X<br>Strap8 = X | ディセーブル      | ディセーブル        | ディセーブル             | ディセーブル       | ディセーブル                    |

| Strap7 = HIGH<br>Strap1 = HIGH<br>Strap8 = LOW      | イネーブル       |               | イネーブル              | イネーブル        | イネーブル                     |

| Strap7 = HIGH<br>Strap1 = LOW<br>Strap8 = LOW       | イネーブル       |               | ディセーブル             | イネーブル        | ディセーブル                    |

| Strap7 = HIGH<br>Strap1 = LOW<br>Strap8 = HIGH      | イネーブル       |               | ディセーブル             | ディセーブル       | ディセーブル                    |

図 2-1. DP83826x のブートストラップ構成フローチャート

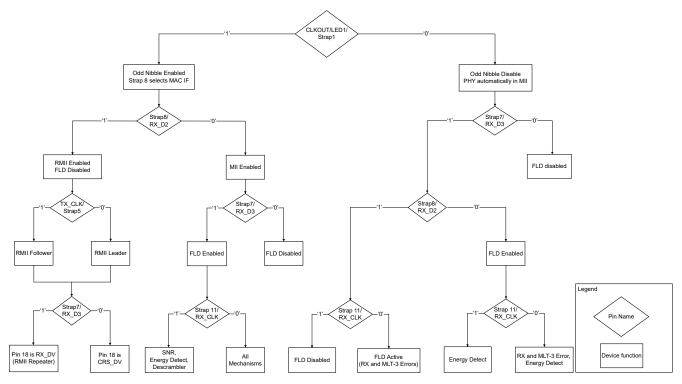

DP83826Ax FLD 検出モード構成を、表 2-3 および図 2-2 に示します。同じストラップ構成では、MLT3 エラー カウントがイネーブルになります。DP83826x と DP83826Ax の場合、どちらの場合も RX エラー カウントがイネーブルになります。RX エラーが MLT-3 エラーのスーパーセットである場合、スーパーセットは MLT-3 エラーの前にトリガされます。このため、MLT-3 エラー カウントの設定方法が違いますが、DP83826x と DP83826Ax の間の動作に違いはありません。

## 表 2-3. ブートストラップ構成による DP83826Ax FLD 検出モード

| FLD ストラップ<br>オプション      | ストラップ構成                                                          | <b>RX</b> エラー カウント <sup>(1)</sup> | MLT3 エラー カウント | 低信号対雑音比ス<br>レッショルド | 信号/エネルギー損<br>失 <sup>(1) (2)</sup> | デスクランブラ リン<br>ク損失 |

|-------------------------|------------------------------------------------------------------|-----------------------------------|---------------|--------------------|-----------------------------------|-------------------|

| 1                       | Strap1 = X<br>Strap8 = X<br>Strap11 = X                          | ディセーブル                            | ディセーブル        | ディセーブル             | ディセーブル                            | ディセーブル            |

| 2                       | Strap7 = HIGH<br>Strap1 = HIGH<br>Strap8 = LOW<br>Strap11 = LOW  | イネーブル                             | イネーブル         | イネーブル              | イネーブル                             | イネーブル             |

| 3 (3)                   | Strap7 = HIGH<br>Strap1= LOW<br>Strap8= LOW<br>Strap11 = LOW     | イネーブル                             | イネーブル         | ディセーブル             | イネーブル                             | ディセーブル            |

| <b>4</b> <sup>(3)</sup> | Strap7 = HIGH<br>Strap1 = LOW<br>Strap8 = HIGH<br>Strap11 = LOW  | イネーブル                             | イネーブル         | ディセーブル             | ディセーブル                            | ディセーブル            |

| 5 <sup>(3)</sup>        | Strap7 = HIGH<br>Strap1 = LOW<br>Strap8 = HIGH<br>Strap11 = HIGH | ディセーブル                            | ディセーブル        | ディセーブル             | イネーブル                             | ディセーブル            |

| 6                       | Strap7 = HIGH<br>Strap1 = HIGH<br>Strap8 = LOW<br>Strap11 = HIGH | ディセーブル                            | ディセーブル        | イネーブル              | イネーブル                             | イネーブル             |

- (1) RX\_ERROR カウントと信号 / エネルギー損失を有効化することで、堅牢な FLD 動作が可能になります

- (2) 信号 / エネルギー損失を有効にすることで、最高の耐性特性が得られます

- (3) FLD イネーブル ストラップの推奨設定

図 2-2. DP83826Ax のブートストラップ構成フローチャート

最高の EMC 性能を得るには、信号およびエネルギー損失の FLD モードを有効にすることを推奨します。

DP83826x と DP83826Ax のいずれの場合も、追加構成は制御レジスタ 3 (CR3、レジスタ アドレス 0x000B) を使用してプログラムできます。 ビット [3:0] およびビット [10] を使用すると、各種 FLD 状態を有効化することができます。

#### 2.2 EMC 性能

DP83826Ax は、基本モードと拡張モードの両方で DP83826x よりも優れた EMC 性能を提供します。表 2-4 に、 DP83826x と DP83826Ax の性能の違いを示します。 EMC 性能を向上させるには、 DP83826Ax のモードに関係なくストラップ 11 を high にする必要があります。

EMI/EMC 準拠テストは、DP83826AEVM で実施しています。テスト結果の詳細については、*『DP83826AEVM ユーザー ガイド』*のセクション 4 を参照してください。

表 2-4. DP83826x と DP83826Ax の EMC 性能比較

| テスト  | 標準            | テスト レベル                                 | DP83826x                      | DP83826Ax     |

|------|---------------|-----------------------------------------|-------------------------------|---------------|

| ESD  | IEC 61000 4-2 | +/-4kV 接触 (RJ-45)<br>+/-15kV 空中 (ケーブル上) | +/-4kV 基準 A<br>+/-8kV 基準 B    | +/-8kV の基準 A  |

| サージ  | IEC 61000-4-5 | +/-2kV: ライン間<br>+/-4kV: ラインから GND へ     | 基準 B                          | 基準 A          |

| 放射耐性 | IEC 61000-4-6 | 10V/m (150kHz∼80MHz)                    | 3Vrms 時の基準 A<br>10Vrms 時の基準 B | 基準 A、10Vrms 時 |

基準 A: EMC テスト中にパケット エラーと損失のリンク ドロップ はありません。

基準 B: リンクドロップは許可されますが、PHY はリセットせずにリンクを回復する必要があります。

まとめ

## 3 まとめ

DP83826x と DP83826Ax は類似の 10/100 Mbps PHY であり、同様のアプリケーションで使用できます。このドキュメン トでは、実装の観点から、デバイス間の類似点や相違点について説明します。

## 4参考資料

- 1. Texas Instruments, \$\int DP83826 Deterministic, Low-Latency, Low-Power, 10/100Mbps, Industrial Ethernet PHY』、データ シート

- 2. Texas Instruments, \$\int DP83826Ax Deterministic, Low-Latency, Low-Power, 10/100Mbps, Industrial Ethernet PHY』、データ シート

# 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、 テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、 テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。 テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、 テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、 テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、 テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。 テキサス・インスツルメンツがこれらのリソ 一スを提供することは、適用される テキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありませ ん。

お客様がいかなる追加条項または代替条項を提案した場合でも、 テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated