*Application Note***DP83TD510E ブラブルショーティング ガイド**

*Evan Mayhew, Vivaan Jaiswal*

**概要**

このガイドは、開発、検証、導入の各段階では一般的に対処できない問題の特定と解決に重点を置き、DP83TD510E のトラブルショーティングを実施する体系的なアプローチを紹介します。この資料では、MDI と MAC の両方のインターフェイスに関する回路図とレイアウトのベストプラクティス、部品の選択と検証、シグナル インテグリティなどの主要分野を取り上げています。実用的な測定、テストモードの使用方法、いくつかの診断手法を組み合わせることにより、エンジニアは DP83TD510E についてより深く理解し、根本原因の分析を迅速化できます。

**目次**

|                                     |           |

|-------------------------------------|-----------|

| <b>1 はじめに</b> .....                 | <b>2</b>  |

| <b>2 アプリケーションのトラブルショーティング</b> ..... | <b>3</b>  |

| 2.1 回路図とレイアウトのチェックアウト.....          | 3         |

| 2.2 部品チェックリスト.....                  | 3         |

| 2.3 デバイスの正常性チェック.....               | 3         |

| 2.4 レジスタ値の読み出しと確認.....              | 5         |

| 2.5 ストラップ設定の確認.....                 | 6         |

| 2.6 ループバック.....                     | 6         |

| 2.7 MDI ヘルス チェック.....               | 7         |

| 2.8 MII ヘルス チェック.....               | 10        |

| <b>3 まとめ</b> .....                  | <b>14</b> |

| <b>4 参考資料</b> .....                 | <b>15</b> |

**商標**

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

DP83TD510E は、IEEE 802.3cg 10Base-T1L 仕様に準拠した物理層トランシーバです。PHY は低ノイズ結合の信号処理レシーバーアーキテクチャを使用して、ケーブルの到達範囲と超低消費電力を実現します。このデバイスは、IEEE 802.3cg 10Base-T1L 仕様で定義されている 2.4V p2p と 1V p2p の両方の電圧モードをサポートしています。

DP83TD510E は複数のメディア アクセスコントローラ (MAC) インターフェイス (MII、RMII、RGMII、低消費電力 RMII) への直接接続をサポートしています。また、このデバイスはバックツーバック RMII モードと非マネージド モードの RGMII にも対応しており、レンジ拡張とリピータ機能を実現できます。

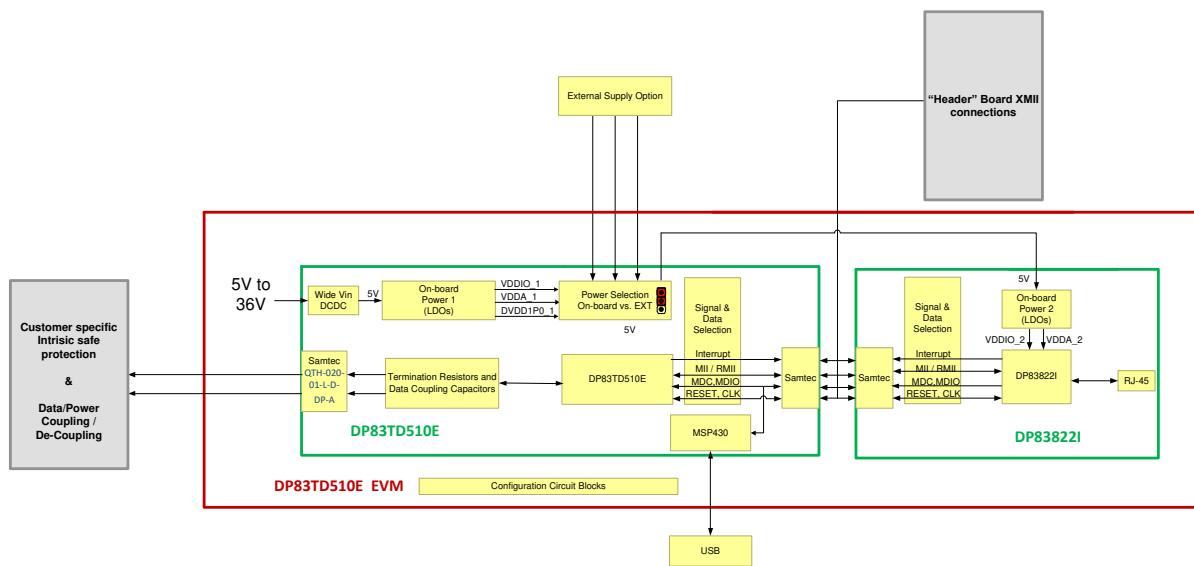

図 1-1 に、DP83TD510E を使用した代表的なメディア変換アプリケーション (SPE ⇄ RJ-45) の概要を示します。

図 1-1. DP83TD510E-EVM のブロック図

## 2 アプリケーションのトラブルシューティング

以下のセクションでは、アプリケーションを高レベルからデバッグする方法として、より焦点を当てた設計の側面に焦点を当てる前に、大きな影響があるアプリケーション特性から始めます。

このアプリケーションノートは、次の 3 つの主要なセクションでレイアウトしています。

- [デバイスの正常性チェック](#)

- [MDI ヘルス チェック](#)

- [MII ヘルス チェック](#)

観測された特定の挙動によっては、これら 3 つのセクションすべてが必要ない場合があります。このため、正しい動作が観察された場合は、特定のセクションをスキップできます。コメントは各セクションの冒頭に記載されており、以下にも記載されている。

デバイスのヘルス チェック セクションはスキップできます

- リンクパートナーに接続されている場合はリンクアップし (ステータスはレジスタ 0x0010 から読み取り)、イーサネットケーブルが接続されていない場合は NLP 信号が表示されます。

- 想定どおりに登録アクセスに応答します

デバイスの場合は、MDI ヘルス チェック セクションをスキップできます

- デバイスを介してトライフィックを送信するときに、レジスタ 0x0015 を介してリンクアップされ、パケット エラーが報告されません

このアプリケーションノートでは、複数のレジスタ設定について説明します。アクセスを容易にするため、このアプリケーションノートにはいくつかのデバッグ スクリプトを含めました。これらは、ツールの [USB-2-MDIO](#) と組み合わせて使用し、DP83TD510E をさまざまなモードに再プログラム (書き込み) を行うことができます。ここに記載されているすべてのスクリプトのコレクションなどは、[製品ページ](#)にも記載されています。

### 2.1 回路図とレイアウトのチェックアウト

回路図およびレイアウトをレビューするときは、それぞれ「回路図」と「レイアウト チェックリスト」に記載されている推奨リファレンス ガイドラインに従って設計が行われていることを確認してください。これは、記載されている要件を遵守しない場合に、異常な PHY 動作が発生する可能性があるさまざまな設計の選択肢を検証するために重要です。この慎重なレビューにより、潜在的な設計上の問題を早期に特定し、パフォーマンス上の問題が発生する可能性を低減することができます。以下のチェックリストに記載されている回路図とレイアウトに関する推奨事項をすべて参照し、検証します。

[産業用 PHY レイアウト チェックリスト](#)

[DP83TD510E 回路図 チェックリスト](#)

以下のセクションでは、PHY に電源が供給され、正しく初期化された場合に予想される動作を示します。予期される動作から逸脱した場合、不適切なペリフェラル回路によるエラーが原因である可能性があります。

### 2.2 部品チェックリスト

CMC や水晶振動子/発振器などの部品が、データシートに記載されている要件を満たしていることを確認してください (以下にもリンク先を示します)。

[CMC 要件 \(セクション 7.2.1.4\)](#)

[25MHz 水晶振動子の要件 \(セクション 7.2.2.1.2\)](#)

[発振器の要件 \(セクション 5.6\)](#)

### 2.3 デバイスの正常性チェック

このセクションでは、デバイスの電源が供給され、正しく初期化されていることを確認するデバイスの状態チェックについて説明します。DP83TD510 が次の場合、このセクションはスキップできます。

- リンクパートナーに接続されている場合はリンクアップし (ステータスはレジスタ 0x0010 から読み取り)、イーサネットケーブルが接続されていない場合は NLP 信号が表示されます。

- 想定どおりに登録アクセスに応答します

### 2.3.1 電圧供給ピンの確認

より複雑な診断を検討する前に、PHY に電力が正しく供給されているかを確認することが不可欠です。DP83TD510E は、シングル電源とデュアル電源の両方の動作をサポートしています。単一電源動作の場合は、DVDD を C\_EXT に短絡する必要があり、VDDA ピンと VDDIO ピンの電圧を測定する必要があります。ただし、デュアル電源動作では、VDDA、VDDIO、DVDD の 3 つの電圧ピンすべてをチェックし、電圧が安定しており、表 2-1 に記載されている許容誤差内であることを確認します。また、シングル電源とデュアル電源の両方の構成に適切なデカップリング コンデンサ (1uF、100nF、10nF) を使用してください。

これらの電圧は、PHY 電圧入力ピンで、または入力ピンのできるだけ近くで測定するよう設計されています

表 2-1. 電源ピンの想定電圧レベル

| ピン名      | ピン番号 | 説明               | 最小値  | 公称値 | 最大値  | 単位 |

|----------|------|------------------|------|-----|------|----|

| DVDD 1.0 | 1    | デジタル電源           | 0.90 | 1.0 | 1.1  | V  |

| VDDA 1.8 | 3    | アナログ電源           | 1.62 | 1.8 | 1.98 | V  |

| VDDA 3.3 |      | アナログ電源           | 3.0  | 3.3 | 3.6  | V  |

| VDDIO    | 17   | デジタル電源電圧、1.8V 動作 | 1.62 | 1.8 | 1.98 | V  |

|          |      | デジタル電源電圧、2.5V 動作 | 2.25 | 2.5 | 2.75 |    |

|          |      | デジタル電源電圧、3.3V 動作 | 3.0  | 3.3 | 3.6  |    |

### 2.3.2 RST\_N ピンのプローブ

RST\_N ピンは PHY へのアクティブ "Low" 入力です。コントローラが RST\_N 信号を Low で駆動していないことを確認します。そうしないと、デバイスをリセット状態に保持し、機能しないように見える可能性があります。この場合、デバイスはリシクアップできず、レジスタ アクセスも許可されません。選択した VDDIO 電圧にこのピンの電圧が対応していることを確認します。

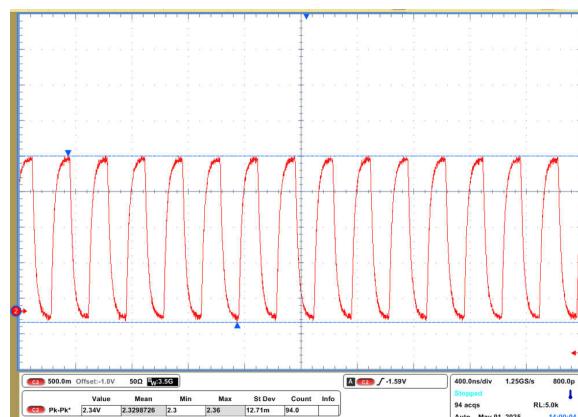

### 2.3.3 CLKOUT ピンのプローブ

CLKOUT/LED\_1 ピン (ピン 30) はデフォルトの入出力 GPIO ピンで、リファレンス クロック信号を出力します。この信号を使用して、ボード上の他のデバイスにクロックを供給できます。この基準クロックは、PHY の適切な動作を維持するために最も重要です。データシートの要件を満たさないと、ビット エラー、読み出しあり書き込みの問題、場合によっては PHY の完全な動作以外につながる可能性があります。

電源オン時に入力クロック水晶振動子または発振器が利用可能であることを確認します。

このクロック信号は、入力クロックの水晶振動子または発振器をバッファ付きで表現します。水晶振動子を使用する場合、水晶振動子を直接プローブしないでください。プローブに起因する容量の変化によって水晶振動子の動作が変化する可能性があるためです。

この CLKOUT 信号が ppm 要件内であることを確認します。

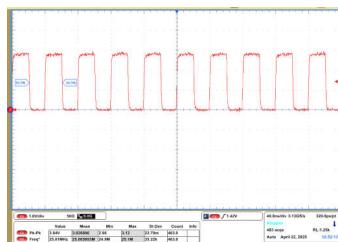

図 2-1. CLKOUT 信号

### 2.3.4 SMI ピンのプローブ

レジスタの読み取りまたは書き込みが成功した場合、このセクションはスキップできます。

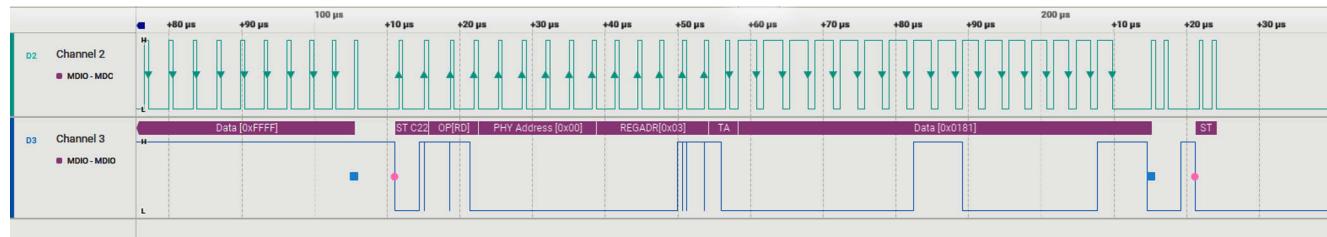

レジスタの読み取りや書き込みが成功しない場合は、MDC ピン (ピン 12) を調べて、ホストコントローラがソースとなっている  $\leq 1.75\text{MHz}$  クロック信号が存在することを確認します。これは低速デバイスのため、10Mbps では、サポートされている MDC クロックレートも低くなります。また、MDIO ピンに外部プルアップ抵抗  $2.2\text{k}\Omega \sim 4.0\text{k}\Omega$  が接続されていることも確認してください。さらに、ロジックアナライザを使用して MDIO 信号 (ピン 11) をデコードすることもできます。

図 2-2. MDC/MDIO 信号

信号 ib 図 2-2 は、デバイスモデル番号を含むレジスタ 0x3 の単純な読み取りコマンドを示しており、DP83TD510 の場合は常に 0x0181 として読み出す必要があります。

0x1F を超えてレジスタにアクセスするには、[データシートのセクション 6.3.10](#) に記載されている拡張レジスタアクセス手順に従う必要があります。

## 2.4 レジスタ値の読み出しと確認

レジスタを読み取り、返された値がデータシートのデフォルト値と一致することを確認します。一部のレジスタの初期値はストラップオプションに応じて異なることに注意してください。

PHY がリンクされている場合は、これらの値を参考にして、予想される動作との差異を特定します。デバイス構成を確認するため、以下の主要なレジスタを確認することを推奨します。

表 2-2. DP83TD510E キー レジスタ

| レジスタ・アドレス            | リセット値  | キー ビット/情報                                                                                         |

|----------------------|--------|---------------------------------------------------------------------------------------------------|

| 0x0000               | 0x0000 | [15] - デジタルリセット<br>[14] - MII ループバック                                                              |

| 0x0003               | 0x0181 | デバイスのモデルとリビジョン番号                                                                                  |

| 0x0010               | 0x0000 | [0] - リンクステータス                                                                                    |

| 0x0012/0x0013        | 0x0000 | 割り込み                                                                                              |

| 0x0015               | 0x0000 | MII RX エラー カウント                                                                                   |

| 0x0016               | 0x0100 | [8] - パワーモード(スリープ)<br>[6-0] - ループバック                                                              |

| 0x0017<br>(Mac の設定)  | 0x4001 | [12:11] - RGMII シフト/アラインモード<br>[9] - RGMII 有効<br>[7] - XI は {25, 50}MHz<br>[5] - RMII または MII モード |

| 0x012A               | 0x0000 | [1-0] - TX/RX CRC エラー表示                                                                           |

| 0x012D               | 0x0000 | TX CRC エラー カウンタ                                                                                   |

| 0x0130               | 0x0000 | RX CRC エラー カウンタ                                                                                   |

| 0x0200               | 0x1000 | [15] - AN リセット<br>[12] - イネーブル/ディセーブル                                                             |

| 0x20E (自動ネゴシエーション設定) | 0xA000 | [15] - T1L 機能<br>[14] - EEE 機能<br>[13] - 送信/受信レベル アドバタイズの増加<br>[12] - 送信レベル要求の増加                  |

| 0x020F               | 0x0000 | リンクパートナー アドバタイズ                                                                                   |

**表 2-2. DP83TD510E キー レジスタ (続き)**

| レジスタ・アドレス | リセット値  | キー ビット情報                           |

|-----------|--------|------------------------------------|

| 0x18F6    | 0x0000 | [12] - 送信レベル選択<br>[10] - EEE イネーブル |

## 2.5 ストラップ設定の確認

ストラップ構成が正しくないことは、データスループットの低下につながる最も一般的な問題の 1 つです。たとえば、誤った MII インターフェイスが選択された場合、または誤った PHY アドレスがストラップされた場合、データ送信を成功させることができません。

パワーアップまたは RESET ピンのデアサークル時は、MAC が PHY に接続されているピンを駆動していないことを確認してください。これにより、この間に誤った電圧がサンプリングされ、ストラップ値が変化する可能性があります。これにより、デバイスが化学的に動作する可能性があります。PHY に接続されているすべての MAC ピンは、PHY に電源を投入している間、またはリセットから復帰している間に、ハイインピーダンス状態にする必要があります。

電源投入時にサンプリングされるストラップ値は、拡張レジスタアクセスを使用してレジスタ 0x467 (CHIP\_SOR\_1) から読み出すことができます。ストラップの詳細については、[データシートのセクション 6.4.1](#) を参照してください。

## 2.6 ループバック

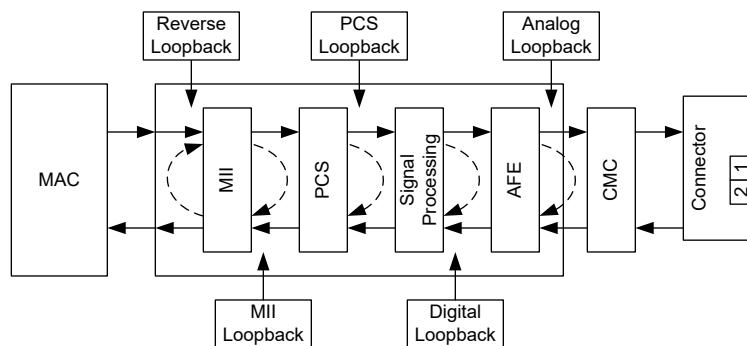

DP83TD510E には複数のループバック方法があり、PHY 内の各種機能ブロックの検証を可能にします。PHY が提供する各種ループバックモードのブロック図を [図 2-3](#) に示します。

**図 2-3. ループバック ブロック図**

MII ループバックは、制御レジスタ (BMCR、アドレス 0x0000) を介して設定できます。その他のすべてのループバックモードは、BIST 制御レジスタ (BISCR、アドレス 0x0016) を使用して有効化します。これらのループバックモードを使用して、PHY 内の MII、MDI、および内部ブロックの両方を検証できます。これは、パケット損失/エラーなどの動作を担当するデータパスの部分を絞り込む際に非常に重要です。

[表 2-3](#) に、各ループバックモードをイネーブルにするためのレジスタ書き込みを示します。この場合、他のレジスタ設定はデフォルトのままになっているとします。

**表 2-3. ループバックのレジスタ書き込み**

| ループバック モード  | 登録     | 書き込み値  |

|-------------|--------|--------|

| MII のループバック | 0x0000 | 0x4000 |

| PCS のループバック | 0x0016 | 0x0102 |

| デジタル ループバック | 0x0016 | 0x0104 |

| アナログ ループバック | 0x0016 | 0x0108 |

| リバース ループバック | 0x0016 | 0x0110 |

TX と RX の両方に、ループバックによるデバッグに役立ついくつかのカウンタが内蔵されています。このカウンタを使用して、さまざまなループバックモードで受信または送信されるパケット数を検証できます。TX カウンタは 0x12B、0x12C、

0x12D、RX カウンタは 0x12E、0x12F、0x130 の場合にリセットされることに注意してください。これらのカウンタは、表 2-4 に示すレジスタセットにあります。

**表 2-4. TX/RX パケット カウンタ レジスタ**

| 登録     | 機能                                     |

|--------|----------------------------------------|

| 0x012A | [1] RX CRC インジケータ<br>[0] TX CRC インジケータ |

| 0x012B | 下位 16 ビット TX パケット カウンタ                 |

| 0x012C | 上位 16 ビット TX パケット カウンタ                 |

| 0x012D | CRC エラーがある TX パケット                     |

| 0x012E | 下位 16 ビット RX パケット カウンタ                 |

| 0x012F | 上位 16 ビット RX パケット カウンタ                 |

| 0x0130 | CRC エラーがある RX パケット                     |

## 2.7 MDI ヘルス チェック

MDI の問題には、通常、パケット損失、オートネゴシエーションの問題、およびリンク ドロップが含まれます。予期しない動作の根本原因を絞り込むために、いくつかの異なるテストがあります。

DP83TD510 が以下のような場合、このセクションはスキップできます。

- デバイスを介してトライフィックを送信するときに、レジスタ 0x0015 を介してリンクアップされ、パケット エラーが報告されません

### 2.7.1 一般的な問題のリンクアップ

DP83TD510E がリンク パートナーとのリンク アップに問題が発生している場合、以下の一般的な理由を確認してください。

電源を供給していないリンク パートナーに接続する場合、または  $50\Omega$  で適切に終端された場合に、デバイスが MDI ライノで通常リンク パルス (NLP) を送信していることを確認してください。これらの信号は、リンクを共有する 2 つの PHY 間の情報交換として機能するため、両方のデバイス用に設計された構成で信号をリンクアップできます。以下の波形は、想定された信号を示しています。

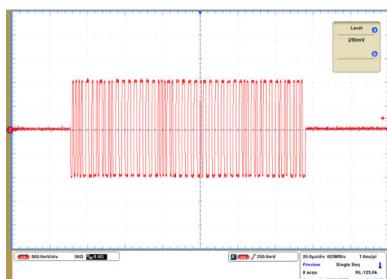

図 2-4. 通常リンク パルス (拡大)

図 2-5. 通常リンク パルス

また、DP83TD510 は、手動で自動ネゴシエーションをディセーブルにし、各デバイス (1 つはホスト、その他はクライアント) を構成することで、この自動ネゴシエーション ステージをバイパスし、強制的にリンクを設定することもできます。これらの関数のスクリプトを次に示します。選択した送信レベルは、デバイスがストラップされているものと同じで、レジスタ 0x18F6[12] に反映されます。

```

begin

000D 0007

000E 0200

000D 4007

000E 0000 // Disable AN

```

```

000D 0001

000E 08F6

000D 4001

000E 1000 // Force transmit level to 2.4V, write 0000 for 1V

000D 0001

000E 0834

000D 4001

000E 4002 // configure Device as Master, write 0002 for slave

end

```

## 2.7.2 送信レベル

10Base-T1L デバイスには、2.4Vpp と 1Vpp の 2 つの送信レベルを切り替える機能があります。通常、自動ネゴシエーションは、リンクパートナーから受信したアドバタイズに基づいて送信レベルを選択しますが、これは、リンクされる両方の PHY が目的の送信レベルをアドバタイズするように設定されていることを確認することが重要です。アドバタイズされた送信レベルは、レジスタ 0x20E のビット 12 でチェックできます。

優れたプロセスは、目的の送信レベルにストラップアップすることにより送信レベルを選択しますが、電源投入後にレジスタ構成を使用してこれらのレベルを変更することもできます。

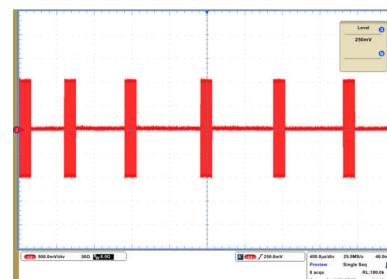

また、電圧出力レベルを測定する際は、適切な 100Ω 終端を使用することが重要です。

図 2-6. MDI の測定

### 2.7.2.1 送信レベルの変更

大まかに言うと、送信レベルを切り替える方法は 2 通りあります。1 つ目はリンクが確立されていないとき、2 つ目は 2 つの PHY の間にリンクが確立されているときです。

リンクが確立されていない場合は、レジスタ 0x20E を変更して、必要な電圧のみをアドバタイズします。これをテストするには、デジタルループバックをイネーブルにしてリンクを強制的にアップし、3 レベル出力信号を有効にします。これにより、MDI 信号でアイドル波形が開始され、プロープして電圧スイング レベルを確認できます。

```

begin

000D 0001

000E 08F6

000D 4001

000E 1000 // Force transmit level to 2.4V, write 0000 for 1V

000D 001F

000E 0016

000D 401F

000E 0104 // Enable digital loopback to force link up to have three level signal

end

```

2 つ目の状況では、両方の PHY で送信レベルを変更する必要があります。そのため、これは 3 ステップのプロセスです。最初に、自動ネゴシエーションを無効にし、目的の電圧を強制的に設定して、送信レベルを変更し、PHY 1 でソフトリセットを実行する必要があります。次に、PHY 2 で同じ操作を実行し、最後にオートネゴシエーションを再度イネーブルにする必要があります。最後に、PHY 1 に戻り、オートネゴシエーションを再度イネーブルにします。これら 3 つのステップのスクリプトは、次のとおりです。

### ステップ 1 (DP83TD510 PHY 1)

```

begin

000D 0007

000E 0200

000D 4007

000E 0000 // Disable AN

000D 0001

000E 08F6

000D 4001

000E 1000 // Force transmit level to 2.4V, write 0000 for 1V

000D 0007

000E 020E

000D 4007

000E B000 // Increase the transmit level advertisement, write 8000 for 1V

000D 001F

000E 0010

000D 401F

000E 4000 // soft reset

end

```

### ステップ 2 (DP83TD510 PHY 2)

```

begin

000D 0007

000E 0200

000D 4007

000E 0000 // Disable AN

000D 0001

000E 08F6

000D 4001

000E 1000 // Force transmit level to 2.4V, write 0000 for 1V

000D 0007

000E 020E

000D 4007

000E B000 // Increase the transmit level advertisement, write 8000 for 1V

000D 001F

000E 0010

000D 401F

000E 4000 // soft reset

000D 0007

000E 0200

000D 4007

000E 1000 // Re-enable AN

end

```

### ステップ 3 (DP83TD510 PHY 1)

```

begin

000D 0007

000E 0200

000D 4007

000E 1000 // Re-enable AN

end

```

#### 2.7.3 時間領域反射計測

時間領域反射計測は、ケーブル長の推定の他に、ケーブル、コネクタ、終端の品質を判断するために使用されます。これにより、断線、ショート、ケーブルインピーダンスの不一致、コネクタ不良、終端の不一致、クロス障害、クロスショート、およびケーブル上のその他の不連続性などの障害が判定されます。

このプロセスには、ペア内の各配線を通して既知の振幅 1V のテストパルスを送信し、欠陥とケーブルの端によって引き起こされる信号反射のリターン時間と振幅を測定することが含まれます。

DP83TD510 のケーブル診断ツールキットの詳細については、以下にリンクを掲載したアプリケーションノートを参照してください。

#### ケーブル診断ツールキット

##### 2.7.4 信号品質チェック

レジスタ 0x0010 を読み取ってリンクアップを確認した後、内蔵の信号品質表示 (SQI) 機能を使用してリンクの信号品質を確認できます。リンク品質の低下は、レイアウトまたはケーブルの欠陥によって引き起こされる可能性があり、パケット損失やエラー、またはリンクドロップにつながる可能性もあります。

TDR はケーブル障害の存在と場所に関する情報を提供できますが、この信号品質のリアルタイム監視は、リンクが達成された後の周期的な間隔で信号対雑音比 (SNR) を測定することで、障害が発生する前に貴重な情報を提供できます。

この MSE 値は、メモリレジスタ 0x0A85 に保存されます。これらの値を [表 2-5](#) と比較して、リンクの健全性を評価できます。

**表 2-5. SQI リンク ヘルス**

| SQI リンク ヘルス | MSE                 | SNR (dB)            |

|-------------|---------------------|---------------------|

| 貧乏          | MSE > 0660h         | SNR < 17.29         |

| マージン設定      | 0660h ≥ MSE > 0320h | 17.29 < SNR < 20.38 |

| 良好          | MSE ≤ 0320h         | SNR > 20.38         |

DP83TD510 のケーブル診断ツールキットの詳細については、[ケーブル診断ツールキット](#)、アプリケーションノートを参照してください。

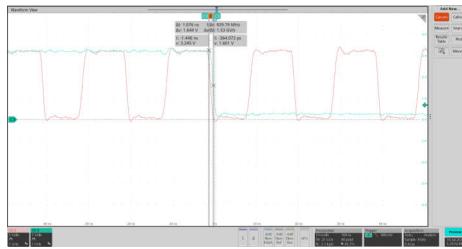

#### 2.7.5 MDI テスト モード

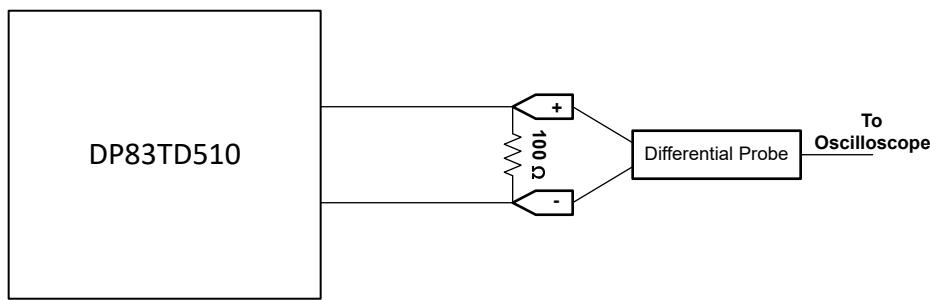

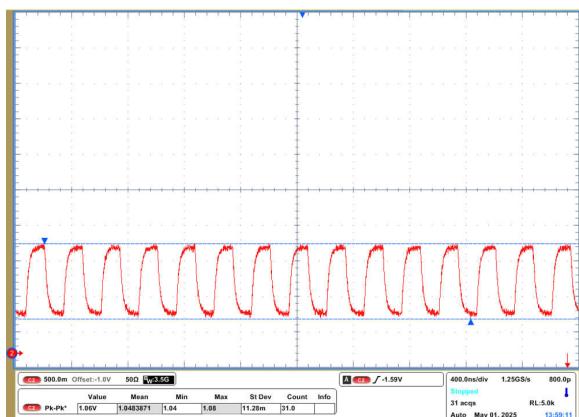

3 つの内蔵テスト モードがあり、MDI 出力が予想される仕様内であることを検証できます。これらのテスト モードは、レジスタ 0x18F8 によりアクティブにできます。これらのテスト モードは、PMA 準拠テストを実行したり、出力電圧が正しいことを検証したりするのに役立ちます。テスト モード 1 でキャプチャされた波形のいくつかを次の図に示します。

図 2-7. テスト モード 1 (1Vpp)

図 2-8. テスト モード 1 (2.4Vpp)

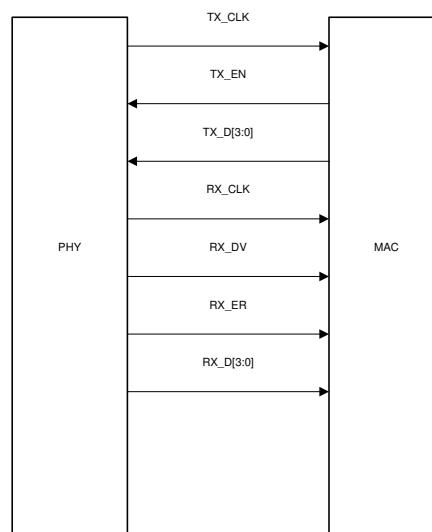

#### 2.8 MII ヘルス チェック

MII の問題には通常、MII モードの不一致、マスターまたはスレーブの構成、クロック、タイミングの不一致が含まれます。DP83TD510 は、MII、RMII (マスター、スレーブ)、RGMII モードをサポートしています。さらに調査を進める前に、PHY と MAC の両方で正しい MII インターフェイスが選択されていることを確認してください。これは、レジスタ 0x17 (MAC\_CFG\_1) のビット 5 と 9 でチェックできます。

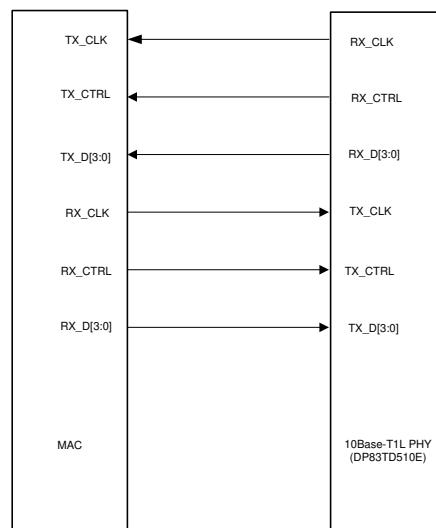

## 2.8.1 RGMII

RGMII インターフェイスは、ストラップにより、またはレジスタ 0x17 を使用して選択できます。RGMII のデータシートに記載されているタイミング要件を満たさないことは、一般的な問題です。RGMII インターフェイスのタイミング要件は、インターフェイスオプションの数として最も厳しいものですが、ギガビット RGMII に比べると、10Mbps 速度の要件はそれほど厳格ではありません。いずれにしても、タイミング要件を満たしていることを検証することが重要です。これらの要件は、[データシートのセクション 5.6](#) に記載されています。

また、以下に示す RGMII に必要な信号がすべて PHY と MAC の間で正しく配線されていることを確認します。

MAC バスに問題があると思われる場合は、トレースのレシーバ側のラインを調べ、レシーバのセットアップ時間とホールド時間が VIH/VIL と一致することを確認します。これらの仕様に違反する典型的な症状は、PHY がクリーントラフィックを示している間に MAC でパケットエラーが発生することです (レジスタ 0x15)

RGMII クロックのシフトは、これらの要件を満たすために、レジスタ 0x0017 ビット [12:11] を使ってトグルできます

図 2-9. RGMII シグナリング

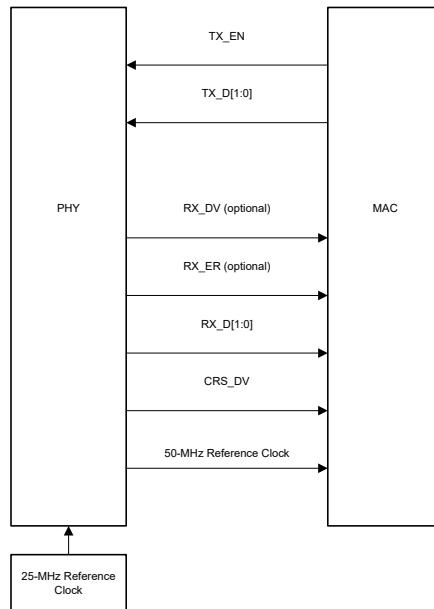

## 2.8.2 RMII

RMII インターフェイスは、ストラップにより、またはレジスタ 0x17 を使用して選択できます。RGMII および MII と同様に、RMII には PHY が適切に機能するために満たす必要がある特定のタイミング要件もあります。これらの要件は、[データシートのセクション 5.6](#) に記載されています。

RGMII および MII とは異なり、RMII にはマスター モードとスレーブ モードがあります。これらのモードは、電源オン時にストラップでき、レジスタで変更することはできません。

MAC バスに問題があると思われる場合は、トレースのレシーバ側のラインを調べ、レシーバのセットアップ時間とホールド時間が VIH/VIL と一致することを確認します。これらの仕様に違反する典型的な症状は、PHY がクリーントラフィックを示している間に MAC でパケットエラーが発生することです (レジスタ 0x15)

RMII クロック シフトは、これらの要件を満たすために、レジスタ 0x0017 ビット [8] を使ってトグルできます

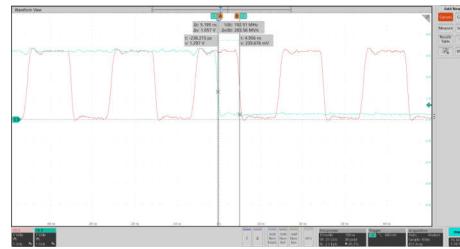

RMII マスター モードでは、DP83TD510 は 25MHz 入力クロック (水晶振動子または発振器) で動作し、MAC に基準 50MHz クロックを供給してデータを同期します。レジスタ 0x17 [9] を使用して、レシーバ (MAC) のセットアップおよびホールド時間が確実に満たされるよう、このクロックをシフトできます。この遅延をイネーブルにすると、50MHz 出力クロックに約 4ns の遅延が追加されます。セットアップ時間とホールド時間は重要なタイミング要件であり、送信中にパケット損失やエラーが発生しないようにする必要があります。

図 2-10. RMII マスタ信号伝達

図 2-11. RMII クロックシフトディスエーブル

図 2-12. RMII クロックシフトイネーブル

RMII スレーブモードでは、DP83TD510 は PHY と MAC の両方が共有する 50MHz 入力クロックで動作します。または、MAC によって供給される 50MHz クロックを使用して PHY を動作させることもできます。このクロックは、RMII スレーブモードで PHY に供給されるものが PHY を適切に機能させるための  $\pm 100\text{ppm}$  の要件を満たしていることを確認します。

図 2-13. RMII スレーブ信号伝達

各モードには異なる入力クロック信号が必要なため、電源投入時に想定される RMII モードが適切（または想定される）ストラップされていることを確認して、デバイスが起動して正常に動作するようにしてください。

### 2.8.3 MII

MII インターフェイスは、ストラップにより、またはレジスタ 0x17 を使用して選択できます。RGMII と同様に、MII には PHY が適切に機能するために満たす必要がある特定のタイミング要件もあります。これらの要件は、[データシートのセクション 5.6](#) に記載されています。

また、以下に示す MII に必要な信号がすべて PHY と MAC の間で正しく配線されていることを確認します。

MAC バスに問題があると思われる場合は、トレースのレシーバ側のラインを調べ、レシーバのセットアップ時間とホールド時間が VIH/VIL と一致することを確認します。これらの仕様に違反する典型的な症状は、PHY がクリーントラフィックを示している間に MAC でパケットエラーが発生することです（レジスタ 0x15）

図 2-14. MII シグナリング

### 3 まとめ

このアプリケーション ノートでは、新しいアプリケーションを評価し、予想される機能を確認するための推奨フローを紹介します。ステップバイステップの推奨事項を活用すると、DP83TD510 を使用した設計のボード立ち上げと初期評価を容易に実施できます。

## 4 参考資料

- ・ テキサス インスツルメンツ、『[DP83TD510E 超低消費電力 802.3cg 10Base-T1L 10M シングルペア イーサネット PHY](#)』データシート

- ・ テキサス インスツルメンツ、『[DP83TD510E ケーブル診断ツールキット](#)』、アプリケーションノート

- ・ テキサス・インスツルメンツ、[DP83TD510E-USB-2-MDIO-SCRIPTS](#)、サポートソフトウェア

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](#) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1)お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所 : Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated