*Application Note***AM62P の DSS の概要**

*Aradhya Bhatia, Krunal Bhargav, Divyansh Mittal*

**概要**

このアプリケーションノートでは、ディスプレイパラレルインターフェイス (DPI)、ディスプレイシリアルインターフェイス (DSI)、OpenLDI/LVDS など、Sitara™ AM62P プロセッサ上の主要なディスプレイインターフェイスの Linux ベースの構成について詳しく説明します。AM62P システム オン チップ (SoC) は、2 つのディスプレイサブシステム (DSS) によって構築されており、それぞれに 2 つのビデオ ポート (VP) が搭載されており、統合型 DSI および OLDI ブリッジを介して柔軟に配線できます。本書は、サポートされているさまざまな出力構成について解説しており、最大 3 つのディスプレイを同時に駆動する方法を示しています。さらに、関連する Sitara プロセッサ (AM62x, AM62A, AM62L) に搭載されている DSS モジュールは AM62P のサブセットであるため、構成方法を習得することで、Sitara AM6x 製品ライン全体にわたって効率的にディスプレイソリューションを実装することが可能になります。

**目次**

|                                    |           |

|------------------------------------|-----------|

| <b>1 はじめに</b> .....                | <b>2</b>  |

| 1.1 DSS 部品.....                    | 2         |

| 1.2 DSS を使用した PLL および出力ルーティング..... | 4         |

| <b>2 個々のディスプレイの設定</b> .....        | <b>5</b>  |

| 2.1 OLDI の構成.....                  | 5         |

| 2.2 DPI の構成.....                   | 6         |

| 2.3 DSI の構成.....                   | 7         |

| <b>3 同時表示の設定</b> .....             | <b>8</b>  |

| <b>4 ソフトウェアの設定</b> .....           | <b>9</b>  |

| 4.1 OLDI (デュアルリンク).....            | 9         |

| 4.2 OLDI (シングルリンク - クローンモード).....  | 11        |

| 4.3 OLDI (シングルリンク - 独立モード).....    | 13        |

| 4.4 DPI / HDMI.....                | 15        |

| 4.5 DSI.....                       | 16        |

| <b>5 まとめ</b> .....                 | <b>18</b> |

| <b>6 参考資料</b> .....                | <b>18</b> |

**商標**

Sitara™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

# 1 はじめに

## 1.1 DSS 部品

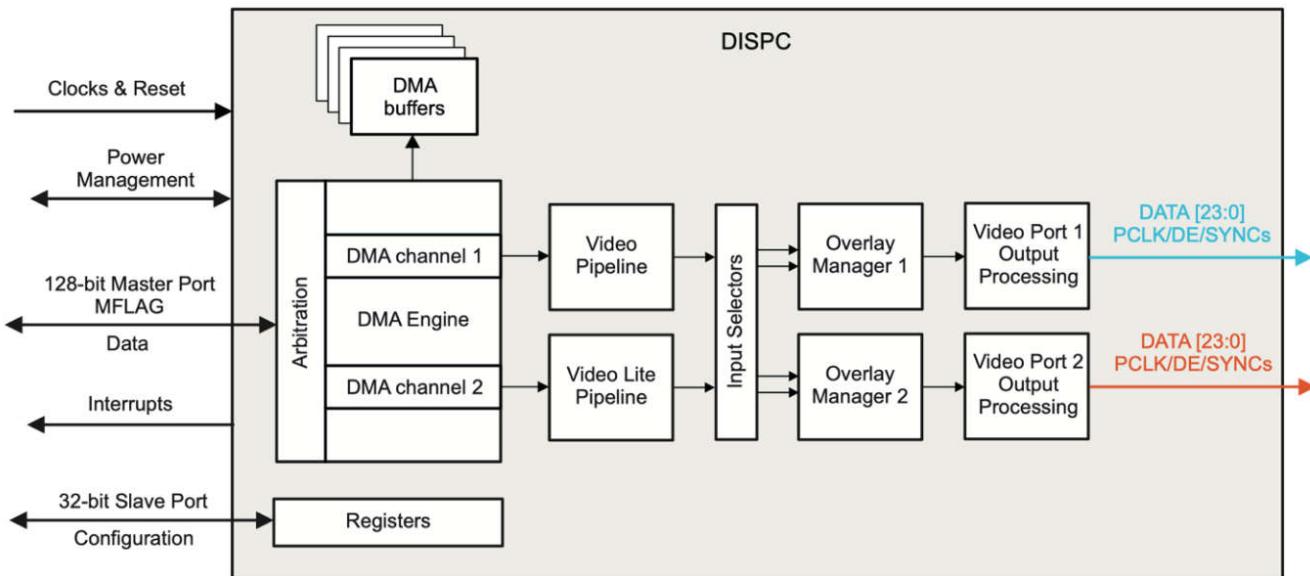

図 1-1 に、DSS 内のデータのフロー図を示します。表 1-1 に、DSS 内の各部品の概要を示します。

図 1-1. DISPC アーキテクチャの概要

表 1-1. DSS 部品の概要

| 部品名                                        | 説明                                                                                                                         | サポートされている機能                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMA エンジン                                   | デバイスのシステム メモリ内に配置されたフレーム バッファへの直接アクセスを可能にします。                                                                              | <b>複数の DMA 内部バッファ:</b> DMA バッファは 2 つあり、それぞれ 40KB の 1D 転送のみサポート<br><b>セルフ リフレッシュ モード:</b> データは一度 DMA バッファに取得され、その後のフレームでは同じ DMA チャンネルを再利用して画面に表示されます。                                                                                                                                                                                                                                                                                                                                                           |

| ビデオ パイプライン (VID)/<br>ビデオ ライト パイプライン (VIDL) | DSS には次の 2 つのパイプラインがあります: ビデオ パイプラインと Video-Lite パイプライン。これらのパイプラインは DSS のフレーム処理エンティティです。DMA エンジンがフェッチしたフレームに対して直接操作を実行します。 | <b>すべてのピクセル形式をサポート</b><br>すべてのビットマップ、YUV、RGB ピクセル形式がサポートされています。<br><b>カラー スペース変換</b><br>YUV カラー スペースから RGB カラー スペースにピクセルを変換します。<br><b>ビデオと色の参照テーブル</b> <ul style="list-style-type: none"> <li>ビットマップ ピクセルを RGB に変換します</li> <li>逆ガンマ補正</li> </ul> <b>スケーラ ポリフェーズ フィルタ*</b> <ul style="list-style-type: none"> <li>ピクセルをアップサンプリングまたはダウンサンプリングします</li> <li>アンチ エイリアシングの低減</li> <li>色信号の再サンプリング</li> </ul> <b>Luma Key</b><br>輝度が特定の範囲に収まるピクセルを透明にします。<br>Video-lite パイプラインにはスケーラ フィルタはありませんが、専用の色信号アップサンプラーがあります。 |

**表 1-1. DSS 部品の概要 (続き)**

| 部品名                | 説明                                                      | サポートされている機能                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| オーバーレイ (OVL) マネージャ | 選択した入力レイヤを合成して、最終的な表示出力フレームを生成します。                      | <p><b>注:</b> OVL マネージャは、RGB フォーマットでの入力および出力とともに、RGB フォーマットのみを受け付けます。</p> <p><b>プログラマブルな背景色</b><br/>DSS は、背景画像に単色の色を書き込むことができます。</p> <p><b>コンポジション</b><br/>コンポジット背景色の上に複数のレイヤ (VIDI または VIDL) を配置</p> <p><b>透過性カラー キー</b><br/>ソース色の透過性: ソースの透過カラー判定に一致する最上位レイヤのピクセルは、透明にされます。<br/>出力先の色の透過性: 最下位レイヤのピクセルが透過カラーの条件を満たさない場合に限り、最上位レイヤのピクセルは透明にされます。</p> <p><b>アルファブレンディング</b><br/>グローバル アルファモードおよびピクセル単位のアルファモードに対応しています。</p> <p><b>Z順序</b><br/>選択したレイヤがブレンドされる順序を決定します。</p> <p><b>カラー パー テスト</b><br/>テスト用のカラー パー パターンを生成する機能。</p>                                                                                      |

| ビデオ ポート (VP)       | オーバーレイ マネージャから最終フレームを入力として受け取り、ビデオ信号を生成します              | <p><b>出力フォーマット</b></p> <ul style="list-style-type: none"> <li>• RGB           <ul style="list-style-type: none"> <li>- RGB-444/565/666/888</li> </ul> </li> <li>• YUV           <ul style="list-style-type: none"> <li>- BT.1120 モードおよび BT.656 モード</li> </ul> </li> </ul> <p><b>カラー スペース変換/カラー位相回転</b></p> <ul style="list-style-type: none"> <li>• RGB カラー スペースのピクセルを YUV カラー スペースに変換します。</li> <li>• RGB 出力の位相を GBR または BRG に変更します。</li> </ul> <p><b>時間ディザリング</b><br/>24 ビット未満の色深度の LCD パネルにデータを表示する際のカラー バンディングを最小限に抑えます。</p> <p><b>複数サイクル出力フォーマット (TDM を使用)</b><br/>ピクセルは、それより少ない数のビデオ出力ラインで 1~3 サイクルで送信されます。</p> |

| 安全                 | 安全が重要なシステム アプリケーション向けに、DSS はハードウェアでさまざまな安全機能をサポートしています。 | <p><b>データ修正チェック</b><br/>意図したデータが正しくディスプレイに表示されていることを検証します。</p> <p><b>フリーズ フレーム検出</b><br/>複数のフレーム期間にわたって表示フレームに変化がない場合に、フレームのフリーズの可能性を通知します。</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

表 1-1 に、各種機能の概要を示します。詳細については、TRM の DSS 章を参照してください。

## 1.2 DSS を使用した PLL および出力ルーティング

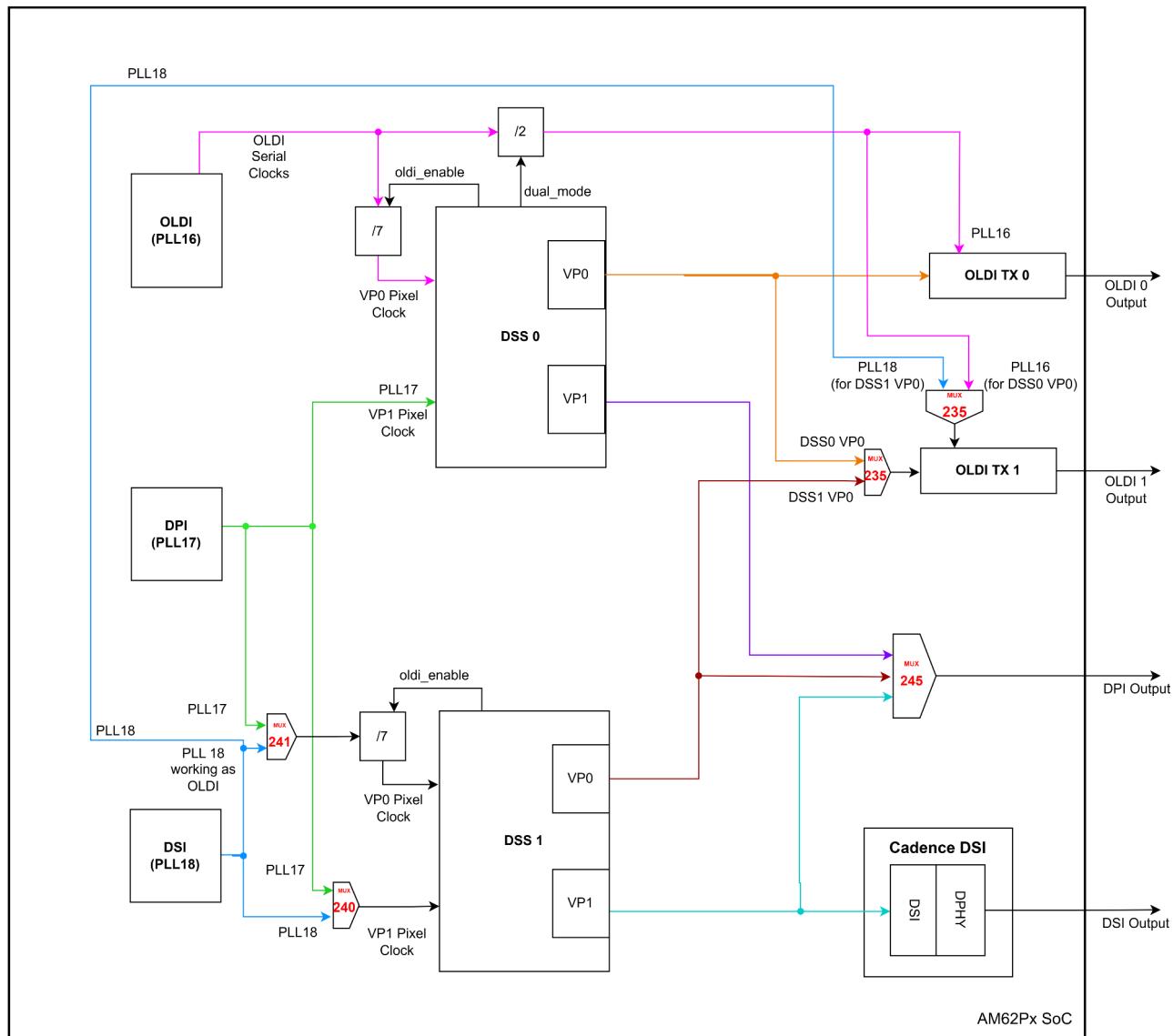

図 1-2 に示すように、AM62P は 2 つの DSS コントローラと 3 つの PLL を搭載しており、最大 3 つのディスプレイを同時に駆動できます。特定のインターフェイスを駆動するには、ユーザーは目的の出力を得るために DSS のビデオポート (VP) および PLL を正しく構成する必要があります。このアプリケーションノートでは、VP と PLL の正しい構成を要約します。

図 1-2. DSS から出力へのルーティング

## 2 個々のディスプレイの設定

### 2.1 OLDI の構成

OLDI を駆動する方法は 5 通りあり、OLDI の制御は Mux 235 によって行われます。

1. シングルリンク OLDI は、最大 165MHz のピクセルクロックで動作する DSS0 VP0 によって制御されます。

2. シングルリンク OLDI は、最大 100MHz のピクセルクロックで動作する DSS1 VP0 によって制御されます。

3. 2 つの独立したシングルリンク OLDI があり、1 つは DSS0 VP0 によって制御され、最大 165MHz のピクセルクロックで動作し、もう 1 つは DSS1 VP0 によって制御され、最大ピクセルクロックで動作します。最大 100MHz のピクセルクロック。

4. 2 つのクローンされたシングルリンク OLDI は、どちらも DSS0 VP0 によって制御され、最大 165MHz のピクセルクロックで動作します。

5. デュアルリンク OLDI は DSS0 VP0 によって制御され、最大 300MHz のピクセルクロックで動作します。

表 2-1. OLDI の構成

| ディスプレ<br>イインター<br>フェイス                           | DSS VP 構成   |             |             |             | PLL 構成 |       |       | 最大ピクセ<br>ル周波数     | マルチプ<br>レクサ | まとめ                                                                                                                                            |

|--------------------------------------------------|-------------|-------------|-------------|-------------|--------|-------|-------|-------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                  | DSS0<br>VP0 | DSS0<br>VP1 | DSS1<br>VP0 | DSS1<br>VP1 | PLL16  | PLL17 | PLL18 |                   |             |                                                                                                                                                |

| OLDI(SL)<br>[OLDI<br>TX0]                        | ✓           |             |             |             | ✓      |       |       | 165MHz            | 該当なし        |                                                                                                                                                |

| OLDI(SL)<br>[OLDI<br>TX1]                        |             |             | ✓           |             |        |       | ✓     | 100MHz            | Mux 235     | Mux 235 は、OLDI1 の入力および PLL クロックを制御します。値が 0 の場合は「DSS0 VP0 + PLL16」、値が 1 の場合は「DSS1 VP0 + PLL18」を意味します。詳細については、TRM 内の CFG0_OLDI1_CLKSEL を参照してください |

| 2x<br>OLDI(SL)<br>[OLDI<br>TX0 &<br>OLDI<br>TX1] | ✓           |             | ✓           |             | ✓      |       | ✓     | 165MHz、<br>100MHz | Mux 235     | Mux 235 は、OLDI1 の入力および PLL クロックを制御します。値が 0 の場合は「DSS0 VP0 + PLL16」、値が 1 の場合は「DSS1 VP0 + PLL18」を意味します。詳しくは、TRM の CFG0_OLDI1_CLKSEL を参照してください     |

| クローンモ<br>ード [OLDI<br>TX0 およ<br>び OLDI<br>TX1]    | ✓           |             |             |             | ✓      |       |       | 165MHz            | 該当なし        | 他の DSS を設定する必要はなく、DSS をドライプします                                                                                                                 |

| OLDI(DL)<br>[OLDI<br>TX0 およ<br>び OLDI<br>TX1]    | ✓           |             |             |             | ✓      |       |       | 300MHz            | 該当なし        |                                                                                                                                                |

## 2.2 DPI の構成

DPI を駆動する方法は 3 通りあり、いずれも複数のマルチプレクサ構成を使用しながら、最大 165MHz のピクセルクロックで動作します。

1. DSS0 VP1 を使用

2. DSS1 VP0 を使用

3. DSS1 VP1 を使用

詳細情報については、CFG0\_DPI0\_OUT\_SEL をご覧ください。

**表 2-2. DPI の構成**

| ディスプレイインターフェイス | DSS VP 構成 |          |          |          | PLL 構成 |        |        | 最大ピクセル周波数 | マルチプレクサ                                                                                                                                                                                                   | まとめ |

|----------------|-----------|----------|----------|----------|--------|--------|--------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                | DSS0 VP0  | DSS0 VP1 | DSS1 VP0 | DSS1 VP1 | PLL 16 | PLL 17 | PLL 18 |           |                                                                                                                                                                                                           |     |

| DPI            |           | ✓        |          |          |        | ✓      |        | 165MHz    | 該当なし                                                                                                                                                                                                      |     |

|                |           |          | ✓        |          |        | ✓      |        | 165MHz    | マルチプレクサ 241:<br>「Select 1 -> PLL17」<br>についての詳細は、以<br>下を参照してください：<br>CFG0_DSS1_DISPC<br>0_CLKSEL(bit16) マ<br>ルチプレクサ 245:<br>「Select 1 -> DSS1<br>VP0」についての詳細<br>は、<br>CFG0_DPI0_OUT_S<br>EL を参照してください      |     |

|                |           |          |          | ✓        |        | ✓      |        | 165MHz    | マルチプレクサ 240:<br>「Select 1 -> PLL17」<br>についての詳細は、以<br>下を参照してください：<br>CFG0_DSS1_DISPC<br>0_CLKSEL (BIT18)<br>マルチプレクサ 245:<br>「Select 2 → DSS1<br>VP1」についての詳細<br>は、以下を参照してくだ<br>さい：<br>CFG0_DPI0_OUT_S<br>EL |     |

## 2.3 DSI の構成

DSI を駆動する方法は 2 通りあり、いずれもマルチプレクサ 240 によって制御されます

1. PLL 18 を最大 300MHz ピクセル クロックで使用します。

2. PLL 17 を最大 165MHz ピクセル クロックで使用します。

| ディスプレ<br>イインター<br>フェイス | DSS VP 構成   |             |             |             | PLL 構成 |        |        | 最大ピクセ<br>ル周波数 | マルチプ<br>レクサ     | まとめ                                                                                               |

|------------------------|-------------|-------------|-------------|-------------|--------|--------|--------|---------------|-----------------|---------------------------------------------------------------------------------------------------|

|                        | DSS0<br>VP0 | DSS0<br>VP1 | DSS1<br>VP0 | DSS1<br>VP1 | PLL 16 | PLL 17 | PLL 18 |               |                 |                                                                                                   |

| DSI                    |             |             |             | ✓           |        |        | ✓      | 300MHz        | 該当なし            |                                                                                                   |

|                        |             |             |             | ✓           |        | ✓      |        | 165MHz        | マルチプ<br>レクサ 240 | マルチプレクサ 240: 1<br>-> PLL 17 を選択しま<br>す。詳細については、<br>CFG0_DSS1_DISPC<br>0_CLKSEL(bit18) をご<br>覧ください |

### 3 同時表示の設定

表 3-1 に、複数のディスプレイが同時に使用されている場合の、各種の VP および PLL 構成を示します。

**表 3-1. 同時表示の設定**

| ディスプレイ 1 (PLL 16)                                        |          | ディスプレイ 2 (PLL 17) |                                              | ディスプレイ 3 (PLL 18) |          | まとめ                  |

|----------------------------------------------------------|----------|-------------------|----------------------------------------------|-------------------|----------|----------------------|

| 出力                                                       | ソース      | 出力                | ソース                                          | 出力                | ソース      |                      |

| OLDI (DL) [または]<br>OLDI(SL) クローン<br>[または] OLDO10<br>(SL) | DSS0 VP0 | DPI               | DSS0 VP1 [または]<br>DSS1 VP0                   | DSI               | DSS1 VP1 | 3 台のディスプレイ<br>が並列で動作 |

| OLDO10 (SL)                                              | DSS0 VP0 | DPI               | DSS0 VP1 [または]<br>DSS1 VP1                   | OLDI1 (SL)        | DSS1 VP0 |                      |

| OLDO10 (SL)                                              | DSS0 VP0 | DSI               | DSS1 VP1                                     | OLDI1 (SL)        | DSS1 VP0 |                      |

| OLDI (DL) [または]<br>OLDI(SL) クローン<br>[または] OLDO10<br>(SL) | DSS0 VP0 | DPI               | DSS0 VP1 [または]<br>DSS1 VP0 [または]<br>DSS1 VP1 | -                 | -        | 2 台のディスプレイ<br>が並列で動作 |

| OLDI (DL) [または]<br>OLDI(SL) クローン<br>[または] OLDO10<br>(SL) | DSS0 VP0 | -                 | -                                            | DSI               | DSS1 VP1 |                      |

| OLDO10 (SL)                                              | DSS0 VP0 | -                 | -                                            | OLDI1 (SL)        | DSS1 VP0 |                      |

| -                                                        | -        | DPI               | DSS0 VP1 [または]<br>DSS1 VP1                   | OLDI1 (SL)        | DSS1 VP0 |                      |

| -                                                        | -        | DSI               | DSS1 VP1                                     | OLDI1 (SL)        | DSS1 VP0 |                      |

| -                                                        | -        | DPI               | DSS0 VP1 [または]<br>DSS1 VP0                   | DSS               | DSS1 VP1 |                      |

## 4 ソフトウェアの設定

### 4.1 OLDI (デュアルリンク)

以下の DTS オーバーレイ (.dtso) を使用して、デュアルリンク OLDI を有効にします。このコードは、次のサイトからも入手できます: [テキサス・インスツルメンツのカーネルソースページ](#)。

```

// SPDX-License-Identifier: GPL-2.0-or-later OR MIT

/**

* Microtips integrated OLDI panel (MF-101HIEBCAF0) and touch DT overlay for AM62P5-SK

*

* Panel data sheet: https://simplespec.microtipsusa.com/uploads/spec/datasheetFile/2588/13-101HIEBCAF0-S\_V1.1\_20221104.pdf

*

* Copyright (C) 2024 Texas Instruments Incorporated - http://www.ti.com/

*/

/dts-v1/;

/plugin/;

#include <dt-bindings/gpio/gpio.h>

#include <dt-bindings/interrupt-controller/irq.h>

&{/} {

display {

compatible = "microtips,mf-101hiebcf0", "panel-simple";

/*

* Note that the OLDI TX 0 transmits the odd set of pixels

* while the OLDI TX 1 transmits the even set. This is a

* fixed configuration in the IP integration and is not

* changeable. The properties, "dual-lvds-odd-pixels" and

* "dual-lvds-even-pixels" have been used to merely

* identify if a Dual Link configuration is required.

* Swapping them will cause an error in the dss oldi driver.

*/

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

dual-lvds-odd-pixels;

lcd_in0: endpoint {

remote-endpoint = <&oldi0_dss0_out>;

};

};

port@1 {

reg = <1>;

dual-lvds-even-pixels;

lcd_in1: endpoint {

remote-endpoint = <&oldi1_dss0_out>;

};

};

};

};

&dss0 {

status = "okay";

};

&oldi0_dss0 {

status = "okay";

ti,companion-oldi = <&oldi1_dss0>;

};

&oldi1_dss0 {

status = "okay";

ti,secondary-oldi;

};

&oldi0_dss0_ports {

```

```

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

oldi0_dss0_in: endpoint {

remote-endpoint = <&dss0_dpi0_out0>;

};

};

port@1 {

reg = <1>;

oldi0_dss0_out: endpoint {

remote-endpoint = <&lcd_in0>;

};

};

&oldi1_dss0_ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

oldi1_dss0_in: endpoint {

remote-endpoint = <&dss0_dpi0_out1>;

};

};

port@1 {

reg = <1>;

oldi1_dss0_out: endpoint {

remote-endpoint = <&lcd_in1>;

};

};

};

&dss0_ports {

#address-cells = <1>;

#size-cells = <0>;

/* VP1: output to OLDI */

port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

dss0_dpi0_out0: endpoint@0 {

reg = <0>;

remote-endpoint = <&oldi0_dss0_in>;

};

dss0_dpi0_out1: endpoint@1 {

reg = <1>;

remote-endpoint = <&oldi1_dss0_in>;

};

};

};

&main_i2c0 {

#address-cells = <1>;

#size-cells = <0>;

touchscreen@41 {

compatible = "ilitek,ili251x";

reg = <0x41>;

interrupt-parent = <&exp1>;

interrupts = <0 IRQ_TYPE_EDGE_FALLING>;

reset-gpios = <&exp2 20 GPIO_ACTIVE_LOW>;

};

};

```

- すべての LCD ベンダには固有のタイミング パラメータがあり、Microtips の LCD にも同様に固有のタイミング パラメータがあります。互換性のあるフィールドは、上記のように DTS ファイルで定義されています。互換フィールドは

- panel-simple.c というファイルにマッピングされ、フィールドはカーネル ディレクトリ `drivers/gpu/drm/panel` の下にあります。panel-simple.c ファイルでは、タイミング パラメータは SK-LCD1 ベンダによって定義されます。

2. デュアルリンク OLDI を使用する場合は、dss0 を使用して、ビデオ信号を OLDI TX0 および OLDI TX1 の両方に送信します。デュアルリンク モードでは、両方の olditx IP が有効になるため、dss0 vp0 の下に 2 つのエンドポイントを使用します。

3. 表示ノードがあり、表示ノード内には 2 つのポート (port@0 および port@1) があります。

4. `dual-lvds-odd-pixels` フラグおよび `dual-lvds-even-pixels` フラグは、構成されているパネルがデュアルリンク OLDI パネルであることを示します。

5. SK-LCD1 はタッチ IC を統合しており、バス アドレス 0x41 で通信します。カスタム ハードウェア設計に基づいて、ユーザーは I2C バス信号、割り込み信号、リセット GPIO 信号を変更する必要があります。

6. DT の詳細については、[AM625 向けのテキサス・インスツルメンツのカーネルソースページ](#)と、[AM65x 向けのテキサス・インスツルメンツのカーネルソースページ](#)を参照してください。

## 4.2 OLDI (シングル リンク - クローン モード)

以下の DTS オーバーレイ (.dtso) の例を使用して、クローン モードでシングルリンク OLDI を有効にします。このコードは [SDK github ページ以外](#) でも利用可能です。

```

// SPDX-License-Identifier: GPL-2.0-or-later OR MIT

/***

* Rocktech Panel (single-link lvds) with AM62P-SK EVM in cloned mode

* AM62P-SKEVM: https://www.ti.com/tool/SK-AM62P-LP

* Copyright (c) 2024 Texas Instruments Incorporated - http://www.ti.com/

*/

/dts-v1/;

/plugin/;

#include <dt-bindings/gpio/gpio.h>

#include <dt-bindings/interrupt-controller/irq.h>

&{/} {

display0 {

compatible = "rocktech,rk101ii01d-ct", "panel-simple";

port {

lcd0_in: endpoint {

remote-endpoint = <&oldi0_dss0_out>;

};

};

};

display1 {

compatible = "rocktech,rk101ii01d-ct", "panel-simple";

port {

lcd1_in: endpoint {

remote-endpoint = <&oldi1_dss0_out>;

};

};

};

};

&dss0 {

status = "okay";

};

&oldi0_dss0 {

status = "okay";

ti,companion-oldi = <&oldi1_dss0>;

};

&oldi1_dss0 {

status = "okay";

ti,secondary-oldi;

};

&oldi0_dss0_ports {

#address-cells = <1>;

#size-cells = <0>;

};

```

```

port@0 {

reg = <0>;

oldi0_dss0_in: endpoint {

remote-endpoint = <&dss0_dpi0_out0>;

};

};

port@1 {

reg = <1>;

oldi0_dss0_out: endpoint {

remote-endpoint = <&lcd0_in>;

};

};

&oldi1_dss0_ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

oldi1_dss0_in: endpoint {

remote-endpoint = <&dss0_dpi0_out1>;

};

};

port@1 {

reg = <1>;

oldi1_dss0_out: endpoint {

remote-endpoint = <&lcd1_in>;

};

};

};

&dss0_ports {

#address-cells = <1>;

#size-cells = <0>;

/* VP1: Output to OLDI */

port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

dss0_dpi0_out0: endpoint@0 {

reg = <0>;

remote-endpoint = <&oldi0_dss0_in>;

};

dss0_dpi0_out1: endpoint@1 {

reg = <1>;

remote-endpoint = <&oldi1_dss0_in>;

};

};

};

```

- すべての LCD ベンダには固有のタイミング パラメータがあり、(例として) Rocktech 製 LCD の場合は、上記のように DTS ファイル内で **compatible** フィールドが定義されています。互換性のあるフィールドは、**panel-simple.c** というファイルにマッピングされます。このファイルは、カーネル ディレクトリ **drivers/GPU/DRM/panel** の下にあります。**panel-simple.c** ファイルでは、タイミング パラメータは SK-LCD1 ベンダによって定義されます。

- クローン モードでのシングル リンク OLDI では、dss0 を使用してビデオ信号を OLDI TX0 および OLDI TX1 の両方に送信します。クローン モードでは、両方の olditx IP が有効になるため、dss0 vp0 の下に 2 つのエンド ポイントが存在します。

- このモードが OLDI (デュアルリンク) モードと異なる点は、**dual-lvds-odd-pixels** および **dual-lvds-even-pixels** が存在しないことです。一方で、コンパニオン ノードは保持されており、これによりシングル リンク クローンモードが適用されます。

- 2 つの個別のディスプレイ ノードがあり、それぞれに 1 つのポート (port@0) があります。

## 4.3 OLDI (シングル リンク - 独立モード)

以下の DTS オーバーレイ (.dtso) の例を使用して、2 系統のシングルリンク OLDI を独立モードで有効にします。このコードは、[SDK Github](#) 以外からも入手できます。

```

// SPDX-License-Identifier: GPL-2.0-or-later OR MIT

/***

* Rocktech Panel (single-link lvds) with AM62P-SK EVM in independent mode

*

* AM62P-SKEVM: https://www.ti.com/tool/SK-AM62P-LP

*

* Copyright (c) 2024 Texas Instruments Incorporated - http://www.ti.com/

*/

/dts-v1/;

/plugin/;

#include <dt-bindings/gpio/gpio.h>

#include <dt-bindings/interrupt-controller/irq.h>

&{/} {

display0 {

compatible = "rocktech,rk101ii01d-ct", "panel-simple";

port {

lcd0_in: endpoint {

remote-endpoint = <&oldi0_dss0_out>;

};

};

};

display1 {

compatible = "rocktech,rk101ii01d-ct", "panel-simple";

port {

lcd1_in: endpoint {

remote-endpoint = <&oldi1_dss1_out>;

};

};

};

};

&dss0 {

status = "okay";

};

&dss1 {

status = "okay";

assigned-clocks = <&k3_clks 235 7>,

<&k3_clks 241 0>;

assigned-clock-parents = <&k3_clks 235 9>, /* OLDI TX1 driven by PLL18 and DSS1 VP0 */

<&k3_clks 241 1>; /* PLL18 for DSS1 VP0 */

};

;

&oldi0_dss0 {

status = "okay";

};

&oldi1_dss1 {

status = "okay";

};

&oldi0_dss0_ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

oldi0_dss0_in: endpoint {

remote-endpoint = <&dss0_dpi0_out0>;

};

};

port@1 {

reg = <1>;

};

}

```

```

oldi0_dss0_out: endpoint {

remote-endpoint = <&lcd0_in>;

};

};

&oldi1_dss1_ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

oldi1_dss1_in: endpoint {

remote-endpoint = <&dss1_dpi0_out1>;

};

};

port@1 {

reg = <1>;

oldi1_dss1_out: endpoint {

remote-endpoint = <&lcd1_in>;

};

};

};

&dss0_ports {

#address-cells = <1>;

#size-cells = <0>;

/* DSS0 VP1: Output to OLDI0 */

port@0 {

reg = <0>;

dss0_dpi0_out0: endpoint {

remote-endpoint = <&oldi0_dss0_in>;

};

};

};

&dss1_ports {

#address-cells = <1>;

#size-cells = <0>;

/* DSS1 VP1: Output to OLDI1 */

port@0 {

reg = <0>;

dss1_dpi0_out1: endpoint {

remote-endpoint = <&oldi1_dss1_in>;

};

};

};

```

- すべての LCD ベンダには固有のタイミング パラメータがあり、(例として) Rocktech 製 LCD の場合は、上記のように DTS ファイル内で **compatible** フィールドが定義されています。互換フィールドは **panel-simple.c** というファイルに対応しており、このファイルはカーネルディレクトリの **drivers/gpu/drm/panel** にあります。panel-simple.c ファイルでは、タイミング パラメータは SK-LCD1 ベンダによって定義されます。

- 独立モードでシングルリンク OLDI を使用する場合は、dss0 を使用して OLDI TX0 を、dss1 を使用して OLDI TX1 をそれぞれ個別に駆動します。独立モードでは、両方の olditx IP が有効になりますが、1 つのエンドポイントは dss0 vp0 の下に、もう 1 つは dss0 vp1 の下に配置されます。

- MUX 構成の詳細については、[AM62P の TISCI ドキュメント](#)を参照してください。

- このモードは、OLDI (シングルリンク — クローン モード) と異なり、OLDI TX0 と OLDI TX1 を連結するコンパニオン ノードが存在しない点で区別されます。

- 2 つの個別のディスプレイノードがあり、それぞれに 1 つのポート (port@0) があります。

## 4.4 DPI / HDMI

- TI の SK-AM62P EVM では、SoC 外部にある Sii902x HDMI ブリッジが DPI 出力に接続されており、DPI 信号を HDMI に変換するために使用されます。関連する DPI およびブリッジ統合の DTS コードは、[テキサス・インスツルメンツのカーネルソースページ](#)に掲載されています。

- カスタムボードで HDMI が不要 (DPI を直接使用する場合) の場合は、上記の DTS ファイルから sii902x ブリッジノードを削除し、該当する dss<x> vp<y> を自分の DPI\_in に接続します。

```

hdmi0: connector-hdmi {

compatible = "hdmi-connector";

label = "hdmi";

type = "a";

port {

hdmi_connector_in: endpoint {

remote-endpoint = <&sii9022_out>;

};

};

};

sii9022: bridge-hdmi@3b {

compatible = "sil,sii9022";

reg = <0x3b>;

interrupt-parent = <&exp1>;

interrupts = <16 IRQ_TYPE_EDGE_FALLING>;

#sound-dai-cells = <0>;

sil,i2s-data-lanes = <0>;

hdmi_tx_ports: ports {

#address-cells = <1>;

#size-cells = <0>;

/*

* HDMI can be serviced with 3 potential VPs -

* (DSS0 VP1 / DSS1 VP0 / DSS1 VP1).

* For now, service with DSS0 VP1.

*/

port@0 {

reg = <0>;

sii9022_in: endpoint {

remote-endpoint = <&dss0_dpi1_out>;

};

};

port@1 {

reg = <1>;

sii9022_out: endpoint {

remote-endpoint = <&hdmi_connector_in>;

};

};

};

};

&dss0_ports {

/* DSS0-VP2: DPI/HDMI Output */

hdmi0_dss: port@1 {

reg = <1>;

dss0_dpi1_out: endpoint {

remote-endpoint = <&sii9022_in>;

};

};

};

```

- 別の DSS/VP から DPI / HDMI を駆動するには、「[DPI の設定](#)」に示されている可能な構成に従ってクロック マルチプレクサを変更します。詳細については、[AM62P の TISCI ドキュメント](#)を参照してください。

## 4.5 DSI

DSI を有効にするには、次の DTS オーバーレイ (.dtso) の例を使用します。このコードは、[テキサス・インストルメンツのカーネルソースページ](#)でも入手可能です。

```

// SPDX-License-Identifier: GPL-2.0-or-later OR MIT

/***

* DT Overlay for RPi 7inch touchscreen panel interfaced with DSI on

* AM62P5-SK EVM.

*

* RPi DSI Panel: https://www.raspberrypi.com/products/raspberry-pi-touch-display/

*

* Copyright (C) 2024 Texas Instruments Incorporated - https://www.ti.com/

*/

/dts-v1/;

/plugin/;

#include <dt-bindings/gpio/gpio.h>

#include <dt-bindings/interrupt-controller/irq.h>

#include "k3-pinctrl.h"

&{/} {

panel0 {

compatible = "raspberrypi,7inch-dsi", "simple-panel";

backlight = <&display_reg>;

power-supply = <&display_reg>;

port {

panel_in: endpoint {

remote-endpoint = <&panel_bridge_out>;

};

};

};

bridge_reg: bridge-regulator {

compatible = "regulator-fixed";

regulator-name = "bridge-reg";

gpio = <&display_reg 0 0>;

vin-supply = <&display_reg>;

enable-active-high;

};

};

&dphy_tx0 {

status = "okay";

};

&main_i2c0 {

#address-cells = <1>;

#size-cells = <0>;

display_reg: regulator@45 {

compatible = "raspberrypi,7inch-touchscreen-panel-regulator";

reg = <0x45>;

gpio-controller;

#gpio-cells = <2>;

};

};

&dss1 {

status = "okay";

};

&dss1_ports {

#address-cells = <1>;

#size-cells = <0>;

/* DSS1-VP1: DSI Output */

port@1 {

reg = <1>;

dss1_dpil_out: endpoint {

remote-endpoint = <&dssi0_in>;

};

};

};

```

```

};

&dsi0 {

status = "okay";

#address-cells = <1>;

#size-cells = <0>;

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

dsi0_out: endpoint {

remote-endpoint = <&panel_bridge_in>;

};

};

port@1 {

reg = <1>;

dsi0_in: endpoint {

remote-endpoint = <&dss1_dpi1_out>;

};

};

};

bridge@0 {

status = "okay";

compatible = "toshiba,tc358762";

reg = <0>;

vddc-supply = <&bridge_reg>;

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

panel_bridge_in: endpoint {

remote-endpoint = <&dsi0_out>;

};

};

port@1 {

reg = <1>;

panel_bridge_out: endpoint {

remote-endpoint = <&panel_in>;

};

};

};

};

};

}

```

- DSI 出力は、DSS1 VP1 からの DPI 出力に接続された Cadence DSI/DPHY ブリッジを介して生成されます。このブリッジドライバに関する詳細は、[テキサス・インスツルメンツのカーネル ソース ページ](#)に掲載されています。このブリッジは SoC の内部にあります。

- DSI 出力は Raspberry Pi DSI パネルの DSI\_in に接続されており、このパネル内部では Toshiba ブリッジを使用して DSI を DPI に変換しています。同じ dtso にドライバを実装します。その他の資料については、[テキサス・インスツルメンツのカーネル ソース ページ](#)を参照してください。

## 5 まとめ

本アプリケーションノートは、システムのディスプレイサブシステムを構成するための技術ガイドとして機能し、複数のディスプレイパネルを同時に駆動するためのガイドラインをエンジニアに提供します。

本書では、3つの主要なディスプレイインターフェイスの動作モードおよび性能の特性について詳しく説明しています。このドキュメントでは、それぞれのインターフェイスがどのように構成可能であるかを説明しており、高解像度ディスプレイのサポートと複数ディスプレイの同時運用とのバランスを柔軟に調整できる方法を示しています。

このアプリケーションノートの主要な目的の一つは、複数のディスプレイを同時に使用する際のルールや制限事項を明確にすることです。このドキュメントでは、DSS固有のリソース割り当てに関するさまざまな組み合わせを取り上げており、設計者がアプリケーション固有の要件を満たす安定かつ実用的なマルチディスプレイ構成を実現できるよう、適切な判断ができる目的としています。

ディスプレイ関連の問題のデバッグのヘルプについては、この[デバッグガイド](#)を参照してください。問題が解決しない場合は、[e2e.ti.com](http://e2e.ti.com)でクエリを投稿してください。

## 6 参考資料

- テキサス・インスツルメンツ、[AM62P](#) 製品フォルダ。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1)お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所 : Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated