*Application Note***TDP142 構成ガイド**

Jae Yoon

**概要**

TDP142 は、DisplayPort 1.4 から HBR3 (8.1Gbps) までをサポートするリニアリドライバです。このようにデータレートが高い場合、シグナルインテグリティの問題によりシステムのパターン長が制限されます。TDP142 は、符号間干渉 ISI による基板の損失を補償するため、16 のレベルの受信リニアイコライゼーションを行えます。このドキュメントは、TDP142 をソース/シンク アプリケーションで使用する方法に関する一般的なガイドラインを示すことを目的としています。

**目次**

|                                      |          |

|--------------------------------------|----------|

| <b>1はじめに</b> .....                   | <b>2</b> |

| <b>2デバイス設定</b> .....                 | <b>2</b> |

| <b>3イコライゼーションの選択</b> .....           | <b>3</b> |

| <b>4イコライゼーションの選択例</b> .....          | <b>4</b> |

| <b>5AUXP/N および SNOOPENZ 構成</b> ..... | <b>5</b> |

| <b>6レイアウトのガイドライン</b> .....           | <b>6</b> |

| 6.1 GND スティング.....                   | 7        |

| 6.2 AC カップリング コンデンサ.....             | 7        |

| 6.3 レイアウト例.....                      | 8        |

| <b>7まとめ</b> .....                    | <b>8</b> |

| <b>8参考資料</b> .....                   | <b>9</b> |

**商標**

DisplayPort™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

TDP142 は、レーンごとに最大 HBR3 (8.1Gbps) をサポートすることを目的とした DisplayPort™ リニアリドライバです。さらに、DP リンクトレーニングの透過性により、TDP142 はソースまたはシンク アプリケーション向けに設計された位置に依存しないデバイスになります。DisplayPort 規格では、準拠した受信機が動作する必要があるチャネルの最後の最小アイの高さと幅が定義されています。トレース長が長いと、ISI がチャネルの損失に寄与し、アイの高さと幅が準拠せず、受信側がそのチャネル上のデータを確実に回復できなくなるよう、アイを閉じます。TDP142 は、ISI による基板配線損失を補償し、規格に準拠したアイパターンに復元するためのイコライゼーション ゲインを提供します。

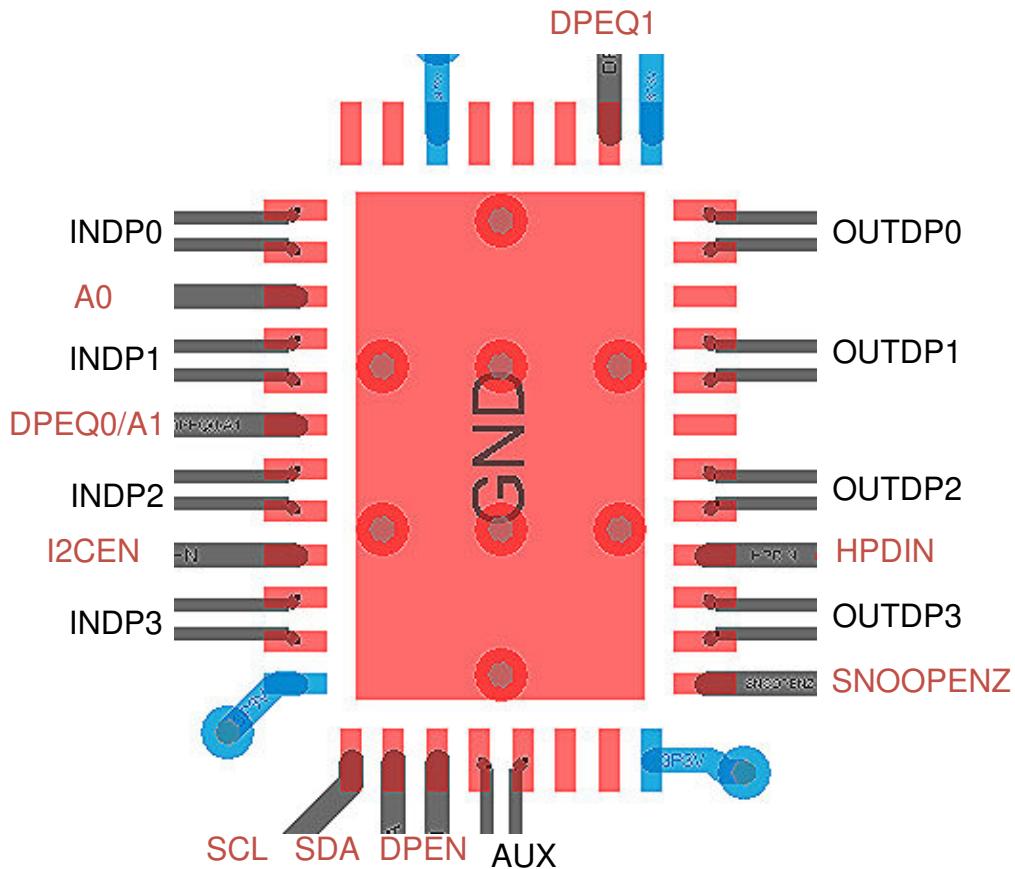

## 2 デバイス設定

TDP142 は、GPIO および I2C モードの構成モードをサポートしています。[表 2-1](#) に、TDP142 の 4 レベル制御ピンの設定の詳細を示します。[表 2-2](#) に、ピン設定に基づいた TDP142 モード構成の詳細を示します。デバイスが GPIO モードに設定されている場合、DisplayPort および AUX スヌープ機能を有効にするためのピン構成については[表 2-2](#) を参照し、イコライゼーション設定を変更するための DPEQ1 および DPEQ0 ピン構成については[表 3-1](#) を参照してください。構成の詳細と I2C 経由のレジスタ マッピングについては、[『TDP142 DisplayPort™ 8.1Gbps リニアリドライバ』](#)のデータシートを参照してください。

**表 2-1. 4 レベル制御ピンの設定**

| レベル | 設定                                                |

|-----|---------------------------------------------------|

| 0   | オプション 1:1kΩ 5% を GND に接続します。<br>オプション 2:GND に直接接続 |

| R   | 20kΩ 5% を GND に接続します。                             |

| F   | フロート (ピンはオープンのままにする)                              |

| 1   | オプション 1:1kΩ 5% を VCC に接続します。<br>オプション 2:VCC に直接接続 |

**表 2-2. TDP142 モード構成**

| I2C_EN | 構成                |

|--------|-------------------|

| F      | I2C は 1.8V でイネーブル |

| 1      | I2C は 3.3V でイネーブル |

| 0      | GPIO モード          |

**表 2-3. TDP142 GPIO モード構成**

| DPEN/HPDIN | SNOOPENZ/RSVD8 | 構成              |

|------------|----------------|-----------------|

| 1          | -              | DisplayPort は有効 |

| 0          | -              | DisplayPort は無効 |

| -          | 1              | AUX スヌープは有効     |

| -          | 0              | AUX スヌープは無効     |

### 3 イコライゼーションの選択

ソース/シンクアプリケーションで使用される TDP142 により、システムは DisplayPort 1.4 のトランシミッタの電気的規格に準拠することと、DisplayPort 1.4 のレシーバジッタ耐性試験の両方に合格することができます。TDP142 は、チャネル挿入損失を補償するイコライゼーションを適用して、ソースからシンクに受信データを回復します。イコライゼーションは、TDP142 レシーバ（プリチャネル）前のチャネル挿入損失の量と、TDP142（ポストチャネル）後のチャネル挿入損失に基づいて設定できます。GPIO またはピンストラップモードでは、DPEQ[1:0] ピンを設定することにより、各レーンの EQ 値がグローバルに設定されます。I2C モードでは、等価なレジスタをプログラムすることで、各チャネルの EQ 値が個別のチャネルでの損失に基づいて個別に設定されます。[表 3-1](#) に、イコライゼーション値の詳細を示します。[表 3-2](#) に、FR4 パターンの代表的な損失を示します。

**表 3-1. TDP142 のイコライゼーション**

| イコライゼーション設定番号 | すべての DisplayPort レーン |             |                     |

|---------------|----------------------|-------------|---------------------|

|               | DPEQ1 ピンレベル          | DPEQ0 ピンレベル | EQ ゲイン 4.05GHz (dB) |

| 0             | 0                    | 0           | 1.0                 |

| 1             | 0                    | R           | 3.3                 |

| 2             | 0                    | F           | 4.9                 |

| 3             | 0                    | 1           | 6.5                 |

| 4             | R                    | 0           | 7.5                 |

| 5             | R                    | R           | 8.6                 |

| 6             | R                    | F           | 9.5                 |

| 7             | R                    | 1           | 10.4                |

| 8             | F                    | 0           | 11.1                |

| 9             | F                    | R           | 11.7                |

| 10            | F                    | F           | 12.3                |

| 11            | F                    | 1           | 12.8                |

| 12            | 1                    | 0           | 13.2                |

| 13            | 1                    | R           | 13.6                |

| 14            | 1                    | F           | 14.0                |

| 15            | 1                    | 1           | 14.4                |

**表 3-2. FR4 トレース損失の例**

| 4mil 幅 FR4 PCB パターン長 (インチ) | 2.5GHz での損失 (0.49dB/インチ) (dB) | 4.05GHz での損失 (0.73dB/インチ) (dB) | 5GHz での損失 (0.87dB/インチ) (dB) |

|----------------------------|-------------------------------|--------------------------------|-----------------------------|

| 1                          | 0.5                           | 0.7                            | 0.9                         |

| 2                          | 1                             | 1.5                            | 1.7                         |

| 3                          | 1.5                           | 2.2                            | 2.6                         |

| 4                          | 2                             | 2.9                            | 3.5                         |

| 5                          | 2.5                           | 3.7                            | 4.3                         |

| 6                          | 2.9                           | 4.4                            | 5.2                         |

| 7                          | 3.4                           | 5.1                            | 6.1                         |

| 8                          | 3.9                           | 5.9                            | 7                           |

| 9                          | 4.4                           | 6.6                            | 7.8                         |

| 10                         | 4.9                           | 7.3                            | 8.7                         |

## 4 イコライゼーションの選択例

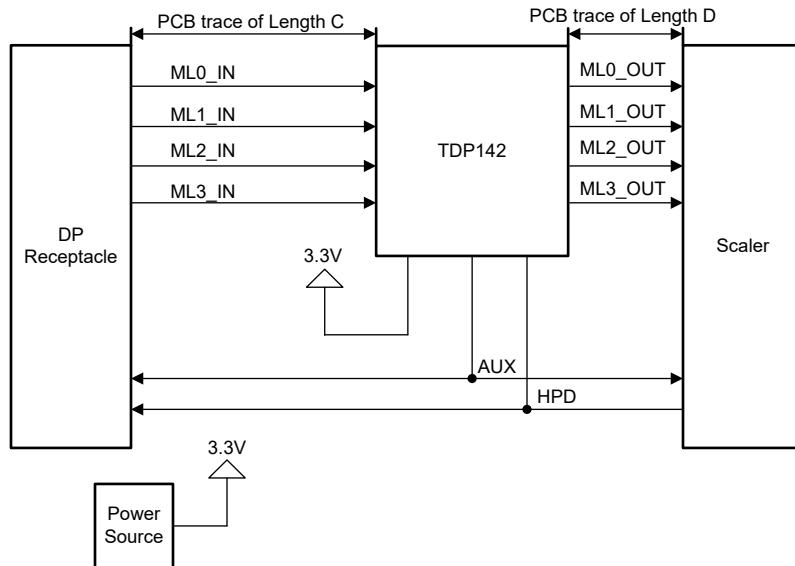

図 4-1. TDP142 シンク側イコライゼーションの例

このセクションでは、さまざまなパターン長のイコライゼーションを選択する例について説明します。図 4-1 に、TDP142 のシンク側アプリケーションの例を示します。このシンク側アプリケーションのイコライゼーション値を選択するには、以下の方法が使用されます。

- PCB パターンの長さ  $C = 8$  インチ FR4 PCB パターン (4.05GHz で 5.9dB 損失)。使用する DPEQ 設定 = 設定値 5 (6.5dB)。

レイアウト品質、DP ドライバ、レシーバ品質などの他の要因では、最高の性能を得るためにイコライゼーション設定を高くまたは低く調整する必要があります。上記の方法は、システム基板のトレース長に基づいて初期構成設定を選択するために使用することを推奨します。

## 5 AUXP/N および SNOOPENZ 構成

TDP142 は、AUXp ピンと AUXn ピンを使用して AUX をスヌープします。AUX スヌーピングにより、TDP142 は、DisplayPort ソースと DisplayPort シンク間のトラフィックが通過するときにネイティブ AUX トラフィックを監視できます。

TDP142 は、DisplayPort シンクの DPCD レジスタ 0x00101 (LANE\_COUNT\_SET) および 0x00600 (SET\_POWER\_STATE) へのネイティブ AUX 書き込みをスヌープします。TDP142 は、LANE\_COUNT\_SET に書き込まれた値に基づいてレーンを無効化または有効化します。SET\_POWER\_STATE が D3 のとき、TDP142 はすべてのレーンを無効化します。それ以外の場合、アクティブなレーンは LANE\_COUNT\_SET の値に基づいています。

GPIO モードでは、SNOOPENZ ピンを low にストラップすることで、直接 GND にプルダウンするか、1k のプルダウン抵抗で GND にプルダウンすることで、AUX スヌーピングが有効になります。I2C モードでは、AUX スヌーピングはデフォルトで有効になります。AUX スヌーピングは、レジスタ 0x13 のビット 7 に 1 を書き込むことで無効にできます。

AUX スヌーピングが無効化されている場合、GPIO モードにおいて 4 つの DisplayPort レーンすべてがアクティブになります。I2C モードでは、レジスタ 0x13 のビット [3:0] に書き込むことで、各レーンをイネーブルまたはディセーブルできます。

AUXP には  $100\text{k}\Omega$  プルダウン抵抗が必要で、AUXN にはソース用の  $100\text{k}\Omega$  プルアップ抵抗が必要です。シンクの場合、AUXp は 3.3V に 1M プルアップし、AUXn は GND に 1M プルダウンしています。これらの抵抗は、 $100\text{nF}$  コンデンサの TDP142 側に配置する必要があります。

デュアル モード DisplayPort をサポートするアプリケーションの場合:SNOOPENZ ピンは、SN74AHC125 などのバッファを介して、DisplayPort レセプタクルの CONFIG1 に接続する必要があります。デュアル モードアダプタが DisplayPort レセプタクルに接続されている場合、SNOOPENZ ピンの内部プルダウンが強すぎて有効な VIH を登録できないため、バッファが必要です。

## 6 レイアウトのガイドライン

高速 DisplayPort 信号を TDP142 との間で配線するには、以下のレイアウト ガイドラインを使用する必要があります。

- INDP と OUTDP のペアは、制御された  $100\Omega$  差動インピーダンス ( $\pm 10\%$ ) で配線する必要があります。

- 差動ペアを他の高速信号から遠ざけてください。

- ペア内の配線は 5mil 以内に維持する必要があります。

- 「[DisplayPort 設計ガイド](#)」に従って、DisplayPort レーンのペア間配線は 2 UI 以内に抑える必要があります。

- 差動ペアの長さのマッチングは、不一致の場所の近くで行う必要があります。

- 各ペアは、信号トレース幅の少なくとも 3 倍離す必要があります。

- 差動配線での曲げの使用は最小限に抑える必要があります。曲げを使用する場合、左曲げと右曲げの数はできる限り等しくする必要があります、曲げ角度は  $135^\circ$  以上である必要があります。これにより、曲げによって生じる長さの不一致を最小限に抑え、曲げが EMI に与える影響を最小限に抑えることができます。

- すべての差動ペアは同じ層に配線します。

- ビアの数を最小限に抑える。ビアの数を 2 以下にすることを推奨します。

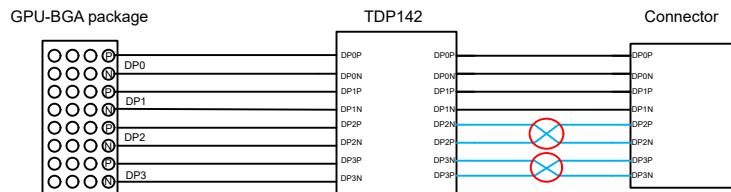

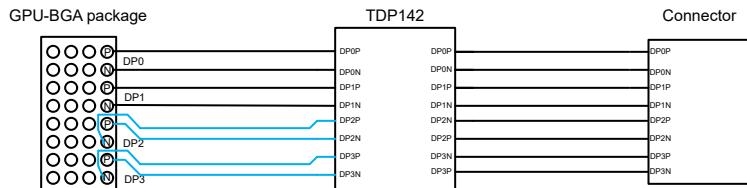

- デバイスの出力ピンとコネクタとの間の順序が一致していないため、レイアウトでは OUTDP2 と OUTDP3 で信号が交差する可能性があります。設計の 1 つは、GPU が BGA パッケージの場合にデバイスの入力で極性をスワップすることです。これにより、使用するビアの数を最小限に抑えることができます。[図 6-1](#) と [図 6-2](#) を参照してください。

図 6-1. 出力側での信号交差

図 6-2. INDP2 と INDP3 の極性スワップ

- 差動トレースをグランドプレーンに隣接するレイヤーに配置します。

- 差動ペアを分割プレーン上に配線しないでください。

- スルーホールコネクタを使用する場合は、コネクタの反対側に高速信号を配線し、コネクタピンが伝送ラインにスタブを形成しないようにします。

- インピーダンスの不連続性を防止するため、テスト ポイントを直列に対称に配置する必要があります。

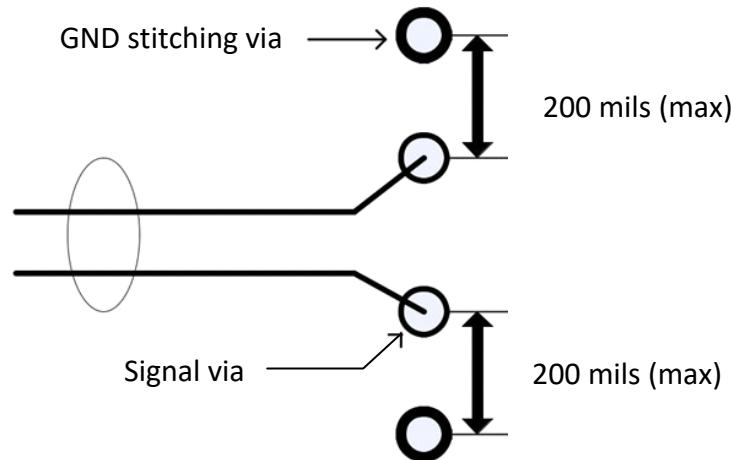

## 6.1 GND スティッチング

高速信号トレース全体は、同じ GND 基準プレーンの起点から終端に維持する必要があります。同じ GND 基準プレーンが維持されない場合は、両方の GND プレーンを互いにビアステッチして、連続的なグランドと均一なインピーダンスを確保します。これらのステッチングビアは、信号遷移ビアの 200mil 以内(中心から中心、近い方が良い)に対称的に配置します。GND スティッチングビアの例については、図 6-3 を参照してください。

図 6-3. GND スティッチングビアの例

## 6.2 AC カップリングコンデンサ

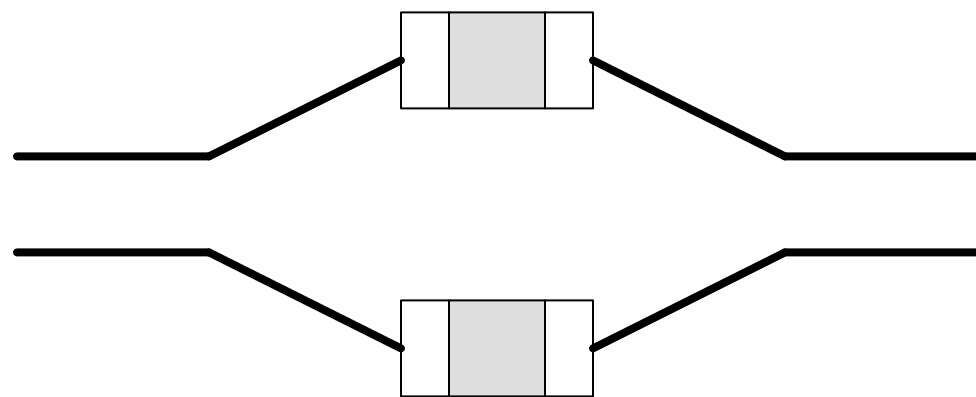

AC カップリングコンデンサを配置する場合に推奨される部品サイズは 0201 です。使用する最大部品サイズは 0402 にする必要があります。レイアウト中、最適な信号品質を確保し、反射を最小限に抑えるため、AC カップリングコンデンサは本デバイスのトランミッタピンの近くに対称的に配置する必要があります。AC カップリングコンデンサは、デバイスのできるだけ近くに、またはトランミッタ側に配置します。AC 結合コンデンサのレイアウト対称性を表す図 6-4。

図 6-4. AC カップリングコンデンサのレイアウトの対称性の例

### 注

高速トレースにテストポイントを追加すると、インピーダンスの不連続性が生じ、信号性能に悪影響を及ぼします。テストポイントを使用する場合、テストポイントを連続的かつ対称的に配置する必要があります。差動ペアにスタブを形成するような方法で、テストポイントを配置するべきではありません。

### 6.3 レイアウト例

図 6-5. レイアウト例

### 7 まとめ

このドキュメントには、システムで TDP142 をセットアップおよび構成するために必要なツールが記載されています。詳細については、このドキュメントに加えて、[TDP142 DisplayPort™ 8.1 Gbps リニアリドライバ](#)および[TDP142 回路図チェックリスト](#)を参照してください。

## 8 参考資料

- テキサス インスツルメンツ、*TDP142 DisplayPort™ 8.1 Gbps リニアリドライバ*、データシート

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月