*Application Note***TPS65992S PD コントローラを使用して TPS55288 と

TUSB1044 を制御****概要**

このアプリケーションノートでは、TPS65992S USB Type-C®/PD コントローラーの I2C コントローラ機能を利用して、USB-C Power Delivery システムにおける 2 つの主要なコンパニオン デバイス、つまり TPS55288 (昇降圧レギュレータ) と TUSB1044 (リニアリドライバ/USB Type-C クロスポイントスイッチ) を制御する方法について説明します。このアプリケーションノートでは、自動 I2C 制御のために必要な TPS65992S の設定、VBUS 電圧を制御するための TPS55288 のレジスタ設定、USB3/DisplayPort レーンの切り替えを行うための TUSB1044 の設定について説明します。特に注意が必要なのは、マルチバイト I2C トランザクション (例: TPS55288 の出力電圧リファレンス設定)、TUSB1044 の制御レジスタビット (CTLSEL、FLIP\_SEL、EQ\_OVERRIDE など) の解釈、およびアタッチ、デタッチ、DisplayPort オルタネートモード時のデバイスの正常な動作維持です。各レジスタ値の根拠となるデータシートに基づいた説明もあわせて記載し、設定内容の論理を明確にしています。その結果、外部マイコンを必要とせず、PD コントローラが電源およびデータバスの切り替えをシームレスに制御する協調設計が実現します。

**目次**

|                                               |    |

|-----------------------------------------------|----|

| 1はじめに.....                                    | 2  |

| 2 TPS65992S アプリケーションツールにおける I2C コントローラ設定..... | 4  |

| 3 I2C3 を使用して TPS55288 昇降圧コンバータを構成する.....      | 6  |

| 4 I2C3 経由での TUSB1044 リドライバの構成.....            | 11 |

| 5 I2C イベント表の概要.....                           | 22 |

| 6 参考資料.....                                   | 24 |

**商標**

USB Type-C® is a registered trademark of USB Implementers Forum.

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

TPS65992S は、単一ポート対応の USB Type-C および USB Power Delivery (PD) コントローラであり、他のデバイスとの通信のためのさまざまなデジタルインターフェイスを統合しています。TPS65992S は 3 つの I<sub>2</sub>C ポートを提供しています:I<sub>2</sub>C1 および I<sub>2</sub>C2 は、I<sub>2</sub>C ペリフェラルインターフェイス(ホストまたは EC 通信用)として機能し、I<sub>2</sub>C3 は I<sub>2</sub>C コントローラとして機能します。この I<sub>2</sub>C コントローラポートにより、TPS65992S はボード上の外付け部品を直接制御できます。ここで説明する設計では、I<sub>2</sub>C3 を使用して、TPS55288 昇降圧コンバータと TUSB1044 リニアリドライバという 2 つの主要なデバイスを管理します。

TUSB1044 は、USB Type-C オルタネートモード対応リドライバスイッチ兼スイッチ(高速信号用のリニアリピータ)であり、最大 10Gbps の SuperSpeed データレートをサポートし、プロトコルに依存しません。つまり、TUSB1044 は USB3.1 Gen2 信号を透過できるだけでなく、DisplayPort オルタネートモード時に USB-C コネクタ上で DisplayPort のレーンをルーティングすることも可能です。このデバイスは、固定ピン設定による構成のほか、I<sub>2</sub>Cインターフェイスを通じた動的制御にも対応しています。内部レジスタでは、動作モードの制御、高速レーンマッピングの反転、イコライゼーション(EQ) 設定、その他の機能の制御が可能です(詳細は TUSB1044 のデータシートのレジスタマップを参照してください)。TPS65992S を I<sub>2</sub>C コントローラとして使用することで、システムは、ケーブルの向きや交渉されたモードに応じて、TUSB1044 に USB3 専用動作と複数の DisplayPort オルタネートモード構成の間で切り替えるようにコマンドできます。

**表 1-1. TUSB1044 レジスタマップ**

| オフセット | 略称            | レジスタ名                             |

|-------|---------------|-----------------------------------|

| Ah    | General_1     | 汎用レジスタ 1                          |

| Bh    | General_2     | 汎用レジスタ 2                          |

| Ch    | General_3     | 汎用レジスタ 3                          |

| 10h   | UFP2_EQ       | UFP2 EQ コントロール                    |

| 11h   | UFP1_EQ       | UFP1 EQ コントロール                    |

| 12h   | DisplayPort_1 | AUX スヌープステータス                     |

| 13h   | DisplayPort_2 | DP レーン有効化/無効化制御                   |

| 1Bh   | SOFT_RESET    | I <sub>2</sub> C および DPCD ソフトリセット |

| 20h   | DFP2_EQ       | DFP2 EQ コントロール                    |

| 21h   | DFP1_EQ       | DFP1 EQ コントロール                    |

| 22h   | USB3_MISC     | その他の USB3 制御                      |

| 23h   | USB3_LOS      | USB3 LOS スレッショルド制御                |

TPS55288 は、USB Power Delivery のソース用途向けに設計された同期式 4 スイッチの昇降圧コンバータです。

TPS55288 は、入力電圧以下、同等、またはそれ以上の出力電圧を制御でき、広い入力範囲(2.7V ~ 36V)と 0.8V から最大 22V までの出力範囲をサポートします。TPS55288 は、出力レベルを決定する内部リファレンス電圧を設定するための 10 ビット DAC を搭載しており、1LSB は約 1.129mV に相当します。I<sub>2</sub>Cインターフェイスを介して、出力電圧および電流制限をプログラム可能であり、USB PD 要件(プログラム可能電源[PPS]を含む)に準拠できます。実際には、このコンバータは典型的な 12V 入力から最大 100W(例えば 20V で 5A)までの出力を供給できます。TPS55288 の主要な設定レジスタには、内部リファレンス電圧を設定する REF レジスタ(0x00 および 0x01)、電流制限用の I<sub>OUT\_LIMIT</sub> レジスタ(0x02)、スルーレートやフィードバック選択などを制御するレジスタがあります。例えば、REF レジスタ(0x00/0x01)は 10 ビットの値を形成し、コンバータのリファレンス電圧をプログラムします。適切な値を書き込むことで、内部帰還比に応じて出力電圧が調整されます。

**表 1-2. TPS55288 レジスタ マップ**

| アドレス   | 略称         | レジスタ名   |

|--------|------------|---------|

| 0h, 1h | REF        | 基準電圧    |

| 2h     | IOUT_LIMIT | 電流制限の設定 |

| 3h     | VOUT_SR    | スルーレート  |

| 4h     | VOUT_FS    | 帰還の選択   |

| 5h     | CDC        | ケーブル補償  |

| 6h     | モード        | モード制御   |

| 7h     | STATUS     | 動作ステータス |

このアプリケーションノートでは、TPS65992S PD コントローラの I2C3 コントローラ インターフェイスが、TPS55288 と TUSB1044 を連携して制御するためにどのように設定されているかを説明しています。TPS65992S アプリケーション カスタマイズ ツールでの必要な設定、I2C コマンド シーケンスの構成 (適切なペリフェラル アドレスとレジスタ アドレスを含む)、および PD ネゴシエーションや USB-C オルタネート モード動作中にこれらのデバイスがシームレスに機能するためのイベントトリガ型 I2C トランザクションについて説明します。以下の各セクションでは、それぞれパワー コンバータとリドライバの設定について説明し、その後、本設計で使用されるすべての I2C イベントの概要をまとめています。

## 2 TPS65992S アプリケーションツールにおける I<sub>C</sub> コントローラ設定

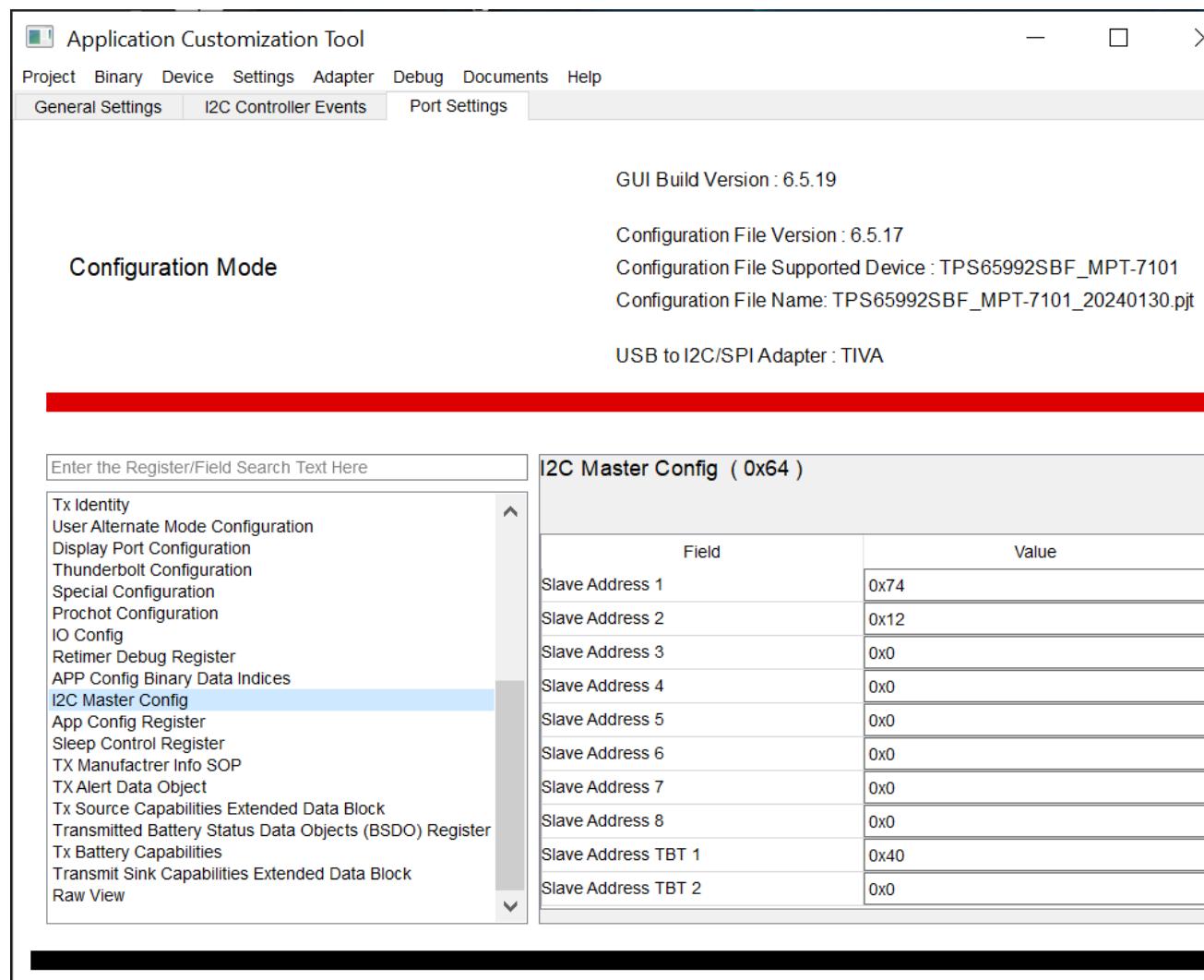

TPS65992S が TPS55288 および TUSB1044 を管理するには、I<sub>C</sub>3 コントローラポートを正しいペリフェラルアドレスで設定し、各デバイスに対応するコマンドインデックスをマッピングする必要があります。TPS65992S アプリケーションカスタマイズツール(PD コントローラファームウェアを構成するための GUI)を使用して、各外部 I<sub>C</sub> ペリフェラルに 7 ビットアドレスが追加され、アドレスインデックス(PD ファームウェアで使用される識別子)が割り当てられます。このツールでは、特定の PD イベント(パワーオン、アタッチ、契約交渉など)に関連付けて、I<sub>C</sub> レジスタの読み書き操作のシーケンスを定義することもできます。

このデザインでは、I<sub>C</sub>3 コントローラポートを次のように設定しています：

- **TPS55288 (昇降圧コンバータ)** - 7 ビットの I<sub>C</sub> アドレス **0x74**。このデバイスは、PD コントローラの I<sub>C</sub> コントローラ設定で **Address0**(アドレスインデックス = 0)として追加されます。PD コントローラの I<sub>C</sub> イベントテーブルでは、TPS55288 を対象とするコマンド用にレジスタインデックス 0 から 8 が予約されています。(注: 0x74 は、デバイスの I<sub>C</sub>CADD ピン/モードビットが 0 のときの TPS55288 のデフォルト I<sub>C</sub> アドレスであり、これは当社の設定と一致しています。)

- **TUSB1044 (USB-C リドライバー)** - 7 ビット I<sub>C</sub> アドレス **0x12**。このデバイスは、PD コントローラの設定で **Address1**(アドレスインデックス = 1)として追加されます。イベントテーブルでは、TUSB1044 向けのコマンド用にレジスタインデックス 9 から 28 を割り当てています。(I<sub>C</sub> モードにおける TUSB1044 のアドレスはピンストラップによって決まりますが、ここではアドレスを 0x12 に設定しています。)

2 つのペリフェラルとアドレスが定義されると、TPS65992S のファームウェアは、割り当てられたアドレスインデックスを使って I<sub>C</sub> トランザクションを正しいデバイスに送信できるようになります。[図 2-1](#) に、TPS65992S GUI の例を示します：**Address0** は 0x74 の TPS55288 に対応し、**Address1** は 0x12 の TUSB1044 に対応します。アドレスマップが設定できたら、PD コントローラの I<sub>C</sub> コントローライベントテーブルにエントリを作成できます。各エントリ(上記のレジスタインデックスで管理)は、イベントトリガ、ターゲットとなるペリフェラル(アドレスインデックスで指定)、ペリフェラル上のレジスタアドレス、書き込み(または読み出し)データバイト、およびコマンドが方向に依存するかどうかを指定します。以下のセクションでは、それぞれのデバイスに対して設定されたコマンドシーケンスの詳細を説明します。

図 2-1. TPS65992S GUI での I2C コントローラ設定

### 3 I2C3 を使用して TPS55288 昇降圧コンバータを構成する

TPS55288 では、PD ネゴシエーションに基づいてコンバータの出力動作をプログラミし、電源投入時や接続解除時には安全なデフォルト状態を維持することが目的です。TPS65992S のイベントテーブル（インデックス 0~8 は TPS55288 に割り当てられています）は、それに応じて設定されています。TPS55288 の主要なレジスタ設定は、データシートに基づいて決定されています：

- **REF (0x00/0x01):** 内部基準電圧を設定します。これをフィードバック構成と組み合わせることで、 $V_{OUT}$  が決定されます。これは 10 ビットの値で、2 つのレジスタに分割されています（0x01 が MSB、0x00 が LSB です）。1LSB は、基準電圧のおよそ 1.129mV に相当します。**REF** を調整することで、出力は約 45mV の最小リファレンス（0x0000 で最低出力）から 1.2V の最大リファレンス（0x03FF で最大出力）まで変更可能です。リセット後のデフォルト **REF** 値は 0x00D2（LSB=0xD2、MSB=0x00）で、これは約 282mV に相当します。TPS55288 のデフォルトのフィードバック比率は内部検出用に設定されており（以下の  $V_{OUT\_FS}$  参照）、そのため 282mV のリファレンスは出力で約 5V に相当します（詳細は以下で説明します）。

- **$V_{OUT\_FS}$  (0x04):** 帰還選択レジスタは、コンバータが  $V_{OUT}$  検出に内部分圧抵抗を使用するか、外部帰還回路を使用するかを制御します。帰還選択レジスタは、使用する場合、内部帰還比を選択します。デフォルトで、 $V_{OUT\_FS}$  は 0x03（2 進数 0000\_0011）となっており、これは内部帰還が有効（bit7 = 0）で、内部帰還比率が 0.0564（bits1:0 = 11b）に設定されていることを意味します。比率 0.0564 は、リファレンスから出力への約 20 倍の増幅を意味します（ $0.0564 \times 20 \approx 1$ ）。これにより、リファレンスが最大の約 1.129V の場合、出力は約 20V に達します。簡単に言うと、デフォルトの比率では、282mV のリファレンスが約 5V の出力に、1.129V のリファレンスが約 20V の出力に対応し、これは PD プロファイルで必要な範囲をカバーしています。

- **モード (0x06):** モード制御レジスタにはさまざまな制御ビットが含まれており、特に、bit7 は **OE**（出力イネーブル）で、コンバータ出力をオンにするにはこのビットを 1 に設定する必要があります。その他のビットは、ヒカッピ保護、シャットダウン時の放電、I2C アドレスの選択、軽荷負時モード（PFM/FPWM）などの機能を設定します。ちなみに、bit2（I2CADD）は I2C アドレスを選択し（0 は 0x74、1 は 0x75）、bit0（MODE）は特定の設定を外部抵抗から取得するか内部レジスタから取得するかを選択します。このデザインでは、I2CADD を 0（アドレス 0x74 使用）に設定し、VCC および PFM の制御方法はデフォルトの外部抵抗制御（bit0 = 0）を採用しています。これはハードウェア設計が適切なデフォルトを提供しているためです。ただし、出力イネーブル（OE）は I2C 経由で有効にし、その他のビットも動作に適した状態に設定されていることを確認しています。

これらのレジスタを使用して、TPS65992S I2C イベントシーケンスを以下のように構成します：

#### パワーオン初期化

PD コントローラのパワーオンリセット（PoR）時に、TPS55288 を既知の安全な状態に初期化します。これにより、ポートがアクティブになると PD コントローラは標準的な USB-C のデフォルト電圧である 5V を供給できる準備が整います。TPS65992S のファームウェアは、PD コントローラのリセット直後に複数の I2C 書き込みを TPS55288 に対して実行します：

- **基準電圧を設定:** TPS55288 レジスタ 0x00（REF の LSB）に 0xD2 を書き込みます。これに加え、デフォルトの MSB（0x00）と組み合わせることで、REF 値は 0x00D2 に設定されます。前述の通り、0x00D2 は約 282mV のリファレンスに相当し、デフォルトの帰還比と組み合わせることで約 5V の出力になります。これにより、コンバータは初期状態として 5V 出力に設定されます。

- **帰還構成を設定:** レジスタ 0x04（ $V_{OUT\_FS}$ ）に 0x03 を書き込みます。これは、コンバータが内部帰還ネットワークと 0.0564 の比率（デフォルトのリセット状態）を使用していることを明示的に確認するものです。ここで 0x03 を書き込むのは主に完全性のためであり、非デフォルトの設定がラッチされている場合や起動時の不確実性を防ぐために帰還モードを確認する役割があります。これにより、内部帰還が有効なままとなり、内部スケーリングによって最大 20V までの PD 電圧範囲を可能にする比率が選択されます。

- **コンバータ出力の有効化:** レジスタ 0x06（MODE）に 0xA0 を書き込みます。これにより、bit7（OE）が 1 に設定されて出力がオンになり、さらに bit5 も 1 に設定されてヒカッピモードがデフォルトで有効な状態が維持されます。値 0xA0（2 進数 1010\_0000）は、OE ビットを 1 に切り替えつつ、他のビットは希望する値のまま維持します。例えば、0x20 はリセット時の値で OE=0、HICCUP=1 などですが、0xA0 は OE を 1 に変更します。この書き込み後、TPS55288 は有効化され、約 5V の出力を制御します。

これら 3 つの書き込み (アドレス 0x00, 0x04, 0x06 への書き込み) は、PD コントローラの初期化中に順次実行されます。PoR 時にパワーコンバーターを設定することで、USB-C 接続が行われる前でも TPS55288 がデフォルトの 5V 待機出力状態で起動する (または有効化時に 5V を供給する準備ができた状態になります) ことを設計上保証しています。これは、USB-C 規格に準拠するために重要であり、接続開始時に VBUS に 5V が供給されていることが求められているためです。今回のケースでは、実際にコネクタへの VBUS の有効化は PD コントローラのパワー パス スイッチによって制御されますが、TPS55288 の出力は内部で適切なレベルに設定され、オンになっています。

(選択された正確な数値、0xD2, 0x03, 0xA0 は、TPS55288 のデータシートから導き出された望ましい起動時設定に対応しています。0xD2 (10 進数 210) の REF LSB は約 5V を示すコードであり、0x03 の VOUT\_FS は 0.0564 の比率の内部帰還を選択し、0xA0 は出力を有効にします。詳細なビット定義については、データシートの TPS55288 レジスタマップを参照してください。)

### 動的 PDO 電圧調整 (ソース PDO ネゴシエーション)

コンバータが初期化されたとき、次に PD コントローラは、新しい PD 契約がネゴシエーションされるたびに TPS55288 の出力を調整する必要があります。TPS65992S は、接続されたデバイスによってソース PDO が選択されるたび (例えば、PD のソース電圧が変わるたび) に、REF レジスタへの I2C 書き込みを実行するように設定されています。今回の例では、システムが固定 PDO として 5V、9V、15V、20V の 4 種類を提供していると仮定します。TPS65992S のファームウェア内で、4 つのイベントトリガを定義しています。(例えば、SRC\_PDO1\_NEGOTIATED、SRC\_PDO2\_NEGOTIATED などがあり) それぞれに対応した値を TPS55288 の REF レジスタに書き込む動作が割り当てられています。

- **5V 契約 (PDO1):** TPS55288 レジスタ 0x00 に 0xD2 0x00 を書き込みます。これは 2 バイトの書き込みです (0x00 は REF LSB の開始レジスタです)。データ バイトの 0xD2 0x00 は、REF を 0x00D2 (LSB = D2h, MSB = 00h) に設定します。これは先述の通り、約 5.0V の出力に対応しています。(PD ツールでは、このエントリのデータ長は 3 バイトです: 1 バイトがレジスタ アドレス、2 バイトがデータとなっています。)

- **9V 契約 (PDO2):** レジスタ 0x00 に 0x9A 0x01 を書き込みます (2 バイト データ、REF = 0x019A に設定)。TPS55288 の内部 DAC コードで、0x019A はおよそ 9V に相当します。具体的には、0x019A は 10 進数で 410 に相当し、 $410 \times 1.129\text{mV} \approx 463\text{mV}$  のリファレンス電圧となります。帰還比が 0.0564 であり、 $V_{\text{OUT}} \approx 463\text{mV} / 0.0564 \approx 8.21\text{V}$  となります。ただし、コンバータの出力は負荷で 9V を満たすために、わずかにオーバーシュートします (正確な値は較正と実験に基づいて選択されます)。一般的な設定によると、本設計では 9V 用のコードとして 0x019A が使用されています。

- **15V 契約 (PDO3):** レジスタ 0x00 に 0xC5 0x02 を書き込みます (REF = 0x02C5)。0x02C5 は 10 進数で 709 に相当し、 $709 \times 1.129\text{mV} \approx 800\text{mV}$  のリファレンス電圧となります。0.0564 で割ると、約 14.2V となります。(負荷やコンバータの許容範囲を考慮した上で) このコードは、想定される条件下で約 15V を出力するように選択されています。

- **20V 契約 (PDO4):** レジスタ 0x00 に 0xBF 0x03 を書き込みます (REF = 0x03BF)。0x03BF は 10 進数で 959 に相当し、 $959 \times 1.129\text{mV} \approx 1.083\text{V}$  のリファレンス電圧となります。0.0564 の比率を使用すると、約 19.2V となります。これは無負荷または定格負荷時に約 20V を出力することを意図しており、TPS55288 の帰還とリファレンスは調整されているため、0x03C0 では 20V をわずかにオーバーシュートする可能性があるため、典型的に 20V 付近かそれ以下に収まるように 0x03BF が使用されています。基本的に、0x03BF は今回のセットアップにおける 20V<sub>in</sub> 電圧の較正コードです。

これらの書き込みは、それぞれ TPS55288 REF レジスタをターゲットにして、V<sub>OUT</sub> を即座に動的に変更します。PD 契約が確立されると、PD コントローラは直ちに適切なコマンドを発行します。このようにして、シンクが高い電圧 (例えば 15V) を要求すると、TPS65992S は新しい REF 値を書き込み、TPS55288 は出力を要求されたレベルまで調整します。必要に応じて、TPS55288 の VOUT\_SR レジスタ (0x03) で出力のスルーレートを制御できますが、当設計ではコンバータのデフォルトのスルーレートに依存しており、これは通常 PD のタイミング要件を満たすように設定されています。

### デタッチおよびリセット時の動作

USB-C ケーブルが抜かれたり、シンク デバイスが切断された場合には、電源供給を安全な状態に戻します。レジスタ 0x00 (LSB) および 0x01 (MSB) に 0xD2 0x00 を書き込みます。この 2 バイトの書き込みにより、リファレンス電圧は望ましい 5V のデフォルト設定に完全にリセットされ、高電圧の残留状態が発生する可能性がなくなります。いずれにせよ、接続解除が発生した際には TPS55288 の出力が安全なレベル (約 5V 以下) まで低下することになります。これにより、ケーブルが取り外された後も VBUS に高電圧が残ることを防止します。

これらの I<sup>2</sup>C コマンド イベントを TPS55288 に設定することで、電源の調整はすべて TPS65992S のファームウェアによって自動化され、外部 MCU の介入を必要としません。PD コントローラは USB-C の状態や PD メッセージを監視し、適切な事前プログラムされた I<sup>2</sup>C 書き込みをトリガします。これにより、PD 契約が変化してもコンバータは要求された電圧をスムーズに供給し、契約がアクティブでない場合(切断や待機時)には既知のデフォルト状態にあることが維持されます。

| Record index 1 ( 0x1 )  |                                  |

|-------------------------|----------------------------------|

| Field                   | Value                            |

| Trigger Event           | I2C_MASTER_EVENT__POWER_ON_RESET |

| Data Length             | 3                                |

| Target Address Index    | 0                                |

| Orientation Independent | <input type="checkbox"/>         |

| Data                    | 0xd200                           |

図 3-1. レジスタ 0x00 でのパワーオン リセット イベント

| Record index 2 ( 0x2 )  |                                  |

|-------------------------|----------------------------------|

| Field                   | Value                            |

| Trigger Event           | I2C_MASTER_EVENT__POWER_ON_RESET |

| Data Length             | 2                                |

| Target Address Index    | 0                                |

| Orientation Independent | <input type="checkbox"/>         |

| Data                    | 0x304                            |

図 3-2. レジスタ 0x04 でのパワーオン リセット イベント

| Record index 3 ( 0x3 )  |                                  |

|-------------------------|----------------------------------|

| Field                   | Value                            |

| Trigger Event           | I2C_MASTER_EVENT__POWER_ON_RESET |

| Data Length             | 2                                |

| Target Address Index    | 0                                |

| Orientation Independent | <input type="checkbox"/>         |

| Data                    | 0xa006                           |

図 3-3. レジスタ 0x06 でのパワーオン リセット イベント。

| Record index 4 ( 0x4 )  |                                       |

|-------------------------|---------------------------------------|

| Field                   | Value                                 |

| Trigger Event           | I2C_MASTER_EVENT__SRC_PDO1_NEGOTIATED |

| Data Length             | 3                                     |

| Target Address Index    | 0                                     |

| Orientation Independent | <input type="checkbox"/>              |

| Data                    | 0xd200                                |

図 3-4. レジスタ 0x00 での SRC PDO1 ネゴシエーション イベント

| Record index 5 ( 0x5 )  |                                       |

|-------------------------|---------------------------------------|

| Field                   | Value                                 |

| Trigger Event           | I2C_MASTER_EVENT__SRC_PDO2_NEGOTIATED |

| Data Length             | 3                                     |

| Target Address Index    | 0                                     |

| Orientation Independent | <input type="checkbox"/>              |

| Data                    | 0x19a00                               |

図 3-5. レジスタ 0x00 での SRC PDO2 ネゴシエーション イベント

| Record index 6 ( 0x6 )  |                                       |

|-------------------------|---------------------------------------|

| Field                   | Value                                 |

| Trigger Event           | I2C_MASTER_EVENT__SRC_PDO3_NEGOTIATED |

| Data Length             | 3                                     |

| Target Address Index    | 0                                     |

| Orientation Independent | <input type="checkbox"/>              |

| Data                    | 0x2c500                               |

図 3-6. レジスタ 0x00 での SRC PDO3 ネゴシエーション イベント

| Record index 7 ( 0x7 )  |                                       |

|-------------------------|---------------------------------------|

| Field                   | Value                                 |

| Trigger Event           | I2C_MASTER_EVENT__SRC_PDO4_NEGOTIATED |

| Data Length             | 3                                     |

| Target Address Index    | 0                                     |

| Orientation Independent | <input type="checkbox"/>              |

| Data                    | 0x3bf00                               |

図 3-7. レジスタ 0x00 での SRC PDO4 ネゴシエーション イベント

| Record index 8 ( 0x8 )  |                          |

|-------------------------|--------------------------|

| Field                   | Value                    |

| Trigger Event           | I2C_MASTER_EVENT__DETACH |

| Data Length             | 3                        |

| Target Address Index    | 0                        |

| Orientation Independent | <input type="checkbox"/> |

| Data                    | 0xd200                   |

図 3-8. レジスタ 0x00 におけるデタッチ イベント

## 4 I2C3 経由での TUSB1044 リドライバの構成

TUSB1044 は、Type-C ケーブルの向きおよびオルタネートモードの状態に応じて、USB3 SuperSpeed レーンおよび(オプションで)DisplayPort レーンといった高速信号の経路切り替えと信号補正を行います。通常、TUSB1044 はピン制御(GPIO)モードで動作可能ですが、このデザインでは PD コントローラを介して細かく動的に制御できるよう、I2C 制御モードを使用します。TUSB1044 は、TPS65992S の I2C コントローラを介して、ポートの電源投入時、ケーブル接続時(向きの判別を含む)、および DisplayPort モードへの移行時など、さまざまなイベントに応じて設定されます。TUSB1044 に関するすべての I2C コマンドは、アドレスインデックス 1 (ペリフェラルアドレス 0x12) に割り当てられており、PD コントローラのテーブル内ではイベントインデックス 9~28 を占めています。

この構成で使用される TUSB1044 の主なレジスタは次のとおりです:

- **General\_1 (レジスタ 0x0A)**: このレジスタは、TUSB1044 の動作モードおよび特定の無効動作を制御します。0x0A の重要なフィールド:

- ビット [1:0] **CTLSEL** - データモードを選択: 0 = すべてのチャネルが無効、1 = USB3 のみ有効、2 = DisplayPort (DP のみ) 4 レーン有効、3 = USB3 + DP 2 レーン有効。

- ビット [2] **FLIP\_SEL** - 高速マルチプレクサの向き(反転)を設定: 0 = 通常の向き、1 = 反転した向き。

- ビット [4] **EQ\_OVERRIDE** - 1 に設定すると、(ピンストラップによる EQ レベルを無効にして)、I2C レジスタからの EQ 設定が有効になります。この機能を有効にすると、I2C 経由で EQ をプログラムできます。

- ビット [5] **SWAP\_SEL** - 設定されている場合、チャネルの方向 (DFP と UFP) を全体的に入れ替えます。ソースデバイスの場合、通常はこの設定を 0 (スワップなし) のままにしておきますが、設計上方向を反転する必要がある場合(たとえばシンク用途など)には設定を有効にします。当社の構成では、DP ソースとして SWAP\_SEL をデフォルト値の 0 のままにしています。

- ビット [3] **HPD\_IN\_OVERRIDE** - 当社のフローでは使用していません (HPD 入力の無効を制御するもので、シンク用途で使用されます)。

- **General\_3 (レジスタ 0x0C)**: リドライバの VOD (差動出力電圧) および DC ゲインの設定を制御するほか、I2C モードにおけるポートのデータの役割 (Dir) を設定するフィールドも含まれます。関係するフィールド:

- ビット [6] **VOD\_DCGAIN\_OVERRIDE** - 1 に設定すると、VOD/DC ゲインのピン設定を無効にし、レジスタ設定が使用されます。当社では、振幅を I2C 経由で設定するために、これを 1 に設定しています。

- ビット [5:2] **VOD\_DCGAIN\_SEL** - すべてのチャネルに対する VOD の直線性および DC ゲイン設定を選択する 4 ビットの複合フィールドです。これは本質的に、EQ ゲインを設定する 2 ビットのピン設定 (CFG1 および CFG0) をレジスタ上で符号化したもので、当社の設計では、想定されるケーブル長に対して適切な信号振幅が得られる設定を選択しています。(提供されている設定では、書き込まれている値は特定のピン設定の組み合わせに対応しています—下記参照)。

- ビット [1:0] **DIR\_SEL** - デバイスデータの役割を設定します: 0 = USB および DP Alt モードソース、1 = USB および DP Alt モードシンク、2 = USB + カスタム Alt モードソース、3 = USB + カスタム Alt モードシンク。当社のデザインはソース側(たとえば、DisplayPort を出力するノート PC やドック)であるため、DIR\_SEL は 0 に設定しています。

- **EQ 制御レジスタ (0x10, 0x11, 0x20, 0x21)**: これらのレジスタは、各高速チャネルのイコライゼーション設定を構成します。TUSB1044 には 4 組の高速差動ペアがあり、それぞれを TX および RX の方向を持つ、アップストリーム向きチャネル 2 本とダウンストリーム向きチャネル 2 本として考えることができます。I2C モードの場合:

- **0x10:UFP1\_EQ** - ビット [7:4] はアップストリームポートチャネル 1 (UTx1) TX 用 EQ を、ビット [3:0] はアップストリームチャネル 1 (URx1) の RX 用 EQ を設定します。

- **0x11:UFP2\_EQ** - アップストリームチャネル 2 (UTx2 と URx2) についても同様です。

- **0x20:DFP1\_EQ** - ビット [7:4] はダウンストリームポートチャネル 1 (DTx1: コネクタ側への送信) を、ビット [3:0] はダウンストリーム RX1 (DRx1) を設定します。

- **0x21:DFP2\_EQ** - ダウンストリームチャネル 2 (DTx2/DRx2) の EQ 設定。

これらのレジスタに値を書き込むことで、各レーンの信号品質を微調整できます。当社のユースケースでは、USB3 および DP 信号向けに推奨されている特定の EQ 値をプログラムしています(構成内に見られる 0x66 および 0x33 の値は、それぞれ特定の EQ ゲイン設定に対応しています)。

さまざまなイベントにおいて TPS65992S が TUSB1044 を制御するために、どのように設定されているかを以下に示します：

#### パワーオンリセット(初期構成)

PD コントローラのパワーオンリセットでは、TUSB1044 は、安全のため無効状態で起動し、I2C 制御が有効になっていることが望ましいと考えています。ファームウェアのトリガ:

- **0x10** を **TUSB1044 レジスタ 0x0A** に書き込みます。データ 0x10 (16 進数) は、2 進数では 0001\_0000 に相当します。ビット定義を確認すると、この値は bit4 (EQ\_OVERRIDE) を 1 に設定し、それ以外の下位ビット 2:0 はすべて 0 (CTLSEL = 000b、つまりすべて高速チャネルが無効) に設定されています。言い換えれば、I2C による EQ 無効化は有効にしつつ、リドライバの TX/RX 経路は無効のままにしています。これはリセット時のデフォルトとして適切です。リドライバは、追加の設定が行われるまでは高速信号を転送せず、EQ 設定についてはピンではなくレジスタに依存するようになります。本質的に、0x10 は TUSB1044 をソフトウェア制御下のアイドル状態にします。(リセット時の TUSB1044 のデフォルトでもチャネルは無効になっていますが、0x10 を明示的に書き込むことで、正しい動作モードと無効ビットが設定されていることを確実に確認できます。)

このコマンドによって、TUSB1044 は信号を出力しない状態を維持し、今後の構成 (USB または Alt モード) に備えて待機する状態になります。これは、ケーブルの接続が検出されるまで、リドライバをリセットまたはスタンバイ状態に保つとの同等です。また、必要に応じて他のイベント (たとえばデタッチ時) でも同じ値を使用し、このベースライン状態に戻すようにしています。

| Record index 9 ( 0x9 )  |                                  |

|-------------------------|----------------------------------|

| Field                   | Value                            |

| Trigger Event           | I2C_MASTER_EVENT__POWER_ON_RESET |

| Data Length             | 2                                |

| Target Address Index    | 1                                |

| Orientation Independent | <input type="checkbox"/>         |

| Data                    | 0x100a                           |

図 4-1. レジスタ 0x0A でのパワーオンリセットイベント

#### デタッチイベント

デタッチ(ケーブル抜去)イベント時には、PD コントローラが TUSB1044 のレジスタ 0x0A に 0x10 を再送信します。これにより、電源オン時と同じ値が書き込まれます: EQ\_OVERRIDE = 1, CTLSEL = 0 (チャネルがオフ)。デタッチ時にこの処理を行うことで、リドライバのレーン切り替えが実質的に無効化され、デフォルト状態に戻ります。それまで有効だったオルタネートモードの構成はすべてクリアされ、デバイスは次回の新たな接続シーケンスに備えた状態になります。本質的には、初回の電源投入時とデタッチ時の両方で、TUSB1044 に対してスイッチング (USB3 や DP のレーン動作なし) を無効にし、今後の設定は I2C によって行うよう指示します。これにより、デバイスが接続されていない状態で、不要な信号の通過や以前の設定が保持されたまま動作することを防げます。

(注: 設計によっては、デタッチ時に TUSB1044 のハードウェアリセットピンをトグルさせる場合もあります。このように I2C コマンドを使用することで、追加の GPIO トグル操作を行わなくとも、制御レジスタを既知の安全な状態に書き込むことで同様の効果が得られます。)

| Record index 10 ( 0xa ) |                          |

|-------------------------|--------------------------|

| Field                   | Value                    |

| Trigger Event           | I2C_MASTER_EVENT_DETACH  |

| Data Length             | 2                        |

| Target Address Index    | 1                        |

| Orientation Independent | <input type="checkbox"/> |

| Data                    | 0x100a                   |

図 4-2. レジスタ 0x0A におけるデタッチ イベント

#### アタッチ イベント - ケーブルの向きの処理

USB-C ケーブルが接続されると、TPS65992S は CC ピンを介してケーブルの向きを検出し、同時に USB-PD のネゴシエーションも開始します。オルタネートモードに入る前に、最初に行うべき重要なタスクは、TUSB1044 内部の *SuperSpeed* マルチプレクサを正しい向きに設定し、USB3 信号（および今後の DP 信号）が正しくルーティングされるようになります。TPS65992S のファームウェアは、2 種類のケーブルの向きを区別します。これらは一般に *ATTACH\_UU* と *ATTACH\_UD* とラベル付けされており、PD コントローラのイベント定義に由来します。（これらのラベルは本質的に、アップストリーム ポートが上向きかアップストリーム ポートが下向きか、つまりケーブルが反転していない状態かケーブルが反転している状態かを示しています）。簡単に言えば次のようになります：

- *ATTACH\_UU* は、コネクタの A 面が上向きになっている向きに対応しており、このときレーンのマッピングは特定の構成になります。

- *ATTACH\_UD* は、コネクタが 180° 回転した状態（反対のレーン マッピング）に対応します。

それぞれの向きに対して、通常の USB3 動作のための設定（および将来的な DP モードへの備え）として、TUSB1044 に対する一連の I2C 書き込みシーケンスを定義しています：

*Attach\_UU* シーケンス：（ケーブルがデフォルトの向きの場合）PD コントローラは、以下の書き込みを連続して実行します：

1. レジスタ 0x0A に 0x11 を書き込み：これは General\_1 レジスタに 0x11（16 進数）（2 進数では 0001\_0001）を設定します。0x10 と比べると、bit0 が 1 (CTLSEL = 001b) になり、bit4 は 1、bit2 は 0 のままで。CTLSEL = 1 は、USB3.1 専用モードがイネーブルであることを意味します。したがって、0x11 は所定の向きでリドライバを介して USB3 パスをオンにします。ここでは Bit2 (FLIP\_SEL) が 0 に設定されており、これは通常の向き（UU ケース）を想定していることを意味します。そのため、0x11 は TUSB1044 を USB3 モードに構成し、反転しません。

解説：TUSB1044 は、ホスト側の SuperSpeed 送受信レーンを、非反転のプラグ挿入に対応するコネクタ側の適切な TX/RX ピンに接続します。この時点では、DP レーン（存在する場合）は無効のままで（CTLSEL = 1 により USB3 のみが選択されているため）。EQ\_OVERRIDE は 1 のままで、プログラムされた EQ 設定を使用します（以降のステップで設定）。

1. レジスタ 0x0C に 0x58 を書き込み：General\_3 に 0x58 を書き込みます。バイナリで 0x58 = 0101\_1000 とします。内訳は以下のとおりです：

- Bit6 (0x40) が設定されており（0x58 に 0x40 が含まれている）、その結果 VOD\_DCGAIN\_OVERRIDE = 1 となり、VOD/DC 設定にはレジスタの値が使用されます。

- Bits5:2 = 0b0110。データシートによると、このフィールド [5:2] は、CFG1 ピンおよび CFG0 ピンの設定と同等の内容を符号化しています。0b0110 は、CFG1 = 01 (R)、CFG0 = 10 (F) に対応します。つまり、特定の VOD/DC ゲイン レベルを選択しました（これは中程度の EQ 設定に対応するもので、R と F はおそらく抵抗とフロートの組み合わせを示しています）。これはおそらく、TUSB1044 のデータシートの推奨値や実験室での調整によって決定されたものです。

- Bits1:0 = 0b00 は DIR\_SEL = 0 を設定し、これはソース モード（USB + DP ソース）を示します。これは当社のシステムの役割に一致しています（TUSB1044 はアップストリーム側をホスト側、ダウンストリーム側をコネクタ側として扱います）。

つまり、**0x58** は基本的に I2C 経由で提供される VOD/DC ゲインを使用し、特定のゲイン設定 (R-F 構成) を適用し、デバイスがソースであることを確認するという意味です。この設定は、リドライバーの出力レベルが今後の信号に対して適切に構成されるよう、デバイス接続時に書き込まれます。

- レジスタ **0x10** に **0x66 0x66** を書き込みます:これは、UFP1\_EQ レジスタ (アドレス **0x10**) への 2 バイト書き込みです。データ **0x66 0x66** は、UFP1\_EQ の高位ニブルと低位ニブルの両方を **0x6** に設定します。具体的には、**0x10** は 1 ペア分の UFP の TX/RX EQ を制御します:

- 単一バイトの **0x66** は、UFP チャネル 1 の TX EQ を **0x6**、RX EQ を **0x6** に設定することを意味します。2 バイトの **0x66** を送信することで、おそらく次のレジスタ (**0x11**) も一括で設定する意図があり、**0x10** から始まる連続したマルチバイト書き込み (**0x10** に対するデータと **0x11** に対するデータの両方) を行っていることを意味します。ただし、設定リストでは「**0x66 0x66** を **0x10** に書き込む」となっており、これは PD ツールがマルチバイト書き込みをどのように扱うかによって、実際には **0x10** に **0x66**、続く **0x11** にも **0x66** を一度に書き込むことを意味しています。

つまり、アップストリーム向けの EQ を、TX と RX ともに両チャネルで中程度の値 (**0x6**) に設定しているということです。これは、USB3 や DP 動作時にリドライバのホストコントローラ側で推奨される EQ 設定である可能性があります。これにより、デフォルトのピンベースの EQ 設定を無効にし、基板パターンの損失などを補正して信号品質を確保します。

- レジスタ **0x20** に **0x33 0x33** を書き込みます:次に、DFP1\_EQ レジスタ (アドレス **0x20**) への 2 バイト書き込みを行います。**0x33 0x33** は、同様にダウンストリーム側 (コネクタ側) チャネル 1 (および 2 バイトの場合はチャネル 2 も) の TX および RX の EQ 設定をそれぞれ **0x3** に設定します。**0x3** という値は **0x6** よりもやや低いゲインであり、これはリドライバからコネクタまでの接続が短いことや、ケーブルに対する標準的な要件を反映している可能性があります。基本的に、ダウンストリーム側 (USB-C コネクタ) EQ を両チャネルに設定しています。

上記の EQ 設定の組み合わせ (UFP 側が **0x6**、DFP 側が **0x3**) は、おそらく TI のガイドラインや実験室での調整に基づいており、対象の PCB およびコネクタにおいて USB3 の信号品質および適合性試験を通過するためのものです。

これら 4 つの書き込み (**0x0A**, **0x0C**, **0x10**, **0x20**) は、Attach\_UU 構成を完了させます。この時点で、反転していないケーブルを挿入する場合は、TUSB1044 はアクティブな USB3 モードに設定され、正しい高速レーンが接続され、EQ やゲインが調整されています。

**Attach\_UD** シーケンス:(ケーブルの反転方向) ケーブルが逆向きに挿入された場合、PD コントローラは代わりに ATTACH\_UD イベントをトリガします。シーケンスはほぼ同様ですが、向きが重要となる部分に違いがあります。

- レジスタ **0x0A** に **0x15** を書き込み:**0x15** (16 進数) = **0001\_0101** (2 進数)。**0x11** (**0001\_0001**)との比較:

- Bit2 (FLIP\_SEL) は現在 1 です (**0x15** は bit2 がセットされています。**0x15** = **21** (10 進数) であり、これは **0x04** を含んでいます)。

- Bits1:0 は引き続き **01** (CTLSEL = 1、USB3 専用モード) となっています。

- Bit4 は引き続き 1 のままで (**EQ\_OVERRIDE** が有効です)。

つまり、**0x15** は USB3 専用モードを有効にしつつ、ケーブルの向きが反転している状態を設定しています。これは、TUSB1044 に対してレーンの経路を適切に切り替えるよう指示しており (デバイス内部のマルチプレクサに対して A ポートと B ポートのレーンが入れ替わることを意味します)。基本的に、このデバイスはケーブルが反転していることを考慮し、UU ケースとは逆の高速ピンセットに USB3 信号を接続します。

- 0x58~0x0C:General\_3** レジスタは、以前と同じ **0x58** の値を取得します。これは実際には向きに依存せず、VOD/DC ゲイン設定と DIR (ソース) はケーブルの反転に関係なく同じまま維持されます。UU と UD の両方に同じ **0x58** 構成を使用します。(これは理にかなっています。ケーブルの向きが変わっても、当社がソースであり特定の EQ 設定を使うという事実は変わらず、変わるのは信号を伝える物理的なチャネルだけだからです。)

- 0x66 0x66~0x10:**同じ EQ 設定を再度、UFP EQ レジスタに書き込みます。ここで考慮すべきは、ケーブルが反転している場合に、TUSB1044 の各チャネルが物理的にどの接続に対応しているかという点です。FLIP\_SEL で示されるように、デバイスはレーンの Channel1 と Channel2 の使用を入れ替えます。しかし、両方の UFP チャネル (**0x10** および **0x11**) に同じ値 (**0x66**) を 2 バイトシーケンスで書き込むことで、どちらのチャネルが実際の USB の TX/RX になる場合でも、EQ が **0x6** に設定されていることを確認しています。つまり、当社の設定では両方のアップストリーム チャネルが同じ EQ 値を持っているため、ケーブルの反転によって異なる値を設定する必要はなく、対称性が保たれています。

4. **0x33 0x33~0x20:** 同様に、両方のダウンストリーム チャネルの EQ を 0x3 に設定します (0x20 と 0x21 はどちらもマスクレジスタ書き込みにより 0x33 を取得します)。この対称性により、UD ケースでも、どちらのコネクタ向きでも同じ EQ 強度が使用されます。

この結果、UD シーケンスは 0x0A レジスタ値 (0x15 対 0x11) だけが異なることになります。その他のレジスタ書き込み (0x0C、0x10、0x20 およびそれに対応するデータ) は、UU と UD のアタッチ時で同一です。これは理にかなっています。唯一変わるのはフリップ ビットであり、これがリドライバに対してレーンの経路をどのように切り替えるかを指示しているからです。両者を比較すると、0x0A の値が 0x11 と 0x15 で異なっており、その差は 0x04 です。これはまさに FLIP\_SEL ビットに対応しています。それ以外のすべて (EQ ゲインなど) は一定のままであり、設計上、ケーブルの向きが反転している場合でも反転していない場合でも、異なるゲイン設定は不要であり、電気的には同じ扱いをしていることを示しています。

アタッチイベントシーケンス (UU または UD) の後、TUSB1044 は通常の USB3 動作用に設定されます。オルタネート モードが開始されない場合、システムはリドライバを介して USB3 トрафィックが流れたまま動作を継続します。PD コントローラのアタッチ時の役割は基本的に完了しており、これにより高速経路が正しく向き付けられ、最適化されている状態が維持されます。

| Record index 11 ( 0xb ) |                             |

|-------------------------|-----------------------------|

| Field                   | Value                       |

| Trigger Event           | I2C_MASTER_EVENT__ATTACH_UU |

| Data Length             | 2                           |

| Target Address Index    | 1                           |

| Orientation Independent | <input type="checkbox"/>    |

| Data                    | 0x110a                      |

図 4-3. レジスタ 0x0A でのアタッチ イベント

| Record index 12 ( 0xc ) |                             |

|-------------------------|-----------------------------|

| Field                   | Value                       |

| Trigger Event           | I2C_MASTER_EVENT__ATTACH_UU |

| Data Length             | 2                           |

| Target Address Index    | 1                           |

| Orientation Independent | <input type="checkbox"/>    |

| Data                    | 0x580c                      |

図 4-4. レジスタ 0x0C でのアタッチ イベント

| Record index 13 ( 0xd ) |                             |

|-------------------------|-----------------------------|

| Field                   | Value                       |

| Trigger Event           | I2C_MASTER_EVENT__ATTACH_UU |

| Data Length             | 3                           |

| Target Address Index    | 1                           |

| Orientation Independent | <input type="checkbox"/>    |

| Data                    | 0x666610                    |

図 4-5. レジスタ 0x10 でのアタッチ イベント

| Record index 14 ( 0xe ) |                             |

|-------------------------|-----------------------------|

| Field                   | Value                       |

| Trigger Event           | I2C_MASTER_EVENT__ATTACH_UU |

| Data Length             | 3                           |

| Target Address Index    | 1                           |

| Orientation Independent | <input type="checkbox"/>    |

| Data                    | 0x333320                    |

図 4-6. レジスタ 0x20 でのアタッチ イベント

| Record index 15 ( 0xf ) |                             |

|-------------------------|-----------------------------|

| Field                   | Value                       |

| Trigger Event           | I2C_MASTER_EVENT__ATTACH_UD |

| Data Length             | 2                           |

| Target Address Index    | 1                           |

| Orientation Independent | <input type="checkbox"/>    |

| Data                    | 0x150a                      |

図 4-7. レジスタ 0x0A でのアタッチ イベント

| Record index 16 ( 0x10 ) |                             |

|--------------------------|-----------------------------|

| Field                    | Value                       |

| Trigger Event            | I2C_MASTER_EVENT__ATTACH_UD |

| Data Length              | 2                           |

| Target Address Index     | 1                           |

| Orientation Independent  | <input type="checkbox"/>    |

| Data                     | 0x580c                      |

図 4-8. レジスタ 0x0C でのアタッチ イベント

| Record index 17 ( 0x11 ) |                             |

|--------------------------|-----------------------------|

| Field                    | Value                       |

| Trigger Event            | I2C_MASTER_EVENT__ATTACH_UD |

| Data Length              | 3                           |

| Target Address Index     | 1                           |

| Orientation Independent  | <input type="checkbox"/>    |

| Data                     | 0x666610                    |

図 4-9. レジスタ 0x10 でのアタッチ イベント

| Record index 18 ( 0x12 ) |                            |

|--------------------------|----------------------------|

| Field                    | Value                      |

| Trigger Event            | I2C_MASTER_EVENT_ATTACH_UD |

| Data Length              | 3                          |

| Target Address Index     | 1                          |

| Orientation Independent  | <input type="checkbox"/>   |

| Data                     | 0x333320                   |

図 4-10. レジスタ 0x20 でのアタッチ イベント

### DisplayPort オルタネート モード設定

接続されたパートナー (例えばモニタやドッキング ステーション) が DisplayPort オルタネート モードに対応しており、PD ネゴシエーションがそのモードに入ると、DisplayPort 動作用に TUSB1044 を再設定するための追加の I2C イベントがトリガれます。当社の PD コントローラの設定では、特定の *DisplayPort* 構成ステップに対応するイベントを定義しており、便宜上それぞれ *DP\_CONFIG\_ACE* および *DP\_CONFIG\_BDF* と名付けています。これらには向きの違い (UU または UD) に対応したバリエントも用意されています。これらのラベルは、標準的な USB-C の DisplayPort ピンの割り当て (通常はピン C と E、あるいは B, D, F) を指しています。つまり、PD コントローラは、DisplayPort で使用される 4 つの高速レーンの使い方に応じて異なる構成シーケンスを使用します。1 つの構成は 4 レーンの DisplayPort (USB3 データなし) 用であり、もう 1 つは 2 レーンの DisplayPort と USB3 動作の組み合わせで、これらは DP Alt モードで一般的な動作モードです。正確な名称 (ACE、BDF) は、ソースが特定のピン割り当てをサポートしていることを示すために使われています。例えば、4 レーン用のピン割り当て C や E、あるいは 2 レーン + USB 用のピン割り当て D や F などがそれに該当します。当社の構成では、各シナリオにおいて TUSB1044 がレーンの経路設定および EQ を適切に構成されるように維持しています。

シーケンスを要約します。

- *DP\_CONFIG\_ACE\_UU*: このイベントは、非反転状態で (A, C, E) マッピングを使用する DisplayPort オルタネート モード構成への移行に対応しています。このモードでは、通常、4 本のレーンすべてが DP に割り当てられます (USB3 の通信は行われません)。PD コントローラの書き込み:

- *0x1A ~ 0xA0 : 0x1A* (16 進数) = 0001\_1010 (2 進数)。Bits [1:0] は 10 (CTLSEL = 2) であり、TUSB1044 の仕様によると 4 レーンの DisplayPort が有効であることを示しています。Bit2 は 0 (UU 向き)、Bit4 は 1 (EQ 無効化が有効) となっています。つまり、0x1A は通常動作時にリドライバを DP モード (すべてのレーンが DP を伝送) に切り替えます。

- *0x55 0x55 ~ 0x10 : UFP1\_EQ* (および UFP2\_EQ) への 2 バイト書き込みです。データ 55 55 は、アップストリーム の EQ レジスタをそれぞれ 0x55 に設定します。0x55 の内訳は、各チャネル TX が 0x5、RX も 0x5 に設定されていることを意味します。つまり、DP モードでは、アップストリーム側でやや異なる EQ 設定を使用しています: 0x5 (USB 時に使用していた 0x6 よりもやや低めの設定です)。これは DP 信号品質を最適化するために使用できます (DP 信号のイコライゼーションのニーズが異なる場合や、DP ソースでいくつかの EQ を実行できる場合があるためです)。

このイベントでは 0x20 への書き込みは明示的に確認されていません (つまり、ダウンストリームの EQ は既存の設定のままか、4 レーン DP UU の場合は変更が不要であることを示唆しています)。推測されるのは、ダウンストリーム側 (コネクタ向き) の EQ は、前回のアタッチ時に設定された値 (0x33) のままで維持されているということです。これは妥当な推測です。なぜなら、USB でも DP でも、コネクタまでの物理的なチャネル特性は変わらないためです。ただし、DP の周波数特性に合わせて調整することも可能です。当社の設定表では、ACE\_UU のための新たな 0x20 への書き込みは記載されていないため、DFP の EQ はこれまで通り 0x33 0x33 のまま維持しています。

- *DP\_CONFIG\_ACE\_UD*: こちらは上記の反転向きの場合の対応です。

- *0x1E ~ 0xA0 : 0x1E* (16 進数) = 0001\_1110。ビット [1:0] は 10 (CTLSEL = 2, 4 レーン DP のまま)、Bit2 は 1 (反転向き)、Bit4 は 1 (EQ 無効化が有効) となっています。0x1E は DP 4 レーン モードで、反転方向を意味します。

- **0x55 0x55~0x10:**同じ 55 55 のデータが UFP EQ レジスタに書き込まれます。ACE\_UU と ACE\_UD の唯一の違いは 0x0A の値 (0x1A 対 0x1E) であることが再確認できます。この 0x04 の差は、アタッチ イベントと同様に反転ビットを示しています。レジスタ 0x10 のデータは 0x55 0x55 のままで変わっておらず、フリップによる変化はありません。これは両チャネルに同一の値を設定しているためです。

これまでと同様に、ACE\_UD についても新たな DFP EQ 書き込みは示されておらず、このシーケンスの DP モード移行によって DFP 側の EQ は変更されていないことを示唆しています。

- **DP\_CONFIG\_BDF\_UU:**これは異なるピン割り当てのシナリオに対応しており、おそらく 2 レーンの DP (B および D) と USB3 (F) の組み合わせを示しています。この場合、PD コントローラは以下のように書き込みます:

- **0x1B~0x0A:0x1B (16 進数) = 0001\_1011.** Bits[1:0] は 11 (CTLSEL = 3) であり、これは「USB3 + 2 レーン の DP」モードを意味します。Bit2 は 0 (反転なし、UU)、Bit4 は 1 (EQ 無効化が有効) となっています。つまり、0x1B は TUSB1044 を通常向きで設定し、4 本のうち 2 本のレーンを DP 用に割り当てる、残りのレーンペアを USB3 用に保持することを意味します。これは例えば、2 本のレーンを DP (HBR レーン) 用に使用し、残りの 2 本のレーンを USB3 の TX/RX 用に割り当てるに対応しています。

- **0x66 0x55~0x10:**ここには UFP EQ レジスタに対するデータ 66 55 の 2 バイトシーケンスがあります。これは以前のケースとは異なります。次の意味があります。UFP1\_EQ は 0x66、UFP2\_EQ は 0x55 に設定されます (最初のバイト 0x66 がレジスタ 0x10 に、2 番目のバイト 0x55 がレジスタ 0x11 に書き込まれます)。実質的に、アップストリームの一方のチャネル EQ を 0x6 に、もう一方を 0x5 に設定していることになります。なぜでしょうか。BDF のシナリオでは、アップストリームの片方のチャネルが USB3 信号を伝送しており (以前に 0x6 に調整済み)、もう一方が DP 信号を伝送しているため、DP 用には 0x5 の設定で十分と判断したからです。そのため、チャネル 1 (USB3 用) は EQ を 6 に設定し、チャネル 2 (DP レーン用) は EQ を 5 に設定しています。0x66 0x55 の順序は、次のことを示しています: UFP1\_EQ は USB3 チャネル用に 0x66、UFP2\_EQ は DP チャネル用に 0x55 に設定されています。

- **0x33 0x33~0x20:0x20 (DFP1\_EQ) および 0x21 (DFP2\_EQ)** に対して、2 バイトのデータ 33 33 を書き込みます。これにより、伝送される信号に関係なく、両方のダウンストリームチャネルの EQ が 0x3 (これまでと同じ) に設定されます。興味深いことに、アタッチ時と同じ値にもかかわらず、表によると BDF\_UU の場合、0x20 への書き込みは更新されていません。おそらくこれは、DP レーンの出力 (物理的なラインが変わっている可能性がある) を既知の EQ 設定に維持するために行われていると考えられます。いずれにせよ、DFP1\_EQ および DFP2\_EQ は共に 0x33 であり、対称的で以前の値から変更されません。

- **DP\_CONFIG\_BDF\_UD:**2 レーン DP + USB シナリオの反転ケースは以下の通りです:

- **0x1F~0x0A:0x1F (16 進数) = 0001\_1111.** Bits[1:0] は 11 (USB3 + 2DP)、Bit2 は 1 (反転)、Bit4 は 1 (無効化が有効) となっています。つまり、0x1F は 0x1B に反転ビット (0x04) を加えたもので、「反転向きの USB3 + 2DP」を意味します。

- **0x55 0x66~0x10:**データの 55 66 がアドレス 0x10 から書き込まれます。これはおそらく、UFP1\_EQ を 0x55、UFP2\_EQ を 0x66 に設定することを意味しています。なぜ UU の場合と比べてバイトの順序が入れ替わっていますか? ケーブルが反転している場合、どちらのアップストリームチャネルが USB 信号を、どちらが DP 信号を伝送するかが入れ替わるためです。UU の場合は、チャネル 1 が USB、チャネル 2 が DP と想定していました (チャネル 1 に 66、チャネル 2 に 55 を設定しています)。UD 向きでは、物理的な経路の関係で割り当てる必要があります。チャネル 1 が DP 信号を、チャネル 2 が USB3 信号を伝送する場合があります (レーンの反転の仕方にあります)。PD 構成ではこれを想定して EQ 設定を入れ替えており、現在はチャネル 1 に 0x5、チャネル 2 に 0x6 が割り当てられています。これにより、どちらのチャネルが USB3 信号を扱っていても高い EQ (0x6) が割り当てられ、DP 信号を扱うチャネルは 0x5 に設定される状態が、ケーブルが反転していても維持されます。BDF\_UU と BDF\_UD の設定 (66 55 対 55 66) の明確な違いは、向きの反転によってレーンごとの設定を入れ替える必要があることを示しています。

- **0x33 0x33~0x20:**UU と同様に、DFP EQ レジスタに 0x33 0x33 を書き込みます。BDF\_UD の場合も同様に、両方のダウンストリームチャネルの EQ を 3 に維持する動作である可能性が高くなります。ケーブルの反転によつても、両方のコネクタレーン (DP を伝送する 2 本と、USB を伝送する他のレーン、場合によっては未使用のレーン) が同じ EQ 設定であるという事実は変わらないため、そのまま維持しています。

DP 構成を以下にまとめます。PD コントローラは、主に 2 つの DP Alt モード構成 (4 レーンと 2 レーン) に対応したイベントセットを持ち、それぞれの構成に対して両方のケーブルの向きを処理します。各ケースでは、レジスタ 0x0A に新しい

値を書き込んで TUSB1044 のモード (DP または DP + USB) および反転状態を切り替え、さらに EQ レジスタ 0x10/0x11 (場合によっては 0x20/0x21) を調整して、新しいモードでの信号品質を維持します。reg0x0A の値 (0x1A/1E, 0x1B/1F) や各種 EQ コードは、TUSB1044 の仕様や要件に基づいて選定されています。

- **0x0A 値:** 主に下位 3 ビットで異なります。CTLSEL は、DP 専用モードで 2、DP+USB モードで 3 に設定されます。FLIP は向きを示し、0 または 1 の値を取ります。Bit4 は常に 1 に設定されています (常に EQ 無効化モードを使用しています)。

- **EQ 値:** アップストリーム側では USB3 チャネルに 0x6、DP チャネルに 0x5 を使用し、ダウンストリーム側では全般的に 0x3 を使用しています。これらの特定のコードは、TI のリファレンス設計や実験室での調整に基づいており、USB3 Gen2 および DP HBR2/HBR3 の適合性を満たすために設定されています。重要なのは、具体的な数値そのものではなく、PD コントローラがシナリオに応じてこれらの設定を柔軟に変更できることです。例えば、特定の設計で長いケーブルを検出した場合には、ファームウェアが異なる EQ 値を使用する可能性があります (ただし、今回の例ではモードごとに固定されています)。

DisplayPort 構成イベントが実行されると、TUSB1044 は Alt モードの設定を完全に終えます。これにより、システムの GPU からリドライバを経由して USB-C コネクタへ DisplayPort 信号がレーンを通じて伝送され、(BDF の場合は) そのうちの 2 本のレーンが USB3 データの伝送を継続します。ここで PD コントローラの積極的な関与は終了し、システムは通常通り DisplayPort の AUX ハンドシェイクなどを行ってモニタを設定します。TUSB1044 はプロトコルに依存しないため、高速信号を単に透過します。当社は I2C を介してスイッチやゲインを制御しているだけです。

| Record index 19 ( 0x13 ) |                                    |

|--------------------------|------------------------------------|

| Field                    | Value                              |

| Trigger Event            | I2C_MASTER_EVENT__DP_CONFIG_ACE_UU |

| Data Length              | 2                                  |

| Target Address Index     | 1                                  |

| Orientation Independent  | <input type="checkbox"/>           |

| Data                     | 0x1a0a                             |

図 4-11. レジスタ 0x0A に対する DP 割り当て ACE 構成イベント

| Record index 20 ( 0x14 ) |                                    |

|--------------------------|------------------------------------|

| Field                    | Value                              |

| Trigger Event            | I2C_MASTER_EVENT__DP_CONFIG_ACE_UU |

| Data Length              | 3                                  |

| Target Address Index     | 1                                  |

| Orientation Independent  | <input type="checkbox"/>           |

| Data                     | 0x555510                           |

図 4-12. レジスタ 0x10 に対する DP 割り当て ACE 構成イベント

| Record index 21 ( 0x15 ) |                                    |

|--------------------------|------------------------------------|

| Field                    | Value                              |

| Trigger Event            | I2C_MASTER_EVENT__DP_CONFIG_ACE_UD |

| Data Length              | 2                                  |

| Target Address Index     | 1                                  |

| Orientation Independent  | <input type="checkbox"/>           |

| Data                     | 0x1e0a                             |

図 4-13. レジスタ 0x0A に対する DP 割り当て ACE 構成イベント

| Record index 22 ( 0x16 ) |                                   |

|--------------------------|-----------------------------------|

| Field                    | Value                             |

| Trigger Event            | I2C_MASTER_EVENT_DP_CONFIG_ACE_UD |

| Data Length              | 3                                 |

| Target Address Index     | 1                                 |

| Orientation Independent  | <input type="checkbox"/>          |

| Data                     | 0x555510                          |

図 4-14. レジスタ 0x10 に対する DP 割り当て ACE 構成イベント

| Record index 23 ( 0x17 ) |                                   |

|--------------------------|-----------------------------------|

| Field                    | Value                             |

| Trigger Event            | I2C_MASTER_EVENT_DP_CONFIG_BDF_UU |

| Data Length              | 2                                 |

| Target Address Index     | 1                                 |

| Orientation Independent  | <input type="checkbox"/>          |

| Data                     | 0x1b0a                            |

図 4-15. レジスタ 0x0A に対する DP 割り当て BDF 構成イベント

| Record index 24 ( 0x18 ) |                                   |

|--------------------------|-----------------------------------|

| Field                    | Value                             |

| Trigger Event            | I2C_MASTER_EVENT_DP_CONFIG_BDF_UU |

| Data Length              | 3                                 |

| Target Address Index     | 1                                 |

| Orientation Independent  | <input type="checkbox"/>          |

| Data                     | 0x665510                          |

図 4-16. レジスタ 0x10 に対する DP 割り当て BDF 構成イベント

| Record index 25 ( 0x19 ) |                                   |

|--------------------------|-----------------------------------|

| Field                    | Value                             |

| Trigger Event            | I2C_MASTER_EVENT_DP_CONFIG_BDF_UU |

| Data Length              | 3                                 |

| Target Address Index     | 1                                 |

| Orientation Independent  | <input type="checkbox"/>          |

| Data                     | 0x333320                          |

図 4-17. レジスタ 0x20 に対する DP 割り当て BDF 構成イベント

| Record index 26 ( 0x1a ) |                                    |

|--------------------------|------------------------------------|

| Field                    | Value                              |

| Trigger Event            | I2C_MASTER_EVENT__DP_CONFIG_BDF_UD |

| Data Length              | 2                                  |

| Target Address Index     | 1                                  |

| Orientation Independent  | <input type="checkbox"/>           |

| Data                     | 0x1f0a                             |

図 4-18. レジスタ 0x0A に対する DP 割り当て BDF 構成イベント

| Record index 27 ( 0x1b ) |                                    |

|--------------------------|------------------------------------|

| Field                    | Value                              |

| Trigger Event            | I2C_MASTER_EVENT__DP_CONFIG_BDF_UD |

| Data Length              | 3                                  |

| Target Address Index     | 1                                  |

| Orientation Independent  | <input type="checkbox"/>           |

| Data                     | 0x556610                           |

図 4-19. レジスタ 0x10 に対する DP 割り当て BDF 構成イベント

| Record index 28 ( 0x1c ) |                                    |

|--------------------------|------------------------------------|

| Field                    | Value                              |

| Trigger Event            | I2C_MASTER_EVENT__DP_CONFIG_BDF_UD |

| Data Length              | 3                                  |

| Target Address Index     | 1                                  |

| Orientation Independent  | <input type="checkbox"/>           |

| Data                     | 0x333320                           |

図 4-20. レジスタ 0x20 に対する DP 割り当て BDF 構成イベント

これらのアタッチおよび DP 構成イベントハンドラを通じて、TPS65992S は TUSB1044 が各段階で適切に設定されていることを維持しています。すなわち、初期のアタッチ時 (USB 3.2 SuperSpeed またはベースライン動作) と DisplayPort オルタネート モードへの移行時の両方で維持されます。必要なすべての I2C 書き込みは、PD コントローラのファームウェアによって自動的に行われるため、専用の EC や MCU がリアルタイムでリドライバの設定を管理する必要がなくなります。

## 5 I2C イベント表の概要

TPS65992 I2C コントローラ機能を使用することで、Type-C のイベントに応答して電源 (TPS55288) と信号リドライバ (TUSB1044) の両方を調整することが可能となりました。表 5-1 に、インデックス、トリガ、ターゲットデバイスレジスタ、書き込まれたデータを含む、構成されたすべての I2C イベントを示します：

**表 5-1. すべての I2C インデックスの概要**

|         | トリガイベント                              | レジスタ | 値         |

|---------|--------------------------------------|------|-----------|

| Index1  | I2C_MASTER_EVENT_POWER_ON_RESET      | 0x00 | 0xD2      |

| Index2  | I2C_MASTER_EVENT_POWER_ON_RESET      | 0x04 | 0x03      |

| Index3  | I2C_MASTER_EVENT_POWER_ON_RESET      | 0x06 | 0xa0      |

| Index4  | I2C_MASTER_EVENT_SRC_PDO1_NEGOTIATED | 0x00 | 0xD2 0x00 |

| Index5  | I2C_MASTER_EVENT_SRC_PDO2_NEGOTIATED | 0x00 | 0x9A 0x01 |

| Index6  | I2C_MASTER_EVENT_SRC_PDO3_NEGOTIATED | 0x00 | 0xC5 0x02 |

| Index7  | I2C_MASTER_EVENT_SRC_PDO4_NEGOTIATED | 0x00 | 0xBF 0x03 |

| Index8  | I2C_MASTER_EVENT_DETACH              | 0x00 | 0xD2      |

| Index9  | I2C_MASTER_EVENT_POWER_ON_RESET      | 0x0A | 0x10      |

| Index10 | I2C_MASTER_EVENT_DETACH              | 0x0A | 0x10      |

| Index11 | I2C_MASTER_EVENT_ATTACH_UU           | 0x0A | 0x11      |

| Index12 | I2C_MASTER_EVENT_ATTACH_UU           | 0x0C | 0x58      |

| Index13 | I2C_MASTER_EVENT_ATTACH_UU           | 0x10 | 0x66 0x66 |

| Index14 | I2C_MASTER_EVENT_ATTACH_UU           | 0x20 | 0x33 0x33 |

| Index15 | I2C_MASTER_EVENT_ATTACH_UD           | 0x0A | 0x15      |

| Index16 | I2C_MASTER_EVENT_ATTACH_UD           | 0x0C | 0x58      |

| Index17 | I2C_MASTER_EVENT_ATTACH_UD           | 0x10 | 0x66 0x66 |

| Index18 | I2C_MASTER_EVENT_ATTACH_UD           | 0x20 | 0x33 0x33 |

| Index19 | I2C_MASTER_EVENT_DP_CONFIG_ACE_UU    | 0x0A | 0x1A      |

| Index20 | I2C_MASTER_EVENT_DP_CONFIG_ACE_UU    | 0x10 | 0x55 0x55 |

| Index21 | I2C_MASTER_EVENT_DP_CONFIG_ACE_UD    | 0x0A | 0x1E      |

| Index22 | I2C_MASTER_EVENT_DP_CONFIG_ACE_UD    | 0x10 | 0x55 0x55 |

| Index23 | I2C_MASTER_EVENT_DP_CONFIG_BDF_UU    | 0x0A | 0x1B      |

| Index24 | I2C_MASTER_EVENT_DP_CONFIG_BDF_UU    | 0x10 | 0x66 0x55 |

| Index25 | I2C_MASTER_EVENT_DP_CONFIG_BDF_UU    | 0x20 | 0x33 0x33 |

| Index26 | I2C_MASTER_EVENT_DP_CONFIG_BDF_UD    | 0x0A | 0x1F      |

| Index27 | I2C_MASTER_EVENT_DP_CONFIG_BDF_UD    | 0x10 | 0x55 0x66 |

| Index28 | I2C_MASTER_EVENT_DP_CONFIG_BDF_UD    | 0x20 | 0x33 0x33 |

(表の項目は、上記で説明した構成を反映しています。「REG0x00」に 2 バイトのデータを書き込むというのは、アドレス 0x00 から始まるマルチバイトの書き込みを意味します。未使用的インデックス 8 は、将来の拡張や必要に応じた他のイベントのために確保されています。方向に依存しない書き込み (0x0C、0x10、0x20 など) は、データが同一ですが、このテーブルの UU トリガと UD トリガの両方の下に複製されています。)

図に示すように、TPS65992S は、ポートの初期電源投入からケーブルのどちらの向きでの接続、USB PD 契約の交渉、さらには DisplayPort オルタネートモードへの移行まで、幅広いイベントを事前定義された I2C トランザクションの実行に

よって処理しています。このイベント駆動制御方式により、各段で、外部ハードウェア（パワー コンバータおよびリドライバ）を適切な状態に維持します：

- リセットおよびデタッチ時には、電源は安全な状態（5V またはオフ）に保たれ、高速スイッチはリセットされます。

- アタッチ時には、より高い電圧が要求されるまで電力は 5V のままでなり、USB3 リドライバは SuperSpeed レーンを正しく接続します。

- より高い電圧の PDO が要求されると、PD コントローラは TPS55288 の出力を必要なレベルまで上げます。

- DisplayPort モードに入ると、PD コントローラはリドライバを再構成し、適切なレーンが DisplayPort 信号を伝送し、残りのレーンが USB3 信号を伝送するように設定します。また、信号の整合性を保つために必要に応じて EQ 設定も調整します。

- これらすべての動作は、PD コントローラがカスタマイズ ツールを通じてプログラムされた後は、リアルタイムのソフトウェア介入なしで自律的に行われます。

### まとめ

TPS65992S の統合された I2C ホスト機能を活用することで、USB-C PD システムは電力供給と高速信号の切り替えを緊密に連携させることができます。このアプリケーションでは、TPS65992S が TPS55288 の昇降圧コンバータを PD 契約ごとに適切な電圧に設定し、TUSB1044 リドライバを管理して、ケーブルの向きやモードに関係なく USB3/DisplayPort 信号を正しく経路制御します。論理的な不整合の排除（適切な電圧を設定した後にのみコンバータがイネーブルになっており、モードスイッチ中にリドライバが未定義状態になることがないことの確認など）は、PD コントローラ フームウェアでの慎重なイベント順序により実現されます。

このアプローチでは、従来は外部 MCU や複雑な GPIO ロジックを必要とした制御を、TI のツールを用いてメンテナンスやアップデートが容易なファームウェア駆動のデザインで置き換えていました。各重要イベント（アタッチ、デタッチ、契約交渉、モード移行）は事前定義されたシーケンスをトリガし、常にハードウェアの状態が USB-C の状態と一致するように維持されます。

その結果として得られるのは、例えばノート PC がモニタに接続された際に、Type-C コントローラが瞬時に TUSB1044 を正しい向きに設定し、その後より高い電圧を交渉して TPS55288 に充電用の 20V への昇圧を指示し、さらに DisplayPort オルタネート モードが開始されるとリドライバを再構成してディスプレイを正常に動作させる、という堅牢な設計です。これらすべての作業がユーザーの操作なしで、数分の一秒の間に完了します。これは、統合型 PD コントローラ設計の電力を示します。

## 6 参考資料

- I<sub>2</sub>C インターフェイス付き TPS55288 36V、16A 昇降圧コンバータ

- TUSB1044 USB Type-C™ 10Gbps マルチプロトコル双方向リニア リドライバ

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](#) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1)お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所 : Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated