# Application Note

# AFE7950-SP/SEP のコールドスペアリング

Srinivas Murthy, Dineej A

#### 概要

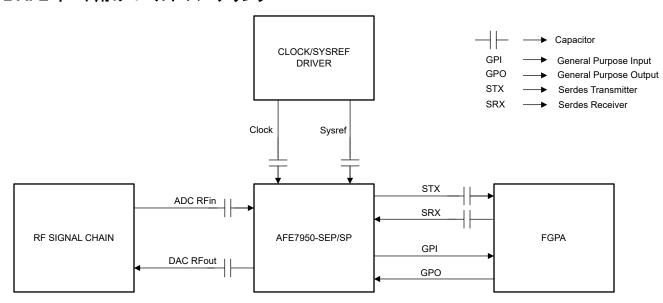

このドキュメントでは、AFE7950-SxP デバイスのコールドスペアリングにおける RF 入力ポート、クロック、SYSREF、SerDes、GPIO ピンについての注意事項を説明します。コールドスペアリングは宇宙アプリケーションでは一般的なシナリオであり、AFE デバイスが電源オフ状態の間、FPGA、クロックチップ、RF LNAドライバなどによりポートが駆動されます。このデバイス状態における重要な要件は、信号が印加されても AFE ポートが損傷しないことです。

# 目次

| 1 はじめに                           | 2 |

|----------------------------------|---|

| 2 AFE ポート用のコールド スペアリング           | 2 |

| <b>2.1 RF Rx</b> 入力ポート           | 3 |

| 2.2 Dev/RefClock ポートと SYSREF ポート | 3 |

| 2.3 GPIO 入力ポート                   |   |

| 2.4 GPIO 出力ポート                   | 3 |

| 2.5 SerDes Rx ポート                |   |

| 3 まとめ                            | 4 |

| 4 参考資料                           | 4 |

| -> 1211                          |   |

# 商標

すべての商標は、それぞれの所有者に帰属します。

### 1 はじめに

人工衛星は通常、メイン モジュールとバックアップ モジュールを搭載しています。この冗長バックアップ モジュールは、メ イン モジュールに問題が発生し、電源がオフになっている場合にのみ、オンボード コンピュータによって起動されます。コ ールドスペアリングはフォルトトレラント手法であり、メインの AFE7950-SxP と交代する必要が生じるまで、バックアップで ある AFE7950-SxP を電源オフの動作停止状態に維持します。この方法を採用すると、システムの稼働時間を維持し、万 が一部品に障害が発生した場合にも動作を継続できます。このアプリケーションノートでは、AFE の電源がオフのときに、 ペリフェラルドライバ (クロック パス上の GPIO を駆動する FPGA、SerDes、Dev/RefCLK、SYSREF、レシーバ (Rx) パ ス上の LNA ドライバなど) によって駆動される際の注意事項について詳しく説明します。 目標は、AFE への電気的な過 剰ストレスを避け、デバイスの損傷を防ぐことです。

### 2 AFE ポート用のコールド スペアリング

図 2-1. ペリフェラル ドライバを搭載した AFE7950-SxP の概略ブロック図

# 2.1 RF Rx 入力ポート

RF 入力ポートには、アナログ電圧電源に接続された ESD 保護ダイオードがあります。ダイオードの最大電流処理キャパシティ制限は 10mA です。入力ポートは常に AC 結合されているため、DC 電流要件はありません。AC 信号の場合、Rx ポートの RF 信号を信頼性限界の約 17dBm 未満に維持します。

#### 表 2-1. Rx ピンでの最大フルスケール電力

| P <sub>FS_CW,MAX</sub> | 最大フルスケール入力電力:デバイスピンでの信頼性は<br>限定的 | f <sub>IN</sub> = 830MHz  | 16.7 | dBm |

|------------------------|----------------------------------|---------------------------|------|-----|

|                        |                                  | f <sub>IN</sub> = 1760MHz | 17   | dBm |

|                        |                                  | f <sub>IN</sub> = 2610MHz | 18   | dBm |

|                        |                                  | f <sub>IN</sub> = 3610MHz | 18.5 | dBm |

|                        |                                  | f <sub>IN</sub> = 4910MHz | 19.3 | dBm |

#### 2.2 Dev/RefClock ポートと SYSREF ポート

Dev/RefClock および SYSREF ポートには ESD 保護ダイオードが内蔵されており、内部で安定化された 1V 電源に接続されています。Dev/RefClock および SYSREF 入力の AC 結合モードでは、これらのポートへの最大電力は 10dBm に制限されます。SYSREF およびクロック入力の DC 結合モードのダイオードの最大電流処理キャパシティ制限は 10mA です。TI の推奨は、AFE 電源レールに電源を供給した後に外部リファレンス クロックと SYSREF ドライバを起動して、これらのポートでのコールド スペアリングを避けることです。

#### 2.3 GPIO 入力ポート

すべての GPIO 入力ポートには、VDDGPIO1p8V に接続された ESD ダイオードがあります。電流駆動を制限するため、外部 FPGA ドライバと直列に 100 $\Omega$  を使用することを推奨します。

別のアプローチは、AFE のパワーダウン中に FPGA 出力を入力として構成することです。 通常のユース ケースでは、SPI ポートは FPGA によって AFE に駆動されます。 コールド スペアリング中、パワーアップ時にこれらのポートを FPGA 上の入力として構成し (そのため AFE へのドライバはなし)、 AFE のパワーアップ後に出力として再構成して、 AFE のプログラミングを開始できます。

同様に、この方法は AFE LVDS 同期入力ピンにも適用できます。

#### 2.4 GPIO 出力ポート

TI は、すべての GPIO 出力ポートに 100Ω の電流制限抵抗を直列に使用して、FPGA 入力ポートを保護することを推奨しています。

#### 2.5 SerDes Rx ポート

SerDes Rx ポートには、VDDA 1.8V に接続された ESD ダイオードがあります。ダイオードの最大電流処理キャパシティ制限は 10mA です。SerDes Rx ポートは通常 AC 結合されており、1Vpp の差動スイングに制限されている必要があります。

# 3 まとめ

このアプリケーション ノートは、宇宙アプリケーション向けの AFE7950-SxP のコールド スペアリングに関する主な要件を掲載しています。このドキュメントでは、AFE の電源がオフでペリフェラルドライバによって駆動する際に考慮すべき RF 入出力、GPIO と SerDes 入力の要件について説明しています。

### 4参考資料

• テキサス インスツルメンツ、AFE7950-SxP 4T6R 宇宙グレード RHA RF サンプリング AFE、データシート。

# 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated

### 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、 テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、 テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。 テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、 テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、 テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、 テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。 テキサス・インスツルメンツがこれらのリソ 一スを提供することは、適用される テキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、 テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated