*Application Note***TAS278x Class-D アンプの Y ブリッジで効率の向上に寄与**

Nayeem Mahmud

**概要**

ノート PC、タブレット、スマートワイヤレススピーカなどのバッテリ駆動デバイスが、より高度な機能を継続的に統合するにつれて、電力効率は設計の重要な検討事項になっています。この課題に対処するために、テキサスインストルメンツ(TI)が開発した Y ブリッジパワー アーキテクチャは、従来の Class-D オーディオアンプ設計に比べて大幅な強化となっています。この高度なアーキテクチャは、TI の最新の TAS2781 および TAS2783 デバイスに実装されています。このデバイスは、デジタル信号処理(DSP)とスピーカ保護アルゴリズムを内蔵したデジタル入力 Class-D スマートオーディオアンプです。このアプリケーションノートは、電源選択をインテリジェントに管理して電圧ヘッドルームを最適化し、それによってアンプ全体の効率が向上し、バッテリの消費電力が減少する方法を詳細に説明して、Y ブリッジアーキテクチャの概要を解説します。また、このアプリケーションノートは、実践的な実装シナリオを紹介し、従来の Class-D アンプ設計に比べた Y ブリッジ設計の主な利点についても説明しています。

**目次**

|                                  |    |

|----------------------------------|----|

| 1はじめに.....                       | 2  |

| 2 Y ブリッジとは何か.....                | 2  |

| 3 Class-D スイッチングモードとレジスタ設定.....  | 4  |

| 4 PWR_MODE1 [CDS_MODE = 00]..... | 5  |

| 5 PWR_MODE2 [CDS_MODE = 11]..... | 6  |

| 6 外付け部品必要.....                   | 7  |

| 7 Y ブリッジの利点.....                 | 8  |

| 8 まとめ.....                       | 10 |

| 9 参考資料.....                      | 11 |

| 10 改訂履歴.....                     | 12 |

**商標**

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

従来のオーディオアンプアーキテクチャでは、出力段のスイッチングと増幅のために単一の高電圧電源レール(PVDD)と、I/OおよびLDO用の低電圧レールを使用しています。ただし、アイドル期間(オーディオ信号が存在しない場合)は、アンプのスイッチングを継続するため、電力効率が低下します。スイッチングは高電圧レールのみで行われるため、電圧ヘッドルームが過剰になると、アイドル効率が20%を下回る結果になります。この制限を克服するため、テキサスインスツルメンツはYブリッジパワーアーキテクチャを導入しました。このインテリジェントな設計により、出力電力の需要に基づいて、アンプは2つの電源レール間でシームレスに切り替えられます。Yブリッジアーキテクチャは、電源電圧をリアルタイムで最適化することにより、アイドル時の消費電力を最大90%削減し、オーディオ性能を犠牲にすることなく低出力レベルでの効率を15%から20%向上させます。TIの先進のスピーカ保護と信号処理アルゴリズムとの組み合わせにより、次世代のポータブルオーディオアプリケーションのバッテリ寿命とシステム全体の性能を最大化できます。

## 2 Yブリッジとは何か

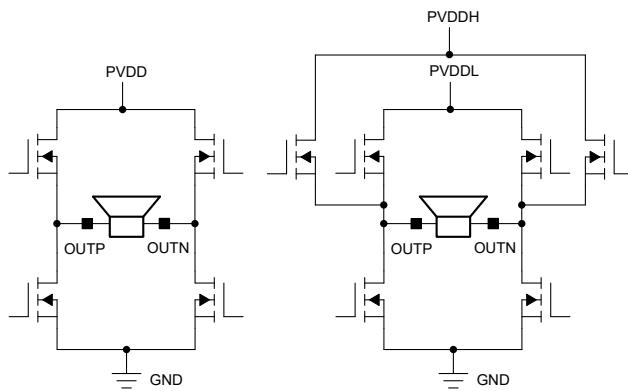

Yブリッジの電源アーキテクチャは、その名前が示すように、従来のリニアハーフブリッジトポロジとは対照的に「Y」構成に似ています。従来のハーフブリッジClass-Dアンプでは、出力段は、出力電力の要件にかかわらず、単一の高電圧電源レール(PVDD)のみで動作します。その結果、低消費電力またはアイドル条件で完全な電圧ヘッドルームが不要などきに大幅な効率損失が発生します。Yブリッジアーキテクチャは、高電圧レール(PVDDH)と低電圧レール(PVDDL)の両方を出力段に組み込むことで、この制限に対応しています。

アイドル状態を含む低出力電力レベルでは、アンプは必要なヘッドルームが最小限で、信号クリッピングにリスクを冒さず満たすことができるため、低電圧レール(PVDDL)で動作します。このアプローチにより、低い出力レベルにおいて電力効率が大幅に向上します。より高い出力電力が必要な場合、アンプは高電圧レール(PVDDH)にシームレスに遷移し、性能を犠牲にすることなく必要なヘッドルームを提供します。この状態では、システムの効率は従来型Class-Dアンプの効率と一致しています。その結果、Yブリッジアーキテクチャは、通常、従来型アンプが最も効率的に動作しない低出力レベルから中程度の出力レベルで最も顕著な効率向上を実現します。

図2-1に、従来のClass-Dアンプと、Yブリッジアーキテクチャを利用したアンプの構造と動作の違いを示します。

図2-1. 従来のClass-Dアンプと簡略化したYブリッジアーキテクチャの比較

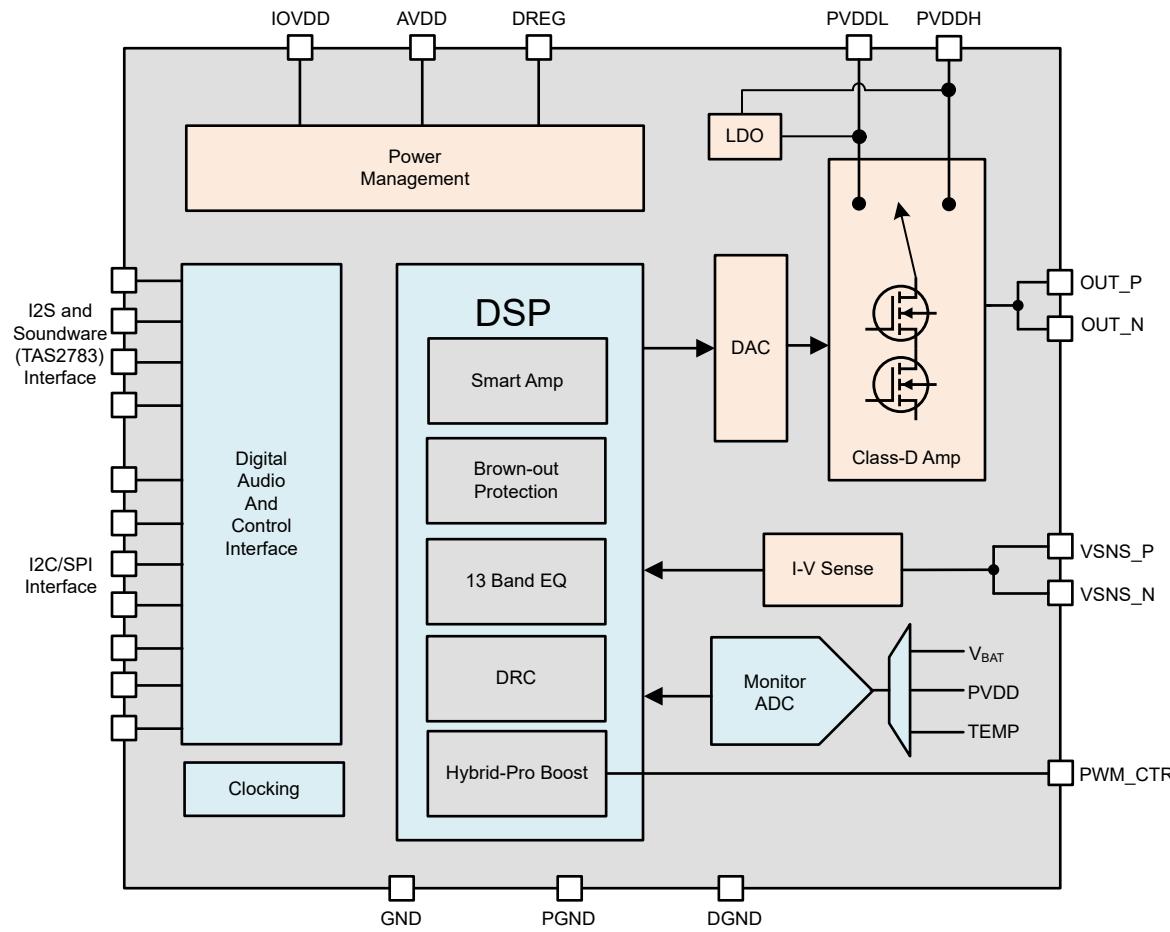

テキサスインスツルメンツの最新のオーディオアンプであるTAS2781とTAS2783にはYブリッジアーキテクチャが組み込まれており、オーディオ再生時の電力効率を向上させています。TAS278xデバイスの機能ブロック図を図2-2に示します。Yブリッジ機能は、デバイス構成を使用してイネーブルまたはディセーブルにでき、システム要件に基づいて柔軟に実現できます。さらに、目的の性能特性に応じて、アンプは低電圧レール(PVDDL)または高電圧レール(PVDDH)からのみ動作するように設定できます。PVDDLまたはPVDDHのみを使用するように構成した場合、特に高い出力要求において、出力クリッピングを回避するのに十分な電源電圧を選択することが重要です。これらの設定と運用上の影響の詳細については、[セクション3](#)を参照してください。

図 2-2. Y ブリッジ機能を使用した TAS278x の機能ブロック図

### 3 Class-D スイッチング モードとレジスタ設定

TAS2781 および TAS2783 デバイスは高度に構成可能であり、各種のシステム要件に対応するため、複数の電源構成をサポートしています。Y ブリッジ アーキテクチャによる動的スイッチングのために、PVDDL と PVDDH の両方の電源レールを使用して動作することも、デバイスは PVDDH と PVDDL のどちらからも排他的に動作するように構成することもできます。

表 3-1 に、利用可能な電源モードと、対応する使用事例を示します。これにより、設計者はアプリケーション固有のニーズに基づいて最も効率的な構成を選択できます。

**表 3-1. Class-D スイッチング パワー モード**

| 電力モード             | PVDDL_MODE | CDS_MODE | Y ブリッジ | 説明                                                                                                                                                                                                                                                                                              |

|-------------------|------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWR_MODE0         | 0          | 10       | ディセーブル | <b>PVDDH</b> と <b>PVDDL</b> の両方が <b>外部</b> からデバイスに電源供給されますが、Class-D スイッチングに使用されるのは <b>PVDDH</b> のみであり、 <b>PVDDL</b> はゲートドライバと内部回路に電力を供給します。                                                                                                                                                     |

| PWR_MODE1 (デフォルト) | 0          | 00       | イネーブル  | <b>PVDDH</b> と <b>PVDDL</b> の両方が <b>外部</b> からデバイスに電源供給され、Class-D スイッチングに使用されます。このモードでは、Y ブリッジ機能がイネーブルになります。                                                                                                                                                                                     |

| PWR_MODE2         | 1          | 11       | イネーブル  | <b>PVDDH</b> のみが外部から供給され、 <b>PVDDL</b> はデバイスによって <b>内部</b> で生成されます。 <b>PVDDH</b> と <b>PVDDL</b> の両方が Class-D のスイッチングに使用され、Y ブリッジ機能がイネーブルになります。オーディオ信号レベルが LVS_TH_LOW[2:1] で定義されているデフォルトのスレッショルドである -71.5dBFS を超えると、Class-D 出力は <b>PVDDH</b> に切り替わります。 <b>PVDDL</b> からは、アイドル チャンネルの切り替えのみが発生します。 |

| PWR_MODE3         | 0          | 01       | ディセーブル | 外部からデバイスに供給されるのは <b>PVDDL</b> のみであり、デバイスは Class-D スイッチングのために <b>PVDDL</b> レールのみから動作するように強制的に設定できます。ただし、このモードでは <b>PVDDH</b> がオーディオ切り替えに積極的に使用されていない場合でも、 <b>PVDDH</b> 電源は依然として必要であり、デバイスが適切に動作するためには <b>PVDDH &gt; PVDDL + 0.7V</b> の条件を満たす必要があります。                                             |

**表 3-2. パワー モード レジスタ設定**

| アドレス | フィールド [ビット]   | タイプ | リセット | 説明                                                                                                 |

|------|---------------|-----|------|----------------------------------------------------------------------------------------------------|

| 0x04 | PVDDL_MODE[7] | RW  | 21h  | PVDDL 電源<br>0h = 外部から供給 (デフォルト)<br>1h = PVDDH から内部生成                                               |

| 0x03 | CDS_MODE[7:6] | RW  | 28h  | Class-D スイッチング モード<br>0h = PWR_MODE1 (デフォルト)<br>1h = PWR_MODE3<br>2h = PWR_MODE0<br>3h = PWR_MODE2 |

このアプリケーションノートでは、特に **PWR\_MODE1** と **PWR\_MODE2** について説明します。これらは Y ブリッジ機能をサポートする 2 つの構成であるためです (表 3-1 を参照)。これについては、以下のセクションで詳細に説明します。

## 4 PWR\_MODE1 [CDS\_MODE = 00]

この構成では、PVDDH と PVDDL の両方の電源レールが外部から供給され、Class-D スイッチングに使用され、Y ブリッジ機能がイネーブルになります。

TAS278x デバイスには、受信オーディオ ストリームの絶対振幅を監視して、適切な電源レール (PVDDH または PVDDL) を決定するメカニズムが内蔵されています。オーディオ信号がプログラム可能な低電圧信号処理 (LVS) スレッショルド (固定または相対として構成) を超えると、Class-D 段は高電圧レール (PVDDH) に切り替わり、信号のクリッピングを防止します。信号が、*LVS\_HYS[3:0]* レジスタビットで定義されるヒステリシスの持続時間を超えて、このスレッショルドを下回るまでの時間が経過すると、アンプは消費電力を節約するため、低電圧レール (PVDDL) に遷移します。信号がスレッショルドを再度超えると、電源は PVDDH に戻ります。

デフォルトでは、LVS スレッショルドは PVDDL 電圧 (*LVS\_DET* = 1) を基準にして設定されます。相対スレッショルド レベルを構成するには、*LVS\_RTH[3:0]* レジスタビットを使用し、デフォルト値は 0.7V です。または、*LVS\_DET* = 0 に設定すると、*LVS\_FTH[4:0]* レジスタビットで定義された固定 LVS スレッショルドがイネーブルになります。LVS スレッショルドは出力信号レベルを基準とし、dBFS で表されます。

アンプが PVDDL から PVDDH に切り替わる相対スレッショルド電圧は、次のように計算されます。

$$\text{相対スレッショルド (VP)} = (\text{PVDDL} \times \text{Class-D 効率} - \text{相対スレッショルド ヘッドルーム}) / \text{変曲係数}$$

ここで

- 相対スレッショルド ヘッドルームは、*LVS\_RTH* レジスタによって定義されます

- Class-D 効率の代表値は 85% (0.85)

- 変曲率は 1.2 の固定設計パラメータです

たとえば、PVDDL = 5V の場合、Y ブリッジ スイッチングの相対スレッショルド =  $(5 \times 0.85 - 0.7) / 1.2 = 2.96\text{Vp}$  です

このインテリジェントなレール スイッチング メカニズムにより、Y ブリッジ アーキテクチャでオーディオ性能を維持すると同時に、特に低い出力レベルで電力効率を大幅に向上させることができます。

**表 4-1. PWR\_MODE1 レジスタの設定**

| アドレス | フィールド [ビット]  | タイプ | リセット | 説明                                                                                                                                                                 |

|------|--------------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x37 | LVS_DET[7]   | RW  | A8h  | PWR_MODE1 の LVS 検出スレッショルド:<br>0h = 固定<br>1h = PVDDL 電圧を基準とする (デフォルト)                                                                                               |

| 0x37 | LVS_FTH[4:0] | RW  | A8h  | LVS 固定スレッショルド (PWR_MODE1):<br>CDS_MODE=0h<br>00h = -18.5dBFS<br>01h = -18.25dBFS<br>.....<br>08h = -16.5dBFS (デフォルト)<br>.....<br>1Eh = -11dBFS<br>1Fh = -10.75dBFS |

| 0x6A | LVS_RTH[3:0] | RW  | 12h  | PWR_MODE1 の LVS 相対スレッショルド ヘッドルーム: CDS_MODE=0h<br>0h = 0.5 V<br>1h = 0.6 V<br>2h = 0.7V (デフォルト)<br>.....<br>Eh = 1.9V<br>Fh = 2V                                    |

**表 4-1. PWR\_MODE1 レジスタの設定 (続き)**

| アドレス      | フィールド [ビット]      | タイプ | リセット       | 説明                                                                                                                                                                                                                       |

|-----------|------------------|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x36      | LVS_HYST[3:0]    | RW  | ADh        | PVDDH から PVDDL までのヒステリシス時間<br>(PWR_MODE1 および PWR_MODE2)<br>0h~9h=予約済み<br>Ah = 1ms<br>Bh = 10ms<br>Ch = 20ms<br>Dh = 50ms (デフォルト)<br>Eh = 75ms<br>Fh = 100ms<br>*サンプリング レート $fs < 48\text{kspS}$ の場合、上記の値を $48/fs$ で乗算します |

| 0x14-0x17 | CLASSD_EFF[31:0] | RW  | 6CCCCCCCCh | クラス D 効率を EFF (%) 値に設定<br>dec2hex [round (EFF*2^31)]                                                                                                                                                                     |

## 5 PWR\_MODE2 [CDS\_MODE = 11]

この構成では、PVDDH レールのみから外部から供給され、PVDDL 電圧はデバイスによって内部で生成されます。PVDDH と PVDDL の両方が Class-D のスイッチングに使用され、このモードでは Y ブリッジ機能がイネーブルになります。

このアンプはオーディオ信号レベルを監視し、低電圧信号処理 (LVS) スレッシュルドである -71.5dBFS (デフォルトは LVS\_TH\_LOW[2:1] レジスタ ビットで設定) を超えると、Class-D 出力は PVDDL から PVDDH に切り替わります。このモードでは、PVDDL レールでアイドル チャネルのスイッチングのみが発生し、アクティブなオーディオ再生では、信号がスレッシュルドを超えると PVDDH が使用されます。

**表 5-1. PWR\_MODE2 レジスタの設定**

| アドレス | フィールド [ビット]     | タイプ | リセット | 説明                                                                                                                       |

|------|-----------------|-----|------|--------------------------------------------------------------------------------------------------------------------------|

| 0x34 | LVS_TH_LOW[2:1] | RW  | 06h  | LVS 固定スレッシュルド (PWR_MODE2): CDS_MODE=3h<br>0h = -121.5dBFS<br>1h = -101.5dBFS<br>2h = -81.5dBFS<br>3h = -71.5dBFS (デフォルト) |

PWR\_MODE2 の Y ブリッジ機能を十分に活用するには、PVDDH 電源が内部生成された PVDDL より少なくとも 2.5V 高いことが重要です。たとえば、PVDDL が内部で 4.8V に設定されている場合、PVDDH は 7.3V 以上にする必要があります。この要件を保護するには、PVDDH の低電圧保護スレッシュルドを PVDDH\_UV\_TH[5:0] レジスタ ビットで構成する必要があります。このスレッシュルドを適切に設定することにより、シームレスな Y ブリッジ動作を実現するための電圧ヘッドルームが維持されます。

**表 5-2. PVDDH 低電圧スレッシュルド**

| アドレス | フィールド [ビット]      | タイプ | リセット | 説明                                                                                               |

|------|------------------|-----|------|--------------------------------------------------------------------------------------------------|

| 0x71 | PVDDH_UV_TH[5:0] | RW  | 02h  | PVDDH 低電圧スレッシュルド<br>00h = 1.753 V<br>01h = 2.09 V<br>02h = 2.428V (デフォルト)<br>.....<br>3Fh = 23 V |

PVDDH が (PVDDL +2.5V) を下回ると、Y ブリッジ機能をディセーブルにして、信号レベルに関係なく Class-D 出力は PVDDH のままになることに注意してください。

また、LVS スレッショルドを超えるオーディオ信号に応答して、PVDDL から PVDDH (またはその逆) に遷移するのは瞬間的ではありません。プログラム可能な遅延によりこの遷移が制御され、**CDS\_DLY[1:0]** レジスタ ビットを使用して構成できます。この遅延設定により、スイッチング動作を微調整して応答性とオーディオ性能のバランスをとることができます。

**表 5-3. Class-D スイッチング遅延**

| アドレス | フィールド [ビット]  | タイプ | リセット | 説明                                 |

|------|--------------|-----|------|------------------------------------|

| 0x6A | CDS_DLY[7:6] | RW  | 12h  | 書き込み入力信号の Y ブリッジ スイッチングの遅延 (1/fs)。 |

## 6 外付け部品必要

Y ブリッジ機能を実装する際、特にデカップリング要件に関して、設計者は推奨の外部部品に細心の注意を払う必要があります。安定した動作を確保するために、すべての電源モードにわたって 100nF のデカップリング コンデンサが必須です。

100nF のコンデンサ (C2) に加えて、特定の電力モードでさらにデカップリングを必要とします。

- PWR\_MODE0、PWR\_MODE1、PWR\_MODE3 の場合は、PVDDL に追加の 10μF コンデンサ (C1) が必要です。

- PWR\_MODE2 の場合は、PVDDL の内部生成のため、追加の 1μF コンデンサ (C1) をお勧めします。

これらの部品要件を表 6-1 にまとめ、適切な電源安定性と Y ブリッジ性能向けの設計に不可欠です。

**表 6-1. 推奨外付け部品**

| 部品 | 説明                                                    | 仕様        | 最小値 | 標準値 | 最大値 | 単位 |

|----|-------------------------------------------------------|-----------|-----|-----|-----|----|

| C1 | PVDDL デカップリング コンデンサ<br>-PVDDL 外部電源 (PWR_MODE0/1/3)    | 容量、公差 20% |     | 10  |     | μF |

|    |                                                       | 定格電圧      |     | 10  |     | V  |

| C2 | PVDDL デカップリング コンデンサ<br>- PVDDL が内部生成されました (PWR_MODE2) | 容量、公差 20% |     | 1   |     | μF |

|    |                                                       | 定格電圧      |     | 10  |     | V  |

| C3 | PVDDH デカップリング コンデンサ                                   | 容量、公差 20% |     | 10  |     | μF |

|    |                                                       | 定格電圧      |     | 25  |     | V  |

| C4 | PVDDH デカップリング コンデンサ                                   | 容量、公差 20% |     | 0.1 |     | μF |

|    |                                                       | 定格電圧      |     | 25  |     | V  |

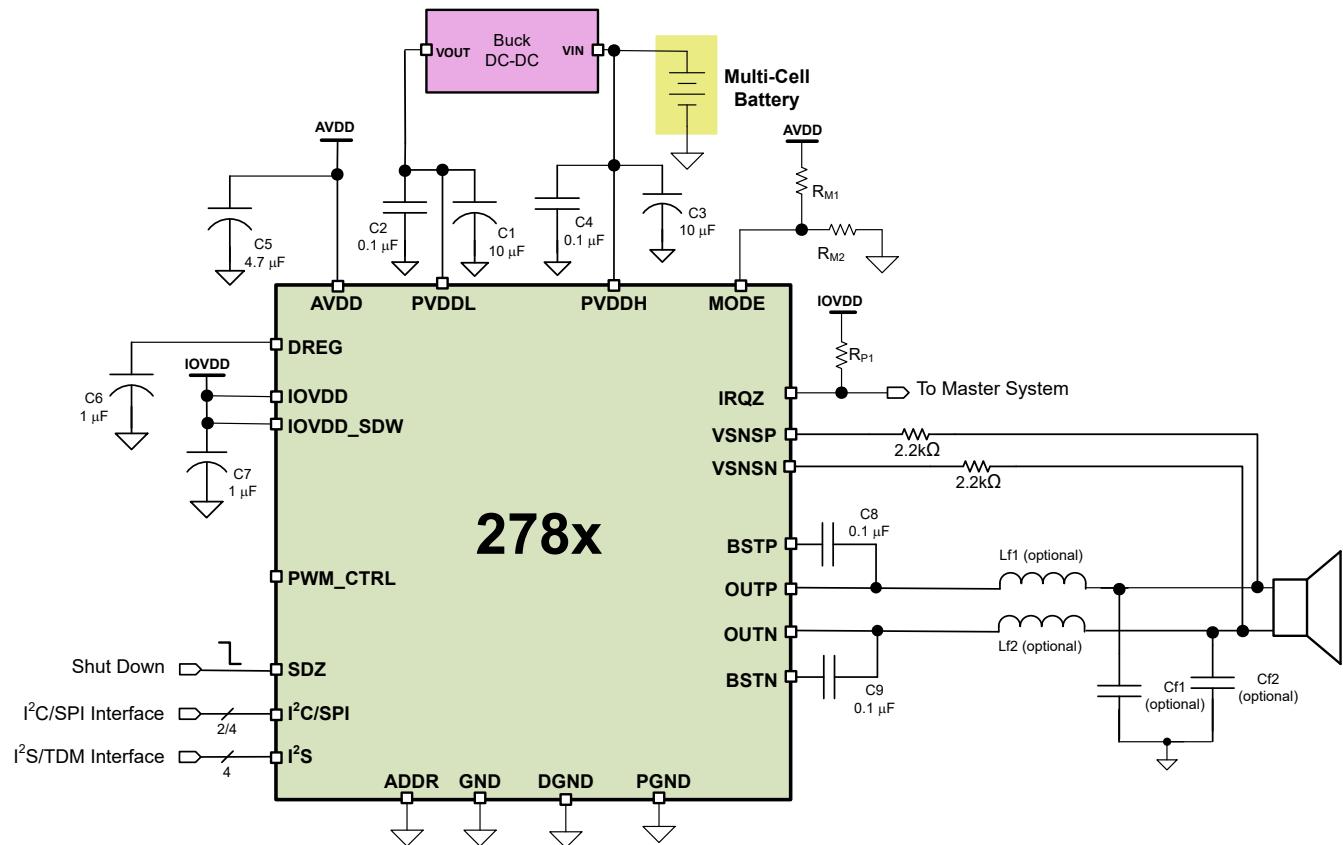

図 6-1 は、PVDDL ピンに 10μF のデカップリング コンデンサ (C1) を追加した、PWR\_MODE0/1/3 のマルチセル バッテリシステム用の TAS2783 の標準的なアプリケーション回路を示しています。

図 6-1. 代表的なアプリケーション - マルチセル バッテリ システム

## 7 Y ブリッジの利点

Y ブリッジアーキテクチャは、2S ~ 4S (2 セル ~ 4 セル) バッテリ構成 (通常は 7V ~ 14V) で駆動するものなど、高電圧の電力段電源を必要とするシステムで特に有利です。TAS2781 および TAS2783 では、この高電圧入力は PVDDH ピンから供給され、4V ~ 24V の電圧範囲をサポートします。PVDDH は、マルチセル バッテリから直接、またはシングルセル (1S) バッテリシステムの昇圧コンバータの出力から電源を供給できます。低電圧レール PVDDL (2.7V ~ 5.5V の範囲) は通常、1S バッテリから直接、または 2S ~ 4S 構成の降圧コンバータから供給されます。

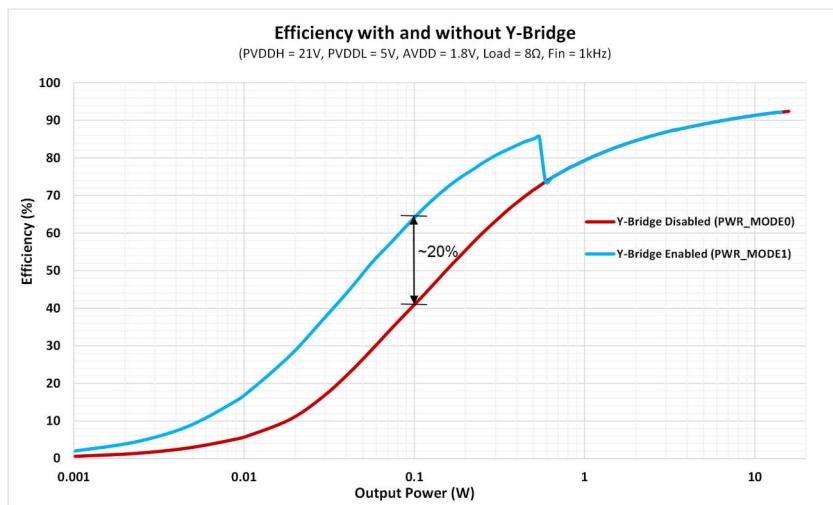

図 7-1 に示すように、Y ブリッジアーキテクチャを使用すると、固定高電圧電源のみで動作する従来の Class-D アンプに比べて、低い出力レベルでの効率が大幅に向上します。

図 7-1. Y ブリッジありなしで効率を測定

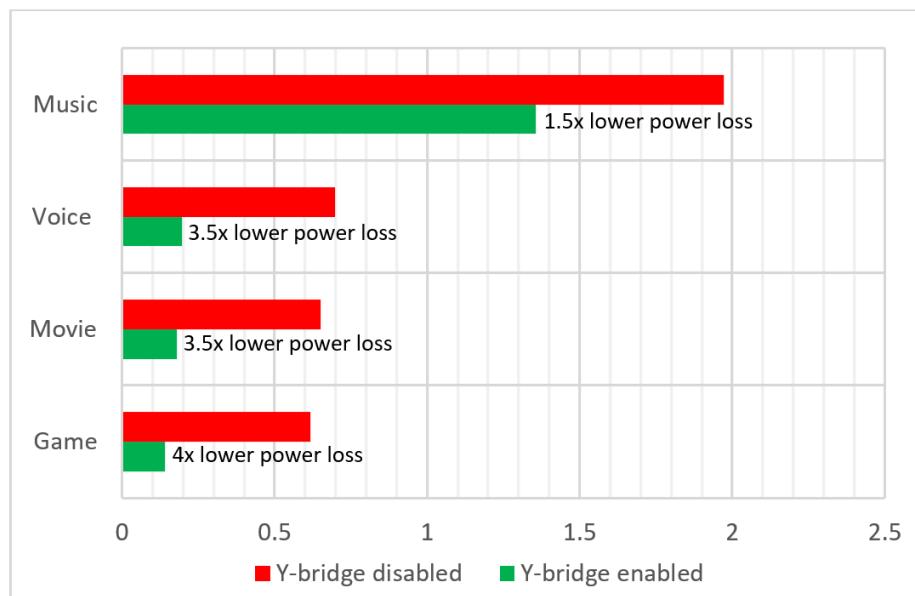

図 7-2 は、Y ブリッジ機能を有効にすることで、これを使用しない場合と比べて電力損失を最大 75% 削減できることを示しています。節電の程度は、アプリケーションとオーディオコンテンツによって異なります。たとえば、断続的に無音または信号レベルが低いオーディオトラックは、音楽のような高エネルギーの連続コンテンツよりも効率が向上する傾向があります。

この電力損失の低減により、全体のバッテリ寿命が最大 20% 向上します。ソフトウェア制御の追加やシステム レベルの変更は必要ありません。Y ブリッジ機能は信号条件に基づいて自動的に動作するため、ポータブル オーディオ デバイスのバッテリ寿命を延長するためのシンプルかつ効果的な方法を実現します。

図 7-2. ラップトップ スピーカに接続した EVM で測定した電力損失 (W 単位)

## 8 まとめ

高効率とバッテリ動作時間の延長を必要とするオーディオ設計向けに、Y ブリッジ アーキテクチャ採用アンプは魅力的なデザインを提供します。テキサス インスツルメンツの最新のオーディオ アンプは、このアーキテクチャを高度なオーディオ処理アルゴリズムと統合し、電力効率と高性能の音質を提供します。Y ブリッジ テクノロジーの実装により、AC 電源システムの消費電力を削減し、バッテリ動作デバイスの再生時間を大幅に延長できます。

Y ブリッジ対応オーディオ アンプで構成された TI の製品ラインアップの詳細は、[TI.com](http://TI.com) をご覧ください。

## 9 参考資料

- テキサス インスツルメンツ、[TAS2781:25W, 4.5V ~ 23V、デジタル入力、オーディオ処理機能内蔵、スピーカ保護機能搭載、Class-D アンプ](#)

- テキサス インスツルメンツ、『[TAS2x20 での Y ブリッジによる効率向上、TAS257x』、アプリケーション ノート](#)

- テキサス インスツルメンツ、[オーディオ アンプ:オーディオ システムをアンプ](#)

## 10 改訂履歴

### Changes from Revision \* (June 2025) to Revision A (September 2025)

|                                      | Page |

|--------------------------------------|------|

| • ドキュメント全体にわたって表、図、相互参照の採番方法を更新..... | 1    |

| • 消費電力を電力損失に変更.....                  | 8    |

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](#) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月