# Application Brief

# TI のプログラマブル ロジック デバイスの PWM ジェネレータ

#### アプリケーションの説明

パルス幅変調 (PWM) とは、方形波または矩形波信号を、さまざまなデューティサイクルで提供する方法であり、電力変換や LED の輝度制御などのアプリケーションで一般的に採用されています。TI のプログラマブルロジック デバイス (TPLD) はパルス幅変調ジェネレータを内蔵しており、設計者はデューティサイクルが可変の方形波の生成と制御を簡単に実行できます。この文書では、TPLD1202 に含まれる PWM ジェネレータの概要、すなわち、使用可能な設定と Interconnect Studio (ICS) での構成方法について説明します。

#### PWM ジェネレータ部品

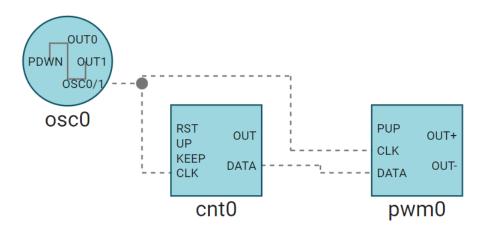

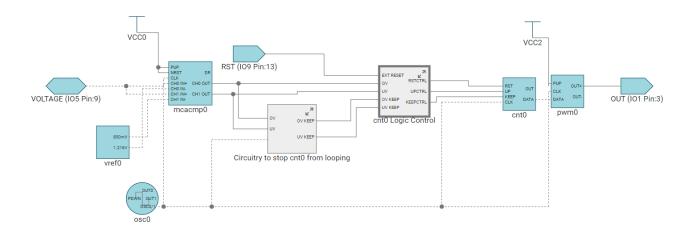

ICS でインスタンス化されると、図 1 に示すように、PWM ジェネレータ (*pwm0*) は有限ステートマシン (FSM) モードのカウンタモジュール (*cnt0*) と内部発振器 (*osc0*) と一緒に表示されます。

図 1. IC の PWM ジェネレータ

内部発振器は、カウンタと PWM ジェネレータの両方に対するクロックとして機能するように自動的に設定されます。内部発振器には、出力周波数を変更できる設定があります。カウンタまたは PWM ジェネレータのクロック ソース設定を変更することで周波数を分周することもできます。クロック ソース設定では、必要に応じて外部クロック ソースを使用することもできます。出力歪みを回避するため、カウンタと PWM ジェネレータは同じクロック ソースを使用し、同じ周波数で動作することに注意します。発振器モジュールの構成については、TPLD のタイミング部品の活用で詳細に説明されています。

#### カウンタ FSM 機能

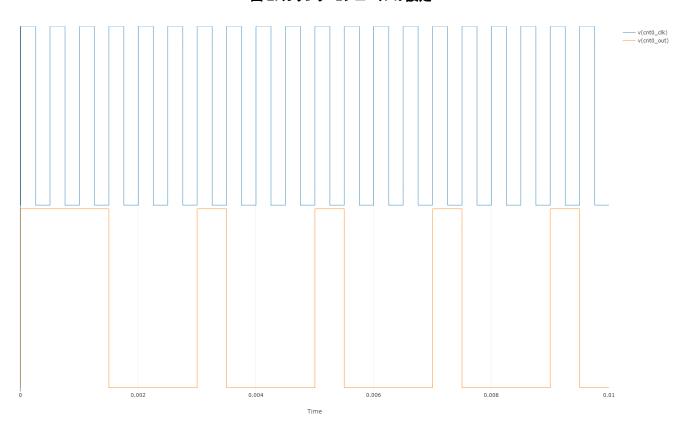

デフォルトでは、カウンタ FSM は、内部カウント値がゼロになるまで、受信するクロック パルスごとに*制御データ*値から 1 つの値をカウント ダウンすることで動作します。この時点で FSM は 1 クロック サイクルの出力パルスを供給し、リセットします。 図 2 は、図 3 に示すカウンタ設定で*制御データが*が 3 に設定された ICS カウンタ シミュレーションの例を示します。 カウンタ (黄色) は、3 クロック サイクル (青) ごとに High にパルスします。

| COUNTER ⊚                  |                  | Q [ i |

|----------------------------|------------------|-------|

| Name                       | cnt0             |       |

| Label                      |                  |       |

| Clock Source               | External Clock   | •     |

| Control Data               | 3                |       |

| RST Sync Bypass            | 2-DFF sync       | •     |

| Initial Value              | Bypass initial   | •     |

| Output Polarity            | Non-inverted     | ~     |

| Reset Mode                 | High Level Reset | ~     |

| Enable FSM Mode            | <b>✓</b>         |       |

| UP Sync Bypass             | 2-DFF sync       | •     |

| KEEP Sync Bypass           | Bypass 2-DFF     | •     |

| Device MacroCell Allocated | Any(CNT_FSM_0)   | ~     |

図 2. カウンタ モジュールの設定

図 3.3 の制御データによるカウンタ シミュレーション

図 1 に示す DATA 接続は、現在の内部カウント値を PWM ジェネレータに提供するカウンタです。この値によって、 PWM ジェネレータ出力のデューティサイクルが決定されます。 PWM 信号のデューティサイクルは次の式で計算できま す。 デューティ サイクル (%) = (*DATA* / 256) × 100、最小デューティ サイクルは 0% (0/256)、最大は 99.61% (255/256) です。 カウント値が変化するたびに、 デューティ サイクルが追加で 0.39% 増加または減少します。

図 1 に示すカウンタ入力信号 *UP* および *KEEP* は、特定のカウンタに対して図 2 に表示されている *FSM モードの有効 化*設定が選択されている場合に存在します (PWM に *DATA* を提供するカウンタは FSM モードでロックされます)。 これらの信号を使用して、カウンタが提供する内部カウント値 / *DATA* を制御し、PWM ジェネレータのデューティサイクルを動的に変更することができます。 *UP* のロジックを High にすると、カウンタは 0 までではなく、パルスを発生させる前に最大 255 までカウントされます。 *KEEP* のロジックを High にすると、受信クロック パルスに関係なく、現在の内部カウント値が維持されます。 *RST* 入力ロジックを High にすると、現在の内部カウント値は、制御データ設定で設定された初期値にリセットされます。

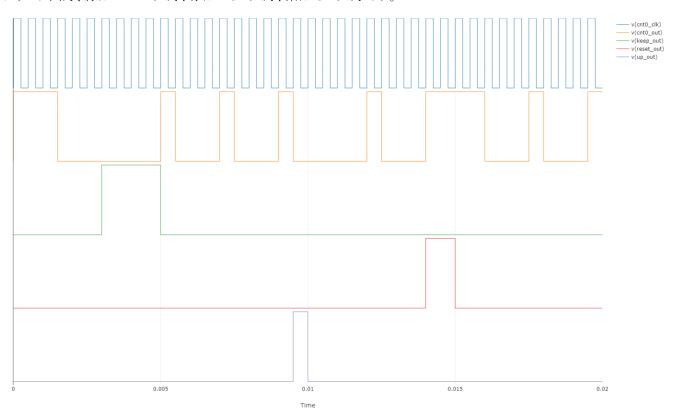

図 4 に、さまざまな FSM 信号を使用したカウンタの ICS シミュレーションを示します。上から下まで青はクロック、黄色はカウンタ出力、緑は KEEP 入力、赤は RST 入力、紫は UP 入力です。

図 4.3 の制御データによる FSM カウンタ シミュレーション

### PWM ジェネレータ構成

CLK と DATA の接続に加えて、PWM ジェネレータには、図 1 に示すように、ジェネレータが出力信号を供給するためのロジック High である PUP (電源オン) 入力と、2 つの出力 OUT+ および OUT- がデフォルトで互いに同相である必要があります。 PWM 構成オプションを図 5 に示します。

| PULSE WIDTH MODULATOR   ③  |             | Q [ i |

|----------------------------|-------------|-------|

| Name                       | pwm0        |       |

| Label                      |             |       |

| Clock Select               | OSCO/1      | ~     |

| Output - Inversion         |             |       |

| Output + Inversion         |             |       |

| Deadband Time              | No Deadband | ~     |

| Source Select              | CNTFSM0     | ~     |

| Device MacroCell Allocated | Any(PWM_0)  | *     |

図 5. PWM 構成オプション

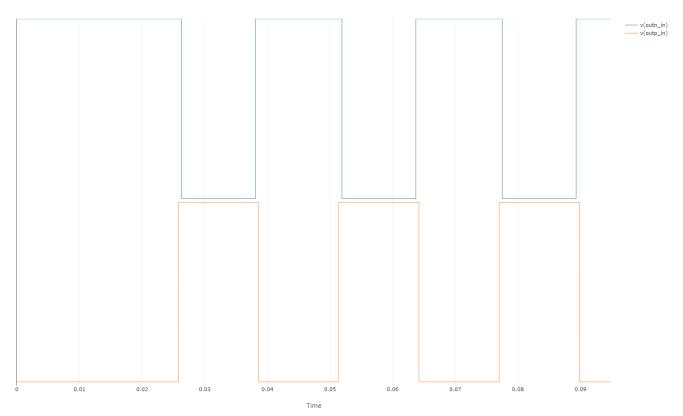

適切な出力反転ボックスをチェックすることで、OUT+と OUT- 両方を反転できます。OUT- に対してはデッドバンド 0、1、 2、5 クロックを選択できます。この設定により、PWM が H ブリッジなどの回路で使用されたときの貫通電流の可能性を低 減できます。 データが 128 (50% デューティ サイクル))、 反転 OUT- 出力、5 クロック デッドバンドを持つ PWM ジェネレ ータのシミュレーション波形を図 6 に示します。 OUT- は青、OUT+ は黄色です。 完全な出力期間の 1 つは、255 クロック サイクルを要し、PWM 入力クロックソースによって決定されます。

図 6. PWM シミュレーション

#### 回路例

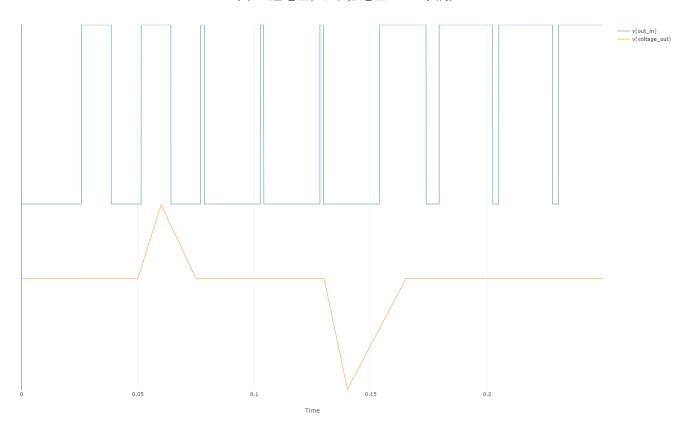

図 7 の回路は、過電圧および低電圧の検出および制御アプリケーションの例で、PWM ジェネレータのデューティサイクルを動的に変化させるように構成されています。PWM はデフォルトで 50% のデューティサイクルで動作するように設定されており (cnt0 には制御データ 128 が与えられます)、KEEP はロジック high に設定されています。マルチチャネルアナログ コンパレータ (mcacmp0) を使用して、800mV 未満、1.216V を上回る電圧を検出できます。1.216V を超える電圧が検出された場合、KEEP が Low に設定されたまま、カウンタはカウント ダウンして、電圧が 1.216V スレッショルドを下回るまでデューティサイクルを減少させます。800mV 未満の電圧が検出された場合、KEEP は Low に設定され、UP は High に設定されて、カウンタがデューティサイクルを増加させます。図 8 に、この回路のシミュレーションを示します。PWM 出力は青色で、入力電圧は黄色で示されています。

図 7. 過電圧および低電圧 PWM 回路

図 8. PWM の回路シミュレーション

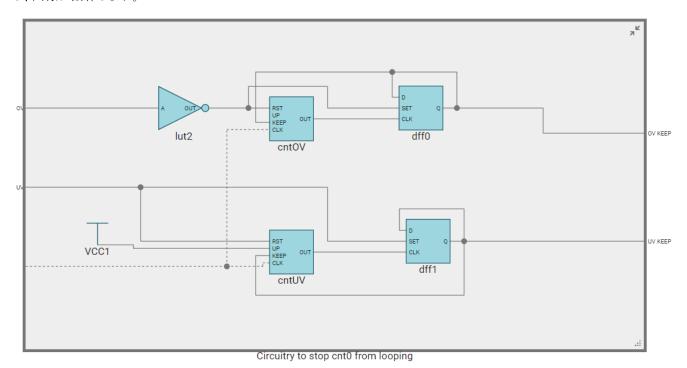

以前に Counter FSM 機能で説明したように、カウンタ モジュールは 0 または 255 までカウント ダウンしてから、カウント値をリセットします。そのため、最小および最大のデューティサイクルを維持し、カウンタがループしないようにするため、0 または 255 の値に近くなって cnt0 を一時停止する回路を追加する必要があります。この回路を図 9 に示します。cntOV は 125 (cnt0 より 3 つ小さい) の制御データで構成され、cntUV は 131 (cnt0 より 3 つ高い) の制御データで構成されます。過電圧状態に移行すると、cnt0 と cntOV はどちらもリセットされ、カウントダウンを開始します。制御データが低くなるため、cnto より先に cntOV は 0 にカウントされ、対応する出力パルスは dff0 によってラッチされ、KEEP を high に設定し、電流カウント値を cnt0 保持するために使用されます。低電圧状態の場合、cntUV は、ダウンではなくカウントアップし、同様に動作します。

図 9. PWM ループ防止回路

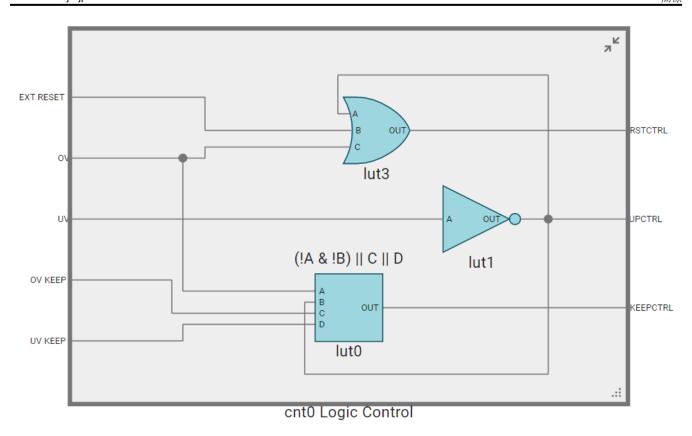

*cnt0* の前に *cntOV* および *cntUV* のカウントを完了させ維持するには、過電圧または低電圧状態に遷移したときに *cnt0* もリセットする必要があります。これは、いずれかの状態に遷移するとデューティ サイクルが 50% にリセットされることを意味します。*cnt0* へのリセットおよび FSM 信号を制御するロジック図 10 をに示します。

図 10. PWM カウンタ FSM 制御回路

#### 追加の検討事項

図8に、PWM 出力が最大および最小デューティサイクル値に迅速に到達することを示します。カウンタクロックを PWM クロックより遅く設定すると、デューティサイクルがより緩やかに変化することができます。ただし、クロックのジッタやスキューが原因で、PWM 出力に時折グリッチが発生する可能性があります。

また、PWM デューティサイクルは、I2C または SPI レシーバを使用して制御し、適切なカウンタ FSM のデータ レジスタ に必要な制御データを書き込むこともできます。

## 結論

PWM モジュールを使用すると、TPLD はデューティサイクルがさまざまに異なる方形波を生成できます。複数の異なるロジック機能とアナログ センサを内蔵し、TPLD はリアルタイム PWM の生成と制御を実施できる統合型設計を実現します。

TI のプログラマブル ロジック デバイスのポートフォリオについて詳しく知る

## 商標

すべての商標は、それぞれの所有者に帰属します。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、 テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、 テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。 テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、 テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、 テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、 テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。 テキサス・インスツルメンツがこれらのリソ 一スを提供することは、適用される テキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、 テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated