*Application Note***TPS65219 PMIC による AM62x への電力供給****概要**

このアプリケーション・ノートでは、AM62 Sitara™ プロセッサおよび主要なペリフェラルへの電力供給を行う、TPS65219 電力管理集積回路 (PMIC) とその機能セットすべてについて説明します。この資料で説明している電力供給ネットワーク (PDN) は、テキサス・インスツルメンツの AM62x Sitara プロセッサに電力を供給する産業用または車載アプリケーションに TPS65219 電力管理集積回路 (PMIC) を組み込むためのガイドとして使用できます。注文可能な型番の比較表には、AM62x のさまざまな使用事例をサポートする、工場出荷時にプログラム済みの TPS65219 のバリエーションの構成が詳細に記載されています。設計プロセスを支援するために、電源マップの例が提供されます。ご質問や技術サポートについては、[パワー・マネージメント E2E フォーラムをご利用ください](#)。

**目次**

|                                            |    |

|--------------------------------------------|----|

| 1はじめに.....                                 | 3  |

| 2 TPS65219 の概要.....                        | 3  |

| 2.1 TPS65219 機能ブロック図.....                  | 5  |

| 3 TPS65219 のバリエーション.....                   | 6  |

| 3.1 産業用アプリケーション向け TPS65219 NVM.....        | 6  |

| 3.2 車載アプリケーション用 TPS65219-Q1 NVM.....       | 7  |

| 4 TPS6521905 ユーザー プログラマブル NVM .....        | 9  |

| 5 AM62x のコア電圧の選択.....                      | 10 |

| 6 VSYS 電圧ランプ.....                          | 11 |

| 7 パワー ブロック図.....                           | 13 |

| 7.1 AM62x に電力を供給する TPS6521901 .....        | 13 |

| 7.2 AM62x に電力を供給する TPS6521902 .....        | 15 |

| 7.3 AM62x に電源を供給する TPS6521903 .....        | 17 |

| 7.4 AM62x に電力を供給する TPS6521904 .....        | 19 |

| 7.5 AM62x に電力を供給する TPS6521907 .....        | 21 |

| 7.6 AM62x に電力を供給する TPS6521908 .....        | 22 |

| 7.7 AM62x-Q1 に電力を供給する TPS6521920W-Q1 ..... | 25 |

| 7.8 AM62x-Q1 に電力を供給する TPS6521922W-Q1.....  | 27 |

| 7.9 AM62x-Q1 に電力を供給する TPS6521923W-Q1.....  | 29 |

| 8まとめ.....                                  | 31 |

| 9参考資料.....                                 | 31 |

| 10改訂履歴.....                                | 31 |

**図の一覧**

|                                           |    |

|-------------------------------------------|----|

| 図 2-1. TPS65219 機能ブロック図.....              | 5  |

| 図 4-1. 供給オプション.....                       | 9  |

| 図 6-1. FSD がイネーブルの場合の VSYS スロー ランプ .....  | 11 |

| 図 6-2. FSD がディセーブルの場合の VSYS スロー ランプ ..... | 12 |

| 図 7-1. AM62 に電力を供給する TPS6521901.....      | 14 |

| 図 7-2. AM62 に電力を供給する TPS6521902.....      | 16 |

| 図 7-3. AM62x に電力を供給する TPS6521903.....     | 18 |

| 図 7-4. AM62x に電力を供給する TPS6521904.....     | 20 |

| 図 7-5. AM62 に電力を供給する TPS6521907 .....     | 22 |

| 図 7-6. AM62 に電力を供給する TPS6521908 .....     | 24 |

| 図 7-7. AM62x に電力を供給する TPS6521920W-Q1..... | 26 |

|                                           |    |

|-------------------------------------------|----|

| 図 7-8. AM62x に電力を供給する TPS6521922W-Q1..... | 28 |

| 図 7-9. AM62x に電力を供給する TPS6521923W-Q1..... | 30 |

## 表の一覧

|                                                  |    |

|--------------------------------------------------|----|

| 表 2-1. TPS65219 の電力リソース.....                     | 3  |

| 表 2-2. TPS65219 と TPS65219-Q1 の比較.....           | 4  |

| 表 3-1. AM62x 産業用アプリケーション向け TPS65219 NVM.....     | 6  |

| 表 3-2. AM62x-Q1 車載アプリケーション用 TPS65219-Q1 NVM..... | 7  |

| 表 4-1. TPS6521905 プログラミング リソース.....              | 9  |

| 表 5-1. コア電圧の選択.....                              | 10 |

## 商標

Sitara™ is a trademark of Texas Instruments.

Arm® is a registered trademark of Arm Ltd.

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

TPS65219 PMIC は、AM62x プロセッサおよび主要なペリフェラルへの電力供給用に設計された、低コストで省スペースの実装です。TPS65219 はフレキシブルなマッピング機能を備えており、AM62x のさまざまな使用事例をサポートする、工場出荷時にプログラム済みの注文可能な型番が複数提供されます。AM62x SK EVM により、ハードウェア実装をただちに利用できます。AM62x は、Sitara™ Arm® プロセッサ ファミリーの最新製品であり、組込み 3D グラフィックス アクセラレーション、デュアル ディスプレイインターフェイス、広範なペリフェラルおよびネットワーク オプションをサポートする機能を搭載しています。このプロセッサは、ヒューマン マシン インターフェイス (HMI) から 3D ポイント クラウドまで各種アプリケーションで使用できるように、強力なコンピューティング能力を提供すると同時に、ポータブル システムや電力に制約のあるシステム向けに設計されたパワー マネージメント機能をサポートします。AM62x プロセッサには、少なくとも 7 つのメインレール用の電力が必要です。これには、コア電源 (VDD\_CORE)、RAM 電源 (VDDR\_CORE)、DDR PHY IO 電源 (VDDS\_DDR)、1.8V VDDA アナログ電源、1.8V または 3.3V IO 電源、アナログ IO レール (VDDSHV) が含まれます。AM62x ファミリーなどのプロセッサに電力を供給するには、十分な電流ヘッドルーム、厳格な過渡要件、電源オン / 電源オフ シーケンス用に完全に制御可能な多数のレールなどの要件を満たす必要があります。ユーザーズ ガイドやアプリケーション レポート、その他の参考資料の間に矛盾がある場合、データシートの仕様を最終的な情報源としてください。

## 2 TPS65219 の概要

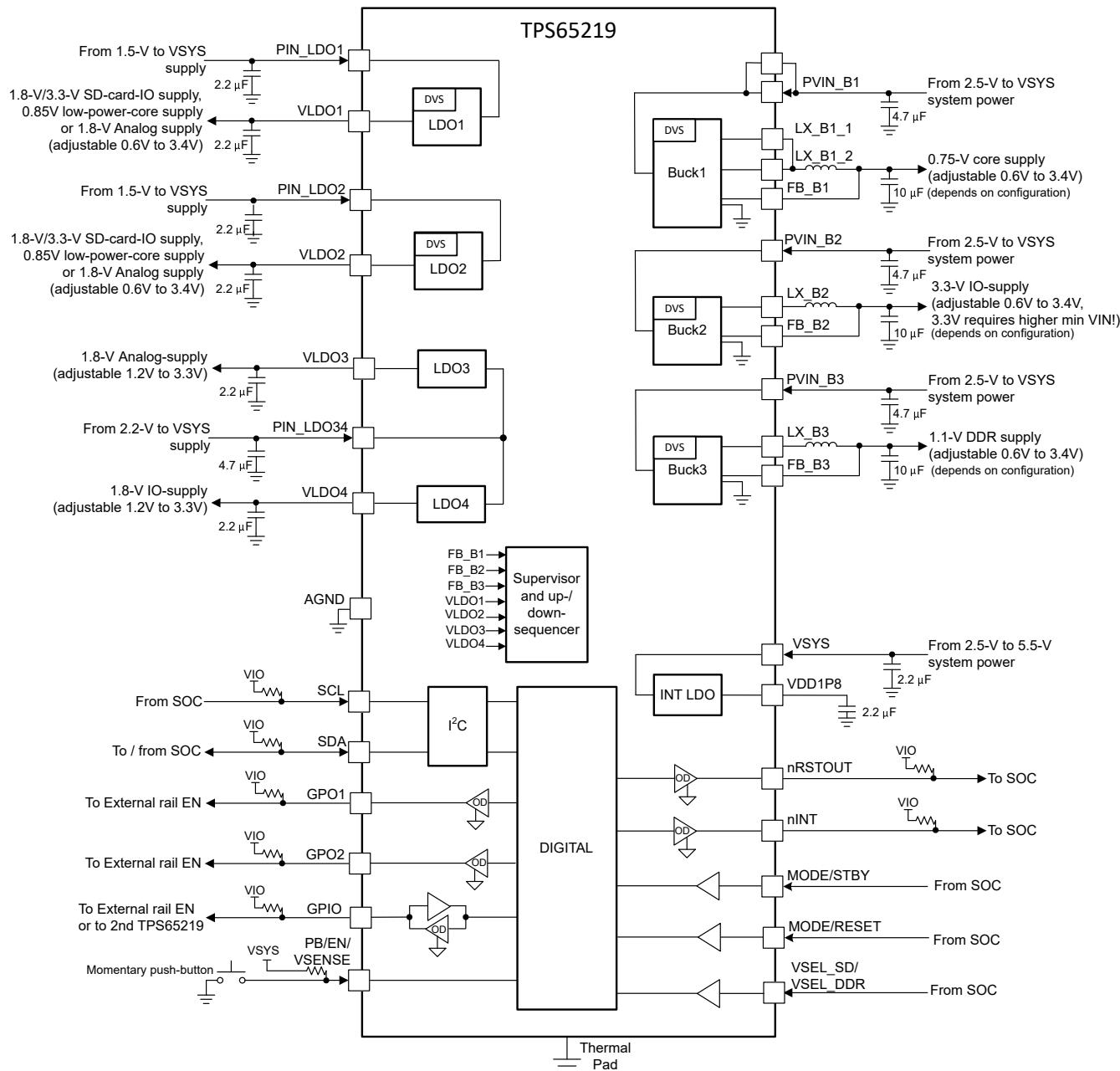

TPS65219 PMIC は、7 個のレギュレータ、3 個の降圧レギュレータ、4 個の低ドロップアウト レギュレータ (LDO) を内蔵しています。降圧コンバータは、Buck1 で最大 3.5A、その他の降圧レギュレータでそれぞれ 2A をサポートします。LDO1 および LDO2 (2×400mA) は、ロード スイッチとして、動的な SD カード電圧をサポートするバイパス モードに構成することができます。LDO3 および LDO4 (2×300mA) は、ロード スイッチとして構成できます。この PMIC は VIN 範囲が 2.5V～5.5V と広く、3.3V または 5V の一般的なシステム電圧をサポートします。表 2-1 に、各アナログ リソースの電圧および電流能力の概要を示します。I2C インターフェイス、3 本の GPIO ピン、3 本のマルチファンクション ピンを備えた TPS65219 PMIC は、AM62x SoC や他の多くの SoC に電力を供給できる完全な電源パッケージを提供します。

この PMIC には 2 つのバージョンがあり、TPS65219 は -40°C～+105°C の周囲温度範囲の産業用アプリケーションをサポートし、TPS65219-Q1 は -40°C～+125°C の拡張温度範囲を必要とする車載アプリケーションをサポートしています。表 2-2 に、産業用と車載用の PMIC バリエーションの違いを示します。

表 2-1. TPS65219 の電力リソース

|       | 入力電圧                                            | 出力電圧                                | 電流能力  | 備考                                                                                                                                                          |

|-------|-------------------------------------------------|-------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUCK1 | 2.5V ~ 5.5V                                     | 0.6V ~ 3.4V                         | 3.5A  |                                                                                                                                                             |

| BUCK2 | 2.5V ~ 5.5V                                     | 0.6V ~ 3.4V                         | 2A    |                                                                                                                                                             |

| BUCK3 | 2.5V ~ 5.5V                                     | 0.6V ~ 3.4V                         | 2A    | <ul style="list-style-type: none"> <li>2.3MHz のスイッチング周波数</li> <li>ダイナミック電圧スケーリング</li> <li>電源シーケンスとデフォルト電圧をプログラム可能。</li> <li>低電圧監視用の電圧スレーブバイザを内蔵。</li> </ul> |

| LDO1  | 1.5V～5.5V (LDO、ロード<br>スイッチ)<br>1.5V～3.4V (バイパス) | 0.6V～3.4V (LDO)<br>1.5V～3.4V (バイパス) | 400mA | <ul style="list-style-type: none"> <li>電源シーケンスとデフォルト電圧をプログラム可能。</li> <li>ロード スイッチとして、バイパス モードに構成することも可能。</li> <li>低電圧監視用の電圧スレーブバイザを内蔵</li> </ul>            |

| LDO2  | 1.5V～5.5V (LDO、ロード<br>スイッチ)<br>1.5V～3.4V (バイパス) | 0.6V～3.4V (LDO)<br>1.5V～3.4V (バイパス) | 400mA |                                                                                                                                                             |

| LDO3  | 2.2V ~ 5.5V                                     | 1.2V ~ 3.3V                         | 300mA | <ul style="list-style-type: none"> <li>電源シーケンスとデフォルト電圧をプログラム可能。</li> <li>ロード スイッチとして構成可能</li> <li>低電圧監視用の電圧スレーブバイザを内蔵</li> </ul>                            |

| LDO4  | 2.2V ~ 5.5V                                     | 1.2V ~ 3.3V                         | 300mA |                                                                                                                                                             |

**表 2-2. TPS65219 と TPS65219-Q1 の比較**

| 機能            | TPS65219<br>(産業用)                                                           | TPS65219-Q1<br>(車載用)                                                                                                |

|---------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| ターゲット プロセッサ   | AM62x<br>13mm × 13mm、0.5mm ピッチ、425 ピン FCCSP<br>BGA (ALW)                    | AM62x-Q1<br>17.2mm × 17.2mm、0.8mm ピッチ、441 ピン FCBGA<br>(AMC)                                                         |

| スイッチング周波数     | 最高 2.3MHz<br>擬似固定周波数<br>• 自動 PFM<br>• 強制 PWM                                | 最大 2.3MHz デバイスの構成に応じて、疑似固定周波数または固定周波数のいずれかに対応。<br>擬似固定周波数<br>• 自動 PFM<br>• 強制 PWM<br><br>固定周波数<br>• スペクトラム拡散機能を利用可能 |

| 自由気流での動作温度 TA | 40°C~105°C                                                                  | 40°C~125°C                                                                                                          |

| 動作接合部温度 TJ    | -40°C~125°C                                                                 | -40°C~150°C                                                                                                         |

| 機能安全対応        | なし                                                                          | 機能安全対応 (テキサス・インストゥルメンツの品質管理プロセス、機能安全 FIT 率の計算、故障モード分布が利用可能)                                                         |

| パッケージ         | 2 パッケージ オプション<br>• 4mm × 4mm、0.4mm ピッチの VQFN<br>• 5mm × 5mm、0.5mm ピッチの VQFN | 1 パッケージ オプション<br>• 5mm × 5mm、0.5mm ピッチの VQFN<br>• (ウェッタブル フランク)                                                     |

## 2.1 TPS65219 機能ブロック図

図 2-1. TPS65219 機能ブロック図

### 3 TPS65219 のバリエーション

TPS65219 PMIC には、AM62x プロセッサおよびペリフェラルに電力を供給するために、独自のレジスタ設定を工場出荷時にプログラムした複数のバリエーションがあります。適切な注文可能な型番 (OPN) の選択は、アプリケーションの使用事例、特に入力電源、メモリの種類、コア電圧によって異なります。セクション 3.1 は、産業用アプリケーション向けに現在利用可能な注文可能な型番の主な NVM 設定を比較したものです。同様に、車載用アプリケーションをサポートするために現在利用可能な OPN の主な NVM 設定を セクション 3.2 に示します。これらの表には、テクニカル・リファレンス・マニュアルや AM62x スタータ・キットなど、新規設計をサポートするために利用可能なリソースも掲載されています。詳細な情報については、デバイス・データシートを参照してください。

#### 注

注文可能な型番には、デフォルトのレジスタ設定を記載したテクニカル・リファレンス・マニュアル (TRM) があります。NVM レジスタ設定は、データシートのレジスタ・マップの RESET 列に「X」で示されています。事前プログラミング済みの注文可能な型番 (OPN) がいずれもアプリケーションの要件を満たしていない場合、カスタム NVM のオプションについては セクション 4 を参照してください。

#### 3.1 産業用アプリケーション向け TPS65219 NVM

表 3-1. AM62x 産業用アプリケーション向け TPS65219 NVM

|                          |                         | TPS6521901                                        | TPS6521902                                        | TPS6521903                                        | TPS6521904                                        | TPS6521907                                        | TPS6521908                                        |

|--------------------------|-------------------------|---------------------------------------------------|---------------------------------------------------|---------------------------------------------------|---------------------------------------------------|---------------------------------------------------|---------------------------------------------------|

| 使用事例                     | Vsys                    | 5V                                                | 3.3V                                              | 3.3V                                              | 3.3V                                              | 5V                                                | 3.3V                                              |

|                          | VDD_CORE <sup>(3)</sup> | 0.75V                                             | 0.75V                                             | 0.75V                                             | 0.85V                                             | 0.85V                                             | 0.85V                                             |

|                          | 外部メモリ                   | DDR4                                              | LPDDR4                                            | DDR4                                              | DDR4                                              | DDR4                                              | LPDDR4                                            |

| テクニカル リファレンス マニュアル (TRM) | SLVUCH3                 | SLVUCLO                                           | SLVUCJ2                                           | SLVUCL1                                           | SLVUCL9                                           | SLVUCMO                                           |                                                   |

| ハードウェア <sup>(2)</sup>    | TPS65219EVM             |                                                   | AM62B PMIC 搭載、スタータ キット                            | AM62B PMIC 搭載、スタータ キット                            |                                                   |                                                   |                                                   |

| BUCK1                    | Vout (出力電圧)             | 0.75V                                             | 0.75V                                             | 0.75V                                             | 0.85V                                             | 0.85V                                             | 0.85V                                             |

|                          | 帯域幅                     | 高帯域                                               | 高帯域                                               | 高帯域                                               | 高帯域                                               | 高帯域                                               | 高帯域                                               |

| BUCK2                    | Vout (出力電圧)             | 3.3V                                              | 1.8V                                              | 1.8V                                              | 1.8V                                              | 3.3V                                              | 1.8V                                              |

|                          | 帯域幅                     | 高帯域                                               | 高帯域                                               | 高帯域                                               | 高帯域                                               | 高帯域                                               | 高帯域                                               |

| BUCK3                    | Vout (出力電圧)             | 1.2V                                              | 1.1V                                              | 1.2V                                              | 1.2V                                              | 1.2V                                              | 1.1V                                              |

|                          | 帯域幅                     | 高帯域                                               | 高帯域                                               | 高帯域                                               | 高帯域                                               | 高帯域                                               | 高帯域                                               |

| LDO1                     | Vout (出力電圧)             | 3.3V/1.8V (ハイパス)                                  |

| LDO2                     | Vout (出力電圧)             | 0.85V                                             | 0.85V                                             | 0.85V                                             | 1.8V                                              | 1.8V                                              | 1.2V (ディセーブル時)                                    |

| LDO3                     | Vout (出力電圧)             | 1.8V                                              | 1.8V                                              | 1.8V                                              | 1.8V                                              | 1.8V                                              | 1.8V                                              |

| LDO4                     | Vout (出力電圧)             | 2.5V                                              | 2.5V                                              | 2.5V                                              | 2.5V                                              | 2.5V                                              | 2.5V                                              |

| GPIO                     | GPO1                    | イネーブル                                             | ディセーブル                                            | ディセーブル                                            | ディセーブル                                            | イネーブル                                             | ディセーブル                                            |

|                          | GPO2                    | ディセーブル                                            | イネーブル                                             | イネーブル                                             | イネーブル                                             | ディセーブル                                            | イネーブル                                             |

|                          | GPIO                    | ディセーブル                                            | ディセーブル                                            | ディセーブル                                            | ディセーブル                                            | ディセーブル                                            | ディセーブル                                            |

| モード / リセット               | 設定                      | ウォームリセット                                          | ウォームリセット                                          | ウォームリセット                                          | ウォームリセット                                          | ウォームリセット                                          | ウォームリセット                                          |

|                          | 極性                      | High = 通常動作<br>Low = ウォームリセット                     |

| MODE/SBY                 | 設定                      | モードおよびスタンバイ                                       | モードおよびスタンバイ                                       | モードおよびスタンバイ                                       | モードおよびスタンバイ                                       | モードおよびスタンバイ                                       | モードおよびスタンバイ                                       |

|                          | 極性                      | High = アクティブ状態および強制 PWM<br>Low = スタンバイ状態および自動 PFM |

**表 3-1. AM62x 産業用アプリケーション向け TPS65219 NVM (続き)**

|                   |              | TPS6521901                     | TPS6521902                     | TPS6521903                     | TPS6521904                     | TPS6521907                     | TPS6521908                     |

|-------------------|--------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|

| 使用事例              | Vsys         | 5V                             | 3.3V                           | 3.3V                           | 3.3V                           | 5V                             | 3.3V                           |

|                   | VDD_CORE (3) | 0.75V                          | 0.75V                          | 0.75V                          | 0.85V                          | 0.85V                          | 0.85V                          |

|                   | 外部メモリ        | DDR4                           | LPDDR4                         | DDR4                           | DDR4                           | DDR4                           | LPDDR4                         |

| VSEL_SD/DDR       | 設定           | SD                             | SD                             | SD                             | SD                             | SD                             | SD                             |

|                   | レール          | LDO1                           | LDO1                           | LDO1                           | LDO1                           | LDO1                           | LDO1                           |

|                   | 極性           | High = LDO1_VSET<br>Low = 1.8V |

| EN/PB/VSENSE ピン構成 |              | イネーブル                          | プッシュボタン                        | プッシュボタン                        | プッシュボタン                        | イネーブル                          | イネーブル                          |

| 最初の電源検出 (1)       |              | イネーブル                          | イネーブル                          | イネーブル                          | イネーブル                          | イネーブル                          | イネーブル                          |

- (1) 最初の電源検出 (FSD) により、EN, PB, VSENSE ピンが OFF\_REQ ステータスであっても、電源電圧が印加された直後に電源オンが可能になります。FSD は、EN, PB、または VSENSE などの任意のオノリクエスト構成と組み合わせて使用できます。最初の電源投入時に、EN, PB、VSENSE ピンは、有効なオノリクエストがあるかのように見なされます。

- (2) AM62 スタータキットには、デフォルトで TPS6521904 PMIC が搭載されており、VDD\_CORE = 0.85V をサポートしています。VDD\_CORE = 0.75V をサポートするには、以下の変更が必要です。TPS6521904 PMIC の TPS6521903 への交換と R699 のアンインストール、R123 の取り付けが必要です。

- (3) 2 つの VDD\_CORE 動作ポイントの比較については「セクション 5」を参照してください。

### 3.2 車載アプリケーション用 TPS65219-Q1 NVM

**表 3-2. AM62x-Q1 車載アプリケーション用 TPS65219-Q1 NVM**

|                         |             | TPS6521920W-Q1                     | TPS6521922W-Q1                | TPS6521923W-Q1                  |

|-------------------------|-------------|------------------------------------|-------------------------------|---------------------------------|

| 使用事例                    | Vsys        | 3.3V                               | 3.3V                          | 5V                              |

|                         | VDD_CORE(2) | 0.75V                              | 0.85V                         | 0.75V                           |

|                         | 外部メモリ       | LPDDR4                             | LPDDR4                        | LPDDR4                          |

| テクニカル リファレンスマニュアル (TRM) |             | SLVUCN8                            | SLVUDE1                       | SLVUCM6                         |

| ハードウェア                  |             | 低消費電力 Sitara プロセッサ向け AM62x スタータキット |                               |                                 |

| BUCK1                   | Vout (出力電圧) | 0.75V                              | 0.85V                         | 0.75V                           |

|                         | 帯域幅         | 高帯域                                | 高帯域                           | 高帯域                             |

| BUCK2                   | Vout (出力電圧) | 1.8V                               | 1.8V                          | 3.3V                            |

|                         | 帯域幅         | 高帯域                                | 高帯域                           | 低帯域幅                            |

| BUCK3                   | Vout (出力電圧) | 1.1V                               | 1.1V                          | 1.1V                            |

|                         | 帯域幅         | 高帯域                                | 高帯域                           | 低帯域幅                            |

| LDO1                    | Vout (出力電圧) | 3.3V/1.8V (バイパス)                   | 3.3V/1.8V (バイパス)              | ディセーブル                          |

| LDO2                    | Vout (出力電圧) | 0.85V                              | 0.85V                         | 0.85V                           |

| LDO3                    | Vout (出力電圧) | 1.8V                               | 1.8V                          | 1.8V                            |

| LDO4                    | Vout (出力電圧) | 1.2V                               | 1.2V                          | ディセーブル                          |

| GPIO                    | GPO1        | ディセーブル                             | ディセーブル                        | イネーブル                           |

|                         | GPO2        | イネーブル                              | イネーブル                         | ディセーブル                          |

|                         | GPIO        | ディセーブル                             | ディセーブル                        | ディセーブル                          |

| モード/リセット                | 設定          | ウォームリセット                           | ウォームリセット                      | ウォームリセット                        |

|                         | 極性          | High = 通常動作<br>Low = ウォームリセット      | High = 通常動作<br>Low = ウォームリセット | High = 通常動作<br>Low = ウォームリセット   |

| MODE/SBY                | 設定          | モード                                | モード                           | スタンバイ                           |

|                         | 極性          | High = 強制 PWM<br>Low = 自動 PFM      | High = 強制 PWM<br>Low = 自動 PFM | High = スタンバイ状態<br>Low = アクティブ状態 |

**表 3-2. AM62x-Q1 車載アプリケーション用 TPS65219-Q1 NVM (続き)**

|                        |                         | TPS6521920W-Q1                 | TPS6521922W-Q1                 | TPS6521923W-Q1                 |

|------------------------|-------------------------|--------------------------------|--------------------------------|--------------------------------|

| 使用事例                   | Vsys                    | 3.3V                           | 3.3V                           | 5V                             |

|                        | VDD_CORE <sup>(2)</sup> | 0.75V                          | 0.85V                          | 0.75V                          |

|                        | 外部メモリ                   | LPDDR4                         | LPDDR4                         | LPDDR4                         |

| VSEL_SD/DDR            | 設定                      | SD                             | SD                             | SD                             |

|                        | レール                     | LDO1                           | LDO1                           | LDO1                           |

|                        | 極性                      | High = LDO1_VSET<br>Low = 1.8V | High = LDO1_VSET<br>Low = 1.8V | High = 1.8V<br>Low = LDO1_VSET |

| EN/PB/VSENSE ピン構成      |                         | イネーブル                          | イネーブル                          | イネーブル                          |

| 最初の電源検出 <sup>(1)</sup> |                         | イネーブル                          | イネーブル                          | ディセーブル                         |

- (1) 最初の電源検出 (FSD) により、EN、PB、VSENSE ピンが OFF\_REQ ステータスであっても、電源電圧が印加された直後に電源オンが可能になります。FSD は、EN、PB、または VSENSE などの任意のオノリクエスト構成と組み合わせて使用できます。最初の電源投入時に、EN、PB、VSENSE ピンは、有効なオノリクエストがあるかのように見なされます。

- (2) 2 つの VDD\_CORE 動作ポイントの比較については「セクション 5」を参照してください。

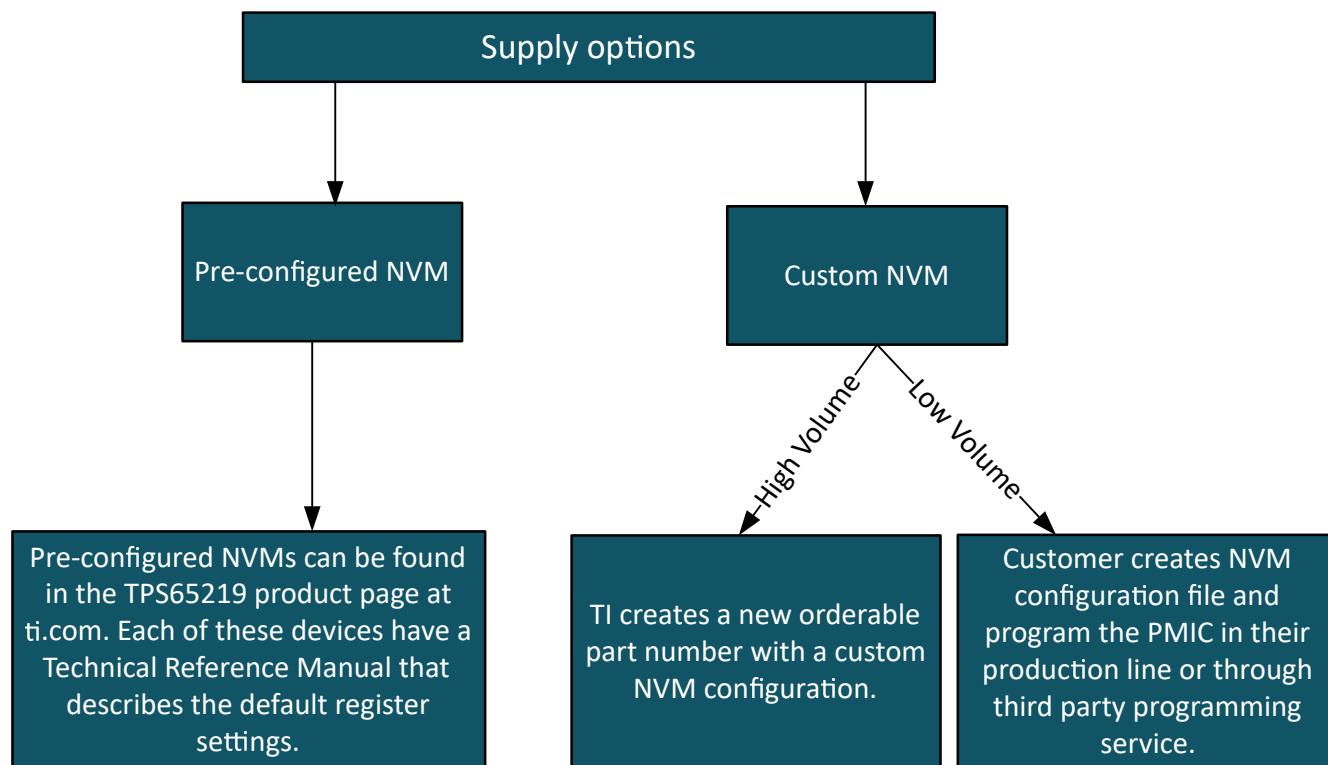

## 4 TPS6521905 ユーザー プログラマブル NVM

図 4-1 に、利用可能な電源オプションを示します。このアプリケーションノートでは、さまざまな使用事例で AM62x に電力を供給するために使用できる、事前設定済みの NVM について説明しています。このドキュメントに記載されている注文可能な型番 (OPN) がどれもアプリケーションの要件を満たしていない場合や、デフォルト設定に小さな変更が必要な場合は、カスタム NVM が必要です。大量生産向けに、テキサス・インスツルメンツではカスタム NVM 設定で注文可能な新しい型番を作成しています。少量生産の場合、お客様は 表 4-1 に記載されているリソースを使用し、生産ラインで、またはサード パーティーのプログラミング サービスを通じて PMIC をプログラムできます。

図 4-1. 供給オプション

表 4-1. TPS6521905 プログラミング リソース

| 関連資料                       | リンク                                                               |

|----------------------------|-------------------------------------------------------------------|

| プログラミング ガイド                | 『TPS65219 不揮発性メモリ (NVM) プログラミング ガイド』                              |

| グラフィカル ユーザー インターフェイス (GUI) | 『TPS65219 グラフィカル ユーザー インターフェイス』                                   |

| ソケット付き EVM                 | 『TPS65219 不揮発性メモリ (NVM) プログラミング ボード』                              |

| TPS6521905 データシート          | 『3 個の降圧 DC/DC コンバータと 4 個の LDO を搭載した、ユーザー プログラマブルな電力管理集積回路 (PMIC)』 |

## 5 AM62x のコア電圧の選択

VDD\_CORE は、AM62x プロセッサのコア電源です。このドメインには 2 つの動作ポイントがあります。表 5-1 は、周波数、消費電力、パワー マッピング、シーケンシング要件の観点から、0.75V と 0.85V の動作ポイントを比較したものです。AM62x はダイナミック電圧スケーリングをサポートしていないため、0.75V と 0.85V の動作ポイントに異なる TPS65219 の注文可能な型番を使用します。

**表 5-1. コア電圧の選択**

| VDD_CORE                     |                                                                                                                                                                                                                         |                                                                                                                                                        |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              | <b>0.75V</b><br>(フレキシブル コア)                                                                                                                                                                                             | <b>0.85V</b><br>(最小 BOM (部品表) オプション)                                                                                                                   |

| A53SS (Cortex-A53x) の最大動作周波数 | 最高 1.25GHz                                                                                                                                                                                                              | 最高 1.4GHz                                                                                                                                              |

| 消費電力                         | 低消費電力 VDD_CORE <sup>(1)</sup>                                                                                                                                                                                           | 高消費電力 <sup>(1)</sup>                                                                                                                                   |

| PMIC とプロセッサのパワー マッピング        | 2 つの PMIC レールが必要です。1 つは 0.75V で VDD_CORE に電力を供給し、もう 1 つは 0.85V で VDDR_CORE に電力を供給する PMIC レールです。<br>Buck1 は、0.75V を出力するよう構成されている場合、VDD_CORE に電力を供給するために使用されます。LDO2 は、0.85V を出力するよう構成されている場合、VDDR_CORE に電力を供給するために使用されます。 | 最小 BOM (部品表) オプション。<br>同じ PMIC レールから VDD_CORE (コア電源) と VDDR_CORE (RAM 電源) への電力供給を可能にします。<br>Buck1 は、0.85V を出力するよう構成されている場合、両方のコア レールに電力を供給するために使用されます。 |

| シーケンシング                      | 電源オン / 電源オフ シーケンス要件<br>VDD_CORE は、VDDR_CORE よりも前に立ち上がる必要があります。<br>VDD_CORE は、VDDR_CORE の後に立ち下がる必要があります。                                                                                                                 | コア電源はどちらも同じ PMIC レールから供給されるため、シーケンシング要件はありません。                                                                                                         |

(1) プロセッサの消費電力の詳細については、アプリケーション ノート『AM62x 電力推定ツール』を参照してください。

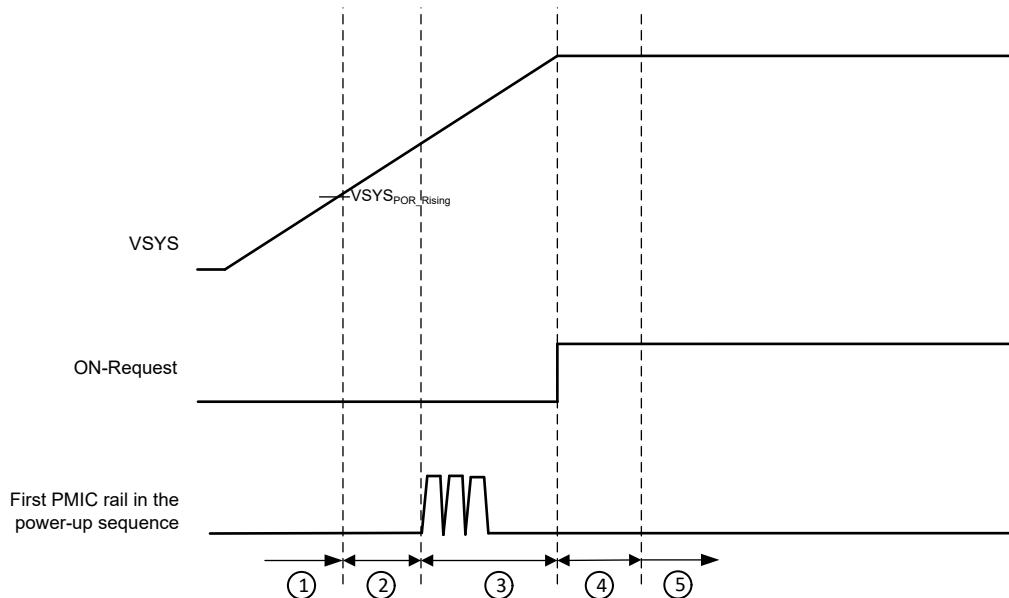

## 6 VSYS 電圧ランプ

TPS65219 の電源オンシーケンスは、以下の主なステップでゲートされます。VSYS の電圧が POR\_Rising スレッショルドを上回り、PMIC が NVM の内容をレジスタマップにロードした後、オンの要求を待機してから電源オンシーケンスを実行します。最初のオンリクエストは PU\_ON\_FSD レジスタフィールドの最初の電源検出機能 (FSD) をイネーブルにすることでバイパスできます。PU\_ON\_FSD=0x1 の場合、NVM 設定がレジスタマップにロードされた後、PMIC はオンリクエストを待たずに電源オンシーケンスの実行を開始します。このシナリオでは、お客様は PMIC が電源オンシーケンスの実行を開始する前に VSYS を供給するプリレギュレータが安定した出力電圧に達していることを確認する必要があります。VSYS の電圧は、VSYS が POR\_threshold を上回ってから約 2.3ms 以内に目標の Vout に達する必要があります。

### 注

FSD がイネーブル (PU\_ON\_FSD=0x1) で VSYS のランプが遅い場合、PMIC は要求されている入力電圧から出力電圧へのヘッドルームを確保せずに、最初のレールをイネーブルしようとします。この条件が成立すると PMIC に障害が発生します。

図 6-1 に FSD がイネーブルで VSYS のランプが遅い場合の例を示します。

図 6-1. FSD がイネーブルの場合の VSYS スロー ランプ

- **ステップ 1:** VSYS が POR\_Rising スレッショルドに達します。

- **ステップ 2:** NVM 設定は約 2.3ms 後にレジスタにロードされます。

- **ステップ 3:** FSD がイネーブルになっているため PMIC は電源オンシーケンスの実行を開始しますが、VSYS の電圧は依然として低すぎ、入力から出力へのヘッドルームを満たしていません。電源オンシーケンスの最初の PMIC レールには、最初の電源オンを表す 3 つの電圧ピークと、再試行カウント (MASK\_RETRY\_COUNT) に設定された 2 つの試行が示されています。

- **ステップ 4:** イネーブルピンが High になり、ピンのデグリッチが有効になります。

- **ステップ 5:** ステップ 3 で電源オンを試みた後、デバイスは初期化状態のままであるため、PMIC は電源オンシーケンスを実行できません。PMIC を初期化状態から復帰させるには、より高速なランプで VSYS のパワー サイクルを実行する必要があります。

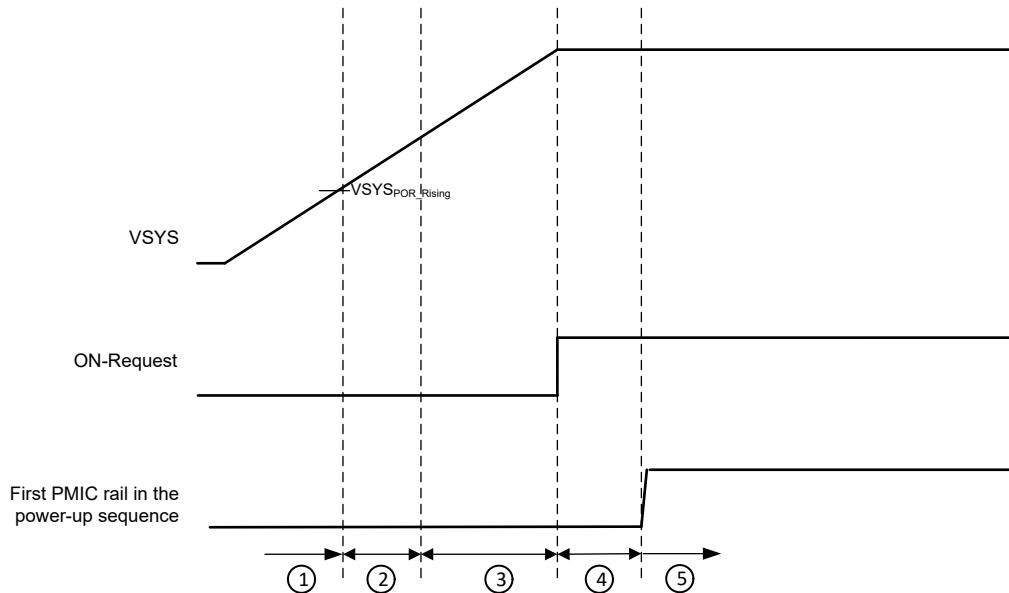

図 6-2 に、FSD がディセーブルで VSYS のランプが低速の例を示します。

- **ステップ 1:** VSYS が POR\_Rising スレッショルドに達します。

- **ステップ 2:** NVM 設定は約 2.3ms 後にレジスタにロードされます。

- **ステップ 3:** FSD がディセーブルのため、PMIC は電源オン シーケンスを実行するためのオンリクエストを待ちます。

- **ステップ 4:** イネーブル ピンが High になり、ピンのデグリッチが有効になります。

- **ステップ 5:** PMIC は、最初のスロットに割り当てられたレールから、電源オン シーケンスの実行を開始します。

図 6-2. FSD がディセーブルの場合の VSYS スロー ランプ

## 7 パワー ブロック図

AM62 プロセッサおよびペリフェラルに電力を供給する目的で TPS65219 を設計する際には、いくつかの検討事項を考慮に入れる必要があります。

- アプリケーションで LPDDR4 または DDR4 メモリを使用するか？

- SD カードをサポートする必要はあるか？

- システムの電源電圧は？

- 完全に制御されたシーケンスを必要とする外部ディスクリート IC はあるか？

- システム アプリケーションで高い集積度と少ない消費電力のどちらを優先するか？

これらの問い合わせはそれぞれ、電源ブロック図の設計、構成、セットアップなどに影響を与えるものであり、非常に堅牢な電源実装を設計するために重要です。以下のセクションでは、さまざまなアプリケーション要件で TPS65219 PMIC から AM62x プロセッサに電力を供給する方法について説明します。

このアプリケーションノートで説明されている TPS65219 のすべてのバリエーションで、SD カードのデュアル電圧 I/O (3.3V および 1.8V) に給電するバイパスとして LDO1 を設定しています。最初に SD IO を 3.3V に設定するため、ロジックの HIGH のデフォルト値と外部プルアップを持つプロセッサ GPIO 制御信号を使用します。電源オンシーケンスの後、プロセッサは SD 仕様に基づき高速カード動作に必要な 1.8V レベルを選択するために GPIO 信号を LOW に設定できます。このバイパス構成により、SD カード動作からのブート時に I2C 通信を確立しなくとも、LDO1 電圧を 3.3V～1.8V の範囲で制御可能となります。LDO1 のバイパス構成では、その入力電源ピン (PVIN\_LDO1) を 3.3V に接続する必要があります。

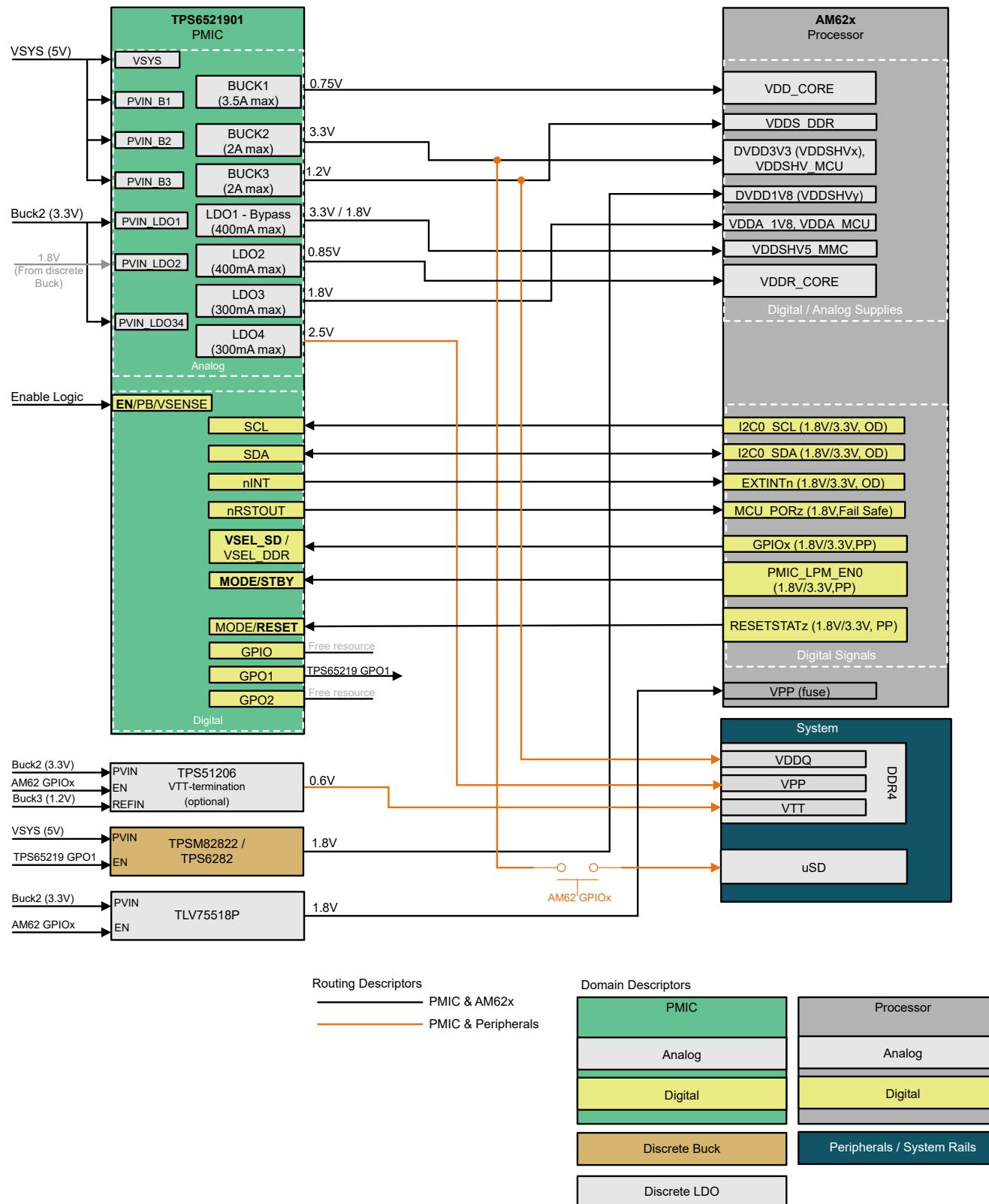

### 7.1 AM62x に電力を供給する TPS6521901

VSYS = 5V | メモリ:DDR4 | VDD\_CORE = 0.75V

図 7-1 に、5V 入力電源と DDR4 メモリを搭載したシステム上で AM62x プロセッサに電力を供給する TPS6521901 バリエーションを示します。プリレギュレータから供給される 5V は、リファレンスシステムのメイン入力電源 (VSYS) と、降圧コンバータの電力入力 (PVIN\_Bx) に接続されます。Buck1、Buck2、Buck3 は、それぞれ 0.75V、3.3V VDDSHVx IO、および DDR IO で VDD\_CORE に電力を供給するのに使用されます。Buck2 (3.3V の PMIC レール) は、電源オンシーケンスで最初に上昇するようにプログラムされているため、一部の LDO の入力電源として使用して、消費電力を最小限に抑えることができます。LDO1 をバイパスとして構成すると、SD カードの電圧を 3.3V と 1.8V の間に動的に変化させることができます。LDO1 のこの電圧の変化は、VSEL\_SD ピンを HIGH (LDO1 = 3.3V) または LOW (LDO1 = 1.8V) に設定することによってトリガできます。LDO2 は、VDDR\_CORE に電力を供給するのに使用されます。LDO3 は 1.8V のアナログドメインをサポートし、LDO4 は DDR4 メモリ用の 2.5V VPP をサポートします。この電源実装には、1.8V VDDSHV IO ドメインへの電力供給用の外部ディスクリート降圧レギュレータが必要です。この外部ディスクリートレギュレータは、PMIC の GPO1 を使用してイネーブルにできます。TPS6521901 は、電源オンシーケンスの 2 番目のスロットで GPO1 をイネーブルにするように、事前にプログラムされています。外部ディスクリートレギュレータは、PMIC が次のスロットのレールへの給電を開始する前にアクティブ放電を行い、安定した出力電圧まで昇圧する必要があります。残りの 2 本の汎用ピン (GPIO および GPO2) は、デフォルトでディセーブルになる空きデジタルリソースですが、(nRSTOUT がリリースされた後) PMIC の電源オンシーケンスの完了後に I2C を介してイネーブルにすることができます。

#### 注

NVM 設定および電源オン / 電源オフ シーケンス図については、『[TPS6521901 テクニカルリファレンスマニュアル](#)』を参照してください。

図 7-1. AM62 に電力を供給する TPS6521901

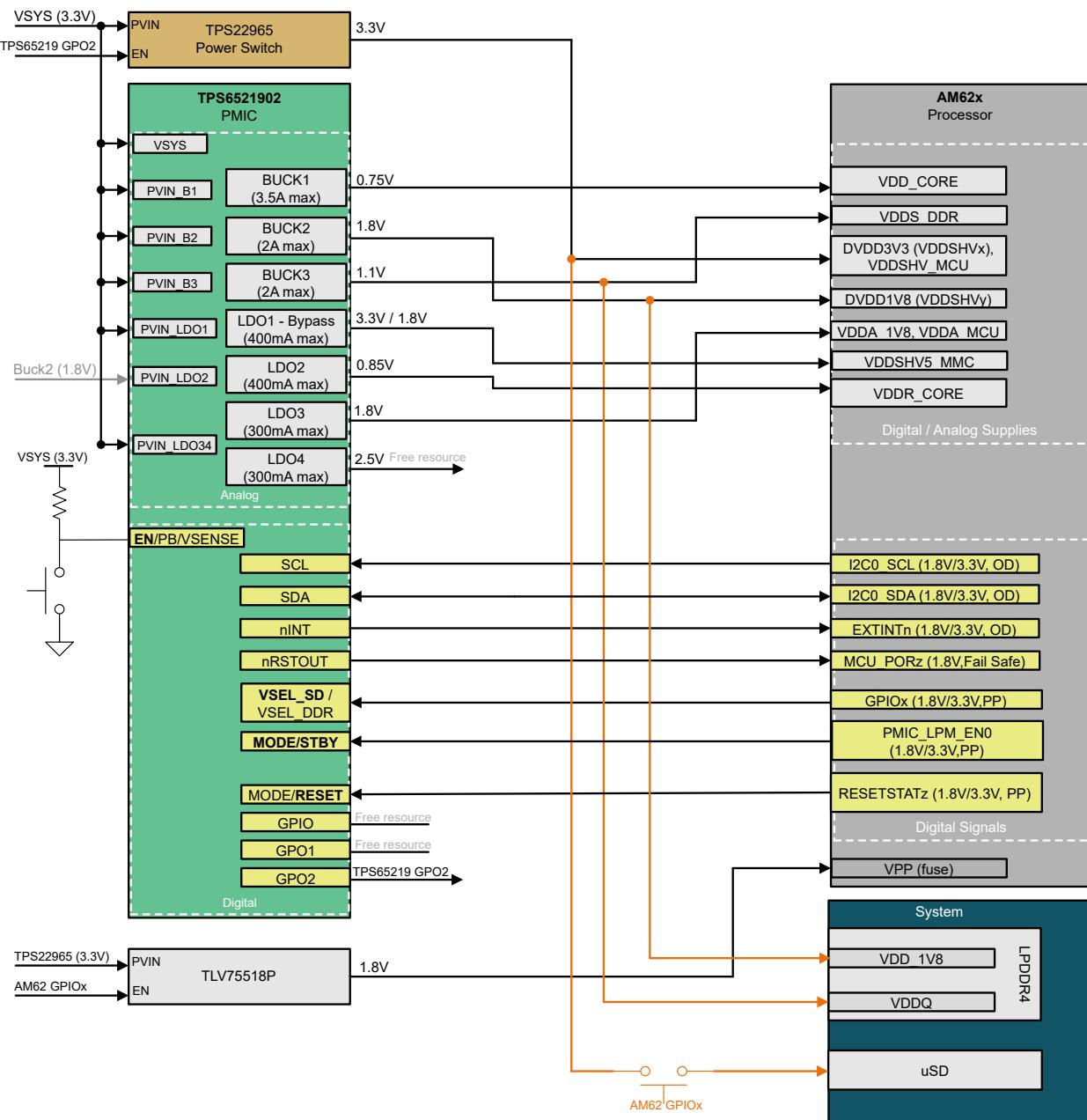

## 7.2 AM62x に電力を供給する TPS6521902

VSYS = 3.3V または 5V | メモリ:LPDDR4 | VDD\_CORE = 0.75V

図 7-2 に、3.3V 入力電源と LPDDR4 メモリを搭載したシステム上で AM62x プロセッサに電力を供給する TPS6521902 バリエーションを示します。Buck1、LDO3、LDO2、LDO1 を使用して、前のブロック図で説明したのと同じ AM62x ドメインに電力を供給します。プリレギュレータから供給される 3.3V をパワー スイッチと組み合わせて、3.3 DVDDSH IO ドメインに電力を供給できます。この外部パワー スイッチは、PMIC によってイネーブルまたはディセーブルになり、更にアクティブ放電が必要です。GPO2 は、電源オン シーケンスの 2 番目のスロット (持続時間 10ms) でイネーブルになるように事前にプログラムされています。これを使用して、外部パワー スイッチをイネーブルにし、プロセッサのシーケンス要件を満たすことができます。このスイッチには適切なランプレート仕様の製品を選択し、2 番目のスロットの持続時間 10ms の間に (PMIC が電源オン シーケンスの次のスロットを開始する前に) 安定した出力電圧を供給する必要があります。Buck3 および Buck2 は、VDDS\_DDR および 1.8V DVDD3V3 IO ドメインで必要とされる 1.1V および 1.8V をサポートします。また、LPDDR4 メモリに必要とされる電圧をサポートするのにも使用されます。LDO4 は、イーサネット PHY などの外部ペリフェラルに使用できる、2.5V の空き電源リソースです。GPIO と GPO1 は、デフォルトでディセーブルになる空きデジタルリソースですが、必要に応じて I2C 経由でイネーブルにすることもできます。

また、TPS6521902 は 5V 入力電源もサポートしています。VSYS = 5V を使用する場合は、外部パワー スイッチを 3.3V 降圧コンバータに置き換えます。この外部降圧コンバータは、同じ PMIC GPO2 によってイネーブルになります。

### 注

NVM 設定、および電源オンまたは電源オフ シーケンス図については、『[TPS6521902 テクニカル リファレンスマニュアル](#)』を参照してください。

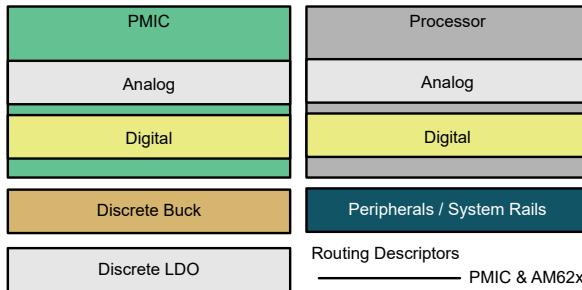

パワー ブロック図

Routing Descriptors

— PMIC & AM62x

— PMIC & Peripherals

Domain Descriptors

図 7-2. AM62x に電力を供給する TPS6521902

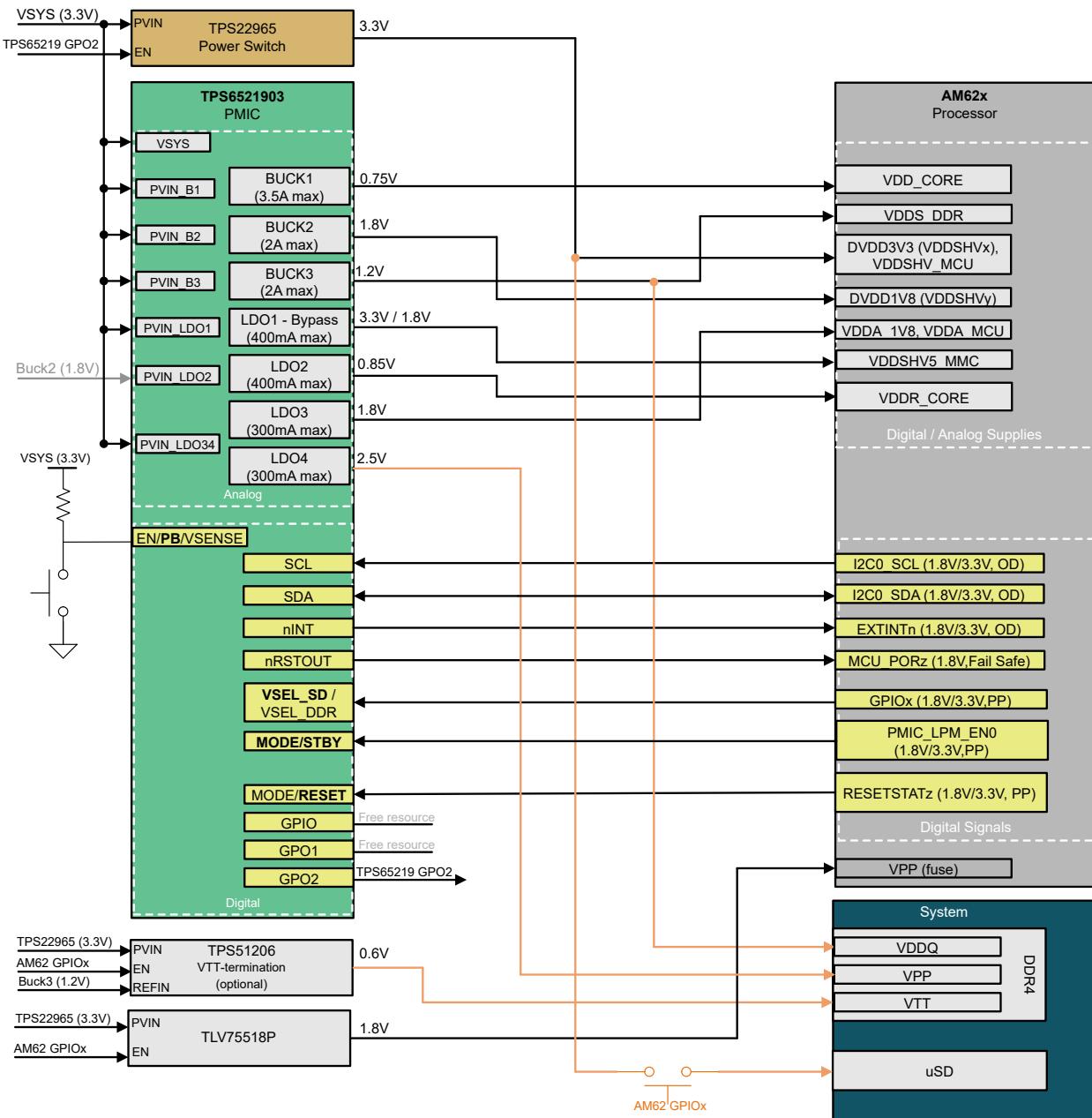

## 7.3 AM62x に電源を供給する TPS6521903

VSYS = 3.3V または 5V | メモリ:DDR4 | VDD\_CORE = 0.75V

図 7-3 に、3.3V 入力電源と DDR4 メモリを搭載したシステム上で AM62x プロセッサに電力を供給する TPS6521903 バリエーションを示します。この PMIC NVM 構成は TPS6521902 と類似していますが、Buck3 が LPDDR4 ではなく 1.2V (DDR4) を供給するように構成されています。プリレギュレータから供給される 3.3V をパワー スイッチと組み合わせて、3.3 DVDDSH IO ドメインに電力を供給できます。GPO2 は、電源オンシーケンスの 2 番目のスロット (持続時間 10ms) でイネーブルになるように事前にプログラムされています。GPO2 を使用して、外部パワー スイッチをイネーブルにし、プロセッサのシーケンス要件を満たすことができます。このスイッチには適切なランプレート仕様の製品を選択し、2 番目のスロットの持続時間 10ms の間に (PMIC が電源オンシーケンスの次のスロットを開始する前に) 安定した出力電圧を供給する必要があります。Buck3 は、VDDS\_DDR への電力供給に使用され、Buck2 の 1.8V と合わせて DDR4 メモリに必要な電圧をサポートします。GPIO と GPO1 は、デフォルトでディセーブルになる空きデジタルリソースですが、必要に応じて I2C 経由でイネーブルにすることもできます。

また、TPS6521903 は 5V 入力電源もサポートしています。VSYS = 5V を使用する場合は、外部パワー スイッチを 3.3V 降圧コンバータに置き換えます。この外部降圧コンバータは、同じ PMIC GPO2 によってイネーブルになります。

### 注

NVM 設定、および電源オンまたは電源オフシーケンス図については、『[TPS6521903 テクニカルリファレンスマニュアル](#)』を参照してください。

Routing Descriptors

— PMIC & AM62x

— PMIC & Peripherals

Domain Descriptors

図 7-3. AM62x に電力を供給する TPS6521903

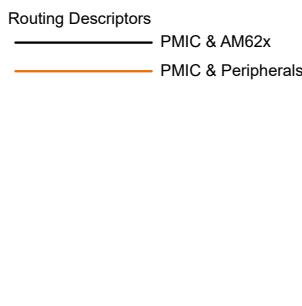

## 7.4 AM62x に電力を供給する TPS6521904

VSYS = 3.3V または 5V | メモリ:DDR4 | VDD\_CORE = 0.85V

図 7-4 に、3.3V 入力電源と DDR4 を搭載したシステム上で AM62x プロセッサに電力を供給する TPS6521904 バリエーションを示します。この構成は TPS6521903 と似ていますが、この場合、VDD\_CORE は 0.75V ではなく 0.85V で動作します。AM62x の仕様で記述されているように、「VDD\_CORE と VDDR\_CORE は同じ電源から給電されることが期待されるため、VDD\_CORE が 0.85V で動作しているときは一緒に電圧が上昇します」。プロセッサのこの要件により、VDD\_CORE と VDDR\_CORE の両方に、同じ PMIC レール (Buck1) から電力を供給できます。LDO2 は、ロードスイッチ同様、バイパスとして構成され、1.8V 出力用に事前プログラミングされた空き電源リソースであり、外部ペリフェラルへの電源供給に使用可能です。TPS6521903 と同様に、この構成では、GPO2 は電源オン シーケンスの 2 番目のスロット(持続時間 10ms)でイネーブルになるように事前にプログラムされています。この構成を使用して、外部パワー スイッチをイネーブルにし、プロセッサのシーケンス要件を満たすことができます。このスイッチには適切なランプレート仕様の製品を選択し、2 番目のスロットの持続時間 10ms の間に (PMIC が電源オン シーケンスの次のスロットを開始する前に) 安定した出力電圧を供給する必要があります。

また、TPS6521904 は 5V 入力電源もサポートしています。VSYS = 5V を使用する場合は、外部パワー スイッチを 3.3V 降圧コンバータに置き換えます。この外部降圧コンバータは、同じ PMIC GPO2 によってイネーブルになります。

### 注

このバリエーションは、[AM62B PMIC 搭載、スタータ キット](#)で使用され、新しい設計に利用できる設計ファイルが提供されます。NVM 設定および電源オン / 電源オフ シーケンス図については、[『TPS6521904 テクニカルリファレンスマニュアル \(Rev. A\)』](#)を参照してください。

図 7-4. AM62x に電力を供給する TPS6521904

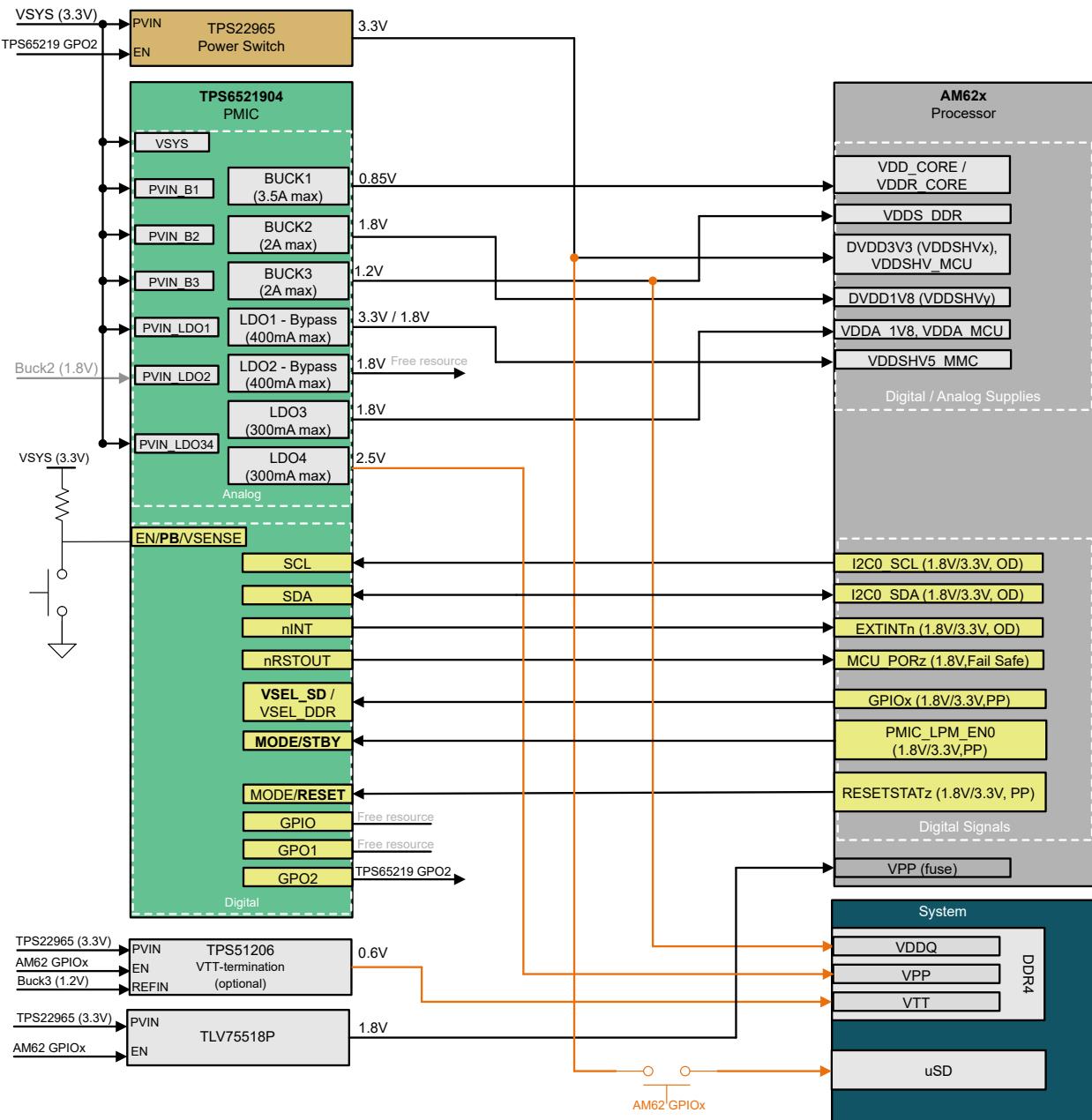

## 7.5 AM62x に電力を供給する TPS6521907

VSYS = 5V | メモリ:DDR4 | VDD\_CORE = 0.85V

図 7-5 に、5V 入力電源と DDR4 メモリを搭載したシステム上で AM62x プロセッサに電力を供給する TPS6521907 バリエーションを示します。この PMIC NVM は TPS6521901 と類似していますが、VDD\_CORE = 0.75V ではなく 0.85V をサポートしています。プリレギュレータから供給される 5V は、リファレンスシステムのメイン入力電源 (VSYS) と、降圧コンバータの電力入力 (PVIN\_Bx) に接続されます。Buck1 を使用して、0.85V のコアレールに電力を供給します。Buck2 および Buck3 は、それぞれ 3.3V VDDSHVx IO および DDR IO に電力を供給します。Buck2 (3.3V の PMIC レール) は、電源オン シーケンスで最初に上昇するようにプログラムされているため、一部の LDO の入力電源として使用して、消費電力を最小限に抑えることができます。LDO1 をバイパスとして構成すると、SD カードの電圧を 3.3V と 1.8V の間で動的に変化させることができます。LDO1 のこの電圧の変化は、I2C によって、または VSEL\_SD ピンを HIGH (LDO1 = 3.3V) または LOW (LDO1 = 1.8V) に設定することによってトリガできます。LDO2 は、外部ペリフェラルに電力を供給するために使用できる空きリソースです。LDO3 は 1.8V のアナログドメインをサポートし、LDO4 は DDR4 メモリ用の 2.5V VPP をサポートします。この電源実装には、1.8V VDDSHV IO ドメインへの電力供給用の外部ディスクリート降圧レギュレータが必要です。この外部ディスクリートレギュレータは、PMIC の GPO1 を使用してイネーブルにできます。

TPS6521907 は、電源オン シーケンスの 2 番目のスロットで GPO1 をイネーブルにするように、事前にプログラムされています。外部ディスクリートレギュレータにはアクティブ放電が行われており、PMIC が次のスロットのレールへの給電を開始する前に立ち上がり、安定した出力電圧に達する必要があります。残りの 2 本の汎用ピン (GPIO および GPO2) は、デフォルトでディセーブルになる空きデジタルリソースですが、PMIC の電源オン シーケンスの完了後に I2C を介してイネーブルにすることもできます。

### 注

NVM 設定、および電源オンまたは電源オフ シーケンス図については、『[TPS6521907 テクニカル リファレンスマニュアル](#)』を参照してください。

**Note**

If the expected total current on the 1.8V IO domain is lower than 400mA, then LDO2 can be used instead of the external 1.8V discrete Buck that is enabled with GPO1

図 7-5. AM62 に電力を供給する TPS6521907

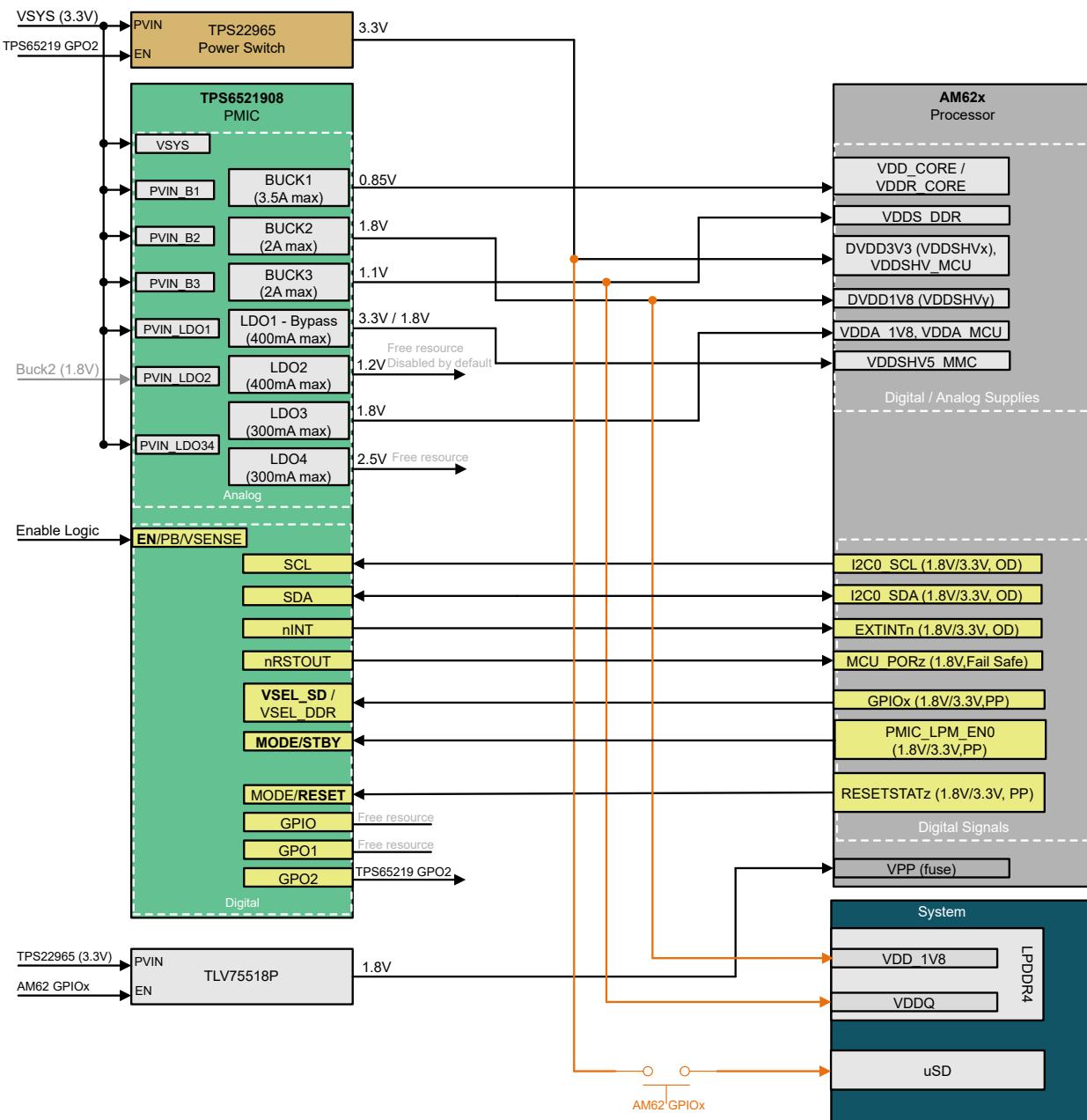

## 7.6 AM62x に電力を供給する TPS6521908

VSYS = 3.3V または 5V | メモリ:LPDDR4 | VDD\_CORE = 0.85V

図 7-6 に、3.3V 入力電源と DDR4 を搭載したシステム上で AM62x プロセッサに電力を供給する TPS6521908 バリエーションを示します。この構成では Buck1 を 0.85V の出力電圧で構成して、コアレールに電力を供給します。AM62x の仕様で記述されているように、「VDD\_CORE と VDDR\_CORE は同じ電源から給電されることが期待されるため、VDD\_CORE が 0.85V で動作しているときは一緒に電圧が上昇します」。プロセッサのこの要件により、VDD\_CORE と VDDR\_CORE の両方に、同じ PMIC レール (Buck1) から電力を供給できます。Buck2 および Buck3 は、それぞれ 1.8V の IO ドメインと LPDDR 電圧を供給します。LDO1 をバイパスとして構成すると、SD カードの電圧を 3.3V と 1.8V の間で動的に変化させることができます。LDO1 のこの電圧の変化は、I<sub>2</sub>C によって、または VSEL\_SD ピンを HIGH (LDO1 = 3.3V) または LOW (LDO1 = 1.8V) に設定することによってトリガできます。LDO3 は 1.8V アナログドメインを供給します。LDO2 および LDO4 は、外部ペリフェラルに電力を供給するために使用できる空き電源リソースです。この NVM のバリエーションでも、電源オンシーケンスの 2 番目のスロット (持続時間 10ms) で GPO2 がイネーブルになるように事前にプログラムされています。これを使用して、外部パワー スイッチをイネーブルにし、プロセッサのシーケンス要件を満たすことができます。この電源スイッチには適切なランプレート仕様の製品を選択し、2 番目のスロットの持続時間 10ms の間に (PMIC が電源オンシーケンスの次のスロットを開始する前に) 安定した出力電圧を供給する必要があります。

また、TPS6521908 は 5V 入力電源もサポートしています。VSYS = 5V を使用する場合は、外部パワー スイッチを 3.3V 降圧コンバータに置き換えます。この外部降圧コンバータは、同じ PMIC GPO2 によってイネーブルになります。

---

注

NVM 設定、および電源オンまたは電源オフシーケンス図については、『[TPS6521908 テクニカルリファレンスマニュアル](#)』を参照してください。

---

パワー ブロック図

Routing Descriptors

— PMIC & AM62x

— PMIC & Peripherals

Domain Descriptors

図 7-6. AM62 に電力を供給する TPS6521908

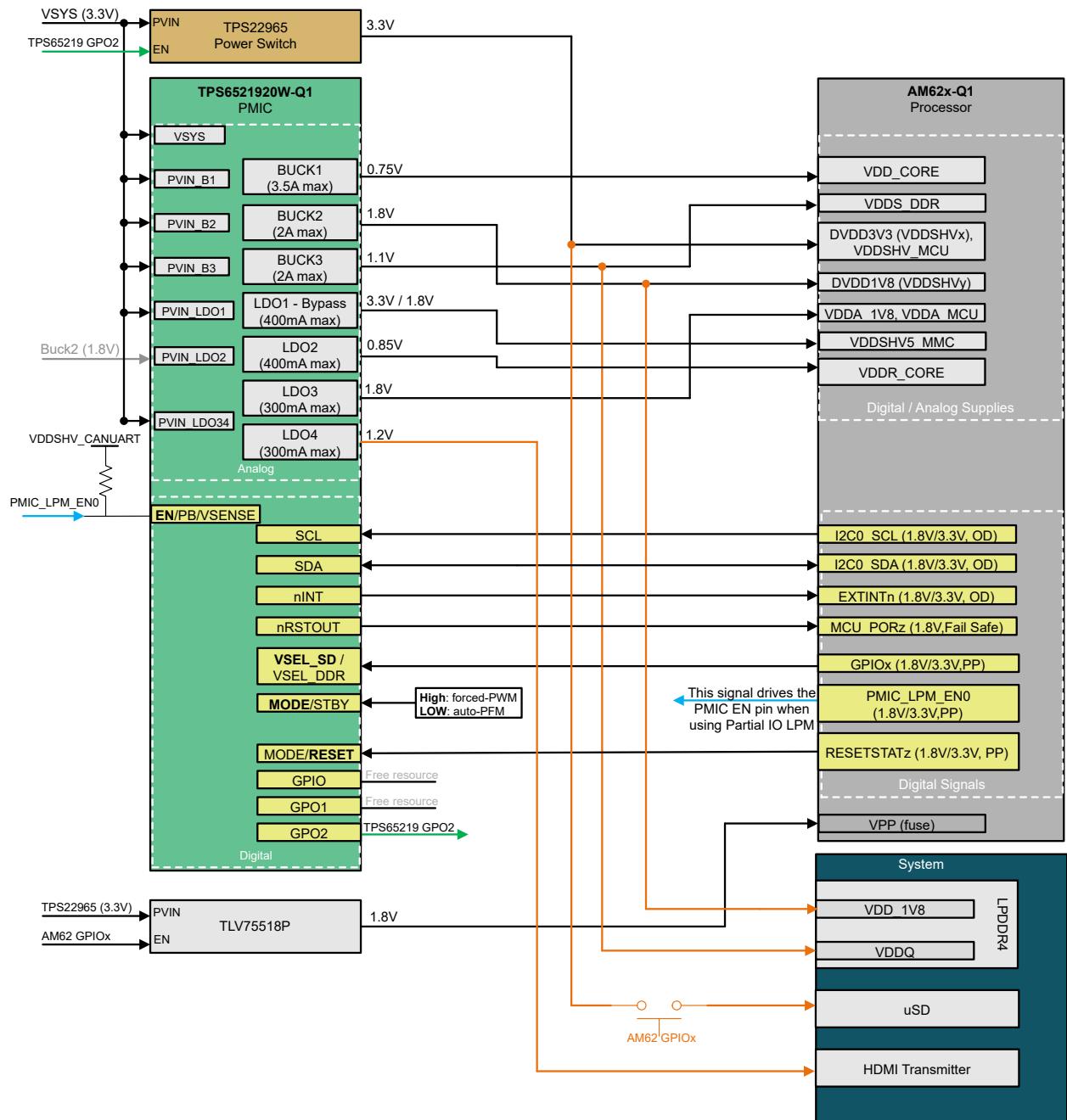

## 7.7 AM62x-Q1 に電力を供給する TPS6521920W-Q1

VSYS = 3.3V または 5V | メモリ:LPDDR4 | VDD\_CORE = 0.75V | 車載用

図 7-7 に 3.3V 入力電源と DDR4 メモリを搭載したシステム上で AM62x-Q1 プロセッサに電力を供給する車載用 TPS6521920W-Q1 バリエーションを示します。Buck1、Buck2、Buck3 は、それぞれ 0.75V、1.8V VDDSHVx IO、および 1.1V DDR IO で VDD\_CORE に電力を供給するのに使用されます。プリレギュレータから供給される 3.3V をパワー スイッチと組み合わせて、3.3 DVDDShx IO ドメインに電力を供給できます。この外部パワー スイッチは、PMIC によってイネーブルまたはディセーブルになり、更にアクティブ放電が必要です。GPO2 は、電源オン シーケンスの 2 番目のスロット (持続時間 10ms) でイネーブルになるように事前にプログラムされています。これを使用して、外部パワー スイッチをイネーブルにし、プロセッサのシーケンス要件を満たすことができます。このスイッチには適切なランプレート仕様の製品を選択し、2 番目のスロットの持続時間 10ms の間に (PMIC が電源オン シーケンスの次のスロットを開始する前に) 安定した出力電圧を供給する必要があります。LDO1 をバイパスとして構成すると、SD カードの電圧を 3.3V と 1.8V の間で動的に変化させることができます。LDO1 のこの電圧の変化は、VSEL\_SD ピンを HIGH (LDO1 = 3.3V) または LOW (LDO1 = 1.8V) に設定することによってトリガできます。LDO2 は、VDDR\_CORE に電力を供給するのに使用されます。LDO3 は 1.8V アナログ ドメインをサポートしています。LDO4 は 1.2V を出力するよう構成されており、HDMI トランスマッタへの電源供給に使用できます。GPIO と GPO1 は、デフォルトでディセーブルになる空きデジタルリソースですが、必要に応じて I2C 経由でイネーブルにすることもできます。

また、TPS6521920W-Q1 は 5V 入力電源もサポートしています。VSYS = 5V を使用する場合は、外部パワー スイッチを 3.3V 降圧コンバータに置き換えます。この外部降圧コンバータは、同じ PMIC GPO2 によってイネーブルになります。

### 注

NVM 設定、および電源オンまたは電源オフ シーケンス図については、『[TPS6521920 テクニカル リファレンスマニュアル](#)』を参照してください。

| PMIC pin   | Function / Polarity                                                 |

|------------|---------------------------------------------------------------------|

| VSEL_SD    | High: LDO1 = 3.3V (requires PVIN_LDO1=3.3V)<br>Low: LDO1 = 1.8V     |

| MODE/STBY  | High: Bucks operate in forced-PWM<br>Low: Bucks operate in auto-PFM |

| MODE/RESET | High: normal operation<br>Falling edge: Warm reset                  |

## Domain Descriptors

Routing Descriptors

— PMIC & AM62x

— PMIC & Peripherals

図 7-7. AM62x に電力を供給する TPS6521920W-Q1

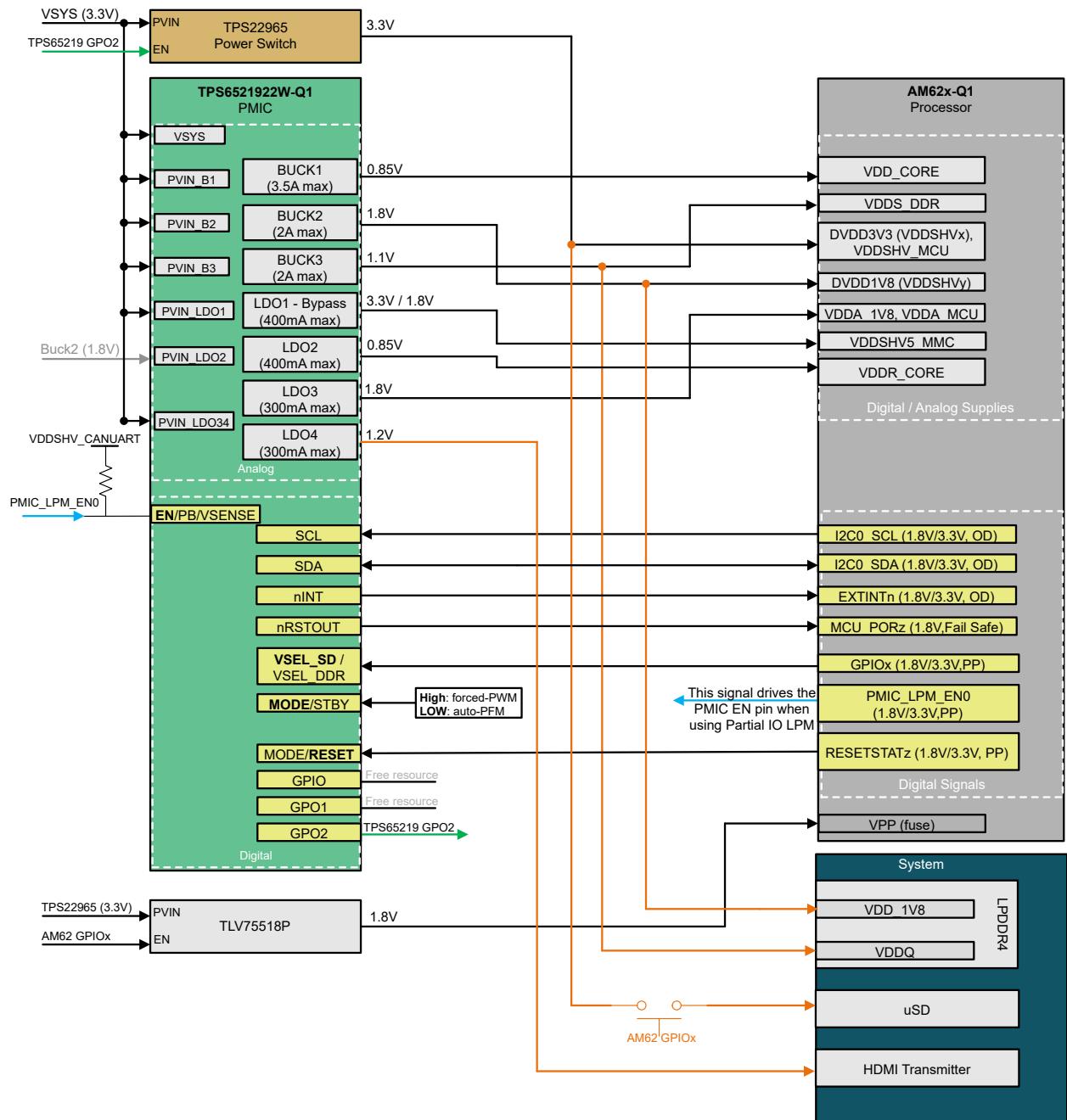

## 7.8 AM62x-Q1 に電力を供給する TPS6521922W-Q1

図 7-8 に 3.3V 入力電源と DDR4 メモリを搭載したシステム上で AM62x-Q1 プロセッサに電力を供給する車載用 TPS6521922W-Q1 バリエーションを示します。Buck1、Buck2、Buck3 は、それぞれ 0.85V、1.8V VDDSHV<sub>y</sub> IO、および 1.1V DDR IO で VDD\_CORE に電力を供給するのに使用されます。プリレギュレータから供給される 3.3V をパワースイッチと組み合わせて、3.3 DVDDSH<sub>x</sub> IO ドメインに電力を供給できます。この外部パワー スイッチは、PMIC によってイネーブルおよびディセーブルになり、更にアクティブ放電が必要です。GPO2 は、電源オンシーケンスの 2 番目のスロット（持続時間 10ms）でイネーブルになるように事前にプログラムされています。これを使用して、外部パワー スイッチをイネーブルにし、プロセッサのシーケンス要件を満たすことができます。このスイッチには適切なランプレート仕様の製品を選択し、2 番目のスロットの持続時間 10ms の間に（PMIC が電源オンシーケンスの次のスロットを開始する前に）安定した出力電圧を供給する必要があります。LDO1 をバイパスとして構成すると、SD カードの電圧を 3.3V と 1.8V の間で動的に変化させることができます。LDO1 のこの電圧の変化は、VSEL\_SD ピンを HIGH (LDO1 = 3.3V) または LOW (LDO1 = 1.8V) に設定することによってトリガできます。LDO2 は、VDDR\_CORE に電力を供給するのに使用されます。LDO3 は 1.8V アナログドメインをサポートしています。LDO4 は 1.2V を出力するよう構成されており、HDMI トランスマッタへの電源供給に使用できます。GPIO と GPO1 は、デフォルトでディセーブルになる空きデジタルリソースですが、必要に応じて I2C 経由でイネーブルにすることもできます。

また、TPS6521922W-Q1 は 5V 入力電源もサポートしています。VSYS = 5V を使用する場合は、外部パワー スイッチを 3.3V 降圧コンバータに置き換えます。この外部降圧コンバータは、同じ PMIC GPO2 によってイネーブルになります。

### 注

NVM 設定、および電源オンまたは電源オフシーケンス図については、『[TPS6521922 テクニカルリファレンスマニュアル](#)』を参照してください。

| PMIC pin   | Function / Polarity                                                 |

|------------|---------------------------------------------------------------------|

| VSEL_SD    | High: LDO1 = 3.3V (requires PVIN_LDO1=3.3V)<br>Low: LDO1 = 1.8V     |

| MODE/STBY  | High: Bucks operate in forced-PWM<br>Low: Bucks operate in auto-PFM |

| MODE/RESET | High: normal operation<br>Falling edge: Warm reset                  |

## Domain Descriptors

Routing Descriptors

- PMIC & AM62x

- PMIC & Peripherals

図 7-8. AM62x に電力を供給する TPS6521922W-Q1

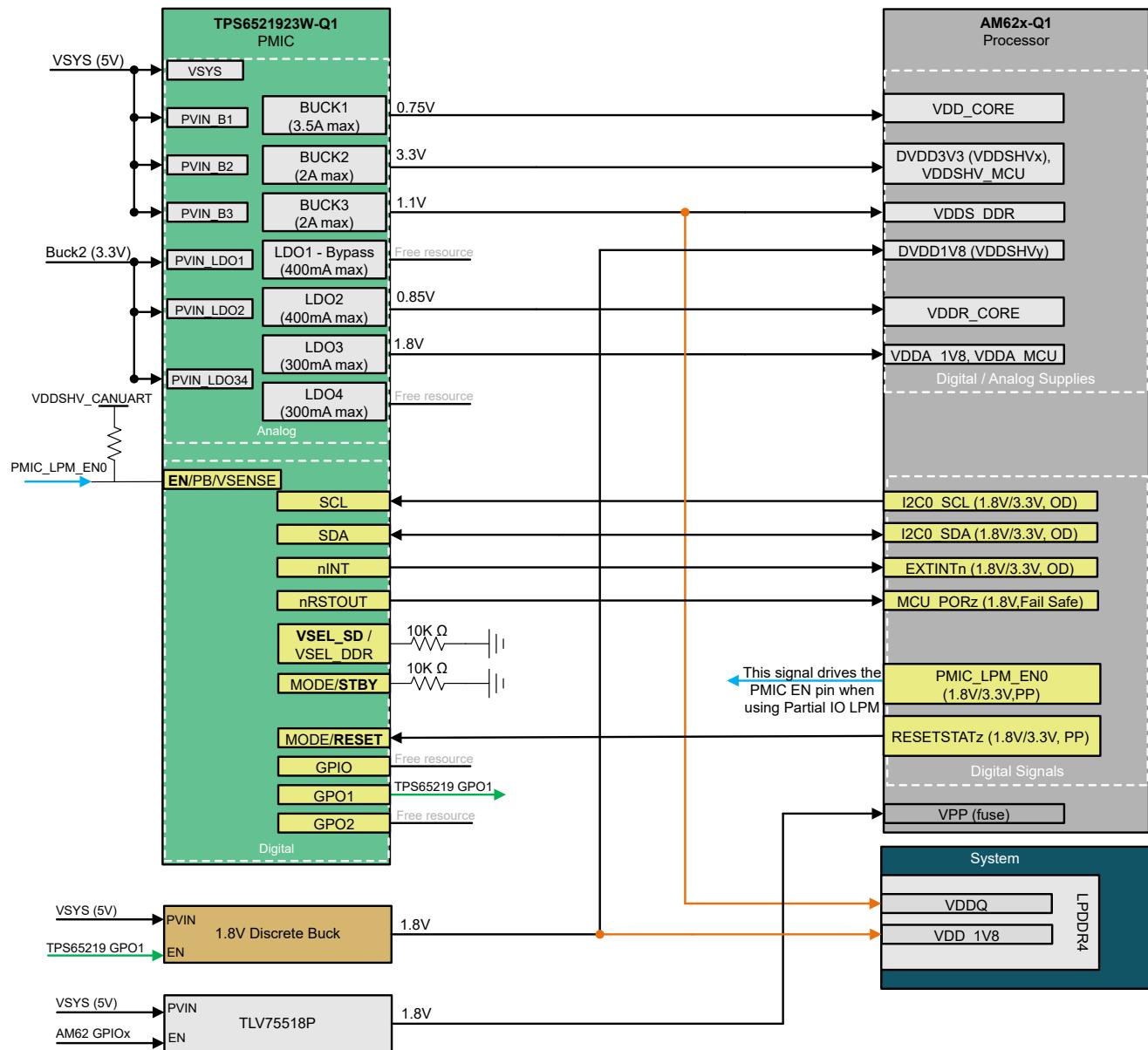

## 7.9 AM62x-Q1 に電力を供給する TPS6521923W-Q1

VSYS = 3.3V または 5V | メモリ:LPDDR4 | VDD\_CORE = 0.75V | 車載用

図 7-9 に 5V 入力電源と LPDDR4 メモリを搭載したシステム上で AM62x-Q1 プロセッサに電力を供給する車載用 TPS6521923W-Q1 バリエーションを示します。Buck1、Buck2、Buck3 は、それぞれ 0.75V、3.3V VDDSHV<sub>y</sub> IO、および 1.1V DDR IO で VDD\_CORE に電力を供給するのに使用されます。GPO1 は、外部降圧から 1.8V IO への電力供給を有効にするように事前にプログラムされています。LDO1 および LDO4 は、デフォルトで無効になっています。LDO2 は、VDD\_CORE に電力を供給するのに使用されます。LDO3 は 1.8V アナログドメインをサポートしています。GPIO と GPO1 は、デフォルトでディセーブルになる空きデジタルリソースですが、必要に応じて I<sub>2</sub>C 経由でイネーブルすることができます。

---

### 注

NVM 設定、および電源オンまたは電源オフ シーケンス図については、『[TPS6521923 テクニカルリファレンスマニュアル](#)』を参照してください。

---

| PMIC pin     | Function / Polarity                                      |

|--------------|----------------------------------------------------------|

| MODE/STBY    | High: PMIC in Standby state<br>Low: PMIC in Active state |

| MODE/RESET   | High: normal operation<br>Falling edge: Warm reset       |

| EN/PB/VSENSE | High: PMIC enable<br>Low: PMIC disabled                  |

Domain Descriptors

図 7-9. AM62x に電力を供給する TPS6521923W-Q1

## 8 まとめ

このドキュメントでは、TPS65219 電源管理 IC を使用してテキサス・インスツルメンツの AM62x Sitara プロセッサおよび産業用および車載アプリケーションのペリフェラルに電力を供給する方法について包括的なガイダンスを提供します。このアプリケーションノートは、電力供給ネットワークの詳細な仕様を提示し、工場出荷時にプログラムされた TPS65219 のさまざまなバリエントをリファレンス表と比較します。また、実装を容易にするための電源マッピングの例を掲載しています。技術サポートは、パワーマネージメント E2E フォーラムでご利用いただけます。

## 9 参考資料

1. テキサス・インスツルメンツ、『[TPS65219 ARM Cortex-A53 プロセッサおよび FPGA 向けの内蔵電力管理集積回路 \(PMIC\)](#)』データシート

2. テキサス・インスツルメンツ、『[TPS65219-Q1 ARM Cortex-A53 プロセッサ向けの内蔵電力管理集積回路 \(PMIC\)](#)』データシート

3. テキサス・インスツルメンツ、『[AM62x Sitara™ プロセッサ](#)』データシート

## 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision B (September 2023) to Revision C (August 2025) | Page               |

|----------------------------------------------------------------------|--------------------|

| • 「AM62x-Q1 に電力を供給する TPS6521922W-Q1」のセクションを追加 .....                  | <a href="#">27</a> |

| • 「AM62x-Q1 に電力を供給する TPS6521923W-Q1」のセクションを追加 .....                  | <a href="#">29</a> |

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](#) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1)お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所 : Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated