*Application Note***基板レイアウトが LDO の放熱性能に及ぼす影響に関する実証的分析**

*Gerard Copeland*

**概要**

本書では、プリント基板 (PCB) のレイアウトが低ドロップアウト (LDO) レギュレータの放熱性能、特に接合部周囲間の熱抵抗  $\theta_{JA}$  に及ぼす影響を調べます。このパラメータは、TPS745 (WSON パッケージ)、TPS7B82-Q1 (TO-252 パッケージ)、TLV755P (SOT-23 パッケージ) の各デバイスで測定されたものです。それぞれのデバイスを、5 つのレイアウトと組み合わせてテストします。レイアウトごとに、内層と外層の両方で銅箔の量が順に増やされています。銅箔の量を増やすと  $\theta_{JA}$  は低下しますが、反射が低下するポイントに達します。サーマル パッド付きのパッケージでは、銅箔の量がより効果を発揮します。これらの結果を使用して、システム設計者が放熱性能を向上させるためのレイアウトのヒントを提供します。この調査でテストされているデバイスは LDO のみですが、本書に記載されている PCB レイアウトと結論は、他の電力消費デバイスにも適用されます。

**目次**

|                                 |    |

|---------------------------------|----|

| 1はじめに.....                      | 2  |

| 2手順.....                        | 7  |

| 3テスト結果と解説.....                  | 8  |

| 4まとめ.....                       | 12 |

| 5今後の調査.....                     | 12 |

| 6参考資料.....                      | 12 |

| 7改訂履歴.....                      | 13 |

| A 热テスト基板のレイアウト.....             | 14 |

| A.1 TPS745 (WSON) の図.....       | 14 |

| A.2 TPS7B82-Q1 (TO-252) の図..... | 19 |

| A.3 TLV755P (SOT-23) の図.....    | 24 |

| B 热テストの結果.....                  | 29 |

| B.1 放熱性能データ.....                | 29 |

**商標**

すべての商標は、それぞれの所有者に帰属します。

## 1 はじめに

LDO は、比較的単純でコストが低いという利点があるため、電子機器の電源の設計で最も一般的な DC/DC コンバータです。アプリケーションの統合と小型化が進むにつれて、電源の設計もより小型で安価になる必要があるため、LDO の使用は増え続けています。LDO はリニアコンバータであり本質的に電力を消費するため、結果として熱性能はますます重要なシステム設計要素となっています。JEDEC は半導体の熱評価基準の測定と報告を統一形式で行う方法を標準化していますが、この標準は放熱性能について十分に最適化されていません。放熱性能に影響を及ぼす最も重要な要因の1つは PCB レイアウトで、これはシステム設計者の担当分野です。本書の目的は、PCB レイアウトが LDO の放熱性能に及ぼす影響を調査し、これらの設計者を支援することです。これまでに、『[『小型 SMD パッケージに封止した LDO の放熱性能』アプリケーションレポート](#)』および『[AN-1520 露出パッケージで最良の熱抵抗を実現するための基板レイアウトガイド](#)』アプリケーションレポートで、このトピックについて解説してきましたが、この調査ではより適切な情報を得るために、機能設定のデータを収集しました。この設定には、TI の評価基板 (EVM) をエミュレートする受動部品を使用した、実際に動作する PCB レイアウトと、アクティブな電力供給時の熱測定も含まれます。アクティブな電力供給とは、LDO を通常に動作させながら、入力電圧と負荷電流を変化させて消費電力を増加させ、デバイスの接合部で熱を発生させることです。

半導体の放熱性能を評価する最も一般的な指標は、接合部周囲間の熱抵抗  $\theta_{JA}$  です。式 1 は、このパラメータが、デバイスの消費電力あたりの、デバイスの動作温度と接合部温度との差として定義されていることを示しています。

$$\theta_{JA} = \frac{T_J - T_A}{P_D} \quad (1)$$

$\theta_{JA}$  が小さくなる設計は、特定の消費電力レベルにおいて接合部温度が低くなり、耐用期間と信頼性が向上します。『[半導体およびIC パッケージの熱評価基準』アプリケーションレポート』では、 \$\theta\_{JA}\$  に大きな影響を及ぼす2つの要因が PCB レイアウトと IC パッケージであることが説明されています。これら2つの要因が放熱性能にどのように影響するかを調べるために、一般的なパッケージとして TPS745 \(WSON パッケージ\)、TPS7B82-Q1 \(TO-252 パッケージ\)、および TLV755P \(SOT-23 パッケージ\) の LDO を選び、5つの異なる PCB レイアウトでテストしました。](#)

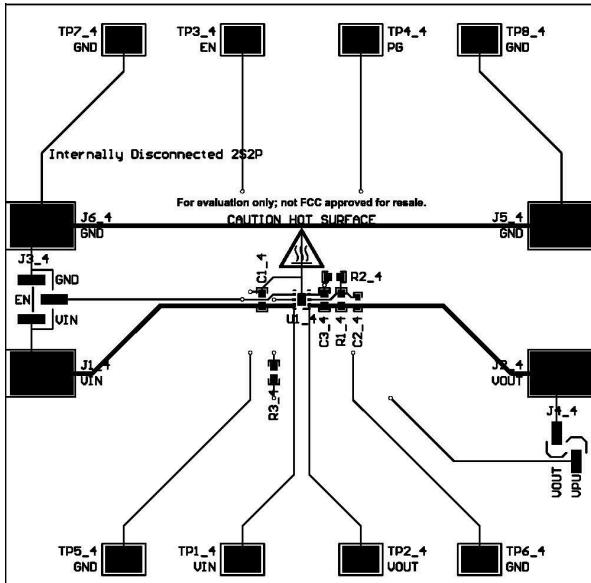

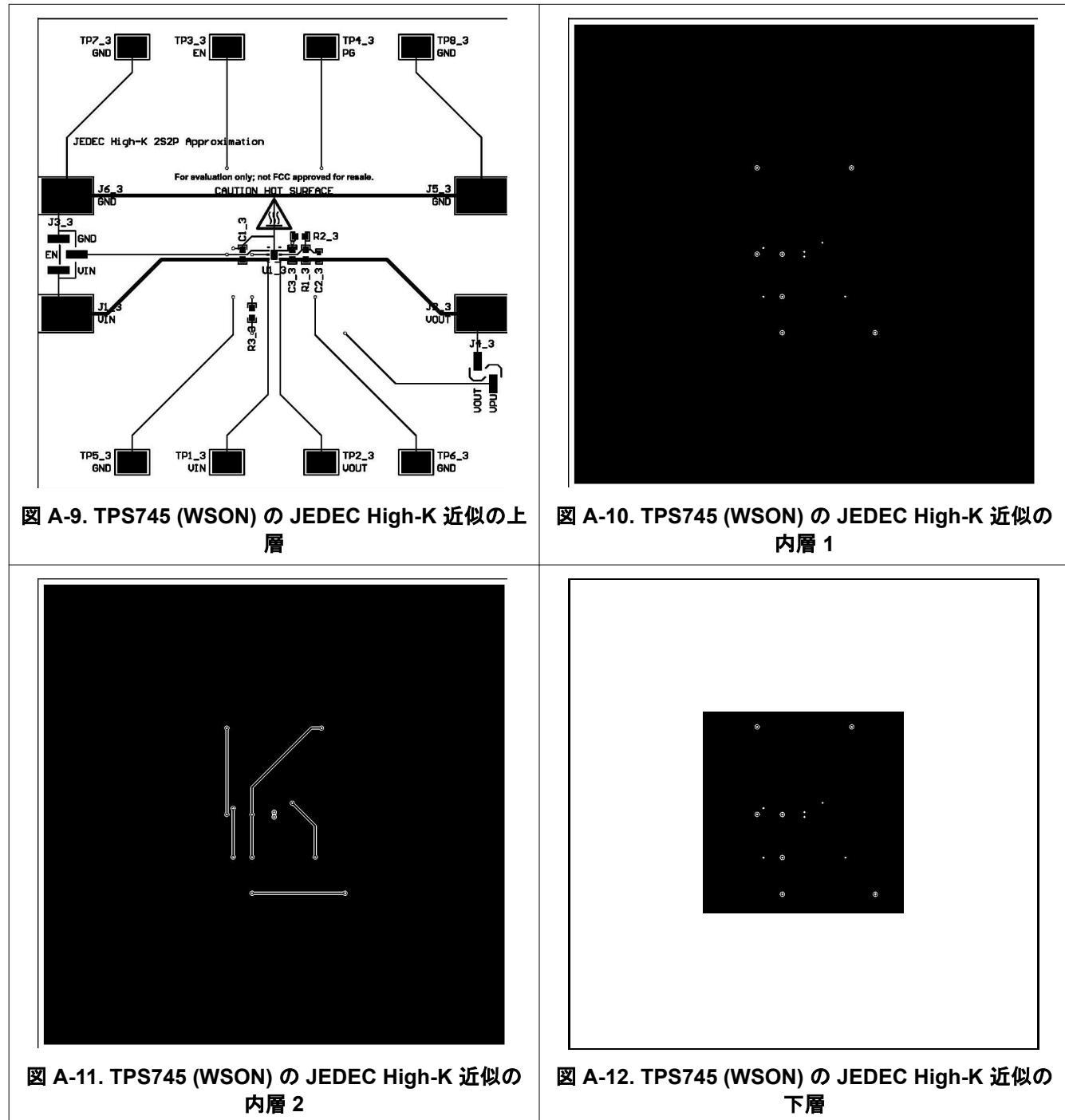

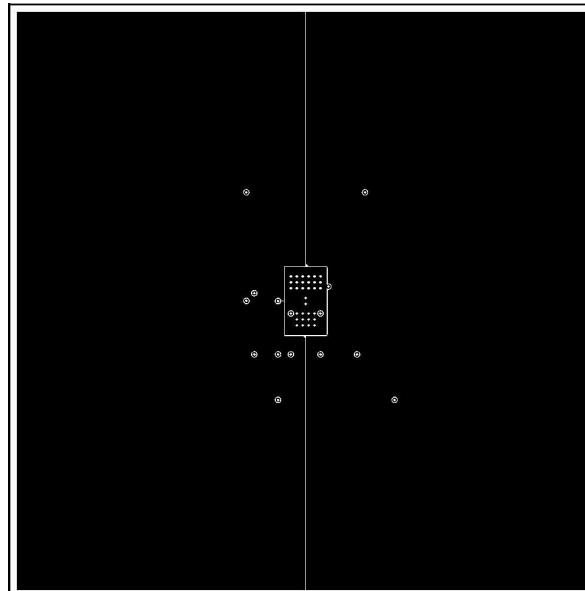

半導体の放熱性能は気流、高度、周囲温度などの他の外部要因に依存するため、JEDEC は  $\theta_{JA}$  や他の熱評価基準をテストするための測定手順とテスト基板を標準化する必要がありました。本書では、実効熱伝導率が低いテスト基板 (<https://www.jedec.org/system/files/docs/JESD51-3.PDF> に規定) と実効熱伝導率が高いテスト基板 (<https://www.jedec.org/system/files/docs/jesd51-7.PDF> に規定) に類似したものを、3つのカスタム レイアウトとともに各パッケージ用に設計しています。各基板の面積と層のスタックは、JEDEC 標準のテスト基板の近似に従い、9インチ<sup>2</sup> (3インチ × 3インチ) の面積を持つ4層 PCB を使用しています。外層は2オンスの銅厚で、内層は1オンスの銅厚です。各パッケージ用に製造された5つのレイアウトでは、デバイスに接続されている銅の量を順に増やしています。これは、 $\theta_{JA}$  を測定し、銅箔の量と反比例することを示すのが目的です。3つのパッケージで一貫した結果を得るために、ヒートシンクに使用される銅箔の量はどのレイアウトでも同じです。それぞれのレイアウトタイプには、銅成分が少ないものから多いものの順に次のような名前が付けられています。

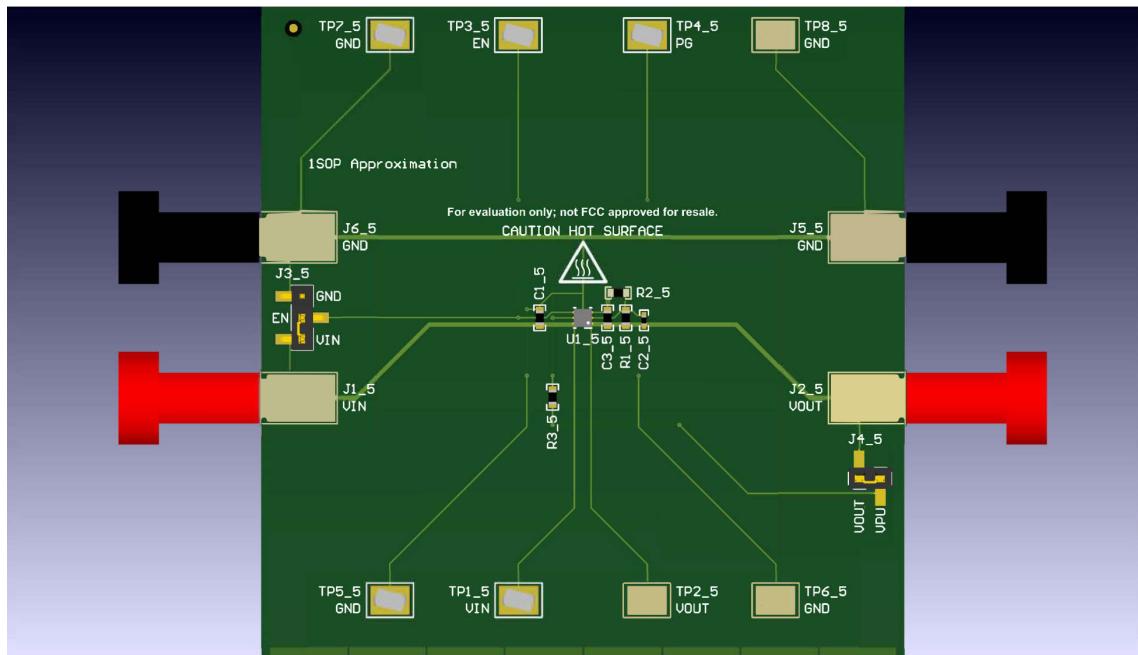

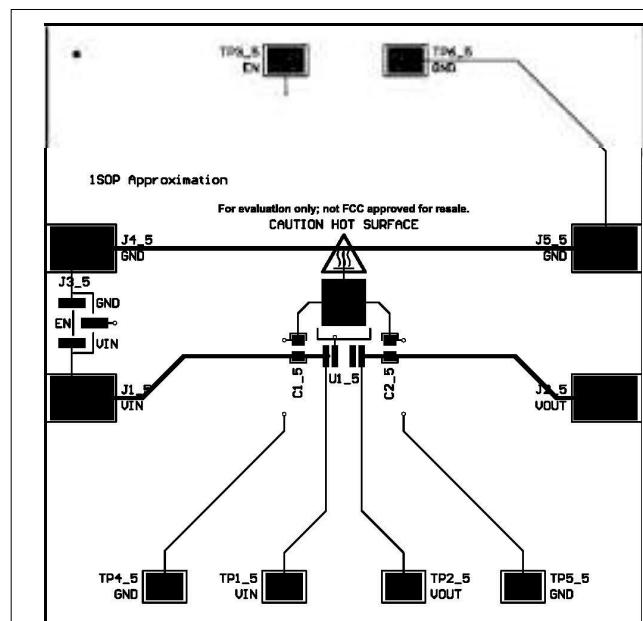

- 1SOP 近似

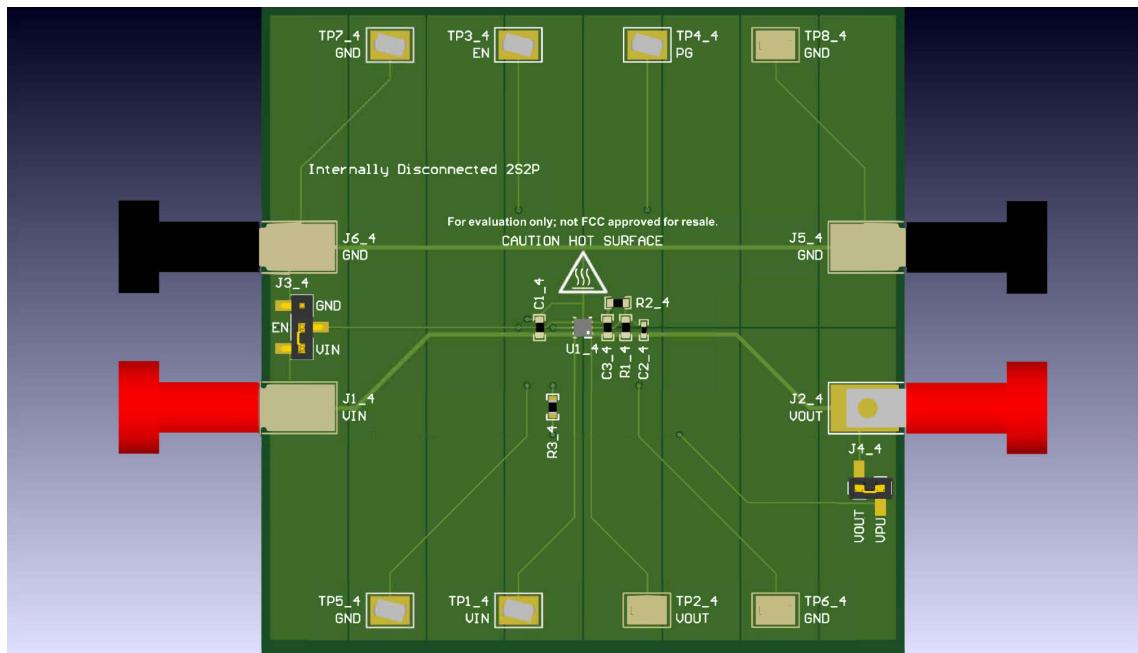

- 内部的に切断された

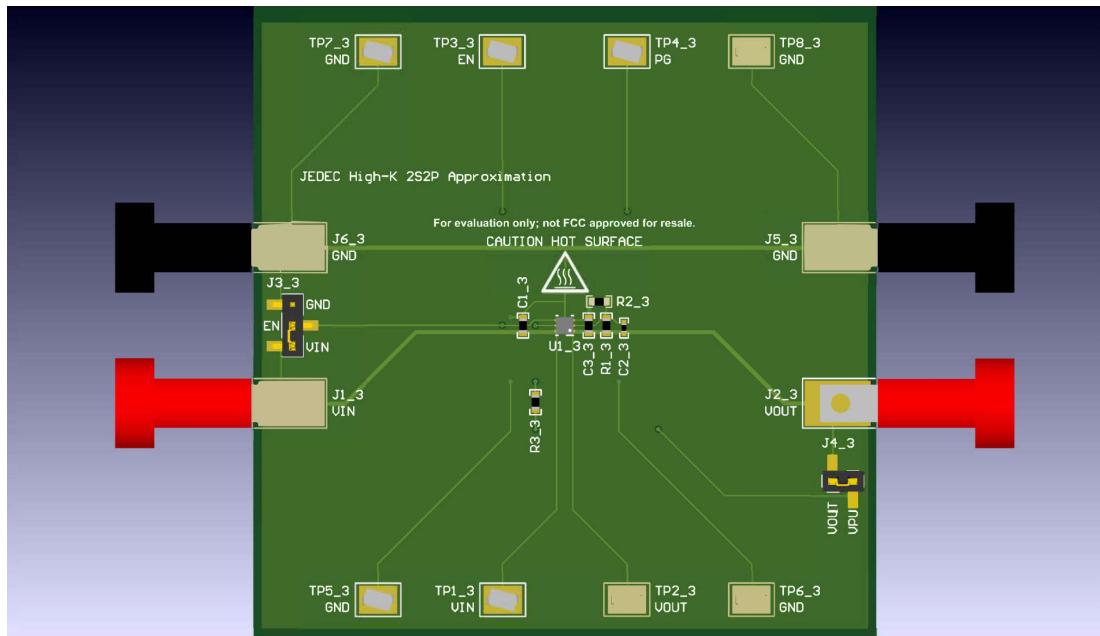

- JEDEC High-K 近似

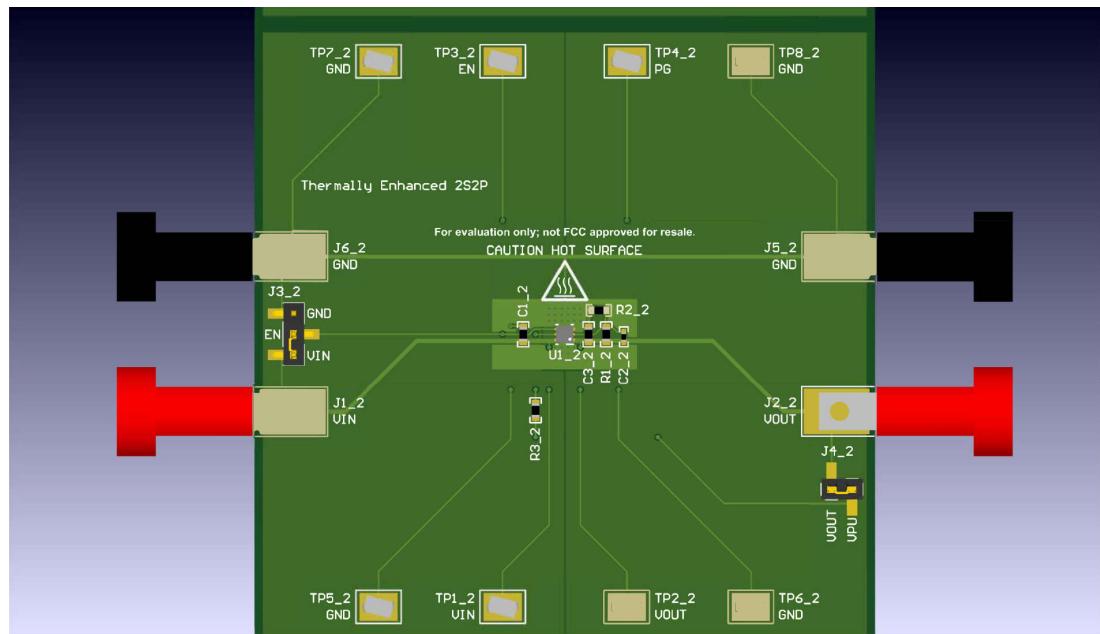

- 熱的に強化された

- 熱的に飽和した

また、<https://www.jedec.org/system/files/docs/JESD51-9.pdf> に規定されている JEDEC 標準に従い、WSON および TO-252 のレイアウトでは、いずれもサーマル ランド パッドにサーマルビアが含まれています。これらのビアは、直径 20mm、穴のサイズが 10mm で、17μm の銅メッキ処理を採用しています。

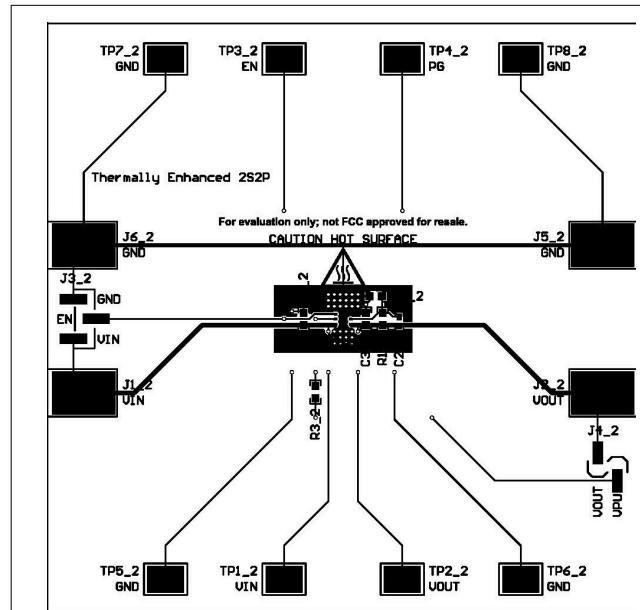

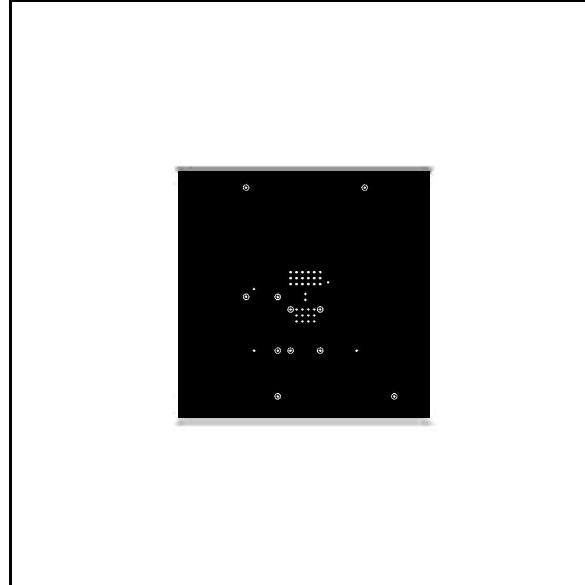

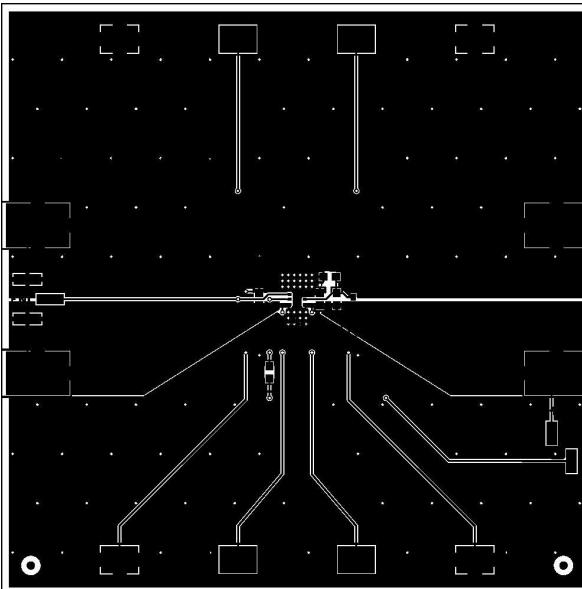

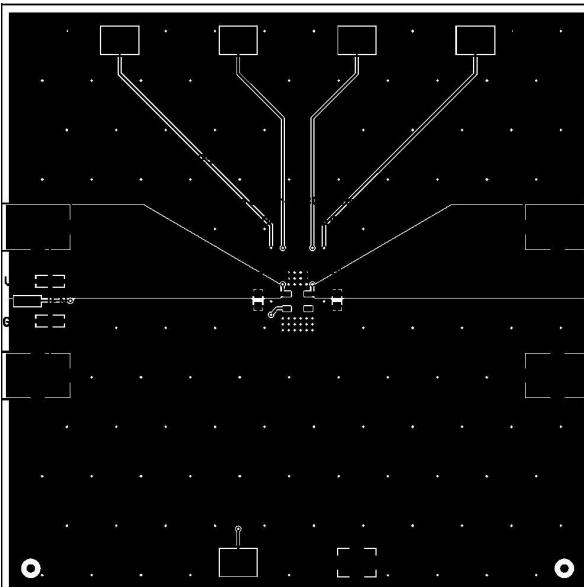

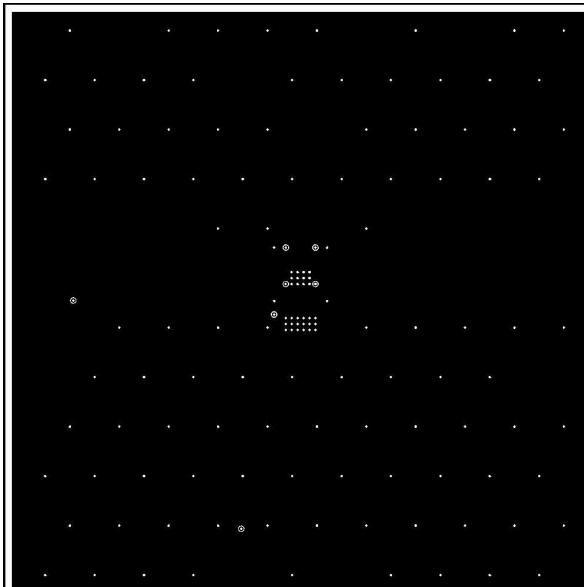

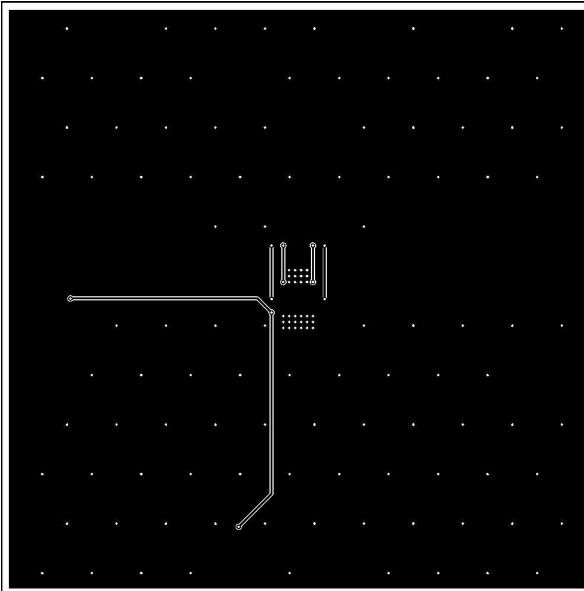

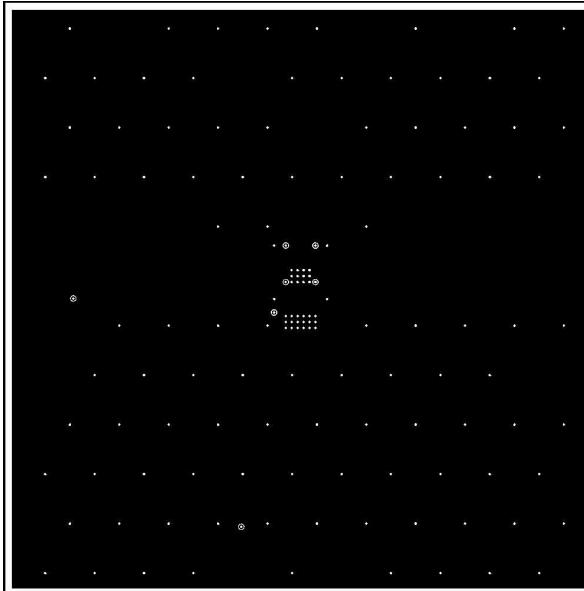

比較用のベンチマークとして、2つの異なる  $\theta_{JA}$  値を使用します。1つ目は、各デバイスのデータシートの「熱に関する情報」表に  $R_{\theta JA}$  として記載されている  $\theta_{JA, datasheet}$  です。 $\theta_{JA, datasheet}$  は、JEDEC High-K 热テスト基板の熱モデルを使用して導出され、熱性能を評価するため設計者によって最も多く使用されます。2つ目の値は、1SOP 近似レイアウトで測定される  $\theta_{JA, 1SOP}$  です。この値は、ワースト ケースのレイアウトで予想される放熱性能の例を示します。図 1-1 から 図 1-5 までは、WSON パッケージの TPS745 用に設計された各レイアウトの 3D 生成画像を示しています。各レイアウトについて、4つの層すべての図を、Appendix A に示します。各設計レイアウトと銅箔の説明を、表 1-1 に示します。

表 1-1. レイアウトの識別子と説明

| 基板                 | 属性        | 説明                             | 接続された銅の面積<br>(in <sup>2</sup> ) | 切断された銅の面積<br>(in <sup>2</sup> ) |

|--------------------|-----------|--------------------------------|---------------------------------|---------------------------------|

| 1SOP 近似            | 上層        | トレースのみ                         | なし                              | なし                              |

|                    | 内層 1      | 銅なし                            |                                 |                                 |

|                    | 内層 2      | 銅なし                            |                                 |                                 |

|                    | 下層        | トレースのみ                         |                                 |                                 |

|                    | 追加のサーマルビア | なし                             |                                 |                                 |

| 内部的に切断された          | 上層        | トレースのみ                         | 0.07                            | 16.8                            |

|                    | 内層 1      | 中程度、接続されていない、不連続なプレーン (1)      |                                 |                                 |

|                    | 内層 2      | 中程度、接続されていない、不連続なプレーン (1)      |                                 |                                 |

|                    | 下層        | トレースと 1 つの小さなグランド プレーン         |                                 |                                 |

|                    | 追加のサーマルビア | なし                             |                                 |                                 |

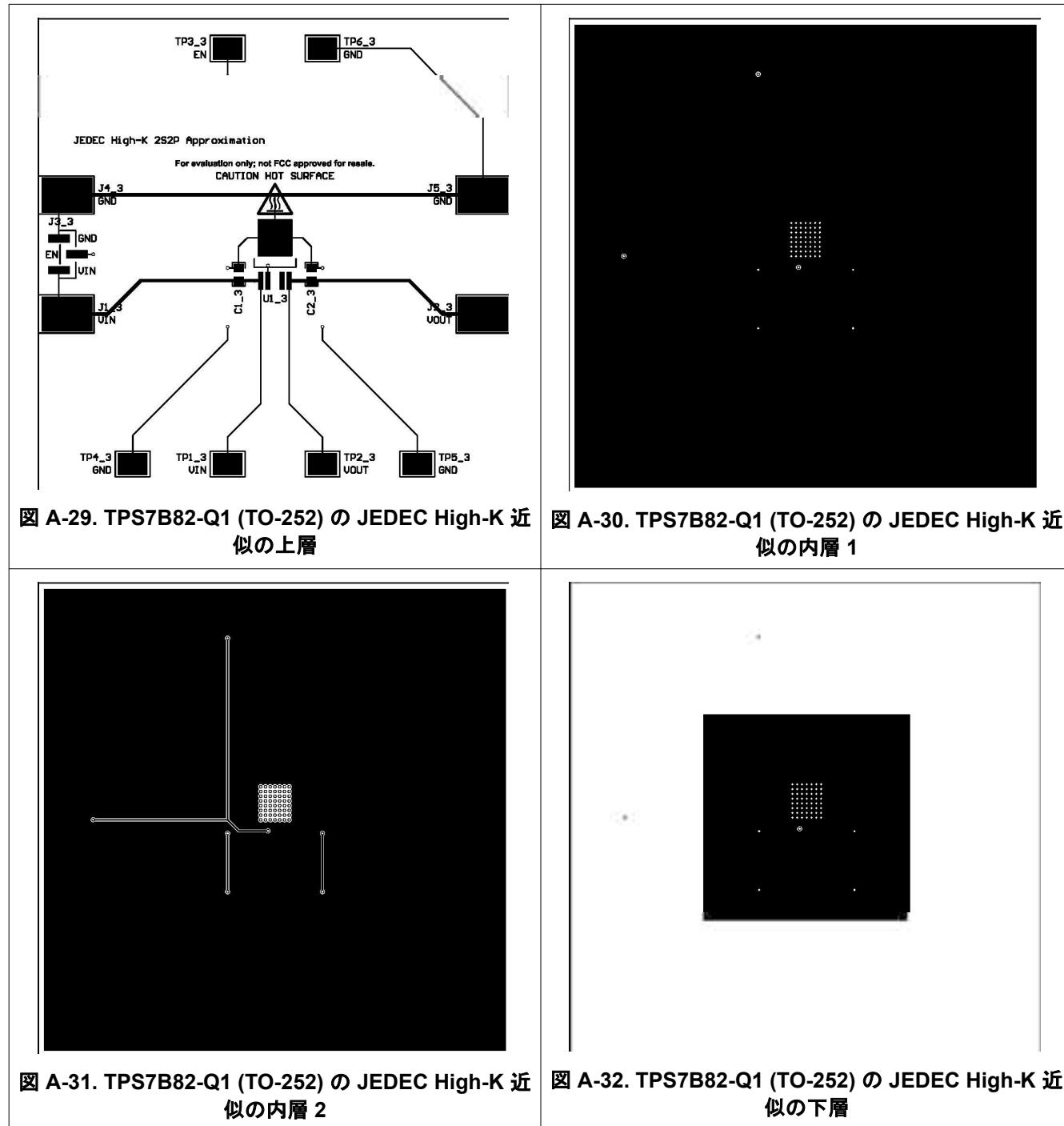

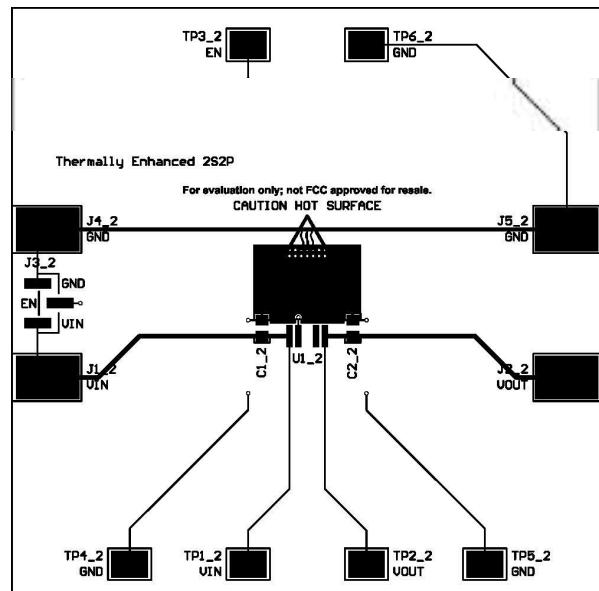

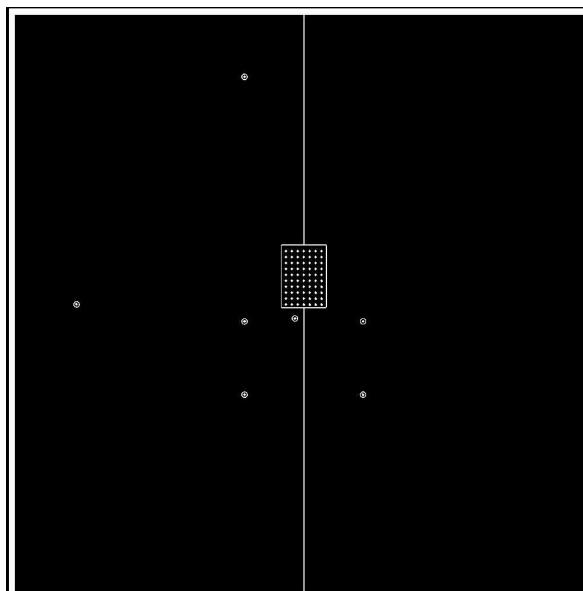

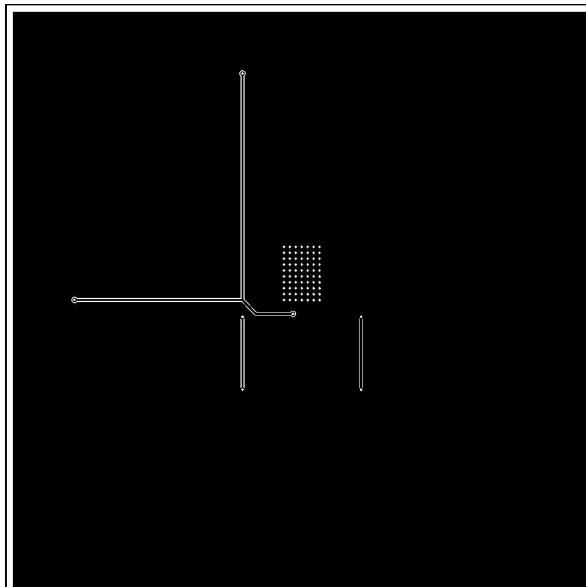

| JEDEC High-K<br>近似 | 上層        | トレースのみ                         | 10.2                            | 8.53                            |

|                    | 内層 1      | 1 つの大きなグランド プレーン               |                                 |                                 |

|                    | 内層 2      | トレースと 1 つの大きな接続されていないプレーン      |                                 |                                 |

|                    | 下層        | 1 つの中程度のグランド プレーン              |                                 |                                 |

|                    | 追加のサーマルビア | なし                             |                                 |                                 |

| 熱的に強化された           | 上層        | トレースと 1 つの小さなグランド プレーン         | 10.5                            | 8.43                            |

|                    | 内層 1      | 小さなグランド プレーンと 2 つの接続されていないプレーン |                                 |                                 |

|                    | 内層 2      | トレースと 1 つの中程度のグランド プレーン        |                                 |                                 |

|                    | 下層        | 1 つの中程度のグランド プレーン              |                                 |                                 |

|                    | 追加のサーマルビア | デバイスの周辺のみ                      |                                 |                                 |

| 熱的に飽和した            | 上層        | 大きなグランド プレーンと電源プレーン            | 34.1                            | なし                              |

|                    | 内層 1      | 1 つの大きなグランド プレーン               |                                 |                                 |

|                    | 内層 2      | トレースと 1 つの大きなグランド プレーン         |                                 |                                 |

|                    | 下層        | 1 つの大きなグランド プレーン               |                                 |                                 |

|                    | 追加のサーマルビア | デバイスの周囲および PCB 全体              |                                 |                                 |

(1) 専用のグランド プレーンを持たない高密度アプリケーションを再現することを意図しています。

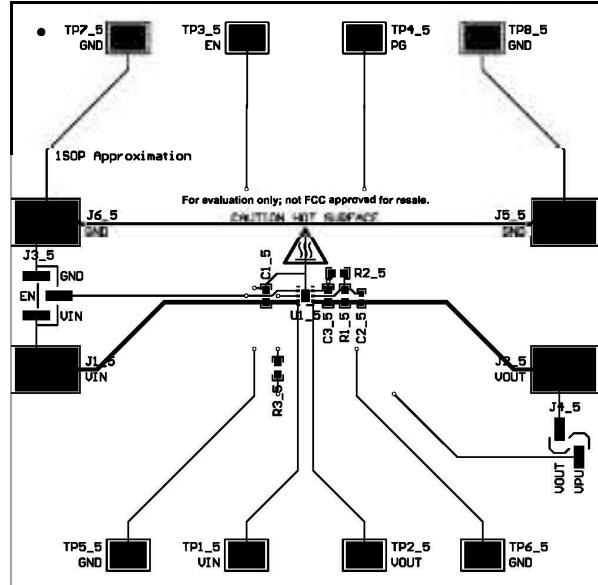

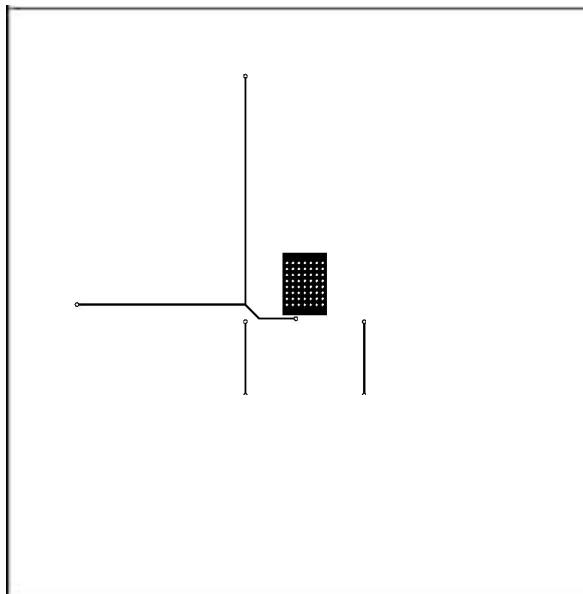

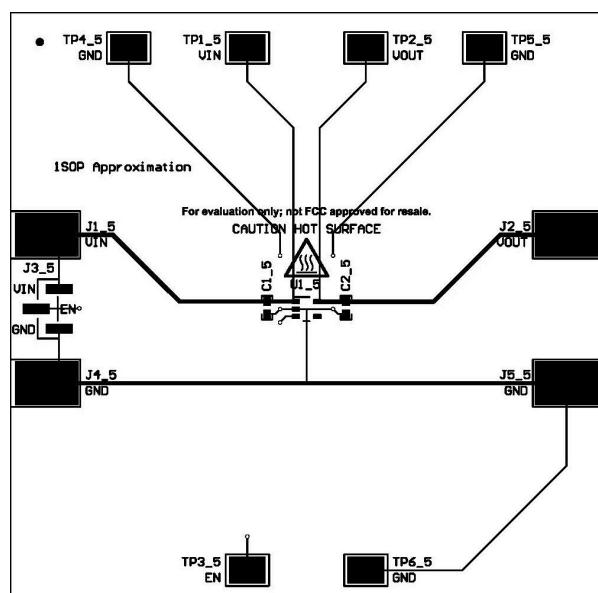

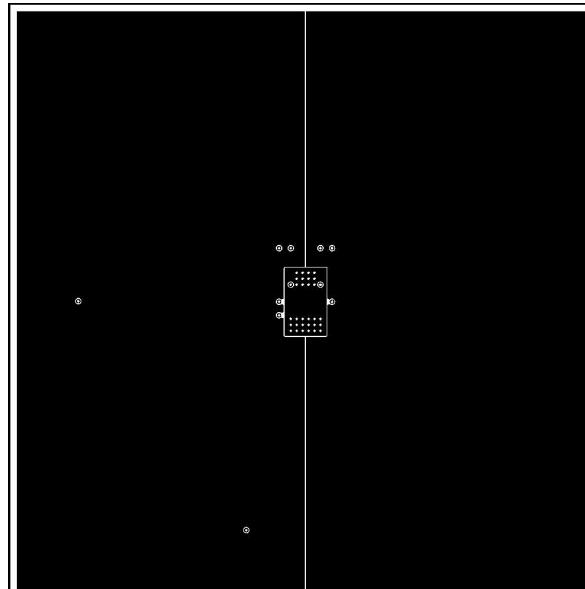

図 1-1. TPS745 (WSON) 1S0P の近似レイアウト

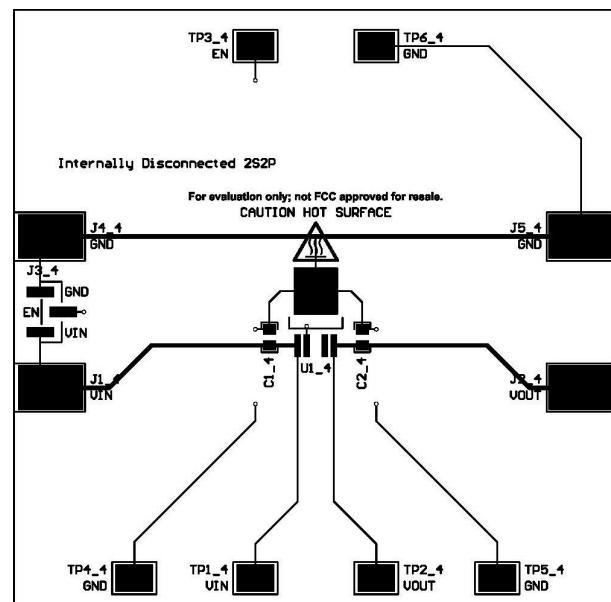

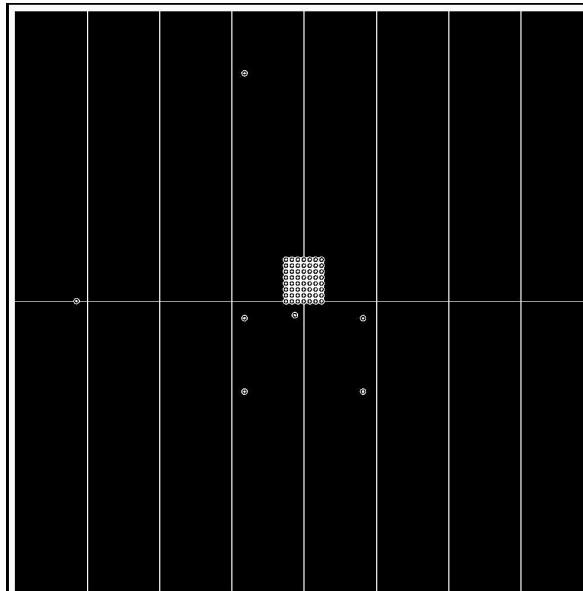

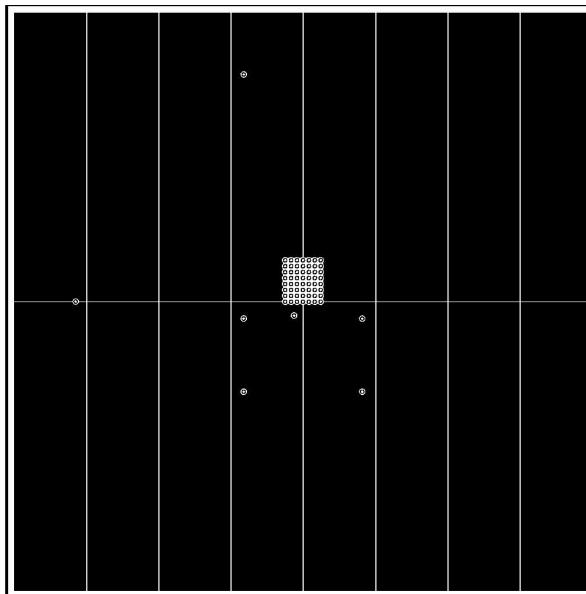

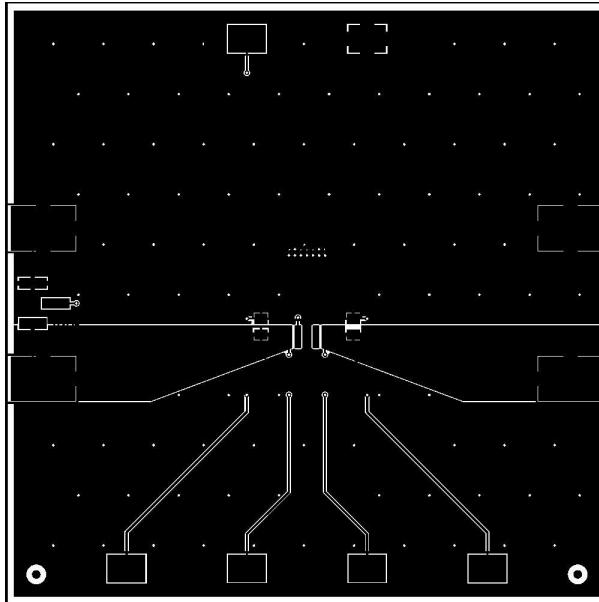

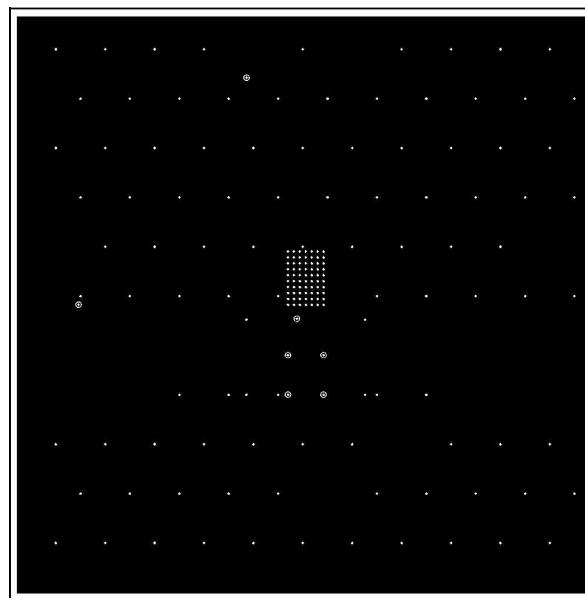

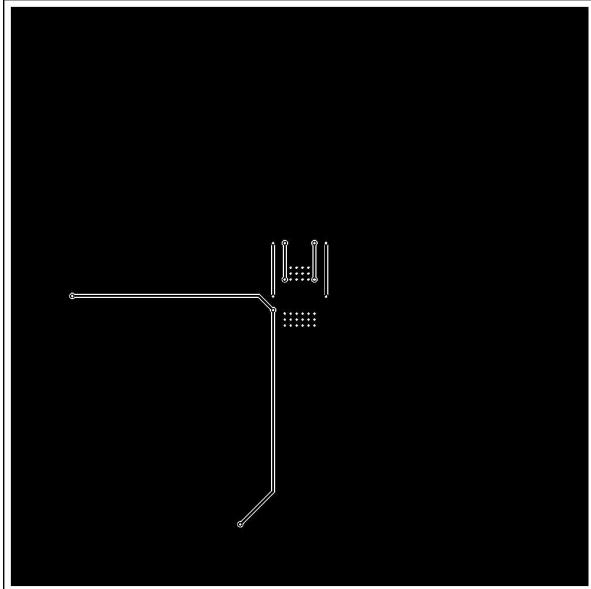

図 1-2. TPS745 (WSON) の内部的に切断されたレイアウト

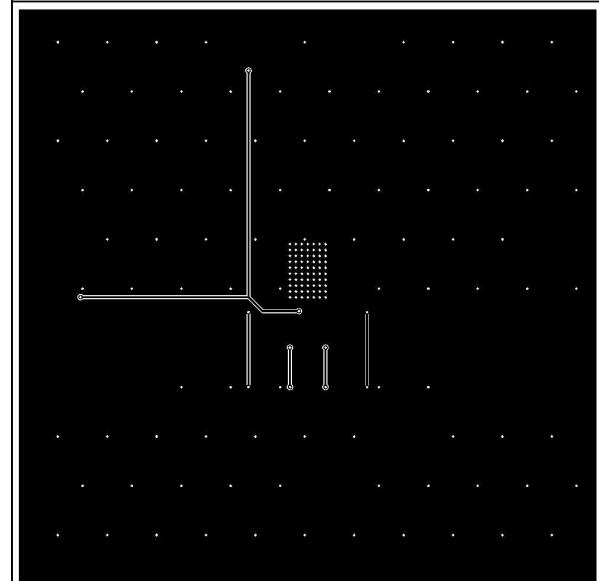

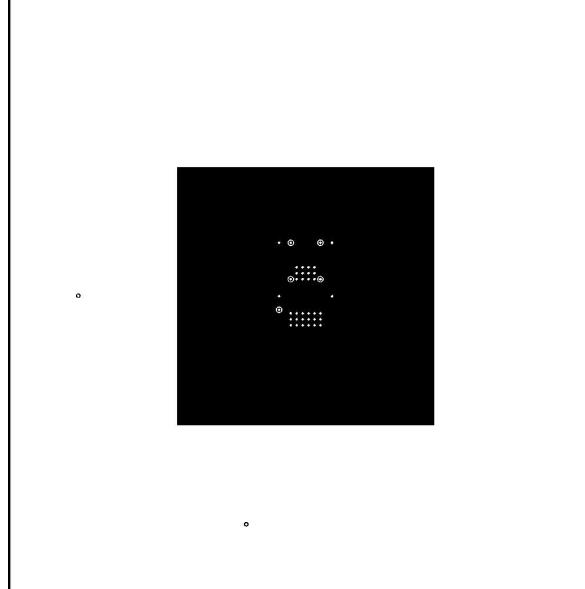

図 1-3. TPS745 (WSON) の JEDEC High-K 近似レイアウト

図 1-4. TPS745 (WSON) の熱的に強化されたレイアウト

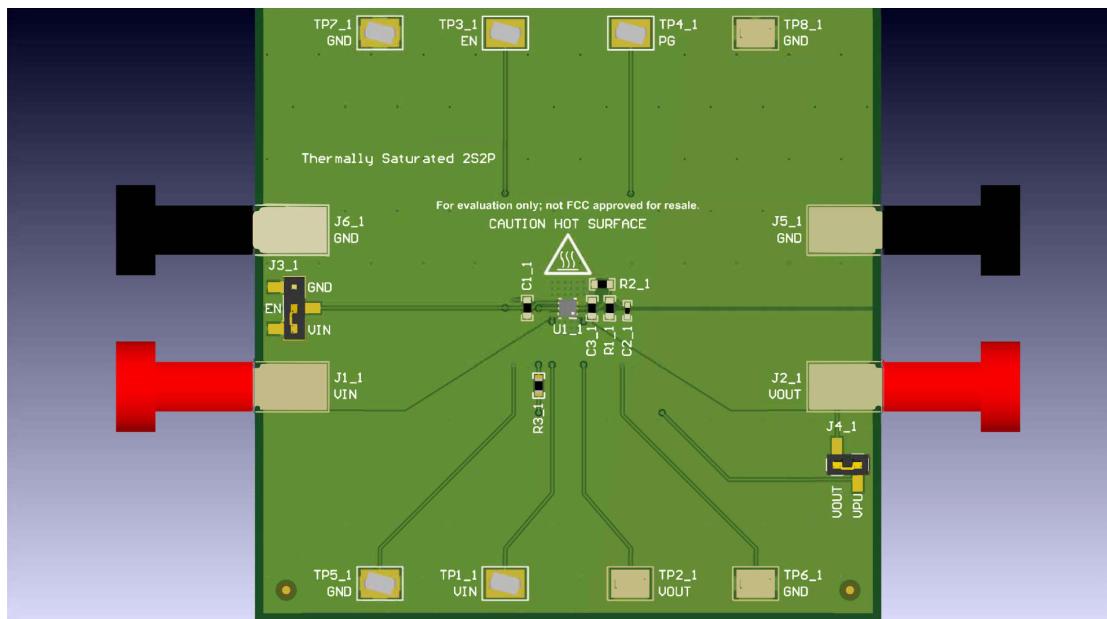

図 1-5. TPS745 (WSON) の熱的に飽和したレイアウト

## 2 手順

最新の LDO のほとんどは、接合部温度の上昇による過度の損傷からデバイスを保護するためにサーマル シャットダウン機能を備えています。サーマル シャットダウン機能付きの LDO では、与えられた消費電力レベルで決まる最高周囲温度を周囲温度が超えると、サーマル シャットダウンがトリガされ機能を停止します。[式 2](#) に、接合部温度をサーマル シャットダウン温度に置き換えて、[式 1](#) を並べ替えたものを示します。

$$T_{A,max} = T_{SD} - \theta_{JA} \times P_D \quad (2)$$

[『LDO の熱インピーダンスの in Situ 測定方法』アプリケーション レポート](#)は、この式を使用することで、デバイスの接合部に直接アクセスする必要なしい  $\theta_{JA}$  を決定できる方法について説明しています。まず、最高動作周囲温度が事実上 LDO のサーマル シャットダウン温度と等しくなるように、小さな消費電力を選択します。ホットオープンを使用して周囲温度を設定し、LDO を 5 分間浸します。JEDEC 標準モデルは強制対流がないことを想定しているため、ホットオープンをオフにして気流を停止する必要があります。次に、LDO 出力がシャットオフするかどうか、オシロスコープで監視します。この挙動（出力の停止）は、サーマル シャットダウンがトリガされたことを示します。LDO がサーマル シャットダウンに移行しない場合、周囲温度を上げ、この手順を繰り返して最高動作周囲温度を求めます。[式 2](#) を使用して  $\theta_{JA}$  を計算するときは、十分な線形回帰を提供するため、消費電力のレベルを上げてこの手順を繰り返します。

測定の際に周囲温度と消費電力が変化しやすいため、この手順の精度には多少の限界があります。自然対流を確保するためホットオープンをオフにすると、周囲温度が徐々に低下します。ホットオープンによって発生する対流による冷却を取り除くと、デバイスの接合部温度も同時に上昇します。LDO リファレンスのバンドギャップの温度変化に対するドリフトにより、出力電圧は下がり、パストランジスタの消費電力は増大します。ホットオープンの測定精度（通常は±2°C）により、 $\theta_{JA}$  の測定精度も低下します。これらの制限に対処するには、可能な限り広い周囲温度の範囲を示せるよう、幅広い消費電力レベルを選択する必要があります。[式 2](#) は、 $\theta_{JA}$  がこれら 2 つの変数間のトレンドラインの勾配として定義されていることを示しています。このため、広い温度範囲と消費電力にわたって線形性が維持されていることを確認すると、 $\theta_{JA}$  測定の信頼性が向上します。

この手順の主な利点は、比較的単純なことです。特定の基板や接合部温度を測定するために PCB や LDO に変更を加える必要がないため、任意の基板の  $\theta_{JA}$  を測定する目的で使用できます。これにより、精度の犠牲を最小限に抑えながら、システム設計者に適用できる、より現実的な PCB レイアウトおよびテスト環境を実現できます。本書の目的は、複数のパッケージにわたる PCB レイアウトと放熱性能の一般的な傾向を調査して設計者を支援することにあるため、機能テスト構成の作成を優先しています。

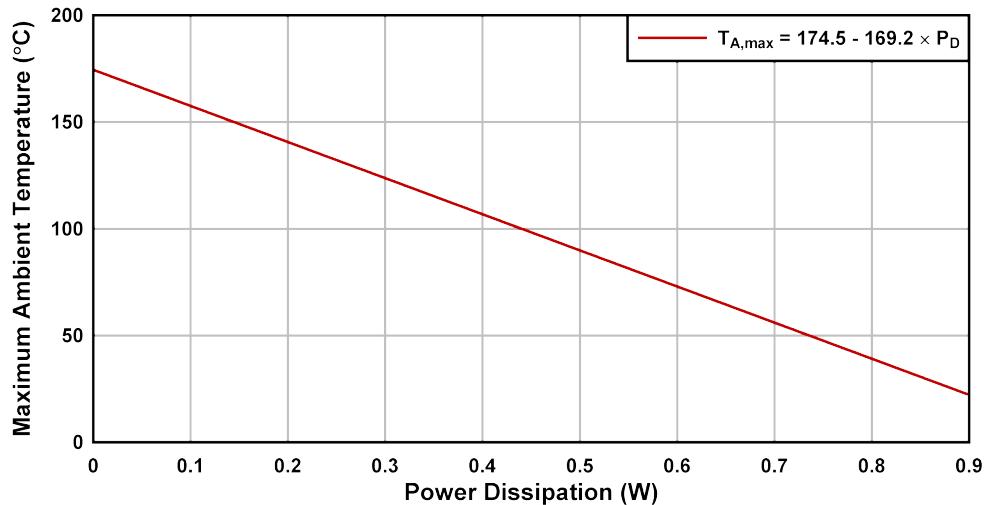

### 3 テスト結果と解説

1SOP 近似レイアウトの TPS745 (WSON パッケージ) の最大周囲温度と消費電力との関係を、図 3-1 に示します。トレンドラインの勾配は、 $169.2\text{C}/\text{W}$  の  $\theta_{JA}$  を示しています。収集されたデータの範囲と直線性は、式 2 で説明されている LDO の消費電力と、最大動作周囲温度との間の予想される関係を支持しています。

図 3-1. TPS745 (WSON) 1SOP の近似レイアウトのテスト結果

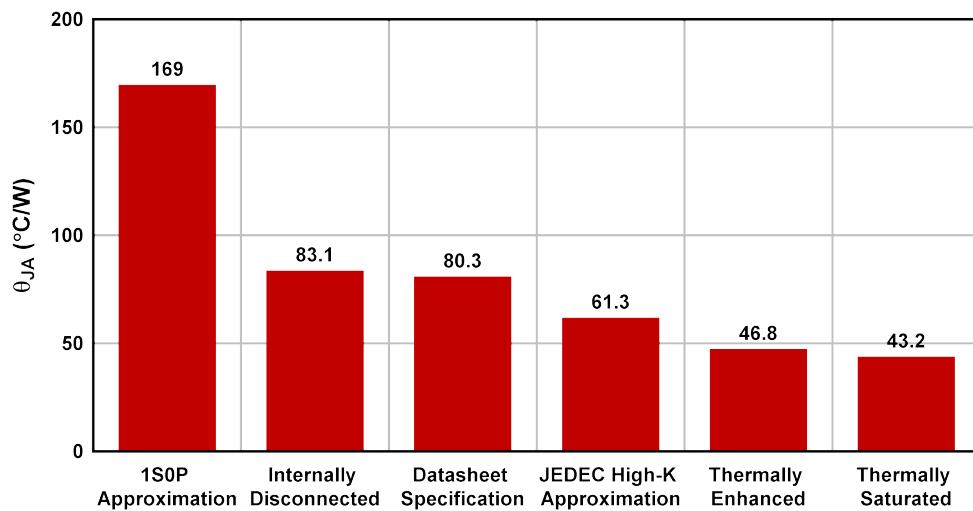

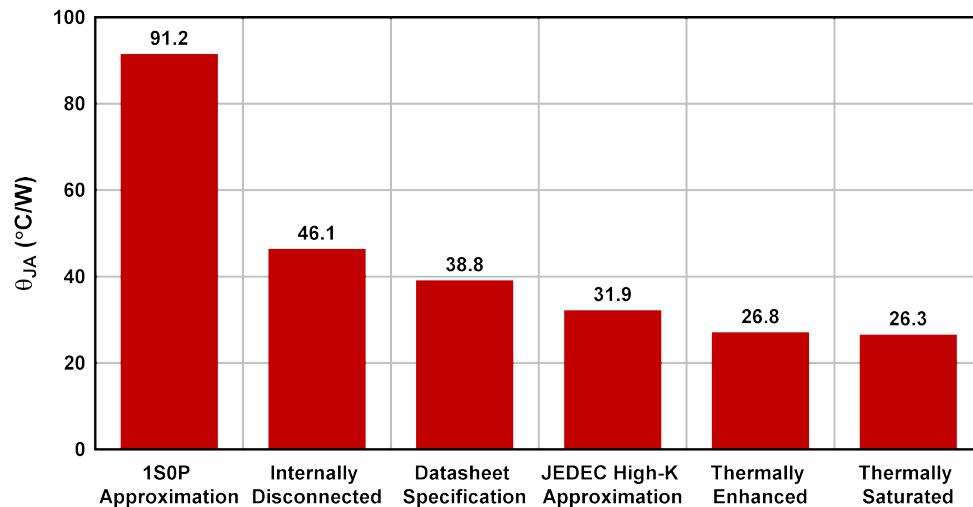

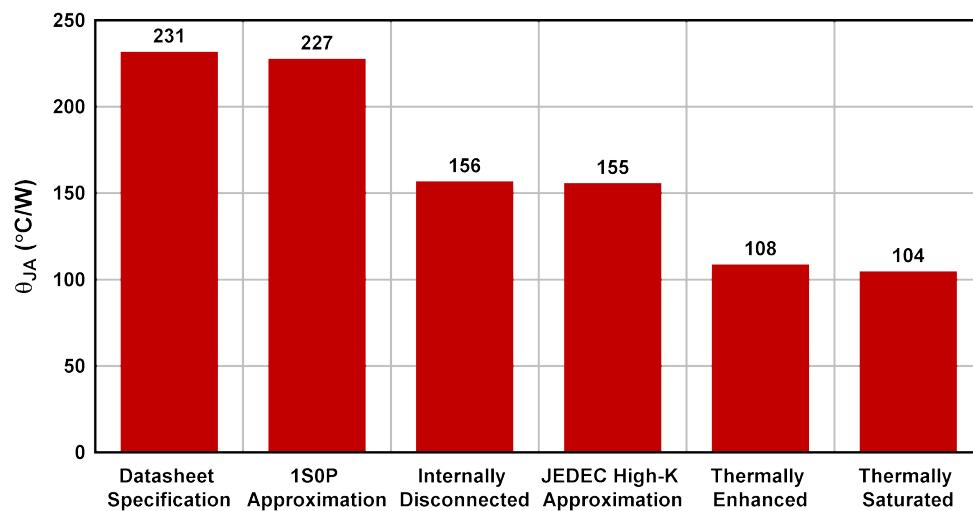

Appendix B には、すべてのパッケージとレイアウトについて収集された同様のデータが示されています。図 3-2 と図 3-3 には、TPS745 (WSON) および TPS7B82-Q1 (TO-252) について得られた  $\theta_{JA}$  値が示されています。これらのパッケージは、5 つのレイアウトすべてにわたって、放熱性能に関して同様のトレンドを示しています。内部的に切断されたレイアウトでは、接続された銅の面積がわずか  $0.07\text{in}^2$  ですが、 $\theta_{JA}$  が約 50% 低減しています。これは、この銅を LDO に直接接続していない場合でも、内層に銅を含めることで放熱性能が大幅に向上去ることを示しています。他のレイアウトでは、銅とサーマルマリビアが増えるにつれ、さらに少しずつ  $\theta_{JA}$  は小さくなり、70% を若干上回ったところで最大の低減率に達します。収集されたデータに基づいて、WSON および TO-252 パッケージでは、放熱効率の高いレイアウトが不可欠です。レイアウトが効率的でない場合、 $\theta_{JA}$  はデータシートで規定された値よりも大幅に大きくなるため、放熱性能の計算が複雑になり、最大動作周囲温度が低下し、デバイスの寿命と信頼性が低下する可能性があります。

図 3-2. TPS745 (WSON) の  $\theta_{JA}$  と基板レイアウトとの関係

図 3-3. TPS7B82-Q1 (TO-252) の  $\theta_{JA}$  と基板レイアウトとの関係

図 3-4 に、TLV755P (SOT-23) の  $\theta_{JA}$  測定値を示します。SOT-23 パッケージにおける  $\theta_{JA}$  の傾向の違いは、サーマルパッドがないことに起因します。JEDEC 標準規格では、サーマルパッドのないパッケージについては、High-K 热テスト基板へのサーマルビアの追加を認めていません。内層および下層に多少の熱を放散できるため、1SOP 近似と、データシート仕様の派生元となる JEDEC High-K テスト基板の熱モデルでは、非常に類似した性能を達成しています。複数の異なるレイアウトで性能が同じにならないよう、内部分離レイアウトではデバイスの下にサーマルビアを 1 つ設けて、上層のグランドトレースを下層のグランドプレーンに接続しました。これに対し、JEDEC High-K 近似レイアウトは、2 つのビアで上層のグランドトレースを内層に接続して、同様の性能を示しています。ビアを 1 つ追加しただけでは、JEDEC High-K 近似レイアウトに存在する追加の銅箔にもかかわらず、 $\theta_{JA}$  を大幅に改善するだけの十分な熱伝達特性は得られません。

熱的に強化された基板と熱的に飽和した基板は、JEDEC High-K 近似基板と比較して  $\theta_{JA}$  が約 33% 低減されています。これは、TPS745 と TPS7B82-Q1 の同様な比較をはるかにこえるものです。これは、SOT-23 パッケージにはサーマルパッドがないということで説明ができます。熱的に強化されたレイアウトと熱的に飽和したレイアウトは、上層に銅プレーンを含む唯一のレイアウトです。このパッケージにはサーマルパッドがないため、放熱の大半は上層で行われます。そのため、上層に銅を含めることがはるかに効果的です。さらに、熱的強化パッケージと熱的飽和パッケージでは、追加したサーマルビアが、内層および下層に熱を拡散させる唯一の経路です。これに対し、TPS745 と TPS7B82-Q1 のレイアウトでは、サーマルビアがサーマルパッド直下に設けられているため、サーマルビアを追加することによる効果を小さくしています。

図 3-4. TLV755P (SOT-23) の  $\theta_{JA}$  と基板レイアウトとの関係

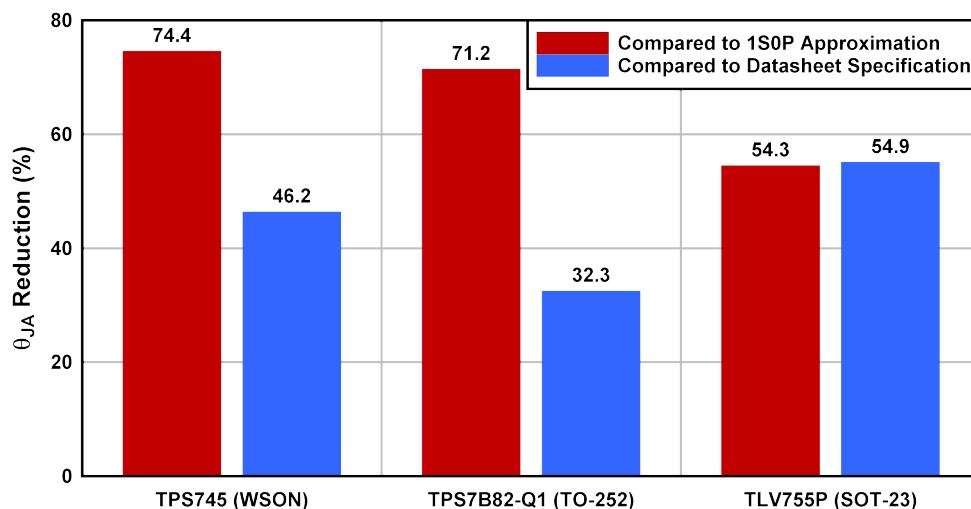

図 3-5 に、PCB レイアウトの効果とパッケージタイプとの関係を比較したものです。有効性は、 $\theta_{JA}$  の減少に対するパーセンテージで計算されます。式 3 で計算したように、熱効率の高いレイアウトでは、データシートで規定されている  $\theta_{JA}$  をパッケージに応じて 32% ~ 55% の範囲で低減できます。データシートで規定されている  $\theta_{JA}$  を使用すると、LDO の接合部温度の上昇を控えめに推定できます。ただし、式 2 に示すように、熱効率の高いレイアウトを使用すると、接合部温度の経験的な上昇を 32% ~ 55% 低減できます。この改善を考慮することで、動作時周囲温度を高くするか、消費電力を高いレベルにするか、またはこれら 2 つを組み合わせることができます。式 4 を使用した 1SOP 近似レイアウトとの比較は、放熱効率の優れたレイアウトの重要性を示しています。このワースト ケースのレイアウトと比較して、放熱効率の優れたレイアウトでは測定される  $\theta_{JA}$  が最小で 4 分の 1 まで小さくなります。

$$\text{Reduction of } \theta_{JA} \text{ compared to Datasheet Specification} = \left( 1 - \frac{\theta_{JA,\text{saturated}}}{\theta_{JA,\text{datasheet}}} \right) \times 100 \quad (3)$$

$$\text{Reduction of } \theta_{JA} \text{ compared to 1SOP Approximation} = \left( 1 - \frac{\theta_{JA,\text{saturated}}}{\theta_{JA,1SOP}} \right) \times 100 \quad (4)$$

図 3-5. 各デバイスでの  $\theta_{JA}$  の低減

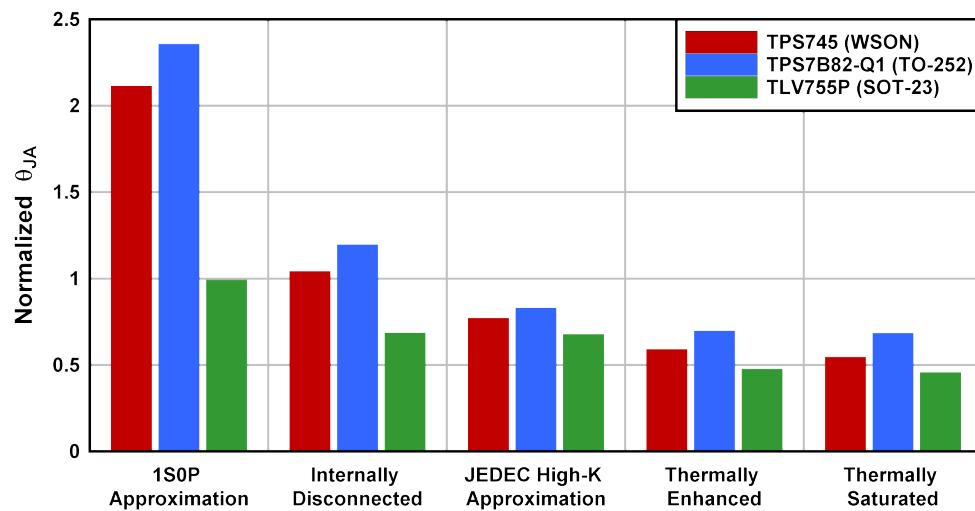

図 3-6 は、図 3-2、図 3-3、図 3-4 から得られた結果を、式 5 を使用してデータシートの仕様に相対的に正規化したものです。

$$\theta_{JA,\text{normalized}} = \frac{\theta_{JA,\text{measured}}}{\theta_{JA,\text{datasheet}}} \quad (5)$$

この図は、3 つのパッケージで収集されたデータをまとめたもので、本調査の重要な発見を示しています。まず、PCB の銅成分と  $\theta_{JA}$  との間には、銅量の増加に伴って飽和する反比例の関係があります。この関係はパッケージに関係なく観察できます。1SOP 近似と内部的に切断されたレイアウトとの間で見られる大幅な低下が示すように、熱性能を向上させるために銅成分を LDO に接続する必要はありません。また、デバイスの周囲にサーマルビアを追加することでも、LDO から発生した熱を内層および下層に放散する経路が増えるため、熱性能は向上します。このビアは、専用のサーマル パッドがない SOT-23 などのパッケージでは特に重要です。しかし、熱的に強化されたレイアウトと熱的に飽和したレイアウトとでは改善の差が極めて小さいことから分かるように、サーマルビアの追加による  $\theta_{JA}$  の改善効果は飽和します。

図 3-6. 各デバイスと基板レイアウトの正規化された  $\theta_{JA}$

## 4 まとめ

LDO の放熱性能のうち、接合部周囲間の熱抵抗  $\theta_{JA}$  は PCB 設計の影響を強く受けます。ただし、PCB の影響は、最終的には LDO のパッケージによって制限されます。WSON パッケージや TO-252 パッケージといったサーマルパッド付きのパッケージは放熱しやすいため、 $\theta_{JA}$  の総低減率は、ワーストケースの 1SOP 近似レイアウトと比較して、それぞれ 74% および 71% 大きくなります。SOT-23 パッケージでは、この低減率が 54% に減少しますが、それでも大幅な減少です。**図 3-5** は、熱的に最適化されたレイアウトではデータシートの仕様と比較して  $\theta_{JA}$  を 32% ~ 55% も低減できることを示しています。この結果から、データシートに規定されている  $\theta_{JA}$  を熱計算に使用すると、放熱性能が低めに推定されることを示しています。ただし、熱効率の高いレイアウトを使用すれば、より高い周囲温度や、より高レベルの消費電力での動作が可能になり、さらにこれら 2 つの利点を両立させることも可能である点に留意してください。

**図 3-6** は、パッケージタイプに関係なく、PCB の銅量の増加に伴って放熱性能が飽和することを示しています。3 つのパッケージすべてについて、熱的に強化されたレイアウトは熱的に飽和したレイアウトと比べて銅の面積が約半分しかありませんが、 $\theta_{JA}$  の差異は 8% 以内です。同様に、サーマルビアの追加による放熱性能の向上も飽和しています。PCB 全体にビアを追加しても、熱的に飽和したレイアウトで見られるような利点はほとんどありません。熱的に強化された基盤と同様なレイアウトにより、十分な放熱性能を持つ設計を実現できます。よりコンパクトな設計については、**図 3-4** を参照してください。この図は、TLV755P (SOT-23) の測定結果を示しています。これらの結果は、上層と下層の銅箔を最大にする必要があることを示しています。これらの層は追加の PCB 材質で囲まれていないため、最も効果的に放熱できます。サーマルビアは、LDO から生じた熱を他の銅層に効果的に拡散するためにのみ、デバイスの周囲に追加する必要があります。SOT-23 パッケージなど、サーマルパッドのないパッケージで設計する際、これらのビアは特に重要です。この場合、ほとんどの熱が発生するデバイス直下にサーマルビアを配置することができます。<https://www.jedec.org/system/files/docs/JESD51-9.pdf> に従って、サーマルパッド付きのパッケージではランドパッドのサーマルビアの数を最大限に増やします。最後に、内部分離されたすべてのレイアウトからのデータ **図 3-6** は、可能であれば内層に銅箔を追加する必要があり、LDO に直接接続されていない場合でも放熱性能に好影響を与えることが示されています。

## 5 今後の調査

今後の調査により対処できる分野がいくつかあります。1 つは、従来は放熱性能が低かった DSBGA や X2SON などの超小型 ( $1\text{mm}^2$  未満) パッケージに対して、これらの、または類似のレイアウトが及ぼす影響を調べることです。小型パッケージは本質的に放熱性能が低いため、この PCB レイアウトでは WSON、TO-252、SOT-23 パッケージと比較して放熱性能への影響が小さい可能性があります。もう 1 つは、この研究の延長線上にあるより複雑なもので、接続されている銅の面積、接続されていない銅の面積、基板の積層に対するこれらの面積の位置、サーマルビアの数などを組み込んだ式または性能指数 (FOM) を求める 것입니다。この FOM は基板の等価熱インピーダンスと相関しており、それを適用すると、特定のレイアウトで予想される  $\theta_{JA}$  をより正確に特定できます。

## 6 参考資料

- 『小型 SMD パッケージに封止した LDO の放熱性能』アプリケーションレポート

- 『AN-1520 露出パッケージで最良の熱抵抗を実現するための基板レイアウトガイド』アプリケーションレポート

- 『半導体および IC パッケージの熱評価基準』

- 『リード付き表面実装パッケージ用の有効熱伝導率の低いテスト基板』

- 『リード付き表面実装パッケージ用の有効熱伝導率の高いテスト基板』

- 『エリアアレイ表面実装パッケージの熱測定用テスト基板』

- 『LDO の熱インピーダンスの *in-situ* 測定方法』アプリケーションレポート

## 7 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision * (February 2019) to Revision A (Septemeber 2025) | Page |

|-------------------------------------------------------------------------|------|

| • ドキュメント全体にわたって表、図、相互参照の採番方法を更新.....                                    | 2    |

## A 热テスト基板のレイアウト

### A.1 TPS745 (WSON) の図

#### A.1.1 1SOP 近似のレイアウト図

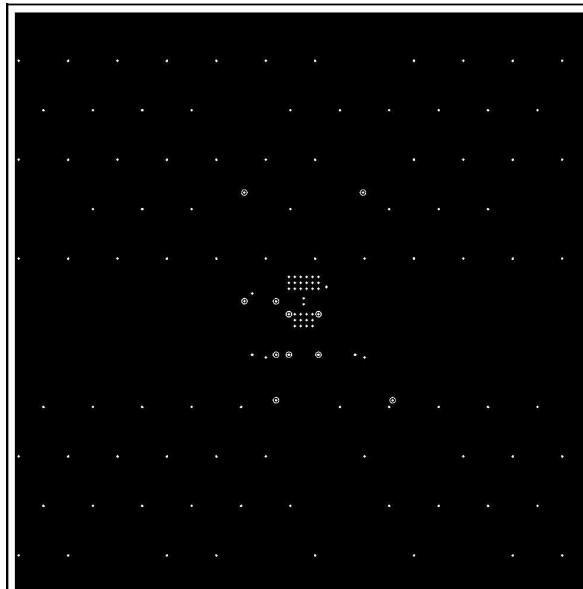

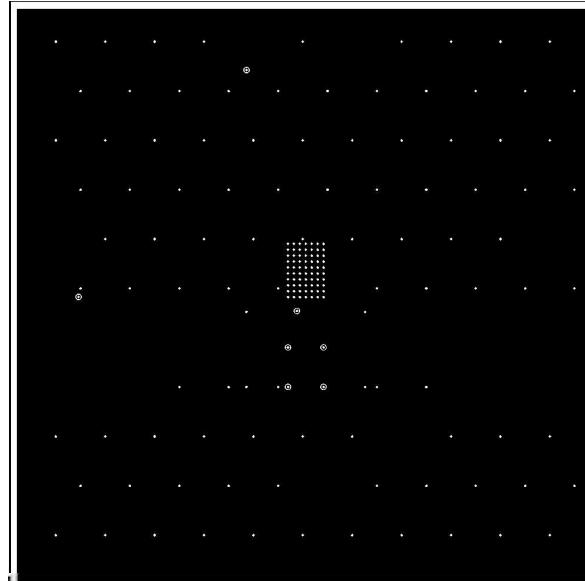

図 A-1. TPS745 (WSON) 1SOP 近似の上層

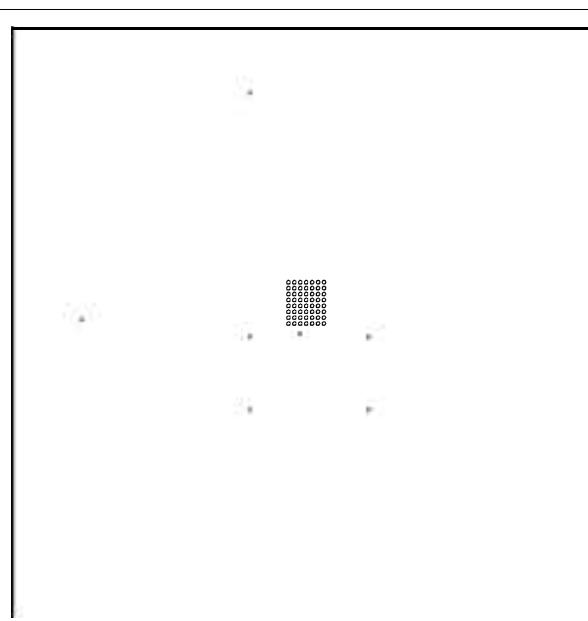

図 A-2. TPS745 (WSON) 1SOP 近似の内層 1

図 A-3. TPS745 (WSON) 1SOP 近似の内層 2

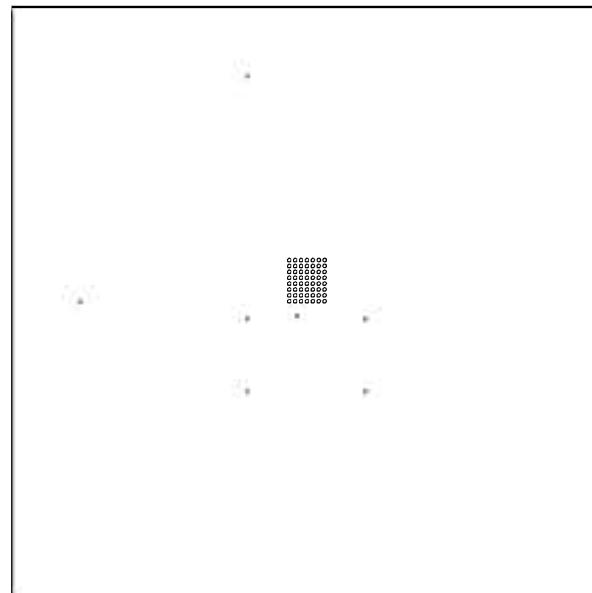

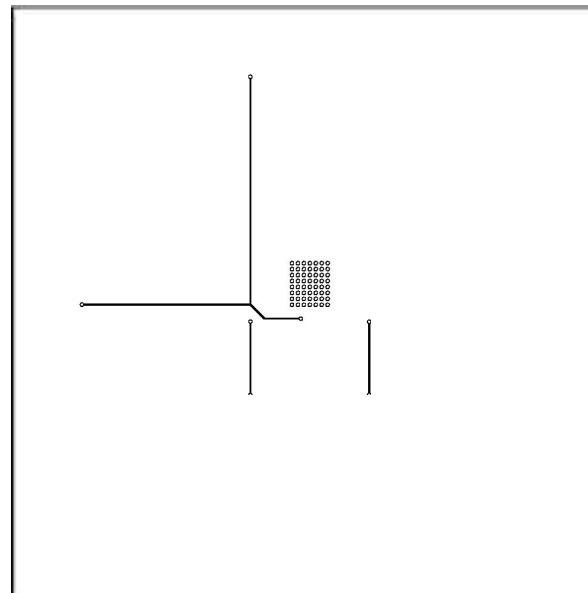

図 A-4. TPS745 (WSON) 1SOP 近似の下層

### A.1.2 内部的に切断されたレイアウトの図

図 A-5. TPS745 (WSON) の内部的に切断された上層

図 A-6. TPS745 (WSON) の内部的に切断された内層 1

図 A-7. TPS745 (WSON) の内部的に切断された内層 2

図 A-8. TPS745 (WSON) の内部的に切断された下層

### A.1.3 JEDEC High-K の近似レイアウト図

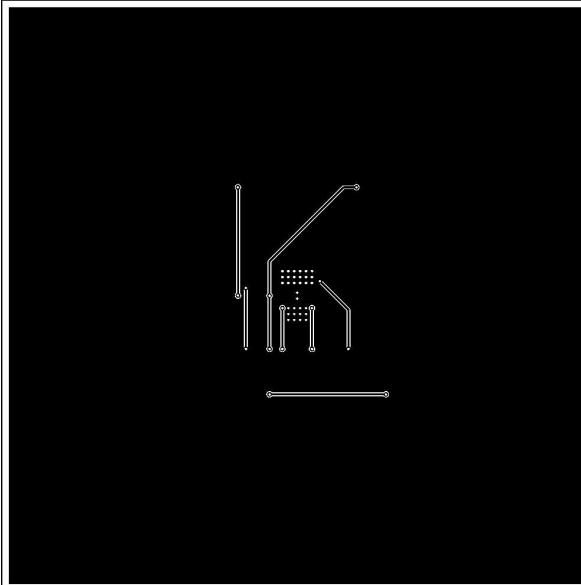

#### A.1.4 热的に強化されたレイアウト図

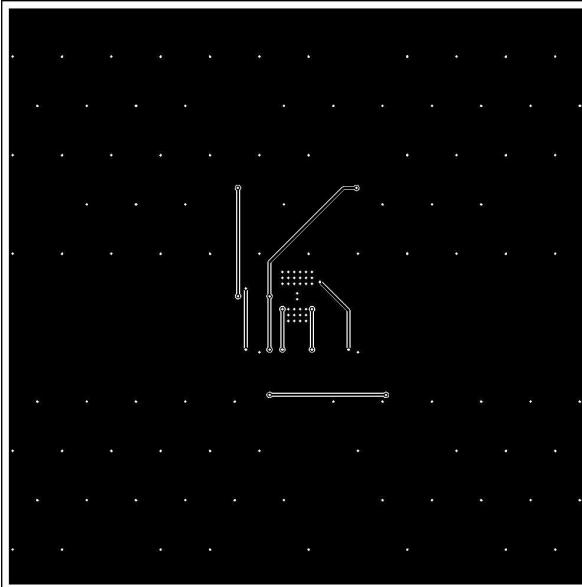

図 A-13. TPS745 (WSON) の熱的に強化された上層

図 A-14. TPS745 (WSON) の熱的に強化された内層 1

図 A-15. TPS745 (WSON) の熱的に強化された内層 2

図 A-16. TPS745 (WSON) の熱的に強化された下層

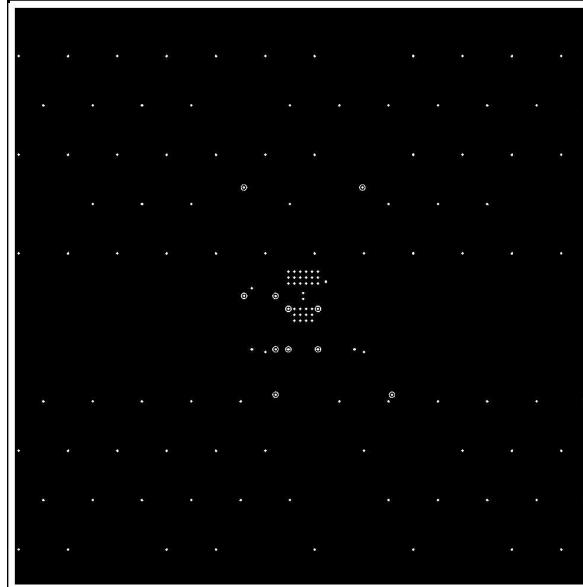

#### A.1.5 热的に飽和したレイアウト図

図 A-17. TPS745 (WSON) の熱的に飽和した上層

図 A-18. TPS745 (WSON) の熱的に飽和した内層 1

図 A-19. TPS745 (WSON) の熱的に飽和した内層 2

図 A-20. TPS745 (WSON) の熱的に飽和した下層

## A.2 TPS7B82-Q1 (TO-252) の図

### A.2.1 1SOP 近似のレイアウト図

図 A-21. TPS7B82-Q1 (TO-252) 1SOP 近似の上層

図 A-22. TPS7B82-Q1 (TO-252) 1SOP 近似の内層 1

図 A-23. TPS7B82-Q1 (TO-252) 1SOP 近似の内層 2

図 A-24. TPS7B82-Q1 (TO-252) 1SOP 近似の下層

### A.2.2 内部的に切断されたレイアウトの図

図 A-25. TPS7B82-Q1 (TO-252) の内部的に切断された上層

図 A-26. TPS7B82-Q1 (TO-252) の内部的に切断された内層 1

図 A-27. TPS7B82-Q1 (TO-252) の内部的に切断された内層 2

図 A-28. TPS7B82-Q1 (TO-252) の内部的に切断された下層

### A.2.3 JEDEC High-K の近似レイアウト図

#### A.2.4 热的に強化されたレイアウト図

図 A-33. TPS7B82-Q1 (TO-252) の熱的に強化された上層

図 A-34. TPS7B82-Q1 (TO-252) の熱的に強化された内層 1

図 A-35. TPS7B82-Q1 (TO-252) の熱的に強化された内層 2

図 A-36. TPS7B82-Q1 (TO-252) の熱的に強化された下層

#### A.2.5 热的に飽和したレイアウト図

図 A-37. TPS7B82-Q1 (TO-252) の熱的に飽和した上層

図 A-38. TPS7B82-Q1 (TO-252) の熱的に飽和した内層

1

図 A-39. TPS7B82-Q1 (TO-252) の熱的に飽和した内層

2

図 A-40. TPS7B82-Q1 (TO-252) の熱的に飽和した下層

## A.3 TLV755P (SOT-23) の図

### A.3.1 1SOP 近似のレイアウト図

図 A-41. TLV755P (SOT-23) 1SOP 近似の上層

図 A-42. TLV755P (SOT-23) 1SOP 近似の内層 1

図 A-43. TLV755P (SOT-23) 1SOP 近似の内層 2

図 A-44. TLV755P (SOT-23) 1SOP 近似の下層

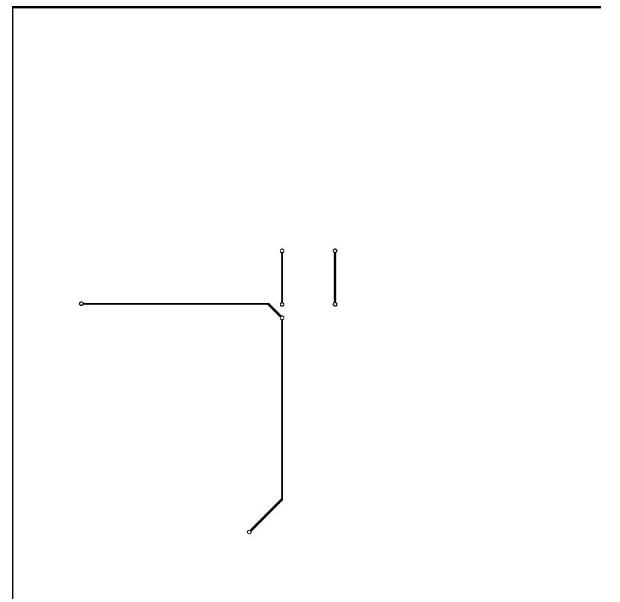

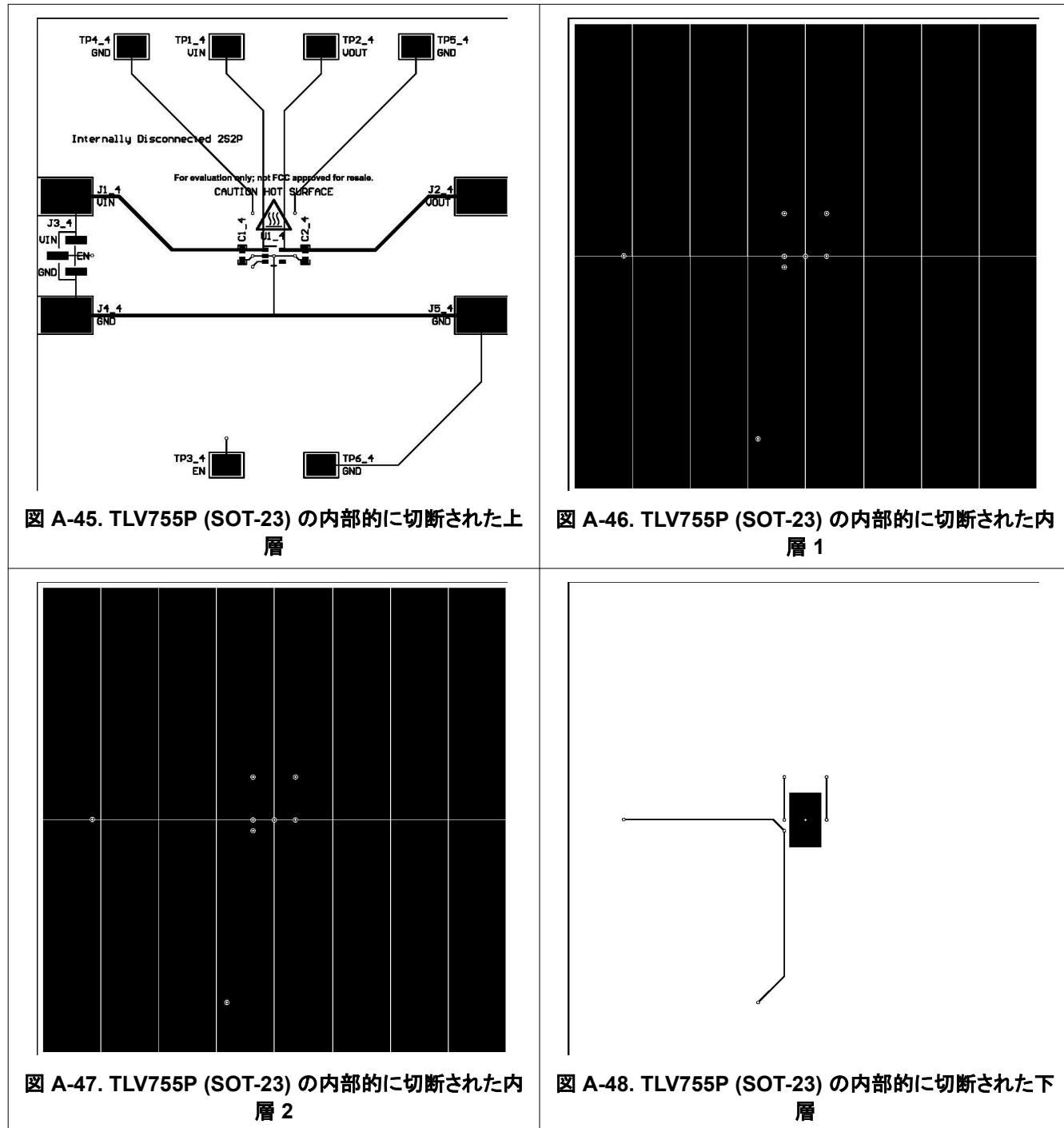

### A.3.2 内部的に切断されたレイアウトの図

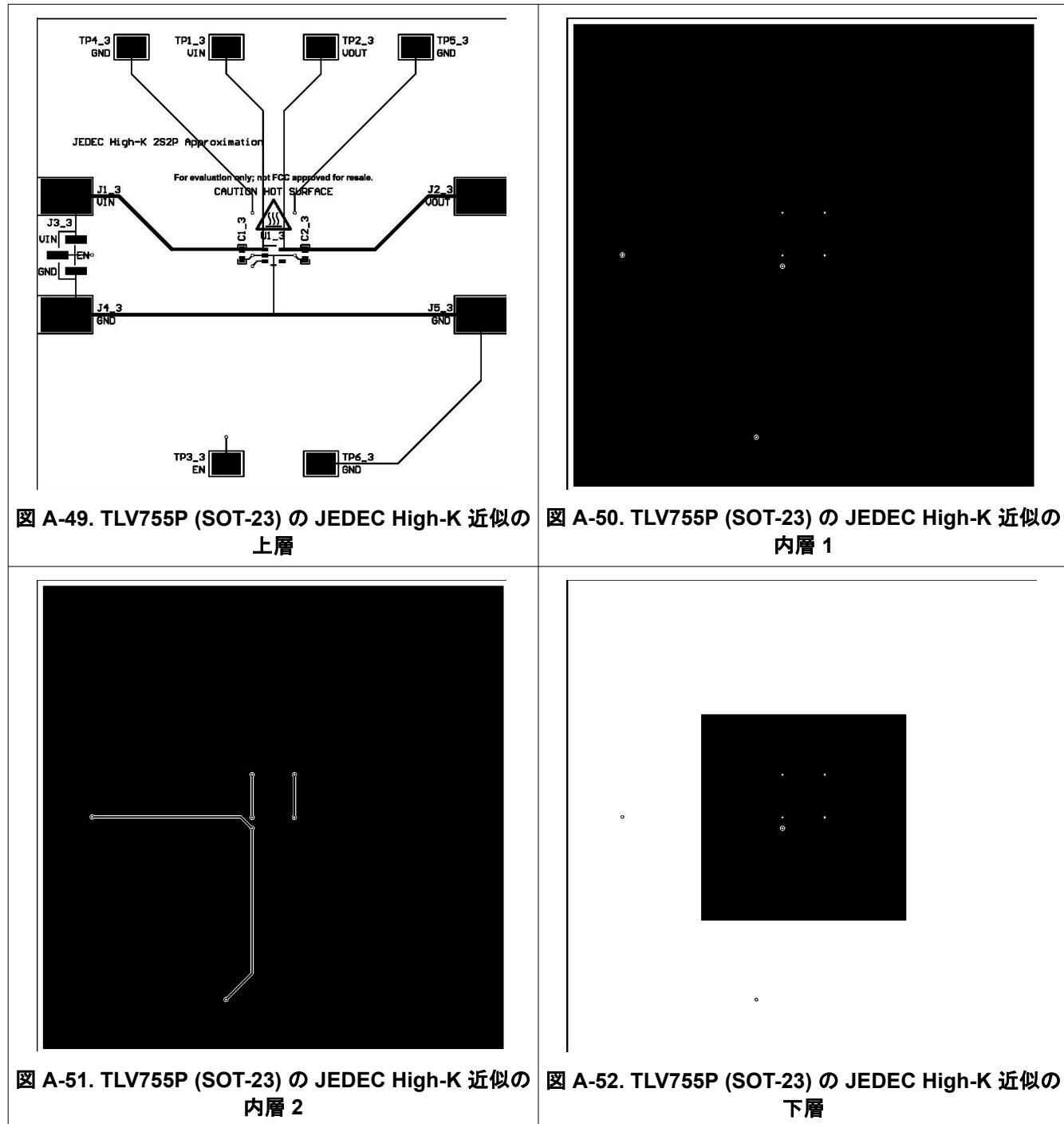

### A.3.3 JEDEC High-K の近似レイアウト図

図 A-49. TLV755P (SOT-23) の JEDEC High-K 近似の上層

図 A-50. TLV755P (SOT-23) の JEDEC High-K 近似の内層 1

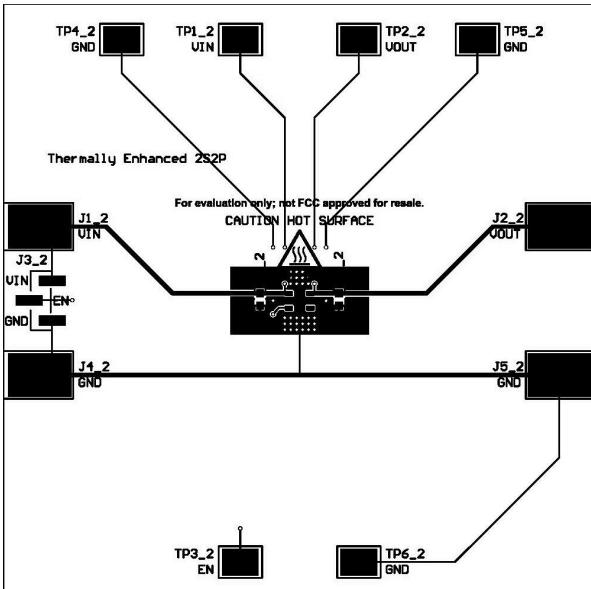

#### A.3.4 热的に強化された図

図 A-53. TLV755P (SOT-23) の熱的に強化された上層

図 A-54. TLV755P (SOT-23) の熱的に強化された内層 1

図 A-55. TLV755P (SOT-23) の熱的に強化された内層 2

図 A-56. TLV755P (SOT-23) の熱的に強化された下層

### A.3.5 热的に飽和したレイアウト図

図 A-57. TLV755P (SOT-23) の熱的に飽和した上層

図 A-58. TLV755P (SOT-23) の熱的に飽和した内層 1

図 A-59. TLV755P (SOT-23) の熱的に飽和した内層 2

図 A-60. TLV755P (SOT-23) の熱的に飽和した下層

## B 热テストの結果

### B.1 放热性能データ

表 B-1. 最大周囲温度と消費電力との関係

| ボード             | TPS745 (WSON)      |                          | TPS7B82-Q1 (TO-252) |                          | TLV755P (SOT-23)   |                          |

|-----------------|--------------------|--------------------------|---------------------|--------------------------|--------------------|--------------------------|

|                 | P <sub>D</sub> (W) | T <sub>A, max</sub> (°C) | P <sub>D</sub> (W)  | T <sub>A, max</sub> (°C) | P <sub>D</sub> (W) | T <sub>A, max</sub> (°C) |

| 1SOP 近似         | 0.00               | 175                      | 0.00                | 182                      | 0.00               | 165                      |

|                 | 0.26               | 130                      | 0.51                | 135                      | 0.20               | 124                      |

|                 | 0.51               | 88                       | 1.00                | 90                       | 0.39               | 80                       |

|                 | 0.90               | 23                       | 1.70                | 27                       | 0.62               | 24                       |

| 内部的に切断された       | 0.00               | 178                      | 0.00                | 178                      | 0.00               | 164                      |

|                 | 0.59               | 129                      | 1.00                | 134                      | 0.25               | 126                      |

|                 | 1.14               | 83                       | 1.95                | 88                       | 0.49               | 88                       |

| JEDEC High-K 近似 | 0.00               | 178                      | 0.00                | 180                      | 0.00               | 163                      |

|                 | 0.74               | 130                      | 1.53                | 133                      | 0.27               | 122                      |

|                 | 1.49               | 87                       | 3.01                | 84                       | 0.53               | 81                       |

| 熱的に強化された        | 0.00               | 179                      | 0.00                | 178                      | 0.00               | 166                      |

|                 | 0.83               | 135                      | 1.77                | 129                      | 0.36               | 128                      |

|                 | 1.73               | 98                       | 3.51                | 84                       | 0.69               | 91                       |

| 熱的に飽和した         | 0.00               | 177                      | 0.00                | 177                      | 0.00               | 164                      |

|                 | 0.84               | 139                      | 1.81                | 128                      | 0.38               | 127                      |

|                 | 1.64               | 106                      | 3.62                | 82                       | 0.76               | 85                       |

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月