# Analog Engineer's Circuit

# プログラム可能、2段構成、ハイサイド電流源回路

Garrett Satterfield

#### 設計目標

| 電 | i源電圧 (V <sub>CC</sub> ) | DAC の出力電圧 | 出力電流    | エラー     | 最大負荷抵抗 | コンプライアンス<br>電圧 |

|---|-------------------------|-----------|---------|---------|--------|----------------|

|   | 5 V                     | 0V-2V     | 0∼100mA | <1% FSR | 45Ω    | 4.5 V          |

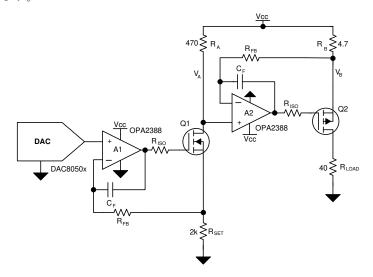

#### 設計の説明

プログラム可能なハイサイド電流源は、グランド基準の負荷に可変電流を供給します。最初のオペアンプ段は、DAC 出力電圧に基づいて基準電流を設定します。2 番目のオペアンプ段は、基準電流を増幅して出力 PMOS から負荷に供給される電流をレギュレートする電流ミラーとして機能します。R<sub>SET</sub>、RA、RB は、DAC 電圧に基づいて出力電流を設定します。 部品 C<sub>F</sub>、R<sub>ISO</sub>、R<sub>FB</sub> は回路の安定性を確保するために補償を行います。この回路を使用する一般的な最終製品として、PLC アナログ出力モジュール、フィールドトランスミッタ、デジタル マルチメータ、プリンタ、光モジュール、LEDドライバ、電子 POS が挙げられます。

#### デザイン ノート

- 1. オフセット、ゲイン、ドリフト誤差の小さい DAC を選択します。 コンプライアンス電圧を低く維持するため RRIO オペアンプを使用し、オフセットが小さいオペアンプを選択します。

- 2.  $R_A$ 、Q1、 $R_{SET}$  を流れる電流を最小限にするため、 $R_A$ : $R_B$  の比率を大きくして効率を最大化し、同時に最初の段における発熱とドリフトを最小限にします。

- 3. R<sub>SET</sub>、R<sub>A</sub>、R<sub>B</sub> には、抵抗のミスマッチと温度ドリフトによる誤差を最小限にするため、高精度で低ドリフトの抵抗を使用します。

- 4. コンプライアンス電圧を最大化するため、R<sub>B</sub>の抵抗は最小限にします。

- 5. 消費電力により発熱するため、熱に敏感な部品の近くに Q2 をレイアウト配置することは避けます。

#### 設計手順

1. V<sub>DAC</sub> に基づいて R<sub>SET</sub> を選択することで、シンク段の基準電流を設定します。この基準電流はグランドへ直接流れて効率を低下させるため、最小限に抑える必要があります。 基準電流を 1mA に設定し、R<sub>SET</sub> を計算します。

$$R_{SET} = \frac{V_{DAC,max}}{I_{SET}} = \frac{2V}{1mA} = 2k\Omega$$

- 2. 求められる出力電流と  $I_{OUT}/I_{SET}$  = 100mA/1mA = 100 ( $R_A$ : $R_B$  に要求される比率) に基づいて、必要なゲイン比率を設定します。

- 3. 最大負荷を経由して最大電流を駆動するときに許容される最大電圧降下から、R<sub>B</sub>の最大値を計算します。

$$R_B < \frac{V_{CC} - I_{OUT,max} R_{LOAD,max}}{I_{OUT,max}} = \frac{5V - 0.1A \times 45\Omega}{0.1A} = 5\Omega$$

4. 電圧  $V_A$  は  $V_{CC}$  -  $I_{SET} \times R_A$  であり、オペアンプの帰還に起因して、電圧  $V_B$  と等しくなります。目的のコンプライアンス電圧を維持するため、電圧降下が 500mV 未満となるよう  $R_A$  を選択します。標準抵抗値の 470 $\Omega$  を選択します。

$$V_A = V_B$$

$$R_A = \frac{V_{CC} - V_A}{I_{SET}} = \frac{470mV}{1mA} = 470\Omega$$

5.  $R_A$  と、手順 2 で選択したゲインに基づいて、 $R_B$  を計算します。

$$R_B = \frac{R_A}{100}$$

6. Q2 の消費電力を確認します。 Q2 の消費電力は、負荷に基づいて次のように与えられます。

$$P_{Diss,Q2} = V_{CC} \times I_{OUT} - I_{OUT}^{2} \times \left(R_{LOAD} + R_{B}\right) = 5V \times 0.1A - 0.1A^{2} \times \left(40\Omega + 4.7\Omega\right) = 0.053W$$

Q2 の最大消費電力は、負荷抵抗がゼロのときに発生します。

$$P_{Diss,Q2,max} = V_{CC} \times I_{OUT} - I_{OUT}^2 \times R_B = 5V \times 0.1A - 0.1A^2 \times 4.7 = 0.453W$$

Q2 の定格が、この消費電力を満たしていることを確認します。

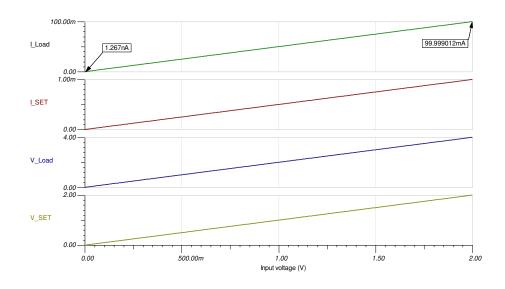

## DC 伝達特性

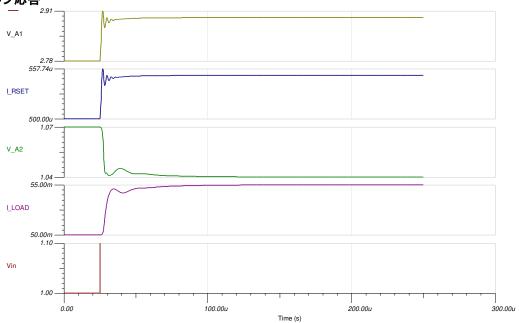

## 小信号ステップ応答

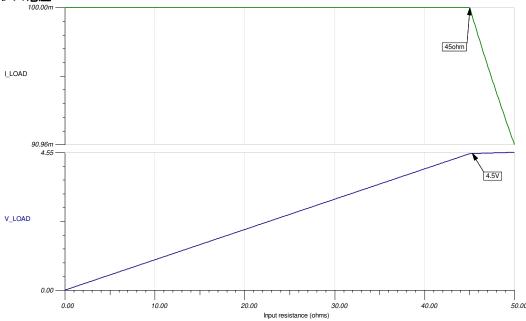

## コンプライアンス電圧

## 高電圧電源への変更

この回路の設計例では、V<sub>CC</sub> に低電圧電源を使用しています。4mA~20mA 電流ループなど一部のアプリケーションでは、大きな抵抗性負荷を駆動するために高電圧電源が必要となります。この電流源を高電圧電源用に変更するには、OPA192 などの高電圧、レールツーレール入出力のアンプを選択します。

## デバイス

| デバイス     | 主な特長                                                            | リンク                                                                    | 他の使用可能デバイス         |

|----------|-----------------------------------------------------------------|------------------------------------------------------------------------|--------------------|

| DAC      |                                                                 |                                                                        |                    |

| DAC80501 | 5ppm リファレンス内蔵、16 ビット分解能、1LSB INL、シングル チャネル、電圧出力 DAC             | WSON パッケージ封止、高精度基準電<br>圧内蔵、真の 16 ビット、1 チャネル、<br>SPI/I2C 対応、電圧出力 DAC    | 高精度 DAC (≦ 10MSPS) |

| DAC80508 | 5ppm リファレンス内蔵、16 ビット分解能、1LSB INL、8 チャネル、電圧出力 DAC                | 高精度基準電圧内蔵、真の 16 ビット、8<br>チャネル、SPI 対応、電圧出力 DAC                          | 高精度 DAC (≦ 10MSPS) |

| DAC8775  | DC/DC コンバータ内蔵の 16 ビット分解能、クワッド チャネル、±10V、<br>±24mA 電圧および電流出力 DAC | 電流出力/電圧出力対応のプログラマ<br>ブルなクワッド チャネル 16 ビット D/A コ<br>ンバータ (DAC)           | 高精度 DAC (≦ 10MSPS) |

| アンプ      |                                                                 |                                                                        |                    |

| OPA388   | 高精度、ゼロドリフト、ゼロクロスオーバー、レール ツー レール入出力、2.5V ~5.5V 電源                | シングル、10MHz、CMOS、ゼロドリフト、<br>ゼロクロスオーバ、真の RRIO (レール<br>ツーレール入出力) 高精度オペアンプ | オペアンプ              |

| OPA192   | 高精度、高電圧、レールツーレール入出力、4.5V~36V電源                                  | 高電圧、レールツーレール入出力、<br>5µV、0.2µV/℃、高精度オペアンプ                               | オペアンプ              |

| TLV170   | 低コストのレール ツー レール出力、2.7V~36V 電源                                   | コスト重視アプリケーション向け、シングル、36V、1.2MHz、低消費電力オペアンプ                             | オペアンプ              |

## 主要なファイルへのリンク

テキサス・インスツルメンツ、ハイサイド V-I コンバータ、0V~2V 入力、0mA~100mA 出力、1% フルスケール誤差のリファレンス デザイン、TIPD102 の概要

テキサス・インスツルメンツ、アダプティブ電源使用、1W 未満、4 チャネル アナログ出力モジュールのリファレンス デザイン、TIPD215 の概要

テキサス・インスツルメンツ、8 チャネル、16 ビット、200mA 電流出力 DAC、リファレンス デザイン テキサス・インスツルメンツ、SLAA867 用のソース ファイル、ソフトウェア サポート

## 商標

すべての商標は、それぞれの所有者に帰属します。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあら ゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated