Application Report JAJA461

# TPS55340を使用したSEPICコンバータ

Anthony Fagnani DCS Industrial DC/DC

#### 要約

アプリケーションによっては、最小入力電圧~最大入力電圧の間に出力電圧のレギュレーションを保つために、DC/DCコンバータを必要とする場合があります。降圧または昇圧だけでは、レギュレーション出力を供給できません。ただし、昇圧コンバータICを使用して、SEPIC(シングルエンド・プライマリ・インダクタ・コンバータ)方式のパワー段を駆動すれば、最小/最

大入力電圧間で出力電圧のレギュレーションを確保できます。 このアプリケーション・レポートでは、TPS55340のデータシート に基づいてこの設計手順を詳しく説明するとともに、部品選択 やレイアウト上の考慮事項についても取り上げます。最後に、 SEPIC設計の改良点や利点についても考察しています。

# 目 次

| 1  | 理想的なSEPICパワー段の概要              | 2  |

|----|-------------------------------|----|

| 2  | 計算および部品選択                     | 4  |

|    | 2.1 スイッチング周波数 (R4)            | 4  |

|    | 2.2 デューティ・サイクルの計算             |    |

|    | 2.3 最大出力電流                    |    |

|    | 2.4 インダクタ(L1)                 |    |

|    | 2.5 出力コンデンサ(C8-C10)           |    |

|    | 2.6 ACコンデンサ(C6)               |    |

|    | 2.7 入力コンデンサ(C2)               | 7  |

|    | 2.8 整流ダイオード(D1)               | 7  |

|    | 2.9 MOSFETの定格                 | 7  |

|    | 2.10 帰還抵抗 (R1、R2)             | 8  |

|    | 2.11 ソフト·スタート·コンデンサ(C3)       | 8  |

|    | 2.12 制御ループの補償 (R3、C4、C5)      | 8  |

| 3  | レイアウトに関する考慮事項                 | g  |

| 4  | テスト結果、レイアウト、部品表               | g  |

| 5  | 改良点および利点                      | g  |

|    | 5.1 インダクタ電流リップル               | g  |

|    | 5.2 SEPICとフライバックの比較           | 10 |

| 6  | 結論                            |    |

| 7  | 参考資料                          | 11 |

|    |                               |    |

|    | 図目次                           |    |

| 1  | SEPICパワー段                     | 2  |

| 2  | スイッチのオン時間およびオフ時間中のSEPICの等価回路  |    |

| 3  | SEPICの電圧波形と電流波形               | 3  |

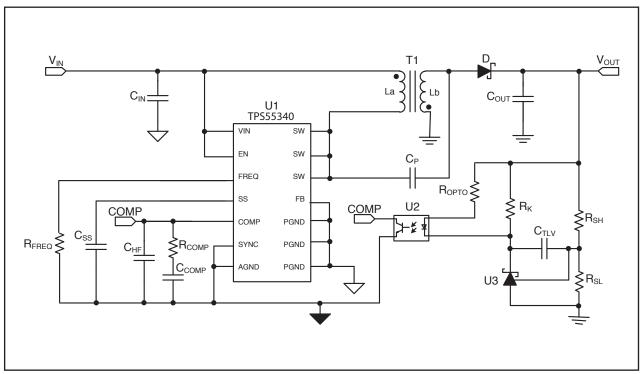

| 4  | TPS55340EVM-147の回路図           |    |

| 5  | 測定したパワー段のゲインおよび位相             |    |

| 6  | 測定したループ全体のゲインおよび位相            |    |

| 7  | CP = 2.2μFでの電流リップル            |    |

| 8  | CP = 20μFでの電流リップル             |    |

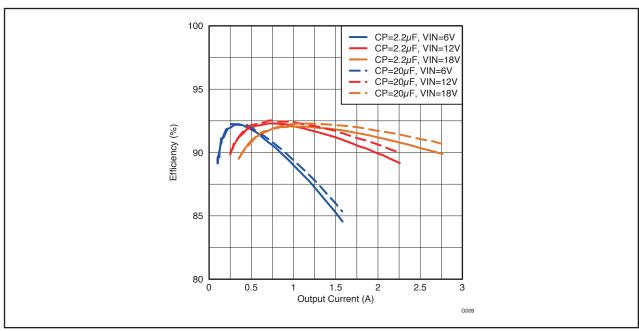

| 9  | CP = 2.2μFおよびCP = 20μFでのCCM効率 |    |

| 10 | 絶縁型SEPIC                      | 11 |

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。

を、首様のこ理解の一切として頂くために日本デキサス・インスグルメング (日本TI)が英文から和文へ翻訳して作成したものです。 資料によっては正規英語版資料の更新に対応していないものがあります。 日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

Tlおよび日本Tlは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

## 表目次

## 1 理想的なSEPICパワー段の概要

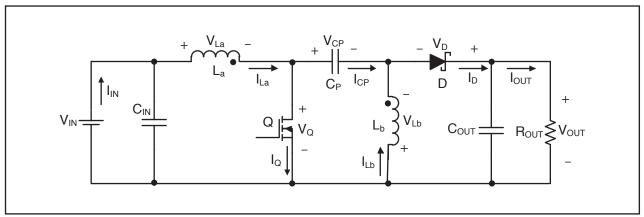

図 1. SEPICパワー段

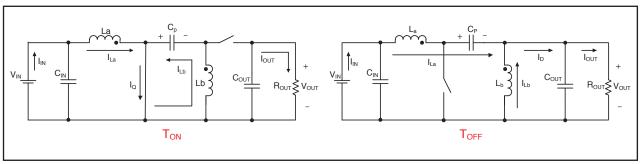

図 2. スイッチのオン時間およびオフ時間中のSEPICの等価回路

SEPICトポロジは、出力電圧より高い値から低い値まで入力電圧が変動するようなシステムで、レギュレーション出力の生成に適しています。これは、低コストの非レギュレーション電源からレギュレーション出力を生成するような場合に、非常に便利です。図1に、基本的なSEPICパワー段のトポロジを示します。

図2に、スイッチのオン時間およびオフ時間中のSEPICの詳細を示し、図3には電流波形と電圧波形を示します。オン時間中は、 $V_{\rm IN}$ からのエネルギーがLaに蓄積されます。 $C_{\rm P}$ の正極側は、内部スイッチによってグランド電位に保持されています。結合インダクタを使用した場合、1対1の巻線比によって、 $C_{\rm P}$ の負極側は $-V_{\rm IN}$ にプルダウンされます。両方のインダクタにかかる電圧は、 $V_{\rm IN}$ に等しくなります。出力ダイオードは逆バイアスとなり、出力負荷電流は出力コンデンサによって供給されます。

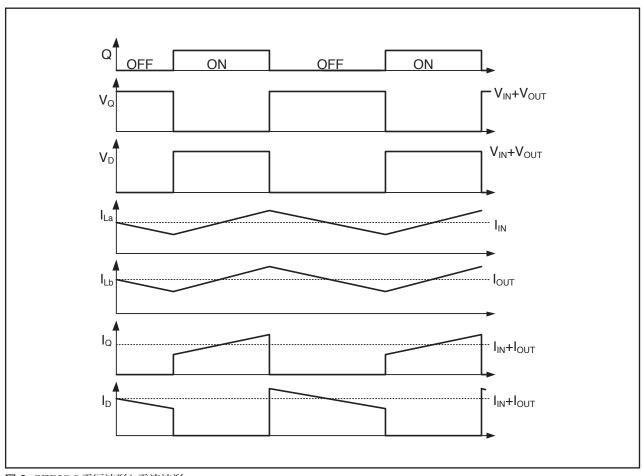

図 3. SEPICの電圧波形と電流波形

オフ時間中は、 $V_{\rm IN}$ からLaを通して $C_{\rm P}$ が再充電されます。 $C_{\rm OUT}$ は、Lbの電流、およびLaから $C_{\rm P}$ を経由した電流の両方によって再充電されます。出力ダイオードが導通しているため、Lbにかかる電圧は $V_{\rm OUT}$ にクランプされます。結合インダクタの1対1の巻線比により、スイッチにかかる電圧は $V_{\rm IN}$ と $V_{\rm OUT}$ の和に等しくなります。LaとLbの両方にかかる電圧は、 $-V_{\rm OUT}$ です。

図からわかるように、このトポロジには2個のインダクタが必要です。ただし、1個の結合インダクタを使用することで、コストとPCB領域を削減できます。それが可能なのは、スイッチのオン時間中とオフ時間中の両方で、各個別のインダクタにかかる電圧が等しいためです。結合インダクタを使用する主な利点の

1つは、2つの巻線間で電流リップルが共有されるため、目的の リップルを満足するために必要なインダクタンスが半分に減少す ることです。また、ほとんどのインダクタ・メーカーから、さまざ まな種類の結合インダクタが市販されており、一般に2つの個別 のインダクタを使用するよりも低コストで済みます。以下の設計 で使用する各式では、1個の結合インダクタが使用されると仮定 していますが、2個のインダクタを使用した設計も可能です。

さらに、TPS55340などの昇圧コンバータを使用することにも利点があります。昇圧コントローラと比較すると、スイッチングMOSFETがICの内部にあるため、部品数およびPCB領域を削減できます。また、外部スイッチングMOSFETを選択する必要がないため、設計の複雑さが軽減されます。

# 2 計算および部品選択

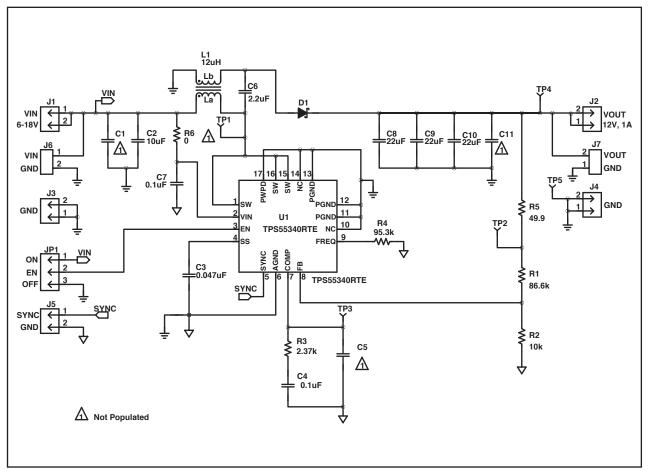

図 4. TPS55340EVM-147の回路図

| パラメータ                                     | 測定条件                                          | 最小  | 標準  | 最大 | 単位   |  |

|-------------------------------------------|-----------------------------------------------|-----|-----|----|------|--|

| 入力特性                                      | •                                             | •   |     |    |      |  |

| 入力電圧範囲、V <sub>IN</sub>                    |                                               | 6   | 12  | 18 | V    |  |

| スイッチング周波数、f <sub>SW</sub>                 |                                               |     | 500 |    | kHz  |  |

| 出力特性                                      |                                               |     |     |    |      |  |

| 出力電圧、V <sub>OUT</sub>                     |                                               |     | 12  |    | V    |  |

| 出力電流、Iout                                 |                                               | 0   |     | 1  | Α    |  |

| 出力電圧リップル、V <sub>RIPPLE</sub>              | V <sub>IN</sub> = 6 V, I <sub>OUT</sub> = 1 A |     | 60  |    | mVpp |  |

| 保守的な効率見積もり、η <sub>EST</sub>               | V <sub>IN</sub> = 6 V, I <sub>OUT</sub> = 1 A | 85% |     |    |      |  |

| 負荷ステップ、ΔI <sub>TRAN</sub>                 |                                               |     | 500 |    | mA   |  |

| V <sub>OUT</sub> の過渡偏差、ΔV <sub>TRAN</sub> |                                               |     | 480 |    | mV   |  |

表 1. リファレンス・デザインの特性仕様

以下の計算は、製品フォルダにあるExcelスプレッドシートを利用し、図4の回路図に基づいて実行されています。

## 2.1 スイッチング周波数 (R4)

スイッチング・レギュレータの通例として、スイッチング周波数の選択は、設計時に考慮する主要なトレードオフの1つとなります。一般に、スイッチング周波数を低くすると、効率が向上しますが、外部部品のサイズが比較的大きくなります。一方、スイッチング周波数が高いと、部品サイズを小さくすることが出

来ますが、効率は比較的低くなります。この設計では、TPS55340の動作範囲の中央となる500kHzを使用しています。この周波数を設定するための抵抗は、製品データシートから式 (1) で計算され、最も近い標準値を使用します。スイッチング周波数が500kHzの場合、抵抗の計算値は94.5k $\Omega$ となります。最も近い標準値として、95.3k $\Omega$ を使用します。

$$R_{FREQ}(k\Omega) = 57500 \times f_{SW}(kHz)^{-1.03}$$

(1)

#### 2.2 デューティ・サイクルの計算

以降の計算のために、最初に連続導通モード(CCM)で最小および最大デューティ・サイクルを見積もります。これは式(2)を用いて行います。デューティ・サイクルに対しては、最初にTPS55340の最大デューティ・サイクル89%(最小)に基づいた制限が課されます。デバイスがパルスのスキップ(DPS)を開始する最小デューティ・サイクルは、選択されたスイッチング周波数およびデバイスの最小制御可能オン時間(標準77ns)に基づいて、式(3)で計算されます。標準的なアプリケーションでは、不連続導通モード(DCM)での動作中、非常に軽い負荷でのみ、パルスのスキップが発生します。このモードでの動作は、昇圧コンバータの設計例に対してデータシートに示されている動作と同じです。

$$D = \frac{V_{OUT} + V_D}{V_{OUT} + V_D + V_{IN}}$$

(2)

$$D_{PS} = T_{ON} \min \times f_{SW}$$

(3)

$V_D$ は、整流ダイオードの順方向電圧降下であり、0.5Vと見積もられます。この設計例での標準パルス・スキップ・デューティ・サイクルは4%です。最小入力電圧 $V_{\rm IN}$ min = 6Vのときに、最大デューティ・サイクルDmax = 0.68となります。同様に、最大入力電圧 $V_{\rm IN}$ max = 18Vのときに、最小デューティ・サイクルDmin = 0.41となります。

2個のインダクタを流れる電流の和が、各スイッチング・サイクルの終わりで0になると、レギュレータはDCM動作に入ります。デバイスがDCMで動作するときの限界電流は、式(4)で計算できます。このモードでの動作中、デューティ・サイクルは、入力および出力電圧に加えて、負荷電流、インダクタンス、およびスイッチング周波数の関数になります。デューティ・サイクルは、式(5)で見積もることができます。

$$I_{OUT}crit = \frac{V_{IN}^2 \times (V_{OUT} + V_D)}{2 \times f_{SW} \times L \times (V_{OUT} + V_D + V_{IN})^2}$$

(4)

$$D_{DCM} = \frac{\sqrt{2 \times L \times (V_{OUT} + V_{D}) \times I_{OUT} \times f_{SW}}}{V_{IN}}$$

(5)

#### 2.3 最大出力電流

最大出力電流を決定するには、最初にいくつかの設計パラメータを決定する必要があります。安定した電源動作を確保し、EMIを最小限に抑えるために、インダクタのリップル電流 ( $\Delta I_L$ )がLaを流れるDC電流 ( $I_{IN}$ DC)と比較して小さい割合となるように、インダクタを選択します。LaのDC電流は、最大DC入力電流 ( $I_{IN}$ DC) に等しくなります。この割合は係数  $K_{IND}$ によって表され、これは通常 $0.2\sim0.4$ です。他のスイッチング・レギュレータと同様に、より大きな $K_{IND}$ を選択することで、推奨インダクタンスが低くなります。それによって電流リッ

プルが増加し、与えられた飽和電流に対して、より小さなインダクタ・パッケージを使用可能になります。一般に、電流リップルが大きいほど、EMIが増加し、最大出力電流が低下し、目的の出力リップルに対して必要な出力容量は大きくなりますが、過渡応答は高速になります。K<sub>IND</sub>が小さい場合は、その逆になります。推奨インダクタンスが高くなり、電流リップルは減少し、インダクタのパッケージ・サイズが大きくなります。一般に、電流リップルが小さいほど、EMIが減少し、最大出力電流が増加し、必要な出力容量が小さくなりますが、過渡応答は遅くなります。システム・レベルの設計目標に応じて、トレードオフを検討する必要があります。

最初に、全負荷効率の保守的な見積もりとして $\eta_{EST}$  = 85%、および $V_{IN}$ min = 6Vを使用して、式 (6) から最大入力電流を計算します。次に、式 (7) を使用して、目的のピーク・ツー・ピーク電流リップルを計算します。

$$I_{IN}DC = \frac{V_{OUT} \times I_{OUT}}{\eta_{EST} \times V_{IN}min}$$

(6)

$$\Delta I_{I} = I_{IN}DC \times K_{IND} \tag{7}$$

$I_{IN}$ DCは2.35Aと見積もられ、 $K_{IND}=0.3$ によって、目的のリップル電流は706mAとなります。これに基づき、最大出力電流  $(I_{OUT}$ max)を式 (8)で計算できます。この式では、結合インダクタを使用し、TPS55340の最小ピーク電流制限  $(I_{IM})$  が5.25Aであると仮定しています。

$$I_{OUT} max = \frac{\left(I_{LIM} - \Delta I_{L}\right)}{\left(\frac{V_{OUT}}{V_{IN} min \times \eta_{EST}} + 1\right)}$$

(8)

目的の電流リップルによって、最大出力電流の見積もりは 1.20Aとなります。これらの式からわかるとおり、最大出力電流は、設計の効率および選択したインダクタに依存しています。インダクタを選択した後、全負荷効率についてさらに評価を行うことで、より大きな最大出力電流を設計で使用できる可能性もあります。

## 2.4 インダクタ(L1)

目的の $\Delta I_L$ に基づき、最少インダクタンス(L) を式 (9) で計算します。ここでは、SEPICでの電流リップルが最大となる条件として、最大入力電圧およびそれに対応するデューティ・サイクルを使用します。この式でも、結合インダクタの使用によって、必要なインダクタンスが半分に減ると仮定しています。

$$L \ge \frac{V_{IN} \times D}{2 \times f_{SW} \times \Delta I_{I}}$$

(9)

この設計では、推奨されるLの最小値が10.5μHと計算され、最も近い標準値として12μHを選択しています。12μHの

インダクタを使用し、式 (9) を変形することで、 $\Delta I_L$ は $V_{IN}$ max で615mA、 $V_{IN}$ minで338mAと計算されます。この時点で、選択したインダクタンスを使用して最大出力電流を再評価することもできます。式 (8) により、最大出力電流は約1.47Aに増加します。インダクタの定格が適切であることを確認するために、ピーク電流とRMS電流を計算する必要があります。結合インダクタでは、合計ピーク電流が各巻線のピーク電流の和となります。式 (10) でピーク電流を計算します。

$I_{L}peak = I_{La}peak + I_{Lb}peak$

$$= \left(I_{\text{IN}} \text{max} + \frac{\Delta I_{\text{L}}}{2}\right) + \left(I_{\text{OUT}} + \frac{\Delta I_{\text{L}}}{2}\right)$$

(10)

この設計の場合、ピーク電流は3.69Aと見積もられます。インダクタの飽和電流は、ピーク電流より20%大きいか、またはICのピーク電流制限よりも大きいことが推奨されます。それによって、ピーク・インダクタ電流が定常状態値を超える可能性のある過渡状況に対して、余裕を確保できます。ICのピーク電流制限を使用するのが最も保守的な条件であり、過電流障害状態でもインダクタが飽和しないことを保証できます。この設計では、最小飽和電流定格として、6.6Aの標準電流制限を使用しています。

式 (11) および式 (12) で、各巻線のRMS電流を計算します。式 (13) および式 (14) では、これらの電流から、結合インダクタのデータシートに通常記載されている定格  $(I_{RMS}$ oneおよび  $I_{RMS}$ both) を求めています。 $I_{RMS}$ oneは1つの巻線だけの導通を表し、 $I_{RMS}$ bothは両方の巻線が等しく導通した状態を表します。これらの定格は通常、40°Cの温度上昇に対して指定されます。

$$I_{l,a}RMS \approx I_{lN}DC$$

(11)

$$I_{Lb}RMS \approx I_{OUT}$$

(12)

$$I_{RMS}one = \sqrt{(I_{La}RMS)^2 + (I_{Lb}RMS)^2}$$

(13)

$$I_{RMS}both = \sqrt{\frac{\left(I_{RMS}one\right)^2}{2}}$$

(14)

インダクタに対して計算される等価なRMS値は、 $I_{RMS}$ one = 2.56Aおよび $I_{RMS}$ both = 1.81Aです。飽和電流定格および RMS電流の計算に基づき、仕様範囲内またはそれに近い結合 インダクタのファミリーが4つあります。それらを表2に示します。この設計では、MSD1260-123を使用します。DCRがより

低いインダクタを選択することで、設計の効率を向上できます。 選択したインダクタで両方の巻線のDCRが等しい場合、導通 損失は式(15)で計算できます。この設計の場合、全負荷時の インダクタでの導通損失は、最小入力電圧で484mWと見積も られます。

$$P_{L} = \left( \left( I_{La} RMS \right)^{2} + \left( I_{Lb} RMS \right)^{2} \right) \times DCR$$

(15)

## 2.5 出力コンデンサ(C8-C10)

出力コンデンサは、最大出力電圧リップルおよび負荷過渡時の最小出力電圧偏差に基づいて選択します。標準的な出力電圧リップル(V<sub>RIPPLE</sub>)仕様は公称出力電圧の0.5%ですが、この値は一般に、システム・レベルで決定されます。60mVppの出力リップル仕様に基づき、式(16)を使用して最小出力容量を計算します。

$$C_{OUT} \ge \frac{Dmax \times I_{OUT}}{f_{SW} \times V_{RIPPLE}}$$

(16)

この仕様を満足するための最小出力容量は22.5µFです。ここでは、ESRを無視できるセラミック出力コンデンサの使用を仮定しています。セラミック以外のコンデンサを使用した場合は、追加の電圧リップルが生じます。合計リップルを式(17)で計算し、電圧リップル仕様を満足する最大ESRを式(18)で計算します。ESRでのリップルは出力容量によるリップルと同相ではないため、式(18)では最大ESRの見積もりが低めになることに注意してください。実際には、回路のテストまたはシミュレーションを通じて、より高いESRを選択できる場合があります。

$$V_{RIPPLE} = \frac{Dmax \times I_{OUT}}{f_{SW} \times C_{OUT}} + ESR_{COUT} \times (I_{La}peak + I_{Lb}peak)$$

(17)

$$ESR_{COUT} \le \frac{V_{RIPPLE} - \frac{Dmax \times I_{OUT}}{f_{SW} \times C_{OUT}}}{(I_{La}peak + I_{Lb}peak)}$$

(18)

表1の負荷過渡応答仕様を満足する最小容量は、式 (19)で計算されます。この設計の仕様は、50%の最大負荷過渡ステップ(500mA)で最大4%の出力電圧変化 (480mV)です。

| メーカー                | 部品番号         | L (µH) | I <sub>RMS</sub> both (A) | I <sub>RMS</sub> one (A) | I <sub>SAT</sub> (A) | DCR (mΩ) |

|---------------------|--------------|--------|---------------------------|--------------------------|----------------------|----------|

| CoilCraft           | MSD1260-123  | 12     | 2.21                      | 3.12                     | 6.86                 | 74       |

| Wurth<br>Elektronic | 744870100    | 10     | 2.7                       |                          | 7                    | 44       |

| Bourns              | SRF1260-10   | 10     | 2.67                      | 5.35                     | 7.17                 | 49.2     |

| Cooper              | DRQ125-100-R | 10     | 2.67                      | 5.35                     | 7.17                 | 37.8     |

表 2. 市販の結合インダクタの例

$$C_{OUT} \ge \frac{\Delta I_{TRAN}}{2\pi \times f_{BW} \times \Delta V_{TRAN}}$$

(19)

ループ帯域幅またはクロスオーバー周波数  $(f_{BW})$  の見積もりが6kHzの場合、最小容量は $27.6\mu$ Fとなります。式 (16)と式 (19) の間で計算された最大の値を使用して、最小出力容量を決定する必要があります。この設計では、過渡仕様から $27.6\mu$ Fとなります。

セラミック以外のコンデンサを使用した場合、または出力コンデンサのRMS電流定格が規定されている場合は、式 (20)でRMS電流を計算します。この設計では、1.44Aと計算されます。

$$I_{COUT}RMS = I_{OUT} \sqrt{\frac{Dmax}{(1-Dmax)}}$$

(20)

選択した出力コンデンサは、 $22\mu F/25 V O X7R$  1210セラミック・コンデンサが3個です。セラミック・コンデンサを使用する場合は、DCバイアスによるディレーティングを考慮することが重要です。出力電圧が12Vの場合、見積もり容量は公称値の46%であり、 $30.4\mu F$ のディレーティング容量となります。

#### 2.6 ACコンデンサ(C6)

ACコンデンサ $(C_P)$ は、リップル電圧 $\Delta V_{CP}$ が最大 $V_{CP}DC$  (=  $V_{IN}$ max) の5%以下となるよう選択することを推奨します。式 (21) で最小容量を計算します。

$$C_{P} \ge \frac{I_{OUT} \times Dmax}{0.05 \times V_{IN} max \times f_{SW}}$$

(21)

最小容量は $1.5\mu$ Fと計算され、ディレーティングによって、次に大きな標準値 $2.2\mu$ Fを使用します。このコンデンサは最大入力電圧に対して適切な定格を持つ必要があり、DCバイアスによる容量のディレーティングも考慮する必要があります。また、RMS電流 ( $I_{CP}$ RMS) に対しても適切な定格を持つ必要があります。これは、式 (22) から1.63Aと計算されます。選択したコンデンサは、 $2.2\mu$ F/50VのX7R 1206セラミック・コンデンサです。

$$I_{CP}RMS = I_{IN}DC \times \sqrt{\frac{(1-Dmax)}{Dmax}}$$

(22)

## 2.7 入力コンデンサ(C2)

TPS55340の最小推奨値4.7 $\mu$ Fに基づいて、 $10\mu$ FのX5RまたはX7Rセラミック入力コンデンサを選択します。また、この設計では、追加のデカップリング用に $0.1\mu$ Fのコンデンサ(C7)を $V_{IN}$ ピンの近くに配置します(このコンデンサの使用はオプションです)。式 (23)で入力電圧リップル( $V_{INRIPPLE}$ )を計算し、式 (24)でRMS電流を計算します(定格が与えられている場合)。ディレーティング後の見積もり容量 $6\mu$ Fを使用して、これらはそれぞれ39.9mVおよび0.098Aとなります。

$$V_{\text{INRIPPLE}} = \frac{\Delta I_{\text{L}}}{4 \times f_{\text{SW}} \times C_{\text{IN}}} + I_{\text{IN}}DC \times ESR_{\text{CIN}} \quad (23)$$

$$I_{CIN}RMS = \frac{\Delta I_L}{\sqrt{12}}$$

(24)

#### 2.8 整流ダイオード(D1)

昇圧コンバータの場合と同様に、ダイオードを流れる平均電流は出力電流に等しくなります。整流ダイオードは、出力電流およびスイッチング・ノードでの電圧を処理できるよう選択する必要があります。ダイオードの平均電流定格に対して、20%以上の余裕を確保することを推奨します。保守的な設計では、 $V_{\rm IN}$ max時の最大出力電流を使用し、標準電流制限によって電流定格を選択します。式 (8) に $V_{\rm IN}$ maxを使用することで、出力過電流制限が2.60Aと求められます。式 (25) で、 $V_{\rm D}$  = 0.5Vと仮定し、ダイオードの最小降伏電圧 ( $V_{\rm BR}$ ) は30.5Vと計算されます。

$$V_{BB} = V_{OUT} + V_{IN} max + V_{D}$$

(25)

ダイオードのパッケージは、消費電力に対して適切な定格を持つ必要があります。消費電力は、式 (26)により、1A出力で0.5Wと計算されます。

$$P_{D} = I_{OUT} \times V_{D} \tag{26}$$

これらの条件に基づいて、Diodes Inc.のB340Bを選択しています。これは、SMBパッケージに実装された40V、3Aのダイオードです。

#### 2.9 MOSFETの定格

ICの内部MOSFETは、定格電圧および定格電流を処理できる必要があります。図3に示されるように、SWでの電圧は $V_{OUT}$ と $V_{IN}$ の和です。同様に、ピーク電流は、入力電流、出力電流、およびピーク・ツー・ピーク・リップル電流の和に等しくなります。式 (27) で電圧を計算し、式 (28) で電流、式 (29) でRMS電流を計算します。

$$V_{Q} = V_{OUT} + V_{IN} max (27)$$

$$I_{O}peak = I_{OUT} + I_{IN}DC + \Delta I_{L}$$

(28)

$$I_{Q}RMS = \frac{I_{IN}DC}{\sqrt{Dmax}}$$

(29)

この設計では、MOSFETの電圧ストレスが30V、ピーク電流が3.69Aとなります。初期テスト時には、SWノードでのリンギングを考慮して、電圧定格に5~10%の余裕を設けることを推奨します。効果的なレイアウト手法を用いることで、SWノードでのリンギングを制限できます。このリンギングは、外部スナバを使用してさらに低減できます。外部スナバの選択方法は、SLVA255で説明されています。

#### 2.10 帰還抵抗(R1、R2)

帰還抵抗の選択は、TPS55340を昇圧トポロジで動作させる場合と同様に行います。帰還分圧回路を流れる電流およびノイズを最小限に抑えるため、下側抵抗 (R2) は推奨値の $10k\Omega$ に固定します。次に、TPS55340の電圧リファレンス ( $V_{REF}$ )である1.229Vを使用して、上側抵抗 (R1)を式 (30)で計算します。R1は87.6 $k\Omega$ と計算され、最も近い標準値の $86.6k\Omega$ を選択します。

$$R1 = R2 \times \left(\frac{V_{OUT}}{V_{REF}} - 1\right)$$

(30)

#### 2.11 ソフト・スタート・コンデンサ(C3)

データシートの推奨値である0.047μFのソフト・スタート・コンデンサを使用します。スタートアップ中に出力の電圧オーバーシュートを低減するため、または突入電流を低減するために、より長いソフト・スタート時間が必要な場合は、この容量をさらに大きくできます。

#### 2.12 制御ループの補償 (R3、C4、C5)

SEPICコンバータの数学的モデルの導出は、極めて複雑です。補償を設計する際に最も早くて簡単な方法は、SPICEモデルまたは測定データを使用することです。この設計では、Venableのゲイン/位相アナライザを使用してパワー段を測定することにより、補償部品を選択します。安定した設計によって、有効な測定が実現されます。最初は、大きな補償コンデンサ $(1\mu F)$ と小さな補償抵抗  $(1k\Omega)$ を使用して、制御ループを低い周波数でロールオフさせます。

目標のクロスオーバー周波数を選択する際には、2つの条件を満足する必要があります。最低周波数の右半平面ゼロ(RHPZ)の1/3未満でクロスオーバーすることが推奨され、また、目的のクロスオーバー周波数で十分な位相が確保されている必要があります。RHPZは式(31)で計算されます。RHPZは、最小入力電圧および最大出力電流時の最低周波数に位置します。したがって、補償設計はこの動作点で行われます。RHPZは36.7kHzであり、クロスオーバー周波数は12.2kHz未満となる必要があります。

$$f_{RHPZ} = \frac{\frac{V_{OUT}}{I_{OUT}}}{2\pi \times L \times \left(\frac{D}{(1-D)}\right)^2}$$

(31)

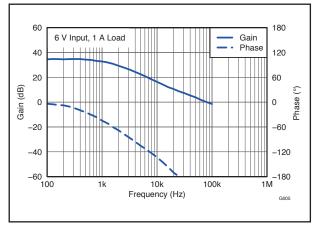

2番目の条件である十分な位相は、目標の位相マージンによって決定されます。推奨される位相マージンの60°に基づき、補償で最大180°の位相を確保すると仮定すると、出力位相への制御には-120°以上が必要となります。図5からわかるように、パワー段の位相は7kHzで約-120°であり、これが目標帯域幅として使用されます。

図 5. 測定したパワー段のゲインおよび位相

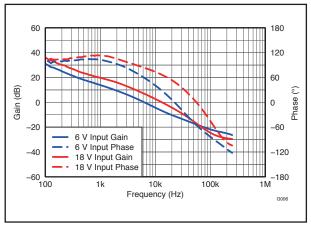

図 6. 測定したループ全体のゲインおよび位相

補償部品は、補償ゲインが目標帯域幅でのパワー段ゲインの逆数となるように選択する必要があります。目標の補償ゲイン $(K_{COMP})$ は、-19.50dBです。R3の値は式(32)で2.37k $\Omega$ と計算され、これは標準値です。Geaの最大値を使用することで、ICでの変動に対する安定性が確保され、標準的な回路では帯域幅が目標の7kHzよりも低くなります。

$$R3 = \frac{10^{\left(\frac{K_{COMP}(f_{BW})}{20dB}\right)}}{Gea \times \frac{R1}{(R1+R2)}}$$

(32)

クロスオーバー周波数で最大の位相を確保するために、補償用のゼロは通常 $f_{BW}$ の $1/5\sim1/10$ に設定されます。この設計では、ゼロが $1/10\times f_{BW}$ に配置されます。C4は式 (33)によって0.096μFと計算され、最も近い標準値の0.1μFを使用します。

$$C4 = \frac{1}{2\pi \times R3 \times \frac{f_{BW}}{10}}$$

(33)

C5は、セラミック出力コンデンサの場合は通常不要ですが、高周波極を追加して高周波ノイズを減衰させるために使用されます。この極は、10×f<sub>BW</sub>以上に配置することを推奨します。式 (34)を使用し、目標の極周波数に基づいて容量を計算します。セラミック以外の出力コンデンサを使用し、ESRが高い場合、この極は出力コンデンサからESRゼロの位置に配置する必要があります。式 (35) は、ESRゼロ周波数に極を追加するために必要なC5の値を計算します。C5を使用しない場合は、浮遊基板容量から10pFとしてモデル化できます。

$$C5 = \frac{1}{2\pi \times R3 \times f_P}$$

(34)

$$C5 = \frac{C_{OUT} \times ESR_{COUT}}{R3}$$

(35)

$f_{BW}$ を高くし、RHPZに基づく最大推奨周波数に近づけるために、より大きな位相マージンが必要である場合は、上側帰還抵抗R1と並列にフィードフォワード・コンデンサ( $C_{FF}$ )を接続することで、追加のゼロを配置します。このゼロは、目標帯域幅周波数よりも高い周波数に配置することを推奨します。 $C_{FF}$ の最大推奨値は、式36で求められます。また、 $C_{FF}$ を使用することで、追加したゼロよりも高い周波数にさらに極が追加されます。

$$C_{FF} \le \frac{1}{2\pi \times R1 \times f_{BW} \times \sqrt{\frac{V_{REF}}{V_{OUT}}}}$$

(36)

選択した補償部品による全体のループ応答を図6に示しています。6V入力による全負荷時に、測定された帯域幅は6.3kHzで、位相マージンが59.3°です。

## 3 レイアウトに関する考慮事項

すべてのスイッチング電源において、レイアウトは設計での 重要なステップとなります。周波数が高く、高電流の場合に は、特に重要です。レイアウトが注意深く行われていないと、 レギュレータではノイズ問題だけでなく安定性の問題も生じる 場合があります。効率を最大にするために、スイッチングの立 ち上がりおよび立ち下がり時間はできる限り短くします。高周 波共振による放射の問題を防ぐためには、高周波スイッチン グ・パスの適切なレイアウトが不可欠です。これは、次のように 行います。

- SWピンに接続されるすべてのパターンの長さと面積を最小にし、常にスイッチング・レギュレータの下のグランド・プレーンを使用して、プレーン間のカップリングを最小限に抑えます。

- SEPIC設計では、 $C_P$ 、D1、L1間の接続上に追加のスイッチング・ノードがあり、この領域も最小にする必要があります。

- スイッチ、C6、ショットキー・ダイオード、および出力コンデンサを含めた高電流パスには、ns単位の立ち上がり/立ち下がり時間が含まれるため、このパスはできる限り短くする必要があります。

- 入力コンデンサは、 $V_{\rm IN}$ ピンの近くに配置するだけでなく、 AGNDピンにも近づけることで、ICの電源リップルを低減します。

- 内部アナログ制御回路に接続される外部部品には別個のグランド(AGND)を使用し、このグランドはスイッチング・グランド(PGND)に1点だけで接続することを推奨します。これには、FREQ、SS、COMP、SYNC、およびFBに接続される部品が含まれます。

TPS55340は、熱特性強化型QFNパッケージで供給されます。このパッケージには、熱特性を向上させるサーマル・パッドが搭載されています。TPS55340直下にサーマル・ビアを使用することで、露出したサーマル・パッドからグランドへのパスを提供してください。

# 4 テスト結果、レイアウト、部品表

この設計の完全なテスト結果、レイアウト、および部品表については、TPS55340EVM-147ユーザーズ・ガイド(SLVU742)を参照してください。

## 5 改良点および利点

#### 5.1 インダクタ電流リップル

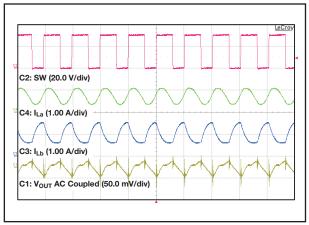

SEPICレギュレータを設計、構築し、テストした後は、結合巻線での電流リップル波形が正弦波に近く、図7に示されるように理想的なのこぎり波になっていないことに気付くかもしれません。これは、実際の設計における2つの特性の組み合わせが原因です。具体的には、結合インダクタのリーケージ・インダクタンス(L<sub>LK</sub>)によって生じる、C<sub>P</sub>での電圧リップルです。インダクタでの電圧の変動によって、余分な電流リップルが生じます。多くの場合、追加の電流リップルは非常に大きいため、観測されるリップル波形に影響が出ます。また、追加の循環電流によって、電力損失が増えることで、効率が低下します。この循環電流の影響は、最大出力電流で動作していて巻線内の電流が最大のときに、最も顕著となります。

**図 7.** C<sub>P</sub> = 2.2μFでの電流リップル

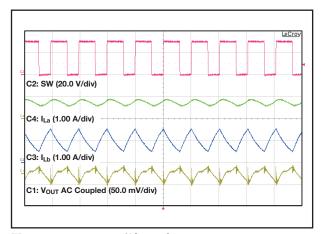

図 8. C<sub>P</sub> = 20μFでの電流リップル

この余分なリップル電流を減らすには、2つの方法があります。 $C_P$ の容量を増やすか、または、1次リーケージ・4ンダクタンスを大きくするかです。容量を増やすことには、サイズとコストが増加するというトレードオフがあります。リーケージ・4ンダクタンスを大きくするには、カスタムの磁気部品が必要となる場合があります。リップルの抑制方法は、設計者の裁量で決定します。式 (37) および式 (38) は、リップルを制限するためのリーク・4ンダクタンスおよび $C_P$ 容量の推奨値をそれぞれ計算します。どちらの式でも、リーケージ・4ンダクタンスによって生じる電流リップルが、磁化電流リップル $\Delta I_L$ とほぼ等しくなります。これらの計算では、 $C_P$ に対して見積もられたディレーティング容量を使用することが重要です。

$$L_{LK} \ge \frac{I_{OUT} \times L \times D}{C_{P} \times V_{IN} \times f_{SW}}$$

(37)

$$C_{P} \ge \frac{I_{OUT} \times L \times D}{L_{LK} \times V_{IN} \times f_{SW}}$$

(38)

ここでは例として、 $C_P$ を増やすことでリーク電流リップルを低減します。MSD1260-123MLに対して与えられている標準1次リーケージ・インダクタンスは、 $0.28\mu$ Hです。式37で最小入力電圧を使用すると、必要な実効容量は $9.7\mu$ Fとなります。 $10\mu$ F/25Vの1210 X5Rセラミック・コンデンサを2個使用し、最大入力電圧でのディレーティング容量が約 $10.8\mu$ Fとなります。図8は、新しい電流リップルを示し、リップル電流波形が改善されたことがわかりますが、理想に近づけるにはさらに改善の余地があります。図9では、新しいコンデンサを使用して、計算された最大出力電流までの効率を比較しています。これにより、最大負荷で効率が最大1%上昇していることがわかります。

#### 5.2 SEPICとフライバックの比較

SEPICとフライバック・トポロジの類似点を示すために、スイッチング・コンデンサCpを除去することで、設計を簡単にフライバック・コンバータに変換します。必要であれば、これを用いて、2つのトポロジ間の違いをすばやく分析することができます。SEPIC設計には、2つの利点があります。まず、入力電流が連続しているため、入力コンデンサへのRMS電流ストレスが減少します。次に、Cpを追加することで、1次リーケージ・インダクタンスによってSWに生じる電圧オーバーシュートおよびリップルがクランプされ、内部MOSFETでのストレスが減少します。その結果、外部でのRCDクランプやRCスナバの必要性が減ります。2つのトポロジ間のトレードオフを公正かつ詳細に評価した結果が、参考資料4で紹介されています。SEPICソリューションは、図10の回路で示されるような絶縁型アプリケーションで使用されます。

図 9.  $C_P = 2.2 \mu F$ および $CP = 20 \mu F$ でのCCM効率

図 10. 絶縁型SEPIC

## 6 結論

SEPIC設計は、最小入力電圧と最大入力電圧の間で出力電圧のレギュレーションを保持するための、単純な非絶縁型オプションの1つです。このSEPIC設計の完全なテスト・データについては、TPS55340EVM-147ユーザーズ・ガイド(SLVU742)を参照してください。アプリケーションによっては、絶縁型フライバックの代わりに、SEPIC設計に絶縁を追加することで、部品(具体的には、入力コンデンサと内部MOSFET)へのストレスが減少します。

# 7 参考資料

- 1. TPS55340 Data Sheet, Integrated 5-A 40-V Boost/ SEPIC/Flyback Regulator (SLVSBD4)

- 2. Jeff Falin, Designing DC/DC converters based on SEPIC Topology (SLYT309)

- John Betten, SEPIC Converter Benefits from Leakage Inductance http://www.powerpulse.net/techPaper.php?paperID=153

- 4. John Betten and Robert Kollman, Guess what: underutilized SEPIC outperforms the flyback topology http://www.eetimes.com/design/

# ご注意

Texas Instruments Incorporated 及びその関連会社(以下総称してTIといいます)は、最新のJESD46に従いその半導体製品及びサービスを修正し、改善、改良、その他の変更をし、又は最新のJESD48に従い製品の製造中止またはサービスの提供を中止する権利を留保します。お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての半導体製品は、ご注文の受諾の際に提示されるTIの標準販売契約約款に従って販売されます。

TIは、その製品が、半導体製品に関するTIの標準販売契約約款に記載された保証条件に従い、販売時の仕様に対応した性能を有していることを保証します。検査及びその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、適用される法令によってそれ等の実行が義務づけられている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援又はお客様の製品の設計について責任を負うことはありません。TI 製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI 製部品を使用したお客様の製品及びアプリケーションに関連する危険を最小のものとするため、適切な設計上及び操作上の安全対策は、お客様にてお取り下さい。

TIは、TIの製品又はサービスが使用されている組み合せ、機械装置、又は方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品又はサービスを使用することについてライセンスを与えるとか、保証又は是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない、又はTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブック又はデータ・シートの中にある情報の重要な部分の複製は、その情報に一切の変更を加えること無く、且つその情報と関連する全ての保証、条件、制限及び通知と共になされる限りにおいてのみ許されるものとします。TIは、変更が加えられて文書化されたものについては一切責任を負いません。第三者の情報については、追加的な制約に服する可能性があります。

TIの製品又はサービスについて TI が提示したパラメーターと異なる、又は、それを超えてなされた説明で当該 TI 製品又はサービスを再販売することは、関連する TI 製品又はサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、且つ不公正で誤認を生じさせる行為です。TI は、そのような説明については何の義務も責任も負いません。

TI からのアプリケーションに関する情報提供又は支援の一切に拘わらず、お客様は、ご自身の製品及びご自身のアプリケーションにおける TI 製品の使用に関する法的責任、規制、及び安全に関する要求事項の全てにつき、これをご自身で遵守する責任があることを認め、且つそのことに同意します。お客様は、想定される不具合がもたらす危険な結果に対する安全対策を立案し実行し、不具合及びその帰結を監視し、害を及ぼす可能性のある不具合の可能性を低減し、及び、適切な治癒措置を講じるために必要な専門的知識の一切を自ら有することを表明し、保証します。お客様は、TI 製品を安全でないことが致命的となるアプリケーションに使用したことから生じる損害の一切につき、TI 及びその代表者にその全額の補償をするものとします。

TI 製品につき、安全に関連するアプリケーションを促進するために特に宣伝される場合があります。そのような製品については、TIが目的とするところは、適用される機能上の安全標準及び要求事項を満たしたお客様の最終製品につき、お客様が設計及び製造ができるようお手伝いをすることにあります。それにも拘わらず、当該TI 製品については、前のパラグラフ記載の条件の適用を受けるものとします。

FDA クラスIII(又は同様に安全でないことが致命的となるような医療機器)へのTI 製品の使用は、TIとお客様双方の権限ある役員の間で、そのような使用を行う際について規定した特殊な契約書を締結した場合を除き、一切認められていません。

TIが軍需対応グレード品又は「強化プラスティック」製品として特に指定した製品のみが軍事用又は宇宙航空用アプリケーション、若しくは、軍事的環境又は航空宇宙環境にて使用されるように設計され、かつ使用されることを意図しています。お客様は、TIがそのように指定していない製品を軍事用又は航空宇宙用に使う場合は全てご自身の危険負担において行うこと、及び、そのような使用に関して必要とされるすべての法的要求事項及び規制上の要求事項につきご自身のみの責任により満足させることを認め、且つ同意します。

TIには、主に自動車用に使われることを目的として、ISO/TS 16949の要求事項を満たしていると特別に指定した製品があります。当該指定を受けていない製品については、自動車用に使われるようには設計されてもいませんし、使用されることを意図しておりません。従いまして、前記指定品以外のTI製品が当該要求事項を満たしていなかったことについては、TIはいかなる責任も負いません。

Copyright © 2014, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導電性マットにアースをとったもの等)、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、 静電気の帯電を防止する措置を施すこと。

- • 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

#### 2. 温·湿度環境

■ 温度: 0~40℃、相対湿度: 40~85%で保管・輸送及び取り扱いを 行うこと。(但し、結露しないこと。) ● 直射日光があたる状態で保管・輸送しないこと。

#### 3. 防湿梱包

● 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

#### 4.機械的衝撃

● 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を与えないこと。

#### 5. 熱衝撃

● はんだ付け時は、最低限 260℃以上の高温状態に、10秒以上さらさないこと。(個別推奨条件がある時はそれに従うこと。)

## 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が 一定以下に保証された無洗浄タイプのフラックスは除く。)

以上