# ADC14V155,LMK02000,LMK03000

Application Note 1721 High Speed ADCs with Interfacing, Driving and Clocking Schemes

Literature Number: JAJA360

## インタフェース、ドライブおよび クロック機能を備えた高性能 ADC

National Semiconductor Application Note 1721 Uwe Kopp 2007 年 9 月

集積型高速パイプライン A/D コンバータ (ADC) の性能が新たなレベルへ到達しようとしており、分解能、サンプリング速度およびダイナミック特性の限界はさらに押し広げられています。なかでも ADC14V155 はクラス最高のコンバータで、フルパワー帯域幅は競合する 14 ビット ADC 製品を57% 上回ります。問題は、データシートに記載された各レベルでのスタティック特性と特にダイナミック特性をどのように維持するかです。設計時には ADC 周りの部品を極めて慎重に選ぶ必要があります。本稿では適切なクロック回路、良好なアナログ入力回路を設計することによって高速パイプライン ADC の性能を最適化する方法と、ADC からFPGA またはASICへデータを歪みなく高速転送する方法について解説します。

アプリケーションの一例として、分解能 14 ビット、サンプリング速度最大 155MSPS の性能を持つ ADC14V155 を取り上げます。ADC14V155 は、差動パイプライン・アーキテクチャを採用し、独自の低ジッタのサンプル/ホールド (S/H)段によって、1.1GHz というフルパワー帯域幅を実現しています。この高い入力帯域幅から、あらゆるタイプの通信用レシーバに非常に適しており、特にアンダー・サンプリングに向いています。最大 450MHz 帯域までの信号のサンプリングが可能で、システムの周波数プラニング時のフレキシビリティを提供するとともに、シングル・キャリア・アーキテクチャから、1 つの ADC で複数のキャリアの信号をデジタル化できるマルチ・キャリア方式への移行を可能にします。

この ADC のもうひとつの用途分野が高速試験 / 計測機器です。FPGA へのクリーンなデータ転送を可能にするため、データは、チップからデュアル・データ・レート (DDR) フォーマットでパラレル LVDS (小振幅差動信号)出力されます。電源構成は出力インタフェース (1.8V) とアナログ系統 (3.3V) を分け、ノイズおよび消費電力のさらなる低減をはかっており、消費電力の代表値は 1W 未満です。入力周波数 70MHz 時の信号対ノイズ比 (SNR) は 71.7dBFS (代表値)、スプリアス・フリー・ダイナミック・レンジ (SFDR) は 86.9dBFS (同)です。

## クロック・ジッタ - SNR 性能の敵

高周波入力 / 高分解能の時は、クロック / データ・ジッタ は、ADC の SNR 性能を制約する最大要因のひとつになります。SNR を悪化させずに、最大ジッタを量子化ノイズ (1/2 LSB) より低く抑える必要があり、これは次式で求められます。

$$T_{j(rms)} = (V_{IN(p-p)} / V_{INFSR}) * (1/(2^{(N+1)} * \pi * f_{in}))$$

入力電圧振幅  $V_{in(p-p)}$ をフルスケール振幅のために最適化した場合、最初の項は 1 になり、ジッタは分解能 (N) と入力周波数  $(f_{in})$  のみに依存することになります。

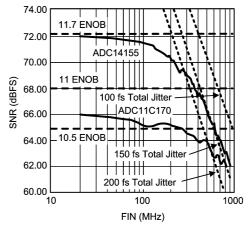

分解能が 11 ビットから 14 ビットの ADC の SNR 性能の測定結果をみると、100MHz を超える入力周波数に対して、トータル・システム・ジッタは、11 ビット ADC では 200fs を超えてはならず、ADC14V155 (ENOB:11.5) では約 100fs が上限です。

FIGURE 1. 11-14 bit ADC SNR Performance and Jitter Limits

これを参考にすると、クロック・ソースの仕様/設計目標の設定に役立ちます。大抵のクロック製品では、クロック周波数と位相ノイズが定義され、データシートのそれぞれのプロットに示されています。位相ノイズとジッタは同り現象ないし問題を言い換えたもので、位相ノイズは周波数領域で表され、ジッタはここから位相ノイズ・プロットを積分して求められます。これは ADC クロックにおけるジッタの原因について良い教示を与えるもので、その後の回路計で対処することによってジッタの問題が解消できょってが必要ないで、まず最初にダイアグラムを2つの領域、すなわち近接位相ノイズと広帯域ノイズに分けます。広帯域ノイズはフィルタで容易に除去できるので、問題は近接位相ノイズに絞られます。クロック・ソースにとっての必要条件は、近接ノイズが低いことと、最小のオフセットでできるだけ急峻にロールオフすることです。

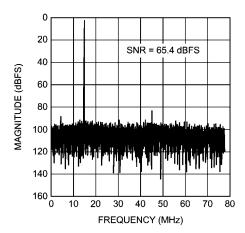

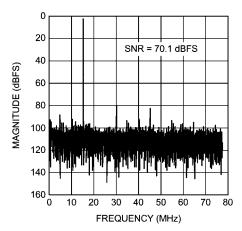

広帯域ノイズをフィルタで除去しなければならないのは、ADCクロック入力に印加される信号がアナログ入力に畳み込まれるからです。ADC14V155の1.1GHzという非常に広い入力帯域幅は、非常に広いクロック入力帯域幅にマッチします。これは、クロック・ソースからの多くの広帯域ノイズはフィルタで除去されていないと、第1ナイキスト・ゾーンでエイリアシングが発生し、SNRを悪化させることを意味します。

FIGURE 2. The Effect on SNR with and without a Bandpass Filter on the Clock Source (Using a BP Filter Reduces the Noise Floor by 4.7 dB)

#### サブ・サンプリングの落とし穴

サブ・サンプリングを用いる場合は、別の罠にはまることもあります。サブ・サンプリングとは、クロック周波数が信号周波数の 2 倍以下である状態を指し、これはエイリアシング防止のため、fs は fin の 2 倍以上にすべきだとするナイキストの定理に反します。サブ・サンプリングの場合、信号とその高調波が第 1 ナイキスト・バンドでエイリアシングを発生させますが、エイリアシングが発生する周波数がわかっていれば、問題となる信号が折り返された高調波スプリアスで壊されないように周波数プランを設計します。

一般的な周波数プランのひとつは、fs/4 に折り返される入力周波数を使う方法です。この周波数プランではすべての高調波が DC、fs/4 または fs/2 に折り返されます。このプランの利点は、各高調波歪みスプリアスが互いに大きく離れることです。このためフィルタ処理は簡単になり、対象はナイキスト・バンドの基本周波数に絞られます。ただし、この周波数プランではすべてのADCの高調波スプリアスが重複によって隠蔽された状態になるので、ADC 出力スペクトラムが実際よりもはるかに良くみえることになります。

真の性能を見極めるには、重複しているスプリアスが分かるように入力周波数を 0.1 ~ 1MHz の範囲でオフセットする必要があります。

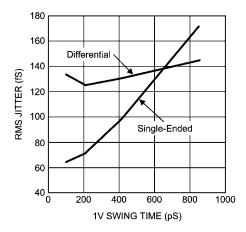

#### ADC クロック・レシーバ

また、ADC 内部のクロック・レシーバ回路がジッタをある程度発生するという問題もあります。この原因は、何らかの電源ノイズによってクロック・レシーバのトリップ・ポイントが少し変わり、有限の傾きを持つクロック信号が印加された時に、このノイズが位相ノイズに変換されることにあります。これは AM (振幅変調)と PM (位相変調)の関係に似ています。すなわち、AM が電源ノイズで、これが PM クロック・ノイズへ変換され、時間領域でみた時のジッタになるという関係です。クロックの遷移時間が長いほど、加わるジッタが増えます。高スルーレートのクロックを用いることで、この影響を最小限に抑えられます。従って、高速な遷移時間を持つ方形波クロック入力を選ぶのがベストで、最良の SNR が得られます。

FIGURE 3. Swing Time vs rms Jitter of a Differential Clock and Single-Ended Clock

ラボおよび概念試験では、周波数アジリティを得るために高品質の信号ジェネレータを用いるのが最良の選択肢です。いったん周波数プランを固定すれば、水晶発振器が高純度のクロックを発生します。PCB上で複数のクロックが必要な時は、ナショナルセミコンダクターの高精度クロック・コンディショナ LMK03000/2000 シリーズ製品を選択するとよいでしょう。

#### 入力ネットワーク

ADC を 1 つ選んで位相をテストする場合、信号ジェネレータを使って入力をドライブします。測定された ADC 性能が入力に印加された信号の純度より優ることがないのははっきりしています。これは、信号ジェネレータ出力のフィルタ処理はジェネレータの高調波歪みとノイズが ADC 入力に達するのを制限することを使命としているからです。代表的なシンセサイザの二次高調波歪み(H2)は - 40dBc から - 50dBcですが、ADC14V155 の 238MHz 時の H2 は - 85dBFS に抑えられます。90dB の二次 / 三次高調波減衰を提供する Trilithic VF シリーズ・フィルタのような、微調整可能なバンドパス・フィルタを使用することを推奨します。

入力信号のフィルタ処理は、もちろん最終的な製品アプリケーションで重要です。ADC14V155 は前節の「サンプリングの落とし穴」で説明したように、不要なすべてのノイズ成分を含むスペクトラム全体をサンプリングできる、1.1GHzの極めて広い入力帯域幅を持っています。この ADCは 155MHz の低い周波数でサンプリングする時でも支障はなく、この周波数より上のノイズが SNR に悪影響を与えるエイリアシングを第1ナイキスト・バンドで発生させても、中心周波数付近で入力信号をバンドパス・フィルタで処理することで問題は回避されます。

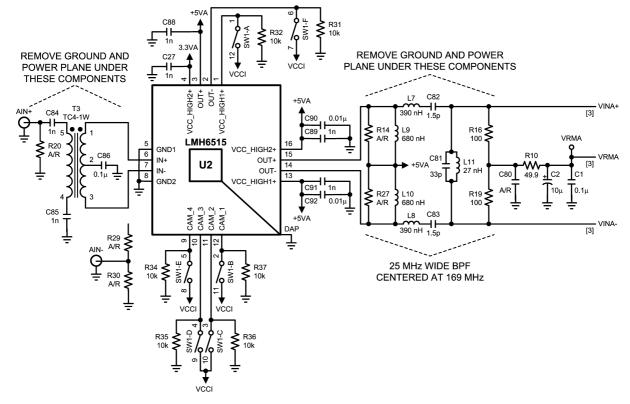

大半の実用例では、この ADC はトランスないしアンプを介して入力信号に結合されることになります。Figure 4 は、LMH6515 DVGA を使って ADC14V155 をドライブする回路例です。ADC とアンプの間には、約 169MHz を中心とする25MHz帯域幅の4次オーダーのフィルタを使用しています。抵抗 R16 および R19 は、ADC に入力同相バイアスを与え、フィルタの負荷インピーダンスを設定します。インピーダンスは高くしすぎないよう注意してください。たとえフィルタの減衰量が低下しても、SFDR も悪化するからです。ADCとアンプ歪みとの間の最良のトレードオフとなるインピーダンスは 500 であることが分かっています。

FIGURE 4. Example Circuit to Drive the Input of the ADC14V155

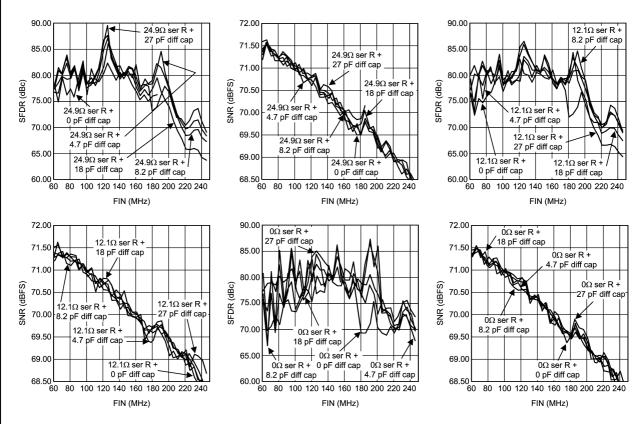

追加の RC ネットワークを用い、これをアプリケーションの入力周波数に合わせることによって、SFDR 特性を最大化することができます。このネットワークは、ADC の入力端子に接続される 2 つの直列抵抗と 1 つのシャント・コンデンサで構成されます。これらの抵抗およびコンデンサは、ADC 入力時の S/H 回路からのかく乱が原因で、セトリング時間に影響を与えます。この RC の組み合わせは、ADC の前の最後のローパス・フィルタともなり、このカットオフ

周波数はノイズの除去および高調波の減衰に影響を与えます。シャント・コンデンサの容量を大きくすると、このローパス・フィルタのカットオフ周波数が低下し、低周波数歪みが改善します(ただし、入力帯域幅の犠牲を伴います)。ADC14V155のデータシートは、広い fin 範囲にわたる良い妥協点は、抵抗が 12.1 、コンデンサが 15pF であることを示しています。

FIGURE 5. Frequency Sweeps Illustrating SFDR Performance with Different Filter Settings

#### デカップリング

適切な低ジッタ・クロックを選択し、フィルタ処理したクリーンな信号をADC入力へ印加した後、さらにもうひとつの注意点があります。ノイズはADCのリファレンス・ピンと電源ピンを通ってADCに結合する可能性もあります。最善の策は、デカップリング・コンデンサをADCパッケージとピンのできるだけ近くに配置することです。これはミリメータ単位で行います。デカップリングには、少なくとも2つの異なるコンデンサ値、すなわち0.1 μ F および0.01 μ F を使い、これらを電源プレーンとグラウンド・プレーンに直接に接続する必要があります。長いパターンは寄生抵抗および寄生インダクタンスの元になるので避けるべきです。

LLP、TQFP 両パッケージで提供される ADC14155 の SNR および SFDR 性能を測定する時は、アドレスされていないとリード長が問題になることがあります。テスト結果によると、TQFP パッケージのリード長の場合、最適な性能を得るにはデカップリング・コンデンサはリファレンス・ピンおよび電源ピンの直下の基板裏面に接続する必要があります。表(おもて)面でのデカップリングだと、SNR はほぼ 3dB、SFDR は 3dB 以上それぞれ悪化します。

### 出力インタフェース

アナログ信号を変換した時点で、この結果を FPGA や ASIC などの次のプロセッシング手順へ送ることができます。デジタル変換されたデータの転送には、長年 CMOS 出力段が使われていました。 CMOS 段の出力レベルは負荷に依存し、信号は電圧モードです。シングルエンド・タイプの出力も、ノイズの同相成分除去には不向きです。 スイッチング速度が上がると容量性負荷をドライブする電流が増え、 CMOS 電圧振幅が小さくなります。 CMOS インタフェース上では、

約150MHz時にデータ転送の信頼性が失われてしまいます。 新タイプのインタフェースが必要ですが、そのための優れ た候補が LVDS です。

LVDS ドライバは差動スキームで 3.5mA の定電流を提供します。100 終端抵抗をできるだけレシーバ・ピンの近くの各差動出力ラインの間に配置する必要があります。ADC14V155はインタリープDDR出力方式を採用しており、同じピン上で奇数ピットを先に、偶数ピットを後に出力します。出力状態はクロックの立ち上がりエッジと立ち下がりエッジで変わります。これにより、パッケージのピン数は50パーセントもしくは14ピン低減し、受信デバイスで同数のコネクション節減になります。ADC14V155 はデータ・ピンの他にも、LVDS フォーマット出力のオーバーレンジ・インジケータ(OVR)ピンおよびデータ・レディ・ストローブ(DRDY)ピンを備えています。

#### まとめ

ADC14V155 は優れた性能を持つ新世代の ADC で、非常に 広い帯域幅による高精度を提供します。周辺コンポーネントはカスケード接続段へのシグナル・インテグリティを決めるのに重要な役割を果たします。所定のシステム性能は いくつかの重要な設計 / レイアウト技法を用いることで達成されます。

このドキュメントの内容はナショナル セミコンダクター社製品の関連情報として提供されます。ナショナル セミコンダクター社は、この発行物の内容の正確性または完全性について、いかなる表明または保証もいたしません。また、仕様と製品説明を予告なく変更する権利を有します。このドキュメントはいかなる知的財産権に対するライセンスも、明示的、黙示的、禁反言による惹起、またはその他を問わず、付与するものではありません。

試験や品質管理は、ナショナル セミコンダクター社が自社の製品保証を維持するために必要と考える範囲に用いられます。政府が 課す要件によって指定される場合を除き、各製品のすべてのパラメータの試験を必ずしも実施するわけではありません。ナショナ ル セミコンダクター社は製品適用の援助や購入者の製品設計に対する義務は負いかねます。ナショナル セミコンダクター社の部品 を使用した製品および製品適用の責任は購入者にあります。ナショナル セミコンダクター社の製品を用いたいかなる製品の使用ま たは供給に先立ち、購入者は、適切な設計、試験、および動作上の安全手段を講じなければなりません。

それら製品の販売に関するナショナル セミコンダクター社との取引条件で規定される場合を除き、ナショナル セミコンダクター社は一切の義務を負わないものとし、また、ナショナル セミコンダクター社の製品の販売か使用、またはその両方に関連する特定目的への適合性、商品の機能性、ないしは特許、著作権、または他の知的財産権の侵害に関連した義務または保証を含むいかなる表明または黙示的保証も行いません。

#### 生命維持装置への使用について

ナショナル セミコンダクター社の製品は、ナショナル セミコンダクター社の最高経営責任者 (CEO) および法務部門 (GENERAL COUNSEL) の事前の書面による承諾がない限り、生命維持装置または生命維持システム内のきわめて重要な部品に使用することは認められていません。

あられてもなどが、とかまされ。 ここで、生命維持装置またはシステムとは (a) 体内に外科的に使用されることを意図されたもの、または (b) 生命を維持あるいは 支持するものをいい、ラベルにより表示される使用法に従って適切に使用された場合に、これの不具合が使用者に身体的障害を与 えると予想されるものをいいます。重要な部品とは、生命維持にかかわる装置またはシステム内のすべての部品をいい、これの不 具合が生命維持用の装置またはシステムの不具合の原因となりそれらの安全性や機能に影響を及ぼすことが予想されるものをいい ます。

National Semiconductor とナショナル セミコンダクターのロゴはナショナル セミコンダクター コーポレーションの登録商標です。その他のブランド や製品名は各権利所有者の商標または登録商標です。

Copyright © 2007 National Semiconductor Corporation

製品の最新情報については www.national.com をご覧ください。

### ナショナル セミコンダクター ジャパン株式会社

本社 / 〒 135-0042 東京都江東区木場 2-17-16

TEL.(03)5639-7300

技術資料(日本語/英語)はホームページより入手可能です。

www.national.com/jpn/

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定して収ない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2011, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

#### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。 1. 熱電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置 類の接地等の静電気帯電防止措置は、常に管理されその機能が確認 されていること。

#### 2. 温·湿度環境

■ 温度:0~40℃、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

- 4. 機械的衝擊

- 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

- 5. 熱衝撃

- はんだ付け時は、最低限260℃以上の高温状態に、10秒以上さら さないこと。(個別推奨条件がある時はそれに従うこと。)

- 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上