UCD90120

www.tij.co.jp JAJS460

# UCD90120 12チャネル・シーケンサおよび システム動作状態監視

## 特長

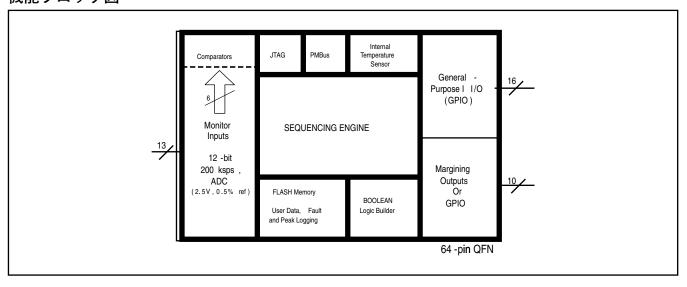

- 12チャネルの電圧の監視とシーケンシング

- 全電源チャネルを200μs毎にサンプリング

- 2.5V, 0.5%精度の内部基準電圧による12ビット ADC

- 時間、電源チャネル、およびピン設定の依存関係に基づいたシーケンス制御

- 6つのハードウェア・コンパレータにより電源障害時に80µs未満の応答時間を実現

- 監視入力毎に4つのプログラマブルな低電圧および過電圧のスレッショルド

- リトライ、スレーブのシャットダウン、および 再シーケンスを含めたプログラマブルな障害対応

- 不揮発性エラー・ログ

- 最大18件の障害情報を記録

- すべての監視入力に対してピーク値を記録

- 10チャネルの電源の閉ループ制御·マージニング 機能

- マージン出力ポートによって電源電圧をユーザ 定義のマージン・スレッショルドに調整

- 一 未使用のマージン出力ポートをGPIOまたは汎用 PWM出力として使用可能

- ウォッチドッグ・タイマとシステム・リセット

- プログラマブルなWDTリセットおよびスタート 時間

- 一 設定可能なシステム・リセット・パルス幅

- 柔軟なデジタルI/O設定

- GPO設定用ブール論理ビルダ

- GPIOをイネーブル、リセット、パワーグッド、 および他のオンボード機能として使用可能

- 広範囲な単一電源電圧(3.3V~12V)

- 内部温度センサ

- 64ピンQFNパッケージ

- JTAGおよびI<sup>2</sup>C/SMBus/PMBusインターフェイス

- Fusion Digital Power™ GUIによるデバイス動作の 設定、監視

Fusion Digital Powerは、テキサス・インスツルメンツの登録商標です。

## アプリケーション

- 産業用/自動試験装置

- 通信、ネットワーク機器

- サーバおよびストレージ・システム

- 複数の電源チャネルのシーケンシングと監視を必要とする任意のシステム

## 概要

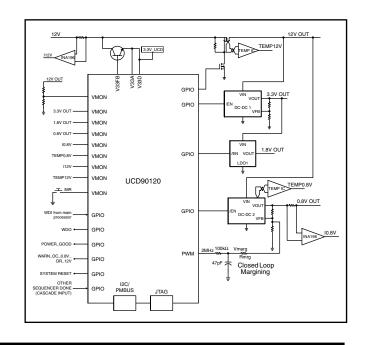

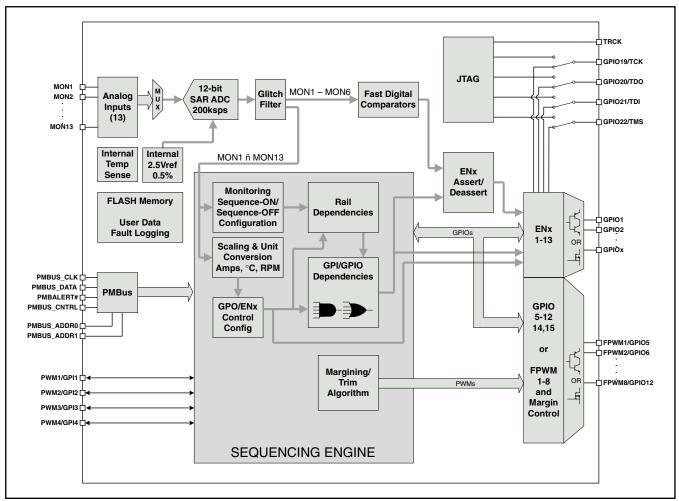

UCD90120電源シーケンサおよびシステム·動作状態監視は、 最大12チャネルの独立した電源電圧を監視し、シーケンシング を行えます。12ビットのADCと2.5Vの内部基準電源を内蔵し、 最大13の電源電圧、電流、および温度の入力を監視できます。

26本のGPIOピンが用意され、電源イネーブル、パワーオン・リセット信号、外部割り込み、複数のUCD90120デバイスのカスケード、または他のシステム機能に利用できます。そのうち12本のピンは、電源のマージニング、およびスイッチ・モード電源用クロック生成などの汎用PWM機能に使用できます。

デバイスの設定には、TIのFusion Digital Power Designerを

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI) が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。 日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料を

Tlおよび日本Tlは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

SLVS966 翻訳版

利用できます。これはPCベースのグラフィカル・ユーザ・インターフェイス (GUI) であり、すべてのシステム動作パラメータの設定、格納、および監視のための直感的なインターフェイスを提供します。

UCD90120は、量産前でのシステム内の設定とモニター用に  $I^2C/PMBus/SMBus$ 通信インターフェイスを備えており、量産 時のプログラミング用にJTAGポートを備えています。

## 静電気放電対策

これらのデバイスは、限定的なESD(静電破壊)保護機能を 内蔵しています。保存時または取り扱い時に、MOSゲートに 対する静電破壊を防止するために、リード線どうしを短絡して おくか、デバイスを導電性のフォームに入れる必要があります。

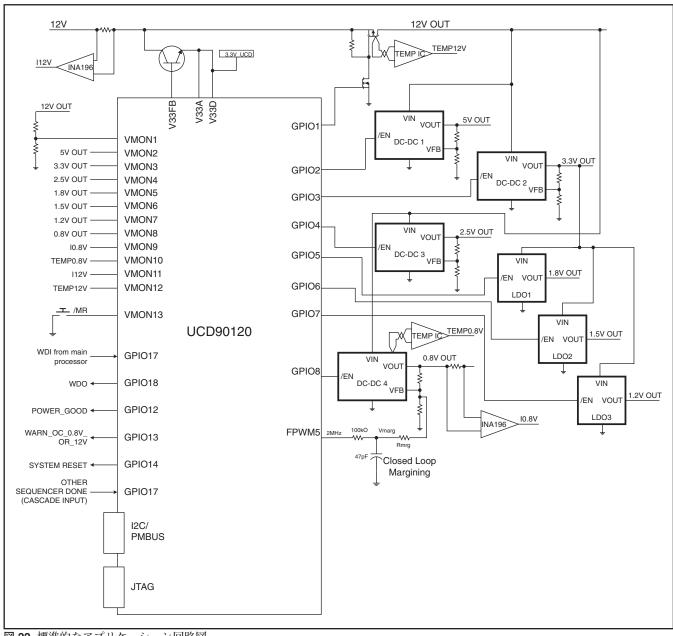

#### 機能ブロック図

#### オーダー情報

| オーダー可能な部品番号  | パッケージ   | 電源           |

|--------------|---------|--------------|

| UCD90120RGCR | 64ピンQFN | 2000個 (1リール) |

| UCD90120RGCT | 64ピンQFN | 250個 (1リール)  |

# 絶対最大定格(1)

|                                         |                                             | VALUE             | 単位 |  |

|-----------------------------------------|---------------------------------------------|-------------------|----|--|

| Voltage applied at                      | /oltage applied at V33D to DV <sub>SS</sub> |                   |    |  |

| Voltage applied at                      | /oltage applied at V33A to AV <sub>SS</sub> |                   |    |  |

| Voltage applied to                      | any pin <sup>(2)</sup>                      | −0.3V ~ 3.8       | V  |  |

| Storage temperature (T <sub>STG</sub> ) |                                             | <b>−</b> 40 ~ 150 | °C |  |

| Human body model (HBM)                  |                                             | 2.5               | kV |  |

| ESD Rating                              | Charged device model (CDM)                  |                   |    |  |

- (1) 絶対最大定格以上のストレスは、致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

- (2) すべての電圧はV<sub>SS</sub>基準

## 推奨動作条件

|                                                          |                                                                                             | MIN | NOM | MAX | 単位 |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------|-----|-----|-----|----|

| V <sub>33D</sub> , V <sub>33DIO</sub> , V <sub>33A</sub> | Supply voltage during operation (V <sub>33D</sub> , V <sub>33DIO</sub> , V <sub>33A</sub> ) | 3.0 | 3.3 | 3.6 | ٧  |

| T <sub>A</sub>                                           | Operating free-air temperature range                                                        | -40 |     | 110 | °C |

| $T_J$                                                    | Junction temperature                                                                        |     |     | 125 | °C |

## 電気的特性

動作温度範囲内(特に記述のない限り)

|                                            | パラメータ                    | テスト条件                                                              | MIN NOM  | MAX  | 単位 |

|--------------------------------------------|--------------------------|--------------------------------------------------------------------|----------|------|----|

| SUPPLY C                                   | CURRENT                  |                                                                    |          |      |    |

| I <sub>V33A</sub>                          |                          | V <sub>V33A</sub> = 3.3V                                           | 8        | 15   | mA |

| I <sub>V33DIO</sub>                        |                          | $V_{V33DIO} = 3.3V$                                                | 2        | 10   | mA |

| I <sub>V33D</sub>                          | Supply current           | $V_{V33D} = 3.3V$                                                  | 40       | 45   | mA |

| I <sub>V33D</sub>                          |                          | $V_{V33D}$ = 3.3V storing configuration parameters in flash memory | 50       | 55   | mA |

| INTERNAL                                   | REGULATOR CONTROLLER INP | UTS/OUTPUTS                                                        |          |      |    |

| V <sub>V33</sub>                           | 3.3V Linear Regulator    | Emitter of NPN transistor                                          | 3.25 3.3 | 3.35 | ٧  |

| V <sub>V33FB</sub>                         | 3.3V linear Reg Feedback |                                                                    | 4        | 4.6  | V  |

| I <sub>V33FB</sub>                         | Series pass base drive   | V <sub>VIN</sub> = 12V                                             | 10       |      | mA |

| Beta                                       | Series NPN pass device   |                                                                    | 40       |      |    |

| EXTERNA                                    | LLY SUPPLIED 3.3V POWER  |                                                                    |          |      |    |

| V <sub>V33D</sub> ,<br>V <sub>V33DIO</sub> | Digital 3.3V power       | T <sub>ambient</sub> = 25°C                                        | 3.00     | 3.60 | V  |

| V <sub>V33A</sub>                          | Analog 3.3V power        | T <sub>ambient</sub> = 25°C                                        | 3.00     | 3.60 | V  |

## 電気的特性

動作温度範囲内(特に記述のない限り)

|                          | パラメータ                                             | テスト条件                                                     | MIN                          | NOM | MAX           | 単位      |

|--------------------------|---------------------------------------------------|-----------------------------------------------------------|------------------------------|-----|---------------|---------|

| ANALOG INP               | UTS (MON1–MON13)                                  |                                                           |                              |     |               |         |

| V <sub>MON</sub>         | Input voltage range                               | MON1-MON9                                                 | 0.0                          |     | 2.5           | V       |

|                          |                                                   | MON10-MON13                                               | 0.2                          |     | 2.5           | V       |

| INL                      | ADC integral nonlinearity                         |                                                           | -2.5                         |     | 2.5           | mV      |

| I <sub>lkg</sub>         | Input leakage current                             | 3V applied to pin                                         |                              |     | 100           | nA      |

| I <sub>OFFSET</sub>      | Input offset current                              | 1kΩ source impedance                                      | -5                           |     | 5             | μΑ      |

| R <sub>IN</sub>          | Input impedance                                   | MON1-MON9, Ground reference                               | 8                            |     |               | ΜΩ      |

|                          |                                                   | MON10-MON13, Ground reference                             | 0.5                          | 1.5 | 3.0           | ΜΩ      |

| C <sub>IN</sub>          | Input capacitance                                 |                                                           |                              |     | 10            | pF      |

| T <sub>CONVERT</sub>     | ADC sample period                                 | 14 voltages sampled, 3.89 μsec/sample                     |                              | 200 |               | μsec    |

| V <sub>REF</sub>         | ADC 2.5V internal                                 | 0°C to 125°C                                              | -0.5%                        |     | 0.5%          |         |

|                          | reference accuracy                                | -40°C to 125°C                                            | -1.0%                        |     | 1.0%          |         |

| ANALOG INP               | UT (PMBUS_ADDRx, INTERNAL TEI                     | MP SENSE)                                                 | ·                            |     |               |         |

| I <sub>BIAS</sub>        | Bias current for PMBus Addr pins                  |                                                           | 9                            |     | 11            | μΑ      |

| V <sub>ADDR_OPEN</sub>   | Voltage – open pin                                | AddrSens0,1 open                                          | 2.26                         |     |               | V       |

| V <sub>ADDR_SHORT</sub>  | Voltage – shorted pin                             | AddrSens0,1 short to ground                               |                              |     | 0.124         | V       |

| Temp <sub>Internal</sub> | Internal temperature sense accuracy               | Over range from 0°C to 100°C                              | -5                           |     | 5             | °C      |

| DIGITAL INPU             | JTS AND OUTPUTS                                   |                                                           |                              |     |               |         |

| V <sub>OL</sub>          | Low-level output voltage                          | $I_{OL} = 6 \text{ mA}^{(1)}, V_{33DIO} = 3.0 \text{ V}$  |                              | D   | gnd +<br>0.25 | V       |

| V <sub>OH</sub>          | High-level output voltage                         | $I_{OH} = -6 \text{ mA}^{(2)}, V_{33DIO} = 3.0 \text{ V}$ | V <sub>33DIO</sub><br>- 0.6V |     |               | V       |

| V <sub>IH</sub>          | High-level input voltage                          | V <sub>33DIO</sub> = 3.0 V                                | 2.1                          |     | 3.6           | V       |

| V <sub>IL</sub>          | Low-level input voltage                           | V <sub>33DIO</sub> = 3.5 V                                |                              |     | 1.4           | V       |

| SYSTEM PER               | RFORMANCE                                         |                                                           | '                            |     |               |         |

| V <sub>DD</sub> Slew     | Minimum V <sub>DD</sub> slew rate                 | V <sub>DD</sub> slew rate between 2.3 and 2.9V            | 0.25                         |     |               | V/ms    |

| V <sub>RESET</sub>       | Supply voltage at which device comes out of reset | For power on reset (POR)                                  |                              |     | 2.4           | V       |

| t <sub>RESET</sub>       | Low pulse length needed at nReset pin             | To reset device during normal operation                   | 2                            |     |               | μS      |

| f(PCLK)                  | Internal oscillator frequency                     | T <sub>A</sub> = 125°C, T <sub>A</sub> = 25°C             |                              | 250 |               | MHz     |

| T <sub>retention</sub>   | Retention of configuration parameters             | $T_J = 25^{\circ}C$                                       | 100                          |     |               | Years   |

| Write_Cycles             | Number of nonvolatile erase/write cycles          | T <sub>J</sub> = 25°C                                     | 20                           |     |               | Kcycles |

<sup>(1)</sup> 規定された最大電圧降下を維持するには、全出力を合わせた最大合計電流IOHmaxおよびIOLmaxが12mAを超えないようにする必要があります。 (2) 規定された最大電圧降下を維持するには、全出力を合わせた最大合計電流IOHmaxおよびIOLmaxが48mAを超えないようにする必要があります。

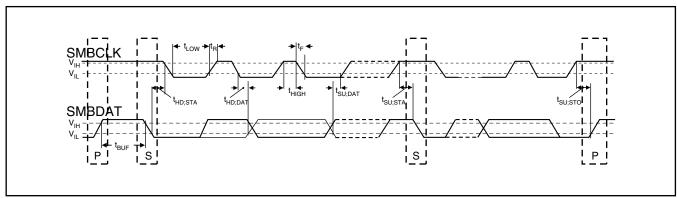

#### PMBus/SMBus/I<sup>2</sup>C

I<sup>2</sup>C、SMBus、およびPMBusをサポートする通信インターフェイスのタイミング特性およびタイミング図を以下に示します。

#### I<sup>2</sup>C/SMBus/PMBusのタイミング要件

T<sub>A</sub> = -40°C~85°C、3.0V < V<sub>DD</sub> < 3.6V、標準値はT<sub>A</sub> = 25°CおよびV<sub>CC</sub> = 2.5Vでの値です(特に記述のない限り)。

|                   | パラメータ                                  | テスト条件                           | MIN  | TYP | MAX  | 単位  |

|-------------------|----------------------------------------|---------------------------------|------|-----|------|-----|

| FSMB              | SMBus/PMBus operating frequency        | Slave mode, SMBC 50% duty cycle | 10   |     | 1000 | kHz |

| FI2C              | I <sup>2</sup> C operating frequency   | Slave mode, SCL 50% duty cycle  | 10   |     | 1000 | kHz |

| t(BUF)            | Bus free time between start and stop   |                                 | 4.7  |     |      | μs  |

| t(HD:STA)         | Hold time after (repeated) start       |                                 | 0.26 |     |      | μs  |

| t(SU:STA)         | Repeated start setup time              |                                 | 0.26 |     |      | μs  |

| t(SU:STO)         | Stop setup time                        |                                 | 0.26 |     |      | μs  |

| t(HD:DAT)         | Data hold time                         | Receive Mode                    | 0    |     |      | ns  |

| t(SU:DAT)         | Data setup time                        |                                 | 50   |     |      | ns  |

| t(TIMEOUT)        | Error signal/detect                    | See <sup>(1)</sup>              |      |     | 35   | ms  |

| t(LOW)            | Clock low period                       |                                 | 0.5  |     |      | μs  |

| t(HIGH)           | Clock high period                      | See (2)                         | 0.26 |     | 50   | μs  |

| t(LOW:SEXT)       | Cumulative clock low slave extend time | See (3)                         |      |     | 25   | ms  |

| t <sub>FALL</sub> | Clock/data fall time                   | See (4)                         |      |     | 120  | ns  |

| t <sub>RISE</sub> | Clock/data rise time                   | See (5)                         |      |     | 120  | ns  |

- (1) いずれかのクロックの "Low" 時間がt<sub>(TIMEOUT)</sub>を超えると、デバイスはタイムアウトします。

(2) t<sub>(HIGH)</sub>の最大値は、最小バス・アイドル時間です。t > 50msでSMBC = SMBD = 1の場合、実行中のトランザクションがリセットされます。この仕様は、NC\_SMB制御ビットがデフォルトのクリア状態(CLK[0] = 0)に保持される場合に有効です。

(3) t<sub>(LOW:SEXT)</sub>は、最初のスタートからストップまでの間、1つのメッセージ内でスレーブ・デバイスがクロック・サイクルを延長できる累積の時間です。

(4) 立ち上がり時間t<sub>r</sub> = (VIL<sub>MAX</sub> 0.15) ~ (VIH<sub>MIN</sub> + 0.15)

(5) 立ち下がり時間t<sub>f</sub> = 0.9VDD ~ (VIL<sub>MAX</sub> 0.15)

図 1. I<sup>2</sup>C/SMBusタイミング図

図 2. 拡張モードのバス・タイミング

#### 製品情報

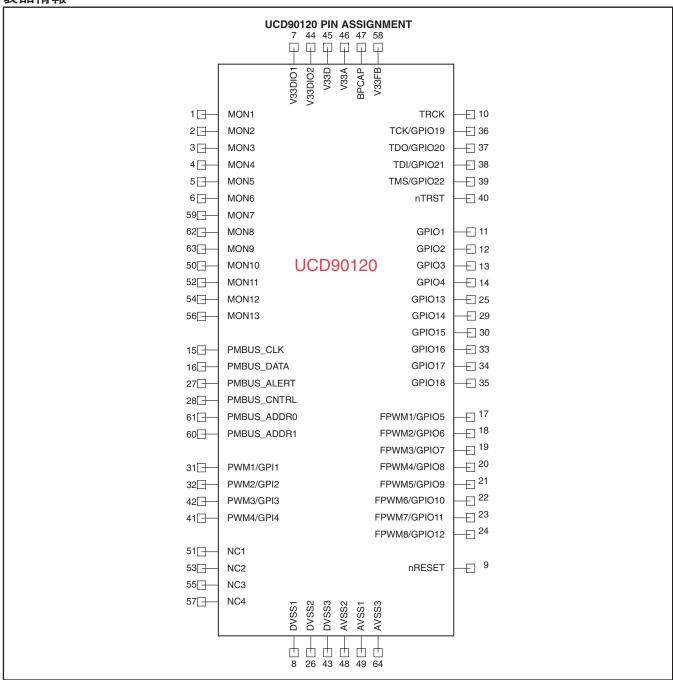

#### ピン機能

| ピン名      | ピン番号 | I/Oタイプ | 説明               |

|----------|------|--------|------------------|

| アナログ監視入力 |      |        |                  |

| MON1     | 1    | I      | アナログ入力 (0V~2.5V) |

| MON2     | 2    | I      | アナログ入力 (0V~2.5V) |

| MON3     | 3    | I      | アナログ入力 (0V~2.5V) |

| MON4     | 4    | I      | アナログ入力 (OV~2.5V) |

| MON5     | 5    | I      | アナログ入力 (0V~2.5V) |

| MON6     | 6    | 1      | アナログ入力 (0V~2.5V) |

#### ピン機能

| ピン機能            |          |           | I                                                     |  |  |

|-----------------|----------|-----------|-------------------------------------------------------|--|--|

| ピン名             | ピン番号     | 1/0タイプ    | 説明<br>                                                |  |  |

| MON7            | 59       | I         | アナログ入力 (0V~2.5V)                                      |  |  |

| MON8            | 62       | I         | アナログ入力 (0V~2.5V)                                      |  |  |

| MON9            | 63       | I         | アナログ入力 (0V~2.5V)                                      |  |  |

| MON10           | 50       | I         | アナログ入力 (0.2V~2.5V)                                    |  |  |

| MON11           | 52       | I         | アナログ入力 (0.2V~2.5V)                                    |  |  |

| MON12           | 54       | I         | アナログ入力 (0.2V~2.5V)                                    |  |  |

| MON13           | 56       | I         | アナログ入力 (0.2V~2.5V)                                    |  |  |

| GPIO            |          |           |                                                       |  |  |

| GPIO1           | 11       | I/O       | 汎用ディスクリートI/O                                          |  |  |

| GPIO2           | 12       | I/O       | 汎用ディスクリートI/O                                          |  |  |

| GPIO3           | 13       | I/O       | 汎用ディスクリートI/O                                          |  |  |

| GPIO4           | 14       | I/O       | 汎用ディスクリートI/O                                          |  |  |

| GPIO13          | 25       | I/O       | 汎用ディスクリートI/O                                          |  |  |

| GPIO14          | 29       | I/O       | 汎用ディスクリートI/O                                          |  |  |

| GPIO15          | 30       | I/O       | 汎用ディスクリートI/O                                          |  |  |

| GPIO16          | 33       | I/O       | 汎用ディスクリートI/O                                          |  |  |

| GPIO17          | 34       | I/O       | 汎用ディスクリートI/O                                          |  |  |

| GPIO18          | 35       | I/O       | 汎用ディスクリートI/O                                          |  |  |

| PWM出力           |          |           |                                                       |  |  |

| FPWM1/GPIO5     | 17       | I/O/PWM   | PWM(15.259kHz~125MHz)またはGPIO                          |  |  |

| FPWM2/GPIO6     | 18       | I/O/PWM   | PWM(15.259kHz~125MHz)またはGPIO                          |  |  |

| FPWM3/GPIO7     | 19       | I/O/PWM   | PWM (15.259kHz~125MHz) またはGPIO                        |  |  |

| FPWM4/GPIO8     | 20       | I/O/PWM   | PWM (15.259kHz~125MHz) \$ 7.44GPIO                    |  |  |

| FPWM5/GPIO9     | 21       | I/O/PWM   | PWM (15.259kHz~125MHz) またはGPIO                        |  |  |

| FPWM6/GPIO10    | 22       | I/O/PWM   | PWM (15.259kHz~125MHz) またはGPIO                        |  |  |

| FPWM7/GPIO11    | 23       | I/O/PWM   | PWM (15.259kHz~125MHz) またはGPIO                        |  |  |

| FPWM8/GPIO12    | 24       | I/O/PWM   | PWM (15.259kHz~125MHz) またはGPIO                        |  |  |

| PWM1/GPI1       | 31       | I/PWM     | 固定10kHz PWM出力またはGPI                                   |  |  |

| PWM2/GPI2       | 32       | I/PWM     | 固定1kHz PWM出力またはGPI                                    |  |  |

| PWM3/GPI3       | 42       | I/PWM     | PWM (0.93Hz~7.8125MHz) またはGPI                         |  |  |

| PWM4/GPI4       | 41       | I/PWM     | PWM (0.93Hz~7.8125MHz) またはGPI                         |  |  |

| PMBus通信インター     |          | 1/1 44141 | 1.0120WH2/ 67C 60H1                                   |  |  |

| PMBUS_CLK       | 15       | I/O       | PMBusクロック(3.3Vへのプルアップが必要)                             |  |  |

| PMBUS_DATA      | 16       | I/O       | PMBusデータ(3.3Vへのプルアップが必要)                              |  |  |

| PMBALERT#       | 27       | 0         | PMBusアラート、アクティブ・ロー、オープン・ドレイン出力(3.3Vへのプルアップが必要)        |  |  |

| PMBUS_CNTRL     | 28       | 1         | PMBus制御                                               |  |  |

| PMBUS_ADDR0     | 61       |           | PMBusアナログ・アドレス入力。最下位アドレス・ビット。                         |  |  |

| PMBUS ADDR1     | 60       | 1         | PMBusアナログ・アドレス入力。最下位アドレス・ビット。                         |  |  |

| JTAG            | 60       | ı         | FMIDUSアプログ・アドレス人力。 販工位アドレス・ピット。                       |  |  |

|                 | 10       | 0         | テスト・リターン・クロック                                         |  |  |

| TRCK TCK/GPIO19 | 10<br>36 | 1/0       | テスト・クロックまたはGPIO                                       |  |  |

| TDO/GPIO20      | 37       | 1/0       | テスト・データ出力またはGPIO                                      |  |  |

|                 |          |           | 1.111                                                 |  |  |

| TDI/GPIO21      | 38       | 1/0       | テスト・データ入力 (10kΩ抵抗でV <sub>dd</sub> に接続) またはGPIO        |  |  |

| TMS/GPIO22      | 39       | 1/0       | テスト・モード選択 (10kΩ抵抗でV <sub>dd</sub> に接続) またはGPIO        |  |  |

| nTRST           | 40       | I         | テスト・リセット - 10kΩ抵抗でグランドに接続                             |  |  |

| 入力電源とグランド       |          |           |                                                       |  |  |

| nRESET          | 9        |           | アクティブ・ローのデバイス・リセット入力。デバイスをリセットするには2μs以上 "Low"<br>に保持。 |  |  |

|                 |          |           | v ← W 1 ± 0                                           |  |  |

#### ピン機能

| ピン名            | ピン番号 | I/Oタイプ | 説明                                                    |  |

|----------------|------|--------|-------------------------------------------------------|--|

| V33FB          | 58   |        | 3.3Vリニア・レギュレータの制御出力                                   |  |

| V33A           | 46   |        | アナログ3.3V電源                                            |  |

| V33D           | 45   |        | デジタル・コア3.3V電源                                         |  |

| V33DIO1        | 7    |        | デジタルI/O 3.3V電源                                        |  |

| V33DIO2        | 44   |        | デジタルI/O 3.3V電源                                        |  |

| BPCap          | 47   |        | 部1.8V用バイパス・コンデンサ接続ピン - アナログ・グランドとの間に0.1μFのコンデンサを<br>続 |  |

| AVSS1          | 49   |        | アナログ・グランド                                             |  |

| AVSS2          | 48   |        | アナログ・グランド                                             |  |

| AVSS3          | 64   |        | アナログ・グランド                                             |  |

| DVSS1          | 8    |        | デジタル・グランド                                             |  |

| DVSS2          | 26   |        | デジタル・グランド                                             |  |

| DVSS3          | 43   |        | デジタル・グランド                                             |  |

| QFP Ground Pad | NA   |        | QFPグランド・パッド PowerPAD - グランド・プレーンに接続                   |  |

### 機能説明

#### TIのFusion GUI

デバイスの設定には、Texas InstrumentsのFusion Digital Power Designerを利用できます。これはPCベースのグラフィカル・ユーザ・インターフェイス (GUI) であり、直感的なデバイスへのI<sup>2</sup>C/PMBusインターフェイス環境を提供します。これによって設計エンジニアは、PMBusコマンドを直接使用せずにアプリケーションのシステム動作パラメータを設定し、設定をチップ上の不揮発メモリに格納して、システムの状態 (電圧、温度など) を監視できます。このデータシートでは全体にわたってFusionを参照し、多くのセクションでは画面のコピーも掲載されています。

#### 動作原理

今日の電子システムでは、多くの場合、膨大な数のマイクロコントローラ、DSP、FPGA、およびASICが使用されています。コア・プロセッサ、A/Dコンバータ、またはI/Oに電源を供給するため、各デバイスには複数の電源が備えられる場合があります。一般にこのようなデバイスでは、電圧をオンおよびオフにする順序やタイミングが重要となります。UCD90120は、不適切なパワーアップまたはパワーダウンによる誤動作、間欠的な動作、またはデバイスの損傷を防ぐために、電源電圧のシーケンシンス起動を制御できます。低電圧/過電圧障害、過電流

障害、および過熱障害を適切に処理することで、システムの寿命を伸ばし、長期的な信頼性を向上させることができます。 UCD90120では、システム障害の解析を助けるために、電源障害情報をチップ上の不揮発性フラッシュ・メモリに記録します。

システム検証時において4コーナー試験によって、システムの信頼性を向上できます。4コーナー試験では、最低および最高の想定周囲温度で、各電源を最低および最高出力電圧に設定した状態でシステムを動作させます(一般にマージニングと呼ばれます)。UCD90120では、最大10チャネルの電源に対して高精度な閉ループ制御のマージニングを実施できます。

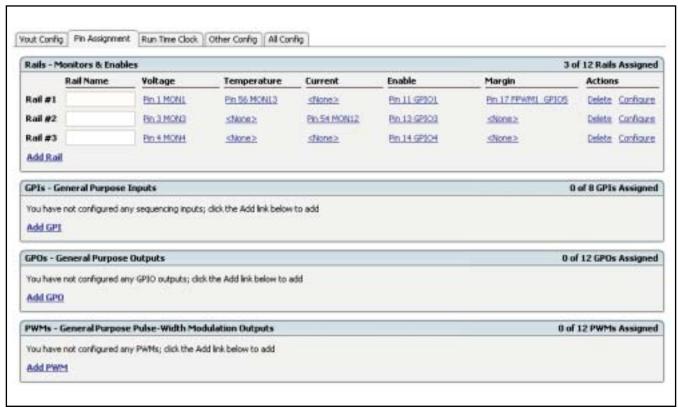

UCD90120の12チャネル・シーケンサは、PMBusベースまたはピン・ベースの制御環境で使用できます。TIのFusion GUIにより、13個のアナログ電圧監視入力、4個のGPI、および22個の柔軟に設定可能なGPIOを使用して、1~12チャネルの電源を備えたシステムのシーケンシング・ソリューションを設定できる強力かつシンプルなインターフェイスが提供されます。電源チャネルの設定には、電圧、温度、電流、電源イネーブル、およびマージニング出力を含めることができます。電源チャネルの定義には、そのうち少なくとも1つを含める必要があります。特定のシステムで求められる電源チャネルの動作をユーザが定義した後、各電源を監視およびイネーブルにするためのアナログ入力ピンおよびGPIOを選択できます(図3を参照)。

**図 3**. Fusionの "Pin Assignment" タブ

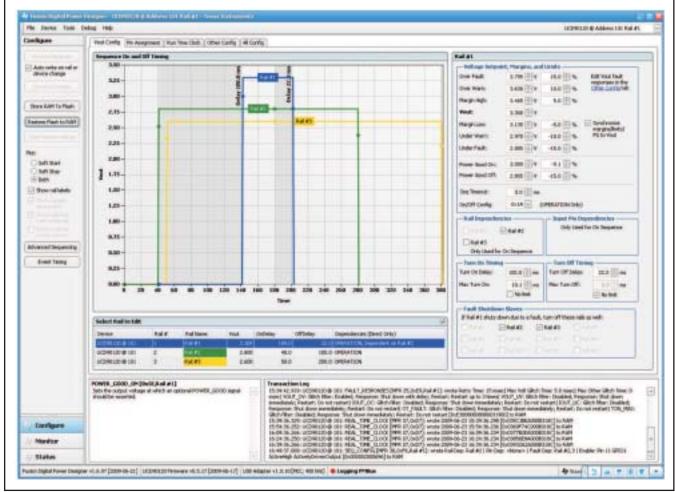

ピンの設定が済んだら、"Vout Config" タブで各電源チャネルに対して他の主要な監視およびシーケンシング条件を選択します(図4を参照)。

- 公称動作電圧(Vout)

- 低電圧 (UV) および過電圧 (OV) の警告/障害制限電圧値

- 最小/最大マージン電圧値

- パワーグッド・オン/オフ閾値

- PMBusベースまたはピン・ベースのシーケンシング制御 ("On/Off Config")

- パワーグッドに達する必要のある電源チャネル、または電源がイネーブルになる前に、定義された論理状態になる必要のある入力ピン ("Rail Dependencies" および "Input Pin Dependencies")

- ターンオンおよびターンオフ遅延タイミング

- イネーブルまたはディスエーブル後に電源がPOWER\_ GOOD\_ONまたはPOWER\_GOOD\_OFFに達するまでの最 大許容時間

- 電源の障害発生時にオフにする他の電源("Fault Shutdown Slaves")

**図 4**. Fusionの "Vout Config" タブ

"Synchronize margins/limits/PG to Vout" チェックボックスを使用すると、電源の公称動作電圧を変更したときに、その電源に関連付けられた他のすべての制限値を、各項目の右側に示されたパーセンテージに従って簡単に更新できます。

図4の左上部分にある図表は、シーケンス・オンおよびシーケンス・オフの設定全体をシミュレーションしたものです。これには、公称電圧、ターンオン/ターンオフ遅延時間、パワーグッド・オン/パワーグッド・オフ電圧、および電源間のすべてのタイミング依存関係が含まれます。

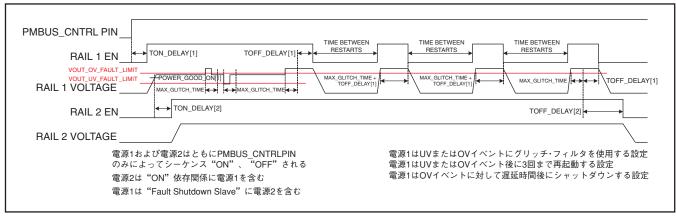

電源電圧がPOWER\_GOOD\_ON電圧に到達し、レギュレーション状態になったと判断された後は、2つのUVスレッショルドおよび2つのOVスレッショルドと比較され、警告制限または障害制限を超えていないかを確認します。障害が検出された場合、UCD90120は各種の柔軟なユーザ設定オプションに基づいて対応します。障害が発生したときには、電源を再起動、直ちにシャットダウン、ターンオフ遅延時間を使用してシーケンス・オフ、または電源のグループをシャットダウンして再度シーケンス・オン、といった処理を行えます。障害の種類によって異なる対応を行うこともできます。

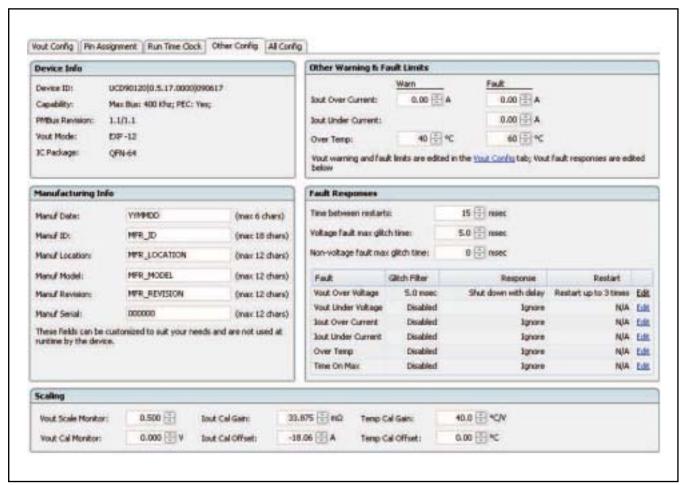

図 5. Fusionの "Other Config" タブによる障害対応設定

障害時の対応は、ユーザ固有の製造情報や外部スケール/オフセット値など他のいくつかのパラメータとともに、Fusionの "Other Config" タブで選択します。ユーザ要件を満足する設定が完了した後は、FusionがI<sup>2</sup>C/PMBus経由でUCD90120に接続されていれば、設定をデバイスのSRAMに書き込むことができます。その後、SRAMの内容をデータ・フラッシュ・メモリに格納することで、リセットまたは電源OFF・ON後も設定がデバイス内に保持されます。

Fusionの "Monitor" ページには、デバイス・ダッシュボード やシステム・ダッシュボードなど、デバイスやシステムの状態を リアルタイムで表示および制御するためのオプションがいくつ か用意されています。

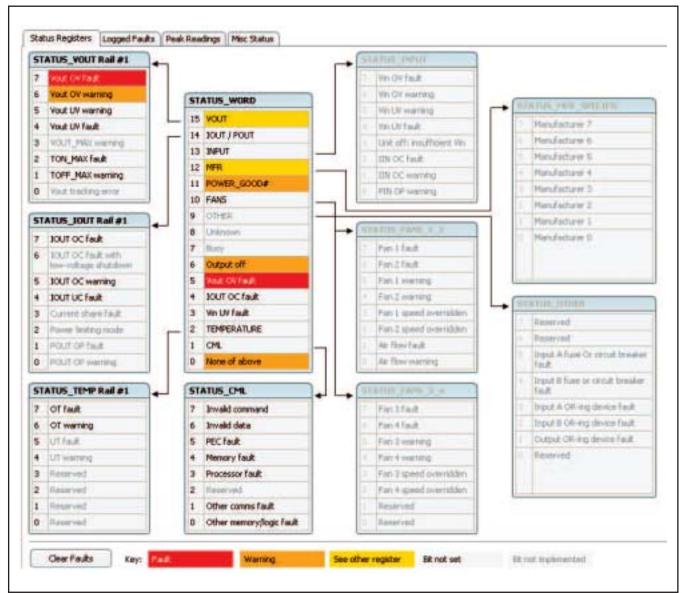

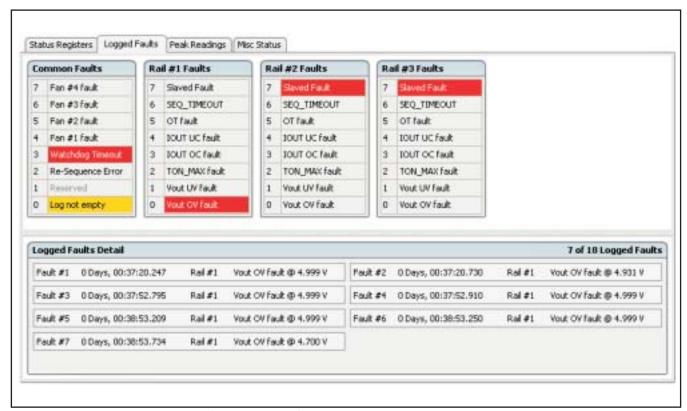

**図6.** Fusionの "Monitor" ページとデバイス・ダッシュボード およびシステム・ダッシュボード また、UCD90120には、各電源に対してステータス・レジスタが用意され、システムのトラブルシューティング用に障害情報をフラッシュ・メモリに記録できます。これは、電源またはシステムの障害時に非常に役立ちます。ステータス・レジスタ(図7)および障害ログ(図8)は、Fusionで表示できます。各ステータス・レジスタとサポートされるPMBusコマンドの詳細については、『UCD90120 PMBus Command Reference』および『PMBus\_Specification\_Part\_II\_Rev\_1-1\_20070205』を参照してください。

図7. Fusionの電源ステータス・レジスタ

図 8. Fusionのフラッシュ・エラー・ログ ("Logged Faults")

図 9. 詳細ブロック図

#### 電源シーケンシング

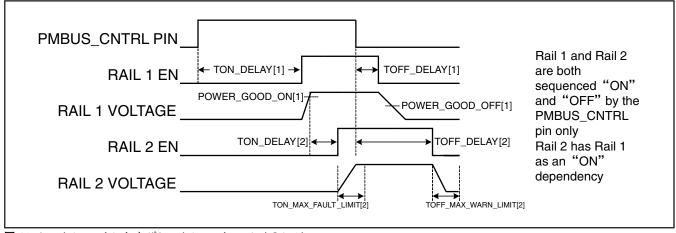

UCD90120は、GPIOを使用して電源のイネーブル・ピンを "High" または "Low" に制御することにより、最大12チャネルの電源のオン/オフ・シーケンシングを制御できます。PMBus ベースの設計では、システムPMBusマスタが、PMBUS\_CNTRL ピンをアサートするか、またはI<sup>2</sup>Cシリアル・バスでOPERATION コマンドを送信することにより、シーケンス・オン・イベントを開始できます。ピン・ベースの設計では、PMBUS\_CNTRLピンを使用してもシーケンス・オンおよびシーケンス・オフを行えます。

自動イネーブル設定では、OPERATIONコマンドおよび PMBUS\_CNTRLピンが無視されます。パワーアップ時に、各電源に対してすべての依存関係および遅延時間が満足される

と、シーケンス・オンが開始されます。電源の測定電圧が "Power Good On" (POWER\_GOOD\_ON(1)) 制限を超えると、電源はオンまたはレギュレーション状態と判定されます。電圧が "Power Good Off" (POWER\_GOOD\_OFF) を下回るまで、電源はレギュレーション状態と判定されます。

(1) このドキュメントでは、"Power Good On"などの設定パラメータは FusionのGUI名を示しています。PMBusのコマンド・リファレンス名は、 パラメータの初出時に括弧内(POWER GOOD ON)に表記されます。

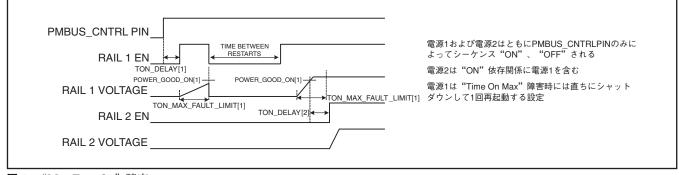

図 10. シーケンス・オンおよびシーケンス・オフ・タイミング

#### ターンオン・シーケンシング

各電源に対して次のシーケンス·オンのオプションがサポート されています。

- 監視のみ シーケンス・オンなし

- PMBus OPERATIONコマンドからオンになるまでの固定遅 延時間

- PMBUS\_CNTRLピンのアサート後の固定遅延時間

- 1つまたは複数の親電源がレギュレーションに達した後の固 定時間

- 指定したGPIがユーザ指定の状態に達した後の固定時間

- 上記のオプションの任意の組み合わせ

最大のTON\_DELAY時間は3276msです。

#### ターンオフ・シーケンシング

各電源に対して次のシーケンス·オフ·オプションがサポート されています。

- 監視のみ シーケンス・オフなし

- PMBus OPERATIONコマンドからオフになるまでの固定 遅延時間

- PMBUS CNTRLピンのデアサート後の固定遅延時間

- 電源での低電圧、過電圧、低電流、過電流、低温、過熱、または "Max Turn On" 障害に対応するための固定遅延時間

- 他の電源での障害に対応するための固定遅延時間(障害電源に対して "Fault Shutdown Slaves"を設定している場合)

- GPIOがユーザ指定状態になったときに対応するための固 定遅延時間

最大のTOFF\_DELAY時間は3276msです。

#### シーケンシング設定オプション

前述のターンオン/ターンオフ·シーケンシング·オプションに加えて、電源がイネーブルになってから、監視対象電源電圧が "Power Good On"設定に達するまでの時間を、"Max Turn On" (TON\_MAX\_FAULT\_LIMIT)として設定できます。"Max Turn On"は1ms単位で設定できます。0msに設定した場合は、"制限なし"を意味し、デバイスは出力電圧の起動を無制限に試行します。

電源は、直ちにオフにするか、またはユーザ定義の遅延時間に従ってシーケンス・オフするように設定できます。シーケンシングによるシャットダウンは、各電源に対して適切な"Turn Off Delay" (TOFF\_DELAY)を選択することにより設定できます。"Turn Off Delay"時間は、PMBUS\_CNTRLピンのデアサート時、PMBus OPERATIONコマンドによるSoft Stopコマンド実行時、または"Fault Shutdown Slaves"として他の電源で設定されている電源の障害発生時に開始されます。

1つの電源のシャットダウンによって、他の電源またはコントローラのシャットダウンを開始することができます。複数のUCD90120を使用したシステムでは、各コントローラが他のコントローラに対してマスタとスレーブの両方になることが可能です。

#### 電圧監視

アナログ入力ピンを使用して、最大13点の電圧を監視できます。入力電圧範囲は、MONピン1~6、59、62、63に対して0V~ 2.5Vです。ピン50、52、54、56は、最低測定値が0.2Vです。これらのピンに0V~0.2Vの電圧が印加されると、0.2Vとして読み取られます。2.5Vを超える電圧は、外部抵抗を使用して分圧すること

により監視できます。

ADCは連続して動作し、1つのアナログ入力の変換に $3.89\mu s$  必要で、オンボード温度センサを含む14個すべてのアナログ入力を変換するのに $54.5\mu s$ かかります。各電圧は、シーケンシングおよび監視アルゴリズムによって $200\mu s$ 毎にサンプリングされます。サンプリングされる電圧の最大ソース・インピーダンスは、 $4k\Omega$ より小さい必要があります。このソース・インピーダンス制限は、アナログ入力ピンに印加された電圧を抵抗分圧回路で低下させる場合には、特に重要となります。

電源1~電源6に対して選択できるMONピンには、オプションのデジタル・ハードウェア・コンパレータが備えられ、より高速の障害検出を行うために使用できます。ソフトウェアのスレッショルドが4つあるのに対して、各ハードウェア・コンパレータには2つのスレッショルド(1つのUVと1つのOV)があります。ハードウェア・コンパレータはUVまたはOV状態に対して約80μsで応答し、それによって電源のディスエーブルまたはGPOのアサートを行えます。ハードウェア・コンパレータで実行できる障害対応は、即時のシャットダウンだけです。

ADCでは2.5Vの内部基準電源が使用されます。ADCリファレンスは、0°C~125°Cで $\pm$ 0.5%、-40°C~125°Cで $\pm$ 1%の公差を持ちます。2.5Vより高い電圧の監視には、外部に分圧回路が必要です。公称電源電圧と外部のスケール・ファクタをFusion GUIに入力でき、それを使用して、ADC入力電圧の代わりに、監視された実際の電圧がレポートされます。公称電圧に基づき、

| 電圧範囲(V) |                  | 分解能 (mV) |

|---------|------------------|----------|

| 0       | 127.99805        | 1.95313  |

| 0       | 63.99902         | 0.97656  |

| 0       | 31.99951         | 0.48828  |

| 0       | 15.99976 0.24414 |          |

| 0       | 7.99988          | 0.12207  |

| 0       | 3.99994          | 0.06104  |

| 0       | 1.99997          | 0.03052  |

| 0       | 0.99998          | 0.01526  |

表 1. 電圧範囲と分解能

レポートされる電圧の範囲と精度が表1に従って設定されます。 監視結果は約15μVの分解能でレポートされていますが、実

監視結果は約15μVの分解能でレホートされていますが、実際の変換分解能は2.5Vのリファレンスおよび12ビットADCによって610μVに固定されています。

MONピンでは電圧を直接測定できますが、各入力は電圧、電流、または温度として定義できます。1つの電源に3つの測定タイプをすべて含める為、それぞれ別のMONピンで監視することができます。電源に電圧と電流の両方が割り当てられている場合は、電源に対して電力を計算してレポートできます。各MON入力に適用されるデジタル・フィルタリングは、信号の種類によって異なります。電圧入力はフィルタリングされません。電流入力には、時定数が約1秒のローパス・フィルタが適用されます。温度入力には、時定数が約12.4秒のローパス・フィルタが適用されます。

#### 電流監視

アナログ入力を使用して電流を監視できます。外部回路を使用して、電流を使用するUCD90120 MONxの入力範囲内の電圧へと変換する必要があります。

監視入力を電流として設定している場合は、時定数が約1秒の移動平均デジタル・フィルタによって、測定値を平滑化できます。このフィルタは、誤った障害検出の可能性を低減し、電流の読み取りにわずかな遅延時間を加えます。電源に電圧監視と電流監視が定義されている場合、電源電圧がPOWER\_GOOD\_ONに達した時点で、低電流警告の監視が開始されます。電源に電圧監視が定義されていない場合、電流監視はTON\_DELAY後に開始されます。

本製品は、電流に関連した複数のPMBusコマンドをサポートしています。これには、MONピンから外部電流を読み取るREAD\_IOUT、過電流障害制限を設定するIOUT\_OC\_FAULT\_LIMIT、過電流警告制限を設定するIOUT\_OC\_WARN\_LIMIT、および低電流障害制限を設定するIOUT\_UC\_FAULT\_LIMITが含まれます。『UCD90120 PMBus Command Reference』には、PMBusコマンドを使用して電流障害時の対応を実装する方法が詳しく記載されています。

IOUT\_CAL\_GAINは、外部電流センサ、および電流センサと MONピンの間にあるアンプまたはアッテネータに対するスケール・ファクタを、ユーザが $m\Omega$ 単位で入力できるようにするためのPMBusコマンドです。IOUT\_CAL\_OFFSETは、MONピンの電圧が0Vとなる電流です。これらのPMBusコマンドの組み合わせにより、電流をアンペア単位でレポートできます。

#### 温度監視と内部温度センサ

アナログ入力を使用して温度を監視できます。外部回路を使用して、温度を使用するUCD90120 MONx入力範囲内の電圧へと変換する必要があります。

入力を温度として設定している場合は、時定数が約12.4秒の移動平均デジタル・フィルタによって、測定値を平滑化できます。このフィルタは、誤った障害検出の可能性を低減し、温度の読み取りにわずかな遅延時間を加えます。内部のデバイス温度は、シリコン・ダイオード・センサを使用して±5℃の精度で測定され、ADCを使用しても監視されます。温度監視は、リセットおよび初期化の直後に開始されます。

本製品は、温度に関連した複数のPMBusコマンドをサポートしています。これには、内部温度を読み取るREAD\_TEM-PERATURE\_1、外部温度を読み取るREAD\_TEMPERATURE\_2、および過熱障害制限を設定するOT\_FAULT\_LIMITが含まれます。『UCD90120 PMBus Command Reference』には、PMBusコマンドを使用して温度障害時の対応を実装する方法が詳しく記載されています。

TEMPERATURE\_CAL\_GAINは、外部温度センサ、および温度センサとMONピンの間にあるアンプまたはアッテネータに対するスケール・ファクタを、ユーザが $\mathbb{C}/\mathbb{V}$ 単位で入力できるようにするためのPMBusコマンドです。TEMPERATURE\_CAL\_OFFSETは、MONピンの電圧が0Vとなる温度です。これらのPMBusコマンドの組み合わせにより、温度を $\mathbb{C}$ 単位でレポートできます。

#### 障害対応と警告処理

監視される各電源には、2つのプログラマブルな警告レベル (UV、OV) および2つのプログラマブルな障害レベル (UV、OV) を持つソフトウェア・ウィンドウ・コンパレータがあります。監視される電圧のいずれかが警告または障害ウィンドウから外れたときや、電流、温度、または他の認識された障害が発生したときには、PMBALERT#ピンが直ちにアサートされ、PMBusステータス・レジスタの該当するビットがセットされます (図9)。ステータス・レジスタの詳細な説明については、『UCD90120 PMBus Command Reference』および『PMBus\_Specification\_Part\_II\_Rev\_1-1\_20070205』を参照してください。

各MON入力に対して、プログラマブルなグリッチ・フィルタをイネーブルまたはディスエーブルにできます。電圧として定義された入力に対するグリッチ・フィルタは、200μsの分解能で0~51msの範囲内で設定できます。電流または温度として定義された入力に対するグリッチ・フィルタは、100msの分解能で0~25.5秒の範囲内で設定できます。時定数が長いのは、電流入力と温度入力には固定ローパス・デジタル・フィルタが関連付けられているためです。

障害対応は、12ビットADCの結果に基づいて決定されます。本製品はADCの結果を順番に、プログラミングされた制限値と比較します。個々のイベントへの対応にかかる時間は、イベントがADC変換サイクル内のどの時点で発生したか、および選択されている障害対応の内容によって決まります。

図11.シーケンシングおよび障害対応のタイミング

図 12. "Max Turn On"障害

設定可能な障害制限は次のとおりです。

Max Turn ON fault: 起動時間障害 - イネーブルになった電源が設定時間内にPOWER\_GOOD\_ON制限に達しなかった場合にセットされます。

Under voltage warning :低電圧警告 - POWER\_GOOD\_ON設定に達した後で、電源電圧が指定されたUV警告制限を下回った場合にセットされます。

Under voltage fault:低電圧障害 - POWER\_GOOD\_ON設定に達した後で、電源が指定されたUV障害制限を下回った場合にセットされます。

Over voltage warning:過電圧警告 - スタートアップ中または動作中の任意の時点で、電源が指定されたOV警告制限を超えた場合にセットされます。

Over voltage fault:過電圧障害 - スタートアップ中または動作中の任意の時点で、電源が指定されたOV障害制限を超えた場合にセットされます。

Max Turn Off fault:停止時間障害 - シャットダウンを指示された電源が設定時間内に公称電源電圧の12.5%に達しなかった場合にセットされます。

障害は、警告よりも重大な状況です。警告または障害が発生すると常に、PMBALERT#ピンが直ちにアサートされます。警告が発生すると、次の動作が実行されます。

#### 警告時の動作

- PMBALERT#ピンを直ちにアサートする

- ステータス·ビットがセットされる

- GPIOピンをアサートする(オプション)

- ― 警告はフラッシュ·メモリに記録されない

障害時の対応は、いくつかのオプションから選択できます。

#### 障害時の対応

- "Continue Without Interruption": 障害のフラグをセットし、何も行いません。

- "Shut Down Immediately":障害電源を直ちにシャットダウンし、電源の設定に従って再起動します。

- 一 "Shut Down using TOFF\_DELAY" :電源に障害が発生した場合、設定に従ってリトライを行います。電源が復旧しない場合は、この電源とすべての"Fault Shutdown Slaves"のシャットダウンをスケジュールします。障害電源を含む選択されたすべての電源が、それぞれのT\_OFF\_DELAY時間に従ってシーケンス・オフされます。"Do Not Restart"を選択した場合は、障害の検出時にすべての選択された電源をシーケンス・オフします。

#### 再起動

- "Do Not Restart":シャットダウン後に障害電源の 再起動を試みません。

- "Restart Up To N Times":シャットダウン後に障害電源の再起動を最大14回試みます。再起動の間隔は、電源のイネーブル・ピンがデアサートされてから(設定されている場合はグリッチ・フィルタリングと"Turn Off Delay"時間の後)、再度アサートされるまでの時

- 間として測定されます。この時間は、5ms単位で0~1275msに設定できます。

- "Restart Continuously": "Restart Up To N Times" と同じですが、本製品は障害が解消されるまで再起 動を続けます。これは、PMBusのOPERATIONコマン ドとPMBUS\_CNTRLピン状態の指定された組み合わ せによって、または本製品の電源が切断されたときに 解除されます。

- "Shut Down Rails and Sequence On":選択された電源を直ちにシャットダウンするか、または "Continue Operation"時間後にシャットダウンした後、"Turn On Delay"時間を使用してそれらの電源をシーケンス・オンします。

### "Shut Down All Rails and Sequence On"

障害発生時に、UCD90120は該当する電源をオフにしてから再度シーケンス・オンを行うように設定できます。システム内のすべての電源のシーケンス起動を行うには、すべての電源が障害電源の "Fault Shutdown Slaves"として選択されている必要があります。障害電源が "Stop Immediately"または "Stop With Delay"に設定されている場合、"Fault Shutdown Slaves"として指定されている電源も同じように動作します。 "Shut Down All Rails and Sequence On"は、特定の障害に対して指定回数のリトライを終了するまでは実行されません。

電源がオフになるのを待つ間に、いずれかの電源が TOFF\_MAX\_WARN\_LIMITに達した場合は、エラーがレポートされます。この場合、再シーケンシング動作を続けるための設定可能なオプションがあります。障害電源と "Fault Shutdown Slaves"をシーケンス・オフした後、UCD90120は、0~1275ms (5ms単位)のプログラマブルな遅延時間だけ待ってから、スタートアップ・シーケンス設定に従って障害電源と "Fault Shutdown Slaves"をシーケンス・オンします。この動作は、障害電源と "Fault Shutdown Slaves"が正常にレギュレーションに達するまで、または、ユーザの選択によって1、2、3、または4回繰り返されます。再シーケンス動作が成功した場合は、再シーケンスされたすべての電源が1秒間正常動作を維持すると、再シーケンス・カウンタがリセットされます。

"Shut Down All Rails and Sequence On"動作がいったん開始されると、"Fault Shutdown Slaves"の電源で障害が発生しても無視されます。異なる"Fault Shutdown Slaves"電源で2つ以上の障害が同時に検出された場合は、より保守的な動作が行われます。例えば、電源のグループが既に2回目の再シーケンスに入っていて、本製品が再シーケンスを3回実行するよう設定されている場合に、別のグループの電源が再シーケンス状態に入った場合には、第2のグループの電源は1回しか再シーケンスのためにそのすべての電源のシャットダウンを待っているときに、別のグループの電源が再シーケンス状態に入った場合には、本製品は両方のグループのすべての電源がシャットダウンするまで待ってから、再シーケンスを行います。

#### **GPIO**

UCD90120には、入力または出力として機能できるGPIOピンが22本あります。各GPIOには、オープン・ドレイン、および3.3Vまたはグランドにアクティブに駆動できるプッシュ・プル出力といった、設定可能ないくつかの出力モード・オプションがあります。さらに、入力またはPWM出力として使用できる(GPOとしては使用できない)ピンが4本あります。表2に、

GPIOピンの可能な使用法と、各使用法に対する各タイプの最大数を示しています。GPIOピンは、シーケンシングおよびアラーム処理では依存関係を持つ場合があります。また、外部割り込み、パワーグッド、リセット、または複数製品のカスケード接続など、システム・レベルの機能にも使用できます。GPOは、MONピンなしでGPIOをイネーブルとした電源を設定することにより、シーケンス・アップ/ダウンできます。

| ピン名          | ピン<br>番号 | 電源・イネーブル<br>(最大12) | GPI<br>(最大8) | GPO<br>(最大12) | PWM OUT<br>(最大12) | マージンPWM<br>(最大12) |

|--------------|----------|--------------------|--------------|---------------|-------------------|-------------------|

| FPWM1/GPIO5  | 17       | X                  | X            | X             | Х                 | X                 |

| FPWM2/GPIO6  | 18       | X                  | X            | Х             | Х                 | X                 |

| FPWM3/GPIO7  | 19       | X                  | X            | Х             | Х                 | X                 |

| FPWM4/GPIO8  | 20       | X                  | X            | X             | Х                 | X                 |

| FPWM5/GPIO9  | 21       | X                  | X            | X             | Х                 | X                 |

| FPWM6/GPIO10 | 22       | X                  | X            | X             | Х                 | X                 |

| FPWM7/GPIO11 | 23       | X                  | X            | Х             | Х                 | X                 |

| FPWM8/GPIO12 | 24       | Х                  | Х            | Х             | Х                 | Х                 |

| GPI1/PWM1    | 31       |                    | Х            |               | Х                 | Х                 |

| GPI2/PWM2    | 32       |                    | Х            |               | Х                 | Х                 |

| GPI3/PWM3    | 42       |                    | X            |               | Х                 | Х                 |

| GPI4/PWM4    | 41       |                    | Х            |               | Х                 | Х                 |

| GPIO1        | 11       | Х                  | X            | Х             |                   |                   |

| GPIO2        | 12       | Х                  | X            | Х             |                   |                   |

| GPIO3        | 13       | Х                  | Х            | Х             |                   |                   |

| GPIO4        | 14       | X                  | Х            | Х             |                   |                   |

| GPIO13       | 25       | Х                  | X            | Х             |                   |                   |

| GPIO14       | 29       | Х                  | X            | Х             |                   |                   |

| GPIO15       | 30       | Х                  | X            | Х             |                   |                   |

| GPIO16       | 33       | Х                  | Х            | Х             |                   |                   |

| GPIO17       | 34       | Х                  | Х            | Х             |                   |                   |

| GPIO18       | 35       | Х                  | Х            | Х             |                   |                   |

| TCK/GPIO19   | 36       | Х                  | Х            | Х             |                   |                   |

| TDO/GPIO20   | 37       | Х                  | Х            | Х             |                   |                   |

| TDI/GPIO21   | 38       | Х                  | Х            | Х             |                   |                   |

| TMS/GPIO22   | 39       | Х                  | Х            | Х             |                   |                   |

表 2. GPIOピンの設定オプション

#### GPIの特殊機能

図13は、GPIを使用できる5つの特殊な入力機能を示しています。これらの各機能には、それぞれ最大1本のピンしか割り当てることができません。

| GPI | Polarity:                                                                                                                                                                                                              |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (   | Active Low                                                                                                                                                                                                             |

| (   | Active High                                                                                                                                                                                                            |

|     | Sequencing timeout source                                                                                                                                                                                              |

|     | If checked and SEQ_TIMEOUT is non-zero on any rail, a faul will occur if this pin does not go active within SEQ_TIMEOUT time after the rail reaches its power good state.<br>SEQ_TIMEOUT is configured in Yout Config. |

|     | Latched Statuses Clear Source                                                                                                                                                                                          |

|     | When a GPO uses a latched status type (_LATCH) , you can configure a GPI that will clear the latched status.                                                                                                           |

|     | Input Source for Margin Enable                                                                                                                                                                                         |

|     | When this pin is asserted, all rails with margining enabled will be put in a margined state (low or high).                                                                                                             |

|     | Input Source for Margin Low/Not+tigh                                                                                                                                                                                   |

|     | When this pin is asserted, all rails with margining enabled will be put in a margined state (low or high).                                                                                                             |

|     | Fans Installed                                                                                                                                                                                                         |

|     | When this pin is asserted, fan control will be enabled. If<br>de-asserted, all fans configured will be ignored.                                                                                                        |

図 13. GPI設定 - 特殊な入力機能

### PWM出力

ピン17〜24は、FPWMとして設定できます。周波数範囲は、 15.259kHz〜125MHzです。FPWMは、閉ループ・マージニング 出力または汎用PWMとして設定できます。

PWM出力として使用しないFPWMピンは、GPIOとして設定できます。ペアとなるFPWMピンの一方をPWM出力として使用し、もう一方をGPOとして使用できます。FPWMピンは、GPOとして使用する場合、リセットから"Low"へアクティブに駆動されます。

ピン31、32、41、および42は、GPIまたはPWM出力として 使用できます。

FPWMの周波数設定は、ピンのペアに適用されます。

- FPWM1およびFPWM2 同じ周波数

- FPWM3およびFPWM4 同じ周波数

- FPWM5およびFPWM6 同じ周波数

- FPWM7およびFPWM8 同じ周波数

PWM出力として設定した場合は、制限が適用されます。

- PWM1は10kHzの固定周波数

- PWM2は1kHzの固定周波数

- PWM3およびPWM4の周波数は0.93Hz~7.8125MHz

#### 電源イネーブル

各GPIOは、アクティブ・ローまたはアクティブ・ハイの極性を持つ電源イネーブル制御ピンとして設定できます。出力モード・オプションには、オープン・ドレイン、および3.3Vまたはグランドにアクティブに駆動できるプッシュ・プル出力があります。リセット時、GPIOピンはハイ・インピーダンスになります。ただし、FPWM/GPIOピン17~24は"Low"に駆動されます。外部のプルダウン抵抗またはプルアップ抵抗をイネーブル・ピンに接続することで、リセット中に電源をオフに維持できます。UCD90120は、最大12本のイネーブル・ピンをサポートできます。

#### 複数製品のカスケード接続

GPIOピンを使用して、複数のコントローラを連携させることができます。その場合、GPIOピンを1つの製品からのパワーグッド出力として使用し、それを別の製品のPMBUS\_CNTRL入力ピンに接続します。これにより、複数の製品間にマスタ/スレーブ関係が構築されます。スタートアップ時には、マスタがスタート・シーケンスを完了してすべての電源がレギュレーション電圧に達した後で、各スレーブ・コントローラがそれぞれのスタート・シーケンスを開始します。シャットダウン時には、マスタがシーケンス・オフを開始するとすぐ、スレーブにシャットダウン信号を送信します。

1つまたは複数のマスタでの電源のシャットダウンによって、スレーブ・デバイスのシャットダウンを開始できます。マスタのシャットダウンは、意図的に開始することも、障害状態によって開始するようにもできます。この方法は、複数のコントローラの連携に役立ちますが、1つのコントローラ内の電源間に相互依存関係を持たせることはできません。

PMBus仕様では、コントローラ内のすべての電源がプログラミングされた電圧でレギュレーション状態になっているときに、パワーグッド信号がアクティブになると規定されています。 UCD90120では、パワーグッドの特定のサブセットに対して応答するようにGPIOを設定できます。

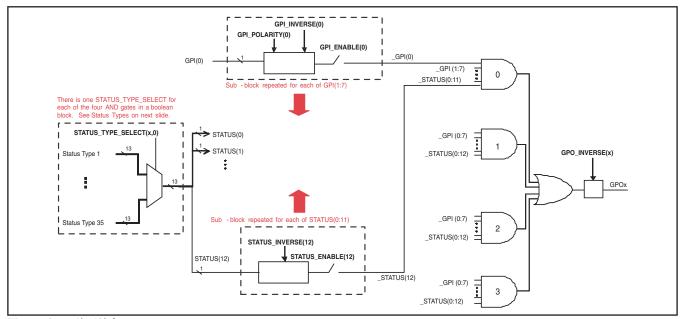

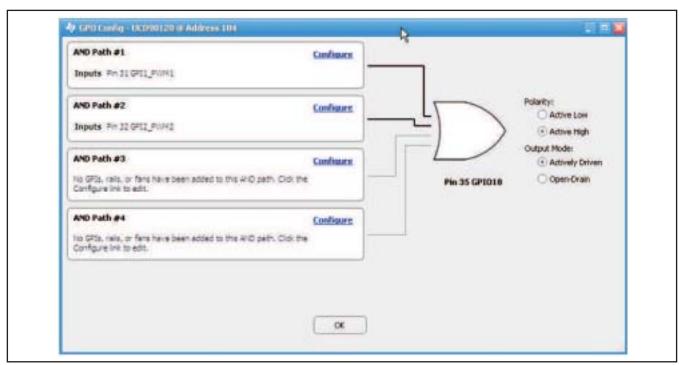

#### GPOの依存関係

GPIOは、最大4つのANDがすべてOR接続された論理結合に基づく出力として設定できます (図14参照)。論理ブロックへの入力には、GPIおよび電源・ステータス・フラグを含めることができます。論理ブロック内の各ANDゲートについて、1つの電源・ステータス・タイプを入力として選択できます。選択した電源・ステータスに対して、すべてのアクティブな電源のステータス・フラグをANDゲートへの入力として含めることができます。"\_LATCH"電源・ステータス・タイプは、MFR PMBusコマンドまたは特別に設定されたGPIピンによってクリアされるまで、アサートされた状態で保持されます。各種の電源・ステータス・タイプを図16に示します。電源・ステータス・タイプの詳細な定義については、『UCD90120 PMBus Command Reference』を参照してください。

図 14. ブール論理結合

図 15. Fusionのブール論理ビルダ

```

POWER_GOOD(0:12)

TEMP_OT_FAULT(0:12)

1.

20.

VOUT_OV_FAULT(0:12)

TEMP_OT_FAULT_LATCH(0:12)

2.

21.

3.

VOUT_OV_FAULT_LATCH(0:12)

22.

TEMP_OT_WARN(0:12)

VOUT_OV_WARN(0:12)

TEMP_OT_WARN_LATCH(0:12)

23.

4.

VOUT_OV_WARN_LATCH(0:12)

24.

INPUT_VIN_OV_FAULT(0:12)

5.

VOUT_UV_WARN(0:12)

25.

INPUT_VIN_OV_FAULT_LATCH(0:12)

6.

VOUT_UV_WARN_LATCH(0:12)

26.

INPUT_VIN_OV_WARN(0:12)

8.

VOUT_UV_FAULT(0:12)

27.

INPUT_VIN_OV_WARN_LATCH(0:12)

INPUT_VIN_UV_WARN(0:12)

VOUT_UV_FAULT_LATCH(0:12)

9

28

INPUT_VIN_UV_WARN_LATCH(0:12)

10

VOUT_TON_FAULT(0:12)

29

VOUT_TON_FAULT_LATCH(0:12)

INPUT_VIN_UV_FAULT(0:12)

11.

30.

12.

VOUT TOFF WARN(0:12)

31.

INPUT VIN UV FAULT LATCH(0:12)

VOUT_TOFF_WARN_LATCH(0:12)

MFR_SEQ_TIMEOUT(0:12)

13.

32.

14.

IOUT_OC_FAULT(0:12)

33.

MFR_SEQ_TIMEOUT_LATCH(0:12)

15.

IOUT_OC_FAULT_LATCH(0:12)

16.

IOUT_OC_WARN(0:12)

17

IOUT_OC_WARN_LATCH(0:12)

18.

IOUT_UC_FAULT(0:12)

IOUT_UC_FAULT_LATCH(0:12)

19.

```

図 16. 電源・ステータス・タイプ

#### マージニング

マージニングは、製品の検証試験で、システム全体がすべての条件で適切に動作することを確認するために使用されます。この条件には、最大および最小の電源電圧、負荷範囲、周囲温度範囲、および他の関連するパラメータ変動が含まれます。マージニングは、PMBusでOPERATIONコマンドを使用する、または2つのGPIOピンをMargin ENおよびMargin UP/DOWN入力として使用することにより、制御できます。『UCD90120 PMBus Command Reference』のMARGIN\_CONFIGコマンドには、マージニング中に障害を無視したり、パワーアップ時に閉ループ・マージニングを使用して電源出力電圧を1回だけ調整するなど、さまざまなマージニング・オプションが記述されています。

開ループ・マージニングは、電源の帰還ノードから1つの抵抗を介してグランドに接続し、別の抵抗を介して $V_{CC}$ または電源入力電圧に接続することで実現できます。電源レギュレーション・ループは、帰還ノード電圧の変動に対して、電源出力電圧を増減して帰還電圧を元の値に戻すことにより応答します。電圧の変化は、固定抵抗値と、 $V_{CC}$ およびグランドの電圧によって決定されます。各電源の帰還ノードと $V_{CC}$ またはグランドとの間に抵抗を接続するために、2本のGPIOピンを出力として設定する必要があります。

閉ループ・マージニングでは、マージニングを行う各電源に対してPWMまたはFPWM出力を使用します。外部RCネットワークによって、FPWMパルス列をDCマージニング電圧に変換します。マージニング電圧は、抵抗を介して目的とする電源帰還ノードに接続されます。電源出力電圧が監視され、その値がユーザによって設定されたMargin LowおよびMargin High電圧に達するまで、PWMデューティ・サイクルを調整することによりマージニング電圧を制御します。

## システム・リセット信号

UCD90120は、シーケンス・オンの一部としてプログラマブルなシステム・リセット・パルスを生成できます。このパルスは、特定の電源または電源の組み合わせがそれぞれのPOWER\_GOOD\_ONレベルに達してから、設定可能な遅延時間が経過するまで、GPIOをデアサート状態に保持するようプログラミングすることによって、生成されます。システム・リセット・パルス幅は、表3に示される値から選択して設定できます。

| パルス幅      |

|-----------|

| 0 ms      |

| 1 ms      |

| 2 ms      |

| 4 ms      |

| 8 ms      |

| 16 ms     |

| 32 ms     |

| 64 ms     |

| 128 ms    |

| 256 ms    |

| 512 ms    |

| 1.02 sec  |

| 2.05 sec  |

| 4.10 sec  |

| 8.19 sec  |

| 16.38 sec |

| 32.8 sec  |

表3.システム・リセット・パルス幅

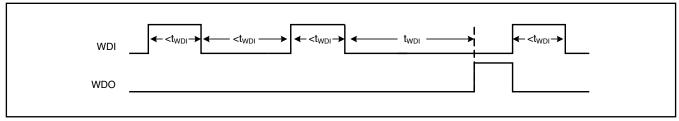

### ウォッチドッグ・タイマ

GPIおよびGPOをウォッチドッグ・タイマ (WDT) として設定できます。WDTは、電源シーケンシングとは独立して動作させるか、またはシステム・リセット信号を出力するよう設定されたGPIOに接続することができます。WDTは、ウォッチドッグ入力 (WDI) ピンの状態を切り替えるか、またはI<sup>2</sup>C経由でSYSTEM\_WATCHDOG\_RESETに書き込むことにより、リセットできます。

WDTは、パワーアップ時にすぐアクティブにするか、またはシステムの初期化完了まで待つように設定できます。表4に、タイムアウト・シーケンスが開始されるまでのプログラマブルな初期待ち時間を示します。

| WDTの初期待ち時間     |

|----------------|

| 0 ms           |

| 100 ms         |

| 200 ms         |

| 400 ms         |

| 800 ms         |

| 1.6 sec        |

| 3.2 sec        |

| 6.4 sec        |

| 12.8 sec       |

| 25.6 sec       |

| 51.2 sec       |

| 102 sec        |

| 205 sec        |

| 410 sec        |

| 819 sec        |

| 1638 sec       |

| ★ 4 以下のかが抱分とは明 |

表 4. WDTの初期待ち時間

図 17. ウォッチドッグ・タイマ動作に設定されたGPIOのタイミング

ウォッチドッグ・タイムアウトは、0~2.55sの範囲でプログラミングできます(10ms間隔)。WDTがタイムアウトすると、UCD90120は、(システム・リセット・ピンとして定義されたGPIOとは別の)WDOとして設定されたGPIOピンをアサートするか、またはシステム・リセット・パルスを生成できます。タイムアウト後、WDIピンの状態を切り替えるか、またはI<sup>2</sup>C経由でSYSTEM\_WATCHDOG\_RESETに書き込むことにより、WDTが再起動されます。

## フラッシュ·メモリへのデータおよびエラー の記録

UCD90120は、障害の発生、およびデバイス・リセットの回数をフラッシュ・メモリに記録できます。ピーク電圧、電流、および温度の測定値も、電源毎に保存されます。フラッシュ・メモリへのストレスを軽減するため、測定値が前回記録した値を超える場合には30秒タイマが開始されます。30秒の時間内で最も大きな値だけが、RAMからフラッシュへと書き込まれます。

複数の障害をフラッシュ・メモリに保存でき、PMBus経由で アクセスすることで、電源のバグや障害のデバッグに役立ちま す。各障害について、次の情報が記録されます。

- 電源番号

- 障害の種類

- 前回のデバイス・リセット以降の障害発生回数

- 最後に測定された電源電圧

デバイス・リセットの合計回数もフラッシュ・メモリに格納されます。この値はPMBusを使用してリセットできます。

ブラウンアウト機能がイネーブルの場合、ランタイム・クロック値、ピーク監視値、および障害は、パワーダウンが検出されたときのみフラッシュに記録されます。ブラウンアウト機能がディスエーブルでない限り、リセットまたはパワー・サイクル間でデバイスのランタイム・クロック値が格納されます。ブラウンアウト機能がディスエーブルの場合、ランタイム・クロック値は各リセット後にゼロに戻ります。

また、PMBusホストを介してUCD90120の内部ランタイム・クロックを更新および校正することも可能です。例えば、リアルタイム・クロックを備えたホスト・プロセッサは、UCD90120のランタイム・クロックを、実際の日時に対応した値へと定期的に更新することができます。ホストは、選択した使用シナリオに基づいて、UCD90120のタイマ値を適切な単位に変換し直す必要があります。詳細については、『UCD9012x PMBus Command Reference』のREAL\_TIME\_CLOCKコマンドを参照してください。

#### ブラウンアウト機能

UCD90120は、ブラウンアウト・イベントが検出されるまでの間、すべての不揮発性記録をオフにするよう設定できます。ブラウンアウト・イベントは、Vccが2.9Vを下回った場合に発生します。この機能をイネーブルにするには、デバイスに最低2.6Vを保持しながら5msにわたって80mAを供給できるだけの十分なローカル容量を用意する必要があります。

この機能がイネーブルの場合、UCD90120は、デバイスの通常動作中に、障害、ピーク、およびその他のログ・データをSRAMに保存します。ブラウンアウト・イベントが検出されると、すべてのデータがSRAMからフラッシュにコピーされます。この機能を使用することで、UCD90120は、デバイスのリセットまたはシステム・パワー・ダウンにわたり、継続したランタイム・クロックを保持できます(デバイスのリセット後にランタイム・クロックをリセットするのではなく)。また、通常のシステム動作中はフラッシュ書き込みが行われないため、イベントに対するUCD9012の内部応答時間も向上します。これは、オプションの機能であり、MISC\_CONFIGコマンドを使用してイネーブルにできます。詳細については、『UCD9012x PMBus Command Reference』を参照してください。

#### **PMBusインターフェイス**

PMBusは、電源管理の支援を目的として設計されたシリアル・インターフェイスです。これは、I<sup>2</sup>Cの物理仕様上に構築されたSMBusインターフェイスに基づいています。UCD90120は、PMBus標準のリビジョン1.1をサポートします。可能な限り、標準のPMBusコマンドを使用してデバイスの機能を支援できます。標準のPMBusコマンドは、『PMBus\_Specification\_Part\_I\_Rev\_1\_0\_20050324』および『PMBus\_Specification\_Part\_II\_Rev\_1-1\_20070205』に記載されています。これらはhttp://pmbus.org/specs.htmlからダウンロードできます。本データシートの動作および機能に関する説明の一部は、PMBus仕様に基づいたものです。UCD90120独自の機能については、これらの機能を設定またはアクティブ化するためのMFR\_SPE-CIFICコマンドが定義されています。これらのコマンドは、『UCD90120 PMBus Command Reference』に定義されています。

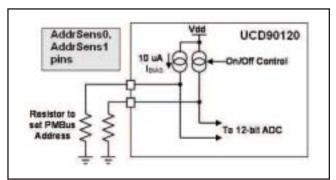

UCD90120は、PMBus仕様の"Compliance"セクションに従って、PMBusに準拠しています。また、ファームウェアはSMBus 1.1仕様に準拠しており、SMBus ALERT (SMBALERT#) 機能のサポートも含まれています。ハードウェアは100kHzおよび400kHzでの動作をサポートします。PMBusアドレスのデコードのために2本のピンが割り当てられています。パワーアップ時に、デバイスは各アドレス検出ピンにバイアス電流を印加し、それらのピンの電圧は内部の12ビットADCでキャプチャされます。PMBusアドレスは次の式で計算されます。

#### PMBus $\mathcal{T} F \mathcal{V} \mathcal{A} = 12 \times bin(V_{AD01}) + bin(V_{AD00})$

ここで、 $bin(V_{AD0x})$ は、表5に示すように、8つのアドレスのうちの1つに対するアドレス・ビンです。アドレス・ビンは、最小および最大電圧範囲 (V) によって定義されます。各ビンは、前のビンからの比が1.25と一定になっています。この方法により、標準1%抵抗の公差を基準として各ビンの幅が一定に維持されます。

一方のアドレス・ピンが低インピーダンス (短絡) で、最小電圧より低い電圧が生成されると、PMBusアドレスはデフォルトのアドレス126 (0x7F) になります。一方のアドレス・ピンが高インピーダンス (オープン) で、最大電圧より高い電圧が生成された場合も、PMBusアドレスはデフォルトのアドレス126 (0x7F) になります。

アドレス0は、PMBusのジェネラル・コール・アドレスであるため、使用されません。アドレス11および127は、製造時のプログラミングおよびテスト用に予約されているため、このデバイス、およびPMBusを共用している他のデバイスでは使用できません。アドレス126は、アドレス・ラインがグランドに短絡するかオープンにされた場合にUCD90120がデフォルトで使用するアドレスであるため、PMBus上のデバイスには使用しないことを推奨します。他のSMBus/PMBusアドレスは、特定のデバイスに対して割り当てられています。他の種類のデバイスが同じPMBusに接続されているシステムについては、最新版のSystem Management Bus (SMBus) 仕様の付録CにあるSMBusデバイス・アドレス割り当て表を参照してください。SMBus世様は、http://smbus.org/specs/smbus20.pdfでダウンロードできます。

**図 18**. PMBusアドレスの検出方法

| アドレス・ビン |       | MBus<br>正範囲(V) | RPMBus<br>PMBus抵抗(kΩ) |

|---------|-------|----------------|-----------------------|

|         | MIN   | MAX            | FINIDUSE(I) (K12)     |

| オープン    | 2.226 | 3.300          |                       |

| 11      | 1.746 | 2.225          | 210                   |

| 10      | 1.342 | 1.746          | 158                   |

| 9       | 1.030 | 1.341          | 115                   |

| 8       | 0.792 | 1.030          | 84.5                  |

| 7       | 0.609 | 0.792          | 63.4                  |

| 6       | 0.468 | 0.608          | 47.5                  |

| 5       | 0.359 | 0.467          | 36.5                  |

| 4       | 0.276 | 0.358          | 27.4                  |

| 短絡      | 0     | 0.097          |                       |

表 5. PMBusアドレス・ビン

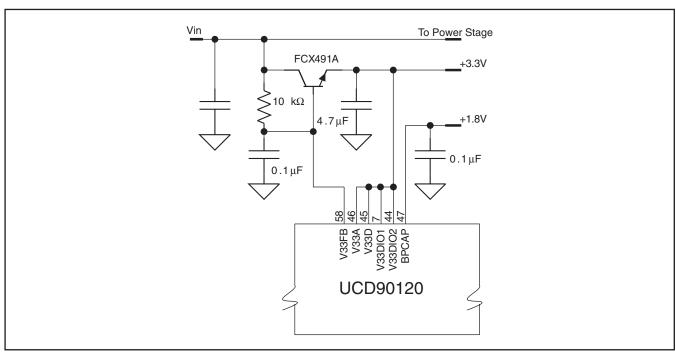

#### 高電源電圧用レギュレータ

UCD90120の動作には、3.3Vを必要とします。これは各種の  $V_{33x}$ ピンから直接供給するか、または内蔵のシリーズ・レギュレータと外部トランジスタを使用して、より高い電圧から生成することもできます。外部トランジスタには、電流増幅率 $\beta$ が40以上で、高電源電圧に適した $V_{CE}$ 定格を持つNPN製品を使用する必要があります。図19に、外部直列パス・トランジスタを使用した標準的な回路を示します。NPNのエミッタ出力が、チップに対する3.3V電源となります。シリーズ・レギュレータの安定化のために、 $4.7\mu$ Fのバイパス・コンデンサが必要です。

本製品内の一部の回路は1.8Vを必要としますが、これは3.3V電源から内部で生成されます。この電圧に対しては、BPCAPとグランドの間に $0.1\mu$ F $\sim 1\mu$ Fのバイパス・コンデンサが必要となります。

#### デバイスのリセット

UCD90120には、電源電圧を監視するパワーオン・リセット (POR) 回路が内蔵されています。パワーアップ時に、PORは  $V_{33D}$ の立ち上がりを検出します。 $V_{33D}$ が $V_{RESET}$ を上回ると、デバイスがリセットから解除されます。

nRESETピンに接続された外部回路によって、デバイスを強制的にリセット状態にすることができます。このピンを時間  $t_{RESET}$ より長く "Low" にすると、デバイスはリセット状態になります。nRESETを解除して "High" レベルに戻すと、デバ

イスは1ms以内にリセットから解除されます。ノイズによる誤トリガを防ぐため、3.3Vへのプルアップ抵抗を接続することを推奨します。

デバイスがリセットから解除されると、初期化ルーチンが開始され、実行に約20msかかります。初期化ルーチンの実行中、FPWMピンは"Low"に保持され、他のすべてのGPIOおよびGPIピンはオープンとなります。初期化が完了すると、デバイス設定での定義に従って通常動作が開始されます。

### デバイス設定のプログラミング

工場出荷時から、デバイスにはシーケンシングと監視用のファームウェアが搭載されています。出荷時点では、すべてのGPOがハイ・インピーダンスで、シーケンシングも障害対応も行わないように設定されています。UCD90120の設定の完全な詳細については、www.ti.comで "Configuration Programming of UCD Devices"を参照してください。

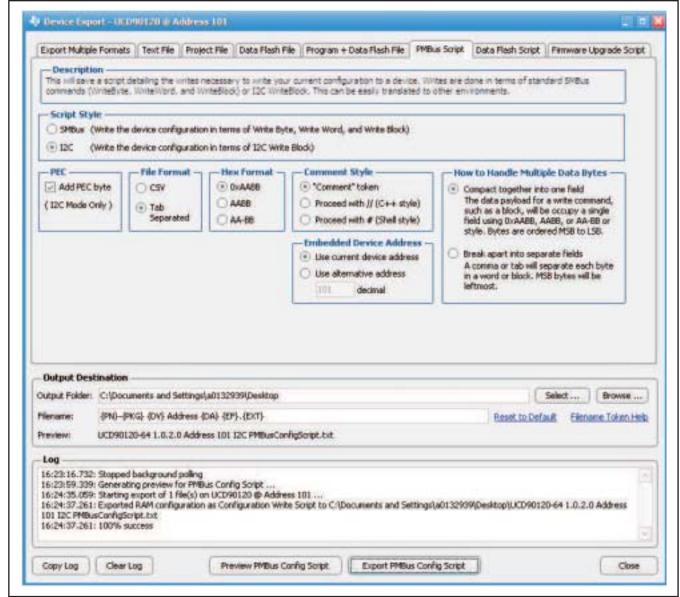

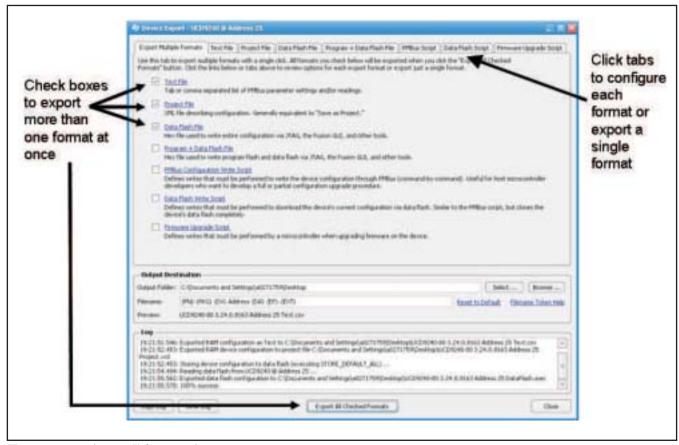

ユーザがFusionを使って設定ファイルを設計した後は、3つの一般的なデバイス設定プログラミング・オプションを使用できます。 $I^2$ C経由でデバイス設定用のPMBusコマンドを使用することにより、ホスト・マイクロコントローラからデバイスをインサーキットでプログラミングできます(『UCD90120 PMBus Command Reference』を参照)。

図 19. 高電圧電源と外部トランジスタ

図 20. FusionのPMBus設定スクリプト・エクスポート・ツール

各パラメータの書き込みにより、関連付けられた場所のメモリ (RAM) のデータが置き換えられます。必要なすべての設定データがデバイスに送信された後、特別なコマンド STORE\_DEFAULT\_ALLを実行することで、データが関連する不揮発性メモリ (データ・フラッシュ) に転送されます。 Fusion GUIによるデバイス設定の読み取りおよび書き込みは、通常このようにして行われます。

FusionではPMBusまたはI2Cのコマンド·スクリプト·ファイルを作成でき、I2Cマスタはそれを使用してデバイスを設定できます(図21)。コマンド·スクリプト·ファイルの一例を次に示します。

Comment Format=Tab; Hex=CoderUpper; BreakOutBytes=False [DO NOT REMOVE THIS LINE IF YOU WANT TO IMPORT USING THE FUSION GUI]

Comment SMBus Fields are Request, Address, Command, Data

Comment For reads, the last field is what is expected back from the device

Comment Write MONITOR\_CONFIG [MFR 05] Pin 1 MON1: Rail #1, Type Voltage; Pin 2 MON2: Rail #2, Type

Voltage; Pin 3 MON3: Rail #3, Type Voltage; Pin 4 MON4: Rail #4, Type Voltage; Pin 5 MON5: Rail #5,

Type Voltage; Pin 6 MON6: Rail #6, Type Voltage; Pin 59 MON7: Rail #7, Type Voltage; Pin 62 MON8: Rail

#8, Type Voltage; Pin 63 MON9: Rail #9, Type Voltage; Pin 50 MON10: Rail #10, Type Voltage; Pin 52

MON11: Rail #11, Type Voltage; Pin 54 MON12: Rail #12, Type Voltage; Pin 56 MON13: Rail #1, Type

Temperature

```

BlockWrite

0x65

0xD5

0x202122232425262728292A2B40

Comment

Write GPI_CONFIG [MFR 41] Inputs: <None>

BlockWrite

0x65

0xF9

Write SEQ_CONFIG [MFR 38, Rail #1] Rail Dep: <None> | Pin Dep: <None> | Fault Dep: <None> |

Comment

Enable: Pin 11 GPIO1 ActiveHigh ActivelyDrivenOutput

WriteBvte

0 \times 65

0 \times 00

0 \times 0.0

BlockWrite

0x000000000096

0x65

0xF6

Comment

Write SEQ_CONFIG [MFR 38, Rail #4] Rail Dep: <None> | Pin Dep: <None> | Fault Dep: <None> |

Enable: Pin 14 GPIO4 ActiveHigh ActivelyDrivenOutput

WriteBvte

0x65

0x00

0x03

0x65

0xF6

0x0000000000AE

BlockWrite

Write VOUT SCALE MONITOR [Rail #12] 0.500

Comment

WriteWord

0x65

0x2A

0x00B2

Store configuration to data flash

Comment

Pause

100

Pausing 100 ms

Comment

Execute STORE_DEFAULT_ALL

0x11

SendByte

0x65

Pause

1000

Pausing 1,000 ms for StoreDefaultAll

```

Fusionでは、他のインサーキット・プログラミング・オプションとして、設定ファイルからデータ・フラッシュ・イメージを作成することもできます(図21)。このイメージ・ファイルは、 $I^2$ CまたはJTAGを使用してデバイスにダウンロードできます。Fusionがターゲット・ボードのI2Cバスを占有できる場合は、オンボードでFusionツールを使用できます。

TIのFusionツールまたは専用のデバイス・プログラマを使用すれば、デバイスをオフボードでプログラミングできます。小規模な実行に対しては、 $I^2$ Cへッダーを持つZIFソケット・ボードを、標準のFusion GUIまたはManufacturing GUIとともに使用できます。また、Fusionでデータ・フラッシュ・ファイルを作成し、専用デバイス・プログラマを使用してUCD90120にロードすることもできます。

$I^2$ CまたはPMBus経由でデバイスの設定を行うには、UCD90120 に電源が供給されている必要があります。また、PMBusのクロックおよびデータ・ピンがアクセス可能になっていて、デバイスに電源を供給しているのと同じ $V_{dd}$ 電源に $I_k\Omega \sim 2k\Omega$ のプルアップ抵抗でプルアップされている必要があります。追加のバス容量が付加されないように注意してください(< 100pF)。デバイスを回路に実装する前に、ギャング・プログラマを使用し、JTAGまたは $I^2$ C経由でユーザ設定をデータ・フラッシュに書き込むことができます。 $I^2$ Cを使用するには、クロックおよびデータ・ラインを多重化するか、またはソケット毎にデバイス・アドレスを割り当てる必要があります。ソケットのアドレス指定にはFusionツールを使用できます。また、 $I_0$ C開用のデバイス・テスト冶具を使用してプリプログラミングを行うこともできます。

図 21. Fusionのデバイス設定エクスポート・ツール

|               | データ・フラッシュ、JTAG経由 | データ・フラッシュ、I <sup>2</sup> C経由               | PMBusコマンド、I <sup>2</sup> C経由               |  |  |

|---------------|------------------|--------------------------------------------|--------------------------------------------|--|--|

|               | データ・フラッシュ・エクスポート | データ・フラッシュ・エクスポート                           | プロジェクト・ファイル、I2C/PMBusスクリプト                 |  |  |

| オフボード設定       | 専用プログラマ          | Fusionツール、専用プログラマ、<br>マイクロコントローラ           | Fusionツール、<br>マイクロコントローラ                   |  |  |

| 1 > 1° 10=0.÷ | データ・フラッシュ・エクスポート |                                            | マイクロコントローラ、                                |  |  |

| オンボード設定       | IC               | Fusionツール(USB I2Cアダプタ経<br>由の排他的バス・アクセスによる) | Fusionツール(USB I2Cアダプタ経<br>由の排他的バス・アクセスによる) |  |  |

表 6. 設定オプション

オフボード設定には、次のような利点があります。

- デバイスのI<sup>2</sup>Cバスへのオンボード·アクセスが不要

- ボードへの半田付け後、追加設定なしでボードの全電源を 使用可能

- デバイスの実装後、部分的な再設定が可能

#### JTAGインターフェイス

実稼働用のプログラミングにはJTAGポートを使用できます。 6本のJTAGピンのうち4本は、通常動作中にGPIOとしても使用 できます。JTAG信号の一覧およびGPIOとして使用できるピン については、このドキュメント冒頭の「ピン機能」の表、およ び表2を参照してください。JTAGポートは、IEEE Standard 1149.1-1990, IEEE Standard Test-Access Port and Boundary Scan ダリ・スキャンはサポートされていません。

JTAGインターフェイスは、デバイスをプログラミングするための代替インターフェイスを提供します。デフォルトでは、多重化されたGPIOピンをイネーブルにするため、JTAGインターフェイスはディスエーブルになっています。JTAGインターフェイスがイネーブルになるには、3つの条件があります。

- 1. ROM MODE PMBusコマンドが発行されたとき

- 2. データ・フラッシュが空の状態でのパワーアップ時。この 場合、JTAGを使用することにより、PMBusの操作なしで 設定パラメータをデバイスに書き込むことができます。

- 3. パワーアップ時に無効なアドレスが検出されたとき。いずれかのアドレス・ピンをグランドに短絡することで、無効なアドレスを生成してJTAGをイネーブルにすることができます。

ドを待ちますが、ファームウェアを実行しません。パワーアップ時には、デバイス設定のチェックサム検証も行われます。一致しない場合は、出荷時のデフォルト設定がロードされます。PMBALERT#ピンがアサートされ、ステータス・レジスタのフラグがセットされます。エラー・ログのチェックサムは、エラー・ログの内容を検証して、フラッシュの一部が破損していないことを確認します。

内部にはファームウェア・ウォッチドッグ・タイマがありま

UCD90120は、パワーアップのたびにファームウェアのチェッ

クサムを検証します。一致しない場合、デバイスはI2Cコマン

内部にはファームウェア・ウォッチドッグ・タイマがあります。ウォッチドッグ・タイマがタイムアウトすると、デバイスはリセットされます。それにより、ファームウェア・プログラムが破損した場合に、デバイスが既知の状態に復帰できます。これは通常のデバイス・リセットであるため、デバイスのリセット中、すべてのGPIOピンはオープン・ドレインになり、FPWMピンは"Low"になります。また、渡される各パラメータについても、値が許容範囲内であることを確認するチェックが行われます。

データの整合性を向上させ、データ・フラッシュの記憶内容の信頼性を高めるために、エラー修正コード(ECC)が使用されています。ECCでは、専用ハードウェアを使用して、ユーザ・データがフラッシュ・メモリに書き込まれるときに、追加のチェック・ビットを生成します。これにより、フラッシュ・アレイに格納される各32ビット・メモリ・ワードに6ビットが追加されます。これらの追加のチェック・ビットに対して、ハードウェアECCアルゴリズムを使用することで、データ・フラッシュの読み取り時に1ビットのエラーを検出して修正することができます。

#### 内部障害管理とメモリ·エラー修正(ECC)

### アプリケーション情報

図 22. 標準的なアプリケーション回路図

#### レイアウトのガイドライン

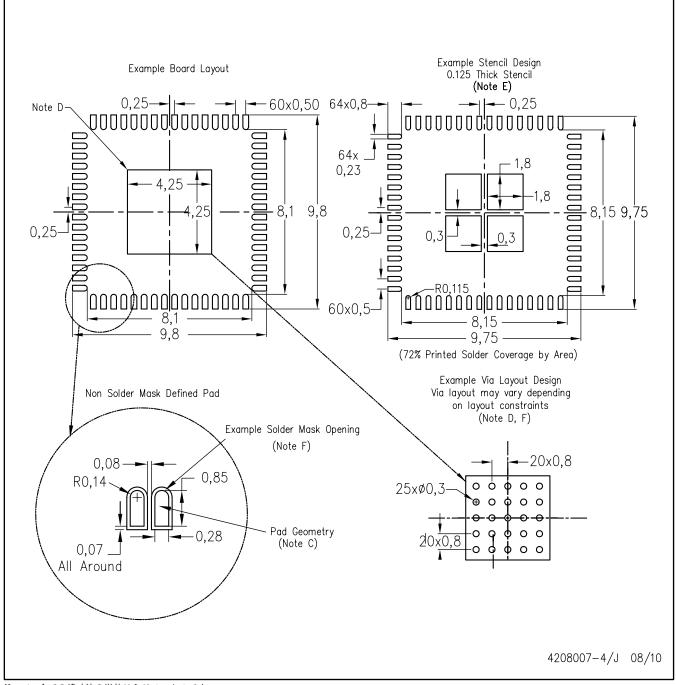

サーマル·パッドは、デバイスとプリント基板 (PCB) の間の 熱的および機械的インターフェイスとなります。デバイスの消 費電力は主要な問題ではありませんが、熱インターフェイスが 堅牢であるほど、内部温度センサがPCBの温度を忠実に示すよ うになります。PCB上の露出したサーマル・パッドをデバイス のVSSピンに接続するとともに、4×4以上のパターンのPCBビ アを用意して、サーマル・パッドとVSSピンをPCBの他の層上 の回路グランドに接続します。

電源電圧のデカップリングのために、次のような電源ピン・ バイパスをデバイスに提供します。

- ピン47 (BPCAP) に、0.1μFのX7Rセラミックと0.01μFの X7Rセラミックを並列接続

- ピン44 (V<sub>33D</sub>) に、0.1μFのX7Rセラミックと4.7μFのX5Rセ ラミックを並列接続

- ピン7 (V<sub>33DIO</sub>) に0.1μFのX7Rセラミックを接続

- ピン46 (V<sub>33A</sub>) に、0.1μFのX7Rセラミックと4.7μFのX5Rセ ラミックを並列接続

デジタル出力として使用される各種GPIO信号の使用法に応 じて、高速の信号エッジを緩和するためのインピーダンス制御 が必要になる場合があります。例えば、FPWMピンをファン制 御または電圧マージニングに使用する場合、このピンはデジタ ル "クロック" 信号として設定されます。これらの信号は、敏 感なアナログ信号から遠ざけて配線します。また、高速なデジ タル・エッジを緩和するために、信号源に20~33Ωの直列イン ピーダンスを追加するのも良い設計手法です。

#### ADCレポート精度の見積もり

UCD90120は、12ビットADCと内部の2.5Vリファレンス  $(V_{REF})$  を使用して、MONピン入力をデジタル・レポート電圧に変換します。最下位ビット (LSB) の値は $V_{LSB}$  =  $V_{REF}/2^N$ であり、N=12で $V_{LSB}=610$  $\mu$ Vとなります。レポートされる電圧の誤差は、ADCの直線性誤差および $V_{REF}$ の変動の関数となります。UCD90120のADCの合計未調整誤差 (ETUE) は $\pm 5LSB$ であり、 $V_{REF}$ の変動は $0^{\circ}$ C  $\sim$   $125^{\circ}$ C  $\sim$   $\pm 0.5\%$ 、 $-40^{\circ}$ C  $\sim$   $125^{\circ}$ C  $\sim$   $\pm 1\%$  です。 $V_{TUE}$ は $V_{LSB}$  ×  $E_{TUE}$ として計算されます。レポート電圧の合計誤差は、リファレンス電圧誤差と $V_{TUE}$ の和になります。監視電圧が低い場合、レポート誤差では $V_{TUE}$ の和になります。り、監視電圧が高い場合は、 $V_{REF}$ 変動の割合が高くなり、ここで、 $V_{REF}$ できます。ここで、 $V_{REF}$ の公差、 $V_{ACT}$ は $V_{CEF}$ 0 公差、 $V_{ACT}$ は $V_{CEF}$ 0  $V_{CEF}$ 0

$$RPT_{ERR} = \left(\frac{1 + REFTOL}{V_{ACT}}\right) \times \left(\frac{V_{REF} \times E_{TUE}}{4096} + V_{ACT}\right) - 1 \tag{1}$$

式 (1) から、温度が0°C~125°Cの場合、 $V_{ACT}$  = 0.5Vであれば RPT $_{ERR}$  = 1.11%となります。 $V_{ACT}$  = 2.2Vの場合は、RPT $_{ERR}$  = 0.64%です。-40°C~+125°Cの動作温度範囲全体では、 $V_{ACT}$  = 0.5Vの場合、RPT $_{ERR}$  = 1.62%です。 $V_{ACT}$  = 2.2Vの場合は、RPT $_{ERR}$  = 1.14%です。

## パッケージ情報

#### 製品情報

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp (3)   |

|------------------|-----------------------|-----------------|--------------------|------|----------------|-------------------------|------------------|---------------------|

| UCD90120RGCR     | ACTIVE                | VQFN            | RGC                | 64   | 2000           | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR |

| UCD90120RGCT     | ACTIVE                | VQFN            | RGC                | 64   | 250            | Green (RoHS & no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR |

(1) マーケティング・ステータスは次のように定義されています。

ACTIVE:製品デバイスが新規設計用に推奨されています。

LIFEBUY:TIによりデバイスの生産中止予定が発表され、ライフタイム購入期間が有効です。

NRND:新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TIでは新規設計にこの部品を使用することを推奨していません。

PREVIEW:デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

OBSOLETE: TIによりデバイスの生産が中止されました。

(2) エコ・プラン - 環境に配慮した製品分類プランであり、Pb-Free (RoHS)、Pb-Free (RoHS Expert) およびGreen (RoHS & no Sb/Br) があります。最新情報および製品内容の詳細については、http://www.ti.com/productcontentでご確認ください。

TBD: Pb-Free/Green変換プランが策定されていません。

Pb-Free (RoHS): TIにおける "Lead-Free" または "Pb-Free"(鉛フリー) は、6つの物質すべてに対して現在のRoHS要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が0.1%を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TIの鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

Pb-Free (RoHS Exempt): この部品は、1) ダイとパッケージの間に鉛ベースの半田バンプ使用、または 2) ダイとリードフレーム間に鉛ベースの接着剤を使用、が除外されています。それ以外は上記の様にPb-Free (RoHS) と考えられます。

**Green (RoHS & no Sb/Br):**TIにおける "Green" は、"Pb-Free"(RoHS互換) に加えて、臭素 (Br) およびアンチモン (Sb) をベースとした難燃材を含まない (均質 な材質中のBrまたはSb重量が0.1%を超えない) ことを意味しています。

(3) MSL、ピーク温度 -- JEDEC業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

重要な情報および免責事項:このページに記載された情報は、記載された日付時点でのTIの知識および見解を表しています。TIの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。TIでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TIおよびTI製品の供給者は、特定の情報を機密情報として扱っているため、CAS番号やその他の制限された情報が公開されない場合があります。

TIは、いかなる場合においても、かかる情報により発生した損害について、TIがお客様に1年間に販売した本書記載の問題となった TIパーツの購入価格の合計金額を超える責任は負いかねます。

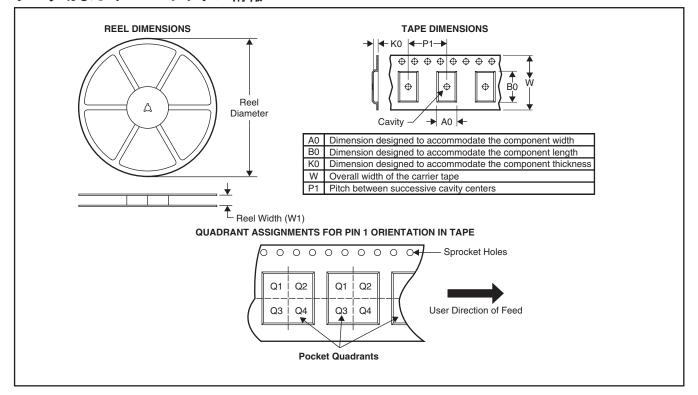

## パッケージ・マテリアル情報

## テープおよびリール・ボックス情報

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| UCD90120RGCR | VQFN            | RGC                | 64 | 2000 | 330.0                    | 16.4                     | 9.3        | 9.3        | 1.5        | 12.0       | 16.0      | Q2               |

| UCD90120RGCT | VQFN            | RGC                | 64 | 250  | 180.0                    | 16.4                     | 9.3        | 9.3        | 1.5        | 12.0       | 16.0      | Q2               |

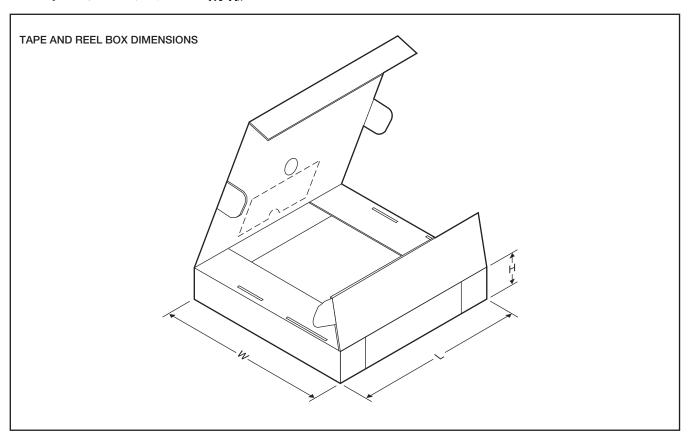

# パッケージ・マテリアル情報

#### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UCD90120RGCR | VQFN         | RGC             | 64   | 2000 | 346.0       | 346.0      | 33.0        |

| UCD90120RGCT | VQFN         | RGC             | 64   | 250  | 190.5       | 212.7      | 31.8        |

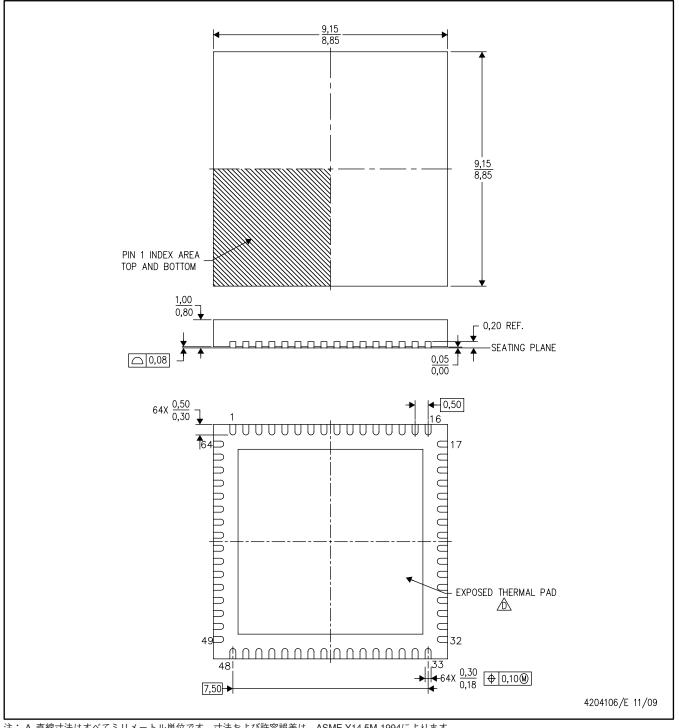

#### CUSTOM DEVICE PLASTIC QUAD FLATPACK NO-LEAD

- -注: A. 直線寸法はすべてミリメートル単位です。寸法および許容誤差は、ASME Y14.5M-1994によります。

- ・A. 直縁寸法はすべてミリメートル単位です。寸法および計容誤差は、ASME Y14.5M-1994によります。

B. 本図は予告なしに変更することがあります。

C. QFN(クゥアド・フラットパック・ノーリード)パッケージ構造。

↑ パッケージのサーマルパッドは、熱的および機構的特性を得るために基板に半田付けする必要があります。

露出サーマルパッドの寸法に関する詳細は、製品データシートをご覧ください。

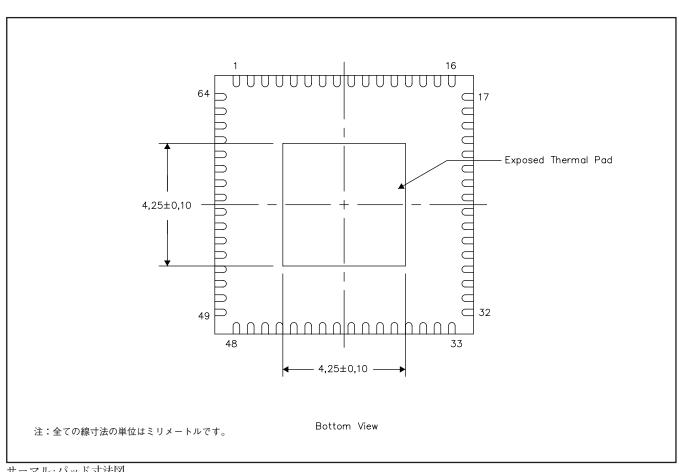

## サーマルパッド・メカニカル・データ

#### RGC (S-PVQFN-N64)

#### 熱特性について

このパッケージには、外部ヒートシンクに直接接続するよう に設計された、露出したサーマル・パッドが装備されています。 このサーマル・パッドは、プリント基板 (PCB) をヒートシンク として使用できるように、PCBに直接半田付けする必要があり ます。また、サーマル・ビアを使用して、サーマル・パッドをグ ランド・プレーンまたはPCB内に設計された特別なヒートシン ク構造に直接接続することができます。この設計により、ICか らの熱伝導が最適化されます。

QFN (Quad Flatpack No-Lead) パッケージとその利点につい ては、アプリケーション·レポート『Quad Flatpack No-Lead Logic Packages』 (Texas Instruments文献番号SLUA271) を参照 してください。このドキュメントは、ホームページwww.ti.com で入手できます。

このパッケージの露出したサーマル・パッドの寸法を次の図 に示します。

サーマル・パッド 寸法図

#### PLASTIC QUAD FLATPACK NO-LEAD

- A. 全ての線寸法の単位はミリメートルです。 B. 図は予告なく変更することがあります。

- C. 代替設計については、資料IPC-SM-782を推奨します。

- G. 代替設計については、資料IPC-SM-782を推奨します。

D. このパッケージは、基板上のサーマル・パッドに半田付けされるように設計されています。熱に関する具体的な情報、ビア要件、および推奨基板レイアウトについては、アプリケーション・ノート『Quad Flat-Pack Packages』(TI文献番号SLUA271) および製品データシートを参照してください。これらのドキュメントは、ホームページwww.ti.comで入手できます。

E. レーザ切断開口部の壁面を台形にし、角に丸みを付けることで、ペーストの離れがよくなります。ステンシル設計要件については、基板組み立て拠点にお問い合わせください。ステンシル設計上の考慮事項については、IPC 7525を参照してください。

F. 半田マスクの許容差については、基板組み立て拠点にお問い合わせください。

(SLVS966)

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定して収ない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2011, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

#### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。 1 熱霊気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置 類の接地等の静電気帯電防止措置は、常に管理されその機能が確認 されていること。

#### 2. 温·湿度環境

■ 温度:0~40℃、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

- 4. 機械的衝撃

- 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

- 5. 熱衝撃

- はんだ付け時は、最低限260℃以上の高温状態に、10秒以上さら さないこと。(個別推奨条件がある時はそれに従うこと。)

- 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上