UCC5880-Q1 JAJSPK1A - DECEMBER 2022 - REVISED FEBRUARY 2024

# UCC5880-Q1 車載アプリケーション用の高度な保護機能を搭載した絶縁型 20A 調整可能ゲート ドライブ IGBT/SiC MOSFET ゲート ドライバ

### 1 特長

- リアルタイムで駆動能力可変のデュアル出力ドライバ

- ±15A および ±5A の駆動電流出力

- SPI なしで駆動強度を調整するためのデジタル入 カピン (GD\*)

- 3 つの抵抗設定 R1、R2、または R1||R2

- 内蔵の 4A アクティブ ミラー クランプ、またはオプ ションで外部のミラー クランプ トランジスタを駆動

- 1 次側と2 次側のアクティブ短絡 (ASC) をサポート

- 内部および外部電源の低電圧および過電圧保護

- ドライバ ダイ温度センシングおよび過熱保護機能

- 短絡保護:

- DESAT イベントへの応答時間 110ns

- DESAT 保護 最大 14V まで選択可能

- シャント抵抗を使った短絡 (SC) および過電流 (OC) 保護

- 保護スレッショルドの値とブランキング時間を構成

- プログラマブル ソフト ターンオフ (STO) および 2 レベルのソフト ターンオフ (2STO) 電流

- 10 ビット ADC 内蔵

- パワー スイッチの温度、DC リンク電圧、ドライバの ダイ温度、DESATピン電圧、VCC2電圧を測定可

- プログラム可能なデジタルコンパレータ

- 高度な VCE/VDS クランプ回路

- 機能安全準拠

- 機能安全アプリケーション向けに開発

- ASIL D までの ISO 26262 システム設計を支援す るドキュメントを提供

- 診断機能内蔵:

- 保護コンパレータ用の内蔵セルフ テスト (BIST)

- パワー デバイスの状態監視用のゲートスレッショ ルド電圧測定

- INP からトランジスタのゲートへの経路の整合性

- 内部クロックの監視

- フォルトアラームおよび警告出力 (nFLT\*)

- ISO 通信データの整合性チェック

- SPI ベースのデバイス再構成、検証、監視、診断機能

- 150V/ns CMTI

- 以下の結果で AEC-Q100 認定済み:

- デバイス温度グレード 1:動作時周囲温度範 囲:-40°C~+125°C

- デバイス HBM ESD 分類レベル 2

- デバイス CDM ESD 分類レベル C2b

# 2 アプリケーション

- EV および HEV トラクション・インバータ

- EV および HEV 電源モジュール

### 3 概要

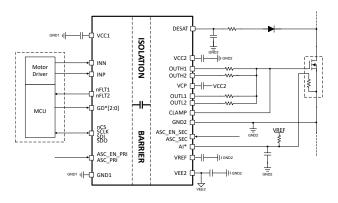

UCC5880-Q1 デバイスは、EV/HEV アプリケーションの 大電力 SiC MOSFET および IGBT を駆動するための高 度に構成可能で駆動能力可変の絶縁型ゲートドライバで す。シャント抵抗をベースにした過電流検出、過熱 (PTC、NTC またはダイオード) 検出、DESAT 検出などに よるパワートランジスタ保護機能を備えており、これらの障 害発生時にソフトターンオフまたは2レベルのソフトター ンオフを選択できます。 内蔵の 10 ビット ADC を使うと、 最 大2 つのアナログ入力 (VCC2、DESAT) とゲート ドライ バ温度を監視することでシステム管理を強化できます。 ASIL 準拠システムの設計を簡素化する診断および検出 機能を内蔵しています。これらの機能のパラメータとスレッ ショルドは SPI を使って設定できるため、本デバイスはほ とんどすべての SiC MOSFET または IGBT と組み合わ せて使用できます。

#### 製品情報

| 部品番号       | パッケージ <sup>(1)</sup> | パッケージ サ<br>イズ <sup>(2)</sup> | 本体サイズ (公称)        |  |  |

|------------|----------------------|------------------------------|-------------------|--|--|

| UCC5880-Q1 | DFC (SSOP, 32)       | 10.3mm ×<br>10.3mm           | 10.5mm x<br>7.5mm |  |  |

- 利用可能なすべてのパッケージについては、「メカニカル、パッケ -ジ、および注文情報」を参照してください。

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ (2) ンも含まれます。

概略回路図

# **Table of Contents**

| 1 特長1                             | 6.2 Layout Example | 7  |

|-----------------------------------|--------------------|----|

| 2 アプリケーション1                       |                    |    |

| 3 概要                              |                    | 10 |

| 4 Pin Configuration and Functions |                    | 10 |

| 5 Power Supply Recommendations6   |                    | 10 |

| 5.1 VCC16                         | 7.4 Trademarks     | 10 |

| 5.2 VCC26                         | 7.5 静電気放電に関する注意事項  | 10 |

| 5.3 VEE26                         | 7.6 用語集            | 10 |

| 6 Layout7                         |                    |    |

| 6.1 Layout Guidelines7            |                    |    |

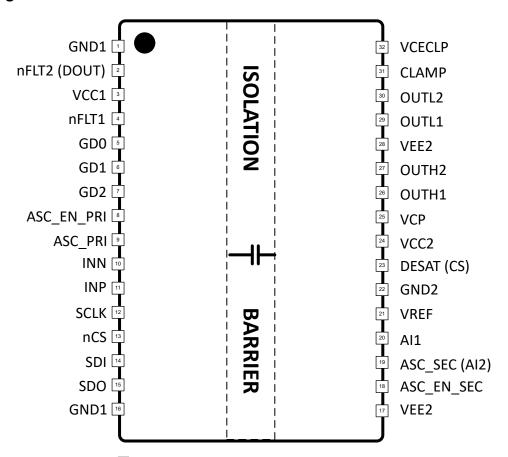

# **4 Pin Configuration and Functions**

図 4-1. 32-Pin DFC SSOP Package Top View

# 表 4-1. Pin Functions

| PIN          |        | (4)                | 致 4-1. First unctions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|--------------|--------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME         | NO.    | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| GND1         | 1, 16  | Р                  | Primary Side Ground. Connect all GND1 pins together and to the PCB ground plane on the primary side. Prioritize pin 1 for supply and input filter decoupling.                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| nFLT2 (DOUT) | 2      | 0                  | Fault Indicator Output 2. nFLT2 is used to interrupt the host when a fault occurs. Faults that are unmasked pull nFLT2 low when the fault occurs. nFLT2 is high when all faults are either non-existent or masked. It is recommended to add an external pull up resistor to VCC1 if faster rise time is needed. Additionally, nFLT2 may be configured as DOUT (push/pull) to provide the host controller a PWM signal with a duty cycle relative to the ADC input of interesting the signal with a duty cycle relative. |  |  |  |  |  |

| VCC1         | 3      | Р                  | Primary Side Power Supply. Connect a 3V to 5.5V power supply to VCC1. Bypass VCC1 to GND1 with ceramic bulk capacitance as close to the VCC1 pin as possible.                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| nFLT1        | 4      | 0                  | Fault Indicator Output 1. nFLT1 is used to interrupt the host when a fault occurs. Faults that are unmasked pull nFLT1 low when the fault occurs. nFLT1 is high when all faults are either non-existent or masked. It is recommended to add an external pull up resistor to VCC1 if faster rise time is needed.                                                                                                                                                                                                         |  |  |  |  |  |

| GD0          | 5      | ı                  | OUTL1/2 and OUTH1/2 Selector Inputs. GD* select combinations of OUT*1 and OUT*2 with                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| GD1          | 6      | I                  | user-selectable resistors. Drive all GD* high to force the gate of the power transistor low and reset all faults. See Adjustable Gate Drive Outputs (OUTL* OUTH*) for more details. Tie to                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| GD2          | 7      | ı                  | GND1 if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| ASC_EN_PRI   | 8      | ı                  | Primary-side Active Short Circuit Enable Input. ASC_EN_PRI enables the ASC function and forces the output to follow the ASC_PRI pin input state. When ASC_EN_PRI is low, the OUT* pins follow the INP and INN pin logical truth table. Tie to GND1 if not used.                                                                                                                                                                                                                                                         |  |  |  |  |  |

| ASC_PRI      | 9      | ı                  | Primary-side Active Short Circuit Polarity Input. The OUT* pins follow the logic level at ASC_PRI when the ASC_EN_PRI input is driven high. See the ASC section for more details. Tie to GND1 if not used.                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| INN          | 10     | ı                  | Negative PWM Input. INN is connected to the INP from the opposite arm of the half-bridge. If INP and INN overlap, the Shoot Through Protection (STP) engages and forces output low. Tie to GND1 if not used.                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| INP          | 11     | ı                  | Positive PWM Input. INP drives the state of the driver output. With the driver enabled, when INP is high, OUTH* is pulled high. When INP is low, OUTL* is pulled low. CMOS input logic level determined by the VCC1 voltage. INP is connected to the INN of the opposite arm of the half-bridge. If INP and INN overlap, STP engages and forces output low.                                                                                                                                                             |  |  |  |  |  |

| SCLK         | 12     | ı                  | SPI Clock. SCLK is the clock signal for the main SPI interface. The SPI interface operates with clock rates up to 4MHz.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| nCS          | 13     | ı                  | SPI Chip Selection Input. nCS is an active low input used to activate the SPI peripheral device. Drive nCS low during SPI communication. When nCS is high, SDO is set to disabled (high-impedance) and commands on SDI are ignored. Tie to VCC1 if not used.                                                                                                                                                                                                                                                            |  |  |  |  |  |

| SDI          | 14     | I                  | SPI Data Input. SDI is the data input for the main SPI interface. Data is sampled on the falling edge of CLK, SDI must be in a stable condition to ensure proper communication.                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| SDO          | 15     | 0                  | SPI Data Output. SDO is the data output for the main SPI interface. Data is clocked out on the falling edge of CLK, SDO is changed with a rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| VEE2         | 17, 28 | Р                  | Secondary Negative Power Supply. Connect all VEE2 supply inputs together. Connect a -12V to 0V power supply to VEE2. The total voltage rail from VCC2 to VEE2 must not exceed 30V. Bypass VEE2 to GND2 with at least 1uF of low-impedance ceramic capacitors as close to pin 28 as possible, to encourage gate current flow through pin 28.                                                                                                                                                                             |  |  |  |  |  |

| ASC_EN_SEC   | 18     | 1                  | Secondary-side Active Short Circuit Enable Input. ASC_EN_SEC enables the ASC function, overriding the INP command and forcing the output of the driver to the defined safe state, set by CONTROL2[ASC_LEV_SEL] register. When ASC_EN_SEC is low, the output is controlled by primary side pins. Tie to GND2 if not used.                                                                                                                                                                                                |  |  |  |  |  |

| ASC_SEC      | 19     | I                  | ASC_SEC (Al2) defaults to Active Short Circuit Polarity Input. When programmed as ASC_SEC, the OUT* pins follow the logic level at ASC_SEC when the ASC_EN_SEC input is driven high.                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Al2          |        | I                  | ASC_SEC (Al2) can be programmed as an ADC input that digitizes analog voltages up to 4.0V. Additionally, a programmable "digital comparator" is available to signal faults when the voltage is above/below (selectable) the programmed threshold. This is useful for monitoring the DC-LINK voltage or phase voltage during the switching cycle. Tie to GND2 if not used.                                                                                                                                               |  |  |  |  |  |

# 表 4-1. Pin Functions (続き)

| PIN(1) |     |                    | 表 4-1. Pin Functions (税さ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------|-----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Al1    | 20  | ı                  | Analog Input 1. Al1 is an ADC input that digitizes analog voltages up to 4.0V. Additionally, a programmable "digital comparator" is available to signal faults when the voltage is above/below (selectable) the programmed threshold. This is useful for monitoring the DC-LINK voltage or phase voltage during the switching cycle. Tie to GND2 if not used.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VREF   | 21  | Р                  | Internal ADC Voltage Regulator Output. VREF provides an external 5.0V reference voltage, which is internally scaled down to 4.0V for the ADC. Bypass VREF to GND2 with at least 1uF of ceramic capacitance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| GND2   | 22  | Р                  | Gate Drive Supply Reference. Connect GND2 to the power FET source/ IGBT emitter. ASC_EN_SEC, ASC_SEC (AI2), AI1, VREF, and DESAT are referenced to GND2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DESAT  | 23  | ı                  | Current Sense Input/ Desaturation based Short Circuit Detection Input. DESAT (CS) is configurable to sense over-current conditions in resistor sense applications, or DESAT over-current in VCE/VDS sensing applications. For DESAT applications, bypass DESAT to GND2 with a ceramic capacitor and, in parallel, connect a Schottky diode with the cathode connected to the DESAT pin, and the anode connected to GND2. See the applications section for details on calculating the component values. Additionally, connect the DESAT pin to a resistor to the anode of a diode to the collector of the power FET. The DESAT pin detects a fault when the VDS/VCE voltage of the power FET exceeds the SPI programmable threshold while the power FET is on. Tie to GND2 if not used. |

| CS     |     | ı                  | Current Sense Positive Input/ Desaturation based Short Circuit Detection Input. CS (DESAT) is configurable to sense over-current and short-circuit conditions in resistor sense applications, or DESAT over-current in VCE/VDS sensing applications. For sense resistor based applications, connect DESAT (CS) pin to the positive side of the sense element through an RC. The current limit threshold is programmable via SPI. Tie to GND2 if not used.                                                                                                                                                                                                                                                                                                                              |

| VCC2   | 24  | Р                  | Secondary Positive Power Supply. Connect a 15V to 30V power supply to VCC2. The total voltage rail from VCC2 to VEE2 must not exceed 30V. Bypass VCC2 to GND2 and VCC2 to VEE2 with bulk ceramic capacitance as close to the VCC2 pin as possible. Additional capacitance may be needed depending on the gate charge of the power device.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VCP    | 25  | Р                  | High-side Drive Supply. VCP supplies power for the OUTH* drive. Bypass VCP to VCC2 with a ceramic capacitor between 10nF and 100nF, as close to the VCP pin as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| OUTH1  | 26  | 0                  | Gate driver source pins (OUTH1 = 15A <sub>PK</sub> , OUTH2 = 5A <sub>PK</sub> ). When the driver is active and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OUTH2  | 27  | 0                  | commanded high, OUTH* pins are used to source current to the gate of the power FET to drive the output high. Connect OUTH* pins to the gate of the power FET through individual gate resistors. The value of the gate resistor is chosen based on the slew rate required for the application. Different slew rates are programmed by using different resistor values for OUTH1 and OUTH2. The two outputs are enabled "on the fly" using the GD* inputs to set 3 different slew rates (OUTH1 only, OUTH2 only, and OUTH1 + OUTH2).                                                                                                                                                                                                                                                     |

| OUTL1  | 29  | 0                  | Gate driver sink pins (OUTL1 = $15A_{PK}$ , OUTL2 = $5A_{PK}$ ). When the driver is active and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OUTL2  | 30  | 0                  | commanded low, OUTL* pins are used to sink current from the gate of the power FET to drive the gate low. Connect OUTL* pins to the gate of the power FET through individual gate resistors. The value of the gate resistor is chosen based on the slew rate required for the application. Different slew rates are programmed by using different resistor values for OUTL1 and OUTL2. The two outputs are enabled "on the fly" using the GD* inputs to set 3 different slew rates (OUTL1 only, OUTL2 only, and OUTL1 + OUTL2).                                                                                                                                                                                                                                                         |

| CLAMP  | 31  | 0                  | Miller Clamp pin. The CLAMP pin is used to hold the gate of the power FET strongly to VEE2 while the power FET is "off". CLAMP is configurable as an internal Miller clamp, or to drive an external clamping circuit. When using the internal clamping function, connect CLAMP directly the power FET gate. When configured as an external clamp, connect CLAMP to the gate of an external pulldown MOSFET. Disable and tie to VEE2 if not used.                                                                                                                                                                                                                                                                                                                                       |

| VCECLP | 32  | I                  | VCE Clamp Input. VCECLP clamps to a diode above the VCC2 rail and indicates a fault when the voltage at VCECLP is above the VCECLPth voltage. Bypass VCECLP to VEE2 with ceramic capacitor and, in parallel, connect a resistor. See the applications section for details on calculating the component values. Additionally, connect VCECLP to the anode of a zener diode to the collector/drain of the power FET. Tie to VEE2 if not used.                                                                                                                                                                                                                                                                                                                                            |

<sup>(1)</sup> I = Input, O = Output, I/O = Input or Output, G = Ground, P = Power.

# 5 Power Supply Recommendations

#### 5.1 VCC1

VCC1 supports an input range of 3V to 5.5V in order to support both 3.3V and 5V controller signaling. VCC1 is monitored with both an undervoltage and overvoltage comparator circuit to ensure valid operation. UV and OV conditions of VCC1 are recorded in FAULT2[UVLO1\_FAULT] and FAULT2[OVLO\_FAULT1], respectively.

#### 5.2 VCC2

VCC2 operates within an input range of 12V and 30V, allowing for use in IGBT and SiC applications. VCC2 is monitored with both an undervoltage and overvoltage comparator circuit to ensure valid operation. UV and OV conditions of VCC2 are recorded in FAULT2[UVLO2\_FAULT] and FAULT2[OVLO2\_FAULT], respectively.

### 5.3 VEE2

VEE2 operates with an input range of -12V to 0V, allowing a negative gate bias on the power FET during turn-off in both IGBT and SiC applications. This prevents the power FET from unintentionally turning on due to current inducted from the Miller effect. For operation with a unipolar supply, connect VEE2 to GND2. VEE2 is monitored with both an undervoltage and overvoltage comparator circuit to ensure valid operation. UV and OV conditions of VEE2 are recorded in FAULT2[UVLO3\_FAULT] and FAULT2[OVLO3\_FAULT], respectively.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2024 Texas Instruments Incorporated

# 6 Layout

# 6.1 Layout Guidelines

Layout best practices must be followed to achieve robust performance from UCC5880-Q1. Failure to follow best practices may lead to low noise immunity. Reach out to TI engineers for feedback during schematic phase, component placement phase, and trace/plane layout phase of board design.

### **6.1.1 Component Placement**

- Low-ESR and low-ESL capacitors must be connected close to the device between the VCC1 and GND1 pins and between the VCC2, VEE2 and GND2 pins to support high peak currents when turning the external power transistor on and off.

- Place the VCP and VREF caps as close to the device as possible.

# **6.1.2 Grounding Considerations**

- It is essential to confine the high peak currents that charge and discharge the transistor gates to a minimal physical area. This decreases the loop inductance and minimize noise on the gate terminals of the transistors. The gate driver must be placed as close as possible to the transistors.

- Ensure a small loop area/inductance between VCP and VCC2.

- Analog signals measured with the integrated ADC on Al1 and Al2 pins must be effectively isolated from high

gate switching currents in GND2 net. It is recommended to create Kelvin connections for these

measurements to reduce impact of ground bounce caused by high di/dt in the gate drive loop.

### 6.1.3 High-Voltage Considerations

- To ensure isolation performance between the primary and secondary side, one should avoid placing any PCB traces or copper below the driver device. A PCB cutout is recommended in order to prevent contamination that may compromise the UCC5880-Q1's isolation performance.

- For half-bridge, or high-side/low-side configurations, where the high-side and low-side drivers could operate with a DC-link voltage up to 1000 VDC, one should try to increase the creepage distance of the PCB layout between the high and low-side PCB traces.

- Conformal coating is commonly used in systems to limit pollution degree and enable shorter creepage/ clearance distances.

#### 6.1.4 Thermal Considerations

- The power dissipated in UCC5880-Q1 is directly proportional to the VCC1, VCC2, and VEE2 voltages, capacitive loading, and switching frequency. Proper PCB layout helps dissipate heat from the device to the PCB and minimize junction to board thermal impedance (θ<sub>JR</sub>).

- Increasing the PCB copper connecting to VCC2 and VEE2 planes is recommended, with priority on maximizing the connection to VEE2.

- If there are multiple layers in the system, it is also recommended to connect the VCC2 and VEE2 to their respective internal planes using multiple vias of adequate size. However, it is still critical to ensure that there are not any traces/planes from different high voltage planes overlapping.

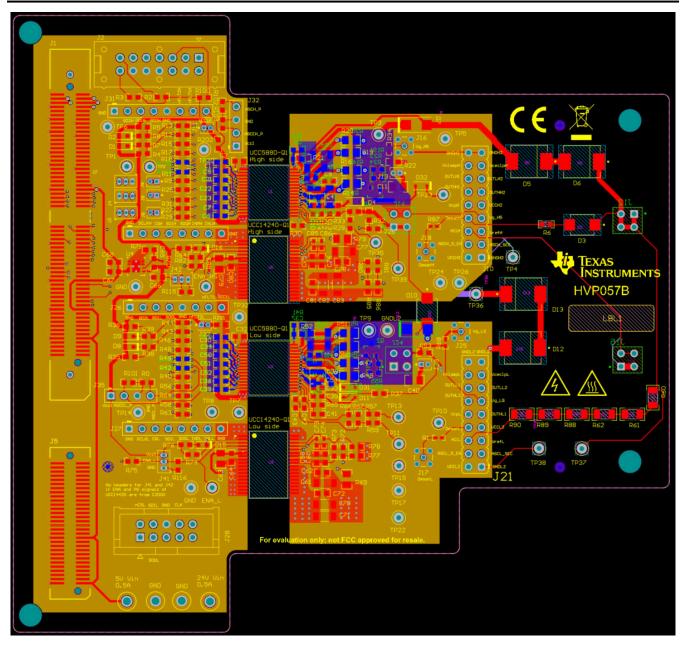

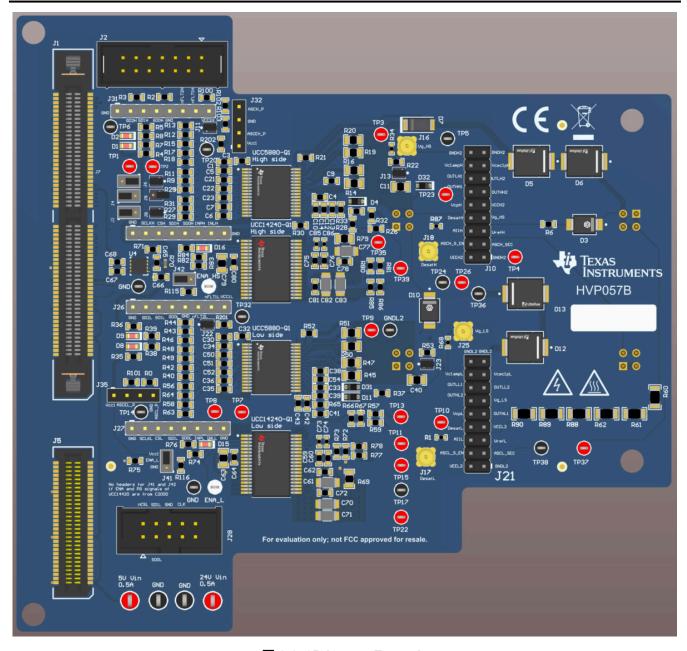

# **6.2 Layout Example**

Please refer to UCC5880EVM-057 Evaluation Module (EVM) design for layout example.

図 6-1. 2D Layout Example

図 6-2. 3D Layout Example

# 7 Device and Documentation Support

# 7.1 Device Support

### 7.1.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

# 7.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、www.tij.co.jp のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。 変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 7.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

#### 7.4 Trademarks

テキサス・インスツルメンツ E2E<sup>™</sup> is a trademark of Texas Instruments. すべての商標は、それぞれの所有者に帰属します。

# 7.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

#### 7.6 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

# **8 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Cł | nanges from Revision * (December 2022) to Revision A (February 2024) | Page |

|----|----------------------------------------------------------------------|------|

| •  | 「事前情報」から「量産データ」に変更                                                   | 1    |

# 9 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

11

# 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated www.ti.com 18-Jul-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|-----------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

| UCC5880QDFCRQ1        | Active | Production    | SSOP (DFC)   32 | 2000   LARGE T&R      | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 125   | UCC5880Q         |

| UCC5880QDFCRQ1.A      | Active | Production    | SSOP (DFC)   32 | 2000   LARGE T&R      | Yes             | NIPDAU                        | Level-3-260C-168 HR        | -40 to 125   | UCC5880Q         |

| UCC5880QDFCRQ1.B      | Active | Production    | SSOP (DFC)   32 | 2000   LARGE T&R      | -               | Call TI                       | Call TI                    | -40 to 125   |                  |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-May-2025

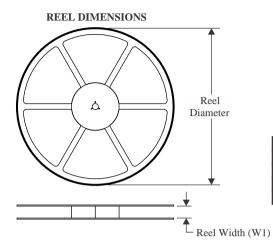

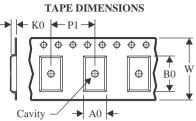

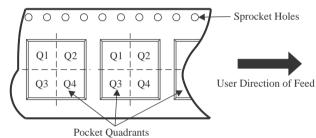

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

|   | Device         | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---|----------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| ١ | UCC5880QDFCRQ1 | SSOP            | DFC                | 32 | 2000 | 330.0                    | 16.4                     | 10.75      | 10.7       | 2.7        | 12.0       | 16.0      | Q1               |

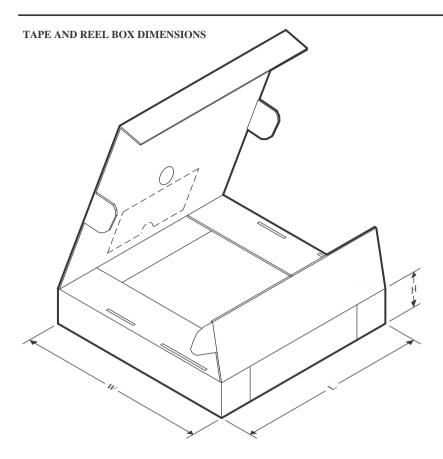

**PACKAGE MATERIALS INFORMATION**

www.ti.com 3-May-2025

### \*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UCC5880QDFCRQ1 | SSOP         | DFC             | 32   | 2000 | 350.0       | 350.0      | 43.0        |

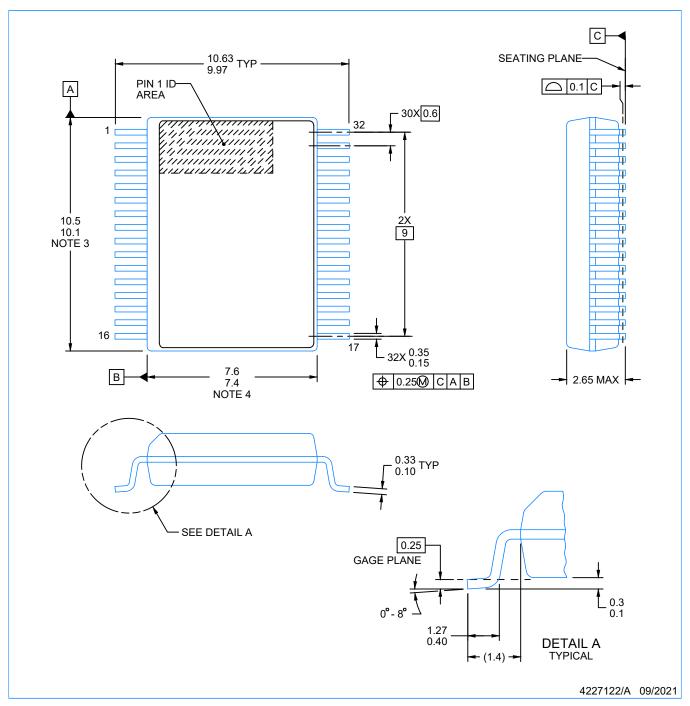

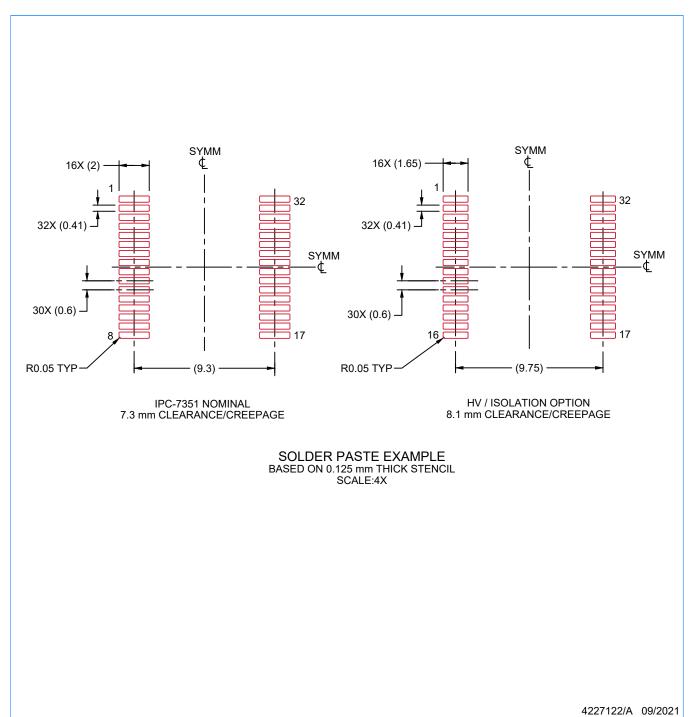

SMALL OUTLINE PACKAGE

### NOTES:

- 1. All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm, per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm, per side.

- 5. Reference JEDEC registration MS-013.

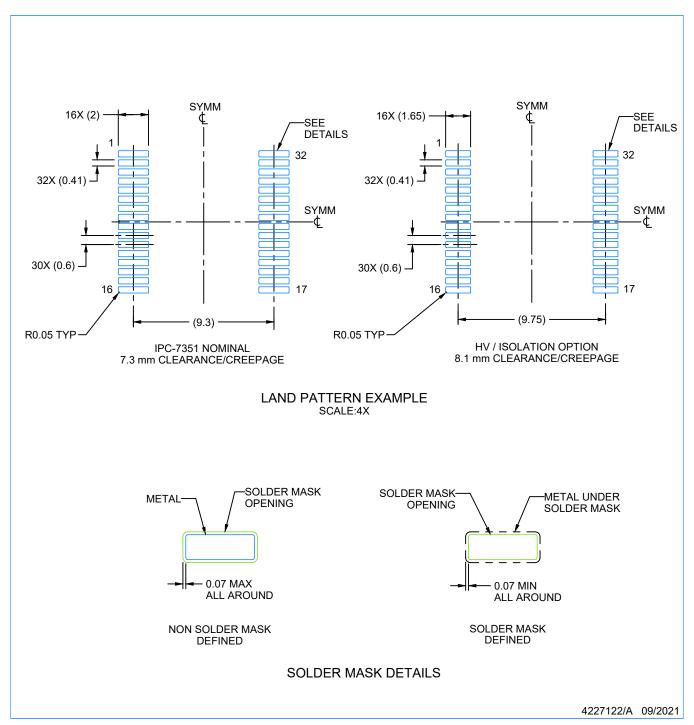

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SAMLL OUTLINE PACKAGE

### NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

# 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、 テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、 テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。 テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、 テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、 テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、 テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。 テキサス・インスツルメンツがこれらのリソ 一スを提供することは、適用される テキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありませ ん。

お客様がいかなる追加条項または代替条項を提案した場合でも、 テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated