# UCC5350L-Q1 SiC/IGBT および車載アプリケーション用 シングルチャネル絶縁型ゲートドライバ

## 1 特長

- $5\text{kV}_{\text{RMS}}$  のシングルチャネル絶縁型ゲートドライバ

- 車載アプリケーション向けに AEC-Q100 認証済み

- 温度グレード 1

- ミラークランプ、12V UVLO

- ピーク電流駆動力:  $\pm 10\text{A}$  (代表値)

- 入力電圧範囲:  $3\text{V} \sim 15\text{V}$

- 最大  $30\text{V}$  のドライバ電源電圧

- 最小 CMTI:  $100\text{V/ns}$

- 負の  $5\text{V}$  に対応可能な入力ピン

- 伝搬遅延時間:  $100\text{ns}$  以下、部品間スキー:  $25\text{ns}$  未満

- 8 ピン DWL (沿面距離  $15.7\text{mm}$ )

- 絶縁バリアの寿命: 40 年超

- 安全性関連認証取得予定:

- UL 1577 部品認定プログラム

- DIN EN IEC 60747-17 (VDE 0884-17)

- CQC - GB4943.1

- CMOS 入力

- 動作時接合部温度:  $-40^{\circ}\text{C} \sim +150^{\circ}\text{C}$

## 2 アプリケーション

- オンボードチャージャ

- EV 用トラクションインバータ

- DC 充電ステーション

- HVAC

- 暖房器具

## 3 説明

UCC5350L-Q1 はシングルチャネルの絶縁ゲートドライバで、10A ソースおよび 10A シンクの代表的なピーク電流を持ち、MOSFET、IGBT、SiC MOSFET を駆動するよう設計されています。UCC5350L-Q1 には、ミラークランプのオプションがあります。CLAMP ピンを使ってトランジスタのゲートを内部 FET と出力に接続することで、ミラー電流による誤ターンオンを防止できます。UCC5350L-Q1 は  $14\text{mm}$  ワイドボディ SOIC-8 (DWL) パッケージで供給され、最大  $5\text{kV}_{\text{RMS}}$  の絶縁電圧をサポートできます。入力側は、絶縁バリア寿命が 40 年以上ある  $\text{SiO}_2$  容量性絶縁技術によって出力側と絶縁されています。UCC5350L-Q1 は、高電圧トラクションインバータおよびオンボードチャージャなどの用途の IGBT または MOSFET の駆動に適しています。フォトカプラと比較して、このデバイスは部品間スキーが小さく、伝搬遅延時間が短く、より高い温度でも動作し、CMTI が高いという特長があります。

## 製品情報

| 部品のバージョン             | 特長                   | パッケージ (1)    | 本体サイズ (公称)                        |

|----------------------|----------------------|--------------|-----------------------------------|

| UCC5350MCQD<br>WL-Q1 | ミラークランプ、<br>12V UVLO | DWL (SOIC-8) | $14\text{mm} \times 6.4\text{mm}$ |

(1) 供給されているすべてのパッケージについては、[セクション 13](#) を参照してください。

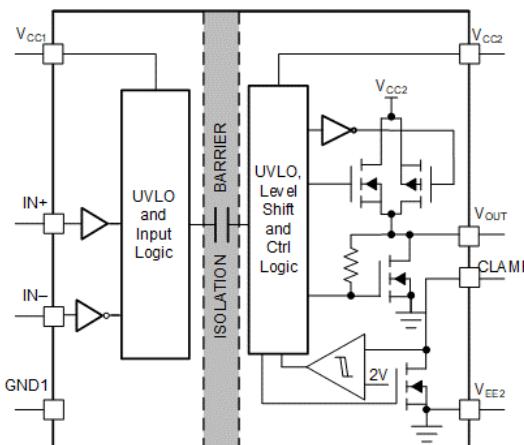

機能ブロック図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、[ti.com](http://ti.com) で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SLUSFL5](#)

## 目次

|                    |    |                         |    |

|--------------------|----|-------------------------|----|

| 1 特長               | 1  | 7.3 機能説明                | 16 |

| 2 アプリケーション         | 1  | 7.4 デバイスの機能モード          | 19 |

| 3 説明               | 1  | 8 アプリケーションと実装           | 20 |

| 4 ピン構成および機能        | 3  | 8.1 アプリケーション情報          | 20 |

| 5 仕様               | 4  | 8.2 代表的なアプリケーション        | 20 |

| 5.1 絶対最大定格         | 4  | 9 電源に関する推奨事項            | 25 |

| 5.2 ESD 定格 (車載用)   | 4  | 10 レイアウト                | 25 |

| 5.3 推奨動作条件         | 4  | 10.1 レイアウトのガイドライン       | 25 |

| 5.4 熱に関する情報        | 4  | 10.2 レイアウト例             | 25 |

| 5.5 電力定格           | 5  | 10.3 PCB 材料             | 26 |

| 5.6 絶縁仕様           | 5  | 11 デバイスおよびドキュメントのサポート   | 27 |

| 5.7 安全関連認証         | 6  | 11.1 デバイス サポート          | 27 |

| 5.8 安全限界値          | 6  | 11.2 ドキュメントのサポート        | 27 |

| 5.9 電気的特性          | 7  | 11.3 認証                 | 27 |

| 5.10 スイッチング特性      | 8  | 11.4 ドキュメントの更新通知を受け取る方法 | 27 |

| 5.11 絶縁特性曲線        | 9  | 11.5 サポート・リソース          | 27 |

| 5.12 代表的特性         | 10 | 11.6 商標                 | 27 |

| 6 パラメータ測定情報        | 13 | 11.7 静電気放電に関する注意事項      | 27 |

| 6.1 伝搬遅延、反転、非反転型構成 | 13 | 11.8 用語集                | 27 |

| 7 詳細説明             | 15 | 12 改訂履歴                 | 27 |

| 7.1 概要             | 15 | 13 メカニカル、パッケージ、および注文情報  | 28 |

| 7.2 機能ブロック図        | 15 |                         |    |

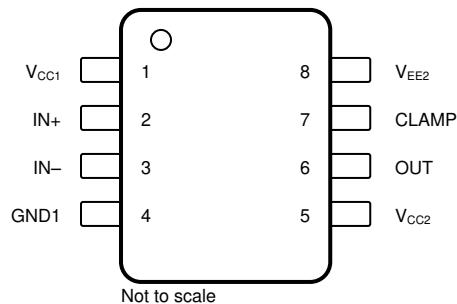

## 4 ピン構成および機能

図 4-1. UCC5350L-Q1 8 ピン SOIC 上面図

表 4-1. ピンの機能

| ピン               |             | 種類 <sup>(1)</sup> | 説明                                                                                                                                                 |

|------------------|-------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称               | UCC5350L-Q1 |                   |                                                                                                                                                    |

| V <sub>CC1</sub> | 1           | P                 | 入力電源電圧。局的にデカッピングされたコンデンサを GND1 に接続します。デバイスと可能な限り近くに配置した低 ESR または低 ESL のコンデンサを使用します。                                                                |

| V <sub>CC2</sub> | 5           | P                 | 正の出力電源レール。局的にデカッピングされたコンデンサを V <sub>EE2</sub> に接続します。デバイスと可能な限り近くに配置した低 ESR または低 ESL のコンデンサを使用します。                                                 |

| V <sub>EE2</sub> | 8           | G                 | グランド ピン。MOSFET ソースまたは IGBT エミッタに接続します。局的にデカッピングされたコンデンサを V <sub>CC2</sub> から V <sub>EE2</sub> に接続します。デバイスと可能な限り近くに配置した低 ESR または低 ESL のコンデンサを使用します。 |

| GND1             | 4           | G                 | 入力グランド。入力側のすべての信号はこのグランドを基準とします。                                                                                                                   |

| IN+              | 2           | I                 | 非反転ゲート駆動電圧制御入力。IN+ ピンには CMOS 入力スレッショルドがあります。このピンは、オープンのままにすると内部で Low にプルされます。表 7-4 を使用して、これらのデバイスの入出力ロジックを理解してください。                                |

| IN-              | 3           | I                 | 反転ゲート駆動電圧制御入力。IN- ピンには CMOS 入力スレッショルドがあります。このピンは、オープンのままにすると内部で High にプルされます。表 7-4 を使用して、これらのデバイスの入出力ロジックを理解してください。                                |

| OUT              | 6           | O                 | ゲート駆動出力                                                                                                                                            |

| CLAMP            | 7           | I                 | アクティブ ミラー クランプ入力を使用することで、パワー スイッチの誤ターンオンを防止します。                                                                                                    |

(1) P = 電源、G = グランド、I = 入力、O = 出力

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|              |                       | 最小値           | 最大値           | 単位 |

|--------------|-----------------------|---------------|---------------|----|

| 入力バイアスピン電源電圧 | $V_{CC1}$ - GND1      | GND1-0.3      | 18            | V  |

| ドライババイアス電源   | $V_{CC2}$ - $V_{EE2}$ | -0.3          | 35            | V  |

| 入力ピンの電圧      | IN+, IN-              | GND1-5        | $V_{CC1}+0.3$ | V  |

| 出力信号電圧       | OUT の電圧               | $V_{EE2}-0.3$ | $V_{CC2}+0.3$ | V  |

| クランプ電圧       | CLMPE の電圧、VEE 基準      | $V_{EE2}-0.3$ | $V_{CC2}+0.3$ | V  |

| $T_J$        | 接合部温度                 | -40           | 150           | °C |

| $T_{stg}$    | 保存温度                  | -65           | 150           | °C |

- (1) 「絶対最大定格」を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについての話で、絶対最大定格において、またはこのデータシートの「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

### 5.2 ESD 定格 (車載用)

|             |      | 値                                           | 単位         |

|-------------|------|---------------------------------------------|------------|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、AEC Q100-002 に準拠 <sup>(1)</sup> | $\pm 4000$ |

|             |      | 荷電デバイス モデル (CDM)、AEC Q100-011 準拠            | $\pm 1500$ |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                |                        | 最小値 | 最大値  | 単位 |

|----------------|------------------------|-----|------|----|

| $V_{CC1}$      | $V_{CC1}$ - GND1       |     | 3    | 15 |

| $V_{CC2}$      | $V_{CC2}$ - $V_{EE2}$  |     | 13.2 | 30 |

| $t_{PWM\_MIN}$ | 最小入力パルス幅 (IN+ および IN-) |     | 50   | ns |

| $T_J$          | 接合部温度                  | -40 | 150  | °C |

### 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>        |                     | <b>UCC5350L-Q1</b> | 単位   |

|-----------------------------|---------------------|--------------------|------|

|                             |                     | <b>DWL</b>         |      |

|                             |                     | <b>8 ピン</b>        |      |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗        | 87.1               | °C/W |

| $R_{\theta JC(\text{top})}$ | 接合部からケース (上面) への熱抵抗 | 47.4               | V    |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗        | 41.2               | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ    | 33.9               | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ    | 39.7               | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 5.5 電力定格

| パラメータ    |                | テスト条件                                                                   | 最小値 | 標準値 | 最大値  | 単位 |

|----------|----------------|-------------------------------------------------------------------------|-----|-----|------|----|

| $P_D$    | 入力および出力の最大消費電力 | $V_{CC1} = 15V, V_{CC2} = 15V, f = 1.9MHz, 50\% デューティサイクル、方形波、2.2nF 負荷$ |     |     | 1.04 | W  |

| $P_{D1}$ | 最大入力消費電力       | $V_{CC1} = 15V, V_{CC2} = 15V, f = 1.9MHz, 50\% デューティサイクル、方形波、2.2nF 負荷$ |     |     | 0.05 | W  |

| $P_{D2}$ | 最大出力消費電力       | $V_{CC1} = 15V, V_{CC2} = 15V, f = 1.9MHz, 50\% デューティサイクル、方形波、2.2nF 負荷$ |     |     | 0.99 | W  |

## 5.6 絶縁仕様

| パラメータ                                    |                                | テスト条件                                                                                                                                          | 仕様           | 単位        |

|------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------|

| <b>一般</b>                                |                                |                                                                                                                                                |              |           |

| CLR                                      | 外部空間距離 <sup>(1)</sup>          | 空気を介した最短のピン間距離                                                                                                                                 | > 14.7       | mm        |

| CPG                                      | 外部沿面距離 <sup>(1)</sup>          | パッケージ表面に沿った最短のピン間距離                                                                                                                            | > 15.7       | mm        |

| DTI                                      | 絶縁物を介した距離                      | 最小内部ギャップ (内部空間距離)                                                                                                                              | > 21         | μm        |

| CTI                                      | 比較トラッキングインデックス                 | DIN EN 60112 (VDE 0303-11), IEC 60112                                                                                                          | > 600        | V         |

|                                          | 材料グループ                         | IEC 60664-1 に準拠                                                                                                                                | I            |           |

|                                          | IEC 60664-1 に準拠した過電圧カテゴリ       | 定格商用電源 $V_{RMS}$ が 600V 以下                                                                                                                     | II-IV        |           |

|                                          | IEC 60664-1 に準拠した過電圧カテゴリ       | 定格商用電源 $V_{RMS}$ が 1000V 以下                                                                                                                    | II-III       |           |

| <b>DIN EN IEC 60747-17 (VDE 0884-17)</b> |                                |                                                                                                                                                |              |           |

| $V_{IORM}$                               | 最大反復ピーク絶縁電圧                    | AC 電圧 (バイポーラ)                                                                                                                                  | 2121         | $V_{PK}$  |

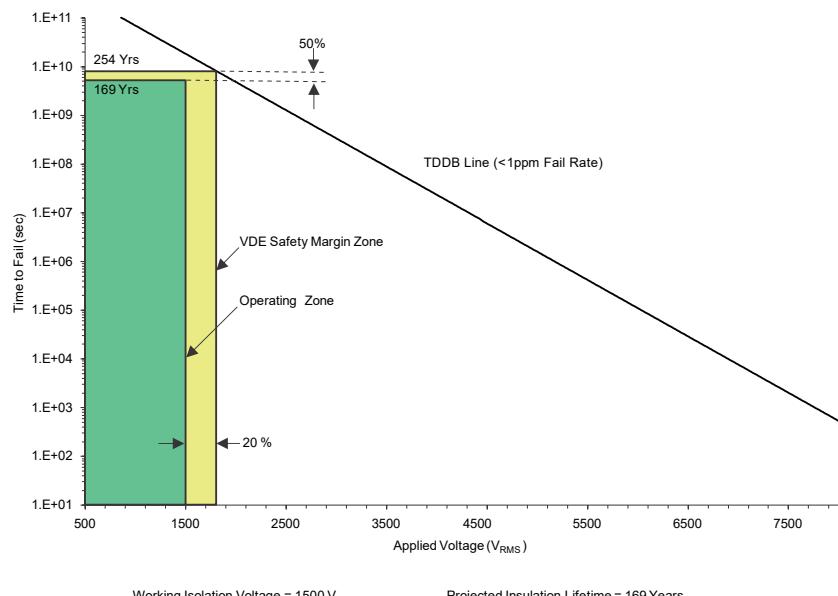

| $V_{IOWM}$                               | 最大絶縁動作電圧                       | AC 電圧 (正弦波)、絶縁膜経時破壊 (TDDB) テスト、図 1 を参照                                                                                                         | 1500         | $V_{RMS}$ |

|                                          |                                | DC 電圧                                                                                                                                          | 2121         | $V_{DC}$  |

| $V_{IOTM}$                               | 最大過渡絶縁電圧                       | $V_{TEST} = V_{IOTM}, t = 60s$ (認定試験)<br>$V_{TEST} = 1.2 \times V_{IOTM}, t = 1s$ (100% 製造試験)                                                  | 7000         | $V_{PK}$  |

| $V_{IOSM}$                               | 最大サージ絶縁電圧 <sup>(2)</sup>       | IEC 60065 に準拠したテスト手法、 $1.2/50\mu s$ 波形、 $V_{TEST} = 1.6 \times V_{IOSM}$ (認定)                                                                  | 8000         | $V_{PK}$  |

| $q_{pd}$                                 | 見掛けの電荷 <sup>(3)</sup>          | 方法 a: I/O 安全テスト サブグループ 2/3 の後、 $V_{ini} = V_{IOTM}, t_{ini} = 60s, V_{pd(m)} = 1.2 \times V_{IORM}, t_m = 10s$                                 | $\leq 5$     | pC        |

|                                          |                                | 方法 a: 環境テスト サブグループ 1 の後、 $V_{ini} = V_{IOTM}, t_{ini} = 60s, V_{pd(m)} = 1.6 \times V_{IORM}, t_m = 10s$                                       | $\leq 5$     |           |

|                                          |                                | 方法 b1: ルーチン テスト (100% 出荷時) および事前条件設定 (タイプ テスト) の場合、 $V_{ini} = V_{IOTM}, t_{ini} = 1s, V_{pd(m)} = 1.875 \times V_{IORM} = x V_{PK}, t_m = 1s$ | $\leq 5$     |           |

| $C_{IO}$                                 | 絶縁バリア容量、入力から出力へ <sup>(4)</sup> | $V_{IO} = 0.5 \times \sin(2\pi ft), f = 1MHz$                                                                                                  | $\leq 1.5$   | pF        |

| $R_{IO}$                                 | 絶縁抵抗、入力から出力へ <sup>(4)</sup>    | $V_{IO} = 500V, T_A = 25^\circ C$                                                                                                              | $10^{12}$ 以上 | $\Omega$  |

|                                          |                                | $V_{IO} = 500V (100^\circ C \leq T_A \leq 125^\circ C$ 時)                                                                                      | $10^{11}$ 以上 |           |

|                                          |                                | $V_{IO} = 500V (T_S = 150^\circ C$ 時)                                                                                                          | $10^9$ 以上    |           |

|                                          | 汚染度                            |                                                                                                                                                | 2            |           |

|                                          | 耐候性カテゴリ                        |                                                                                                                                                | 40/125/21    |           |

| <b>UL 1577</b>                           |                                |                                                                                                                                                |              |           |

## 5.6 絶縁仕様 (続き)

| パラメータ            |      | テスト条件                                                                                                                                                             | 仕様   | 単位               |

|------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------|

| V <sub>ISO</sub> | 絶縁耐圧 | V <sub>TEST</sub> = V <sub>ISO</sub> = 5000V <sub>RMS</sub> , t = 60s (認定), V <sub>TEST</sub> = 1.2 × V <sub>ISO</sub> = 6000V <sub>RMS</sub> , t = 1s (100% 出荷時) | 5000 | V <sub>RMS</sub> |

- (1) アプリケーションに固有の機器の絶縁規格に従って沿面距離および空間距離の要件を適用します。基板設計では、沿面距離および空間距離を維持し、プリント基板 (PCB) のアイソレータの取り付けパッドによりこの距離が短くならないよう注意が必要です。特定の場合には、PCB 上の沿面距離と空間距離は等しくなります。PCB 上にグルーブやリブを挿入するなどの技法を使用して、これらの仕様値を増やすことができます。

- (2) テストは、絶縁バリアの固有サージ耐性を判定するため、気中または油中で実行されます。

- (3) 見掛けの放電電荷とは、部分放電 (pd) により発生する放電です。

- (4) 絶縁バリアのそれぞれの側にあるすべてのピンを互いに接続して、2 つの端子を持つデバイスを構成します。

## 5.7 安全関連認証

| VDE                                        | UL                         | CQC                |

|--------------------------------------------|----------------------------|--------------------|

| DIN EN IEC 60747-17 (VDE 0884-17) による認証を計画 | UL 1577 部品認定プログラムに従う認証を計画中 | GB4943.1 に従う認証を計画中 |

| 認証計画中                                      | 認証計画中                      | 認証計画中              |

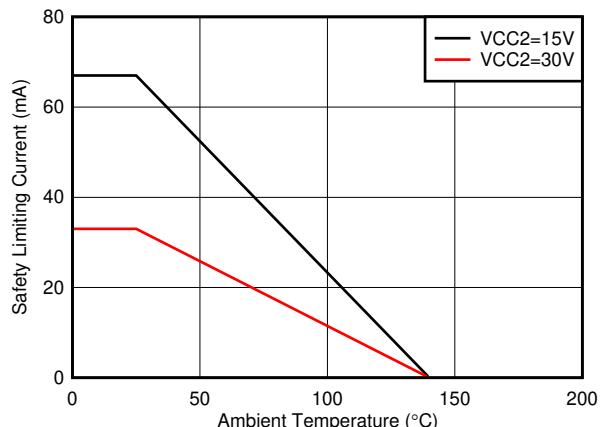

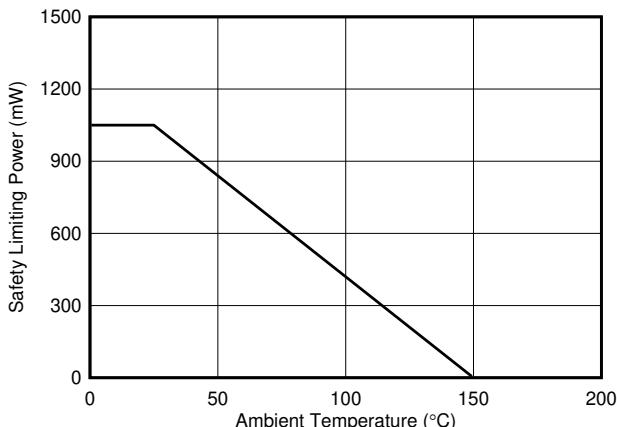

## 5.8 安全限界値

| パラメータ          |                       | テスト条件                                                                                            | 最小値 | 標準値  | 最大値 | 単位 |

|----------------|-----------------------|--------------------------------------------------------------------------------------------------|-----|------|-----|----|

| I <sub>S</sub> | 安全入力、出力、または電源電流       | R <sub>qJA</sub> = 87.1°C/W, V <sub>I</sub> = 15V, T <sub>J</sub> = 150°C, T <sub>A</sub> = 25°C |     | 89.2 |     | mA |

|                |                       | R <sub>qJA</sub> = 87.1°C/W, V <sub>I</sub> = 30V, T <sub>J</sub> = 150°C, T <sub>A</sub> = 25°C |     | 44.6 |     |    |

| P <sub>S</sub> | 安全入力電力                | R <sub>qJA</sub> = 87.1°C/W, T <sub>J</sub> = 150°C, T <sub>A</sub> = 25°C                       |     | 0.05 |     | W  |

| P <sub>S</sub> | 安全出力電力                | R <sub>qJA</sub> = 87.1°C/W, T <sub>J</sub> = 150°C, T <sub>A</sub> = 25°C                       |     | 1.34 |     | W  |

| T <sub>S</sub> | 最高安全温度 <sup>(1)</sup> |                                                                                                  |     | 150  |     | °C |

- (1) 最高安全温度 T<sub>S</sub> は、本デバイスに規定された最大接合部温度 T<sub>J</sub> と同じ値です。I<sub>S</sub> および P<sub>S</sub> パラメータはそれぞれ安全電流と安全電力を表します。I<sub>S</sub> および P<sub>S</sub> の最大限界値を超過してはなりません。これらの限界値は、周囲温度 T<sub>A</sub> によって異なります。「熱に関する情報」表にある接合部から空気への熱抵抗 R<sub>qJA</sub> は、リードあり表面実装パッケージ用の高 K テスト基板に搭載されているデバイスのものです。これらの式を使用して、以下のように各パラメータの値を計算します。T<sub>J</sub> = T<sub>A</sub> + R<sub>qJA</sub> × P, ここで、P はデバイスで消費される電力です。T<sub>J(max)</sub> = T<sub>S</sub> = T<sub>A</sub> + R<sub>qJA</sub> × P<sub>S</sub>, ここで、T<sub>J(max)</sub> は最大許容接合部温度です。P<sub>S</sub> = I<sub>S</sub> × V<sub>I</sub>, ここで、V<sub>I</sub> は最大電源電圧です。

## 5.9 電気的特性

VCC1 = 3.3V または 5V、VCC1 から GND1 への  $0.1\mu\text{F}$  コンデンサ、VCC2 = 15V、VCC2 から VEE2 への  $1\mu\text{F}$  コンデンサ、CL = 100pF、TA =  $-40^\circ\text{C} \sim 125^\circ\text{C}$  (特に記述のない限り)

| パラメータ                          |                                  | テスト条件                                                                                     | 最小値                 | 標準値                 | 最大値           | 単位 |

|--------------------------------|----------------------------------|-------------------------------------------------------------------------------------------|---------------------|---------------------|---------------|----|

| <b>供給電流</b>                    |                                  |                                                                                           |                     |                     |               |    |

| $I_{VCC1}$                     | 入力電源静止電流                         |                                                                                           | 1.67                | 2.4                 | mA            |    |

| $I_{VCC2}$                     | 出力消費静止電流                         |                                                                                           | 1.1                 | 1.8                 | mA            |    |

| <b>VCC1 電源電圧の低電圧スレッショルド</b>    |                                  |                                                                                           |                     |                     |               |    |

| $V_{VCC1\_ON}$                 | $V_{CC1}$ UVLO 立ち上がりスレッショルド      |                                                                                           | 2.6                 | 2.8                 |               | V  |

| $V_{VCC1\_OFF}$                | $V_{CC1}$ UVLO 立ち下がりスレッショルド      |                                                                                           | 2.4                 | 2.5                 |               |    |

| $V_{VCC1\_HYS}$                | $V_{CC1}$ UVLO スレッショルドのヒステリシス    |                                                                                           | 0.1                 |                     |               |    |

| <b>VCC2 電源電圧の低電圧スレッショルドと遅延</b> |                                  |                                                                                           |                     |                     |               |    |

| $V_{VCC2\_ON}$                 | $V_{CC2}$ UVLO 立ち上がりスレッショルド      |                                                                                           | 12                  | 13                  |               | V  |

| $V_{VCC2\_OFF}$                | $V_{CC2}$ UVLO 立ち下がりスレッショルド      |                                                                                           | 10.3                | 11                  |               |    |

| $V_{VCC2\_HYS}$                | $V_{CC2}$ UVLO スレッショルドのヒステリシス    |                                                                                           | 1                   |                     |               |    |

| <b>ロジック I/O</b>                |                                  |                                                                                           |                     |                     |               |    |

| $V_{IT+(IN)}$                  | 入力 High スレッショルド電圧                |                                                                                           | 0.55 x<br>$V_{CC1}$ | 0.7 x<br>$V_{CC1}$  |               | V  |

| $V_{IT-(IN)}$                  | 入力 Low スレッショルド電圧                 |                                                                                           | 0.3 x<br>$V_{CC1}$  | 0.45 x<br>$V_{CC1}$ |               |    |

| $V_{hys\ (IN)}$                | 入力スレッショルドのヒステリシス                 |                                                                                           | 0.1 x<br>$V_{CC1}$  |                     |               |    |

| $I_{IH}$                       | INx ピンの High レベル入力リーク電流          | $IN+ = V_{CC1}$                                                                           | 40                  | 240                 | $\mu\text{A}$ |    |

| $I_{IL}$                       | INx ピンの Low レベル入力リーク電流           | $IN- = GND1$                                                                              | -240                | -40                 | $\mu\text{A}$ |    |

| $I_{IL}$                       | IN- ピンの Low レベル入力リーク電流           | $IN- = GND1 - 5\text{V}$                                                                  | -310                | -80                 | $\mu\text{A}$ |    |

| <b>ゲートドライバ段</b>                |                                  |                                                                                           |                     |                     |               |    |

| $I_{OH}$                       | ピーク出力ソース電流                       | $IN+ = \text{High}, IN- = \text{Low}$                                                     | 5                   | 10                  | A             |    |

| $I_{OL}$                       | ピーク出力シンク電流                       | $IN+ = \text{Low}, IN- = \text{High}$                                                     | 5                   | 10                  | A             |    |

| $V_{OH}$                       | High レベル出力電圧 ( $V_{CC2} - OUT$ ) | $I_{OUT} = -20\text{mA}$                                                                  | 100                 | 240                 | mV            |    |

| $V_{OL}$                       | Low レベル出力電圧 (OUT)                | $IN+ = \text{Low}, IN- = \text{High}, I_{OUT} = 20\text{mA}$                              | 3                   | 7                   | mV            |    |

| <b>短絡クランプ</b>                  |                                  |                                                                                           |                     |                     |               |    |

| $V_{CLP-OUT}$                  | クランプ電圧 ( $V_{OUT} - V_{CC2}$ )   | $IN+ = \text{High}, IN- = \text{Low}, t_{CLAMP} = 10\mu\text{s}, I_{OUT} = 500\text{mA}$  | 1                   | 1.3                 | V             |    |

| $V_{CLP-OUT}$                  | クランプ電圧 ( $V_{EE2} - V_{OUT}$ )   | $IN+ = \text{Low}, IN- = \text{High}, t_{CLAMP} = 10\mu\text{s}, I_{OUT} = -500\text{mA}$ | 1.5                 |                     | V             |    |

| $V_{CLP-OUT}$                  | クランプ電圧 ( $V_{EE2} - V_{OUT}$ )   | $IN+ = \text{Low}, IN- = \text{High}, t_{CLAMP} = 10\mu\text{s}, I_{OUT} = -20\text{mA}$  | 0.9                 | 1                   | V             |    |

| <b>ミラー クランプ</b>                |                                  |                                                                                           |                     |                     |               |    |

| $V_{CLAMP}$                    | Low レベル クランプ電圧                   | $I_{CLAMP} = 20\text{mA}$                                                                 | 7                   | 13                  | mV            |    |

| $I_{CLAMP}$                    | クランプ Low レベル電流                   | $V_{CLAMP} = V_{EE2} + 15\text{V}$                                                        | 5                   | 10                  | A             |    |

| $I_{CLAMP(L)}$                 | Low レベル電流をクランプして低い出力電圧に変換        | $V_{CLAMP} = V_{EE2} + 2\text{V}$                                                         | 5                   | 10                  | A             |    |

| $V_{CLAMP-TH}$                 | クランプのスレッショルド電圧                   |                                                                                           | 2.1                 | 2.3                 | V             |    |

| <b>アクティブ ブルダウン</b>             |                                  |                                                                                           |                     |                     |               |    |

| $V_{OUTSD}$                    | OUT のアクティブ ブルダウン電圧               | $I_{OUT} = 0.1 \times I_{OUT(\text{typ})}, V_{CC2} = \text{オープン}$                         | 1.8                 | 2.5                 | V             |    |

## 5.10 スイッチング特性

VCC1 = 3.3V または 5V、VCC1 から GND1 への  $0.1\mu\text{F}$  コンデンサ、VCC2 = 15V、VCC2 から VEE2 への  $1\mu\text{F}$  コンデンサ、CL =  $100\text{pF}$ 、TJ =  $-40^\circ\text{C} \sim 125^\circ\text{C}$

| パラメータ            | テスト条件                                                          | 最小値 | 標準値 | 最大値 | 単位            |

|------------------|----------------------------------------------------------------|-----|-----|-----|---------------|

| $t_R$            | 出力信号の立ち上がり時間<br>$C_{LOAD}=1\text{nF}$                          |     | 10  | 26  | ns            |

| $t_F$            | 出力立ち下がり時間<br>$C_{LOAD}=1\text{nF}$                             |     | 10  | 22  | ns            |

| $t_{PLH}$        | 伝搬遅延 - Low から High<br>$C_{LOAD}=100\text{pF}$                  |     | 55  | 80  | ns            |

| $t_{PHL}$        | 伝搬遅延 - High から Low<br>$C_{LOAD}=100\text{pF}$                  |     | 55  | 80  | ns            |

| $t_{UVLO1\_rec}$ | $V_{CC1}$ の UVLO 回復遅延                                          |     | 30  |     | $\mu\text{s}$ |

| $t_{UVLO2\_rec}$ | $V_{CC2}$ の UVLO 回復遅延                                          |     | 50  |     | $\mu\text{s}$ |

| $t_{PWD}$        | パルス幅歪み<br>$C_{LOAD}=100\text{pF}$                              | 1   | 20  |     | ns            |

| $t_{sk(pp)}$     | 部品間スキュー<br>$C_{LOAD}=100\text{pF}$                             | 1   | 25  |     | ns            |

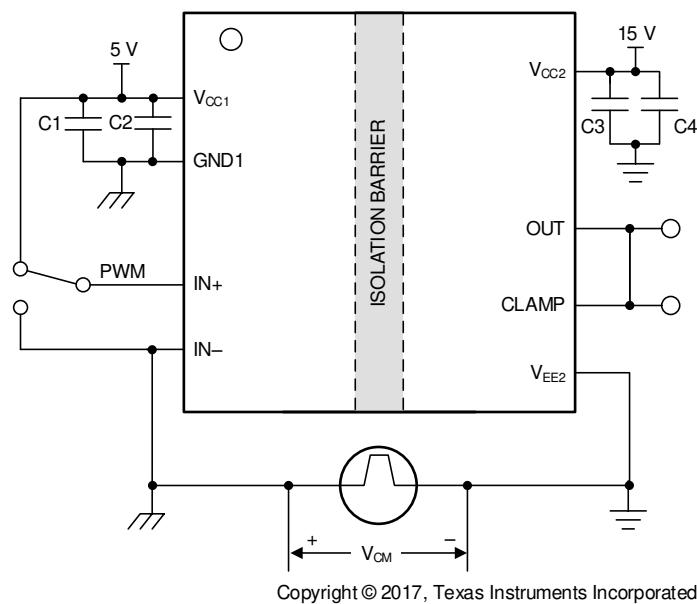

| CMTI             | 同相過渡耐性<br>PWM は GND または $V_{CC1}$ に接続、 $V_{CM} = 1200\text{V}$ | 100 | 120 |     | V/ns          |

## 5.11 絶縁特性曲線

図 5-1. VDE に従う制限電流の熱特性低下曲線

図 5-2. VDE に従う制限電力の熱特性低下曲線

図 5-3. 絶縁寿命予測データ

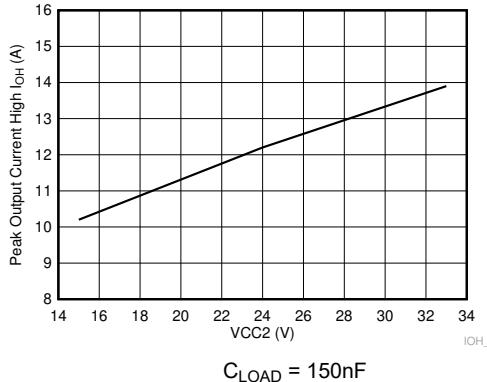

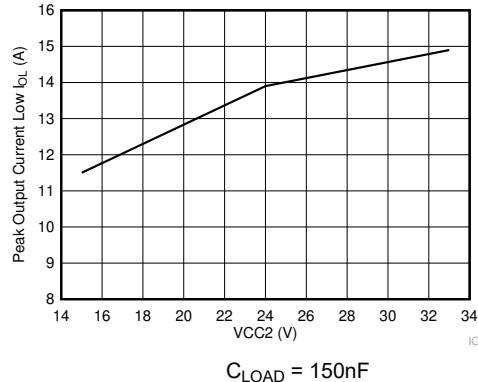

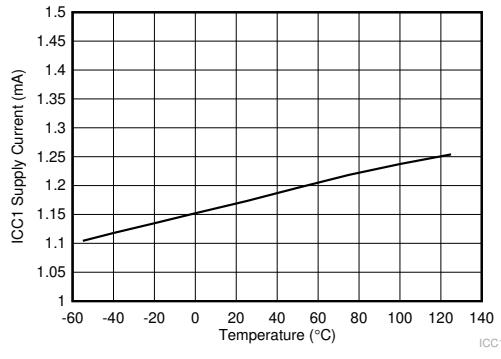

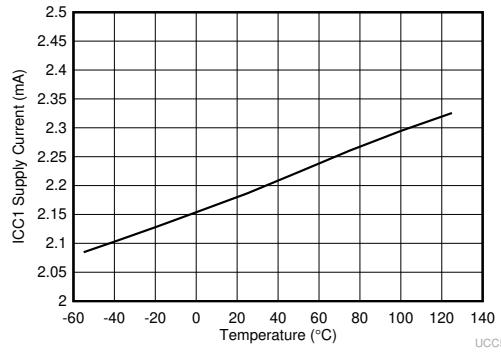

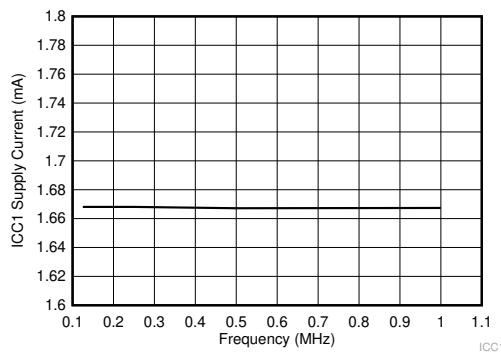

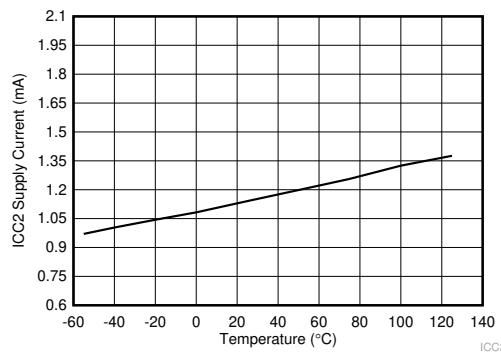

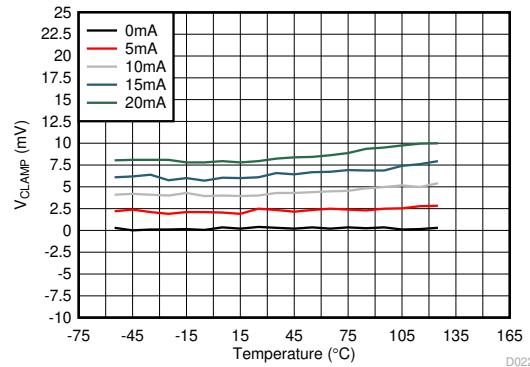

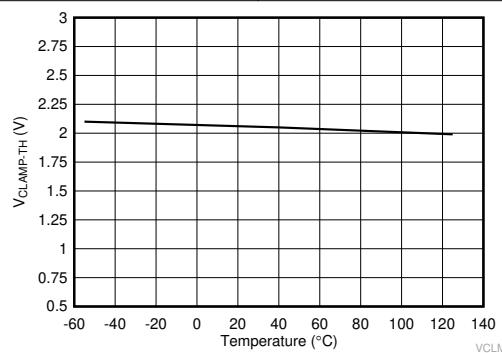

## 5.12 代表的特性

$V_{CC1} = 3.3V$  または  $5V$ 、 $V_{CC1}$  から GND1 への  $0.1\mu F$  コンデンサ、 $V_{CC2} = 15V$ 、 $V_{CC2}$  から  $V_{EE2}$  への  $1\mu F$  コンデンサ、 $C_{LOAD} = 1nF$ 、 $T_J = -40^{\circ}C \sim 125^{\circ}C$  (特に記述のない限り)

図 5-4. 出力 High の駆動電流と出力電圧との関係

図 5-5. 出力 Low の駆動電流と出力電圧との関係

図 5-6. I<sub>CC1</sub> 電源電流と温度との関係

図 5-7. I<sub>CC1</sub> 電源電流と温度との関係

図 5-8. I<sub>CC1</sub> 電源電流と入力周波数との関係

デューティ サイクル

= 50%

図 5-8. I<sub>CC1</sub> 電源電流と入力周波数との関係

図 5-9. I<sub>CC2</sub> 電源電流と温度との関係

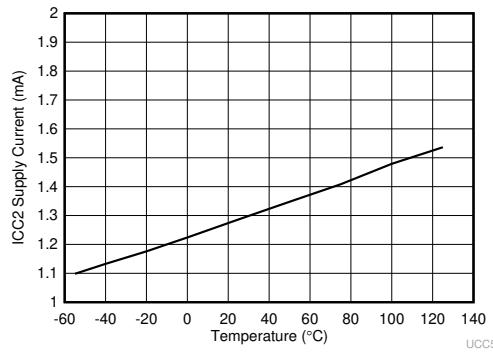

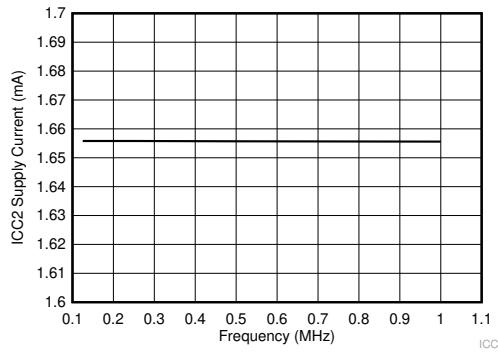

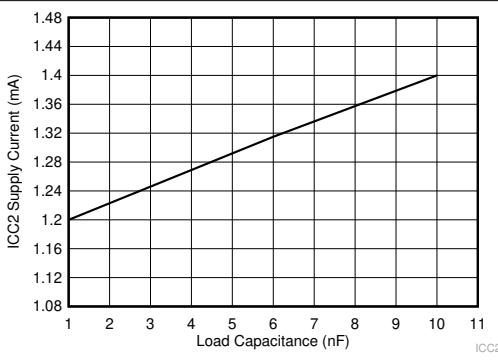

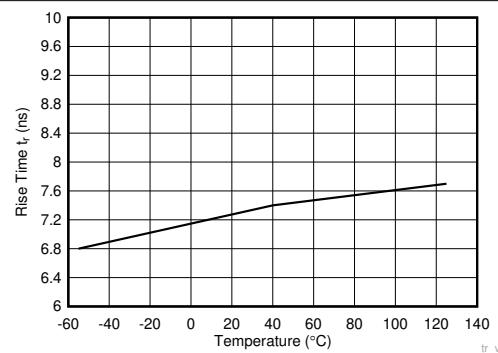

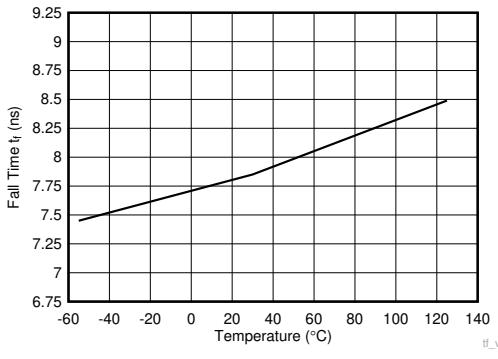

## 5.12 代表的特性 (続き)

$V_{CC1} = 3.3V$  または  $5V$ 、 $V_{CC1}$  から GND1 への  $0.1\mu F$  コンデンサ、 $V_{CC2} = 15V$ 、 $V_{CC2}$  から  $V_{EE2}$  への  $1\mu F$  コンデンサ、 $C_{LOAD} = 1nF$ 、 $T_J = -40^{\circ}C \sim 125^{\circ}C$  (特に記述のない限り)

図 5-10. I<sub>CC2</sub> 電源電流と温度との関係

図 5-11. I<sub>CC2</sub> 電源電流と入力周波数との関係

$f_{SW} = 1kHz$

図 5-12. I<sub>CC2</sub> 電源電流と負荷容量との関係

図 5-13. 立ち上がり時間と温度との関係

図 5-14. 立ち下がり時間と温度との関係

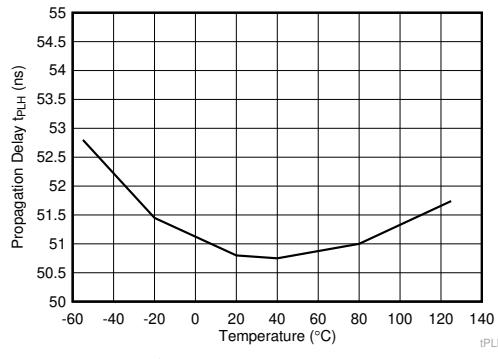

図 5-15. 伝搬遅延 t<sub>PLH</sub> と温度との関係

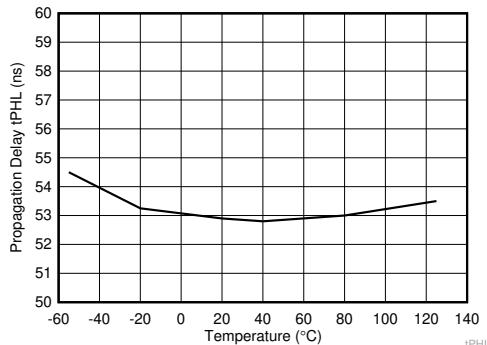

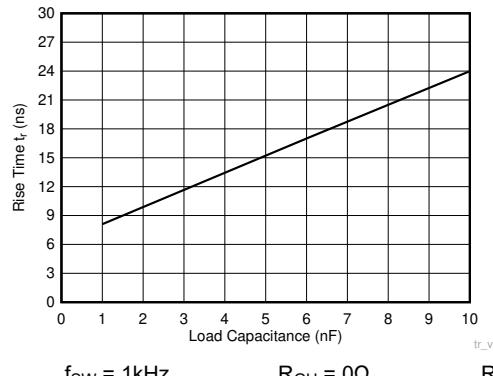

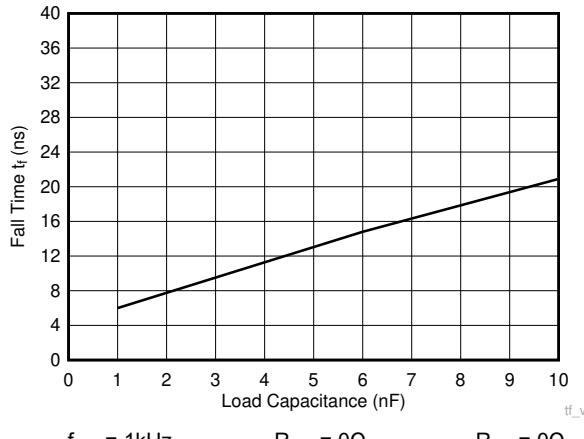

## 5.12 代表的特性 (続き)

$V_{CC1} = 3.3V$  または  $5V$ 、 $V_{CC1}$  から GND1 への  $0.1\mu F$  コンデンサ、 $V_{CC2} = 15V$ 、 $V_{CC2}$  から  $V_{EE2}$  への  $1\mu F$  コンデンサ、 $C_{LOAD} = 1nF$ 、 $T_J = -40^{\circ}C \sim 125^{\circ}C$  (特に記述のない限り)

図 5-16. 伝搬遅延  $t_{PHL}$  と温度との関係

図 5-17. 立ち上がり時間と負荷容量との関係

図 5-18. 立ち下がり時間と負荷容量との関係

図 5-19.  $V_{CLAMP}$  と温度との関係

図 5-20.  $V_{CLAMP-TH}$  と温度との関係

## 6 パラメータ測定情報

### 6.1 伝搬遅延、反転、非反転型構成

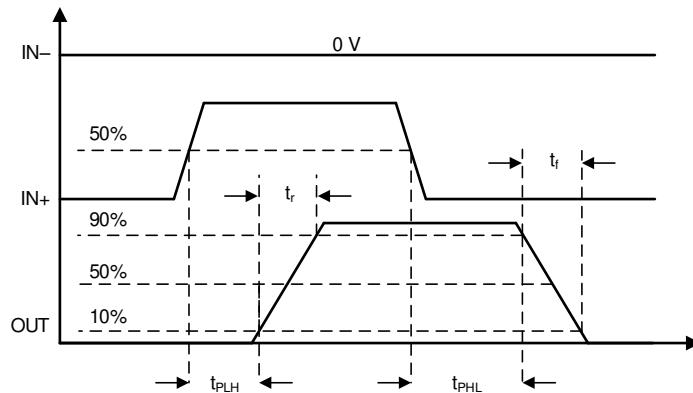

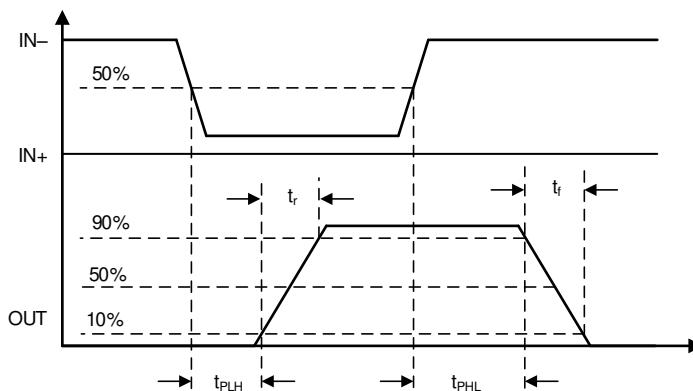

図 6-1 に、非反転型構成での伝搬遅延を示します。図 6-2 に、反転型構成での伝搬遅延を示します。これらの図は、立ち上がり ( $t_r$ ) および立ち下がり ( $t_f$ ) 時間の測定に使用される方法も示しています。

図 6-1. 伝搬遅延、非反転型構成

図 6-2. 伝搬遅延、反転型構成

### 6.1.1 CMTI テスト

図 6-3 は CMTI テスト構成の概略図です。

図 6-3. ミラー クランプ (UCC5350L-Q1) 用の CMTI テスト回路

## 7 詳細説明

### 7.1 概要

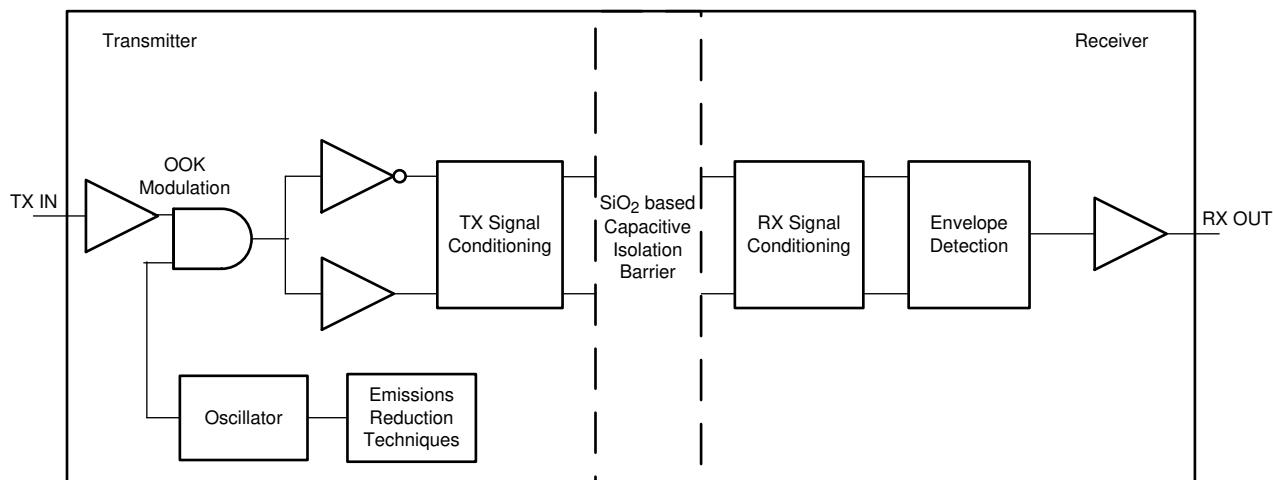

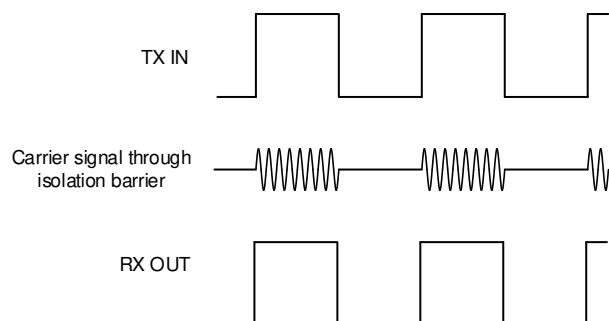

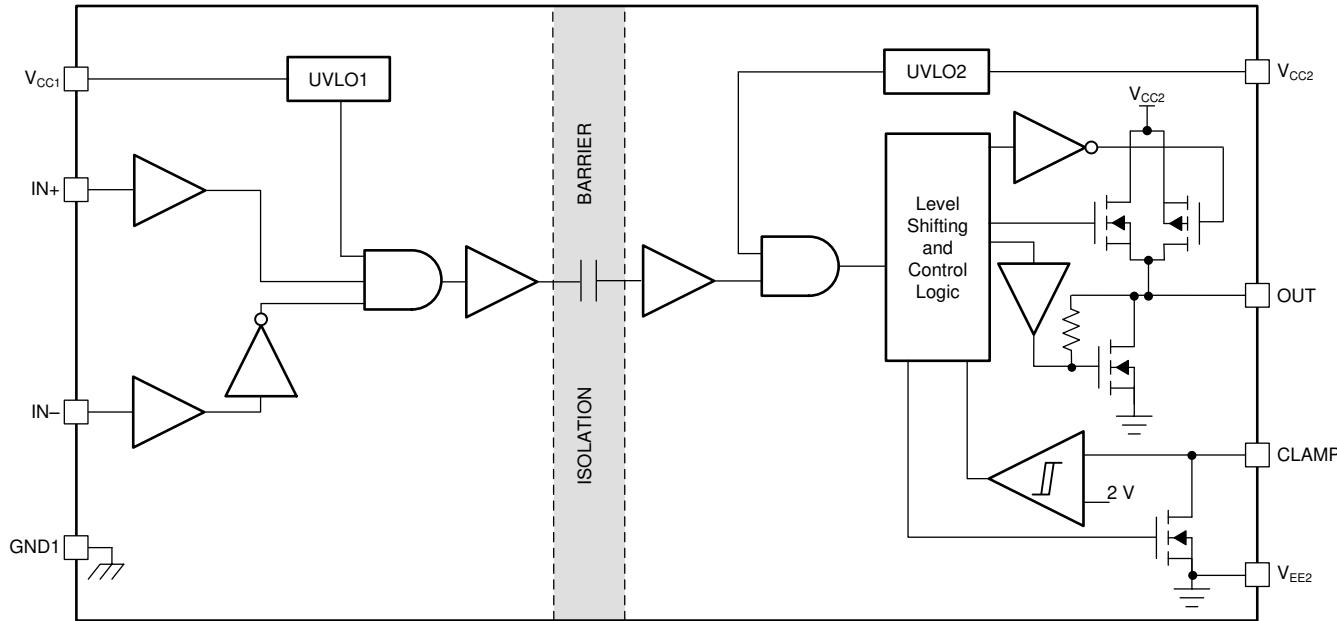

UCC5350L-Q1 内部の絶縁は、高電圧  $\text{SiO}_2$  ベースのコンデンサを使用して実装されています。絶縁を介する信号の送信には、オン オフ キーイング (OOK) 変調方式を使用し、二酸化ケイ素をベースとする絶縁バリアを介してデジタル データを送信します (図 7-2 を参照)。トランスマッタは、バリアを介して 1 つのデジタル状態を表す高周波キャリアを送信し、もう 1 つのデジタル状態を表すのに信号を送信しません。レシーバは、高度な信号コンディショニングを行ってから信号を復調し、バッファ段経由で出力を生成します。UCC5350L-Q1 に高度な回路手法を採用して、CMTI 性能を最大化し、高周波キャリアおよび IO バッファ スイッチングによる放射エミッションを最小化しています。デジタル容量性アイソレータの概念ブロック図である 図 7-1 は、代表的なチャネルの機能ブロック図を示しています。図 7-2 に、OOK 方式の概念図を示します。

図 7-1 に、変調 (OOK) とシグナル コンディショニングを通じ、入力信号が容量性絶縁バリアをどのように通過するかを示します。

### 7.2 機能ブロック図

図 7-1. 容量性データチャネルの概念ブロック図

図 7-2. オン オフ キーイング (OOK) による変調方式

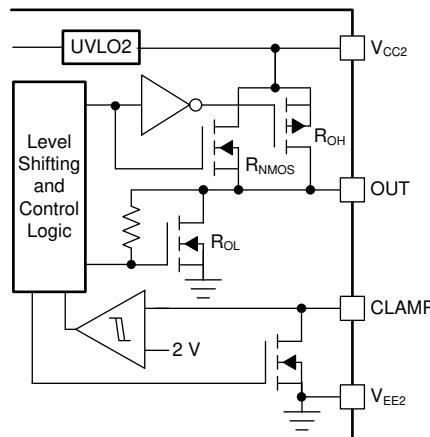

図 7-3. 機能ブロック図

## 7.3 機能説明

### 7.3.1 電源

入力電源  $V_{CC1}$  は 3V ~ 15V の広い電圧範囲に対応し、出力電源  $V_{CC2}$  は 13.2V ~ 30V の電圧範囲に対応します。

ユニポーラ電源を使用する場合、 $V_{CC2}$  電源は IGBT では  $VEE2$  に対して 15V、SiC MOSFET では 20V に接続されます。 $VEE2$  電源は 0V に接続されています。この使用事例では、ミラー クランプを使用すると、負の電圧レールなしで、パワー スイッチが誤ってオンになるのを防止できます。ミラー クランプ機能は、電源デバイスのゲートと  $VEE2$  電源との間に低インピーダンスのパスを追加することで実装されます。クランプ ピンを流れるミラー電流はシンクされ、これによりゲート電圧がゲートのターンオン スレッショルド値よりも低くなるようにクランプされます。

### 7.3.2 入力段

入力ピン (IN+ および IN-) は、CMOS 互換の入力スレッショルド ロジックに基づいており、 $V_{CC2}$  電源電圧から完全に絶縁されています。UCC5350L-Q1 は、標準の High スレッショルド ( $V_{IT+(IN)}$ ) が  $0.55 \times V_{CC1}$ 、標準の Low スレッショルドが  $0.45 \times V_{CC1}$  であるため、ロジック レベルの制御信号 (3.3V マイコンからの信号など) で入力ピンを簡単に駆動できます。 $0.1 \times V_{CC1}$  という広いヒステリシス ( $V_{hys(IN)}$ ) は良好なノイズ耐性と安定動作に役立ちます。いずれかの入力がオープンのままになっている場合、 $128k\Omega$  の内部プルダウン抵抗は IN+ ピンを Low に強制し、 $128k\Omega$  の内部抵抗は IN- を High にします。ただし、ノイズ耐性を向上させるために入力を使用しない場合は、入力を接地するか  $VCC1$  に接続することを TI は推奨します。

UCC5350L-Q1 の入力側は出力ドライバから絶縁されているため、入力信号の振幅は、推奨される制限を超えない限り  $V_{CC2}$  より大きくても小さくてもかまいません。この特長により、ゲートドライバを制御信号ソースと柔軟に統合でき、任意のゲートに対して最も効率的な  $V_{CC2}$  をユーザーは選択できます。ただし、IN+ または IN- に印加される信号の振幅は、 $V_{CC1}$  の電圧を上回ってはいけません。

### 7.3.3 出力段

UCC5350L-Q1 の出力段は、最も必要とされるとき、つまり、パワー スイッチのターンオン遷移のミラー プラトー領域の間 (パワー スイッチのドレインまたはコレクタ電圧に  $dV/dt$  が生じたとき) に最大のピーク ソース電流を供給できるプルアップ構造を採用しています。出力段のプルアップ構造は、並列接続した P チャネル MOSFET と追加のプルアップ N チャネル MOSFET を備えています。N チャネル MOSFET の役割は、ピーク ソース電流を短時間ブーストし、高速ターンオンを実現することです。出力の状態を Low から High に変更しようとする短い瞬間だけ、N チャネル MOSFET をターンオ

ンする方法で、高速ターンオンを実現します。[表 7-1](#) に、プルアップおよびプルダウン構造の標準内部抵抗値を示します。

**表 7-1. UCC5350L-Q1 のオン抵抗**

| デバイスのオプション  | $R_{NMOS}$ | $R_{OH}$ | $R_{OL}$ | $R_{CLAMP}$ | 単位       |

|-------------|------------|----------|----------|-------------|----------|

| UCC5350L-Q1 | 1.54       | 12       | 0.26     | 0.26        | $\Omega$ |

$R_{OH}$  パラメータは DC 測定値であり、P チャネル デバイスのみのオン抵抗を表します。プルアップ N チャネル デバイスは DC 状態ではオフ状態に保たれ、出力が Low から High に変化する瞬間にのみターンオンするため、このパラメータは P チャネル デバイスでのみ使用されます。このため、この短いターンオン段階における UCC5350L-Q1 のプルアップ段の実効抵抗は、 $R_{OH}$  パラメータが表す値よりもはるかに小さくなり、高速ターンオンを実現します。ターンオン段階の出力抵抗は、 $R_{OH} \parallel R_{NMOS}$  の並列組み合わせとなります。

UCC5350L-Q1 のプルダウン構造は、N チャネル MOSFET で単純に構成されています。ミラー クランプの場合、CLAMP ピンと OUT ピンが IGBT または MOSFET のゲートに接続されているとき、プルダウン構造と並列に追加の FET が接続されます。出力は 5A ピーク電流パルスを供給またはシンクできます。 $V_{CC2}$  と  $V_{EE2}$  との間の出力電圧スイングは、レール ツー レールで動作します。

**図 7-4. 出力段**

### 7.3.4 保護機能

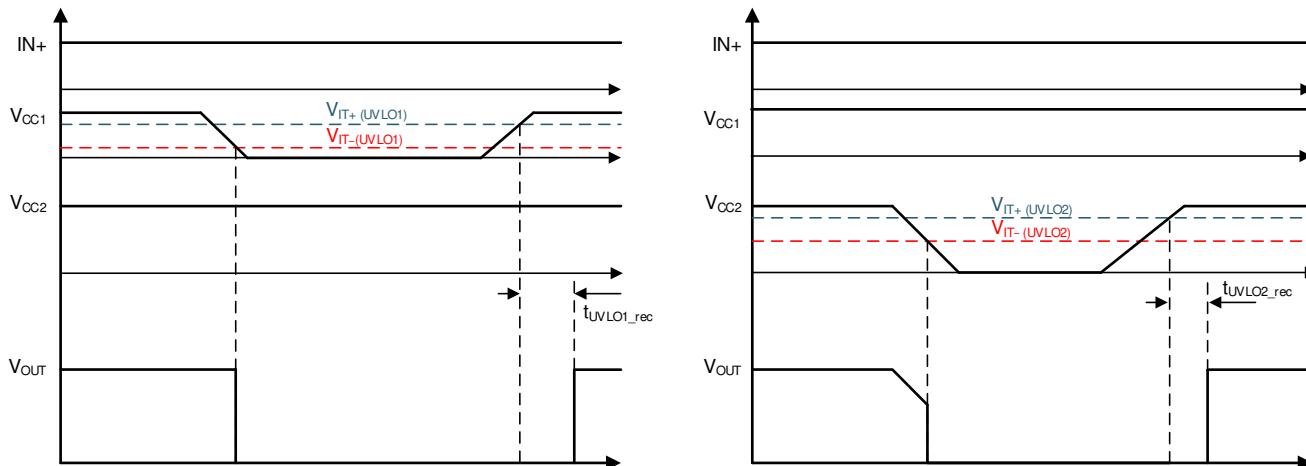

#### 7.3.4.1 低電圧誤動作防止 (UVLO)

UVLO 機能は、 $V_{CC1}$  ピンと GND1 ピン間、および  $V_{CC2}$  ピンと  $V_{EE2}$  ピン間にある  $V_{CC1}$  および  $V_{CC2}$  電源の両方に実装されており、IGBT と MOSFET での駆動不足状態を防止します。デバイス起動時に  $V_{CC}$  が  $V_{IT+}$  (UVLO) を下回っている場合や、起動後に  $V_{IT-}$  (UVLO) を下回った場合、電圧源の UVLO 機能は、入力ピン (IN+ および IN-) にかかわりなく、影響を受ける出力を Low に保持します ([表 7-2](#) を参照)。 $V_{CC}$  UVLO 保護機能はヒステリシス機能 ( $V_{hys(UVLO)}$ ) を備えています。このヒステリシスは、電源がグランド ノイズを生成したときのチャタリングを防止します。これにより、デバイスがスイッチングを開始し、動作電流消費が急激に増加したときに発生するバイアス電圧の小さな降下を許容できます。UVLO 機能を [図 7-5](#) に示します。

**表 7-2. UCC5350L-Q1  $V_{CC1}$  UVLO ロジック**

| 条件                                          | 入力  |     | 出力 |

|---------------------------------------------|-----|-----|----|

|                                             | IN+ | IN- |    |

| デバイス起動時、 $V_{CC1} - GND1 < V_{IT+}$ (UVLO1) | H   | L   | L  |

|                                             | L   | H   | L  |

|                                             | H   | H   | L  |

|                                             | L   | L   | L  |

表 7-2. UCC5350L-Q1  $V_{CC1}$  UVLO ロジック (続き)

| 条件                                          | 入力  |     | 出力  |

|---------------------------------------------|-----|-----|-----|

|                                             | IN+ | IN- | OUT |

| デバイス起動後、 $V_{CC1} - GND1 < V_{IT-}$ (UVLO1) | H   | L   | L   |

|                                             | L   | H   | L   |

|                                             | H   | H   | L   |

|                                             | L   | L   | L   |

表 7-3. UCC5350L-Q1  $V_{CC2}$  UVLO ロジック

| 条件                                             | 入力  |     | 出力  |

|------------------------------------------------|-----|-----|-----|

|                                                | IN+ | IN- | OUT |

| デバイス起動時、 $V_{CC2} - V_{EE2} < V_{IT+}$ (UVLO2) | H   | L   | L   |

|                                                | L   | H   | L   |

|                                                | H   | H   | L   |

|                                                | L   | L   | L   |

| デバイス起動後、 $V_{CC2} - V_{EE2} < V_{IT-}$ (UVLO2) | H   | L   | L   |

|                                                | L   | H   | L   |

|                                                | H   | H   | L   |

|                                                | L   | L   | L   |

$V_{CC1}$  または  $V_{CC2}$  が UVLO1 または UVLO2 スレッショルドを下回る場合、電源電圧が  $V_{IT+}$  (UVLO) または  $V_{IT-}$  (UVLO2) を再度上回ると、出力で遅延  $t_{UVLO1\_rec}$  または  $t_{UVLO2\_rec}$  が発生します。この遅延を図 7-5 に示します。

図 7-5. UVLO 機能

#### 7.3.4.2 アクティブ プルダウン

アクティブ プルダウン機能は、 $V_{CC2}$  電源に電力が接続されていないときに IGBT または MOSFET ゲートを Low 状態にするために使用されます。この機能により、出力を約 2V にクランプすることで、OUT および CLAMP ピンでの IGBT および MOSFET の誤ったターンオンを防止できます。

ドライバの出力段にバイアスが印加されていない場合、または UVLO 状態である場合、ドライバ出力の電圧上昇を制限するアクティブ クランプ回路によってドライバ出力は Low に保持されます。この条件では、下側の NMOS のゲートが 500k $\Omega$  抵抗経由でドライバ出力に接続される一方で、上側の PMOS はプルアップ抵抗によってオフに保持されます。この構成では、出力は下側の NMOS デバイスのスレッショルド電圧 (バイアス電力が存在しない場合は約 1.5V) に実質的にクランプされます。

### 7.3.4.3 短絡クランプ

短絡クランプ機能は、短絡状態のときにドライバ出力の電圧をクランプし、アクティブ ミラー クランプ ピンを  $V_{CC2}$  電圧よりもわずかに高くなるために使用されます。短絡クランプ機能は、過電圧による破損や劣化から IGBT または MOSFET ゲートを保護するのに役立ちます。短絡クランプ機能は、専用ピンとドライバ内の  $V_{CC2}$  ピンの間にダイオード接続を追加することにより実装されます。内部ダイオードは、 $10\mu\text{s}$  の間最大  $500\text{mA}$  の電流を供給でき、 $20\text{mA}$  の電流を連続供給できます。必要に応じて外部ショットキー ダイオードを使用し、電流伝導能力を向上させます。

### 7.3.4.4 アクティブ ミラー クランプ

アクティブ ミラー クランプ機能を使用すると、ユニポーラ電源を使用するアプリケーションにおいて、ミラー電流によってパワー スイッチが誤ってオンになるのを防止できます。アクティブ ミラー クランプ機能は、パワー スイッチのゲート端子とグランド ( $V_{EE2}$ ) の間に低インピーダンスのパスを追加してミラー電流をシンクすることにより実装されます。ミラー クランプ機能により、オフ状態ではパワー スイッチのゲート電圧が  $2\text{V}$  未満にクランプされます。図 8-1 に、この機能の代表的なアプリケーション回路を示します。

## 7.4 デバイスの機能モード

表 7-4 に、 $V_{CC1}$  および  $V_{CC2}$  が推奨範囲内であると仮定した、UCC5350L-Q1 の機能モードを示します。

表 7-4. UCC5350L-Q1 の機能表

| IN+  | IN-  | OUT  |

|------|------|------|

| Low  | X    | Low  |

| X    | High | Low  |

| High | Low  | High |

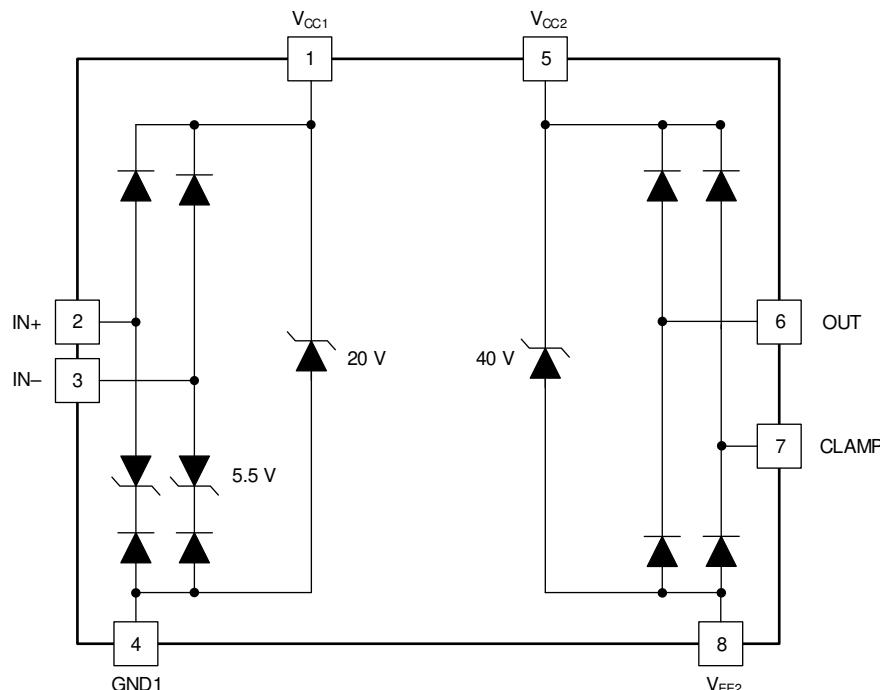

### 7.4.1 ESD 構造

図 7-6 に、UCC5350L-Q1 デバイスの ESD 保護素子に関する複数のダイオードを示します。これは、本デバイスの絶対最大定格を図で表したものです。

図 7-6. ESD 構造の「L」バージョン

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

UCC5350L-Q1 は、MOSFET、IGBT、SiC MOSFET などのパワー半導体デバイス用のシンプルな絶縁型ゲートドライバです。このデバイス ファミリは、モーター制御、ソーラーインバータ、スイッチモード電源、産業用インバータなどのアプリケーションでの使用を想定しています。

UCC5350L-Q1 はアクティブミラークランプを備えており、ミラー電流によってパワートランジスタが誤ってターンオンするのを防止できます。このデバイスは 8 ピンの DWL で供給され、沿面距離は 15.7mm、空間距離は 14.7mm で、基本絶縁または強化絶縁が必要なアプリケーションに適しています。UCC5350L-Q1 の最小駆動電流は 5A です。

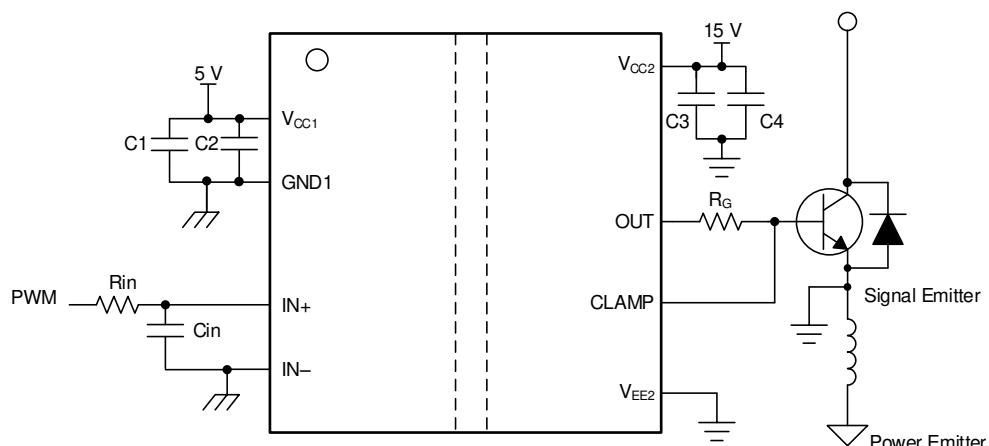

### 8.2 代表的なアプリケーション

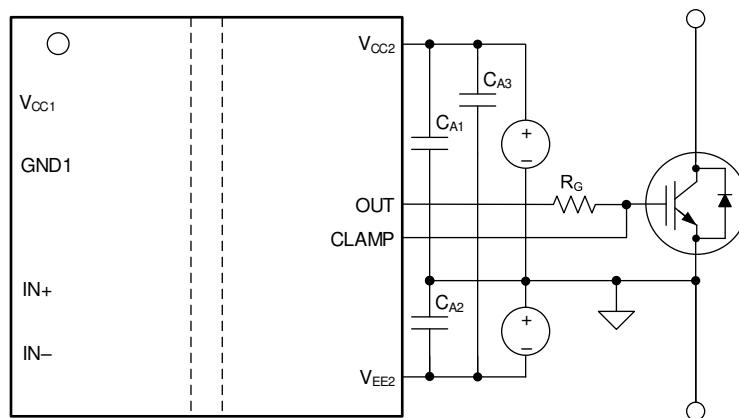

図 8-1 に、IGBT を駆動するための代表的なアプリケーションの回路図を示します。

Copyright © 2017, Texas Instruments Incorporated

図 8-1. IGBT を駆動するための UCC5350L-Q1 の代表的なアプリケーション回路

#### 8.2.1 設計要件

表 8-1. UCC5350L-Q1 設計要件

| パラメータ               | 値    | 単位  |

|---------------------|------|-----|

| $V_{CC1}$           | 3.3  | V   |

| $V_{CC2} - V_{EE2}$ | 18   | V   |

| IN+                 | 3.3  | V   |

| IN-                 | GND1 | -   |

| スイッチング周波数           | 150  | kHz |

| パワー デバイスのゲート電荷      | 126  | nC  |

## 8.2.2 詳細な設計手順

### 8.2.2.1 IN+ および IN- 入力フィルタの設計

ユーザーが出力の信号を低速にする（または遅延させる）目的でゲートドライバへの信号成形を避けることを TI は推奨します。しかし、理想的でないレイアウトまたは長い PCB 配線によって生じるリギングを除去するために小さな入力フィルタ  $R_{IN}$ - $C_{IN}$  を使用することは可能です。

このようなフィルタでは、 $0 \sim 100\Omega$  の  $R_{IN}$  抵抗と  $10 \sim 1000\text{pF}$  の  $C_{IN}$  コンデンサを使用する必要があります。この例では、 $R_{IN} = 51\Omega$  と  $C_{IN} = 33\text{pF}$  が選択されており、コーナー周波数は約  $100\text{MHz}$  です。

これらの部品を選択する際は、ノイズ耐性と伝搬遅延のトレードオフに注意してください。

### 8.2.2.2 ゲート ドライバの出力抵抗

外部ゲートドライバ抵抗  $R_{G(ON)}$  および  $R_{G(OFF)}$  は、以下の目的で使用します。

1. 寄生インダクタンスおよび容量に起因するリギングの制限

2. 高電圧または高電流スイッチングの  $dv/dt$ 、 $di/dt$ 、ボディダイオードの逆方向回復に起因するリギングの制限

3. ゲート駆動強度（すなわちピークシンクおよびソース電流）の微調整によるスイッチング損失の最適化

4. 電磁干渉（EMI）の低減

出力段には、P チャネル MOSFET と N チャネル MOSFET を並列接続したプルアップ構造があります。代表的な合計ピークソース電流は、UCC5350L-Q1 の場合  $10\text{A}$  です。ピークソース電流を見積るには、式 1 を使用します。ワイドボディではインダクタンスが大きくなるため、DWL パッケージの堅牢性を高めるため、少なくとも  $5\Omega$  のゲート抵抗の使用を推奨します。

$$I_{OH} = \frac{V_{CC2} - V_{EE2}}{R_{NMOS} || R_{OH} + R_{GON} + R_{GFET\_Int}} \quad (1)$$

ここで、

- $R_{ON}$  は外部ターンオン抵抗で、この例では  $2.2\Omega$  です。

- $R_{GFET\_Int}$ ：パワー ランジスタのデータシートに記載されているパワー ランジスタの内部ゲート抵抗。この例では  $1.8\Omega$  と想定されています。

- $I_{OH}$  は代表的なピークソース電流であり、これは  $10\text{A}$ （ゲートドライバピークソース電流）とゲート駆動ループ抵抗に基づく計算値のうちの小さい方の値です。

この例では、ピークソース電流は式 2 で計算されたように約  $3.36\text{A}$  です。

$$I_{OH} = \frac{V_{CC2} - V_{EE2}}{R_{NMOS} || R_{OH} + R_{GON} + R_{GFET\_Int}} = \frac{18\text{V}}{1.54\Omega || 12\Omega + 2.2\Omega + 1.8\Omega} \approx 3.36\text{A} \quad (2)$$

同様に、ピークシンク電流を計算するには、式 3 を使用します。

$$I_{OL} = \frac{V_{CC2} - V_{EE2}}{R_{OL} + R_{GOFF} + R_{GFET\_Int}} \quad (3)$$

ここで、

- $R_{OFF}$  は外部ターンオフ抵抗で、この例では  $2.2\Omega$  です。

- $I_{OL}$  は代表的なピークシンク電流であり、これは  $10\text{A}$ （ゲートドライバピークシンク電流）とゲート駆動ループ抵抗に基づく計算値のうちの小さい方の値です。

この例では、ピークシンク電流は式 4 と  $10\text{A}$  の小さい方の値です。

$$I_{OL} = \frac{V_{CC2} - V_{EE2}}{R_{OL} + R_{GOFF} + R_{GFET\_Int}} = \frac{18\text{V}}{0.26\Omega + 2.2\Omega + 1.8\Omega} \approx 4.23\text{A} \quad (4)$$

## 注

推定ピーク電流は、PCB レイアウトと負荷容量の影響も受けます。ゲートドライバのループの寄生インダクタンスは、ピーク ゲート駆動電流を遅れさせ、オーバーシュートとアンダーシュートを発生させる可能性があります。そのため、ゲートドライバのループができるだけ小さくすることを強く推奨します。一方、パワー ランジスタの負荷容量 ( $C_{ISS}$ ) が非常に小さい（通常 1nF 未満）場合、ピーク ソースおよびシンク電流はループ寄生素子に支配されます。なぜなら、立ち上がりおよび立ち下がり時間が非常に小さく、寄生リギングの周期に近いためです。

## 8.2.2.3 ゲート ドライバの電力損失の推定

ゲート ドライバ サブシステムの総損失  $P_G$  には、UCC5350L-Q1 デバイスの電力損失 ( $P_{GD}$ ) と、外部ゲート駆動抵抗などのペリフェラル回路の電力損失が含まれます。

$P_{GD}$  値は、UCC5350L-Q1 デバイスの熱的安定性に関連する制限値を決定する主要な電力損失で、複数の要因からの損失を計算することにより推定できます。

第 1 の要因は静的電力損失  $P_{GDQ}$  です。これにはドライバの静止電力損失と、特定のスイッチング周波数で動作しているドライバの自己消費電力が含まれます。 $P_{GDQ}$  パラメータは、所定の  $V_{CC1}$ 、 $V_{CC2}$ 、スイッチング周波数、周囲温度において、OUT ピンに負荷が接続されていない状態でベンチ測定されます。この例では、 $V_{CC1} = 3.3V$ 、 $V_{CC2} = 18V$  です。PWM を 0V から 3.3V まで 150kHz でスイッチングした場合の各電源の電流は、 $I_{CC1} = 1.67mA$ 、 $I_{CC2} = 1.11mA$  と測定されます。 $P_{GDQ}$  は式 5 を使用して計算されます。

$$P_{GDQ} = V_{CC1} \times I_{VCC1} + (V_{CC2} - V_{EE2}) \times I_{CC2} \approx 23.31mW \quad (5)$$

第 2 の要素はスイッチング動作損失  $P_{GDO}$  であり、所定の負荷容量によりドライバは各スイッチング サイクル中に負荷を充放電します。負荷スイッチングからの総ダイナミック損失  $P_{GSW}$  を計算するには、式 6 を使用します。

$$P_{GSW} = (V_{CC2} - V_{EE2}) \times Q_G \times f_{SW} \quad (6)$$

ここで、

- $Q_G$  は、 $V_{CC2}$  におけるパワー ランジスタのゲート電荷です。

この例のアプリケーションでは、式 7 に示すように、負荷スイッチングによる総ダイナミック損失は約 340mW です。

$$P_{GSW} = 18 V \times 126 nC \times 150 kHz = 340 mW \quad (7)$$

$Q_G$  は、パワー ランジスタの総ゲート電荷量を表します。テスト条件が変わると、この値も変わることがあります。UCC5350L-Q1 の出力段のゲートドライバ損失 ( $P_{GDO}$ ) は  $P_{GSW}$  の一部です。外部ゲートドライバの抵抗とパワー ランジスタの内部抵抗が  $0\Omega$  で、ゲートドライバの損失がすべて UCC5350L-Q1 の内部で消費される場合、 $P_{GDO}$  は  $P_{GSW}$  と等しくなります。外部ターンオンおよびターンオフ抵抗が存在する場合、総損失はゲートドライバのプルアップ / プルダウン抵抗、外部ゲート抵抗、パワー ランジスタの内部抵抗に分散されます。ソース / シンク電流が 10A に飽和していない場合、プルアップ / ダウン抵抗は線形かつ固定ですが、ソース / シンク電流が飽和している場合、プルアップ / ダウン抵抗は非線形であることに注意します。ゲートドライバ損失は、式 8 に示すように飽和していない場合に推定されます。

$$P_{GDO} = \frac{P_{GSW}}{2} \left( \frac{R_{OH} || R_{NMOS}}{R_{OH} || R_{NMOS} + R_{GON} + R_{GFET\_Int}} + \frac{R_{OL}}{R_{OL} + R_{GOFF} + R_{GFET\_Int}} \right) \quad (8)$$

この設計例では、予測されるソースおよびシンク電流はすべて 10A 未満であるため、式 9 を使用してゲートドライバ損失を推定します。

$$P_{GDO} = \frac{340 \text{ mW}}{2} \left( \frac{12 \Omega \parallel 1.54 \Omega}{12 \Omega \parallel 1.54 \Omega + 2.2 \Omega + 1.8 \Omega} + \frac{0.26 \Omega}{0.26 \Omega + 2.2 \Omega + 1.8 \Omega} \right) \approx 53.66 \text{ mW} \quad (9)$$

ここで、

- $V_{OUTH/L(t)}$  は、ターンオンおよびターンオフ中のゲートドライバ OUT ピンの電圧です。出力がある期間飽和している場合、この値は負荷コンデンサを充電または放電する定電流源 (ターンオンおよびターンオフ時は 10A) として簡素化できます。その結果、 $V_{OUTH/L(t)}$  波形は線形となり、 $T_{R\_Sys}$  と  $T_{F\_Sys}$  は簡単に予測できます。

UCC5350L-Q1 ゲートドライバ  $P_{GD}$  で消費されるゲートドライバの総損失は、式 10 を使用して計算します。

$$P_{GD} = P_{GDQ} + P_{GDO} = 25.31 \text{ mW} + 53.66 \text{ mW} = 78.97 \text{ mW} \quad (10)$$

#### 8.2.2.4 推定接合部温度

UCC5350L-Q1 の接合部温度 ( $T_J$ ) を推定するには、以下の式を使用します。

$$T_J = T_C + \Psi_{JT} \times P_{GD} \quad (11)$$

ここで、

- $T_C$  は、熱電対またはその他の手段で測定された UCC5350L-Q1 のケース上面温度です。

- $\Psi_{JT}$  は、「熱に関する情報」表に記載されている、接合部から上面への熱特性パラメータです。

接合部からケースへの熱抵抗 ( $R_{\theta JC}$ ) の代わりに接合部から上面への熱特性パラメータ ( $\Psi_{JT}$ ) を使用することで、接合部温度の推定の精度を大幅に向上させることができます。ほとんどの IC の熱エネルギーの大半は、パッケージのリードを経由して PCB に放散されるのに対して、全エネルギーのごく一部のみがケース上面から放散されます (通常は熱電対で測定されます)。 $R_{\theta JC}$  抵抗は、熱エネルギーの大部分がケースを通して放散される場合 (例: 金属パッケージが使われている場合、IC パッケージにヒートシンクが取り付けられている場合) にのみ有効に使用できます。それ以外の場合に  $R_{\theta JC}$  を使っても、真の接合部温度を正確に推定することはできません。 $\Psi_{JT}$  パラメータは、IC の上面を通して放散される大部分のエネルギーが、テスト環境とアプリケーション環境で同等であると仮定することで実験的に求められます。推奨レイアウトガイドラインが守られている限り、接合部温度は数°C 以内の精度で推定できます。

#### 8.2.2.5 $V_{CC1}$ および $V_{CC2}$ コンデンサの選択

$V_{CC1}$  および  $V_{CC2}$  電源のバイパスコンデンサは、信頼性を高めるために不可欠です。十分な電圧定格、温度係数、静電容量公差の表面実装型の低 ESR/ESL 多層セラミックコンデンサ (MLCC) を推奨します。

#### 注

一部の MLCC の DC バイアスは、実際の容量値に影響を与えます。たとえば、25V、1μF X7R のコンデンサは、15V<sub>DC</sub> の DC バイアスを印加した場合、わずか 500nF に測定されます。

#### 8.2.2.5.1 $V_{CC1}$ コンデンサの選択

$V_{CC1}$  に接続されたバイパスコンデンサは、1 次側ロジックに必要な過渡電流と総消費電流に対応しますが、これはわずか数ミリアンペアです。したがって、この用途には 100nF 以上の 50V MLCC を推奨します。バイアス電源出力が  $V_{CC1}$  ピンから比較的離れた場所に配置されている場合、1μF を超える値のタンタルまたは電解コンデンサを MLCC と並列に配置する必要があります。

#### 8.2.2.5.2 $V_{CC2}$ コンデンサの選択

50V、10μF の MLCC と 50V、0.22μF の MLCC を  $C_{VCC2}$  コンデンサとして選択しています。バイアス電源出力が  $V_{CC2}$  ピンから比較的離れた場所に配置されている場合、10μF を超える値のタンタルまたは電解コンデンサを  $C_{VCC2}$  と並列に接続する必要があります。

### 8.2.2.5.3 出力段の負バイアスを使う応用回路

理想的でない PCB レイアウトと長いパッケージリード (TO-220 および TO-247 タイプのパッケージなど) によって寄生インダクタンスが付くと、高  $di/dt$  および  $dv/dt$  スイッチング中、パワートランジスタのゲート - ソース間駆動電圧にリンクが生じる可能性があります。リンクがスレッショルド電圧を上回る場合、意図しないターンオンおよび貫通電流が発生する可能性があります。ゲート駆動に負のバイアスを印加することは、このようなリンクをスレッショルドよりも低く保つための一般的な方法です。負のゲート駆動バイアスの実装例をいくつか示します。

図 8-2 に、2 つの電源 (または 1 つの 1 入力 2 出力電源) を使う別の例を示します。 $V_{CC2}$  とエミッタ間の電源が正の駆動出力電圧を決定し、 $V_{EE2}$  とエミッタ間の電源が負のターンオフ電圧を決定します。このソリューションでは最初の例よりも多くの電源を必要としますが、正と負のレール電圧をより柔軟に設定できます。

図 8-2. 2 つの絶縁型バイアス電源による負バイアス印加

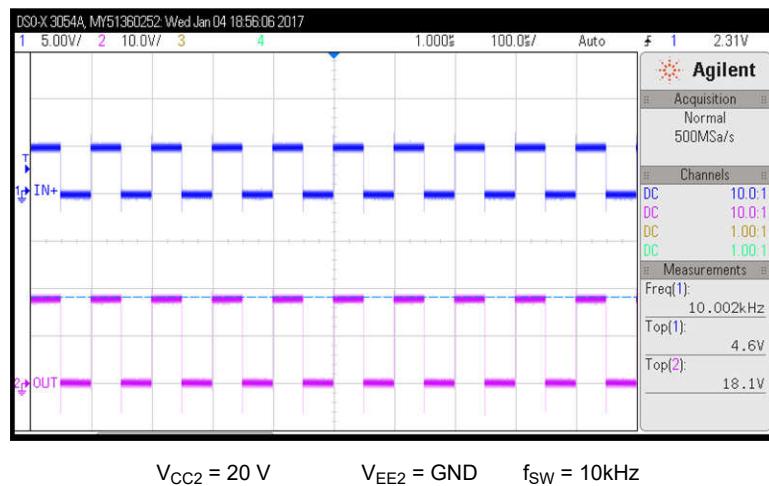

### 8.2.3 アプリケーション曲線

図 8-3. PWM 入力とゲート電圧波形

## 9 電源に関する推奨事項

ターンオンおよびターンオフのスイッチング過渡中、ソースおよびシンクのピーク電流は VCC2 および VEE2 電源から供給されます。大きなピーク電流により、VCC2 および VEE2 の電圧レベルがドレインして、電源で電圧降下が生じる可能性があります。電源を安定させ、信頼性の高い動作を保証するために、電源に一連のデカップリング コンデンサを推奨します。デバイスのピーク駆動能力が  $\pm 10A$  であり、高い  $dV/dt$  を生成できることを考慮して、VCC2 と VEE2 のと間に  $10\mu F$  バイパスコンデンサを推奨します。出力側電源と比較して電流が少ないため、VCC1 と GND1 間に  $1\mu F$  バイパスコンデンサを推奨します。また、高周波ノイズをフィルタリングして除去するため、各電源に  $0.1\mu F$  デカップリング コンデンサも推奨します。デカップリング コンデンサは、高周波ノイズを避けるために低 ESR および低 ESL にする必要があります。また、PCB レイアウトのシステム寄生成分からのノイズ結合を防止するため、VCC1、VCC2、VEE2 ピンにできる限り近づけて配置する必要があります。

## 10 レイアウト

### 10.1 レイアウトのガイドライン

このデバイスは超ワイド ボディであるため、性能を最適化するために、設計者は PCB レイアウトに十分注意する必要があります。主なガイドラインは次のとおりです。

- 部品の配置:

- ノイズをバイパスし、外付けパワー ランジスタをターンオンさせる際の大きなピーク電流に対応するため、低 ESR かつ低 ESL のコンデンサを本デバイスの近く、V<sub>CC1</sub> と GND1 ピンとの間、および V<sub>CC2</sub> と V<sub>EE2</sub> ピンとの間に接続する必要があります。

- スイッチ ノードに接続されている V<sub>EE2</sub> ピンでの大きな負の過渡を防止するため、上側トランジスタのソースと下側トランジスタのソースとの間の寄生インダクタンスを最小限に抑える必要があります。

- 堅牢性を高めるため、この部品とゲート抵抗の組み合わせを  $5\Omega$  以上とすることを強く推奨します。

- 次のセクションの「レイアウト例」に推奨レイアウトを示します。これは、堅牢な性能を確保する上で非常に重要です。

- 接地に関する注意事項:

- トランジスタのゲートを充放電する大きいピーク電流が流れる領域を、最小の物理面積に制限することが不可欠です。これによりループのインダクタンスの減少が制限され、トランジスタのゲート端子のノイズが最小限に抑えられます。ゲートドライバは、トランジスタのできるだけ近くに配置する必要があります。

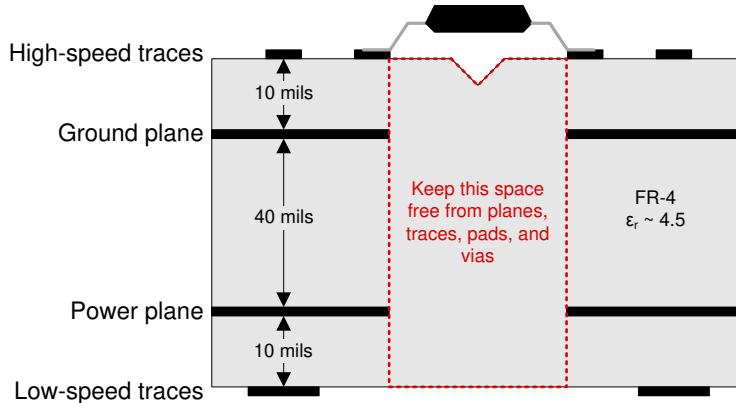

- 高電圧に関する注意事項:

- 1 次側と 2 次側の間の絶縁性能を確保するため、ドライバ デバイスの下には PCB パターンも銅箔も配置しないようにします。絶縁性能を低下させるおそれがある汚染を防止するため、PCB カットアウトや溝を推奨します。

- 熱に関する検討事項:

- 駆動電圧が高い、負荷が大きい、またはスイッチング周波数が高い場合、UCC5350L-Q1 は大きな電力を消費する可能性があります。適切な PCB レイアウトは、デバイスから PCB に熱を放散し、接合部から基板への熱インピーダンス ( $\theta_{JB}$ ) を最小化するのに役立ちます。

- V<sub>CC2</sub> および V<sub>EE2</sub> ピンに接続する PCB 銅箔を増やすことを推奨します。V<sub>EE2</sub> への接続を最大化することを優先します。ただし、前述の高電圧 PCB に関する考慮事項に従う必要があります。

- TI は、システムに複数の層がある場合は、V<sub>CC2</sub> ピンおよび V<sub>EE2</sub> ピンを、適切なサイズの複数のビアを経由して内部のグランドまたは電源プレーンに接続することを推奨しています。熱伝導率を最大化するため、これらのビアは IC ピンの近くに配置する必要があります。ただし、異なる高電圧プレーンからのパターンや銅箔が重ならないように注意してください。

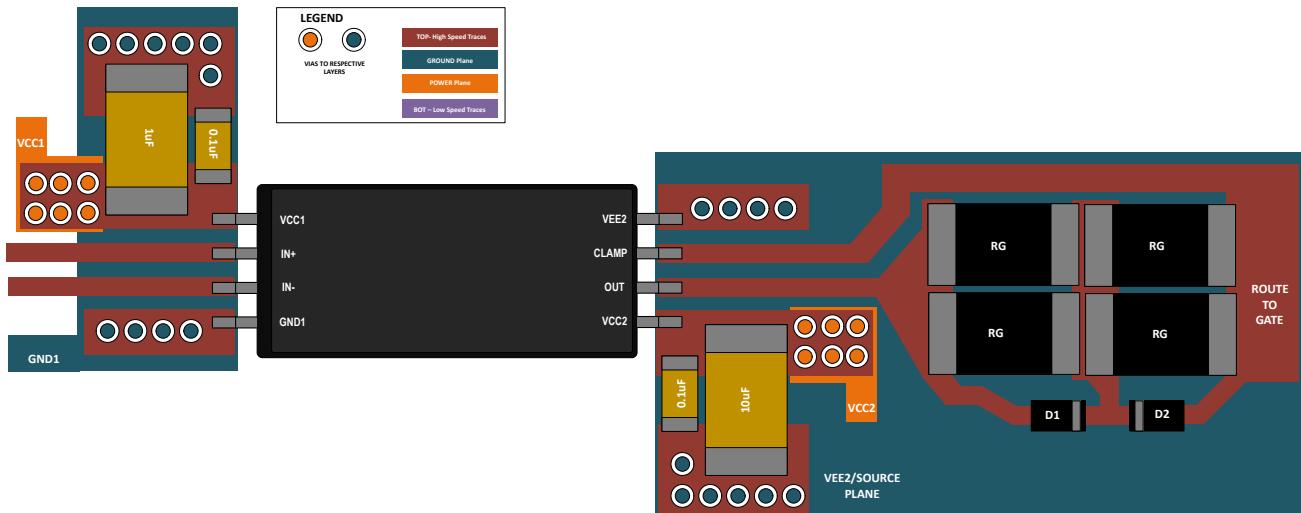

### 10.2 レイアウト例

PCB レイアウトの例を以下の図に示します。この図では、信号と主要部品にラベル付けしています。

A. 1次側と2次側の間に PCB パターンも銅箔も存在しないため、絶縁性能を確保できます。

図 10-1. レイアウト例

### 10.3 PCB 材料

標準的な FR-4 UL94V-0 プリント基板を使用します。この PCB は、高周波での誘電損失の低減、吸湿性の低減、強度と剛性の向上、および自己消火性の特性により、安価な代替品よりも推奨されます。

図 10-2 に、推奨されるレイヤ・スタックを示します。

図 10-2. 推奨されるレイヤ・スタック

## 11 デバイスおよびドキュメントのサポート

### 11.1 デバイス サポート

#### 11.1.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

### 11.2 ドキュメントのサポート

#### 11.2.1 関連資料

関連資料については、以下を参照してください。

- テキサス・インスツルメンツ、『デジタルアイソレータ設計ガイド』

- テキサス・インスツルメンツ、『絶縁の用語集』

- テキサス・インスツルメンツ、『SN6501 絶縁電源用のトランジストドライバ』データシート

- テキサス・インスツルメンツ、『SN6505A 絶縁電源用の低ノイズ、1Aトランジストドライバ』データシート

- テキサス・インスツルメンツ、『UCC5390ECDWV 絶縁型ゲートドライバ評価基板』ユーザー ガイド

- テキサス・インスツルメンツ、『UCC53x0xD 評価基板』ユーザー ガイド

### 11.3 認証

UL オンライン認定ディレクトリ、『FPPT2.E181974 非光学絶縁デバイス - 部品』認定番号: 20170718-E181974、

### 11.4 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 11.5 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 11.6 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 11.7 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 11.8 用語集

#### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 12 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 日付         | 改訂 | 注      |

|------------|----|--------|

| March 2025 | *  | 初版リリース |

## 13 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| UCC5350MCQDWLRQ1      | Active        | Production           | SOIC (DWL)   8 | 500   LARGE T&R       | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | 53MCQ               |

| UCC5350MCQDWLRQ1.A    | Active        | Production           | SOIC (DWL)   8 | 500   LARGE T&R       | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | 53MCQ               |

| UCC5350MCQDWLRQ1.B    | Active        | Production           | SOIC (DWL)   8 | 500   LARGE T&R       | -           | Call TI                              | Call TI                           | -40 to 125   |                     |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**TAPE AND REEL INFORMATION**

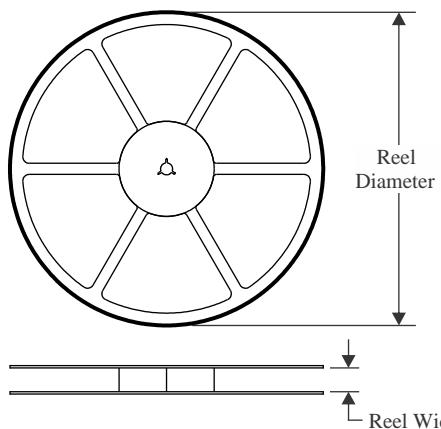

**REEL DIMENSIONS**

**TAPE DIMENSIONS**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

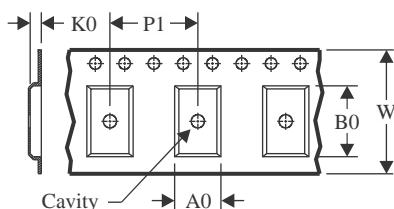

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|------------------|--------------|-----------------|------|-----|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| UCC5350MCQDWLRQ1 | SOIC         | DWL             | 8    | 500 | 330.0              | 24.4               | 18.55   | 7.2     | 4.5     | 24.0    | 24.0   | Q1            |

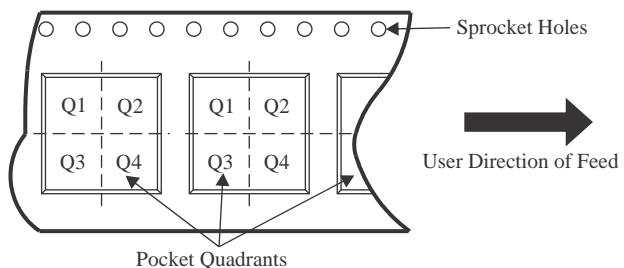

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|-----|-------------|------------|-------------|

| UCC5350MCQDWLRQ1 | SOIC         | DWL             | 8    | 500 | 356.0       | 356.0      | 45.0        |

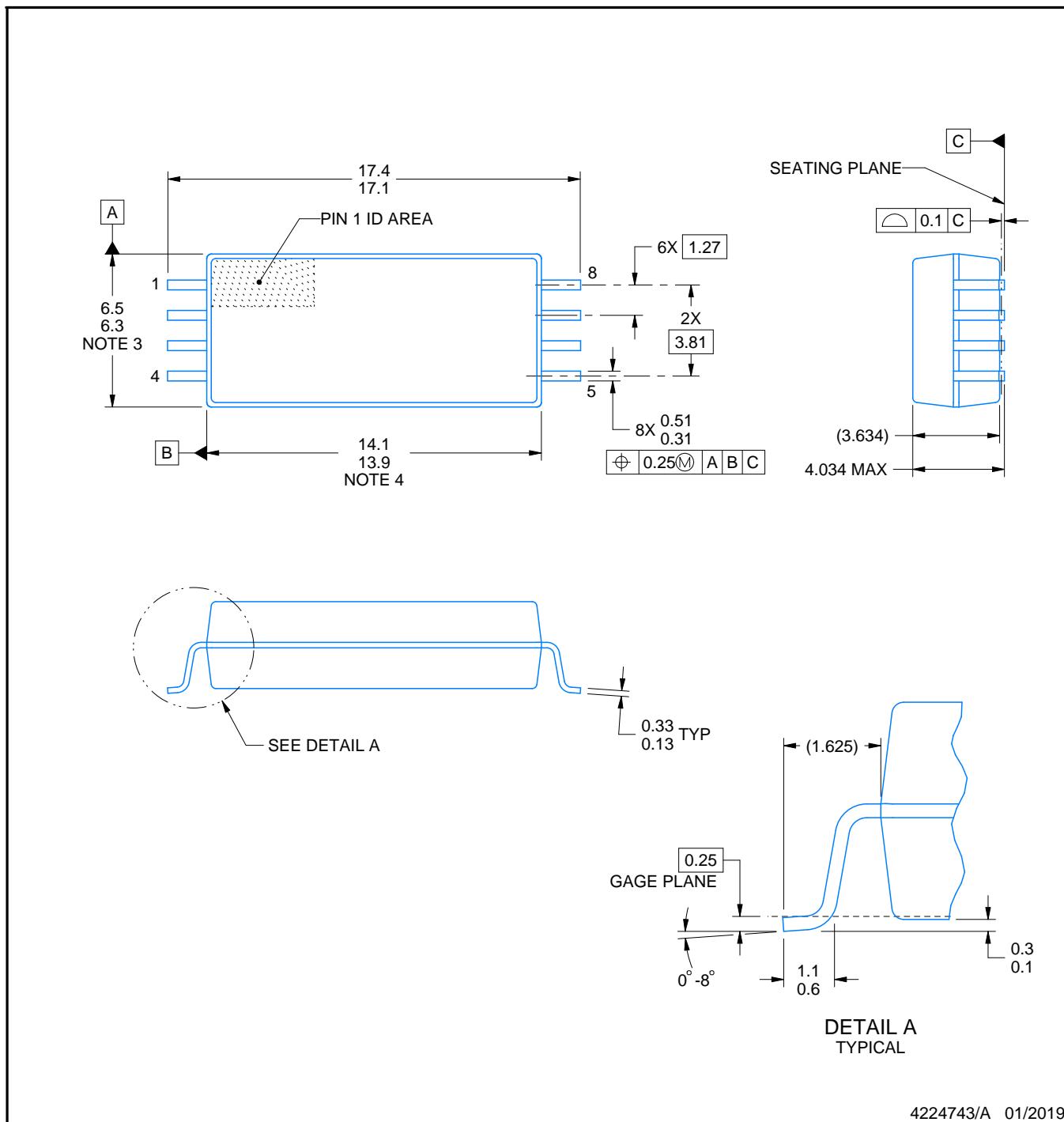

# PACKAGE OUTLINE

DWL0008A

SOIC - 4.034 mm max height

PLASTIC SMALL OUTLINE

4224743/A 01/2019

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. This dimension does not include interlead flash.

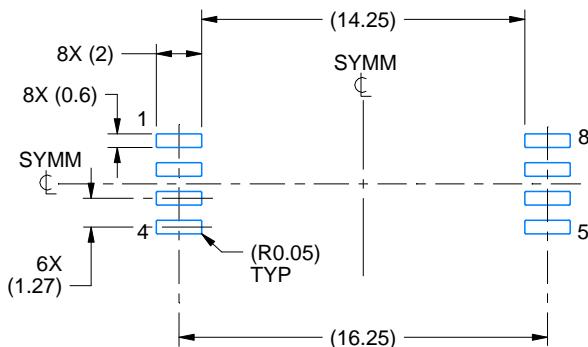

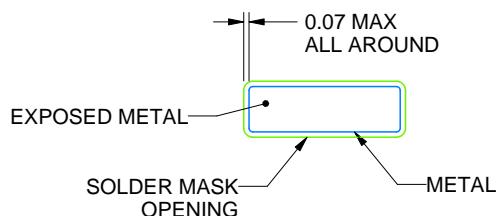

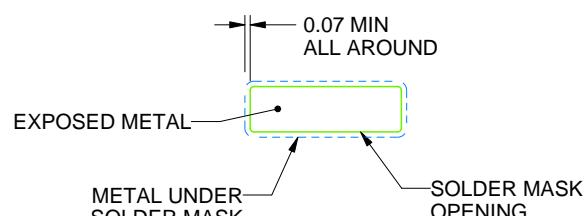

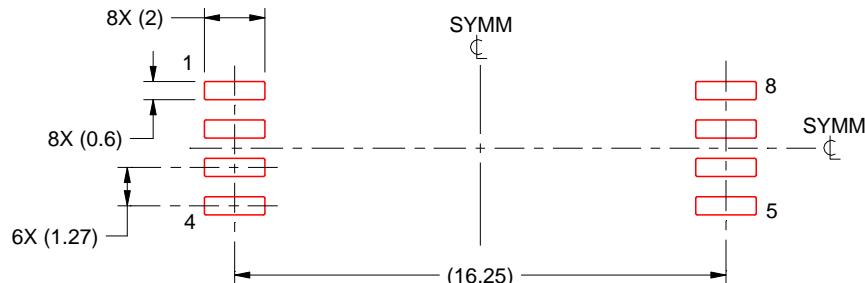

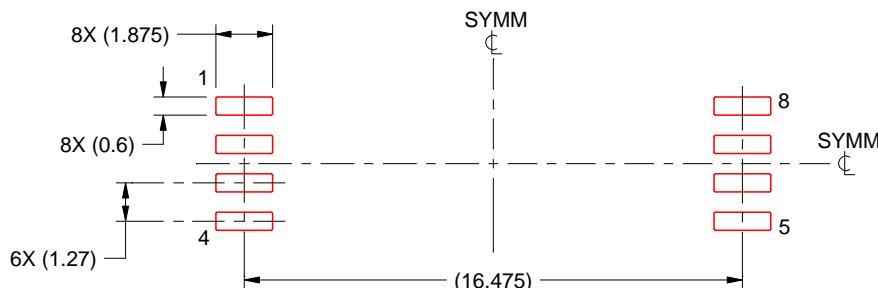

# EXAMPLE BOARD LAYOUT

DWL0008A

SOIC - 4.034 mm max height

PLASTIC SMALL OUTLINE

LAND PATTERN EXAMPLE

STANDARD

EXPOSED METAL SHOWN

SCALE:3X

LAND PATTERN EXAMPLE

PCB CLEARANCE & CREEPAGE OPTIMIZED

EXPOSED METAL SHOWN

SCALE:3X

NON SOLDER MASK

DEFINED

(PREFERRED)

SOLDER MASK

DEFINED

SOLDER MASK DETAILS

4224743/A 01/2019

NOTES: (continued)

5. Publication IPC-7351 may have alternate designs.

6. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

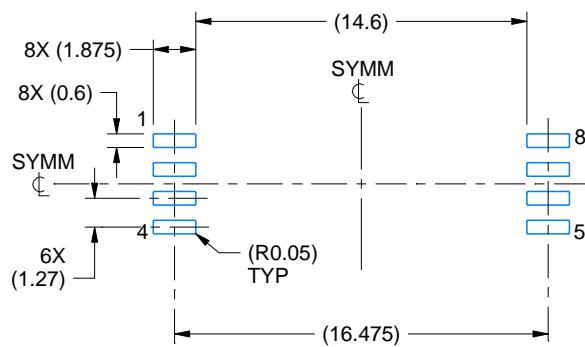

# EXAMPLE STENCIL DESIGN

DWL0008A

SOIC - 4.034 mm max height

PLASTIC SMALL OUTLINE

SOLDER PASTE EXAMPLE

STANDARD

BASED ON 0.125 mm THICK STENCIL

SCALE:4X

SOLDER PASTE EXAMPLE

PCB CLEARANCE & CREEPAGE OPTIMIZED

BASED ON 0.125 mm THICK STENCIL

SCALE:4X

4224743/A 01/2019

NOTES: (continued)

7. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

8. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月