Sample &

🖥 Buy

Software Community

20

# UCC29950

JAJSC35A – SEPTEMBER 2014 – REVISED MARCH 2015

# UCC29950 CCM PFC および LLC コンボ・コントローラ

Technical

Documents

# 1 特長

- 高効率 PFC およびハーフ・ブリッジ共振 LLC コ ンボ・コントローラ

- 連続導通モード(CCM)の昇圧 PFC(力率補 正)

- 自己バイアスまたは補助(外部)バイアス・モードの動作をサポート

- PFC ループによる全面的な内部補正

- PFC 段の設計を3つの簡単なステップで実施 (電圧フィードバック、電流フィードバック、パ ワー段の各設計)

- 100kHz 固定の PFC 周波数で、EMI 準拠を容易に するディザリング機能対応

- ライン電圧から独立した、真の入力電力制限

- 70kHz ~ 350kHz の動作範囲内での固定 LLC 周 波数

- LLC ハーフ・ブリッジ・パワー段の負荷範囲にわたってデッドタイムを変化させることにより、 ZVS 範囲を拡大

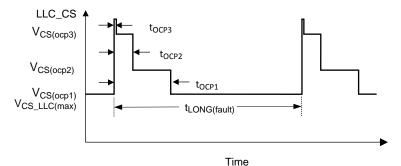

- 3 レベルの LLC 過電流保護

- 連続的な過負荷保護/短絡保護用のヒカップ・モー ド動作

- 高耐圧スタートアップ MOSFET のアクティブ制 御と X-Cap 放電機能によって実現する低スタンバ イ電力消費

- ソフトスタート機能とコンバータ・シーケンス機 能を内蔵し設計を簡素化

- AC ライン・ブラウンアウト保護、異常インジ ケータ付き

- PFC バス過電圧および低電圧保護

- 過熱保護

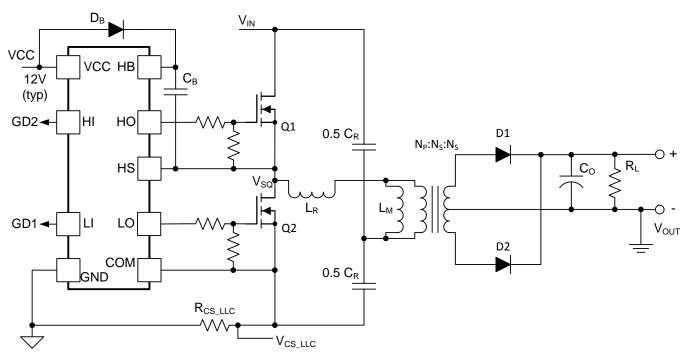

- 電力レベル拡張用外部ゲート・ドライバ

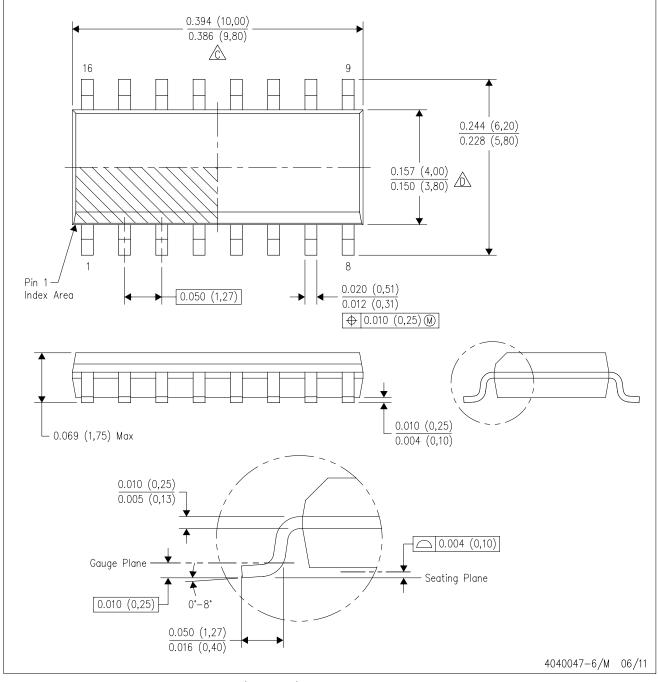

- SOIC-16パッケージ

# 2 アプリケーション

Tools &

- オフライン AC/DC サーバ電源(80 PLUS<sup>®</sup> Bronze/Silver/Gold)

- 産業用 DIN レールおよびオープンフレーム電源

Support &

- ゲーム用およびプリンタ用電源

- 高密度アダプタ

- 照明用ドライバ

# 3 概要

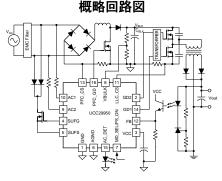

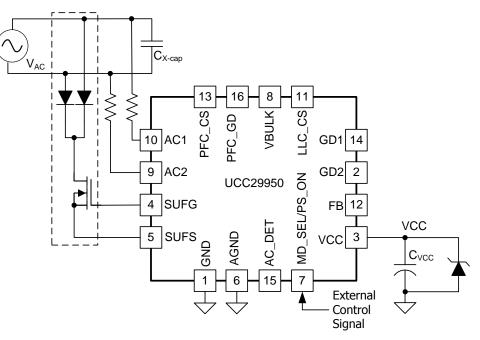

UCC29950 は、CCM 昇圧力率補正(PFC) 段と LLC コ ンバータ段を使用して、AC/DC コンバータのあらゆる制御 機能を実現できます。コントローラは使いやすく最適化さ れています。

独自の CCM PFC アルゴリズムによって、高効率の小型 コンバータ・システムで高力率を達成します。内蔵 LLC コ ントローラでソフトスイッチングを行うことにより、低 EMI ノイ ズで高効率 DC/DC 変換段を実現します。PFC 制御と LLC 制御をコンボ・コントローラに統合し、両段の情報を 利用する制御アルゴリズムが可能です。

このコントローラは、Depletion モード MOSFET を使用す るスタートアップ用制御回路を内蔵しており、内部デバイス 電力管理によって、外付け部品を最小限にしてシステム 実装コストを低減します。

スタンバイ電力をさらに低減するために、X-Cap 放電回路 を内蔵しています。UCC29950 は、AC ライン・ブラウンア ウト、PFC バス低電圧 PFC および LLC、過電流および サーマル・シャットダウンなどのシステム保護機能をすべて 備えています。

|          | 製品情報 <sup>(1)</sup> |               |

|----------|---------------------|---------------|

| 型番       | パッケージ               | 本体サイズ(公称)     |

| UCC29950 | SOIC 16 ピン(D)       | 9.90mm×6.00mm |

(1) 提供されているすべてのパッケージについては、巻末の注文情報 を参照してください。

# LLC 段の過電流保護プロファイル

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、www.ti.comで閲覧でき、その内 容が常に優先されます。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず最新版の英語版をご参照くださいますようお願いいたします。 English Data Sheet: SLUSC18 JAJSC35A – SEPTEMBER 2014 – REVISED MARCH 2015

# 目次

| _ |      |                                  |                |

|---|------|----------------------------------|----------------|

| 1 |      | Ę                                |                |

| 2 | アプ   | ゜リケーション                          | 1              |

| 3 | 概要   | ā<br>                            | 1              |

| 4 | 改訂   | 「履歴                              | 2              |

| 5 | Pin  | Configuration and Functions      | 3              |

|   | 5.1  | Detailed Pin Descriptions        | 4              |

| 6 | Spe  | cifications                      | 6              |

|   | 6.1  | Absolute Maximum Ratings         | <mark>6</mark> |

|   | 6.2  | Storage Conditions               |                |

|   | 6.3  | ESD Ratings                      | <mark>6</mark> |

|   | 6.4  | Recommended Operating Conditions |                |

|   | 6.5  | Thermal Information              | 7              |

|   | 6.6  | Electrical Characteristics       |                |

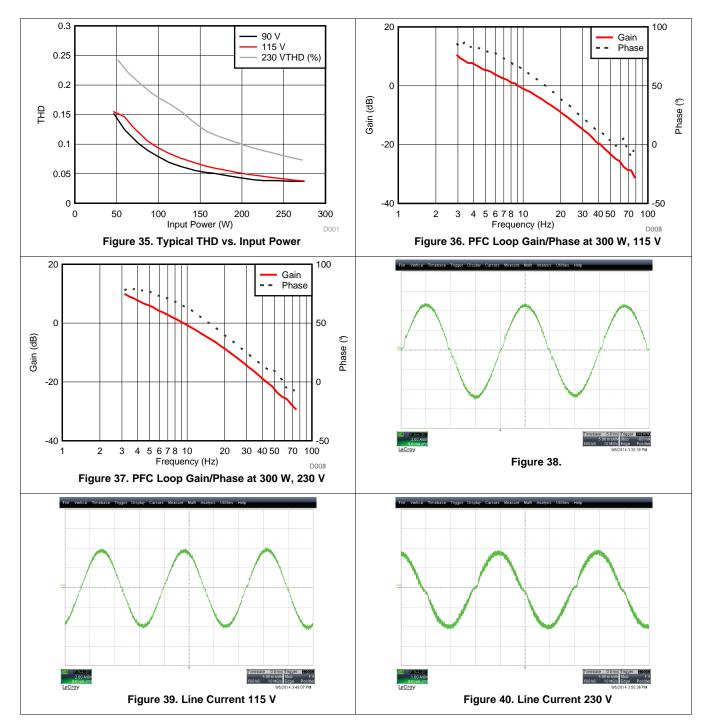

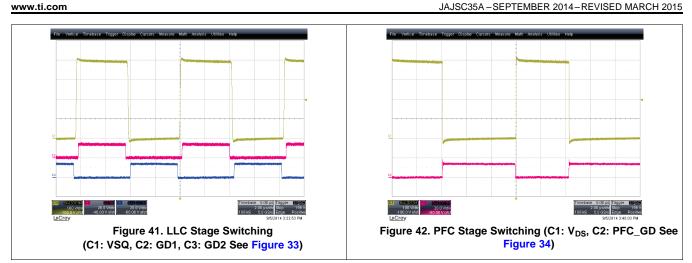

|   | 6.7  | Typical Characteristics          | 11             |

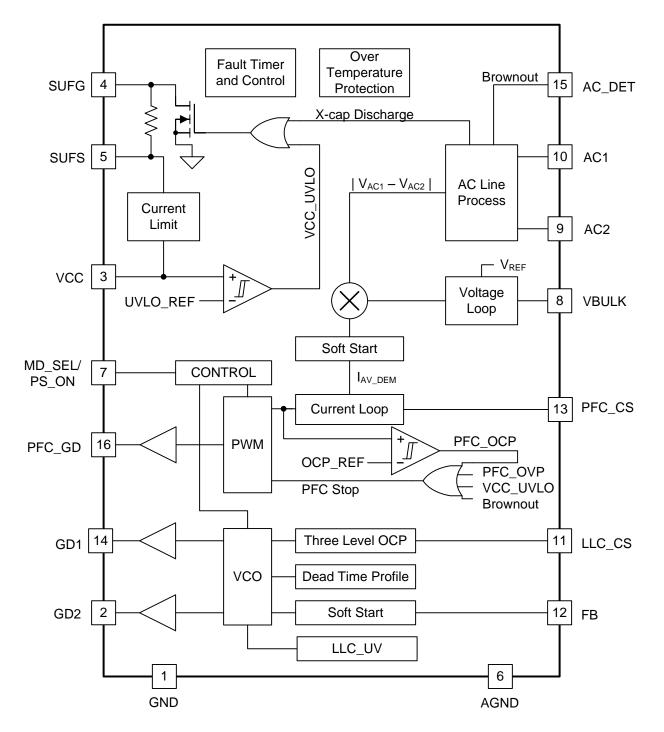

| 7 | Deta | ailed Description                | 13             |

|   | 7.1  | Overview                         | 13             |

|   | 7.2  | Functional Block Diagram         | 14             |

# 4 改訂履歴

### 2014年9月発行のものから更新

• マーケティング・ステータスをカスタムからカタログに変更......1

|    | 7.3  | Feature Description         | 15                 |

|----|------|-----------------------------|--------------------|

|    | 7.4  | Device Functional Modes     | 29                 |

| 8  | Арр  | lication and Implementation | . 36               |

|    | 8.1  | Application Information     | 36                 |

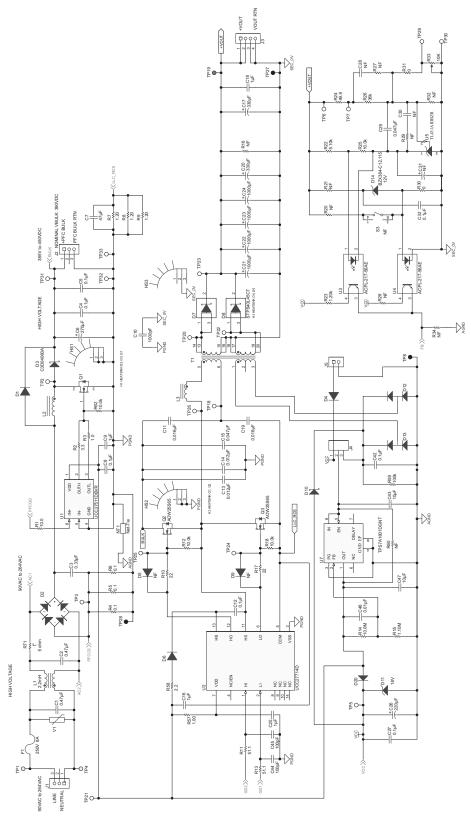

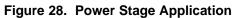

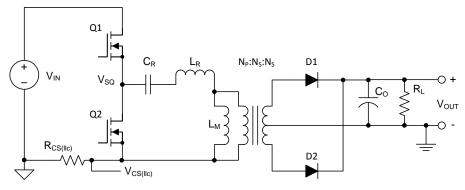

|    | 8.2  | Typical Application         | 36                 |

|    | 8.3  | Do's and Don'ts             | 57                 |

| 9  | Pow  | er Supply Recommendations   | . 58               |

| 10 | Lay  | out                         | . 59               |

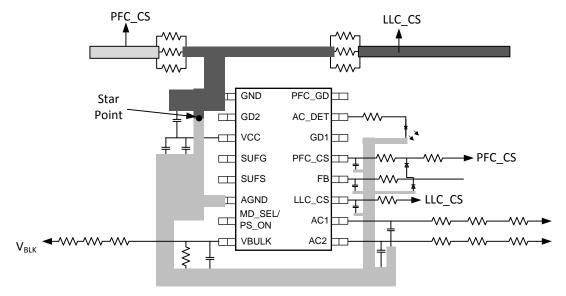

|    | 10.1 | Layout Guidelines           | 59                 |

|    | 10.2 | Layout Example              | 61                 |

| 11 | デバ   | イスおよびドキュメントのサポート            | . <mark>6</mark> 1 |

|    | 11.1 | ドキュメントのサポート                 | 61                 |

|    | 11.2 | 商標                          | 61                 |

|    | 11.3 | 静電気放電に関する注意事項               | <mark>61</mark>    |

|    | 11.4 | 用語集                         | <mark>6</mark> 1   |

| 12 | メカニ  | ニカル、パッケージ、および注文情報           | . <mark>6</mark> 1 |

|    |      |                             |                    |

### Texas Instruments

www.ti.com

Page

### UCC29950 JAJSC35A – SEPTEMBER 2014 – REVISED MARCH 2015

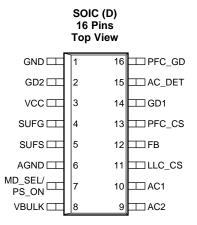

# 5 Pin Configuration and Functions

# **Pin Functions**

| P                | IN  | 1/0 | DESCRIPTION                                                                                                                                                                                                                           |  |

|------------------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME             | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                           |  |

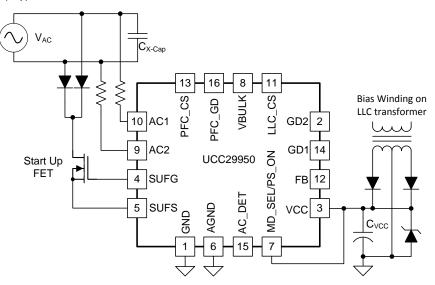

| GND              | 1   | -   | Power ground. Connect all the gate driver pulsating current returns to this pin.                                                                                                                                                      |  |

| GD2              | 2   | 0   | Gate drive output for LLC stage MOSFET. The typical peak current is 1-A source, 1.6-A sink $(C_{LOAD} = 1 \text{ nF})$                                                                                                                |  |

| VCC              | 3   | -   | Bias supply input.                                                                                                                                                                                                                    |  |

| SUFG             | 4   | 0   | Start-up MOSFET gate drive output. Leave open circuit if not used.                                                                                                                                                                    |  |

| SUFS             | 5   | I   | Start-up MOSFET Source. Connect to VCC if not used.                                                                                                                                                                                   |  |

| AGND             | 6   | -   | Signal ground. Connect all device control signal returns to this ground.                                                                                                                                                              |  |

| MD_SEL/PS_<br>ON | 7   | I   | <ul> <li>Dual function pin:</li> <li>1. Mode Select Function (MD_SEL): Select self bias or Aux bias mode of operation</li> <li>2. Power Supply On Function (PS_ON): Stop/start control of PFC and LLC stag Bias mode only.</li> </ul> |  |

| VBULK            | 8   | I   | Voltage sense input for PFC stage output.                                                                                                                                                                                             |  |

| AC2              | 9   | I   | AC line voltage detection. Connect 9.3 $M\Omega$ between AC line and this pin.                                                                                                                                                        |  |

| AC1              | 10  | I   | AC line voltage detection. Connect 9.3 M $\Omega$ between AC line and this pin.                                                                                                                                                       |  |

| LLC_CS           | 11  | I   | Current sense input for the LLC stage.                                                                                                                                                                                                |  |

| FB               | 12  | I   | Feedback signal input for LLC stage.                                                                                                                                                                                                  |  |

| PFC_CS           | 13  | I   | Current sense input for the PFC stage.                                                                                                                                                                                                |  |

| GD1              | 14  | 0   | Gate drive output for LLC stage MOSFET. The typical peak current is 1-A source, 1.6-A sink $(C_{LOAD} = 1 \text{ nF})$ .                                                                                                              |  |

| AC_DET           | 15  | 0   | AC line voltage fail signal output, for system use.                                                                                                                                                                                   |  |

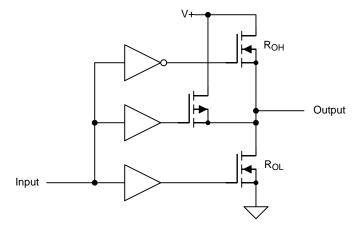

| PFC_GD           | 16  | 0   | The typical peak current is 0.6-A source, 1.3-A sink ( $C_{LOAD} = 1 \text{ nF}$ ).                                                                                                                                                   |  |

# 5.1 Detailed Pin Descriptions

# 5.1.1 VCC

The VCC pin is the power supply input terminal to the device. This pin should be decoupled with a 10-µF ceramic bypass capacitor in both Aux Bias and Self Bias Modes. An additional hold-up capacitor is needed at this pin if operating in Self Bias Mode.

# 5.1.2 MD\_SEL/PS\_ON

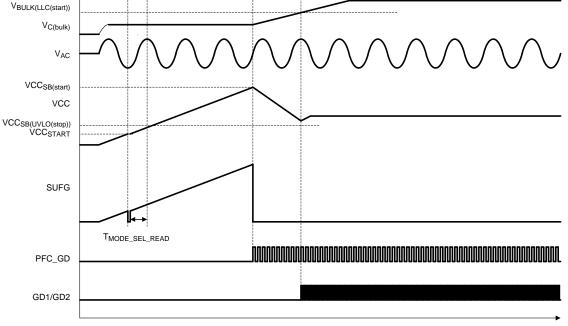

MD\_SEL/PS\_ON pin. This pin can be used to make the UCC29950 operate in Self Bias or Auxiliary Bias Mode. If MD\_SEL/PS\_ON pin is high during start up the controller enters Self Bias Mode. In this mode, the capacitor on the device's VCC rail is charged by an external depletion mode MOSFET connected at the SUFS and SUFG pins. Once the VCC rail reaches an appropriate operating voltage, the FET is turned off and the VCC rail is then supplied from an auxiliary winding on the LLC transformer. This avoids the standing or static losses incurred if a drop resistor from rectified AC line were used to charge the VCC rail during startup.

If the MD\_SEL/PS\_ON pin is held low for at least 10 ms during start up the UCC29950 enters Aux Bias Mode. Once this time has passed this pin may be used to turn on the PFC stage on its own or both the PFC and LLC stages according to the values given in the MD\_SEL/PS\_ON part of the Electrical Characteristics.

# 5.1.3 SUFG, SUFS

The SUFG and SUFS are the control pins for an external start-up depletion mode FET. The use of a switched device here eliminates the static power dissipation in a conventional resistive start-up approach where a drop resistor from the rectified AC line to VCC is typically used. As a result standby power consumption is reduced.

Connect the FET gate to SUFG and its source to SUFS. The drain of the FET is connected to the rectified AC voltage. SUFG and SUFS control the initial charging of the capacitor on the VCC rail during start-up in the Self-Bias mode of operation. In this mode SUFG tracks SUFS as  $C_{VCC}$  is charged and VCC rises. When VCC reaches VCC<sub>SB(start)</sub> (typically 16.2 V) SUFG goes low. This turns the start-up FET off and the PFC and LLC gate outputs start running. SUFG remains low unless VCC falls below VCC<sub>SB\_UVLO(stop)</sub> (typically 7.9 V) or an X-Cap discharge is required. If VCC falls below VCC<sub>SB\_UVLO(stop)</sub> then SUFG goes high to turn the start-up FET on and recharge  $C_{VCC}$  back up to VCC<sub>SB\_START</sub>.

SUFG and SUFS also provide an X-Cap discharge function in both Aux Bias and Self Bias Modes. This function is described fully in Active X-Cap Discharge.

If the UCC29950 is used in Aux Bias Mode then VCC is supplied by an external source and the external depletion mode FET is used only to provide the X-Cap discharge function. SUFG is at 0 V after a time  $T_{MODE\_SEL\_READ}$  has elapsed during power up after  $C_{VCC}$  exceeds VCC<sub>START</sub>. SUFG goes high whenever an X-Cap discharge is required. If the start up FET is not used and X-Cap discharge is not desired then SUFS should be connected to VCC and SUFG should be left open circuit.

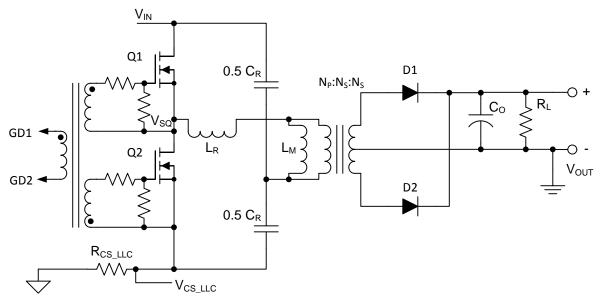

# 5.1.4 GD1, GD2

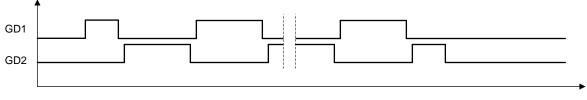

GD1 and GD2 are the LLC gate drive outputs for the LLC half-bridge power MOSFETs. A gate drive transformer or other suitable device is required to generate a floating drive for the high-side MOSFET. The first and last LLC gate drive pulses are normally half width and appear on GD1 and GD2 respectively. If the LLC\_OCP3 level is exceeded then the final pulse is of normal width. The typical peak current is 1-A source, 1.6-A sink (1-nF load).

# **Detailed Pin Descriptions (continued)**

# 5.1.5 GND

GND is the power ground for the device. Connect all the gate-driver pulsating current returns to this pin.

# 5.1.6 AGND

AGND is the signal ground for device control signals. Connect all control signal returns to this pin.

# 5.1.7 LLC\_CS

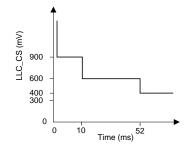

LLC\_CS is the LLC stage current sense input. LLC\_CS is used for LLC stage over-load protection. The load current is reflected to the primary side of the transformer where it is sensed using a resistor. The UCC29950 senses the LLC stage input current level and enters the over-current protection Shut-Down Mode when the current-sense signal exceeds the current and time thresholds described in LLC Three Level Over-Current Protection . The controller tries to resume operation at 1-s intervals.

# 5.1.8 FB

FB is the LLC stage control-loop feedback input. Connect the opto-coupler emitter to this pin. The FB pin is the input to the internal VCO. The VCO generates the switching frequency of the LLC converter. GD1 and GD2 stop switching if this pin is driven above  $V_{FB\_LLC(off)}$  (typically 3.75 V) and resume operation when it falls below  $V_{FB(max)}$  (typically 3.0 V). If this pin is held below  $V_{FB(min)}$  (typically 200 mV) the GD1 and GD2 outputs runs at their minimum frequency.

# 5.1.9 PFC\_GD

PFC\_GD is the gate-driver output for a PFC MOSFET. Connect the PFC MOSFET gate through a resistor to control its switching speed. Because of the limited driving capability an external gate driver might be needed to support certain power MOSFET input capacitance conditions. The typical peak current is 0.6-A source, 1.3-A sink ( $C_{LOAD} = 1 \text{ nF}$ ).

# 5.1.10 PFC\_CS

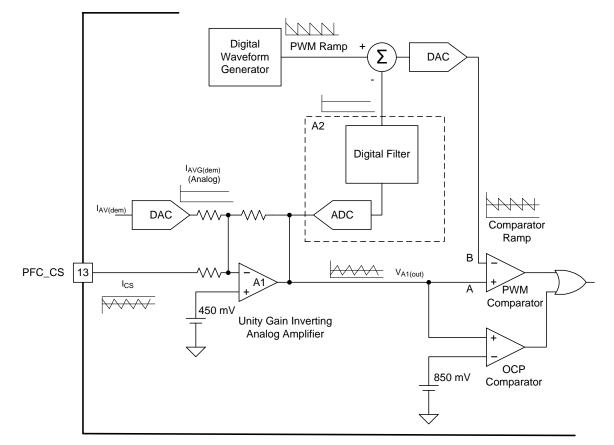

PFC\_CS is the current sense input for the PFC stage. It is recommended to add a current-limiting resistor between the current-sense resistor and current-sense pin, to prevent damage during inrush conditions. A 1-k $\Omega$  resistor normally suffices. The UCC29950 implements a new hybrid average current-control method which controls the average current but uses the peak PFC\_CS signal to terminate each switching cycle (see Hybrid PFC Control Loop). Correct PCB layout is important to ensure that the signal at this pin is an accurate representation of the current being controlled.

### 5.1.11 VBULK

The VBULK pin is used for PFC output-voltage sensing. Connect the sensing resistors to this pin. The upper resistor in the potential divider must be 30 M $\Omega$  and the lower resistor must be 73.3 k $\Omega$ . The high impedance reduces the static power dissipation.

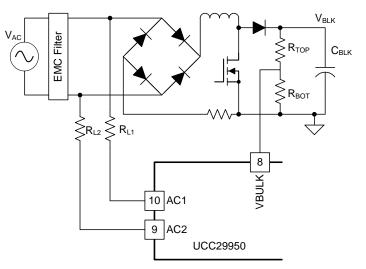

### 5.1.12 AC1, AC2

AC1 and AC2 are the AC line voltage sensing inputs. The UCC29950 uses differential sensing for more accurate measurement of line voltage. These pins must be connected to the two line inputs via 9.3-M $\Omega$  resistors.

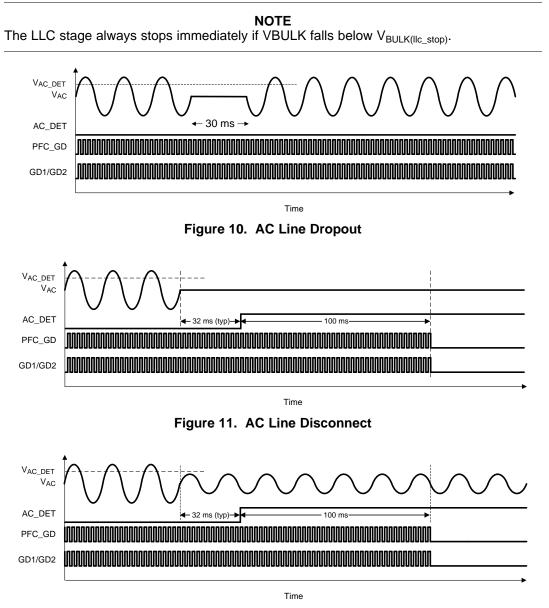

# 5.1.13 AC\_DET

The AC\_DET is a system-level signal which may be used for indication and system control. AC\_DET goes high if the instantaneous AC voltage remains below the brownout level for longer than 32 ms. An opto-coupler can be used to send a signal to a system supervisor device so that appropriate action can be taken. In order to provide hold-up time to the system, the power stages continue to operate for 100 ms after AC\_DET goes high. This behavior is shown in Figure 10, Figure 11 and Figure 12.

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                                   |                                   | MI                                                                                                                                                                                                                                                                                                          | N MAX      | UNIT |

|-----------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|

| Supply Voltage                    | VCC                               | -0.                                                                                                                                                                                                                                                                                                         | 3 20       | V    |

| Continuous Input<br>Voltage Range | LLC_CS                            | -0.                                                                                                                                                                                                                                                                                                         | 3 4.5      | V    |

| Voltage Range                     | FB, AC1, AC2, VBULK, MD_SEL/PS_ON | -0.3     20       -0.3     4.3       , VBULK, MD_SEL/PS_ON     -0.3     VCC-       0     4.3       -0.3     20       -0.3     20       -0.3     20       -0.3     20       -0.3     20       -0.3     20       -0.3     50       FC_GD     -0.5       -1.3     4.3       ±1     ±1       ture (10 s)     26 | 3 VCC+0.3  | V    |

|                                   | AC_DET                            | 0                                                                                                                                                                                                                                                                                                           | 4.5        | V    |

|                                   | SUFS                              | -0.                                                                                                                                                                                                                                                                                                         | 3 20       | V    |

|                                   | SUFG                              | -0.                                                                                                                                                                                                                                                                                                         | 3 SUFS+0.3 | V    |

|                                   | GD1, GD2, PFC_GD                  | -0.                                                                                                                                                                                                                                                                                                         | 5 VCC+0.5  | V    |

|                                   | PFC_CS                            | -1.                                                                                                                                                                                                                                                                                                         | 3 4.5      | V    |

| Continuous Input<br>Current Range | PFC_CS                            |                                                                                                                                                                                                                                                                                                             | ±15        | mA   |

| T <sub>SOL</sub>                  | Lead temperature (10 s)           |                                                                                                                                                                                                                                                                                                             | 260        | °C   |

| Operational Junction              | Temperature, T <sub>J</sub>       | -40                                                                                                                                                                                                                                                                                                         | ) 125      | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 Storage Conditions

|                  |                           | MIN | MAX | UNIT |  |

|------------------|---------------------------|-----|-----|------|--|

| T <sub>stg</sub> | Storage temperature range | -40 | 150 | °C   |  |

### 6.3 ESD Ratings

|                    |                         |                                                                          | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>        | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22- $C101^{(2)}$ | ±500  | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions.

# 6.4 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                           |                                | MIN | NOM MAX | UNIT |

|---------------------------|--------------------------------|-----|---------|------|

| VCC                       | Supply voltage range           | 11  | 18      | V    |

| V <sub>FB</sub>           | FB pin voltage range           | 0   | VCC     | V    |

| V <sub>MD_SEL/PS_ON</sub> | MD_SEL/PS_ON pin voltage range | 0   | VCC     | V    |

| RL1/RL2                   | Line sensing resistors         |     | 9.3     | MΩ   |

### 6.5 Thermal Information

|                       |                                              | UCC29950 |      |

|-----------------------|----------------------------------------------|----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | SOIC (D) | UNIT |

|                       |                                              | 16 PINS  |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 78.9     |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 40.3     |      |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 36.3     | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 8.9      |      |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 36.0     |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

JAJSC35A - SEPTEMBER 2014 - REVISED MARCH 2015

www.ti.com

STRUMENTS

EXAS

# 6.6 Electrical Characteristics

$-40^{\circ}$ C < T<sub>J</sub> < 125°C<sup>(1)</sup>, VCC = 12 V, all voltages are with respect to AGND (unless otherwise noted)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PARAMETER                                                                                                                                  | TEST CONDITIONS                                           | MIN  | TYP  | MAX  | UNIT |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------|------|------|------|

| VCC Bias Supply (Self Bias Mode)IsyrsCharging current into $V_{CC}$ SUFS = 7.5 V, VCC = 4 V-1-2-4mmVCC_SB(BMR)1In Self Bias mode, the controller will not start PFC and LLC gate drive outputs unlit the start up per this levelMD_SEL/PS_ON = VCC at power-up (self bias mode)15.016.217.4VVCC_SB(BMR)1In Self Bias mode, VCC must be greater than this level to allow the controller to continue to output the PFC and LLC gate drives.VCC failing Self Bias Mode7.37.98.5VCC Bias Supply (Aux Bias Mode)VCC rust be greater than this level to allow the controller to continue to output the PFC and LLC gate drives.VCC failing3.75.05.8VCC_STORTController logic starts at this VCC voltageVCC raising MD_SEL/PS_ON = 0 V at power-up (Aux Bias Mode, VCC must be greater than this level to allow the controller to continue to output the PFC and LLC gate drives.VCC failing Aux Bias Mode9.19.610.0VCC_AB_UVLO(INTER)In Aux Bias Mode, VCC must be greater than this level to allow the controller to continue to output the PFC and LLC gate drives.VCC failing Aux Bias Mode9.19.610.0VCC_AB_UVLO(INTER)In Aux Bias Mode, VCC must be greater than this level to allow the controller to continue to output the PFC_GD and PFC_GD pins unloaded.10mmMIDITELPYS_ON Foundaria Modes).After VCC pin exceeds VCC_START. This is the minimum time that the MD_SEL/PS_ON pin that causes PFC stage to run <sup>(3)</sup> < |                                                                                                                                            |                                                           |      |      |      |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                            | SUFS = 7.5 V, VCC = 4 V                                   | -1   | -2   | -4   | mA   |

| VCC <sub>SB(start)</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PFC and LLC gate drive outputs until the start up FET has charged the capacitance on the VCC                                               |                                                           | 15.0 | 16.2 | 17.4 | V    |

| VCC <sub>SB_UVLO(stop)</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | level to allow the controller to continue to output                                                                                        | VCC falling Self Bias Mode                                | 7.3  | 7.9  | 8.5  |      |

| VCC Bias Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | y (Aux Bias Mode)                                                                                                                          |                                                           |      |      | 1    |      |

| VCC <sub>START</sub> <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Controller logic starts at this VCC voltage                                                                                                | VCC rising                                                | 4.4  | 6    | 7.0  |      |

| VCC <sub>STOP</sub> <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Controller logic stops at this VCC voltage                                                                                                 | VCC falling                                               | 3.7  | 5.0  | 5.8  |      |

| VCC <sub>AB_UVLO(start</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | level to allow the controller to start the PFC and                                                                                         | = 0 V at power-up (Aux Bias                               | 10.0 | 10.5 | 10.9 | V    |

| VCC <sub>AB_UVLO(stop)</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | level to allow the controller to continue to output                                                                                        | VCC falling Aux Bias Mode                                 | 9.1  | 9.6  | 10.0 |      |

| VCC Supply Cur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | rent                                                                                                                                       |                                                           |      |      |      |      |

| ICC <sub>ENABLE</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                            | PFC_GD at f <sub>PFC</sub> (100 kHz<br>nom). GD1, GD2 and | 7.5  | 8.0  | 18.3 | mA   |

| MD_SEL/PS_ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | , Mode Select Function at Power Up                                                                                                         | + ł                                                       |      |      |      |      |

| V <sub>MODE_SELSB</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | that will select Self Bias mode on power up (see                                                                                           |                                                           | 1.1  | 1.6  | 2.1  | V    |

| T <sub>MODE_SEL_READ</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | minimum time that the MD_SEL/PS_ON pin must remain below $V_{MODE\_SELSB}$ to ensure that Aux Bias Mode is selected (see Device Functional |                                                           | 10   |      |      | ms   |

| MD_SEL/PS_ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | , Power Supply On Function, Aux Bias Mode On                                                                                               | ly                                                        |      |      |      |      |

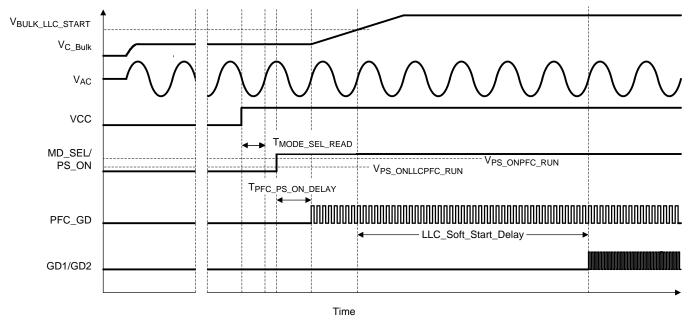

| V <sub>PS_ONPFC_RUN</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Minimum voltage on the MD_SEL/PS_ON pin that causes PFC stage to run <sup>(3)</sup>                                                        |                                                           | 20   | 25   | 33   | %VCC |

| V <sub>PS_ONLLCPFC_R</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                            |                                                           | 66   | 75   | 85   | %VCC |

| AC_DET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                            |                                                           |      |      |      |      |

| V <sub>OH_TP_LZ</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | AC_DET output high                                                                                                                         | $I_{(AC_{DET})} = -1 \text{ mA}$                          | 2.5  | 3.1  | 4.1  | V    |

| V <sub>OL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | AC_DET output low                                                                                                                          | $I_{(AC_{DET})} = 1 \text{ mA}$                           | 19   | 35   | 80   | mV   |

| I <sub>O(max_source)</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | AC_DET source current                                                                                                                      | V <sub>OUT</sub> > 2.4 V                                  |      |      | -1.6 | mA   |

| I <sub>O(max_sink)</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | AC_DET sink current                                                                                                                        | V <sub>OUT</sub> < 0.5 V                                  |      |      | 6.0  | mA   |

The device has been characterized over the entire temperature range during development. Individual devices may enter temperature shutdown ( $T_{SD}$ ) at  $T_J$  lower than 125°C. (1)

(2) VCC<sub>START</sub> is always greater than VCC<sub>STOP</sub>.

(3) Threshold voltage will track VCC and is therefore specified as a percentage of VCC.

# **Electrical Characteristics (continued)**

$-40^{\circ}$ C < T<sub>J</sub> < 125°C<sup>(1)</sup>, VCC = 12 V, all voltages are with respect to AGND (unless otherwise noted)

|                                        | PARAMETER                                                                                                                                                                                                                 | TEST CONDITIONS                                                                                      | MIN   | TYP   | MAX   | UNIT              |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------|-------|-------|-------------------|

| VBULK, PFC OU                          | ITPUT VOLTAGE                                                                                                                                                                                                             |                                                                                                      |       |       |       |                   |

| V <sub>BULK(ovp)</sub>                 | PFC output overvoltage protection (auto recovery)                                                                                                                                                                         |                                                                                                      | 1.06  | 1.10  | 1.14  | V                 |

| V <sub>BULK(reg)</sub>                 | V <sub>BULK</sub> regulation set-point                                                                                                                                                                                    |                                                                                                      | 0.907 | 0.940 | 0.973 | V                 |

| V <sub>BULK(IIc_start)</sub>           | LLC operation start threshold                                                                                                                                                                                             |                                                                                                      | 0.70  | 0.73  | 0.77  | V                 |

| V <sub>BULK(IIc_stop)</sub>            | LLC operation stop threshold                                                                                                                                                                                              |                                                                                                      | 0.45  | 0.49  | 0.53  | V                 |

| AC1, AC2, AC LI                        | INE SENSING FOR PFC                                                                                                                                                                                                       |                                                                                                      |       |       |       |                   |

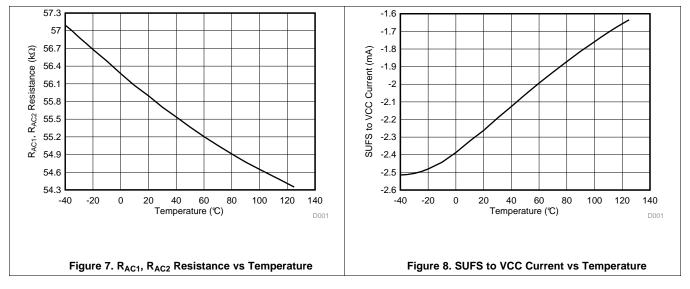

| R <sub>AC1</sub>                       | AC1 pin resistance to AGND                                                                                                                                                                                                | AC1 pin                                                                                              | 45    | 60    | 71    | 1.0               |

| R <sub>AC2</sub>                       | AC2 pin resistance to AGND                                                                                                                                                                                                | AC2 pin                                                                                              | 45    | 60    | 71    | kΩ                |

| I <sub>AC(det)</sub> <sup>(4)(5)</sup> | AC_DET is active HIGH when ${\rm I}_{\rm AC}$ is below this level                                                                                                                                                         | Force current into AC1 or<br>AC2 pins. Unused pin input<br>at 0 V.                                   | 7.03  | 7.48  | 7.93  |                   |

| $I_{AC(low_falling)}^{(4)(5)}$         | PFC stage stops 100 ms after $I_{AC}$ is at or below this level                                                                                                                                                           | Force current into AC1 or<br>AC2 pins. Unused pin input<br>at 0 V.                                   | 7.03  | 7.48  | 7.93  | μA <sub>RMS</sub> |

| $I_{AC(low_rising)}^{(4)(5)}$          | PFC stage is allowed to start when $I_{AC}$ is at or above this level                                                                                                                                                     | Force current into AC1 or<br>AC2 pins. Unused pin input<br>at 0 V.                                   | 8.04  | 8.55  | 9.1   |                   |

| AC(high_falling) <sup>(4)(5</sup>      | PFC stage restarts if $I_{\text{AC}}$ falls below this level. No soft-start                                                                                                                                               | Force current into AC1 or<br>AC2 pins. Unused pin input<br>at 0 V.                                   | 30.7  | 32.0  | 33.3  |                   |

| $I_{AC(high\_rising)}^{(4)(5)}$        | PFC stage stops if $I_{AC}$ is at or above this level                                                                                                                                                                     | Force current into AC1 or<br>AC2 pins. Unused pin input<br>at 0 V.                                   | 31.8  | 33.1  | 34.4  |                   |

| $I_{AC(halt)}^{(4)(5)}$                | PFC and LLC stages stop if $I_{AC}$ is at or above this level                                                                                                                                                             | Force current into AC1 or<br>AC2 pins. Unused pin input<br>at 0 V.                                   | 32.8  | 34.2  | 35.6  |                   |

| PFC_CS, PFC C                          | URRENT SENSE                                                                                                                                                                                                              |                                                                                                      |       |       |       |                   |

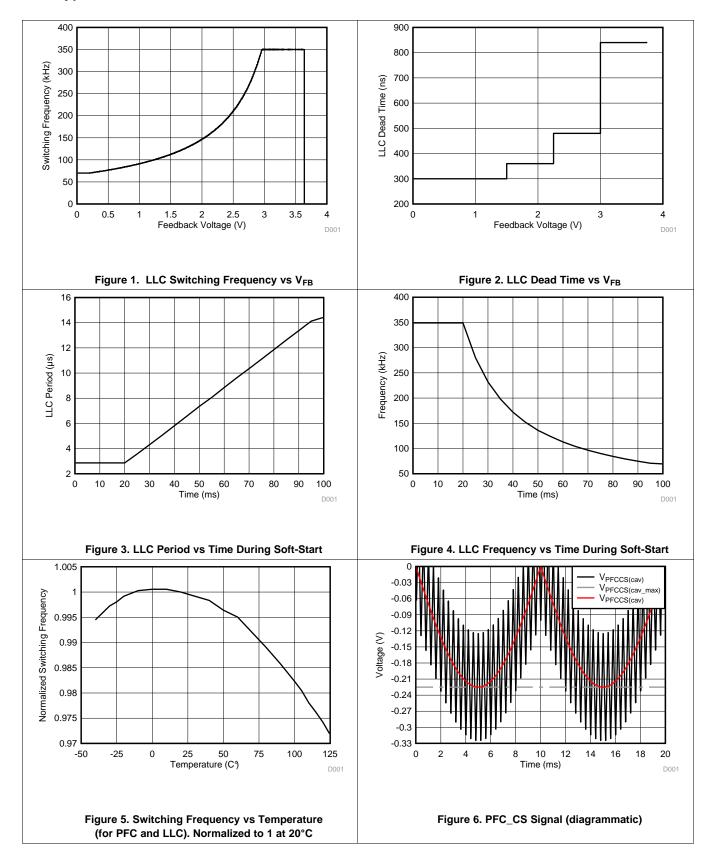

| V <sub>PFCCS(cav_max)</sub>            | Maximum voltage at PFC_CS pin, (ignoring signal ripple due to inductor ripple current) that determines maximum power delivered. Used to determine $R_{CS_{PFC}}$ . (see PFC Stage Current Sensing Figure 13 and Figure 6) |                                                                                                      | -200  | -225  | -250  | mV                |

| V <sub>PFCCS(max)</sub>                | Maximum voltage at PFC_CS pin                                                                                                                                                                                             | $\begin{array}{l} VBULK \ pin = 800 \ mV, \\  V_{AC1} - V_{AC2}  = V_{AC\_PEAK}{}^{(6)} \end{array}$ | -570  | -800  | -950  |                   |

| PFC_GD, PFC G                          | ATE DRIVER                                                                                                                                                                                                                |                                                                                                      |       |       | ,     |                   |

| V <sub>HI(pfc_2mA)</sub>               | PFC_GD high level                                                                                                                                                                                                         | $I_{O(PFC_GD)} = -2 \text{ mA}$                                                                      | 11.5  | 11.8  | 12.0  | V                 |

| V <sub>HI(pfc_75mA)</sub>              | PFC_GD high level                                                                                                                                                                                                         | $I_{O(PFC\_GD)} = -75 \text{ mA}$                                                                    | 8.5   | 9.5   | 10.5  | v                 |

| R <sub>PFC(gd_hi)</sub>                | PFC_GD pull-up resistance                                                                                                                                                                                                 | $I_{O(PFC\_GD)} = -50 \text{ mA}$                                                                    |       | 14    | 25    | Ω                 |

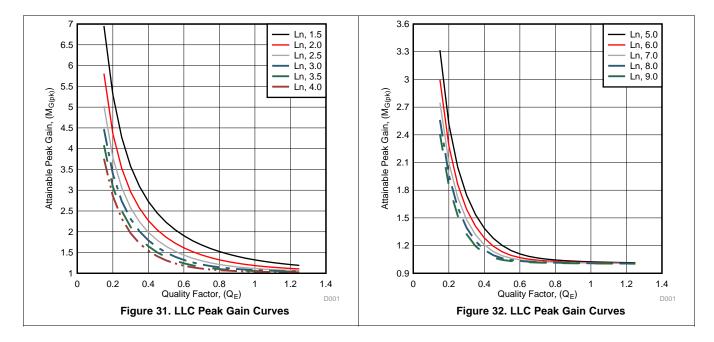

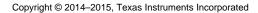

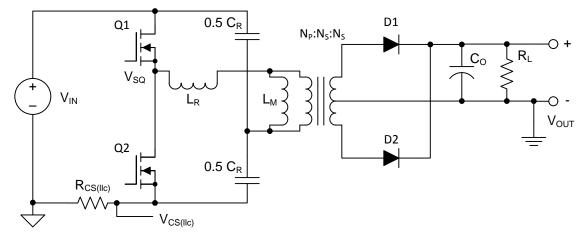

| R <sub>PFC(gd_lo)</sub>                | PFC_GD pull-down resistance                                                                                                                                                                                               | I <sub>O(PFC_GD)</sub> = 75 mA                                                                       |       | 4.4   | 10    | 12                |