UCC28881 SLUSC36B - NOVEMBER 2015 - REVISED JANUARY 2016

# UCC28881 700-V, 225-mA Low Quiescent Current Off-Line Converter

## **Features**

- Integrated 14-Ω, 700-V Power MOSFET

- Integrated High-Voltage Current Source for Internal Device Bias Power

- Integrated Current Sense

- Internal Soft Start

- Self-Biased Switcher (Start Up and Operation Directly from Rectified Mains Voltage)

- Supports Buck, Buck-Boost and Flyback **Topologies**

- <100-µA Device Quiescent Current

- Robust Current Protection During Load Short Circuit

- Protection

- Current Limit

- Overload and Output Short Circuit

- Over Temperature

# 2 Applications

- AC-to-DC Power Supplies (Non-Isolated Buck Converter with Output Current up to 225 mA for CCM; 150 mA for DCM)

- E-Meter, Home Automation SMPS

- Bias Power for MCU, RF and IoT Enabled Devices

- Appliances, White Goods and LED Drivers

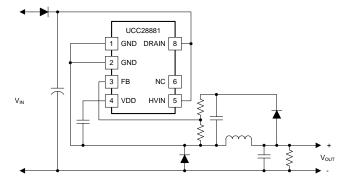

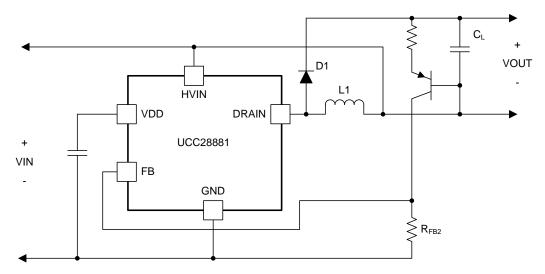

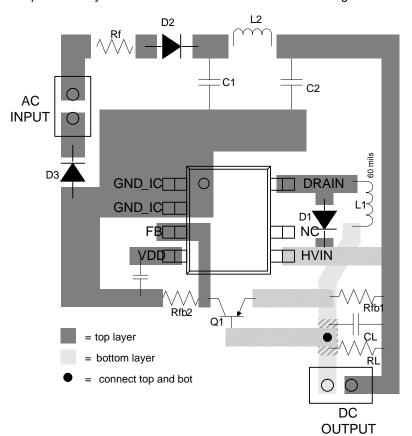

### Simplified Schematic

# 3 Description

The UCC28881 integrates the controller and a  $14-\Omega$ , 700-V power MOSFET into one monolithic device. The device also integrates a high-voltage current source, enabling start up and operation directly from the rectified mains voltage. UCC28881 is the same family device of UCC28880, with higher current handling capability.

The low quiescent current of the device enables excellent efficiency. With the UCC28881 the most common converter topologies, such as buck, buckboost and flyback can be built using a minimum number of external components.

The UCC28881 incorporates a soft-start feature for controlled start up of the power stage which minimizes the stress on the power-stage components.

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE  | BODY SIZE (NOM)   |

|-------------|----------|-------------------|

| UCC28881    | SOIC (7) | 5.00 mm × 6.20 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

# **Table of Contents**

| 1 | Features                             | 1   | 8.3 Feature Description              | 10 |

|---|--------------------------------------|-----|--------------------------------------|----|

| 2 | Applications                         | 1   | 8.4 Device Functional Modes          | 12 |

| 3 | Description                          | 1 9 | Application and Implementation       | 16 |

| 4 | Revision History                     |     | 9.1 Application Information          | 16 |

| 5 | Device Comparison                    |     | 9.2 Typical Application              | 16 |

| 6 | Pin Configuration and Functions      | 40  | Power Supply Recommendations         | 26 |

| 7 | Specifications                       | 11  | Layout                               | 26 |

| • | 7.1 Absolute Maximum Ratings         |     | 11.1 Layout Guidelines               | 26 |

|   | 7.2 ESD Ratings                      |     | 11.2 Layout Example                  | 26 |

|   | 7.3 Recommended Operating Conditions | 40  | Device and Documentation Support     | 27 |

|   | 7.4 Thermal Information              |     | 12.1 Device Support                  | 27 |

|   | 7.5 Electrical Characteristics       |     | 12.2 Community Resources             | 27 |

|   | 7.6 Switching Characteristics        |     | 12.3 Trademarks                      | 27 |

|   | 7.7 Typical Characteristics          |     | 12.4 Electrostatic Discharge Caution | 27 |

| 8 | Detailed Description                 |     | 12.5 Glossary                        | 27 |

| • | 8.1 Overview                         | 42  | Mechanical, Packaging, and Orderable | 27 |

|   | 8.2 Functional Block Diagram         | 9   | Information                          | 21 |

|   |                                      |     |                                      |    |

# 4 Revision History

| CI | hanges from Revision A (December 2015) to Revision B                                                                                                                      | Page |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Changed the documents title from, "UCC28881 700-V, 225-mA Low Quiescent Current Off-Line Switcher", to "UCC28881 700-V, 225-mA Low Quiescent Current Off-Line Converter". | 1    |

| CI | hanges from Original (November 2015) to Revision A                                                                                                                        | Page |

| •  | Changed marketing status from product preview to production data.                                                                                                         | 1    |

# 5 Device Comparison

# **Power Handling Capability with Different Topologies**

| PRODUCT  | MAXIMUM OUTPUT CURRENT<br>for 85 ~ 265 VAC OPEN FRAME DESIGN | MAXIMUM OUTPUT POWER<br>for 85 ~ 265 VAC OPEN FRAME DESIGN |

|----------|--------------------------------------------------------------|------------------------------------------------------------|

|          | NON-ISOLATED BUCK                                            | FLYBACK                                                    |

| UCC28880 | 100 mA                                                       | 3 W                                                        |

| UCC28881 | 225 mA                                                       | 4.5 W                                                      |

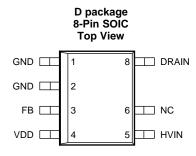

# 6 Pin Configuration and Functions

### **Pin Functions**

|       | PIN | 1/0 | DESCRIPTION                                    |  |

|-------|-----|-----|------------------------------------------------|--|

| NAME  | NO. | 1/0 | DESCRIPTION                                    |  |

| DRAIN | 8   | Р   | Drain pin                                      |  |

| FB    | 3   | I   | Feedback terminal                              |  |

| GND   | 1   | G   | Ground                                         |  |

| GND   | 2   | G   | Ground                                         |  |

| HVIN  | 5   | Р   | Supply pin                                     |  |

| NC    | 6   | N/C | Not internally connected                       |  |

| VDD   | 4   | 0   | Supply pin, supply is provided by internal LDO |  |

# 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)  $^{(1)}$   $^{(2)}$   $^{(3)}$

|                    |                                                               | MIN                | MAX                | UNIT |

|--------------------|---------------------------------------------------------------|--------------------|--------------------|------|

| HVIN               |                                                               | -0.3               | 700 (4)            | V    |

| DRAIN              |                                                               | Internally clamped | 700 (4)            | V    |

| I <sub>DRAIN</sub> | Positive drain current single pulse, pulse max duration 25 µs |                    | 770 <sup>(5)</sup> | mA   |

| I <sub>DRAIN</sub> | Negative drain current                                        | -700               |                    | mA   |

| FB                 |                                                               | -0.3               | 6                  | V    |

| VDD                | VDD is supplied from low impedance source                     | -0.3               | 6                  | V    |

| I <sub>VDD</sub>   | VDD is supplied from high impedance source                    |                    | 400                | μA   |

| TJ                 | Junction temperature                                          |                    | 150                | °C   |

|                    | Lead temperature 1.6 mm (1/16 inch) from case 10 seconds      |                    | 260                | °C   |

| T <sub>stg</sub>   | Storage temperature range                                     | -65                | 150                | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(3) The device is not rated to withstand operating conditions when multiple parameters are at or near, absolute maximum ratings.

### 7.2 ESD Ratings

|                                            |                                                                 |                                                                                       |       | UNIT |

|--------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------|-------|------|

|                                            |                                                                 | Human Body Model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins except HVIN pin $^{(1)}$ | ±2000 | V    |

| V <sub>(ESD)</sub> Electrostatic discharge | Human Body Model (HBM) per ANSI/ESDA/JEDEC JS-001, HVIN pin (1) | ±1500                                                                                 | V     |      |

|                                            |                                                                 | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins $^{(2)}$    | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> All voltages are with respect to GND. Currents are positive into, negative out of the specified terminal. These ratings apply over the operating ambient temperature ranges unless otherwise noted.

<sup>(4)</sup>  $T_A = 25^{\circ}C$

<sup>(5)</sup> The MOSFET drain to source voltage is less than 400V

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                | MIN  | NOM | MAX  | UNIT |

|----------------|--------------------------------|------|-----|------|------|

| $V_{VDD}$      | Voltage On VDD pin             |      | 5   |      | V    |

| $V_{FB}$       | Voltage on FB pin              | -0.2 |     | 5    | V    |

| T <sub>J</sub> | Operating junction temperature | -40  |     | +125 | °C   |

# 7.4 Thermal Information

|                      |                                              | UCC28881 |      |

|----------------------|----------------------------------------------|----------|------|

|                      | THERMAL METRIC (1)                           | D (SOIC) | UNIT |

|                      |                                              | 7 PINS   |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 134.4    | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 42.6     | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 85       | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 6.4      | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 76       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

# 7.5 Electrical Characteristics

$V_{HVIN} = 30 \text{ V}, T_A = T_J = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C} \text{ (unless otherwise noted)}$

|                            | PARAMETER                                                              | TEST CONDITIONS                                                                 | MIN   | TYP   | MAX   | UNIT |

|----------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------|-------|-------|------|

| V <sub>HVIN(min)</sub>     | Minimum Voltage to start-up                                            |                                                                                 |       |       | 30    | V    |

| I <sub>NL</sub>            | Internal supply current, no load                                       | FB = 1.25 V (> V <sub>FB_TH</sub> )                                             |       | 58    | 100   | μΑ   |

| I <sub>FL</sub>            | Internal supply current, full load                                     | FB = 0.75 V (> V <sub>FB_TH</sub> )                                             |       | 86    | 120   | μΑ   |

| I <sub>CH0</sub>           | Charging VDD Cap current                                               | V <sub>VDD</sub> = 0 V,                                                         | -3.8  | -1.6  | -0.4  | mA   |

| I <sub>CH1</sub>           | Charging VDD Cap current                                               | $V_{VDD} = 4.4V, V_{FB} = 1.25 V$                                               | -3.40 | -1.30 | -0.25 | mA   |

| $V_{VDD}$                  | Internally regulated low<br>Voltage supply (supplied from<br>HVIN pin) |                                                                                 | 4.5   | 5.0   | 5.5   | V    |

| $V_{FB\_TH}$               | FB pin reference threshold                                             |                                                                                 | 0.96  | 1.03  | 1.105 | V    |

| V <sub>VDD(on)</sub>       | VDD turn-on threshold                                                  | VDD low-to-high                                                                 | 3.55  | 3.92  | 4.28  | V    |

| $V_{VDD(off)}$             | VDD turn-off threshold                                                 | VDD high-to-low                                                                 | 3.28  | 3.62  | 3.89  | V    |

| $\Delta V_{VDD(uvlo)}$     | VDD UVLO Hysteresis                                                    | VDD high-to-low                                                                 | 0.27  | 0.345 | 0.39  | V    |

| D <sub>MAX</sub>           | Maximum Duty Cycle                                                     | FB = 0.75 V                                                                     | 45%   |       | 55%   |      |

|                            |                                                                        | Static, $T_A = -40^{\circ}C$                                                    |       |       | 630   | mA   |

| I <sub>LIMIT</sub>         | Current Limit                                                          | Static, T <sub>A</sub> = 25°C                                                   | 330   | 440   | 570   | mA   |

|                            |                                                                        | Static, T <sub>A</sub> = 125°C                                                  | 315   |       |       | mA   |

| $T_{J(stop)}$              | Thermal Shutdown Temperature                                           | Internal junction temperature                                                   |       | 138.5 | 150   | °C   |

| T <sub>J(hyst)</sub>       | Thermal Shutdown Hysteresis                                            | Internal junction temperature                                                   |       | 37.   | 45    | °C   |

| BV                         | Power MOSFET Breakdown<br>Voltage                                      | T <sub>J</sub> = 25°C                                                           | 700   |       |       | V    |

|                            | Power MOSFET On-                                                       | $I_D = 60 \text{ mA}, T_J = 25^{\circ}\text{C}$                                 |       | 14    | 18    | Ω    |

| R <sub>DS(on)</sub>        | Resistance (includes internal sense-resistor)                          | I <sub>D</sub> = 60 mA, T <sub>J</sub> = 125°C                                  |       | 24    | 30    | Ω    |

| DRAIN_I <sub>LEAKAGE</sub> | Power MOSFET off state                                                 | $V_{DRAIN} = 700V, T_{J} = 25^{\circ}C$                                         |       |       | 5     | μΑ   |

| DRAIN_ILEAKAGE             | leakage current                                                        | $V_{DRAIN} = 400 \text{ V}, T_{J} = 125^{\circ}\text{C}$                        |       |       | 20    | μΑ   |

|                            | HVIN off state current                                                 | $V_{HVIN} = 700 \text{ V}, T_{J} = 25^{\circ}\text{C}, V_{VDD} = 5.8 \text{ V}$ | 4.0   | 7.5   | 36.0  | μΑ   |

| HVIN_I <sub>OFF</sub>      | TIVIN OII State Culletit                                               | V <sub>HVIN</sub> = 400 V, T <sub>J</sub> = 125°C, V <sub>VDD</sub> = 5.8 V     |       |       | 20    | μΑ   |

| V <sub>VDD(clamp)</sub>    | VDD clamp voltage                                                      | I <sub>VDD</sub> = 250 μA                                                       | 6.0   | 6.7   | 7.5   | V    |

# 7.6 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

|                       |                                                                     | MIN  | TYP  | MAX  | UNIT |

|-----------------------|---------------------------------------------------------------------|------|------|------|------|

| f <sub>SW(max)</sub>  | Maximum switching frequency                                         | 52   | 62   | 75   | kHz  |

| t <sub>ON_MAX</sub>   | Maximum switch on time (current limiter not triggered), FB = 0.75 V | 6.5  | 8.3  | 9.7  | μs   |

| t <sub>OFF_MIN</sub>  | Minimum switch off time follows every $t_{ON}$ time, FB = 0.75 V    | 6.5  | 8.3  | 9.7  | μs   |

| t <sub>MIN</sub>      | Minimum on time                                                     | 0.17 | 0.27 | 0.30 | μs   |

| t <sub>OFF(ovl)</sub> | Max off time (OL condition), $t_{OFF(ovl)} = t_{SW} - t_{ON(max)}$  | 130  | 200  | 270  | μs   |

| t <sub>ON_TO</sub>    | Inductor current run away protection time threshold                 |      | 450  |      | ns   |

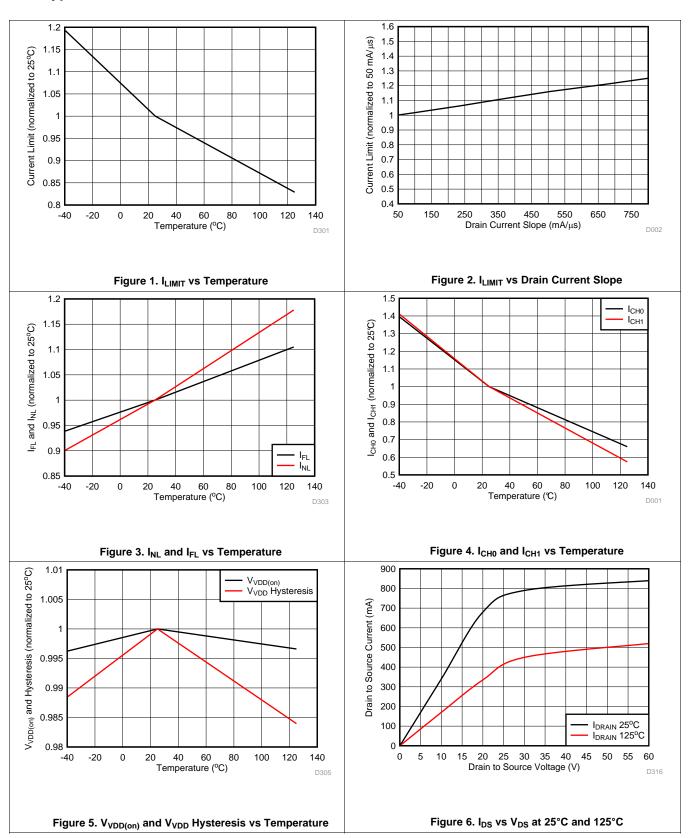

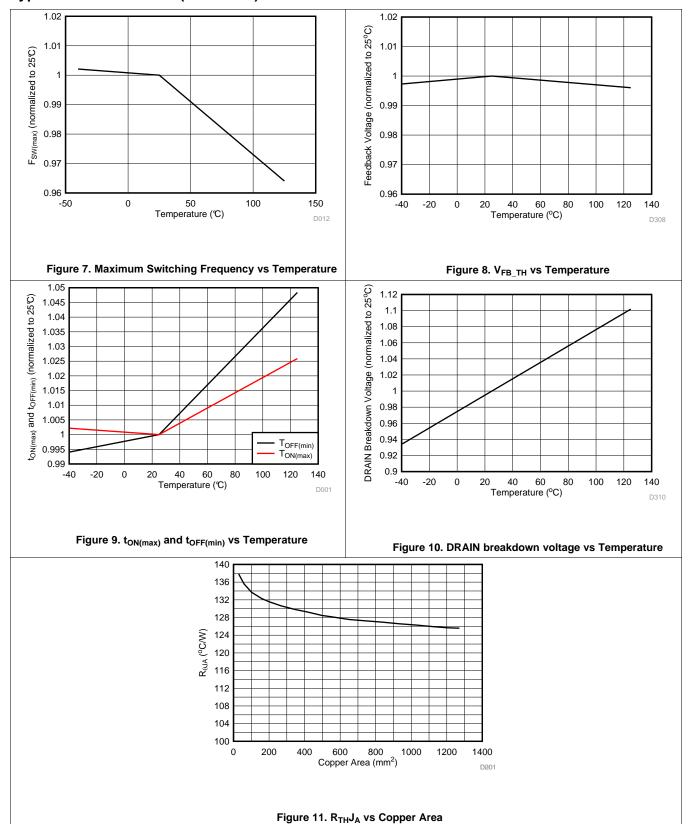

# 7.7 Typical Characteristics

# **Typical Characteristics (continued)**

Submit Documentation Feedback

Copyright © 2015–2016, Texas Instruments Incorporated

# 8 Detailed Description

#### 8.1 Overview

The UCC28881 integrates a controller and a 700-V power MOSFET into one monolithic device. The device also integrates a high-voltage current source, enabling start up and operation directly from the rectified mains voltage. UCC28881 is the same family device as UCC28880 and it provides higher power handling capability.

The low-quiescent current of the device enables excellent efficiency. The device is suitable for non-isolated AC-to-DC low-side buck and buck-boost configurations with level-shifted direct feedback, but also more traditional high-side buck, buck boost and low-power flyback converters with low standby power can be built using a minimum number of external components.

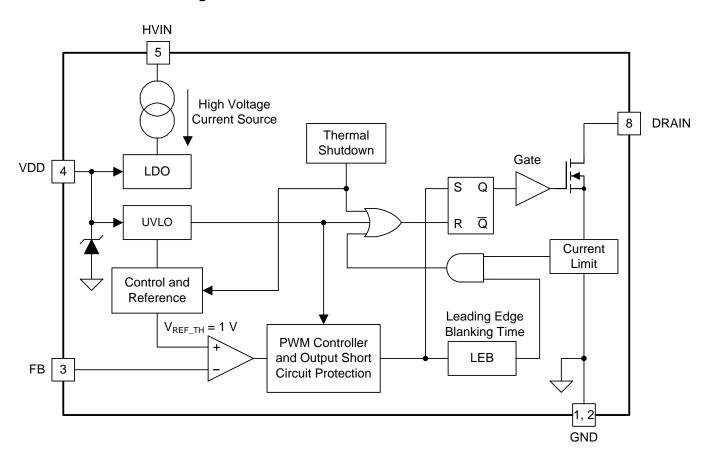

The device generates its own internal low-voltage supply (5 V referenced to the device's ground, GND) from the integrated high-voltage current source. The PWM signal generation is based on a maximum constant on-time, minimum off-time concept, with the triggering of the on-pulse depending on the feedback voltage level. Each onpulse is followed by a minimum off-time to ensure that the power MOSFET is not continuously driven in an on-state. The PWM signal is AND-gated with the signal from a current limit circuit. No internal clock is required, as the switching of the power MOSFET is load dependent. A special protection mechanism is included to avoid runaway of the inductor current when the converter operates with the output shorted or in other abnormal conditions that can lead to an uncontrolled increase of the inductor current. This special protection feature keeps the MOSFET current at a safe operating level. The device is also protected from other fault conditions with thermal shutdown, under-voltage lockout and soft-start features.

### 8.2 Functional Block Diagram

### 8.3 Feature Description

The UCC28881 integrates a 700-V rated power MOSFET switch, a PWM controller, a high-voltage current source to supply a low-voltage power supply regulator. A bias and reference block, thermal shutdown and the following protection features, current limiter, under voltage lockout (UVLO) and overload protection for situations like short circuit at the output are also integrated inside UCC28881. UCC28881 is the same family device as UCC28880 and it provides higher power handling capability.

The positive high-voltage input of the converter node (VIN+) functions as a system reference ground for the output voltage in low-side topologies. In the low-side buck topology the output voltage is negative with respect to the positive high-voltage input (VIN+), and in low-side buck-boost topology the output voltage is positive with respect to the positive high-voltage input (VIN+).

In low-side buck and buck-boost topologies, the external level-shifted direct feedback circuit can be implemented by two resistors and a high-voltage PNP transistor.

In high-side buck configuration, as well as in non-isolated flyback configuration, the output voltage is positive with respect to the negative high-voltage input (VIN-), which is the system reference ground.

UCC28881 can operate under continuous conduction mode (CCM) or discontinuous conduction mode (DCM) mode. CCM operation allows the converter to deliver more output power because of less current ripple. However, it requires a higher inductor value and generally results in lower efficiency due to the added losses associated with diode reverse recovery current. DCM mode operation uses a smaller inductor and achieves better efficiency, but the output current handling capability is reduced because of increased current ripple. The table below shows the current handling capability in DCM and CCM operation for the UCC28880, UCC28881 family.

**DEVICE CURRENT HANDLING MODE** 230 V<sub>AC</sub> ±15% 85 V ~ 265 V<sub>AC</sub> UCC28881 Discontinuous Conduction Mode (DCM) 150 mA 150 mA UCC28881 Continuous Conduction Mode (CCM) 225 mA 225 mA UCC28880 Discontinuous Conduction Mode (DCM) 70 mA 70 mA UCC28880 Continuous Conduction Mode (CCM) 100 mA 100 mA

Table 1. Current Handling Capability for UCC28880 and UCC28881

When the bus voltage is higher than 400 V, it is recommended to limit operation to DCM mode only to avoid the diode reverse recovery current and the associated internal MOSFET stress. Due to the higher switching loss and device stresses at higher bus voltage, it is recommended to keep the converter input voltage less than 560 V for the buck applications.

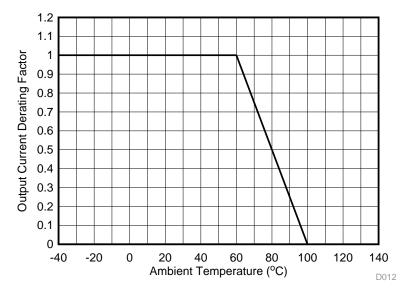

UCC28881 power handling capability is reduced at higher ambient temperature, as a function of the power dissipation of the device, the device's recommended maximum operating junction temperature and the thermal dissipation capability of the total system. De-rating of the output current according to maximum ambient temperature can be estimated from Figure 12. The de-rating estimation assumes CCM operation, 10  $\mu$ J of switching loss and 135°C/W R<sub> $\theta$ JA</sub> and 30-kHz, full-load switching frequency. This is a conservative estimation. The thermal handling capability can be more accurately determined through experimental measurement. For more information on thermal evaluation methods see the IC Package and Thermal Metrics application report: SPRA953.

Figure 12. Output Current (De-Rating Factor) vs. Temperature

It is required to use fast recovery diode for the buck freewheeling diode. When designed in CCM, the diode reverse recovery time should be less than 35 ns to keep low reverse recovery current and the switching loss. For example, STTH1R06A provides 25-ns reverse recovery time. When designed in DCM, a slower diode can be used, but the reverse-recovery time should be kept less than 75 ns. MURS160 can fit the requirement.

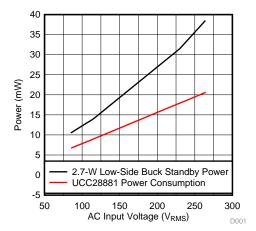

The device has a low-standby power consumption (no-load condition), only 18 mW (typical) when connected to a  $230-V_{AC}$  mains and 9 mW when connected to an  $115-V_{AC}$  mains.

The standby power does not include the power dissipated in the external feedback path, the power dissipated in the external pre-load, the inductor in the freewheeling diode and the converter input stage (rectifiers and filter).

#### 8.4 Device Functional Modes

### 8.4.1 Start-Up Operation

The device includes a high-voltage current source connected between the HVIN pin and the internal supply for the regulator. When the voltage on the HVIN pin rises, the current source is activated and starts to supply current to the internal 5-V regulator. The 5-V regulator charges the external capacitor connected between VDD pin and GND pin. When the VDD voltage exceeds the VDD turn-on threshold,  $V_{VDD(on)}$ , device starts operations. The minimum voltage across HVIN and GND pins, to ensure enough current to charge the capacitance on VDD pin, is  $V_{HVIN(min)}$ . At the First switching cycle the minimum MOSFET off time is set to be >100  $\mu$ s and cycle-by-cycle is progressively reduced up to  $t_{OFF(min)}$  providing soft start.

## 8.4.2 Feedback and Voltage Control Loop

The feedback circuit consists of a voltage comparator with the positive input connected to an internal reference voltage (referenced to GND) and the negative input connected to FB pin. When the feedback voltage at the FB pin is below the reference voltage  $V_{FB\_TH}$  logic high is generated at the comparator output. This logic high triggers the PWM controller, which generates the PWM signal turning on the MOSFET. When the feedback voltage at the FB pin is above the reference voltage, it indicates that the output voltage of the converter is above the targeted output voltage set by the external feedback circuitry and PWM is stopped.

Copyright © 2015–2016, Texas Instruments Incorporated Product Folder Links: *UCC28881*

### **Device Functional Modes (continued)**

#### 8.4.3 PWM Controller

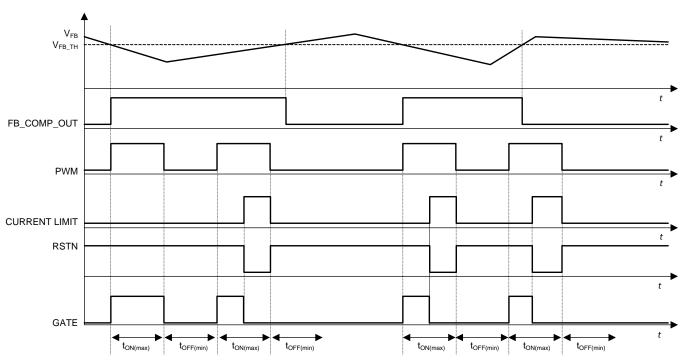

UCC28881 operates under on/off control. When the FB pin voltage is below internal reference 1 V, the converter is switching and sending power to the load. When the FB pin voltage is above internal reference 1 V, the converter shuts off and stops delivering power to the load.

The PWM controller does not need a clock signal. The PWM signal's frequency is set to  $f_{SW(max)} = (1/(t_{ON(max)} + t_{OFF(min)}))$  which occurs when the voltage on the FB pin is continuously below  $V_{FB\_TH}$ .

PWM duty cycle is determined by both the peak current and maximum on time. At each switching cycle, after turn on, the MOSFET is turned off if its current reaches the fixed peak-current threshold or its on time reaches the maximum value of on-time pulse  $t_{ON(max)}$ .

Normally the converter would operate under frequency control, which means the converter is only enabled one switching cycle and then disabled. Next switching cycle starts when output voltage decays and the feedback enable the converter again. This way, the converter appears to operate under variable switching frequency control.

The user might observe the converter operates in burst mode that converter is enabled for multiple switching cycles and then stopped for multiple switching cycles. This causes larger output voltage ripple. However, due to the infrequent switching it actually helps on the standby power at no load.

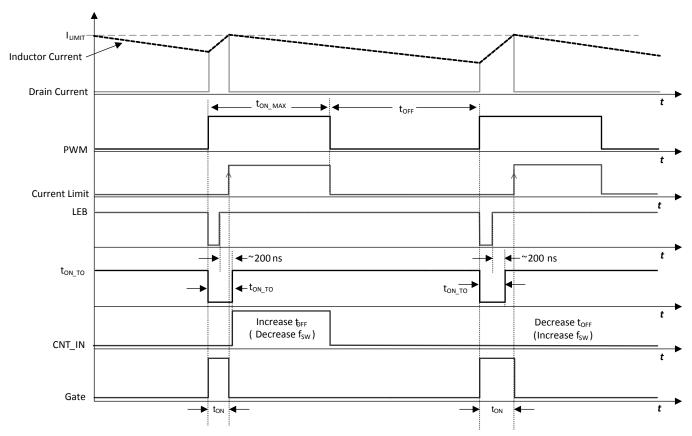

Figure 13. UCC28881 Timing Diagram

### **Device Functional Modes (continued)**

#### 8.4.4 Current Limit

The current limit circuit senses the current through the power MOSFET. The sensing circuit is located between the source of the power MOSFET and the GND pin. When the current in the power MOSFET exceeds the threshold  $I_{\text{LIMIT}}$ , the internal current limit signal goes high, which sets the internal RSTN signal low. This disables the power MOSFET by driving its gate low. The current limit signal is set back low after the falling edge of the PWM signal. After the rising edge of the GATE signal, there is a blanking time. During this blanking time, the current limit signal cannot go high. This blanking time and the internal propagation delay result in minimum on time,  $t_{\text{MIN}}$ .

### 8.4.5 Inductor Current Runaway Protection

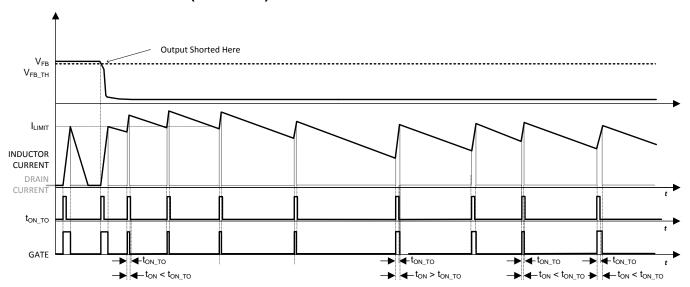

To protect the device from overload conditions, including a short circuit at the output, the PWM controller incorporates a protection feature which prevents the inductor current from runaway. When the output is shorted the inductor demagnetization is very slow, with low di/dt, and when the next switching cycle starts energy stored in the inductance is still high. After the MOSFET switches on, the current starts to rise from pre-existing DC value and reaches the current-limit value in a short duration of time. Because of the intrinsic minimum on-time of the device the MOSFET on-time cannot be lower than  $t_{MIN}$ , in an overload or output short circuit the energy inductance is not discharged sufficiently during MOSFET off-time, it is possible to lose control of the current leading to a runaway of the inductor current. To avoid this, if the on-time is less than  $t_{ON\_TO}$  ( $t_{ON\_TO}$  is a device internal time out), the controller increases the MOSFET off-time ( $t_{OFF}$ ). If the MOSFET on-time is longer than  $t_{ON\_TO}$  then  $t_{OFF}$  is decreased. The controller increases  $t_{OFF}$ , cycle-by-cycle, through discrete steps until the on-time continues to stay below  $t_{ON\_TO}$ . The  $t_{OFF}$  is increased up to  $t_{OFF(ovl)}$  after that, if the on-time is still below  $t_{ON\_TO}$  the off-time is kept equal to  $t_{OFF(ovl)}$ . The controller decreases  $t_{OFF}$  cycle-by-cycle until the on-time continues to stay above  $t_{ON\_TO}$  up to  $t_{OFF(ovl)}$ . This mechanism prevents control loss of the inductor current and prevents over stress of the MOSFET (see typical waveforms in Figure 14 and Figure 15). At start up, the  $t_{OFF}$  is set to  $t_{OFF(ovl)}$  and reduced cycle-by-cycle (if the on-time is longer than  $t_{ON\_TO}$ ) up to  $t_{OFF(min)}$  providing a soft start for the power stage.

Figure 14. Current Runaway Protection Logic Timing Diagram

### **Device Functional Modes (continued)**

Figure 15. Current Runaway Protection, Inductor and MOSFET Current

A minimal value needs to be imposed on the inductance value to avoid nuisance tripping of the protection feature that prevents the loss of control of the inductor current. Inadvertent operation of the protection feature limits the output-power capability of the converter. This condition depends on the converter's maximum input operating voltage and temperature. Use Equation 1 to calculate your minimum inductance value.

$$L > \frac{V_{IN(max)}}{I_{LIMIT}} \times t_{ON\_TO}$$

(1)

In this equation,  $V_{IN(max)}$  is the maximum voltage on the DC input. If the input is a rectifed AC voltage, it should be the peak value of the maximum AC line. For a DC input case, it should be the maximum DC input voltage.

If the inductance value is too low, such that the MOSFET on-time is always less than  $t_{ON\_TO}$  timeout and the device progressively increases the MOSFET off-time up to  $t_{OFF(ovl)}$ , the output power is reduced and the converter fails to supply the load.

### 8.4.6 Over Temperature Protection

If the junction temperature rises above  $T_{J(stop)}$ , the over temperature protection is triggered. This disables the power MOSFET switching. To re-enable the switching of the MOSFET the junction temperature has to fall by  $T_{J(hyst)}$  below the  $T_{J(stop)}$  where the device moves out of over temperature protection.

# **Application and Implementation**

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

# 9.1 Application Information

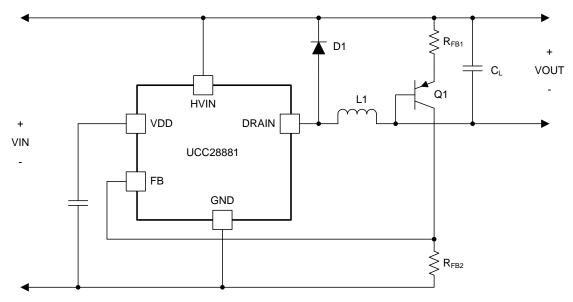

The UCC28881 can be used in various application topologies with direct or isolated feedback. The device can be used in low-side buck, where the output voltage is negative, or as a low-side buck-boost configuration, where the output voltage is positive. In both configurations the common reference node is the positive input node (VIN+). The device can also be configured as a LED driver in either of the above mentioned configurations. If the application requires the AC-to-DC power supply output to be referenced to the negative input node (VIN-), the UCC28881 can also be configured as a traditional high-side buck as shown in Figure 16. In this configuration, the voltage feedback is sampling the output voltage VOUT, making the DC regulation less accurate and load dependent than in low-side buck configuration, where the feedback is always tracking the VOUT. However, highconversion efficiency can still be obtained.

# 9.2 Typical Application

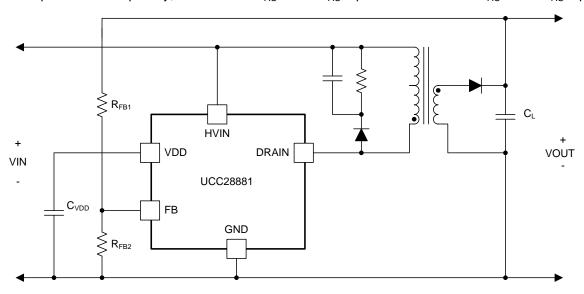

### 9.2.1 13-V, 225-mA High-Side Buck Converter

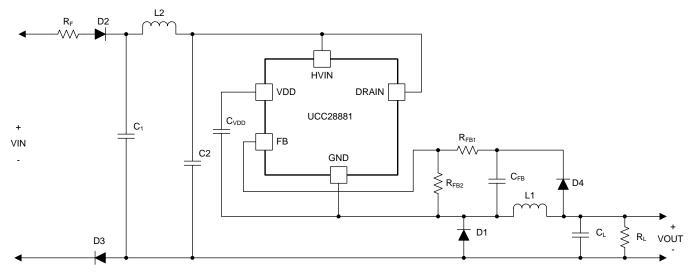

Figure 16 shows a typical application example of a non-isolated power supply, where the UCC28881 is connected in a high-side buck configuration having an output voltage that is positive with respect to the negative high-voltage input (VIN-). The output voltage is set to 13 V in this example, but can easily be changed by changing the value of R<sub>FB1</sub>. This application can be used for a wide variety of household appliances and automation, or any other applications where mains isolation is not required.

Figure 16. Universal Input, 12-V, 225-mA Output High-Side Buck

Product Folder Links: UCC28881

Copyright © 2015-2016, Texas Instruments Incorporated

# **Typical Application (continued)**

### 9.2.1.1 Design Requirements

**Table 2. Design Specification**

|                   |                                | <u> </u> |     |      |           |

|-------------------|--------------------------------|----------|-----|------|-----------|

|                   | DESCRIPTION                    | MIN      | TYP | MAX  | UNIT      |

| DESIGN INP        | UT                             |          |     |      |           |

| $V_{IN}$          | AC input voltage               | 85       |     | 265  | $V_{RMS}$ |

| f <sub>LINE</sub> | Line frequency                 | 47       |     | 63   | Hz        |

| I <sub>OUT</sub>  | Output current                 | 0        |     | 225  | mA        |

| DESIGN RE         | QUIREMENTS                     |          |     |      |           |

| $P_{NL}$          | No-load input power            |          |     | 500  | mW        |

| V <sub>OUT</sub>  | Output voltage                 | 12.5     | 13  | 17.5 | V         |

| $\Delta V_{OUT}$  | Output voltage ripple          |          |     | 350  | mV        |

| η                 | Converter full-load efficiency | 70%      |     |      |           |

# 9.2.1.2 Detailed Design Procedure

#### 9.2.1.2.1 Input Stage (R<sub>F</sub>, D2, D3, C1, C2, L2)

- Resistor  $R_F$  is a flame-proof fusible resistor.  $R_F$  limits the inrush current, and also provide protection in case any component failure causes a short circuit. Value for its resistance is generally selected between 4.7  $\Omega$  to 15  $\Omega$ .

- A half-wave rectifier is chosen and implemented by diode D2 (1N4937). It is a general purpose 1-A, 600-V rated diode. It has a fast reverse recovery time (200 ns) for improved differential-mode-conducted EMI noise performance. Diode D3 (1N4007) is a general purpose 1-A, 1-kV rated diode with standard reverse recovery time (>500 ns), and is added for improved common-mode-conducted EMI noise performance. D3 can be removed and replaced by a short if not needed.

- EMI filtering is implemented by using a single differential-stage filter (C1-L2-C2).

Capacitors C1 and C2 in the EMI filter also acts as storage capacitors for the high-voltage input DC voltage (VIN). The required input capacitor size can be calculated according Equation 2.

$$C_{BULK(min)} = \frac{\frac{2 \times P_{IN}}{f_{LINE(min)}} \times \left[\frac{1}{RCT} - \frac{1}{2 \times \pi} \times arccos\left(\frac{V_{BULK(min)}}{\sqrt{2} \times V_{IN(min)}}\right)\right]}{2 \times V_{IN(min)}^2 - V_{BULK(min)}^2}$$

#### where

- CBULK(min) is minimum value for the total input capacitor value (C1 + C2 in the schematic of Figure 16).

- RCT = 1 in case of half wave rectifier and RCT = 2 in case of full-wave rectifier.

- P<sub>IN</sub> is the converter input power.

- V<sub>IN(min)</sub> is the minimum RMS value of the AC input voltage.

- V<sub>BULK(min)</sub> is the minimum allowed voltage value across bulk capacitor during converter operation.

- $f_{LINE(min)}$  is the minimum line frequency when the line voltage is  $V_{IN(min)}$ .

The converter input power can be easily calculated as follow:

- The converter maximum output power is:  $P_{OUT} = I_{OUT} \times V_{OUT} = 0.225 \text{ A} \times 13 \text{ V} = 2.925 \text{ W}$

- Assuming the efficiency  $\eta = 68\%$  the input power is  $P_{IN} = P_{OUT}/\eta = 4.178$  W

Using the following values for the other parameters

- V<sub>BULK(min)</sub> = 80 V

- V<sub>IN(min)</sub> = 85 V<sub>RMS</sub> (from design specification table)

•

$$f_{LINE(min)} = 57 \text{ Hz}$$

(2)

$C_{BULK(min)}$  = 15.6 µF. Considering that electrolytic capacitors, generally used as bulk capacitor, have 20% of tolerance in value, the minimum nominal value required for  $C_{BULK}$  is:

$$C_{\text{BULKn(min)}} > \frac{C_{\text{BULK(min)}}}{\left(1 - \text{TOL}_{\text{CBULK}}\right)} = 19.5 \,\mu\text{F} \tag{3}$$

Select C1 and C2 to be 10  $\mu$ F each ( $C_{BULK} = 10 \mu$ F + 10  $\mu$ F = 20  $\mu$ F >  $C_{BULKn(min)}$ ).

By using a full-wave rectifier allows a smaller capacitor for C1 and C2, almost 50% smaller.

#### 9.2.1.2.2 Regulator Capacitor (C<sub>VDD</sub>)

Capacitor  $C_{VDD}$  acts as the decoupling capacitor and storage capacitor for the internal regulator. A 100-nF, 10-V rated ceramic capacitor is enough for proper operation of the device's internal LDO.

#### 9.2.1.2.3 Freewheeling Diode (D1)

The freewheeling diode has to be rated for high-voltage with as short as possible reverse-recovery time (t<sub>rr</sub>).

The maximum reverse voltage that the diode should experience in the application, during normal operation, is given by Equation 4.

$$V_{D1(max)} = \sqrt{2} \times V_{IN(max)} = \sqrt{2} \times 265 \, \text{V} = 375 \, \text{V}$$

(4)

A margin of 20% is generally considered.

The use of a fast recovery diode is required for the buck-freewheeling rectifier. When designed in CCM, the diode reverse recovery time should be less than 35 ns to keep low reverse recovery current and the switching loss. For example, STTH1R06A provides 25-ns reverse recovery time. When designed in DCM, slower diode can be used, but the reverse recovery time should be kept less than 75 ns. MURS160 can fit the requirement.

### 9.2.1.2.4 Output Capacitor (C<sub>L</sub>)

The value of the output capacitor impacts the output ripple. Depending on the combination of capacitor value and equivalent series resistor ( $R_{ESR}$ ). A larger capacitor value also has an impact on the start-up time. For a typical application, the capacitor value can start from 47  $\mu$ F, to hundreds of  $\mu$ F. A guide for sizing the capacitor value can be calculated by the following equations:

$$C_{L} > 20 \times \frac{I_{LIMIT} - I_{OUT}}{f_{SW(max)} \times \Delta V_{OUT}} = 20 \times \frac{440 \, mA - 225 \, mA}{62 \, kHz \times 350 \, mV} = 200 \, \mu F \tag{5}$$

$$R_{ESR} < \frac{\Delta V_{OUT}}{I_{LIMIT}} = 0.8\Omega \tag{6}$$

Take into account that both  $C_L$  and  $R_{ESR}$  contribute to output voltage ripple. A first pass capacitance value can be selected and the contribution of  $C_L$  and  $R_{ESR}$  to the output voltage ripple can be evaluated. If the total ripple is too high the capacitance value has to increase or  $R_{ESR}$  value must be reduced. In the application example  $C_L$  was selected (330  $\mu$ F) and it has an  $R_{ESR}$  of 0.03  $\Omega$ . So the  $R_{ESR}$  contributes for 4% of the total ripple. The formula that calculates  $C_L$  is based on the assumption that the converter operates in burst of twenty switching cycles. The number of bursts per cycle could be different, the formula for  $C_L$  is a first approximation.

## 9.2.1.2.5 Pre-Load Resistor (R<sub>L</sub>)

The pre-load resistor connected at the output is required for the high-side buck topology. Unlike low side buck topology, the output voltage is directly sensed, in high-side buck topology the output is sampled and estimated. At no-load condition, because the feedback loop runs with its own time constant, the buck converter operates with a fixed minimum switching frequency. Select the pre-load resistor or using a zener diode to prevent output voltage goes too high at no-load condition.

A simple zener diode would be a good choice without going through the calculation. Besides the simplifying the calculation, zener diode doesn't consumes power at heavy load condition, which helps to improve the converter heavy-load efficiency.

A simple resistor can also be used to limit the output voltage at no load condition. However, this resistor connects to the output all the time and it reduces the full-load efficiency. The pre-load resistor can be calculated based on below equation or based on experiments. In this equation, the  $V_{MAX}$  is allowed maximum output voltage, and  $V_{REG}$  is the regulated output voltage.

$$R_{L} = \frac{4 \times V_{MAX}^{2} \times \left(V_{MAX} - V_{REG}\right)}{V_{MAX} + V_{REG}} \times \frac{C_{FB} \times \left(R_{FB1} + R_{FB2}\right)}{L_{1} \times I_{LIMIT}^{2}}$$

$$(7)$$

#### 9.2.1.2.6 Inductor (L1)

Initial calculations:

Half of the peak-to-peak ripple current at full load:

$$\Delta I_{L} = 2 \times (I_{LIMIT} - I_{OUT})$$

(8)

When operating in DCM, the peak-to-peak current ripple is the peak current of the device.

Average MOSFET conduction minimum duty cycle at continuous conduction mode is:

$$D_{MIN} = \frac{V_{OUT} + V_{d}}{V_{IN(max)} - V_{d}}$$

(9)

If the converter operates in discontinuous conduction mode:

$$D_{MIN} = 2 \times \frac{I_{OUT}}{I_{LIMIT}} \frac{V_{OUT} + V_{d}}{V_{IN(max)} - V_{d}}$$

(10)

Maximum allowed switching frequency at V<sub>IN(max)</sub> and full load:

$$F_{SW\_VIN(max)} = \frac{D_{MIN}}{t_{ON\_TO}}$$

(11)

Switching frequency has a maximum value limit of f<sub>SW(max)</sub>.

The worst case  $I_{LIMIT}$  = 315 mA, but assuming  $\Delta I_{L}$  = 180 mA.

The converter works in continuous conduction mode ( $\Delta I_L < I_{LIMIT}$ ) so based on  $V_{OUT}$  = 13 V,  $V_d$  = 0.5 V and  $V_{IN(max)}$  = 375 V

$$D_{MIN} = \frac{V_{OUT} + V_{d}}{V_{IN(max)} - V_{d}} = 3.61\%$$

(12)

The maximum allowed switching frequency is 62 kHz because the calculated value exceeds it.

$$F_{SW\_VIN(max)} = \frac{D_{MIN}}{t_{ON\_TO}} = 80 \text{ kHz} > f_{SW(max)} = 62 \text{ kHz}$$

(13)

The duty cycle does not force the MOSFET on time to go below  $t_{ON\_TO}$ . If  $D_{MIN}/T_{ON\_TO} < f_{SW(max)}$ , the switching frequency is reduced by current runaway protection and the maximum average switching frequency is lower than  $f_{SW(max)}$ , the converter can't support full load.

The minimum inductance value satisfies both the following conditions:

$$L > \frac{V_{OUT} + V_{d}}{\Delta I_{L} \times F_{SW\_VIN(max)}} = 1 \text{ mH}$$

(14)

$$L > \frac{V_{IN(max)}}{I_{LIMIT}} \times t_{ON\_TO} = \frac{375 \text{ V}}{315 \text{ mA}} \times 450 \text{ ns} \approx 536 \,\mu\text{H}$$

(15)

In the application example, 1 mH is selected as the minimum standard value that satisfy Equation 14 and Equation 15.

Copyright © 2015–2016, Texas Instruments Incorporated

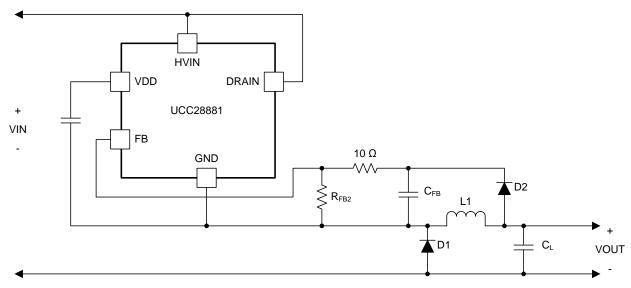

# 9.2.1.2.7 Feedback Path ( $C_{FB}$ , $R_{FB1}$ and $R_{FB2}$ ) and Load Resistor ( $R_L$ )

In low-side buck converter the output voltage is always sensed by the FB pin and UCC28881 internal controller can turn on the MOSFET on VOUT. In high-side buck converter applications the information on the output voltage value is stored on  $C_{FB}$  capacitor. This information is not updated in real time. The information on  $C_{FB}$  capacitor is updated just after MOSFET turn-off event. When the MOSFET is turned off, the inductor current forces the freewheeling diode (D1 in Figure 16) to turn on and the GND pin of UCC28881 goes negative at  $-V_{d1}$  (where  $V_{d1}$  is the forward drop voltage of diode D1) with respect to the negative terminal of bulk capacitor (C1 in Figure 16). When D1 is on, through diode D4, the  $C_{FB}$  capacitor is charged at  $V_{OUT} - V_{d4} + V_{d1}$ . Set the output voltage regulation level using Equation 16.

$$\frac{R_{FB1}}{R_{FB2}} = \frac{V_{OUT(T)} - V_{d4} + V_{d1} - V_{FB\_TH}}{V_{FB\_TH}} \cong \frac{V_{OUT(T)} - V_{FB\_TH}}{V_{FB\_TH}}$$

#### where

- $\bullet \quad V_{FB\ TH}$  is the FB pin reference voltage.

- V<sub>OUT T</sub> is the target output voltage.

- R<sub>FB1</sub>, R<sub>FB2</sub> is the resistance of the resistor divider connected with FB pin (see Figure 16)

- The capacitor  $C_{FB}$  after D1 is discharged with a time constant that is  $\tau_{FB} = C_{FB} x (R_{FB1} + R_{FB2})$ .

• Select the time constant

$$\tau_{FB}$$

, given in Equation 17 (16)

$$\tau_{FB} = C_{FB} \times (R_{FB1} + R_{FB2}) = 0.1 \times C_L \times R_{LOAD}$$

(17)

In this equation, R<sub>LOAD</sub> is the full load resistor value.

The time constant selection leads to a slight output-voltage increase in no-load or light-load conditions. In order to reduce the output-voltage increase, increase  $\tau_{FB}$ . The drawback of increasing  $\tau_{FB}$  is t in high-load conditions  $V_{OUT}$  could drop.

Because of the nature of sample and hold of output voltage feedback, the feedback loop components need some adjustment after the initial design. The larger time constant of the feedback components leads to lower no-load switching frequency. As the results, the no-load standby power and light-load voltage regulation are improved. Because of larger time constant, at heavier load, the load regulation start to get worse. On the contrast, decreasing the time constant makes the heavy load regulation better but increases the no-load standby power and makes the light-load voltage regulation worse. Some tradeoff is required to make the regulation and standby power. Below table summarizes the relationship between the feedback loop time constant and the load regulation. This can be used for an easy guideline for fine tuning the circuit performance.

Table 3. Feedback Loop Time Constant Adjustment

| FEEDBACK LOOP TIME<br>CONSTANT (TFB) | NO-LOAD REGULATION | HEAVY-LOAD OUTPUT<br>VOLTAGE RIPPLE | STANDBY POWER |  |  |

|--------------------------------------|--------------------|-------------------------------------|---------------|--|--|

| Increase                             | Better             | Worse                               | Better        |  |  |

| Decrease                             | Worse              | Better                              | Worse         |  |  |

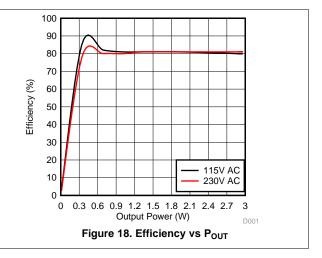

### 9.2.1.3 Application Curves

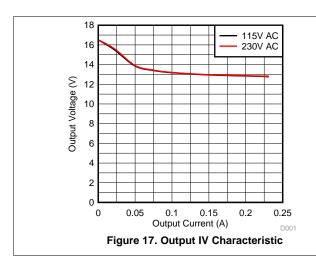

Figure 17 shows the output voltage vs output current. Different curves correspond to different converter AC input voltages. Figure 18 shows efficiency changes vs output power. Different curves correspond to different converter AC input voltages.

**Table 4. Converter Efficiency**

| V <sub>IN_AC</sub> (V <sub>RMS</sub> ) | LOAD (mA) | EFFICIENCY (%) | AVERAGE EFFICIENCY (%) |

|----------------------------------------|-----------|----------------|------------------------|

| 115                                    | 50        | 82             | 81                     |

|                                        | 100       | 81             |                        |

|                                        | 150       | 81             |                        |

|                                        | 225       | 80             |                        |

| 230                                    | 50        | 80             | 80.8                   |

|                                        | 100       | 81             |                        |

|                                        | 150       | 81             |                        |

|                                        | 225       | 81             |                        |

Table 5. Key Component List for 13-V 225-mA High-Side Buck Converter

| DES              | DESCRIPTION                                                | PART NUMBER      | MANUFACTURER (1)        |

|------------------|------------------------------------------------------------|------------------|-------------------------|

| C1, C2           | Bulk capacitor, 10 μF, 450 V                               | EEUED2W100       | Panasonic               |

| $C_FB$           | Feedback capacitor, ceramic, 0.015 µF, 50 V                | C0805C153K5RACTU | Kemet                   |

| $C_L$            | Output capacitor, 330 µF, 35 V                             | EEU-FM1V331L     | Panasonic               |

| D1               | Buck freewheeling diode, ultrafast, 600 V, 1 A             | STTH1R06A        | ST Microelectronics     |

| D2, D3           | Rectifier diodes, standard recovery rectifier, 1000 V, 1 A | 1N4007           | Fairchild semiconductor |

| D4               | Feedback diode, standard recovery rectifier, 600 V, 1 A    | 1N4006-T         | Diodes Inc.             |

| L1               | Buck inductor, 1 mH, 0.4 A,                                | 7447471102       | Wurth Elektronik        |

| L2               | Filter inductor, 1 mH, 0.2 A                               | 5800-102-RC      | Bourns                  |

| R <sub>FB1</sub> | Upper feedback resistor 121 kΩ, 1%                         | ERJ-6ENF1213V    | Panasonic               |

| R <sub>FB2</sub> | Lower feedback resistor, 10.0 kΩ, 1%                       | ERJ-6ENF1002V    | Panasonic               |

(1) See Third-Party Products Discalimer

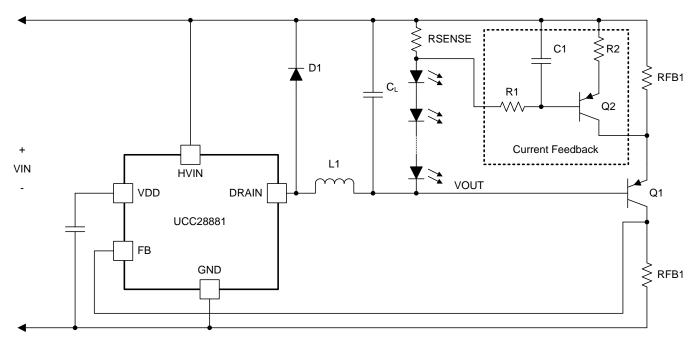

# 9.2.2 Additional UCC28881 Application Topologies

# 9.2.2.1 Low-Side Buck and LED Driver – Direct Feedback (Level Shifted)

### Features include:

- Output Referenced to Input

- Negative Output (V<sub>OUT</sub>) with Respect to VIN+

- Step Down: V<sub>OUT</sub> < V<sub>IN</sub>

- Direct Level-Shifted Feedback

Figure 19. Low-Side Buck, Direct Feedback (Level Shifted)

Figure 20. Low-Side Buck LED Driver, Direct Feedback (Level Shifted)

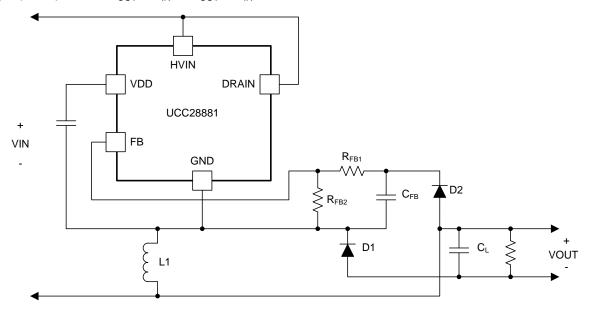

# 9.2.2.2 High-Side Buck Converter

### Features include:

- Output Referenced to Input

- Positive Output (V<sub>OUT</sub>) with Respect to VIN–

- Step Down (V<sub>OUT</sub> < V<sub>IN</sub>)

Figure 21. High-Side Buck Converter Schematic

# 9.2.2.3 Non-Isolated, Low-Side Buck-Boost Converter

### Features Include:

- Output Referenced to Input

- Positive Output (V<sub>OUT</sub>) with Respect to VIN+

- Step Up, Step Down:  $V_{OUT} > V_{IN}$  or  $V_{OUT} < V_{IN}$

- Direct Level-Shifted Feedback

Figure 22. Low-Side Buck-Boost Converter

Copyright © 2015–2016, Texas Instruments Incorporated

### 9.2.2.4 Non-Isolated, High-Side Buck-Boost Converter

### Features include:

- Output Referenced to Input

- Positive Output (V<sub>OUT</sub>) with Respect to VIN–

- Step Up, Step Down:  $V_{OUT} > V_{IN}$  or  $V_{OUT} < V_{IN}$

Figure 23. High-Side Buck-Boost Converter

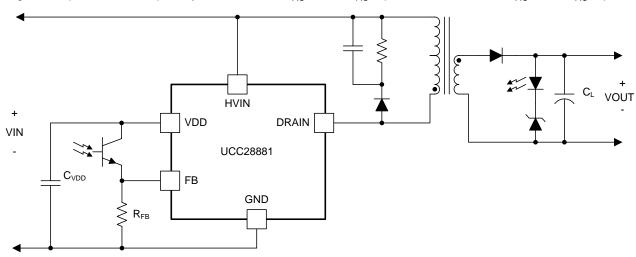

### 9.2.2.5 Non-Isolated Flyback Converter

## Features include:

- Output Referenced to Input

- Positive Output (V<sub>OUT</sub>) with Respect VIN–

- Direct Feedback

- Higher Output Current Capability, 4.5 W for 85 V<sub>AC</sub> ~ 265 V<sub>AC</sub> Input and 6 W for 176 V<sub>AC</sub> ~ 265 V<sub>AC</sub> Input

Figure 24. Non-Isolated Flyback Configuration

Product Folder Links: UCC28881

24

# 9.2.2.6 Isolated Flyback Converter

Features include:

- Output Isolated from Input

- Direct Feedback

- Higher Output Current Capability, 4.5 W for 85  $V_{AC}$  ~ 265  $V_{AC}$  Input and 6 W for 176  $V_{AC}$  ~ 265 $V_{AC}$  Input

Figure 25. Isolated Flyback Converter

# 10 Power Supply Recommendations

The VDD capacitor recommended value is 100 nF to ensure high-phase margin of the internal 5-V regulator and it should be placed close to VDD pin and GND pins to minimize the series resistance and inductance.

The VDD pin provides a regulated 5-V output but it is not intended as a supply for external load. Do not supply VDD pin with external voltage source (for example the auxiliary winding of flyback converter).

Always keep GND pin 1 and GND pin 2 connected together with the shortest possible connection.

# 11 Layout

### 11.1 Layout Guidelines

- In both buck and buck-boost low-side configurations, the copper area of the switching node DRAIN should be minimized to reduce EMI.

- Similarly, the copper area of the FB pin should be minimized to reduce coupling to feedback path. Loop C<sub>L</sub>,

Q1, R<sub>FB1</sub> should be minimized to reduce coupling to feedback path.

- In high-side buck and buck boost the GND, VDD and FB pins are all part of the switching node so the copper area connected with these pins should be optimized. Large copper area allows better thermal management, but it causes more common mode EMI noise. Use the minimum copper area that is required to handle the thermal dissipation.

- Minimum distance between 700-V coated traces is 1.41 mm (60 mils).

### 11.2 Layout Example

Figure 26 shows and example PCB layout for UCC28881 in low-side buck configuration.

Figure 26. UCC28881 Layout Example

# 12 Device and Documentation Support

### 12.1 Device Support

### 12.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

### 12.2 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 12.3 Trademarks

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

### 12.4 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### 12.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

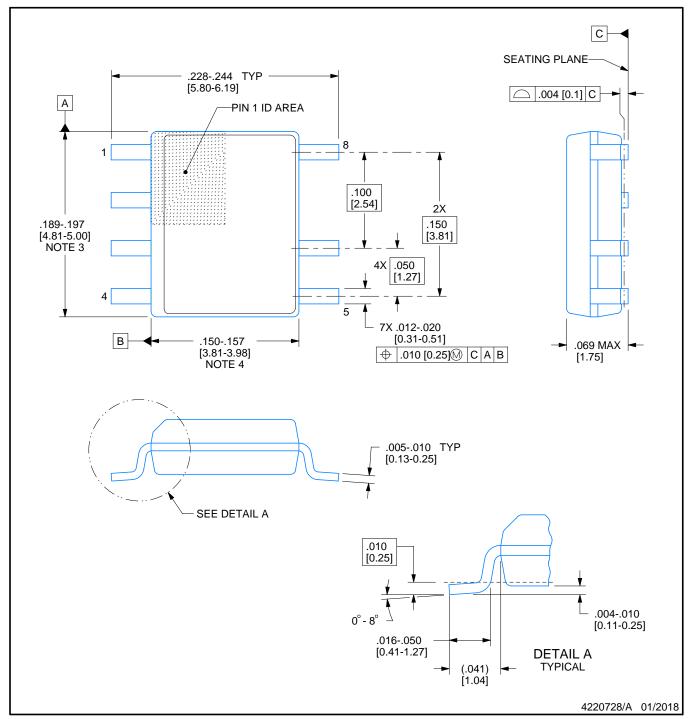

## 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com 17-Jun-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/         | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|----------------|-----------------------|------|---------------|---------------------|--------------|--------------|

|                       | (1)    | (2)           |                |                       | (3)  | Ball material | Peak reflow         |              | (6)          |

|                       |        |               |                |                       |      | (4)           | (5)                 |              |              |

| UCC28881D             | Active | Production    | SOIC (D)   7   | 75   TUBE             | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | U28881       |

| UCC28881D.B           | Active | Production    | SOIC (D)   7   | 75   TUBE             | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | U28881       |

| UCC28881DR            | Active | Production    | SOIC (D)   7   | 2500   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | U28881       |

| UCC28881DR.B          | Active | Production    | SOIC (D)   7   | 2500   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | U28881       |

| UCC28881DRG4          | Active | Production    | SOIC (D)   7   | 2500   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | U28881       |

| UCC28881DRG4.B        | Active | Production    | SOIC (D)   7   | 2500   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | U28881       |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 17-Jun-2025

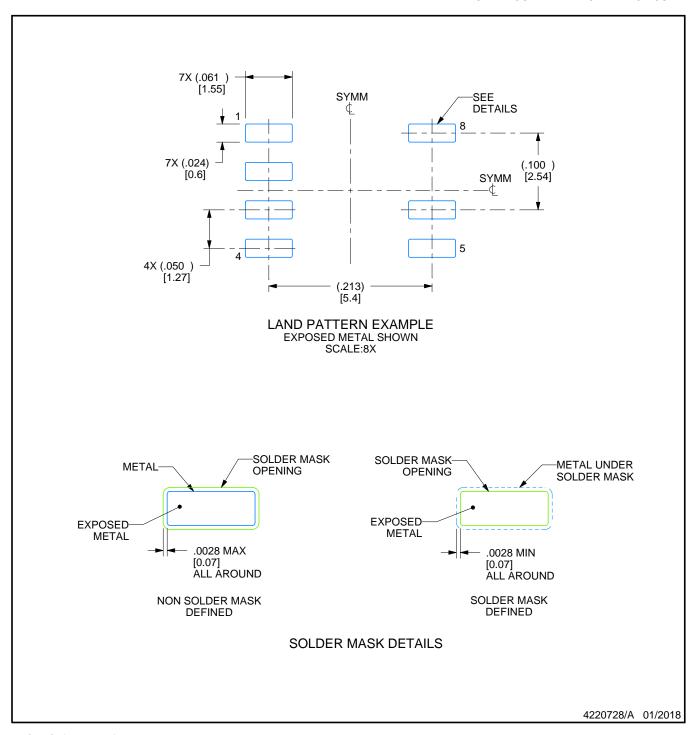

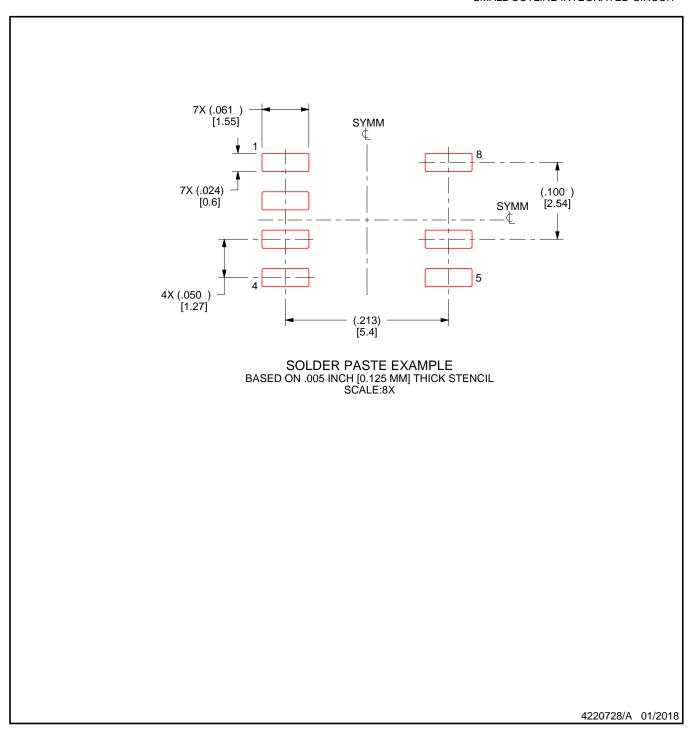

SMALL OUTLINE INTEGRATED CIRCUIT

## NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated