## 8ピン擬似共振制御グリーン・モード・コントローラ

### 特 長

- 高度な待機電力の改善の機能をもつグリーン・モード・コントローラです

- 擬似共振モード動作によりさらなるEMI及びスイッチング損失の低減(低電圧スイッチング)が可能

- 低待機電力モードによりシステム無負荷時の消費電力を大幅に低減が可能

- 低起動電流:最大25μA

- 設定可能な入力/負荷電圧の過電圧保護

- 過熱保護機能内蔵

- 過電流保護

- サイクルごとの電力制限

- 過電流ヒカップモードからの再起動モード

- 1AのシンクTrueDrive<sup>TM</sup>、0.75Aのソース・ゲート駆動出力

- 設定可能なソフトスタート機能

- 外部PFC回路停止機能等に利用できる端子を内蔵

### ア プ リ ケ シ ョ ン

- LCDモニタ、LCD TV、PDP TV、セットトップ・ボックス用バイアス電源

- AC/DCアダプタ、オフラインのバッテリー充電器

- 最大200Wまでの省エネルギー電源

### 概 要

UCC28600は世界的な厳しい省エネルギー要件に適合する高度な省エネルギー機能をもった電力制御コントローラです。

UCC28600は省エネルギー電源用にコスト効率の良いシステムを構築するために高信頼性な保護機能をもち、かつ高度な待機電力改善の機能を内蔵しています。UCC28600は軽負荷及び無負荷動作時に動作周波数を低減する周波数フォルドバック及びバースト・モード機能を内蔵しています。

UCC28600のパッケージは8pinのSOIC(D)パッケージです。UCC28600の動作温度範囲は-40°C~105°Cです。

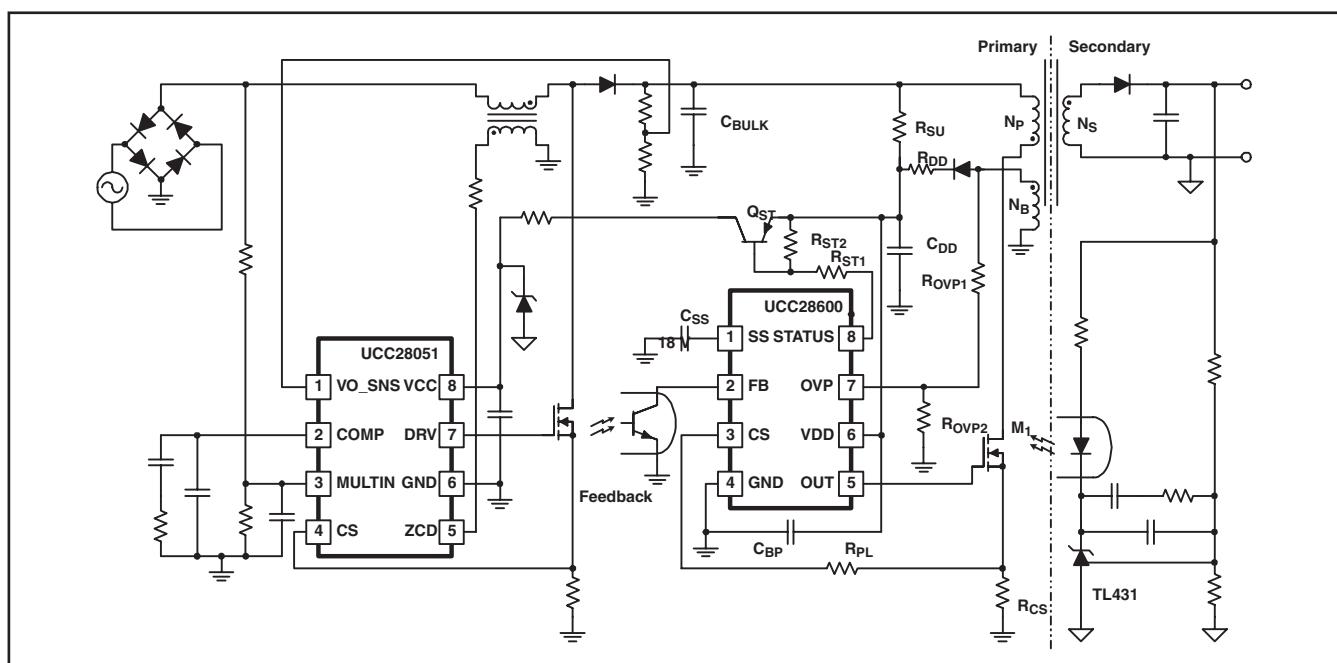

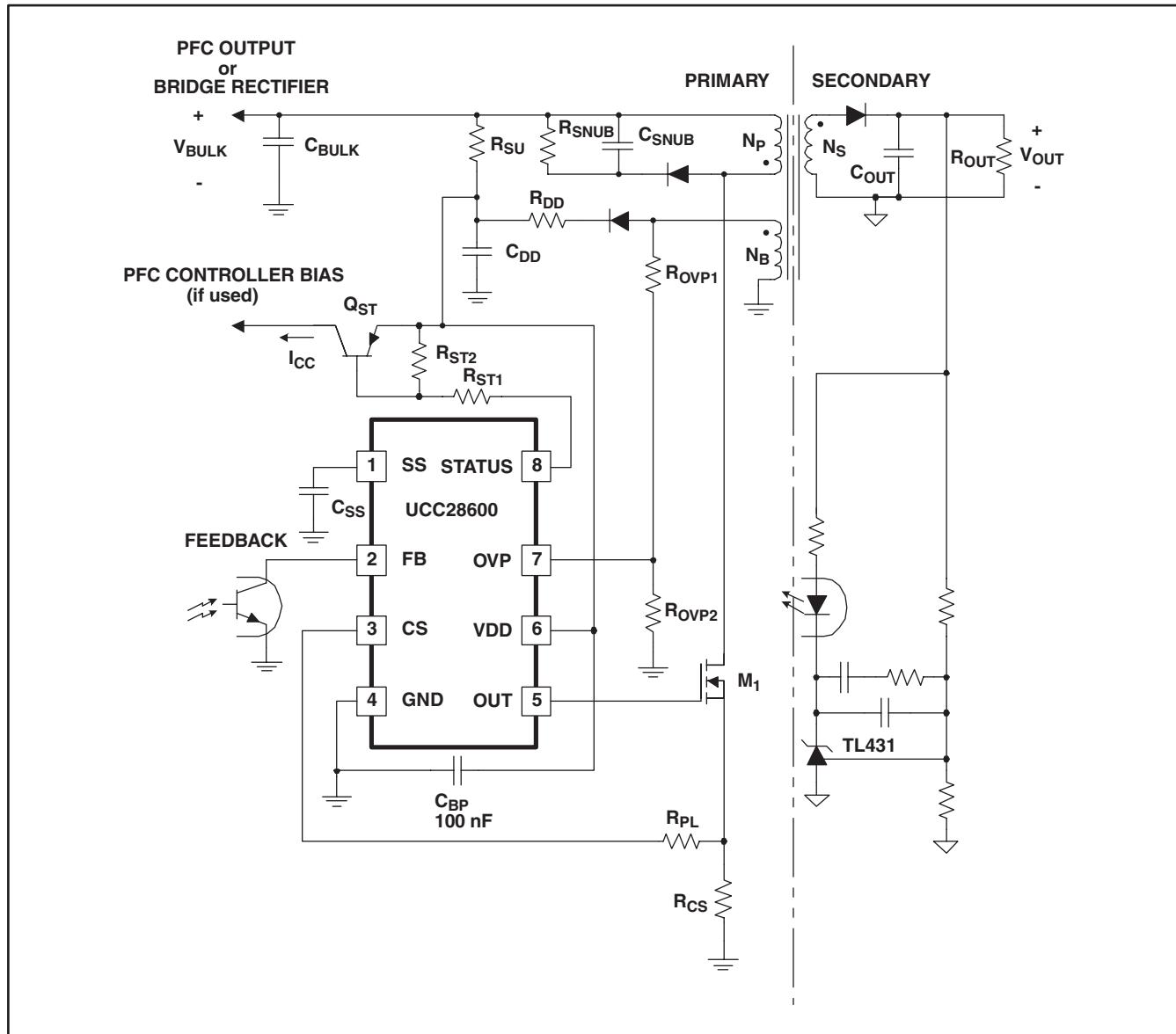

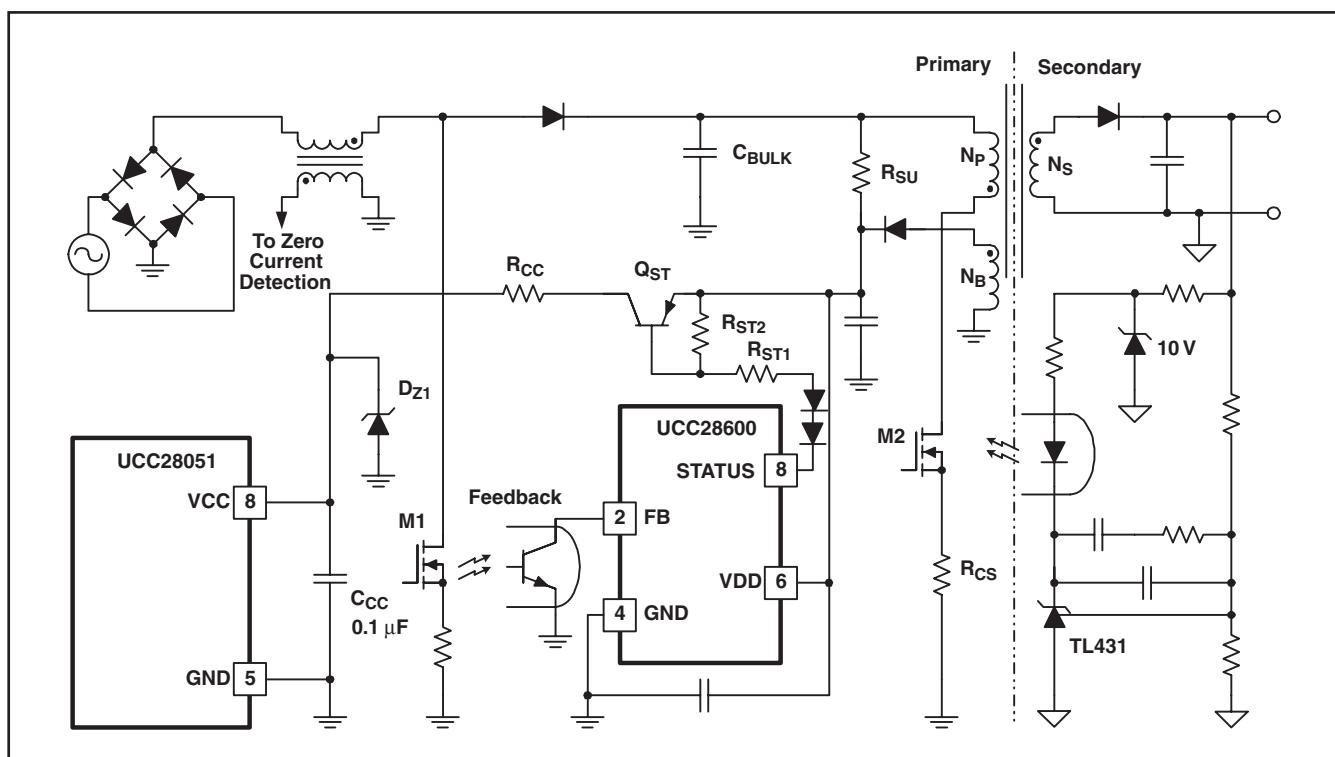

### TYPICAL APPLICATION

TrueDriveは、テキサス・インスツルメンツの登録商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

# 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下

さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

## ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range unless otherwise noted<sup>(1)</sup>

|                          |                                                              |                                       | <b>UCC28600</b> | <b>UNIT</b> |

|--------------------------|--------------------------------------------------------------|---------------------------------------|-----------------|-------------|

| V <sub>DD</sub>          | Supply voltage range                                         | I <sub>DD</sub> < 20 mA               | 32              | V           |

| I <sub>DD</sub>          | Supply current                                               |                                       | 20              | mA          |

| I <sub>OUT(sink)</sub>   | Output sink current (peak)                                   |                                       | 1.2             | A           |

| I <sub>OUT(source)</sub> | Output source current (peak)                                 |                                       | -0.8            |             |

|                          | Analog inputs                                                | FB, CS, SS                            | -0.3 to 6.0     | V           |

| V <sub>OVP</sub>         |                                                              |                                       | -1.0 to 6.0     |             |

| I <sub>OVP(source)</sub> |                                                              |                                       | -1.0            | mA          |

| V <sub>STATUS</sub>      |                                                              | VDD = 0 V to 30 V                     | 30              | V           |

|                          | Power dissipation                                            | SOIC-8 package, T <sub>A</sub> = 25°C | 650             | mW          |

| T <sub>J</sub>           | Operating junction temperature range                         |                                       | -55 to 150      |             |

| T <sub>stg</sub>         | Storage temperature                                          |                                       | -65 to 150      | °C          |

| T <sub>LEAD</sub>        | Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds |                                       | 300             |             |

(1) 絶対最大定格以上のストレスは、製品に恒久的・致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作を意味するものではありません。絶対最大定格の状態に長時間置くことは、本製品の信頼性に影響を与えることがあります。全ての電圧はGNDを基準としています。電流の極性は規定端子に流入する方向が正、流出する方向が負です。パッケージの熱制限や考察についてはデータブックのパッケージの項を参照してください。

## 推奨動作条件

|                  |                                | <b>MIN</b> | <b>NOM</b> | <b>MAX</b> | <b>UNIT</b> |

|------------------|--------------------------------|------------|------------|------------|-------------|

| V <sub>DD</sub>  | Input voltage                  |            |            | 21         | V           |

| I <sub>OUT</sub> | Output sink current            |            | 0          |            | A           |

| T <sub>J</sub>   | Operating junction temperature | -55        |            | 150        | °C          |

## ELECTROSTATIC DISCHARGE (ESD) PROTECTION

|                  | <b>MIN</b> | <b>MAX</b> | <b>UNIT</b> |

|------------------|------------|------------|-------------|

| Human body model |            | 2000       |             |

| CDM              |            | 1500       | V           |

## ELECTRICAL CHARACTERISTICS

V<sub>DD</sub> = 15 V, 0.1- $\mu$ F capacitor from V<sub>DD</sub> to GND, 3.3-nF capacitor from SS to GND charged over 3.5 V, 500- $\Omega$  resistor from OVP to -0.1 V, FB = 4.8 V, STATUS = not connected, 1-nF capacitor from OUT to GND, CS = GND, T<sub>A</sub> = T<sub>J</sub> = -40°C to 105°C, (特に記述のない限り)

| PARAMETER                       |                                                      | TEST CONDITIONS                                    | MIN  | TYP  | MAX  | UNIT       |

|---------------------------------|------------------------------------------------------|----------------------------------------------------|------|------|------|------------|

| <b>Overall</b>                  |                                                      |                                                    |      |      |      |            |

| I <sub>STARTUP</sub>            | Startup current                                      | V <sub>DD</sub> = V <sub>UVLO</sub> - 0.3 V        | 12   | 25   |      | $\mu$ A    |

| I <sub>STANDBY</sub>            | Standby current                                      | V <sub>FB</sub> = 0 V                              | 350  | 550  |      |            |

| I <sub>DD</sub>                 | Operating current                                    | Not switching                                      | 2.5  | 3.5  |      | mA         |

|                                 |                                                      | 130 kHz, QR mode                                   | 5.0  | 7.0  |      |            |

| V <sub>DD</sub> clamp           |                                                      | FB = GND, I <sub>DD</sub> = 10 mA                  | 21   | 26   | 32   | V          |

| <b>Undervoltage Lockout</b>     |                                                      |                                                    |      |      |      |            |

| V <sub>DD(uvlo)</sub>           | Startup threshold                                    |                                                    | 10.3 | 13.0 | 15.3 | V          |

|                                 | Stop threshold                                       |                                                    | 6.3  | 8    | 9.3  |            |

|                                 | Hysteresis                                           |                                                    | 4.0  | 5.0  | 6.0  |            |

| <b>PWM (Ramp)<sup>(1)</sup></b> |                                                      |                                                    |      |      |      |            |

| D <sub>MIN</sub>                | Minimum duty cycle                                   | V <sub>SS</sub> = GND, V <sub>FB</sub> = 2 V       |      |      | 0%   |            |

| D <sub>MAX</sub>                | Maximum duty cycle                                   | QR mode, f <sub>S</sub> = max, (open loop)         |      |      | 99%  |            |

| <b>Oscillator (OSC)</b>         |                                                      |                                                    |      |      |      |            |

| f <sub>QR(max)</sub>            | Maximum QR frequency                                 |                                                    | 117  | 130  | 143  | kHz        |

| f <sub>QR(min)</sub>            | Minimum QR and FFM frequency                         | V <sub>FB</sub> = 1.3 V                            | 32   | 40   | 48   |            |

| f <sub>SS</sub>                 | Soft start frequency                                 | V <sub>SS</sub> = 2.0 V                            | 32   | 40   | 48   |            |

| dT <sub>S</sub> /dFB            | VCO gain                                             | T <sub>S</sub> for 1.6 V < V <sub>FB</sub> < 1.8 V | -38  | -30  | -22  | $\mu$ s/V  |

| <b>Feedback (FB)</b>            |                                                      |                                                    |      |      |      |            |

| Feedback pullup resistor        |                                                      |                                                    | 12   | 20   | 28   | k $\Omega$ |

| FB, no load                     | QR mode                                              |                                                    | 3.30 | 4.87 | 6.00 | V          |

| Green mode ON threshold         | V <sub>FB</sub> threshold                            |                                                    | 0.3  | 0.5  | 0.7  |            |

| Green mode OFF threshold        | V <sub>FB</sub> threshold                            |                                                    | 1.2  | 1.4  | 1.6  |            |

| Green mode hysteresis           | V <sub>FB</sub> threshold                            |                                                    | 0.7  | 0.9  | 1.1  |            |

| FB threshold burst-ON           | V <sub>FB</sub> during Green mode                    |                                                    | 0.3  | 0.5  | 0.7  |            |

| FB threshold burst-OFF          | V <sub>FB</sub> during Green mode                    |                                                    | 0.5  | 0.7  | 0.9  |            |

| Burst Hysteresis                | V <sub>FB</sub> during Green mode                    |                                                    | 0.13 | 0.25 | 0.42 |            |

| <b>Status</b>                   |                                                      |                                                    |      |      |      |            |

| STATUS R <sub>DS(on)</sub>      | V <sub>STATUS</sub> = 1 V                            |                                                    | 1.0  | 2.4  | 3.8  | k $\Omega$ |

| STATUS leakage/off current      | V <sub>FB</sub> = 0.44 V, V <sub>STATUS</sub> = 15 V |                                                    | -0.1 |      | 2.0  | $\mu$ A    |

(1) R<sub>CST</sub>とC<sub>CST</sub>は最大/最小デューティ・サイクル試験、電流検出試験、電力制限試験の回路では接続されていません。

## ELECTRICAL CHARACTERISTICS

VDD = 15 V, 0.1- $\mu$ F capacitor from VDD to GND, 3.3-nF capacitor from SS to GND charged over 3.5 V, 500- $\Omega$  resistor from OVP to -0.1 V, FB = 4.8 V, STATUS = not connected, 1-nF capacitor from OUT to GND, CS = GND, TA = TJ = -40°C to 105°C, (特に記述のない限り)

| PARAMETER                               | TEST CONDITIONS                                   | MIN                                                                               | TYP  | MAX  | UNIT    |

|-----------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------|------|------|---------|

| <b>Current Sense (CS)<sup>(2)</sup></b> |                                                   |                                                                                   |      |      |         |

| A <sub>CS(FB)</sub>                     | Gain, FB = ΔV <sub>FB</sub> / ΔV <sub>CS</sub>    | QR mode                                                                           |      | 2.5  | V/V     |

|                                         | Shutdown threshold                                | V <sub>FB</sub> = 2.4 V, V <sub>SS</sub> = 0 V                                    | 1.13 | 1.25 | 1.38    |

|                                         | CS to output delay time (power limit)             | CS = 1.0 V <sub>PULSE</sub>                                                       | 100  | 175  | 300     |

|                                         | CS to output delay time (over current fault)      | CS = 1.45 V <sub>PULSE</sub>                                                      | 50   | 100  | 150     |

|                                         | CS discharge impedance                            | CS = 0.1 V, V <sub>SS</sub> = 0 V                                                 | 25   | 115  | 250     |

|                                         | CS offset                                         | SS mode, V <sub>SS</sub> ≤ 2.0 V, via FB                                          | 0.35 | 0.40 | 0.45    |

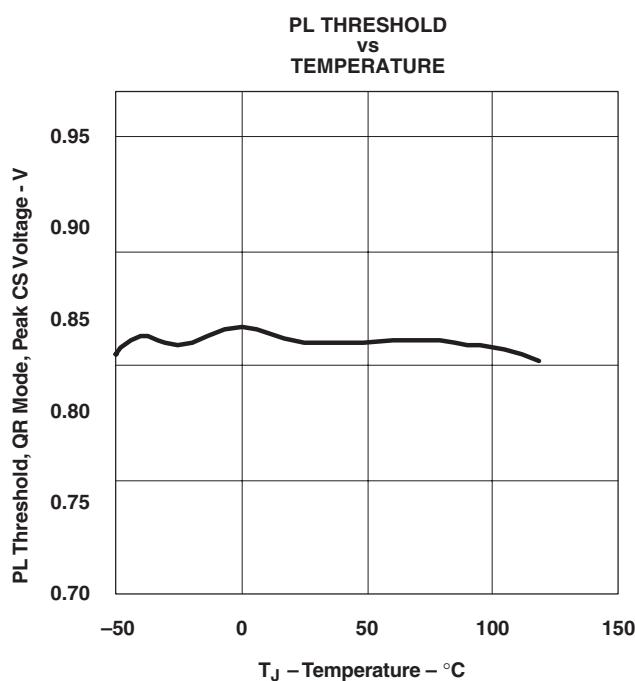

| <b>Power Limit (PL)<sup>(2)</sup></b>   |                                                   |                                                                                   |      |      |         |

| CS current                              | OVP = -300 $\mu$ A                                | -165                                                                              | -150 | -135 | $\mu$ A |

| CS working range                        | QR mode, peak CS voltage                          | 0.70                                                                              | 0.81 | 0.92 | V       |

| PL threshold                            | Peak CS voltage + CS offset                       | 1.05                                                                              | 1.20 | 1.37 |         |

| <b>Soft Start (SS)</b>                  |                                                   |                                                                                   |      |      |         |

| I <sub>SS(chg)</sub>                    | Softstart charge current                          | V <sub>SS</sub> = GND                                                             | -8.3 | -6.0 | -4.5    |

| I <sub>SS(dis)</sub>                    | Softstart discharge current                       | V <sub>SS</sub> = 0.5 V                                                           | 2.0  | 5.0  | 10      |

| V <sub>SS</sub>                         | Switching ON threshold                            | Output switching start                                                            | 0.8  | 1.0  | 1.2     |

| <b>Ovvervoltage Protection (OVP)</b>    |                                                   |                                                                                   |      |      |         |

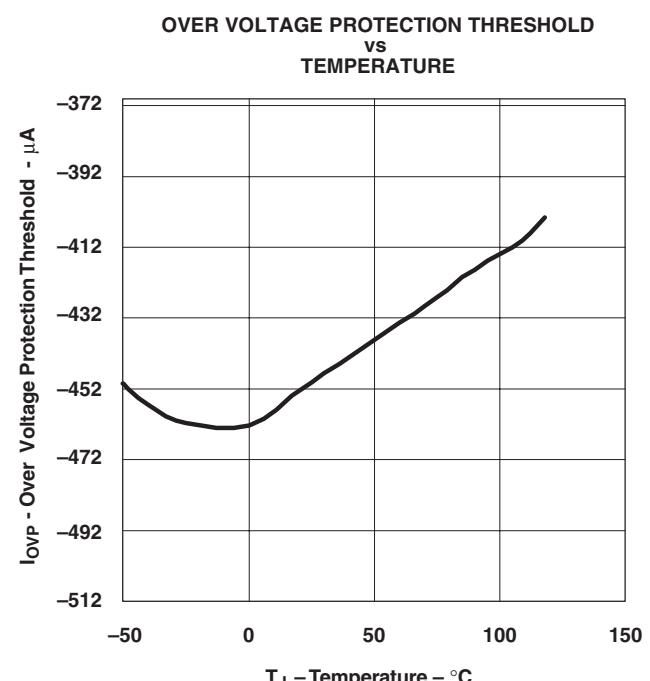

| OVP <sub>(line)</sub>                   | Line overvoltage protection                       | I <sub>OVP</sub> threshold, OUT = HI                                              | -512 | -450 | -370    |

|                                         | OVP voltage at OUT = HIGH                         | V <sub>FB</sub> = 4.8 V, V <sub>SS</sub> = 5.0 V, I <sub>OVP</sub> = -300 $\mu$ A | -125 | -25  | mV      |

| OVP <sub>(load)</sub>                   | Load overvoltage protection                       | V <sub>OVP</sub> threshold, OUT = LO                                              | 3.37 | 3.75 | 4.13    |

| <b>Thermal Protection (TSD)</b>         |                                                   |                                                                                   |      |      |         |

|                                         | Thermal shutdown (TSP) temperature <sup>(3)</sup> |                                                                                   | 130  | 140  | 150     |

|                                         | Thermal shutdown hysteresis                       |                                                                                   |      | 15   | °C      |

| <b>OUT</b>                              |                                                   |                                                                                   |      |      |         |

| t <sub>RISE</sub>                       | Rise time                                         | 10% to 90% of 13 V typical out clamp                                              | 50   | 75   | ns      |

| t <sub>FALL</sub>                       | Fall time                                         |                                                                                   | 10   | 20   |         |

(2) R<sub>CST</sub>とC<sub>CST</sub>は最大/最小デューティ・サイクル試験、電流検出試験、電力制限試験の回路では接続されていません。

(3) 設計で保証されており、テストは行われていません。

## OPEN LOOP TEST CIRCUIT

**NOTE:**  $R_{CST}$  and  $C_{CST}$  are not connected for maximum and minimum duty cycle tests, current sense tests and power limit tests.

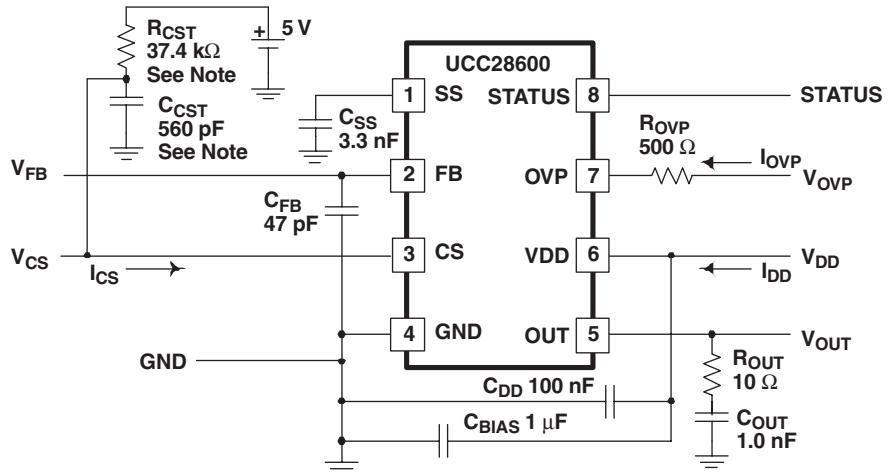

## BLOCK DIAGRAM/TYPICAL APPLICATION

## ORDERING INFORMATION

| T <sub>A</sub> | PACKAGES                | PART NUMBER |

|----------------|-------------------------|-------------|

| -40°C to 105°C | SOIC (D) <sup>(1)</sup> | UCC28600D   |

(1) SOIC(D)パッケージはテープ/リールで供給されており、テープ/リールで発注するには型番にRを付けてください。

UCC28600DRのリールあたりの数量は2500個です。

## DEVICE INFORMATION

| UCC28600<br>D PACKAGE<br>(TOP VIEW) |                 |

|-------------------------------------|-----------------|

| SS                                  | 1      8 STATUS |

| FB                                  | 2      7 OVP    |

| CS                                  | 3      6 VDD    |

| GND                                 | 4      5 OUT    |

## 端子機能

| TERMINAL<br>NAME | I/O<br>NO. | DESCRIPTION                                                                                                                                                                                                                                                                                                                 |

|------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

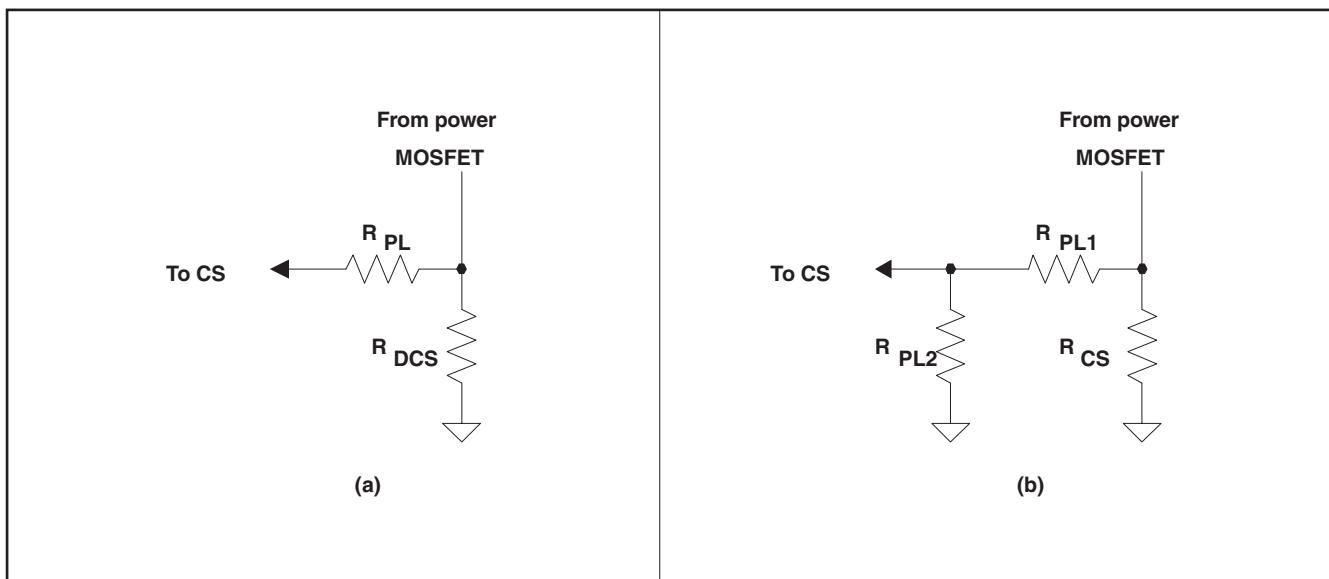

| CS               | 3          | I 過電流検出入力ピンです。このピンは電力制限も同時に設定し、入力信号は電力制御にも使用され、さらに通常の過電流保護を有効に働かせます。CS電圧の入力信号は電流検出抵抗端とグランド間の電圧で発生し電力制限はこのピンと電流検出抵抗間の実効直列抵抗により設定されます。                                                                                                                                                                                        |

| FB               | 2          | I 2次側より帰還される帰還信号を光カプラを利用して制御コンパレータへの入力する端子です。このピンと内部の基準電源の5Vに定電圧化された電圧源との間に20kΩの抵抗が内蔵されています。フィードバック用光カプラのフォトトランジスタのコレクタを直接このピンに、フォトトランジスタのエミッタをGNDに接続してください。このピンの電圧により、擬似共振(QR)、周波数フォルダック・モード(FFM)、グリーン・モード(GM)の3つのモードを、入力される電圧レベルにより動作モードを制御します。                                                                           |

| GND              | 4          | - 内部回路用のグランドです。VDDとGNDの間に0.1μFのセラミック・バイパス・コンデンサができるだけこの2つのピンに近づけて接続してください。                                                                                                                                                                                                                                                  |

| OUT              | 5          | O 1Aのシンク(TrueDrive™)及び0.75Aのソース・ゲート駆動出力ピンです。この出力は外付けのパワーMOSFETのゲート制御信号として働きます。また内部で13Vにクランプされています。                                                                                                                                                                                                                          |

| OVP              | 7          | I 過電圧保護(OVP)入力は、ラインの過電圧保護、負荷の過電圧保護および疑似共振動作を行うために、スイッチングのゼロ電位を検出する3つの働きを有しています。バイアス補助巻線を用いて入力、負荷、共振の状態を検出し、このピンに接続する抵抗により電圧変換され制御を行います。                                                                                                                                                                                     |

| SS               | 1          | I ソフトスタートの設定を行うピンです。グランドに接続されているコンデンサを用いてソフトスタートのレートを設定します。レートはコンデンサ容量と内部のソフトスタート充電電流により決まります。異常の場合は全てSSピンから約100ΩのR <sub>DS(on)</sub> をもつ内部のMOSFETを介してGNDに放電されます。内部の変調器のコンパレータは、最小のSS電圧、内部のFB電圧、ピーク電流制限に反応します。一般的に、C <sub>ss</sub> = 3.3nFの場合T <sub>ss</sub> = 1.5msです。また、極端なバーストモード時にはこの設定と入力の平滑コンデンサとの関係により再起動の周期が決定されます。 |

| STATUS           | 8          | O デバイスがスタンバイ・モードになったことを示すアクティブ “H” レベルのオープン・ドレイン信号端子です。このピンは外部のPFCコントロール回路等を停止にするのに使用することができます(ハイ・インピーダンス=グリーン・モード)。STATUSピンは、UVLO(V <sub>DD</sub> < 起動スレッシホールド)及びソフトスタート(SS < FB)時 “H” レベルです。                                                                                                                              |

| VDD              | 6          | I デバイスに電力を供給するピンです。GNDピンでの説明のように、VDDピンに高周波フィルタを行うため0.1μFのセラミック・バイパス・コンデンサを使用してください。動作エネルギーは通常補助巻線から供給されます。起動時の誤動作を防止するためにVDDとGNDの間に一定のエネルギー蓄積能力をもつコンデンサが必要です。                                                                                                                                                               |

## 端子部品

| TERMINAL<br>NAME | NO. | I/O | DESCRIPTION <sup>(1)(2)(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS               | 3   | I   | $R_{CS} = \frac{(V_{PL} - V_{CS(os)}) (I_{CS(2)} - I_{CS(1)})}{I_{CS(2)} I_{P(1)} - I_{CS(1)} I_{P(2)}}$ $R_{PL} = \frac{(V_{PL} - V_{CS(os)}) (I_{P(2)} - I_{P(1)})}{I_{CS(1)} I_{P(2)} - I_{CS(2)} I_{P(1)}}$ <p>但し、</p> <ul style="list-style-type: none"> <li>• <math>I_{P1}</math>は低ライン、全負荷時の一次側ピーク電流です。</li> <li>• <math>I_{P2}</math>は高ライン、全負荷時の一次側ピーク電流です。</li> <li>• <math>I_{CS1}</math>は低ライン電圧時CSピンから流れ出す電力制限電流です。</li> <li>• <math>I_{CS2}</math>は高ライン電圧時CSピンに流れ込む電力制限電流です。</li> <li>• <math>V_{PL}</math>は電力制限(PL)のスレッショールドです。</li> <li>• <math>V_{CS(os)}</math>はCSのオフセット電圧です。</li> </ul>                                               |

| FB               | 2   | I   | オプトカプラのコレクタ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| GND              | 4   | -   | VDDへのバイパス・コンデンサ、 $C_{BP} = 0.1\mu F$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| OUT              | 5   | O   | パワーMOSFETのゲート                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OVP              | 7   | I   | $R_{OVP1} = \frac{1}{I_{OVP(line th)}} \left( \frac{N_B}{N_P} V_{BULK.ov} \right)$ $R_{OVP2} = R_{OVP1} \left( \frac{V_{OVP(load th)}}{\frac{N_B}{N_S} (V_{OUT.ov} + V_F) - V_{OVP(load th)}} \right)$ <p>但し、</p> <ul style="list-style-type: none"> <li>• <math>I_{OVP(line th)}</math>はOVPline電流のスレッショールドです。</li> <li>• <math>V_{BULK.ov}</math>は許容入力過電圧レベルです。</li> <li>• <math>V_{OVP(load th)}</math>はOVPloadです。</li> <li>• <math>V_{OUT.ov}</math>は許容出力過電圧レベルです。</li> <li>• <math>V_F</math>は二次側整流器の順方向電圧です。</li> <li>• <math>N_B</math>はバイアス巻線の巻数です。</li> <li>• <math>N_S</math>は二次側巻線の巻数です。</li> <li>• <math>N_P</math>は一次側巻線の巻数です。</li> </ul> |

(1) 端子部品表の全ての参照記号については図1を参照してください。

(2) 定数パラメータについては電気的特性表を参照してください。

(3) “UCC28600 Design Calculator” (TI文献番号SLVC104) または動作回路の電流、電圧、時間についての実験室での測定結果を参照してください。

## 端子部品

| TERMINAL<br>NAME | I/O<br>NO. | DESCRIPTION <sup>(1)(2)(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SS               | 1          | <p><math>C_{SS} &gt; I_{SS} \times \frac{t_{SS(min)}(\text{due power limit})}{A_{CS(FB)} \times (V_{PL} - V_{CS(os)})}</math></p> <p>但し、<math>t_{SS(min)}</math>は以下のうちの大きいほうです。</p> $t_{SS(min)} = \left[ \frac{-R_{OUT(ss)}C_{OUT}}{2} \ln \left( 1 - \frac{(V_{OUT} - \Delta V_{OUT(step)})^2}{R_{OUT(ss)}P_{LIM}} \right) \right]$ <p>or</p> $t_{SS(min)} = \left[ \frac{C_{OUT}V_{OUT}^2}{2P_{LIM}} \right]$ <ul style="list-style-type: none"> <li>• <math>R_{OUT(ss)}</math>はソフトスタート時の実効負荷インピーダンスです。</li> <li>• <math>\Delta V_{OUT(step)}</math>は負荷ステップによる<math>V_{OUT}</math>の許容変化量です。</li> <li>• <math>P_{LIM}</math>はプログラムされた電力制限レベルで単位はWです。</li> <li>• <math>A_{CS(FB)}</math>は電流検出ゲインです。</li> <li>• <math>V_{CS(os)}</math>はCSのオフセット電圧です。</li> </ul>                                                                                                                                           |

| STATUS           | 8          | $R_{ST2} = \frac{V_{BE(off)}}{I_{STATUS(\text{leakage})}}$ $R_{ST1} = \frac{R_{ST2} \times \left[ V_{DD(\text{uvlo-on})} - V_{BE(sat)} - R_{DS(on)} \times \left( \frac{I_{CC}}{\beta_{sat}} \right) \right] - R_{DS(on)}V_{BE(sat)}}{\left( \left( \frac{I_{CC}}{\beta_{sat}} \right) \times R_{ST2} \right) + V_{BE(sat)}}$ <p>但し、</p> <ul style="list-style-type: none"> <li>• <math>\beta_{SAT}</math>は飽和状態のトランジスタ<math>Q_{ST}</math>のゲインです。</li> <li>• <math>V_{BE(sat)}</math>は飽和状態のトランジスタ<math>Q_{ST}</math>のベース/エミッタ間電圧です。</li> <li>• <math>V_{DD(\text{uvlo-on})}</math>は起動スレッシホールドです。</li> <li>• <math>I_{CC}</math>は<math>Q_{ST}</math>のコレクタ電流です。</li> <li>• <math>I_{STATUS(\text{leakage})}</math>はSTATUSピンの最大リーク/オフ電流です。</li> <li>• <math>V_{BE(off)}</math>は<math>Q_{ST}</math>をオンにしないベース/エミッタ接合部の最大許容電圧です。</li> <li>• <math>R_{DS(on)}</math>はSTATUSの<math>R_{DS(on)}</math>です。</li> </ul> |

## 端子部品

| TERMINAL<br>NAME | I/O<br>NO. | DESCRIPTION <sup>(1)(2)(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD              | 6          | <p><math>C_{DD}</math>は以下のうちの大きいほうです。</p> $C_{DD} = \left[ \left( I_{DD} + C_{ISS} V_{OUT(hi)} f_{QR(max)} \right) \frac{T_{BURST}}{\Delta V_{DD(burst)}} \right]$ <p>or</p> $C_{DD} = \left[ \left( I_{DD} + C_{ISS} V_{OUT(hi)} f_{QR(max)} \right) \frac{t_{ss}}{\Delta V_{DD(uvlo)}} \right]$ $R_{DD} = \left( \frac{\pi}{4} \right) \left( \frac{N_B}{N_P} \right) \left[ \frac{V_{DS1(os)} f_{QR(max)} \sqrt{L_{LEAKAGE} (C_D + C_{SNUB})}}{I_{DD} + C_{ISS} V_{OUT(hi)} f_{QR(max)}} \right]$ $R_{SU} = \frac{V_{BULK(min)}}{I_{STARTUP}}$ <p>但し、</p> <ul style="list-style-type: none"> <li>• <math>I_{DD}</math>はUCC28600の動作電流です。</li> <li>• <math>C_{ISS}</math>はMOSFET M1の入力容量です。</li> <li>• <math>V_{OUT(hi)}</math>はOUTピンのVOHで、13V(typ)のVoutクランプまたは測定値です。</li> <li>• <math>f_{QR(max)}</math>は高ライン、最大負荷時のfSです。</li> <li>• <math>T_{BURST}</math>は測定バースト・モード期間です。</li> <li>• <math>\Delta V_{DD(burst)}</math>はバースト・モード時のUVLOに許容される<math>V_{DD}</math>リップルです。</li> <li>• <math>\Delta V_{DD(uvlo)}</math>はUVLOのヒステリシスで、<math>V_{DD}</math>または13Vのいずれか小さいほうです。</li> <li>• <math>V_{DS1(os)}</math>はドレイン/ソース間のオーバーシュート電圧量です。</li> <li>• <math>L_{LEAKAGE}</math>は一次側巻線の漏れインダクタンスです。</li> <li>• <math>C_D</math>はMOSFET M1の総ドレイン容量です。</li> <li>• <math>I_{STARTUP}</math>はUCC28600の<math>I_{DD}</math>起動電流です。</li> <li>• <math>C_{SNUB}</math>はスナバのコンデンサ値です。</li> </ul> |

図 1. Pin Termination Schematic

# アプリケーション情報

## 機能説明

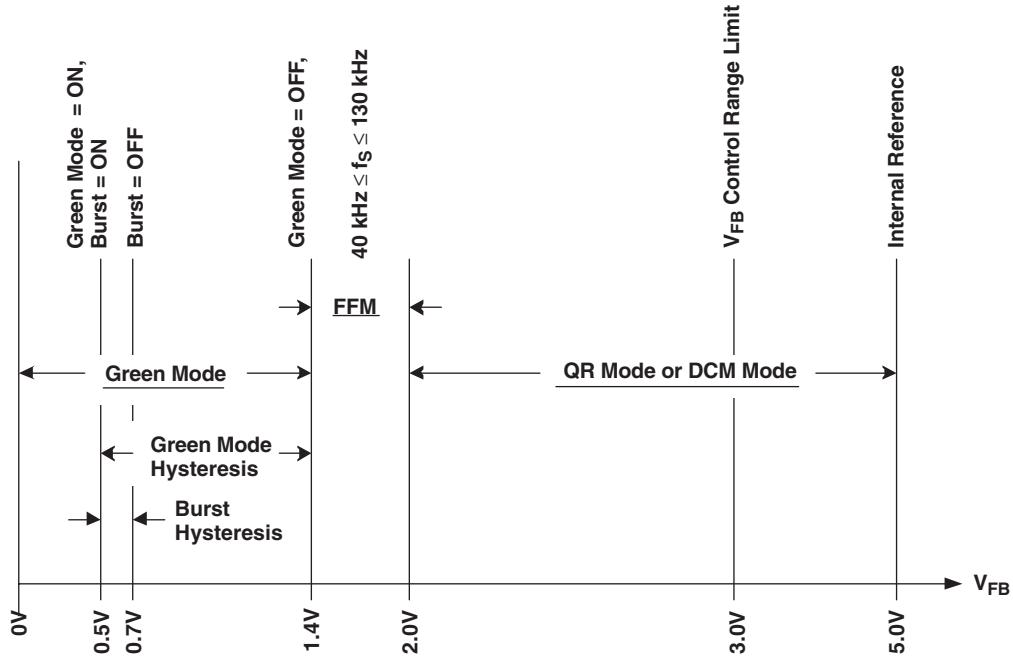

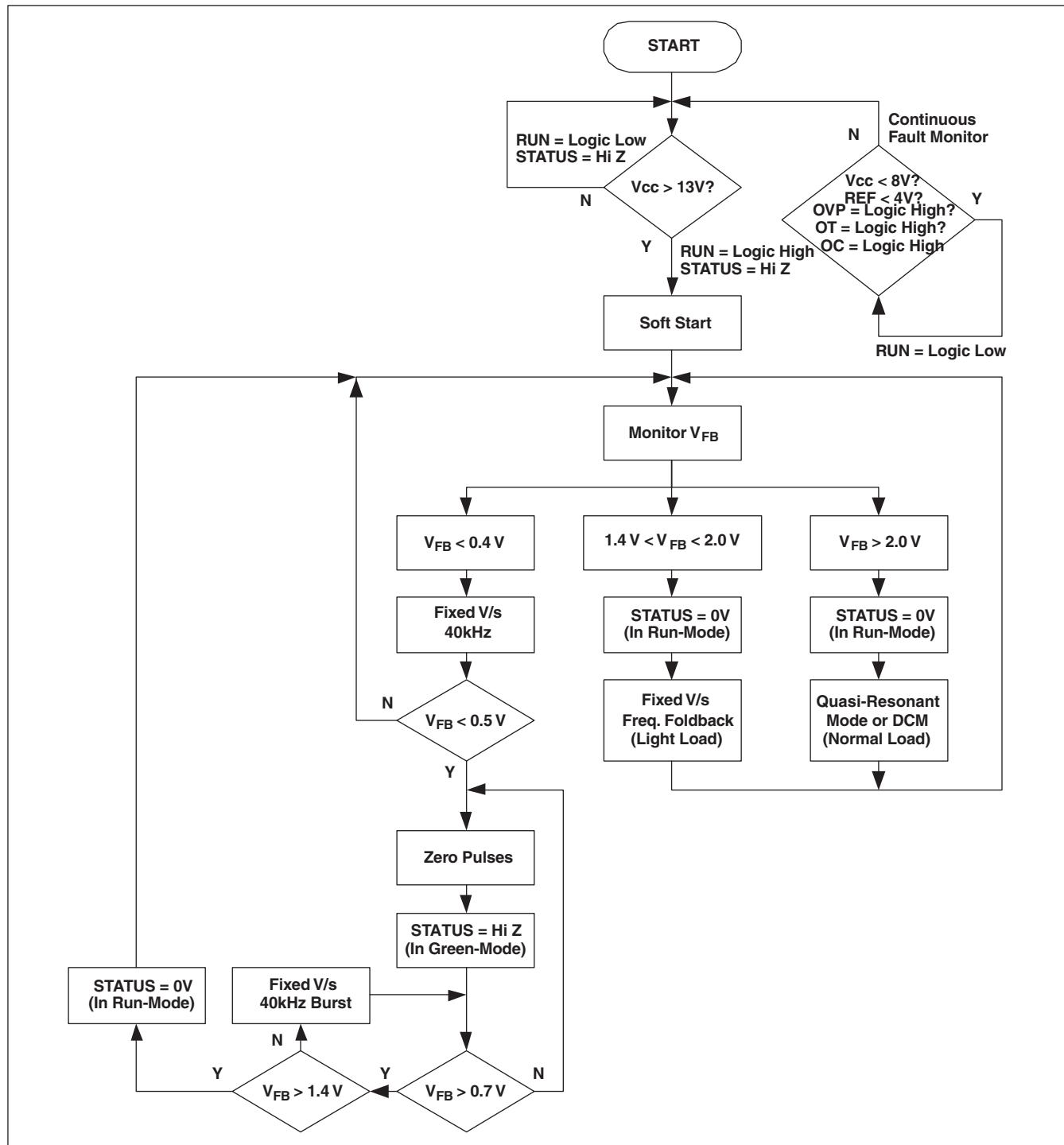

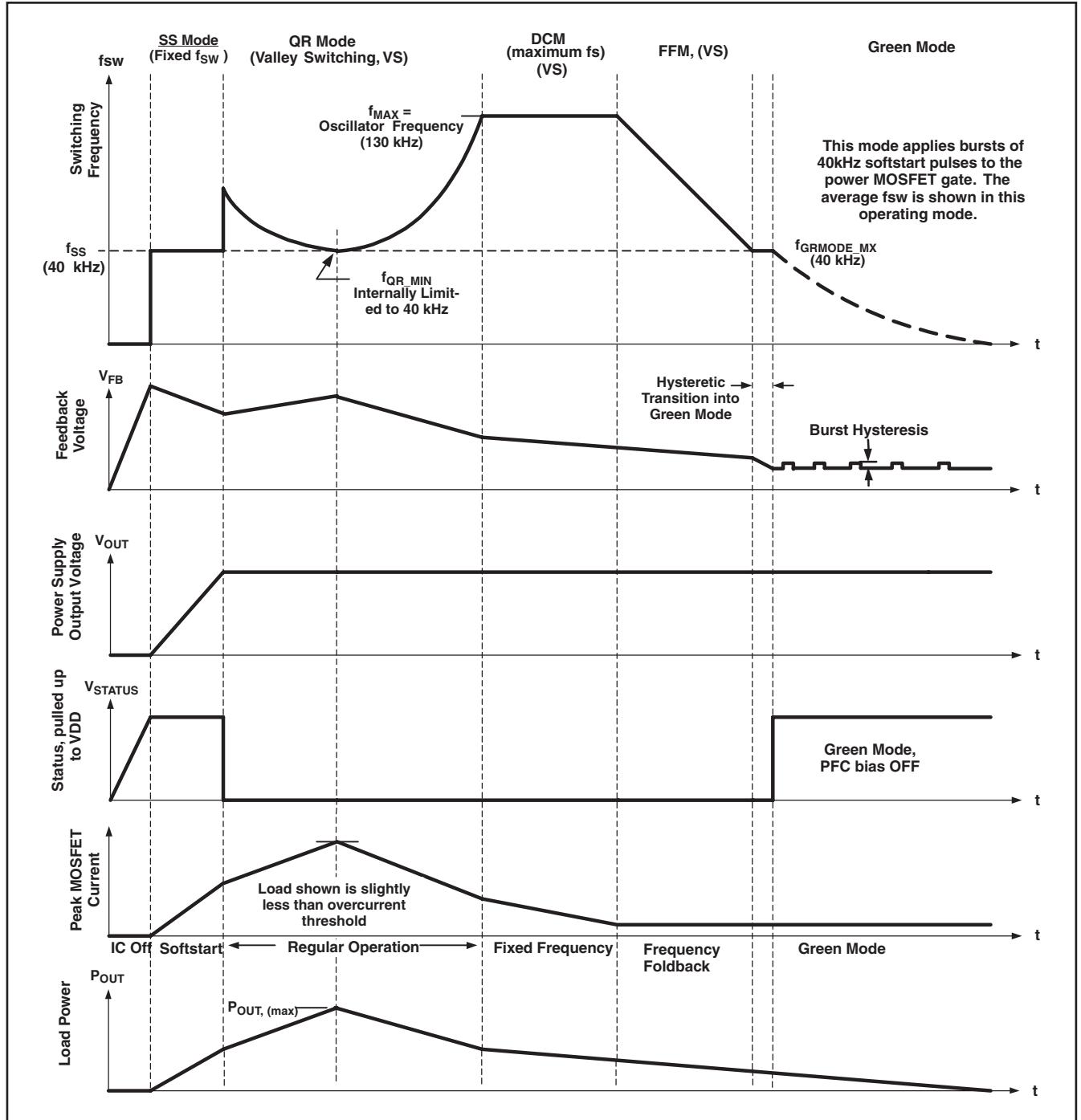

UCC28600は図3と図4に示されているようにマルチ・モードのコントローラです。動作モードはライン及び負荷の状態により決まります。全動作モード下で、UCC28600はスイッチ電流に基づいてOUT=“H”信号で処理を終了します。よって、UCC28600はパワーMOSFETの電流が常時制限できるよう常に電流モード・コントロールとして動作しています。

通常動作状態下では、状態遷移図2に示されているようにFBピンに入力される電圧レベルでUCC28600の各動作モードを制御しています。但し、ソフトスタートと異常への応答は例外で優先されます。ソフトスタート・モードのハードスイッチがコンバータを40kHzにコントロールします。ソフトスタート・モードはV<sub>FB</sub>がUVLO<sub>ON</sub>の後最初にV<sub>SS</sub>より低くなった時オフにラッ奇されます。UVLO<sub>OFF</sub>通過後次のUVLO<sub>ON</sub>までソフトスタート状態には復帰できません。

通常の定格動作負荷時(全定格電力の100%から約30%)、UCC28600はシステムを擬似共振モード(QRM)または不連続導通モード(DCM)でコントロールします。なお、DCM動作は最大スイッチング周波数(130kHz)にクランプされています。負荷が全定格電力の約30%から10%の間の場合、システムは周波数フォルダック・モード(FFM)で動作します。なお、このモードではピーク・スイッチ電流が一定で出力電圧はスイッチング周波数を変調することで安定化されます。事実上、FFMの動作は各スイッチング・サイクルでフライバック・トランジistorに一定のボルト・秒を加えたことになり、FFM動作での電圧の安定化はスイッチング周波数を130kHzから40kHzの範囲で変調させることにより実行されます。極端な軽負荷(全定格電力の約10%以下)の場合には、コンバータは40kHzのバースト・パルスを用いて制御されます。定常状態動作での上記境界はコンバータの設計パラメータに左右されるため概算であることに留意してください。

これらの機能を実行するための電気的接続については代表的アプリケーション・ブロック図を参照してください。

図 2. Mode Control with FBP in Voltage

図 3. Control Flow Chart

#### ☒ 4. Operation Mode Switching Frequencies

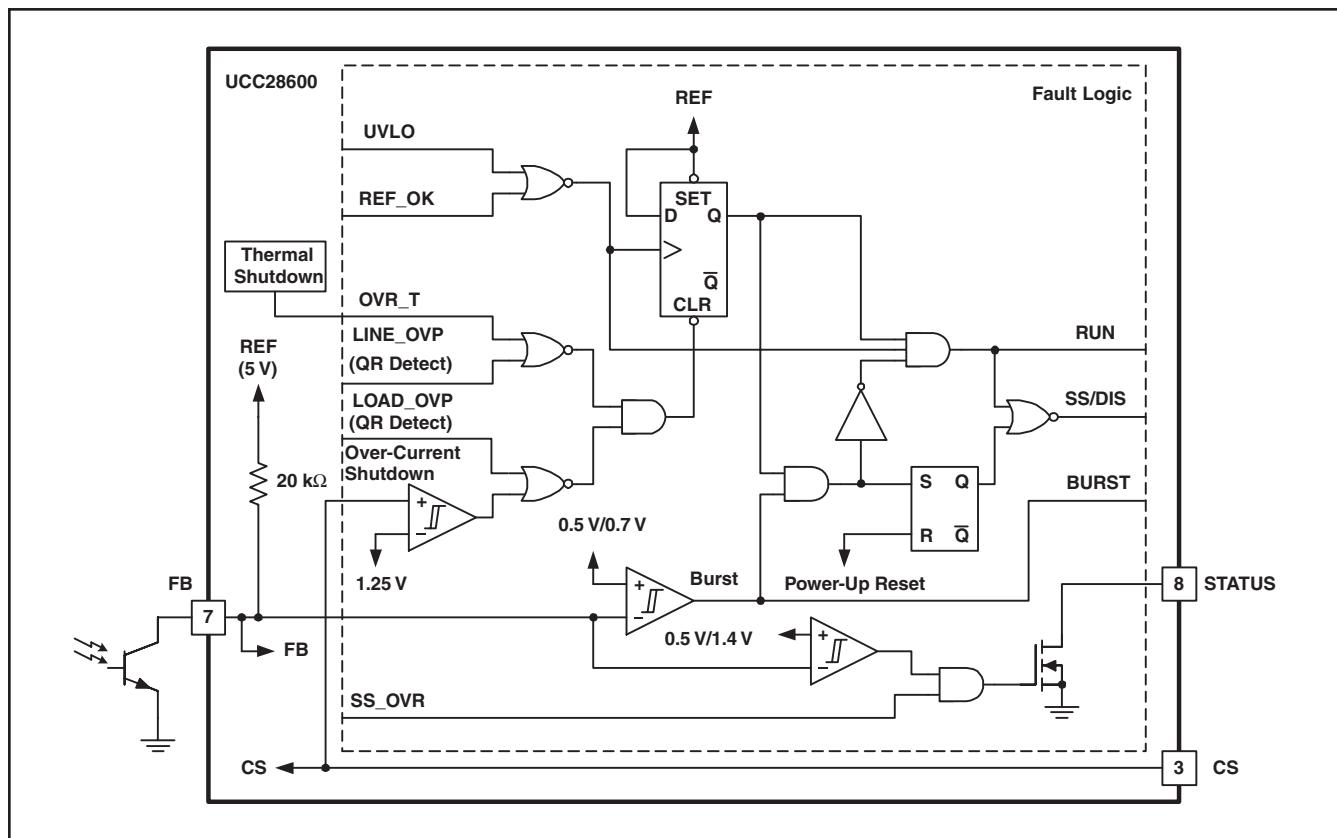

ブロック図/代表的アプリケーション図の機能ボックスの詳細を図5、図6、図7、図8に示します。これらの図では、どのようにUCC28600がFB電圧によるコマンドを実行し図2、図3、図4に示されている対応を行なうかが概念的に説明されています。また、この機能ボックスの詳細にはUCC28600に含まれている様々な異常検出とその対応についても説明されています。

全動作モード時、このコントローラは電流モード・コントローラとして動作します。このことにより、UCC28600はFB電圧をモニタすることができ重負荷、軽負荷、超軽負荷などの様々な負荷レベルの決定やそれらへの応答を行うことが可能になります。

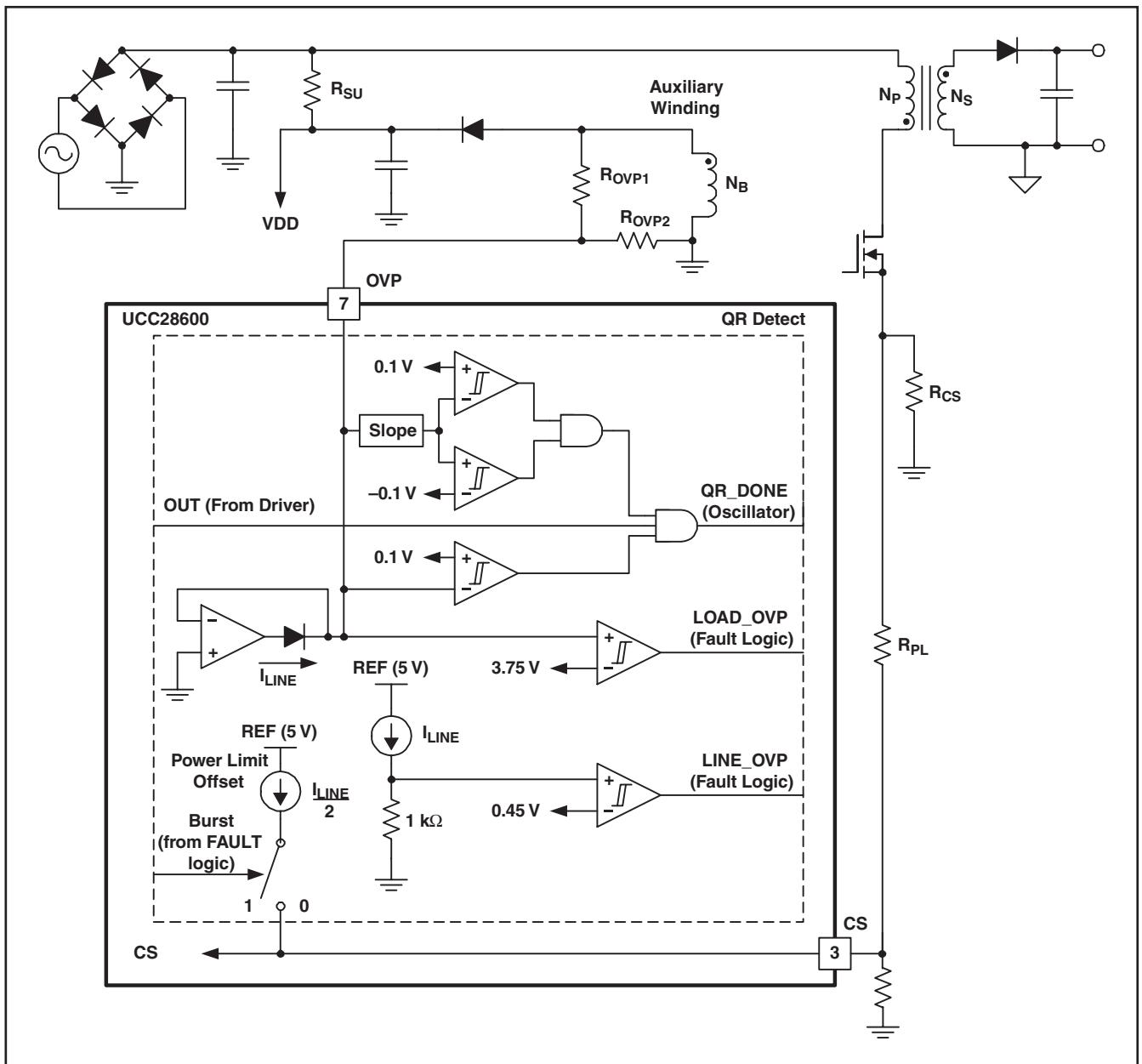

擬似共振モード及びDCMはフィードバック電圧V<sub>FB</sub>が2.0Vから4.0Vの場合に起こります。言い換えると、CS電圧は0.4V~0.8V間であるよう管理されます。サイクルごとの電力制限によりCS電圧のリミットは固定の0.8Vになります。また図8に示されているように、フォルト・ロジックの過電流シャットダウン・スレッショールドにより、短絡、異常等に対する保護機能も付加されます。図7のQR検出回路の電力制限機能により入力電圧に比例したオフセット電位がCS信号に加えられます。この電力制限機能は代表的アプリケーション図に示されているようにR<sub>PL</sub>により設定されます。

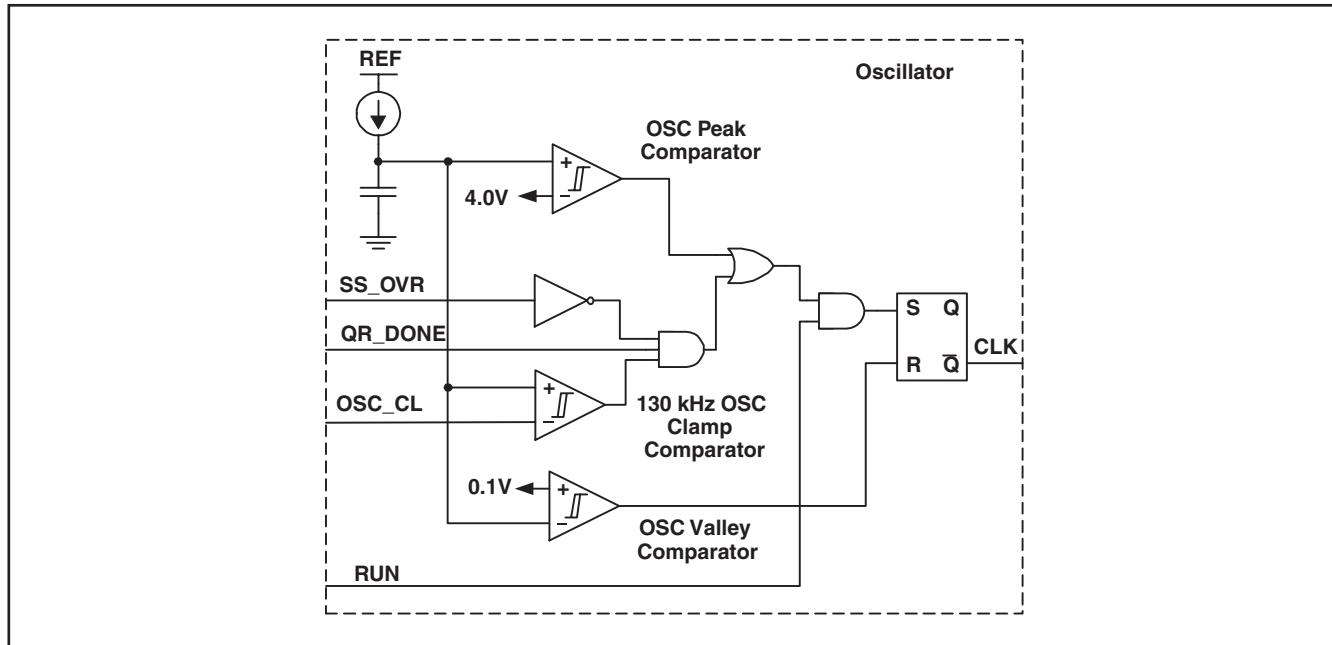

図 5. Oscillator Details

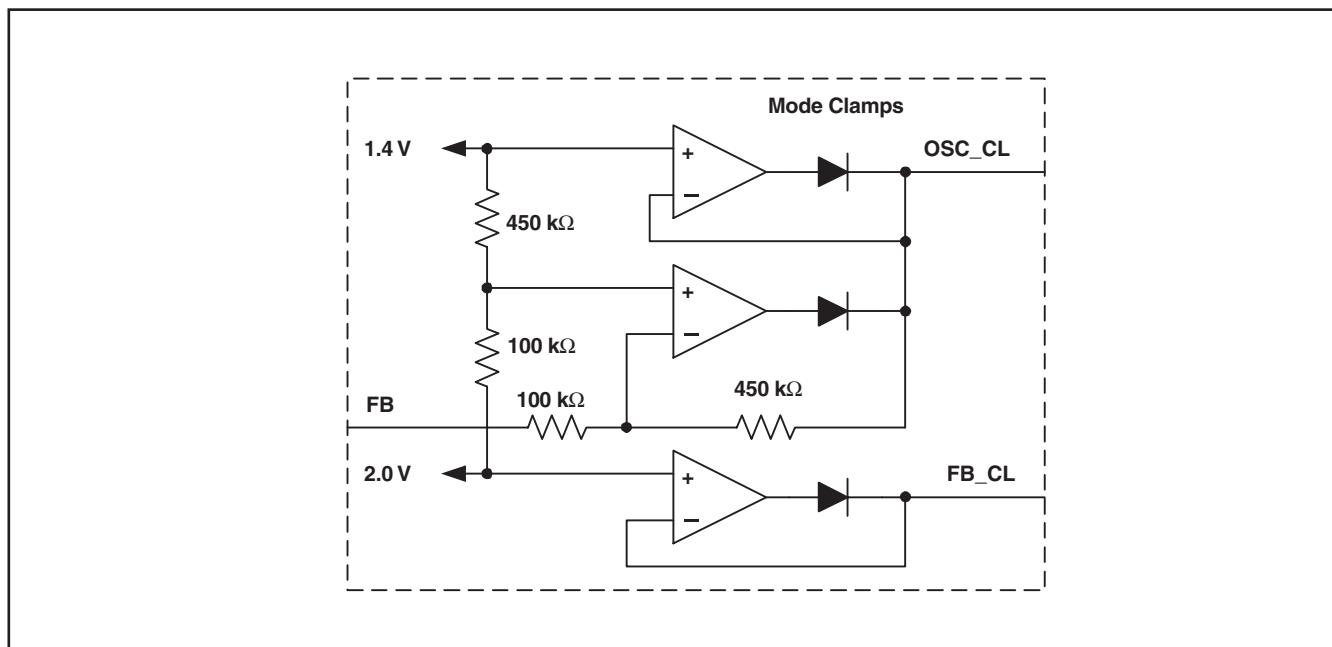

図 6. Mode Clamp Details

图 7. QR Detect Details

図8. Fault Logic Details

## 擬似共振/DCMコントロール

擬似共振(QR)及びDCM動作はフィードバック電圧 $V_{FB}$ が2.0Vから4.0Vの場合に起こります。言い換えると、CS電圧は0.4V～0.8Vであるかのよう管理されます。このコントロール・モードでは、OUTの立ち上りエッジは常時消磁後の共振リングイングの底部で起こります。共振底部(ゼロ電圧)のスイッチングはQR動作にとって不可欠な部分です。また、システムが最大スイッチング周波数クランプで動作している場合にもスイッチングは共振底部で行われます。すなわち、スイッチング動作が7.7μs(130kHz)の間隔の後に生じる最初の共振底部で起こるようDCM動作で周波数は変化します。またCSピンには内部に電流源 $1/2 I_{LINE}$ があることに注意してください。この電流源は“保護機能”の項で説明されるサイクルごとの電力制限機能の一部です。

## 周波数フォルドバック・モード・コントロール

周波数フォルドバック・モードでは、図8に示されているフォルト・ロジック、図6に示されているモード・クランプ回路の原理を使用します。最小動作周波数で、内部発振器の「こぎり波」のピーク電圧は4.0Vで最小電圧は0.1Vです。FB電圧が2.0V～1.4Vの時、図6のFB\_CL信号により発振器のピーク電圧をクランプすることで発振器は電圧制御発振器(VCO)モードになります。発振器の追加クランプ機能によりVCO動作は40kHz～130kHzに限定されます。FB\_CL電圧は変調器のコンパレータに入りCSコマンドを0.4Vにクランプします。

## グリーン・モード・コントロール

グリーン・モードでは図8に示されているフォルト・ロジック、図6に示されているモード・クランプ回路の原理を使用します。OSC\_CL信号はグリーン・モードの動作周波数を40kHzにクランプします。従って、FB電圧が1.4V～0.5Vの時、コントローラは負荷に過度のエネルギーを送るよう指示し、言い換えると誤差を大きくFBを低くします。FBが0.5Vに達した時、OUTパルスは終了し、FBが0.7Vに達するまで再開しません。このモードでは、コンバータはOUTパルスが0.4Vの固定CS電圧レベルで終了するヒステリシスを持った制御で動作します。電力制限のオフセットはグリーン・モードではオフになり、図8で表されているように、FBが1.4Vより高くなった時オンに復帰します。グリーン・モードでは軽負荷状態時スイッチング損失を最小限に抑え、効率を上げるために平均スイッチング周波数を低減します。

## フォルト・ロジック

高機能なロジック制御回路により異常検出が調整され電源復帰が適切に行われます。例えば、このことにより過熱保護に対する制御が行われます。入力の過電圧保護(入力OVP)と負荷のOVPはこのブロックで実行されます。ロジック制御回路は内部の基準電圧から電源の供給を受けていますため、内部の基準電圧が4.5Vより低い時には動作できません。サーマル・シャットダウン、ラインOVP、負荷OVP、基準電圧などの異常が検出されると、UCC28600はシャットダウン/リトライ・サイクルを行います。

ラインOVP及び負荷OVPを設定するには図8のフォルト・ロジック図、図7のQR検出図を参照してください。負荷OVPを設定するには、 $R_{OVP1}$ - $R_{OVP2}$ の分圧比を目的とする出力シャットダウン電圧で3.75Vとなるよう選択してください。ラインOVPを設定するには、最大許容入力電圧時パワーMOSFETのオン時間で $V_{OVP}$ が0.45Vの時450μAの電流が流れるよう $R_{OVP1}$ - $R_{OVP2}$ の合成インピーダンスを選択してください。

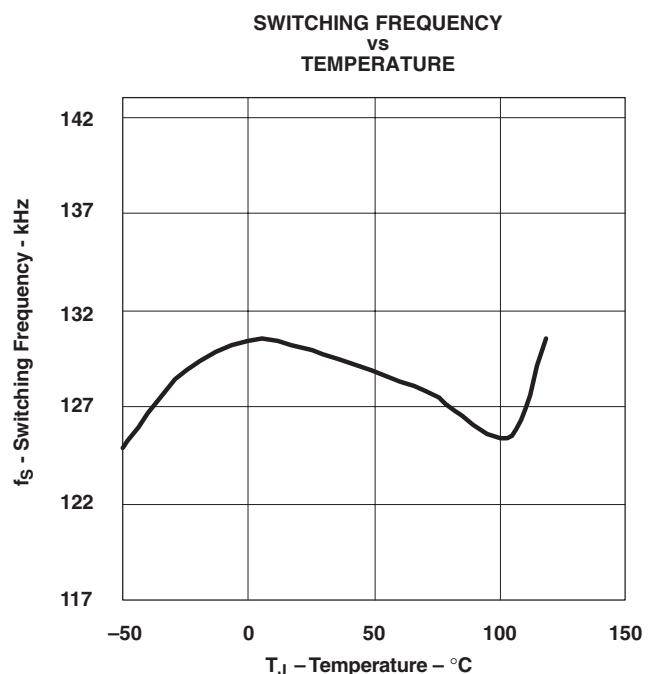

## 発振器

発振器は、図5に示されているように、内部で設定及びトリミングされており、図5の回路で標準130kHzの最大動作周波数

にクランプされています。また、40kHzの最小周波数クランプもあります。FB電圧が40kHzより低い動作を行なうとすると、コンバータはグリーン・モードで動作します。

## ステータス

STATUSピンは図8に示されているようにオープン・ドレイン出力です。ステータス出力はFBが0.5Vより低くなった時オフ状態になり、FBが1.4Vより高くなった時オン状態(GNDに対し低インピーダンス)に戻ります。このピンは、図9に示されているように、外部のPFC段のバイアス電源をコントロールするのに使用されます。この機能を実行するための重要な素子は、図に示されている $Q_{ST}$ 、 $R_{ST1}$ 、 $R_{ST2}$ です。抵抗 $R_{ST1}$ 及び $R_{ST2}$ はPFCが動作可能な条件にある時に $Q_{ST}$ を飽和させるように選択されます。グリーン・モード時、STATUSピンはハイ・インピーダンスになり、 $R_{ST1}$ により $Q_{ST}$ はオフになるため、バイアス電源が節約されます。必要なら、 $V_{CC}$ をPFCコントローラの安全動作範囲に保持するためツェナー・ダイオードと抵抗( $D_{Z1}$ と $R_{CC}$ )を使用します。

図 9. Using STATUS for PFC Shut-Down During Green Mode

## 動作モードの設定

動作モードの境界は、ブロック図/アプリケーション図に示されているフライバック・トランスと4つの部品R<sub>P1</sub>、R<sub>CS</sub>、R<sub>OVP1</sub>、R<sub>OVP2</sub>により設定されます。

モードに大きな影響を与えるトランスの特性は一次側のインダクタンスと、一次側に影響する出力電圧の大きさです。それほどの重要性はありませんが、動作モードの境界はMOSFETの出力容量とトランスの漏れインダクタンスにも影響されます。ここでの設計手順は最大負荷/最大ライン時DCM/CCM境界で動作するインダクタンスと応答出力電圧を選択することです。実際のインダクタンスはインダクタンスとパワーMOSFETのドレインで測定された総浮遊容量間で構成されるためかなり小さくなければなりません。これによりQR/DCM動作境界が設定されます。他の全モードの境界は発振器及びグリーン・モードのブロックのスレッシホールドで予め設定されています。

4つの部品R<sub>P1</sub>、R<sub>CS</sub>、R<sub>OVP1</sub>、R<sub>OVP2</sub>は機能の相互作用をそれぞれ考慮して設定しなければなりません。トランスのパラメータと抵抗の設定間で平衡をとり目的とする結果を得るために“UCC28600 Design Calculator”(TI文献番号SLVC104)を活用することを強く勧めます。

## 保護機能

UCC28600は大型でフル機能のコントローラに通常的に見られる多くの保護機能をもっています。これらの機能がどのようにコントロール機能に組み込まれているかを示す詳細なブロック説明についてはブロック図/代表的アプリケーション及び図1、図4、図5、図6、図7を参照してください。

## 過熱保護

過熱による検出制御は一般的にサブストレート部の温度が140°Cに達した時起ります。サブストレート部の温度がヒステリシス分以上に温度が減少すると再起動が可能になります。過熱異常になると、ソフトスタートのC<sub>SS</sub>は放電されSTATUSはハイ・インピーダンスになります。

## サイクルごとの電力制限

CS電圧と電力制限のオフセットの和が0.8Vを越えた時サイクルは終了します。

QRフライバック・コンバータの全ライン電圧範囲にわたって電力を制限するためには、ライン電圧によりスイッチング周波数が予測可能で変動するためCSピンの電圧は一次側電流に比例する成分とライン電圧に比例する成分の和をもたなければなりません。電力制限時、CSピンの電圧と内部のCSオフセットの和はPWMコンパレータで1.2Vの一定の基準電圧と比較されます。従って、サイクルごとの電力制限時、ピークのCS電圧は通常0.8Vです。

OVPピンから流れ出す電流(I<sub>LINE</sub>)はCSピンに接続されているI<sub>LINE</sub>の1/2の電流源に影響します。電力制限機能はCSピンと電流検出抵抗間の抵抗R<sub>P1</sub>により設定することができます。電流I<sub>LINE</sub>はトランスの巻線比N<sub>B</sub>/N<sub>P</sub>と抵抗R<sub>OVP1</sub>により入力電圧に比例します。電流I<sub>LINE</sub>は入力の過電圧保護を設定するため設定されます。抵抗R<sub>P1</sub>により電流検出信号に入力電圧に比例した電圧が付加されます。付加される電圧量が適性であるとサイクル毎を基準とした電力制限に効果的になります。R<sub>CS</sub>、R<sub>P1</sub>、R<sub>OVP1</sub>、R<sub>OVP2</sub>は機能の相互作用により一式で調整しなければならないことに注意してください。

## 電流制限

一次側の電流がCSピンの電圧が1.25Vで表される最大電流レベルを越えた時、このデバイスはシャットダウン動作をします。UVLO<sub>OFF</sub>/UVLO<sub>ON</sub>のサイクル後に再起動動作が行われます。

## 過電圧保護

入力及び負荷の過電圧保護はトランスの巻線比、R<sub>OVP1</sub>、R<sub>OVP2</sub>により設定されます。OVPピンにはソース電流のみ供給可能な0Vの電圧源があります。なお、OVPはシンク電流は供給できません。

ラインの過電圧保護はOVPピンが0Vにクランプされた時起ります。バイアス巻線が負極性である時、OUT=“H”レベルまたは共振リングの一部で、0Vの電圧源がOVPを0Vにクランプし、OVPピンから流れ出す電流がLine\_OVPコンパレータとQR検出回路にミラーリングされます。Line\_OVPコンパレータはOVPが450μAより大きな電流を流すとシャットダウン/再起動・シーケンスを起動します。

負荷の過電圧保護はOVPピンの電圧が正極性である時起ります。バイアス巻線が正極性である時、消磁または共振リングの一部で、OVP電圧は正極性です。OVP電圧が3.75Vより大きいと、デバイスはシャットダウン動作をします。UVLO<sub>OFF</sub>/UVLO<sub>ON</sub>のサイクル後に再起動動作が行われます。

## 低電圧検出

バイアスが好ましくない状態の時の誤動作を保護するよう保護機能が備えられています。低電圧検出回路(UVLO)はUVLOスレッシホールドより低い電圧での誤動作を防止するため常時VDDをモニタしています。

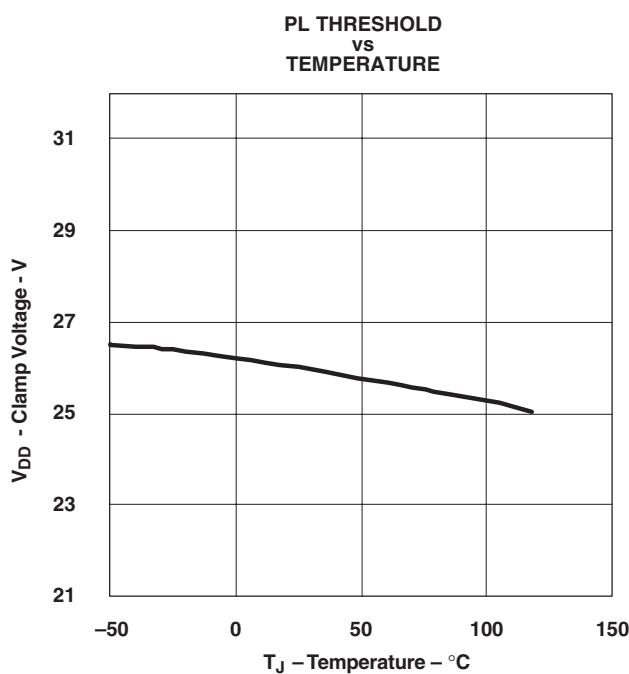

## TYPICAL CHARACTERISTICS

図 10

図 11

図 12

図 13

# 実用デザイン・ノート

## 理想的でない電流検出値

抵抗 $R_{CS}$ 、 $R_{PL}$ 、 $R_{OVP1}$ 、 $R_{OVP2}$ はコンバータの機能的な相互作用を考慮して設定しなければなりません。しばしば、 $R_{CS}$ の理想値は電流検出抵抗の選択範囲が電力制限の要求公差を満足するには粗すぎるため使用できなことがあります。この問題は、図14に示されているように、 $R_{CS}$ の次に大きな有効値と、CS信号をその理想値に減衰するため理想の $R_{PL}$ 値に等しいテブナン抵抗をもつ抵抗分割を使用することで解決することができます。この回路変更についての式は以下のようになります。

$$R_{PL1} = R_{PL} \times \left( \frac{R_{CS}}{R_{DCS}} \right) \quad (2)$$

- $R_{DCS}$  = 理想だが標準的ではない電流検出抵抗の値

- $R_{PL}$  = 電力制限抵抗の前回計算値

図 14. Modifications to Fita Standard Current Sense Resistor Value

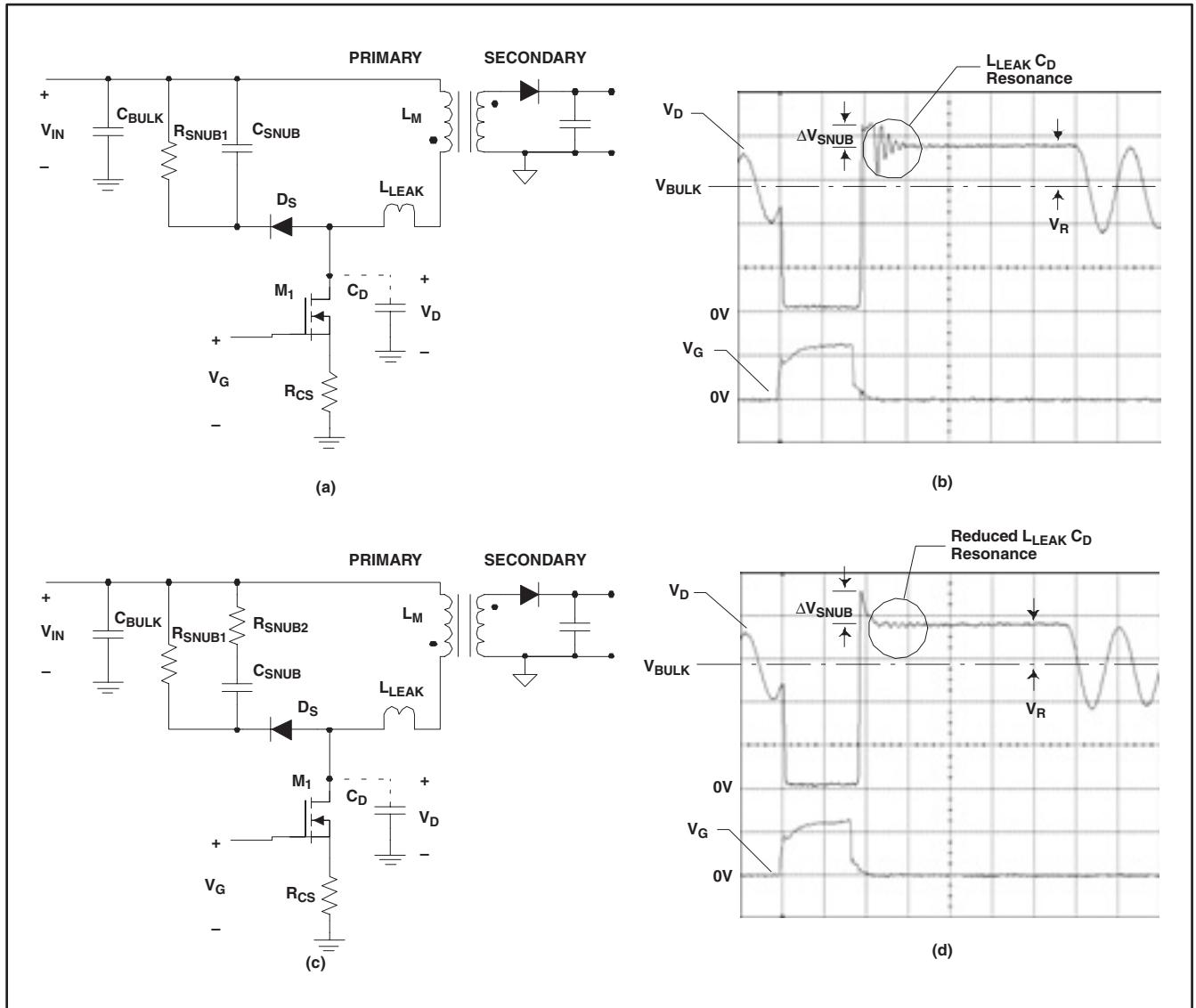

## スナバによる減衰

負荷OVPに標準で約2μsの遅延があるにもかかわらず、漏れインダクタンスとMOSFETのドレイン容量間の共振により誤つて負荷のOVP異常が生じる可能性があります。バイアス巻線は一次巻線によく結合するためオーバーシュートとリンギングに

敏感です。この問題を取り除く手法に、図15に示されているように、RCDスナバの代わりにR<sup>2</sup>CDスナバを用いることがあります。RCDスナバに追加されたダンピング抵抗がスナバ・ダイオードがオフに整流している時ドレイン・コンデンサとインダクタンス間のリンクギングを低減します。

図 15. (a)RCD Snubber, (b)RCD Snubber Waveform, (c)R<sup>2</sup>CD Snubber, (d)R<sup>2</sup>CD Snubber Waveform

RCDスナバの設計と同じ手順を使ってR<sup>2</sup>CDスナバの設計を始めます。次に、ダンピング抵抗R<sub>SNUB2</sub>を追加します。その手順は以下のようになります。

$$\text{Pick } \frac{\Delta V_{\text{SNUB}}}{V_R} = \text{ between 0.5 and 1} \quad (4)$$

$\Delta V_{\text{SNUB}}$ に対するコンデンサを選択します。

$$C_{\text{SNUB}} = \frac{I_{\text{CS(peak)}}^2 L_{\text{LEAK}}}{(V_R + \Delta V_{\text{SNUB}})^2 - V_R^2} \quad (5)$$

$C_{\text{SNUB}}$ を放電するR<sub>SNUB</sub>を選びます。

$$R_{\text{SNUB1}} = \left( \frac{1}{2} + \frac{V_R}{\Delta V_{\text{SNUB}}} \right) \frac{1}{C_{\text{SNUB}}} \left( \frac{1}{f_{S(\max)}} - \frac{L_{\text{LEAK}} I_{\text{CS(peak)}}}{\Delta V_{\text{SNUB}}} \right) \quad (6)$$

$$P(R_{\text{SNUB1}}) = \frac{V_R}{R_{\text{SNUB1}}} + \frac{1}{2} I_{\text{CS(peak)}}^2 L_{\text{LEAK}} f_{S(\max)} \quad (7)$$

Qが1.7~2.2にI<sub>LEAK</sub>-C<sub>SNUB</sub>共振を低下させるようR<sub>SNUB2</sub>を選びます。

$$R_{\text{SNUB2}} = \frac{\Delta V_{\text{SNUB}}}{I_{\text{CS(peak)}}} \quad (8)$$

$$P(R_{\text{SNUB}}) = I_{\text{CS(peak)}}^2 R_{\text{SNUB2}} \left[ \frac{1}{3} \frac{L_{\text{LEAK}} f_{S(\max)}}{\left( V_R + \frac{\Delta V_{\text{SNUB}}}{2} \right)} \right] \quad (9)$$

当初選択した $\Delta V_{\text{SNUB}}$ に対し以下になります。

$$Q = \sqrt{\frac{2V_R}{\Delta V_{\text{SNUB}}} + 1} \quad (10)$$

## 参考資料

1. Power Supply Seminar SEM-1400 Topic 2: Design And Application Guide For High Speed MOSFET Gate Drive Circuits, by Laszlo Balogh, Texas Instruments Literature Number SLUP133

2. Datasheet, UCC3581 Micro Power PWM Controller, Texas Instruments Literature Number SLUS295

3. Datasheet, UCC28051 Transition Mode PFC Controller, Texas Instruments Literature Number SLUS515

4. UCC28600 Design Calculator, A QR Flyback Designer.xls, spreadsheet for Microsoft Excel 2003, Texas Instruments Literature Number SLVC104

## 関連製品

- UCC28051 Transition Mode PFC Controller (SLUS515)

- UCC3581 Micro Power PWM Controller (SLUS295)

**PACKAGING INFORMATION**

| Orderable part number      | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|----------------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">UCC28600D</a>  | Active        | Production           | SOIC (D)   8   | 75   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 105   | 28600D              |

| UCC28600D.A                | Active        | Production           | SOIC (D)   8   | 75   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 105   | 28600D              |

| UCC28600D.B                | Active        | Production           | SOIC (D)   8   | 75   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 105   | 28600D              |

| UCC28600DG4                | Active        | Production           | SOIC (D)   8   | 75   TUBE             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 105   | 28600D              |

| <a href="#">UCC28600DR</a> | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 105   | 28600D              |

| UCC28600DR.A               | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 105   | 28600D              |

| UCC28600DR.B               | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 105   | 28600D              |

| UCC28600DRG4               | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 105   | 28600D              |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF UCC28600 :**

- Automotive : [UCC28600-Q1](#)

NOTE: Qualified Version Definitions:

- Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

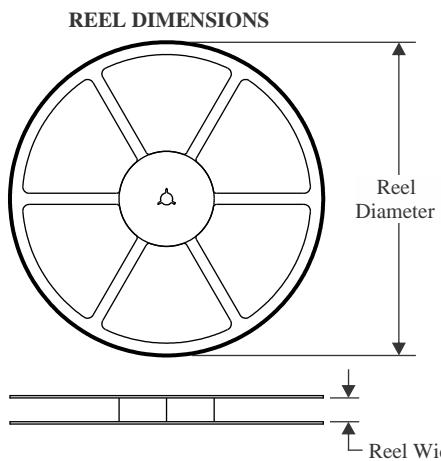

## TAPE AND REEL INFORMATION

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

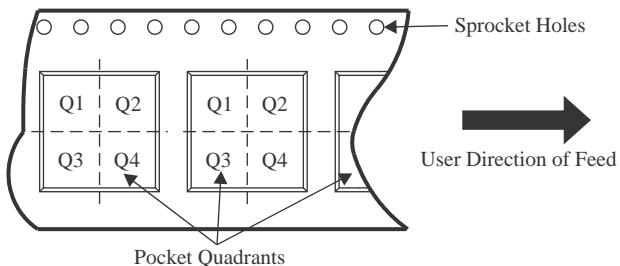

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| UCC28600DR | SOIC         | D               | 8    | 2500 | 330.0              | 12.4               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

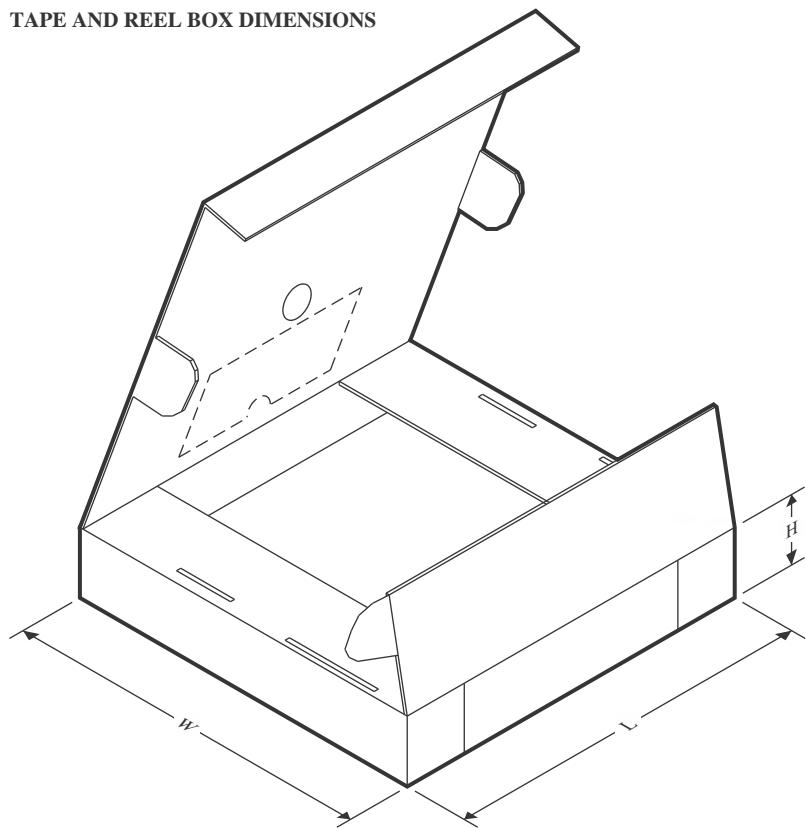

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UCC28600DR | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

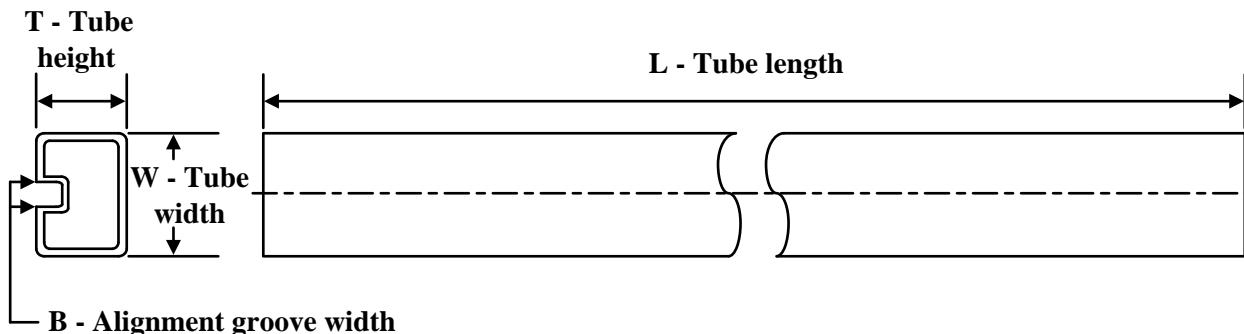

**TUBE**

\*All dimensions are nominal

| Device      | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|-------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| UCC28600D   | D            | SOIC         | 8    | 75  | 507    | 8      | 3940         | 4.32   |

| UCC28600D.A | D            | SOIC         | 8    | 75  | 507    | 8      | 3940         | 4.32   |

| UCC28600D.B | D            | SOIC         | 8    | 75  | 507    | 8      | 3940         | 4.32   |

| UCC28600DG4 | D            | SOIC         | 8    | 75  | 507    | 8      | 3940         | 4.32   |

D0008A

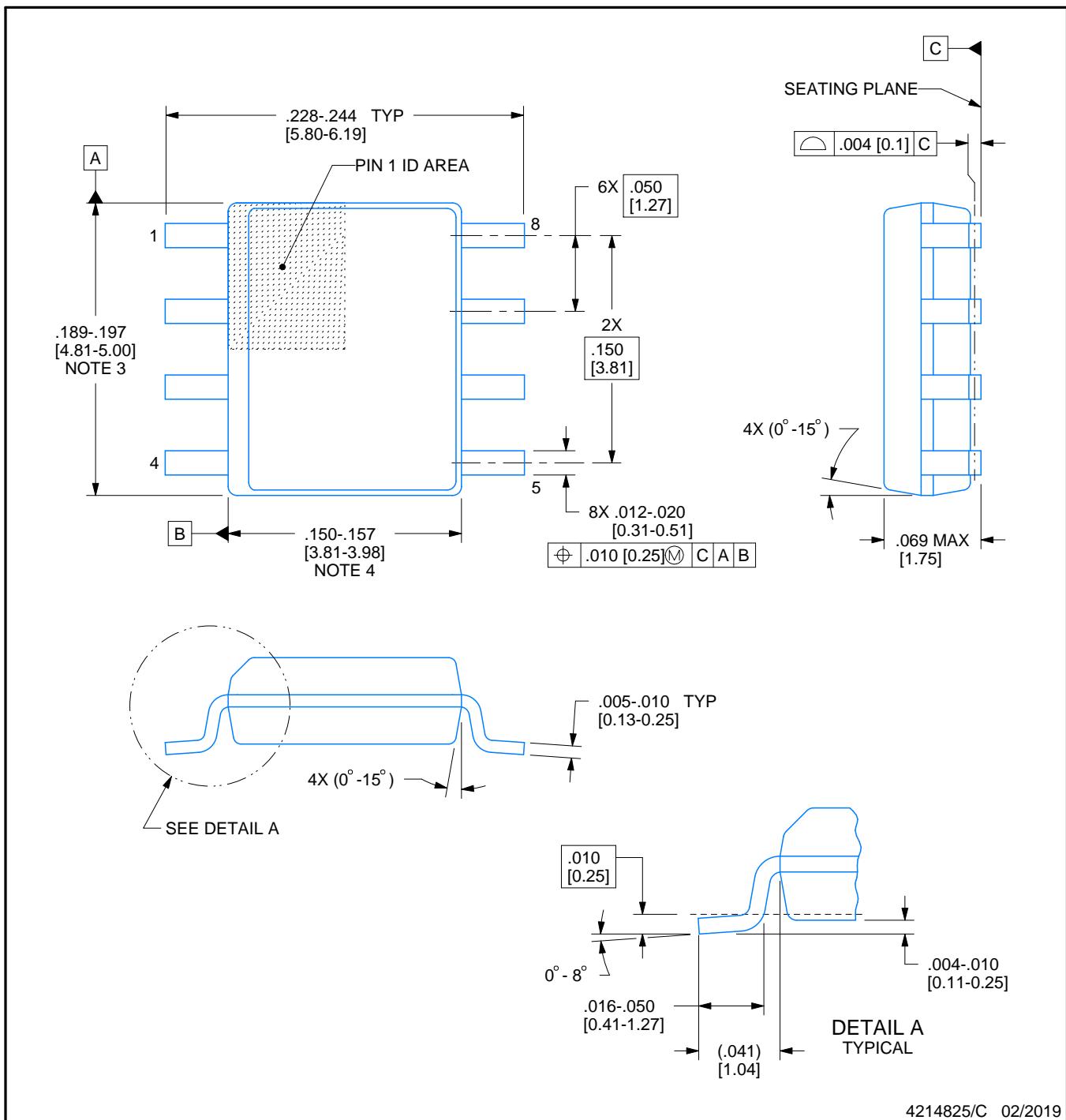

# PACKAGE OUTLINE

## SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

4214825/C 02/2019

### NOTES:

- Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches.

- Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- This dimension does not include interlead flash.

- Reference JEDEC registration MS-012, variation AA.

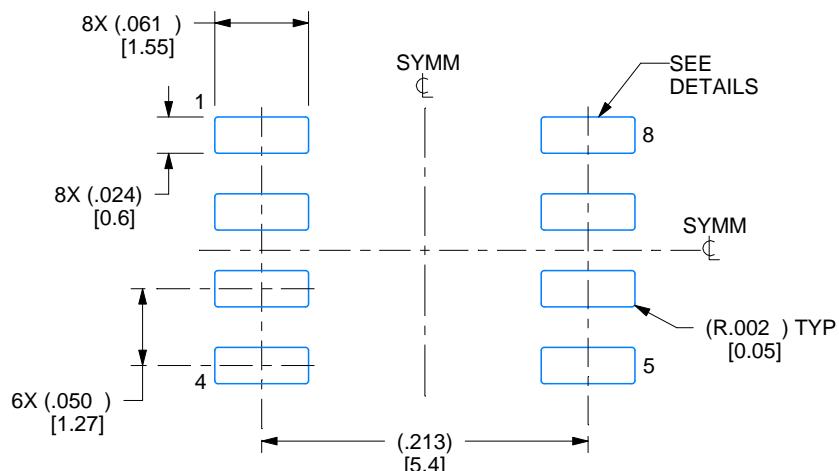

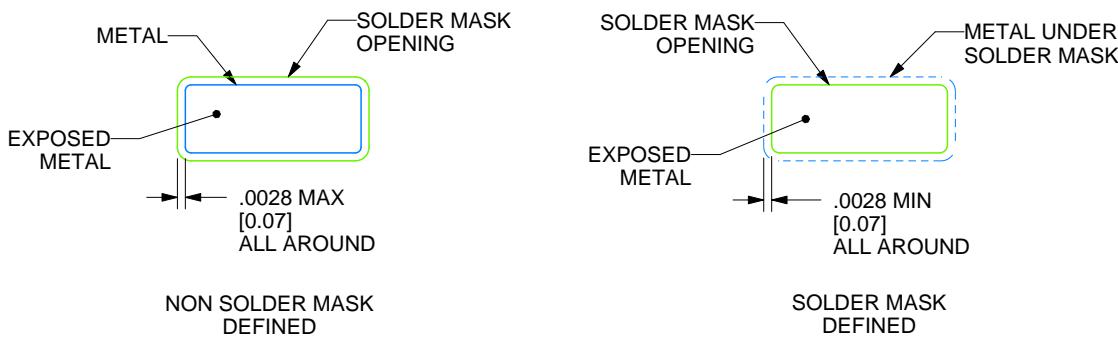

# EXAMPLE BOARD LAYOUT

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:8X

SOLDER MASK DETAILS

4214825/C 02/2019

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

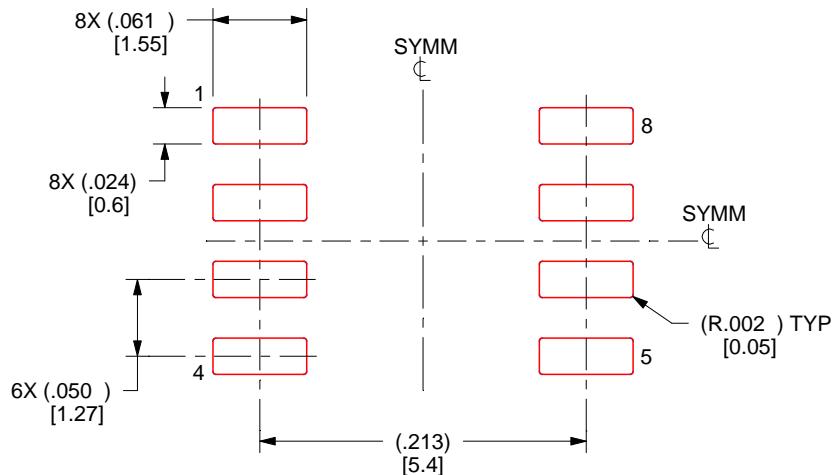

# EXAMPLE STENCIL DESIGN

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

SOLDER PASTE EXAMPLE

BASED ON .005 INCH [0.125 MM] THICK STENCIL

SCALE:8X

4214825/C 02/2019

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月