# UCCx813-x 低消費電力、エコノミー、BiCMOS、電流モード PWM

# 1 特長

- 100µA の開始時消費電流

- 500µA の標準動作消費電流

- 1MHz に対する動作

- 内部ソフトスタート

- 内部的なフォルトソフトスタート

- 電流センス信号の内部リーディング エッジ ブランキン グ機能

- 1A のトーテムポール出力

- 電流検出からゲートドライブ出力への標準応答時間: 70ns

- 基準電圧の許容誤差:1.5%

- UCC3802、UC3842、および UC3842A デバイスファ ミリと同じピン配置

# 2 アプリケーション

- スイッチ モード電源 (SMPS)

- DC/DC コンバータ

- パワー モジュール

- 産業用 PSU

- バッテリ駆動 PSU

# 3 説明

UCC3813-x デバイス ファミリは、 高速で低消費電力の IC で、オフラインおよび DC/DC 固定周波数電流モードのス イッチング電源を最小の部品数で設計するため必要な、 すべての制御および駆動部品が含まれています。

これらのデバイスは、UC384x デバイス ファミリとピン構成 が同じで、内部的なフルサイクルソフトスタートや、電流セ ンス入力の内部リーディングエッジ ブランキングなどの追 加機能も提供します。

UCC3813-x デバイス ファミリは、各種のパッケージ オプ ション、温度範囲オプション、最大デューティサイクルの選 択、クリティカル電圧レベルの選択が使用可能です。 UCC3813-3 や UCC3813-5 のようなリファレンス電圧が 低いデバイスは、バッテリ駆動システムに最適です。一 方、リファレンス電圧が高く、UVLO ヒステリシスも大きい UCC3813-2 および UCC3813-4 は、オフライン電源での 使用に理想的な選択肢となります。

UCC2813-x デバイス シリーズは-40  $^{\circ}$ C ~ 85  $^{\circ}$ C、 UCC3813-x デバイス シリーズは 0°C~70°Cでの動作が 規定されています。

# 製品情報

| 部品番号 (1)               | パッケージ     | 本体サイズ (公称)      |

|------------------------|-----------|-----------------|

|                        | PDIP (8)  | 6.35mm × 9.81mm |

| UCC2813-x<br>UCC3813-x | SOIC (8)  | 3.91mm × 4.90mm |

| 0000010 X              | TSSOP (8) | 4.40mm × 3.00mm |

利用可能なすべてのパッケージについては、データシートの末尾 にある注文情報を参照してください。

Copyright © 2016, Texas Instruments Incorporated

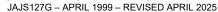

ブロック図

# 目次

| <b>1</b> 特長 1     | 7.4 デバイスの機能モード         | <mark>22</mark> |

|-------------------|------------------------|-----------------|

| 2 アプリケーション1       | 8 アプリケーションと実装          | <mark>23</mark> |

| 3 説明 1            | 8.1 アプリケーション情報         | <mark>23</mark> |

| <b>4</b> デバイス比較表3 | 8.2 代表的なアプリケーション       | 23              |

| 5 ピン構成および機能3      | 8.3 電源に関する推奨事項         | 35              |

| 6 仕様4             | 8.4 レイアウト              | 36              |

| 6.1 絶対最大定格4       | 9 デバイスおよびドキュメントのサポート   | 38              |

| 6.2 ESD 定格        | 9.1ドキュメントのサポート         | 38              |

| 6.3 推奨動作条件4       | 9.2 関連リンク              | 38              |

| 6.4 熱に関する情報5      | 9.3ドキュメントの更新通知を受け取る方法  | 38              |

| 6.5 電気的特性5        | 9.4 サポート・リソース          | 38              |

| 6.6 代表的特性7        | 9.5 商標                 | 38              |

| 7 詳細説明10          | 9.6 静電気放電に関する注意事項      | 38              |

| 7.1 概要10          | 9.7 用語集                | 39              |

| 7.2 機能ブロック図10     | 10 改訂履歴                | 39              |

| 7.3 機能説明10        | 11 メカニカル、パッケージ、および注文情報 |                 |

|                   |                        |                 |

# 4 デバイス比較表

| 部品番号 <sup>(1)</sup> | 最大デューティ サイク<br>ル | 基準電圧 | ターンオン スレッショル<br>ド | ターンオフ スレッショル<br>ド | 単位 |

|---------------------|------------------|------|-------------------|-------------------|----|

| UCCx813-0           | 100%             | 5    | 7.2               | 6.9               | V  |

| UCCx813-1           | 50%              | 5    | 9.4               | 7.4               | V  |

| UCCx813-2           | 100%             | 5    | 12.5              | 8.3               | V  |

| UCCx813-3           | 100%             | 4    | 4.1               | 3.6               | V  |

| UCCx813-4           | 50%              | 5    | 12.5              | 8.3               | V  |

| UCCx813-5           | 50%              | 4    | 4.1               | 3.6               | V  |

<sup>(1)</sup> 型番のxは、UCC2813 デバイスとUCC3813 デバイスの動作温度範囲の違いを表しています。

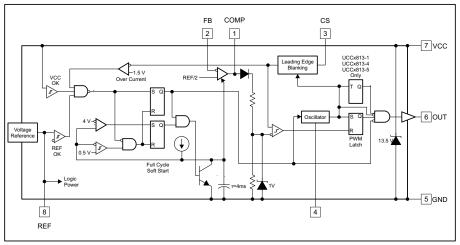

# 5 ピン構成および機能

図 5-1. N および D パッケージ、 8 ピン PDIP および SOIC 上面図

図 5-2. PW パッケージ 8 ピン TSSOP 上面図

表 5-1. ピンの機能

| ۳    | ン  | I/O | <b>米</b> 旧                                                                                |  |

|------|----|-----|-------------------------------------------------------------------------------------------|--|

| 名称   | 番号 | 1/0 | 説明                                                                                        |  |

| СОМР | 1  | 0   | COMP はエラー アンプの出力で、PWM コンパレータの入力です。このピンと FB ピンとの間に帰還ループ補償が適用されます。                          |  |

| CS   | 3  | ı   | S は、電流センスコンパレータ、PWM コンパレータ、および過電流コンパレータへの入力です。                                            |  |

| FB   | 2  | ı   | -B は、エラー アンプの反転入力です。                                                                      |  |

| GND  | 5  | _   | GND は、このデバイスのすべての機能の基準グランドおよび電源グランドです。                                                    |  |

| OUT  | 6  | 0   | OUT は、パワー MOSFET のゲートを駆動できる大電流パワー ドライバの出力です。                                              |  |

| RC   | 4  | I   | RC は、発振器のタイミングを設定するためのプログラミング ピンです。この入力ピンには外付けの抵抗とコンデンサを接続し、スイッチング周波数と最大デューティ サイクルを設定します。 |  |

| REF  | 8  | 0   | REF は、誤差増幅器およびその他多くの機能のための電圧リファレンスであり、またこのデバイスのロジック機能に対するバイアス電源としても使用されます。                |  |

| VCC  | 7  | l   | VCC は、このデバイスのバイアス電源入力です。通常の動作では、VCC は電流制限抵抗を介して電圧源に接続されます。                                |  |

# 6 仕様

# 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)(1)(2)

|                            |               | 最小値  | 最大値                                              | 単位 |

|----------------------------|---------------|------|--------------------------------------------------|----|

| VCC 電圧 <sup>(3)</sup>      |               |      | 12                                               | V  |

| VCC 電流                     |               |      | 30                                               | mA |

| OUT 電流                     |               |      | ±1                                               | Α  |

| OUT エネルギー (容量性負荷)          |               |      | 20                                               | μJ |

| アナログ入力                     | FB、CS、RC、COMP | -0.3 | 6.3 または<br>V <sub>VCC</sub> + 0.3 <sup>(4)</sup> | V  |

| T - 25°C 本の沙弗電力            | N パッケージ       |      | 1                                                | w  |

| T <sub>A</sub> < 25℃での消費電力 | D パッケージ       |      | 0.65                                             | "  |

| リード温度、半田付け、(10 秒)          |               |      | 300                                              | °C |

| 接合部温度                      |               | -55  | 150                                              | °C |

| 保管温度、T <sub>stg</sub>      |               | -65  | 150                                              | °C |

- (1) すべての電圧は GND を基準にしています。指定されたピンに流れ込む電流はすべて正です。

- (2) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これらはストレス評価のみであり、セクション 6.3 で示された条件を超えるこれらの条件またはその他の条件下でのデバイスの機能動作を保証するものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

- (3) 通常の動作時、Vcc は電流制限抵抗を介して電源に接続されます。この抵抗は、すべての動作条件下で VCC 電圧が 12V 未満かつターンオフしきい値を上回るように適切に選定する必要があります。 VCC が低インピーダンスの電源から供給され、ICC が 30mA を超えない場合に限り、最大定格 12V が適用されます。 VCC とICC をこれらの制限値に制限しないと、デバイスに永続的な損傷が生じる可能性があります。これについては、セクション 8.3 でさらに説明します

- (4) どちらか小さい方です。

#### 6.2 ESD 定格

|  |                         |                                                         |       | 値  | 単位 |

|--|-------------------------|---------------------------------------------------------|-------|----|----|

|  | V <sub>(ESD)</sub> 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>    | ±2500 | \/ |    |

|  |                         | デバイス帯電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠 <sup>(2)</sup> | ±1500 | V  |    |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

- (2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

# 6.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                  |                 |                |  | 最小値  | 最大値                                      | 単位  |

|------------------|-----------------|----------------|--|------|------------------------------------------|-----|

| V <sub>VCC</sub> | 低インピーダンスの電源から供給 | される VCC バイアス電圧 |  |      | 11                                       | V   |

| I <sub>VCC</sub> | 電源バイアス電流        |                |  |      | 25                                       | mA  |

| V <sub>OUT</sub> | ゲートドライバの出力電圧    |                |  | -0.1 | V <sub>VCC</sub>                         | V   |

| I <sub>OUT</sub> | OUT ピンの平均電流     | OUT ピンの平均電流    |  |      | 20                                       | mA  |

| I <sub>REF</sub> | REF ピンの出力電流     |                |  |      | 5                                        | mA  |

|                  | アナログ ピンの電圧      | FB、CS、RC、COMP  |  | -0.1 | 6 または<br>V <sub>VCC</sub> <sup>(1)</sup> | V   |

| f <sub>OSC</sub> | オシレータの周波数       |                |  |      | 1                                        | MHz |

| T <sub>A</sub>   | 自由空気での動作温度      |                |  | -40  | 85                                       | °C  |

(1) どちらか小さい方です。

### 6.4 熱に関する情報

|                       |                             | UCCx813-x |          |            |      |  |

|-----------------------|-----------------------------|-----------|----------|------------|------|--|

|                       | <b>熱評価基準</b> <sup>(1)</sup> | P (PDIP)  | D (SOIC) | PW (TSSOP) | 単位   |  |

|                       |                             | 8ピン       | 8ピン      | 8ピン        |      |  |

| $R_{\theta JA}$       | 接合部から周囲への熱抵抗                | 50.9      | 117.9    | 154.4      | °C/W |  |

| R <sub>0JC(top)</sub> | 接合部からケース (上面) への熱抵抗         | 40.3      | 60.8     | 66.7       | °C/W |  |

| $R_{\theta JB}$       | 接合部から基板への熱抵抗                | 28.1      | 62.2     | 94         | °C/W |  |

| $\Psi_{JT}$           | 接合部から上面への特性パラメータ            | 17.6      | 14.4     | 10.4       | °C/W |  |

| ΨЈВ                   | 接合部から基板への特性パラメータ            | 28        | 61.7     | 93.2       | °C/W |  |

<sup>(1)</sup> 従来および最新の熱評価基準の詳細については、『*半導体およびIC パッケージの熱評価基準*』アプリケーション レポートを参照してください。 spra953

## 6.5 電気的特性

特に記述のない限り、これらの仕様は -40°C  $\leq$ T<sub>A</sub> $\leq$  85°C (UCC2813-x デバイス)、0°C  $\leq$  T<sub>A</sub> $\leq$  70°C (T<sub>J</sub> = T<sub>A</sub>) (UCC3813-x デバイス)、 $V_{VCC}$  = 10V<sup>(1)</sup>。 REF から RC への R<sub>T</sub> = 100 k $\Omega$ 、C<sub>T</sub> = 330 pF (RC から GND  $\sim$ )、0.1- $\mu$ F コンデンサを VCC から GND  $\sim$ 、0.1- $\mu$ F キャパシタを VREF から GND  $\sim$ 。

| パラメータ         | テスト条件                                                                 | 最小値   | 標準値  | 最大值   | 単位  |

|---------------|-----------------------------------------------------------------------|-------|------|-------|-----|

| リファレンス        | ·                                                                     |       |      |       |     |

| 山上帝亡          | T <sub>J</sub> = 25°C, I = 0.2mA, UCCx813-[0,1,2,4]                   | 4.925 | 5    | 5.075 | V   |

| 出力電圧          | T <sub>J</sub> = 25°C, I = 0.2mA, UCCx813-[3,5]                       | 3.94  | 4    | 4.06  | V   |

| 負荷レギュレーション    | 0.2mA < I < 5mA                                                       |       | 10   | 30    | mV  |

| 6公本私          | UCCx813-[0、1、2、4] <sup>(5)</sup>                                      | 4.84  | 5    | 5.1   | V   |

| 総変動           | UCCx813-[3、5] <sup>(5)</sup>                                          | 3.84  | 4    | 4.08  | V   |

| 出力ノイズ電圧       | 10 Hz ≤ f ≤ 10 kHz, $T_J = 25^{\circ}C^{(7)}$                         |       | 70   |       | μV  |

| 長期的安定性        | T <sub>A</sub> = 125°C、1000 時間 <sup>(7)</sup>                         |       | 5    |       | mV  |

| 出力短絡          |                                                                       | -5    |      | -35   | mA  |

| 発振器           |                                                                       |       |      | '     |     |

|               | UCCx813-[0、1、2、4] <sup>(2)</sup>                                      | 40    | 46   | 52    | kHz |

| オシレータの周波数     | UCCx813-[3、5] <sup>(2)</sup>                                          | 26    | 31   | 36    | KHZ |

| 温度安定性         | 注を参照(7)                                                               |       | 2.5% |       |     |

| 振幅 (ピークツーピーク) |                                                                       | 2.25  | 2.4  | 2.55  | V   |

| 発振器のピーク電圧     |                                                                       |       | 2.45 |       | V   |

| エラー アンプ       |                                                                       |       |      |       |     |

|               | V <sub>COMP</sub> = 2.5 V, UCCx813-[0, 1, 2, 4]                       | 2.42  | 2.5  | 2.56  | .,, |

| 入力電圧          | V <sub>COMP</sub> = 2 V; UCCx813-[3、5]                                | 1.92  | 2    | 2.05  | V   |

| 入力バイアス電流      |                                                                       | -2    |      | 2     | μA  |

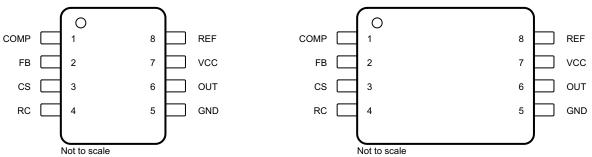

| 開ループ電圧ゲイン     |                                                                       | 60    | 80   |       | dB  |

| COMP シンク電流    | V <sub>FB</sub> = 2.7V <sub>\</sub> V <sub>COMP</sub> = 1.1V          | 0.4   |      | 2.5   | mA  |

| COMP ソース電流    | V <sub>FB</sub> = 1.8 V, V <sub>COMP</sub> = V <sub>REF</sub> – 1.2 V | -0.2  | -0.5 | -0.8  | mA  |

| ゲイン帯域幅積       | 注を参照 <sup>(7)</sup>                                                   |       | 2    |       | MHz |

| PWM           | 1                                                                     | 1     |      |       |     |

|               | UCCx813-[0、2、3]                                                       | 97%   | 99%  | 100%  |     |

| 最大デューティサイクル   | UCCx813-[1、4、5]                                                       | 48%   | 49%  | 50%   |     |

| 最小デューティ サイクル  | V <sub>COMP</sub> = 0V                                                |       |      | 0%    |     |

# 6.5 電気的特性 (続き)

特に記述のない限り、これらの仕様は -40°C  $\leq$ T<sub>A</sub> $\leq$  85°C (UCC2813-x デバイス)、0°C  $\leq$  T<sub>A</sub> $\leq$  70°C (T<sub>J</sub> = T<sub>A</sub>) (UCC3813-x デバイス)、 $V_{VCC}$  =  $10V^{(1)}$ 。 REF から RC  $\sim$ 0 R<sub>T</sub> =  $100~k\Omega$ 、 $C_T$  = 330~pF (RC から GND  $\sim$ )、0.1- $\mu$ F コンデンサを VCC から GND  $\sim$ 0.1- $\mu$ F キャパシタを VREF から GND  $\sim$ 。

|                    | パラメータ                                             | テスト条件                                                               | 最小値  | 標準値  | 最大値  | 単位  |

|--------------------|---------------------------------------------------|---------------------------------------------------------------------|------|------|------|-----|

| 電流検出               |                                                   |                                                                     |      |      |      |     |

|                    | ゲイン                                               | 注を参照(3)                                                             | 1.1  | 1.65 | 1.8  | V/V |

|                    | 最大入力信号                                            | V <sub>COMP</sub> = 5V <sup>(4)</sup>                               | 0.9  | 1    | 1.1  | V   |

|                    | 入力バイアス電流                                          |                                                                     | -200 |      | 200  | nA  |

|                    | CS ブランキング時間                                       |                                                                     | 50   | 100  | 150  | ns  |

|                    | 過電流スレッショルド                                        |                                                                     | 1.32 | 1.55 | 1.7  | V   |

|                    | COMP から CS へのオフセット                                | V <sub>CS</sub> = 0V                                                | 0.45 | 0.9  | 1.35 | V   |

| 出力                 |                                                   |                                                                     | ·    |      | '    |     |

|                    |                                                   | I = 20mA、全パーツ                                                       |      | 0.1  | 0.4  |     |

|                    | OUT 381                                           | I = 200mA、全パーツ                                                      |      | 0.35 | 0.9  | .,  |

|                    | OUT が Low レベル                                     | I = 50mA, V <sub>VCC</sub> = 5V, UCCx813-[3, 5]                     |      | 0.15 | 0.4  | V   |

|                    |                                                   | I = 20 mA、VCC = 0 V、すべての部品                                          |      | 0.7  | 1.2  |     |

|                    |                                                   | I = -20mA、全パーツ                                                      |      | 0.15 | 0.4  |     |

| V <sub>VCC</sub> – | OUT High V <sub>sat</sub>                         | I = -200mA、全パーツ                                                     |      | 1    | 1.9  | V   |

| OUT                | o sut                                             | I = -50mA, V <sub>VCC</sub> = 5V, UCCx813-[3, 5]                    |      | 0.4  | 0.9  |     |

|                    | 立ち上がり時間                                           | C <sub>L</sub> = 1nF                                                |      | 41   | 70   | ns  |

|                    | <br>立ち下がり時間                                       | C <sub>L</sub> = 1nF                                                |      | 44   | 75   | ns  |

| 低電圧誤!              | 動作防止                                              | J -                                                                 |      |      |      |     |

|                    |                                                   | UCCx813-0                                                           | 6.6  | 7.2  | 7.8  | V   |

|                    | HH 1/ (6)                                         | UCCx813-1                                                           | 8.6  | 9.4  | 10.2 |     |

|                    | 開始スレッショルド (6)                                     | UCCx813-[2、4]                                                       | 11.5 | 12.5 | 13.5 |     |

|                    |                                                   | UCCx813-[3、5]                                                       | 3.7  | 4.1  | 4.5  |     |

|                    |                                                   | UCCx813-0                                                           | 6.3  | 6.9  | 7.5  |     |

|                    |                                                   | UCCx813-1                                                           | 6.8  | 7.4  | 8    |     |

|                    | 停止スレッショルド <sup>(6)</sup>                          | UCCx813-[2、4]                                                       | 7.6  | 8.3  | 9    | V   |

|                    |                                                   | UCCx813-[3、5]                                                       | 3.2  | 3.6  | 4    |     |

|                    |                                                   | UCCx813-0                                                           | 0.12 | 0.3  | 0.48 |     |

|                    |                                                   | UCCx813-1                                                           | 1.6  | 2    | 2.4  |     |

|                    | ヒステリシスを停止するために開始                                  | UCCx813-[2、4]                                                       | 3.5  | 4.2  | 5.1  | V   |

|                    |                                                   | UCCx813-[3、5]                                                       | 0.2  | 0.5  | 0.8  |     |

| ソフトスター             |                                                   |                                                                     | 1    |      |      |     |

|                    | COMP の立ち上がり時間                                     | V <sub>FB</sub> = 1.8 V、0.5 V から REF – 1 V に上昇                      |      | 4    |      | ms  |

| 全般的な               |                                                   |                                                                     | 1    |      |      |     |

|                    | スタートアップ電流                                         | V <sub>VCC</sub> < 開始スレッショルド                                        |      | 0.1  | 0.23 | mA  |

|                    | 動作電源電流                                            | V <sub>FB</sub> = 0 V, V <sub>CS</sub> = 0 V, V <sub>RC</sub> = 0 V |      | 0.5  | 1.2  | mA  |

|                    | VCC 内部ツェナー電圧 <sup>(6)</sup>                       | I <sub>CC</sub> = 10mA                                              | 12   | 13.5 | 15   | V   |

|                    | VCC 内部ツェナー電圧から開始ス<br>レッショルド電圧を引いた値 <sup>(6)</sup> | UCCx813-[2、4]                                                       | 0.5  | 1    |      | V   |

- (1) VCC を 10V に設定する前に、開始スレッショルドを超えるように調整します。

- (2) UCCx813-[0、2、3] デバイスの出力周波数は発振器の周波数です。UCCx813-[1、4、5] デバイスの出力周波数は発振器の周波数の半分です。

$$A = \frac{\Delta V_{COMP}}{\Delta V} \quad 0 \le V_{CS} \le 0.8 \text{ V}$$

- (3) ゲインは

- (4) FB を 0V にして、ラッチのトリップ ポイントで測定されたパラメータ。

- (5) 総合的な変動には、温度安定性と負荷レギュレーションも含まれます。

- (6) 開始スレッショルド、停止スレッショルド、およびツェナー シャント スレッショルドは相互に追従します。

- 7) 設計により保証されています。量産時には 100% テストを行っていません。

# 6.6 代表的特性

図 6-1. エラー アンプのゲインと位相との関係

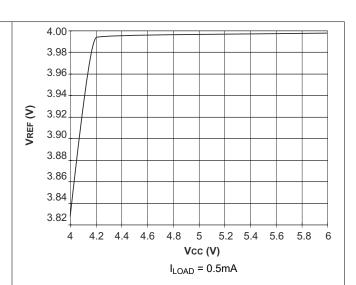

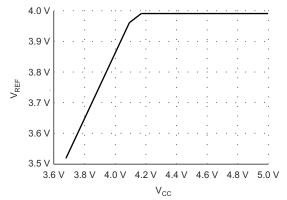

図 6-2. UCC3813-[3、5]: V<sub>REF</sub> と VCC との関係

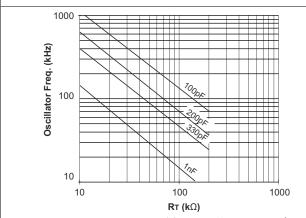

図 6-3. UCC3813-[0、1、2、4]: 発振器周波数と R<sub>T</sub> および C<sub>T</sub> との 関係

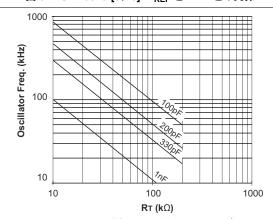

図 6-4. UCC3813-[3、5]: 発振器周波数と R<sub>T</sub> および C<sub>T</sub> との関係

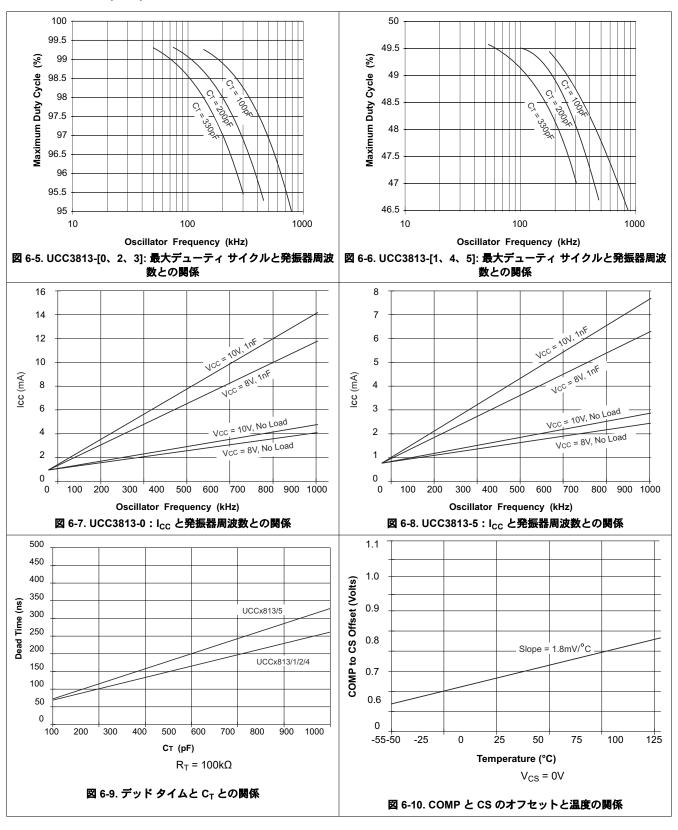

# 6.6 代表的特性 (続き)

# 6.6 代表的特性 (続き)

# 7 詳細説明

# 7.1 概要

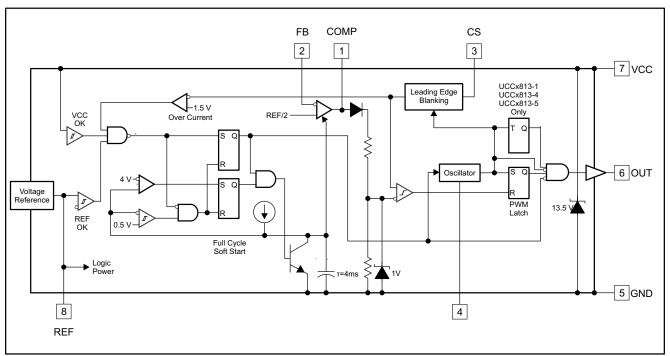

UCCx813-x ファミリは、高速・低消費電力の集積回路で構成されており、外付け部品を最小限に抑えたオフラインおよび DC-DC 固定周波数の電流モード スイッチング電源に必要な、すべての制御および駆動機能を内蔵しています。 UCCx813-x ファミリは、UCCx80x ファミリのコスト削減版であり、いくつかのパラメータ制限が緩和されています。 詳細については、『UCC3813 および UCC3800 PWM ファミリの違い』を参照してください。

これらのデバイスは、UCx84x および UCx84xA ファミリと同じピン構成を持ち、さらに、内部フルサイクル ソフトスタート機能や電流センス入力の内部リーディングエッジ ブランキング機能といった追加機能も備えています。UCCx813-x デバイスは、UCx84x および UCx84xA ファミリとピン配置互換ですが、プラグイン互換ではありません。一般に、UCCx813-x は必要な外付け部品が少なく、動作電流も少なくて済みます。

## 7.2 機能ブロック図

Copyright © 2016, Texas Instruments Incorporated

### 7.3 機能説明

UCCx813-x ファミリは、電源設計エンジニアが厳しい要件を満たすために役立つ多くの利点を提供します。

主な特長は下記の通りです。

- バイ CMOS プロセス

- 開始時電源電流が低い:通常は 100 µA

- 低い動作時消費電流:通常は500 µA

- UC3842 および UC3842A ファミリとピン配置互換

- 5V の動作 (UCCx813-[3、5])

- 電流センス信号のリーディング エッジ ブランキング

- 起動時および故障復帰時のためのオンチップ ソフトスタート機能を搭載

- 内部フルサイクル再起動遅延

- 1.5% の基準電圧

- 最大 1MHz の発振器

- UVLO 中の低い自己バイアス出力

- 電流センスから出力までの応答時間:70ns

- 非常に少ない外部コンポーネントが必要

- 表面実装とPDIP パッケージで提供

### 7.3.1 ピンの詳細説明

#### 7.3.1.1 COMP

COMP はエラー アンプの出力で、PWM コンパレータの入力です。従来世代のデバイスとは異なり、UCCx813-x デバイスファミリの誤差増幅器は、真の低出力インピーダンスを持つ 2MHz のオペアンプです。このような理由で、COMP 端子は電流のソースとシンクの両方を行います。ただし、誤差増幅器には内部的に電流制限がかけられているため、COMPピンを外部から GND に強制的に接続することでゼロ デューティ サイクルを指示することが可能です。

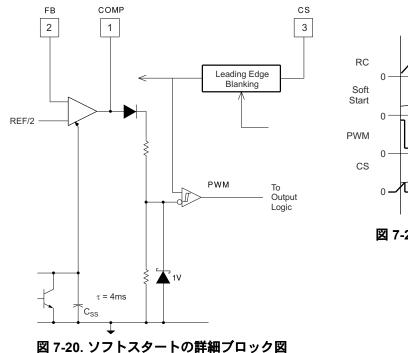

UCCx813-x デバイスファミリは、電源投入時および故障からの復帰後に内蔵のフルサイクル ソフトスタート機能を備えており、外付け部品は不要です。ソフトスタートは、COMP 電圧の立ち上がりクランプとして実装され、4ms で 0V から 5V に上昇します。

#### 7.3.1.2 CS

CS は、電流検出コンパレータへの入力です。UCCx813-x 電流センスは、従来の製品とは大きく異なります。UCCx813-x デバイス ファミリには、PWM コンパレータと過電流コンパレータという、2 種類の電流センスコンパレータが搭載されています。過電流コンパレータは故障検出専用であり、過電流しきい値を超えるとソフトスタート サイクルが開始されます。従来の UC3842 ファミリでは、電流検出入力は PWM コンパレータのみに接続されています。

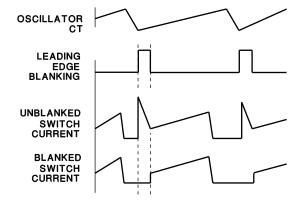

UCCx813-x デバイス ファミリにはデジタル電流検出フィルタが搭載されており、OUT ピンの立ち上がりエッジの直後 100ns の間、CS 端子は電流検出コンパレータから切り離されます。このデジタル フィルタリングは「リーディング エッジ ブランキング」とも呼ばれ、立ち上がり時のノイズによる誤動作を防ぎます。そのため、ほとんどのアプリケーションでは、CS 端子に外付けのアナログ フィルタ (R-C フィルタ) を設ける必要がありません。外部 RC フィルタ方式と比較して、リーディング エッジのブランキングでは CS から OUT への実効遅延が小さくなります。ただし、OUT 信号の最小の非ゼロオン時間は、リーディングエッジ ブランキング時間および CS から OUT への伝搬遅延によって決まります。UCCx813-x ファミリでは、電流検出アンプのゲインは通常 1.65V/V ですが、UC3842 ファミリでは標準 3V/V です。CS を MOSFET のソース電流センス用抵抗に直接接続します。

#### 7.3.1.3 FB

FB は、エラー アンプの反転入力です。最大の安定性を得るため、FB リードの長さはできるだけ短くし、FB の浮遊容量をできるだけ少なくします。2 MHz においては、誤差増幅器のゲイン帯域幅は従来の UC3842 ファミリの 2 倍となっており、フィードバック設計の手法は同一です。

#### 7.3.1.4 GND

GND は、このデバイスにおけるすべての機能の信号基準グランドおよび電源グランドです。 TI は信号がスイッチング電流の影響を受けないように、信号のリターン パスと大電流のゲートドライバ パスは分離することをお勧めします。

#### 7.3.1.5 OUT

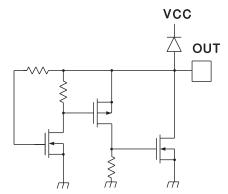

OUT は、大電流のパワードライバの出力であり、±750mA (最大で±1A) を超えるピーク電流でパワー MOSFET のゲートを駆動できる能力を持っています。VCC が UVLO スレッショルドを下回ると、OUT はアクティブに Low に保持されます。この機能により、MOSFET ゲート駆動に関連付けられたゲートソース間ブリーダ抵抗が不要になります。

この大電流パワードライバは、CMOS FET 出力デバイスで構成されており、完全に GND まで、あるいは VCC までスイッチングすることが可能です。この出力は、非常に滑らかな立ち上がりおよび立ち下がり波形を提供し、オーバーシュートやアンダーシュートに対して非常に低いインピーダンスを実現しています。そのため、多くの場合において、出力に外付けのショットキー クランプ ダイオードは不要となる可能性があります。最後に、UCCx813-x ではオンチップのツェナー ダイオードが出力を VCC に自動的にクランプするため、外付けのゲート電圧クランプは不要です。

#### 7.3.1.6 RC

RC は発振器のタイミング ピンです。固定周波数動作の場合、REF から RC に抵抗を接続して、タイミング コンデンサの 充電電流を設定します。タイミング コンデンサを RC から GND に接続して周波数を設定します。最高の性能を得るには、タイミング コンデンサから GND へのリードをできるだけ短く、直線的にします。可能であれば、タイミング コンデンサと 他のすべての機能に別々のグランド配線を使用します。

UCCx813-x の発振回路は、UC3842 ファミリの 500 kHz に対して、最大 1MHz での動作が可能です。両デバイスとも、外付けの抵抗を用いてコンデンサの充電電流を設定し、それによって発振周波数を決定します。UCCx813-[0、1、2、4] の場合は式 1 を使用します。

$$f = \frac{1.5}{\mathsf{R} \times \mathsf{C}} \tag{1}$$

ここで、

- f はスイッチング周波数 (Hz) です。

- R はタイミング抵抗 (Ω) です。

- C はタイミング静電容量 (F) です。

UCCx813-[3、5] には式 2 を使用します。

$$f = \frac{1.0}{\mathsf{R} \times \mathsf{C}} \tag{2}$$

推奨タイミング抵抗は  $10k\Omega$  から  $200k\Omega$  へ、タイミング容量は  $100pF \sim 1000 pF$  です。  $10k\Omega$  より小さいタイミング抵抗を使用してはいけません。

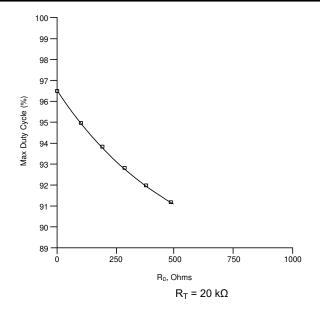

基準電圧が異なるため、2 つの式は異なります。発振波形のピークツーピークの振幅は、UC3842 ファミリの 1.7V に対し、2.45V です。最良の性能を得るために、タイミング用コンデンサのリード線を GND にできるだけ短く接続します。TI は、タイミング コンデンサ用のグラウンド配線と他のすべてのピンのグランド配線を分離することを推奨しています。 UCCx813-[0、2、3] の最大デューティサイクルは約 99% であり、UCCx813-[1、4、5] の最大デューティサイクルは約 49% です。UC3842A ファミリとは異なり、 $R_T$  と  $C_T$  を調整してデューティサイクルを簡単に変更することはできません。最大デューティサイクル制限は、外部発振器充電抵抗  $R_T$  と、内部発振器放電トランジスタ オン抵抗(UC3842 など) の比によって設定されます。ただし、UCCx813-[0、2、3] に対して 90% 未満、UCCx813-[1、4、5] に対して 45% 未満の最大デューティサイクル制限は、この方法では確実に設定することができません。最大デューティサイクルをより的確に制御するには、UCCx807 の使用を検討してください。

#### 7.3.1.7 REF

REF はアンプの電圧リファレンスであると同時に、IC 内の多くの他の機能の基準電圧としても使用されます。REF は、IC 内の高速スイッチング ロジック用のロジック電源としても使用されます。UCCx813-[0、1、2、4] は 5V リファレンスを備え、UCCx813-[3、5] は 4V リファレンスを備えています。 どちらの精度も、25°C で ±1.5% であるのに対して、UC3842 ファミリでは ±2% です。REF 出力短絡電流は、UC3842 ファミリの 30 mA に比べて 5 mA 時に小さくなります。

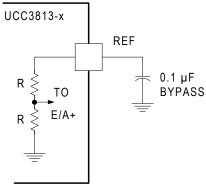

リファレンス電圧の安定性を保ち、高速スイッチングによる過渡ノイズの問題を防ぐために、REF ピンと GND の間にセラミックコンデンサをできるだけ近くに配置してバイパスすることが重要です。0.1μF 以上のセラミックが必要です。リファレンスに対して 2.5mA を超える外部負荷がかかる場合は、追加の REF バイパスが必要です。セラミック コンデンサに加えて電解コンデンサも使用できます。

**VCC** が 1 V を超え、かつ **UVLO** の立ち上がりスレッショルド未満のとき、REF は内部で  $5k\Omega$  の抵抗を介してグランドに引き下げられます。このため、REF は電源システムの状態を示すロジック出力として使用することが可能です。

#### 7.3.1.8 VCC

VCC は、このデバイスの電源入力接続です。通常動作では、VCC は電流制限抵抗を経由して低インピーダンスのソースに電力が供給されます。ノイズの問題を防ぐために、VCC ピンのできるだけ近くに 0.1µF のセラミックコンデンサを並列で接続し、VCC を GND にバイパスしてください。セラミック コンデンサに加えて電解コンデンサも使用できます。

静止時の VCC 電流は非常に小さいものの、OUT 電流に応じて、総電源電流はそれより大きくなります。合計 VCC 電流は、静止 VCC 電流と平均 OUT 電流の合計です。スイッチング周波数と MOSFET ゲート電荷 Qg が判明していれば、平均 OUT 電流は式 3 で計算できます。

$$I_{OUT} = Q_g \times f \tag{3}$$

UCCx813-x は、UC3842 の 30V に対して、VCC (電源電圧) のクランプ値が典型で 13.5V と、より低く設定されています。より高い VCC 電圧を必要とするアプリケーションでは、VCC に直列に抵抗を挿入してソース インピーダンスを高める必要があります。この抵抗の最大値は、式 4 で計算されます。

$$R_{max} = \frac{V_{IN(min)} - V_{VCC(max)}}{I_{VCC} + Q_g \times f}$$

(4)

ここで、

- V<sub>IN(min)</sub>は、VCC の電源供給に使用される最小電圧です

- V<sub>VCC(max)</sub> は、コントローラの 最大 VCC クランプ電圧を指します

- Lycc は、ゲートドライバ電流を考慮していない状態での IC の電源電流です

- Q<sub>a</sub> は外部パワー MOSFET のゲート電荷、f はスイッチング周波数です

さらに、UCCx813-x にはオンチップのツェナー ダイオードが内蔵されており、VCC を 13.5V に制限します。これにより、OUT の最大電圧も制限されます。バイアス電源が常に 12 V より低い場合は、VCC に直接接続できます。UCCx813-3 と UCCx813-5 の UVLO スレッショルドが、それぞれ 4.1V および 3.6V で、5V PWM 動作が可能になりました。

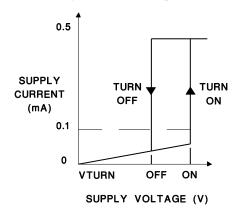

#### 7.3.2 低電圧誤動作防止 (UVLO)

UCCx813-[2、4] デバイスには、電源オンおよび電源オフシーケンス中の動作を制御するため、低電圧誤動作防止保護回路が搭載されています。電源電圧 (V<sub>VCC</sub>) と基準電圧 (V<sub>REF</sub>) の両方が、UVLO 回路によって監視されます。UVLO中に、アクティブ LOW の自己バイアストーテムポール出力構造も組み込まれ、強化されたパワー スイッチ保護のために使用されます。

UCCx813-[2、3、4、5] デバイスの低電圧ロックアウトスレッショルドは、前世代の UCx84[2、3、4、5] PWM コントローラとは異なります。これらのスレッショルドは、オフライン電源と DC/DC コンバータという 2 つのアプリケーション グループ用に最適化されています。各デバイス特有のスレッショルドについては、「表 7-1」を参照してください。

表 7-1. UVLO レベルの比較表

| デバイス          | V <sub>ON</sub> (V) | V <sub>OFF</sub> (V) |

|---------------|---------------------|----------------------|

| UCCx813-0     | 7.2                 | 6.9                  |

| UCCx813-1     | 9.4                 | 7.4                  |

| UCCx813-[2、4] | 12.5                | 8.3                  |

| UCCx813-[3、5] | 4.1                 | 3.6                  |

UCCx813-[2,4] は、立ち上がり時に 12.5V、シャットダウン時に 8.3V の典型的な UVLO (低電圧ロックアウト) しきい値を備えており、4.3V のヒステリシスを提供します。

バッテリや 5V アプリケーションを含む低電圧入力の場合、UCCx813-[3、5] は 4.1V で立ち上がり、3.6V でシャットダウンし、0.5 V のヒステリシスを備えています。

UCCx813-[0、1] は車載用およびバッテリアプリケーション用に最適化された UVLO スレッショルドを備えています。

UVLO 中は、デバイスはおおよそ 100μA の電源電流を消費します。VCC が立ち上がりしきい値を超えると、IC の電源電流は通常約 500μA に増加します。これは、バイポーラ型と比べて 桁違いに低い電流消費です。図 7-1 は、平均的なOUT 電流を含まず、UVLO の立ち上がりおよびシャットダウンしきい値における電源電流の挙動を示しています。

図 7-1. UVLO での IC 消費電流

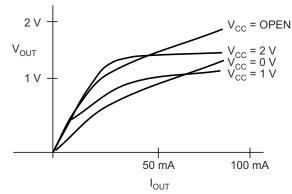

### 7.3.3 自己バイアス、アクティブ LOW 出力

図 7-2 に示されている自己バイアス型のアクティブ Low クランプ回路は、問題となる MOSFET のターンオンを防止します。UVLO 中に PWM 出力電圧が上昇すると、P チャネル デバイスがより大きな N チャネル スイッチをオンに駆動し、出力電圧を低くクランプします。この回路への電力は、外部から上昇してくるゲート電圧によって供給されるため、低電圧ロックアウト中でも、デバイスの電源電圧に関係なく完全な保護が提供されます。

図 7-2. UVLO 中に OUT を Low に保持する内部回路

図 7-3. UVLO 時の OUT 電圧と OUT 電流との関係

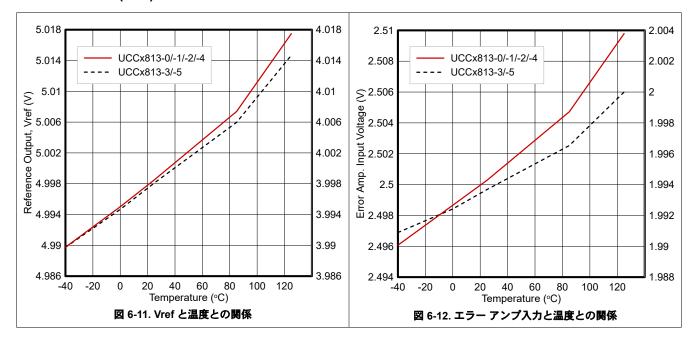

# 7.3.4 基準電圧

UC3842 ファミリの従来の 5V バンドギャップから派生した基準電圧は、UCCx813-[0、1、2、4] デバイスにもあります。ただし、UCCx813-[3、5] デバイスのリファレンス電圧は 4V です。これは、5V 未満の入力電圧でも動作できるようにするために必要な変更でした。リファレンス電圧に関する仕様の多くは UC3842 デバイスと類似していますが、テスト条件は変更されており、これは低電流 PWM アプリケーション向けであることを示しています。バイポーラ品と同様に、BiCMOS デバイスは UVLO 中にリファレンス電圧を内部で LOW にしており、ロジックステータス表示として使用できます。

UCCx813-[3、5] の 4V 基準電圧は電源電圧 ( $V_{VCC}$ ) から得られ、レギュレーションを維持するために約 0.5V のヘッドルームが必要です。 $V_{VCC}$  が約 4.5V を下回ると、通常動作では基準電圧も規定範囲外に低下します。この変動中における  $V_{VCC}$  と  $V_{REF}$  の関係を図 7-4 に示します。

エラー アンプへの非反転入力は、コントローラの基準電圧 (V<sub>REF</sub>) の半分に接続されます。この入力は、UCCx813-[3、5]では 2V、高いリファレンス電圧部品である UCCx813-[0、1、2、4] では 2.5V です。

図 7-4. UCC3813-3 REF 出力と V<sub>VCC</sub> との関係

図 7-5. 必要なリファレンス バイパスの最小容量

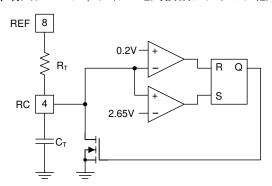

#### 7.3.5 発振器

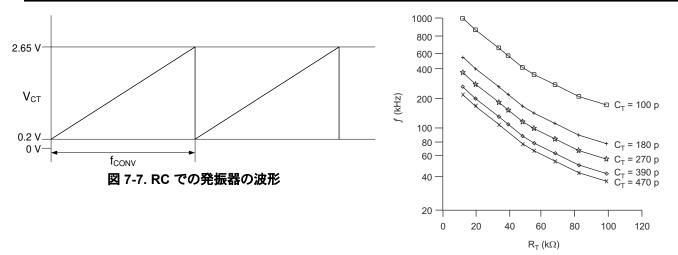

UCCx813-x 発振器は、RC 上にのこぎり波を生成します。立ち上がり時間は、 $R_T$  と  $C_T$  の時定数によって決まります。立ち下がり時間は  $C_T$  と内部トランジスタのオン抵抗によって設定され、約  $130\Omega$  です。立ち下がり時間の間、出力はオフになり、最大デューティサイクルは製品番号に応じて 50% 未満または 100% 未満に低下します。タイミング コンデンサの値を大きくすると、放電時間が長くなり、最大デューティサイクルと周波数がわずかに低下します (図 6-6 と図 6-5 を参照)。

図 7-6. 発振器の等価回路

UCCx813-x BiCMOS ファミリの発振器セクションは、シングル ピン プログラミング以外は UC3842 タイプとほとんど類似していません。依然として、基準電圧と抵抗、およびグランドとの間にコンデンサを使用して、発振器周波数を 1 MHz までプログラムすることができます。低消費電力動作では、充電電流の大幅な低減が求められるため、タイミング部品の値を変更する必要があります。発振器のいくつかの特性は、高速でノイズ耐性の高い動作に最適化されています。発振器のピークツー ピーク振幅は、UC3842 ファミリでは 1.7V に対して標準値 2.45V に増加しました。下側発振器のスレッショルドは約 0.2V まで低下し、上側のスレッショルドは約 2.65V で元の 2.8V にかなり近く維持されています。

タイミング コンデンサの放電電流は、およそ 8 mA ではなくほぼ 20mA ピークまで増加しています。これは、グランドへの 放電スイッチと直列に約 130Ω で表されます。 短いデッド タイムと高いデューティ サイクルを高周波動作で実現するには、より大きい電流が必要です。 実用的なアプリケーションでは、これらのデバイスを 1MHz のスイッチング周波数で使用できます。

図 7-8. いくつか  $C_T$  でのオシレータ周波数と  $R_T$  との 関係

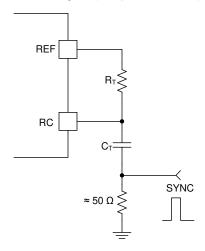

#### 7.3.6 同期

これらの PWM コントローラの同期を行うには、図 7-9 に示すユニバーサル手法を使用して最適な結果が得られます。このデバイスの発振器は、同期周波数より約 20% 低い周波数でフリーラン動作するように設定されています。同期を強制的に行うため、50 Ω の抵抗の両端に短い立ち上がりパルスを印加します。通常、ほとんどのアプリケーションでは、100ns幅の 1V 振幅パルスで十分です。

このコントローラは、発振器の RC ピンに直接印加されたパルストレインに同期させることも可能です。デバイスは、発振器の上限しきい値を超えると、このノードを内部的に Low に引き下げます。RC 端子の電圧が 0.2 V 未満に下がるまで、130Ω の接地インピーダンスは有効な状態を保ちます。外部同期回路はこの条件に対応できる必要があります。

図 7-9. 発振器の同期

## 7.3.7 PWM ジェネレータ

これらのデバイスの最大デューティ サイクルは、従来の UC384[2、3、4、5] よりも高くなります。これは主に、標準的な BiCMOS アプリケーションで 100:1 を超えることができる、タイミング コンデンサの放電/充電電流比率が高いことによるも のです。タイミング成分の  $R_T$  と  $C_T$  を調整して、発振器の最大デューティ サイクルを規定範囲よりも大幅に低く設定する ことを避ける必要があります。この設計慣行を控えるには、2 つの理由があります。まず、このデバイスの放電電流が大き いため、プログラミングに必要な以上の充電電流が求められることになり、低消費電力動作という目的が損なわれてしまい

ます。次に、タイミング抵抗の値が低すぎると、コンデンサが下限しきい値まで放電できず、次のスイッチング サイクルが開始されない可能性があります。

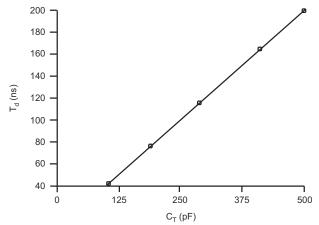

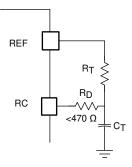

# 7.3.8 最小オフ時間調整 (デッドタイム制御)

デッド タイムは、各発振器サイクル中の PWM 出力の確実なオフ時間を表すために使用される用語です。これにより、最大デューティ サイクルでも磁気回路素子をリセットして飽和を防止するのに十分な時間を確保できます。UCCx813-x PWM ファミリのデッドタイムは、内部の 130 Ω 放電インピーダンスとタイミング・コンデンサの値によって決定されます。容量値を大きくするとデッド タイムが長くなりますが、値が小さいと、同じ動作周波数での最大デューティ サイクルが大きくなります。デッド タイムとタイミング コンデンサの値との関係を示す曲線を 図 7-10 に示します。図 7-11 に示すように、RC ピンとタイミング部品の間に値の小さい抵抗を追加することで、デッド タイムをさらに延ばすことができます。図 7-12 の曲線に示すように、放電抵抗値が大きくなるとデッド タイムは約 470 Ω に増加します。より高い抵抗値を避ける必要があります。これによりデッド タイムが短くなり、発振器のピークツー ピーク振幅が減少する可能性があるためです。R<sub>T</sub>を下げて過度に多くの電流 (1 mA) をシンクすると、0.2V の低い方のコンパレータ スレッショルド電圧への放電を防ぐことで、発振器が停止します。この放電制御抵抗を追加すると、発振器のプログラミングにいくつかの影響があります。まず、この方法では放電期間中にこのコンデンサに DC オフセットを付加します。ただし、タイミング サイクルの充電間隔ではなく、使用可能なピークツー ピーク タイミング コンデンサの振幅が小さくなります。ピーク ツー ピーク振幅が小さいため、正確な発振器周波数を得るには C<sub>T</sub> の正確な値を調整する必要があります。代わりに、より細かい数値的なインクリメントの形で簡単に利用できるため、同じ値のタイミング コンデンサを維持し、タイミング抵抗と放電抵抗の両方の値を調整する方法もあります。

図 7-10. 最小デッドタイムと C⊤ との関係

Copyright © 2016, Texas Instruments Incorporated

図 7-11. 制御された最大デューティ サイクルを生成す る回路

図 7-12. 最大デューティ サイクル対 R<sub>D</sub>

## 7.3.9 リーディング エッジ ブランキング

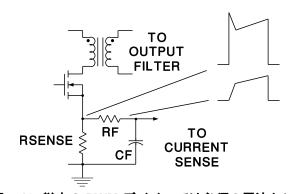

UCCx813-x デバイスの電流検出入力回路には、100ns のリーディング エッジ ブランキング間隔が適用されています。この内部機能により、パワー MOSFET のターンオン時に生じるスイッチングスパイクを抑制するための外部抵抗コンデンサフィルタ回路が不要になります。この 100ns の時間は、ほとんどのスイッチ モード設計で十分ですが、外付け R/C フィルタを追加して、長くすることもできます。サイクル単位の電流制限 PWM 機能に加えて、100ns のリーディング エッジ ブランキングが過電流フォルトコンパレータにも適用されます。

図 7-13. 従来の PWM デバイスでは必須の電流センス フィルタ

図 7-14. リーディング エッジ ブランキングを適用した UCCx813-x の電流検出波形

### 7.3.10 最小パルス幅

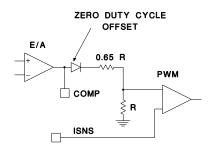

PWM コンパレータには 2 つの入力があります。1 つは電流検出入力からの入力で、もう 1 つの入力は減衰エラー アンプ出力 (COMP)です。この出力にはダイオードとグランドに直列に接続された 2 つの抵抗があります。このネットワークのダイオードは、ゼロ デューティ サイクルに達することを保証するために使用されます。 E/A 出力がダイオードの順方向電圧降下を下回ると、分圧抵抗に電流は流れず、PWM 入力がゼロになり、パルス幅がゼロになります。

特定の条件では、リーディング エッジのブランキング回路によって、ブランキング期間と等しい最小幅の出力パルスが発生することがあります。これは、COMP がダイオードの順方向電圧降下である約 0.5V よりわずかに高い場合に発生し、

PWM コンパレータへの減衰された COMP 入力によって出力パルスが開始されます。減衰された COMP レベルがピーク電流を送り、そのパルス幅がリーディング エッジ ブランキング期間内に収まる場合、ブランキング期間が終了するまで、出力はオンに保持され、ピーク電流は COMP レベルの必要条件を上回るまで保持されます。通常の結果は、コンバータの出力電圧が上昇して誤差が増加し、COMP がダイオード電圧降下よりも低く駆動されて、パルス幅が 0 になります。出力電圧が上昇し、この最小パルス幅条件を中心に低下することで、サイクル スキップが発生する可能性があります。

図 7-15. ゼロ デューティ サイクル オフセット

#### 7.3.11 電流制限

UCCx813-x ファミリには、1V (代表値) サイクル単位の電流制限スレッショルドが組み込まれています。この電流制限回路には、100ns のリーディング エッジ ブランキング間隔が適用されます。ブランキングは電流制限コンパレータ出力よりも優先され、リーディングエッジ スイッチ ノイズが電流制限機能をトリガすることを防止します。電流制限コンパレータから出力までの伝搬遅延は標準 70ns です。この高速パスにより、オン時間を短縮することで、過負荷時の電力半導体の消費電力を最小限に抑えることができます。

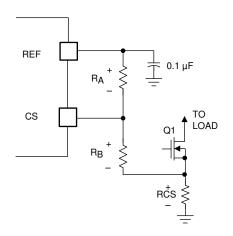

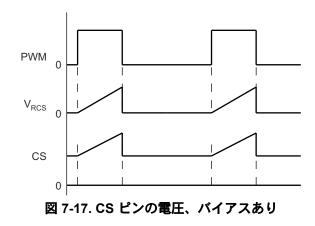

電流センス回路の効率を向上させるため、図 7-16 に示す回路を使用できます。抵抗  $R_A$  および  $R_B$  は、実際の電流検出抵抗電圧を高くバイアスするため、小さな電流検出振幅を使用できます。この回路は、低電力損失電流センシングにより電流制限保護を実現します。

Copyright © 2016, Texas Instruments Incorporated

図 7-16. 電流センス電圧を低減するためのバイアス CS

ここに示す例では、電流センス抵抗で 200mV のフルスケール信号を使用しています。抵抗  $R_B$  は、IC の電流制限コンパレータの 0.9V の最小仕様に合わせて、この電圧を約 700mV バイアスします。抵抗  $R_A$  の値は、基準電圧が異なるため、使用する IC 固有の値も変化します。電力損失が最小限になるよう、この抵抗値を選択する必要があります。たとえば、 $50\mu A$  のバイアス電流を使用する場合、 $R_B$  は  $13k\Omega$  に設定され、 $R_A$  は UCCx813-[0,1,2,4] デバイスでは  $75k\Omega$ 、UCCx813-[3,5] デバイスでは  $R_A$  =  $56k\Omega$  に設定されます。

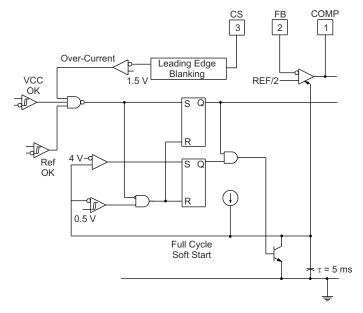

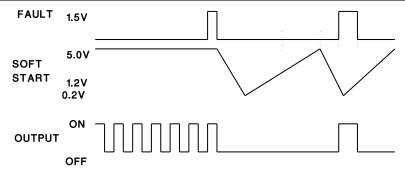

## 7.3.12 過電流保護とフルサイクル再起動

UCCx813-x デバイス内には専用の過電流コンパレータが搭載されており、出力が短絡または深刻な過負荷状態になっ た場合の動作を処理します。この過電流コンパレータには 1.5 V のスレッショルドが設定されており、誤動作を防ぐために リーディング エッジ ブランキング信号によってゲート制御もされています。一度トリガされると、過電流コンパレータは内部 のソフトスタート用コンデンサを使用して、再試行までの遅延時間を生成します。*ヒカップ*とも呼ばれますが、この遅延時間 を使用することで、メイン コンバータとスイッチング部品の入力および消費電力を大幅に低減します。 フルサイクル ソフトス タートにより、異常状態時の動作再試行の間には 3ms を超える予測可能な遅延が確保されます。 図 7-18 に示す回路と 図 7-19 のタイミング図に、飽和インダクタなどの重大な障害に対して IC がどのように応答するかを示します。ピーク電流 異常を最初に検出すると、内部ソフトスタートコンデンサは即座に放電し、障害が解消されるまで放電を続けます。同時 に、PWM 出力はオフに保持されます。障害が解消されると、このコンデンサの充電はゆっくりと行われ、エラー アンプ出 力 (COMP) が上昇します。 COMP 電圧が十分に高くなって出力が有効になると、再び異常が発生し、PWM 出力はラッ チオフされますが、ソフトスタート用コンデンサはそのまま 4V まで上昇を続け、その後に放電されて新しいサイクルの開 始が可能になります。これは、深刻な故障が発生した場合、再試行の間隔はソフトスタート用コンデンサが完全に充電さ れるのに必要な時間によって決まることを意味します。TIは、過電流保護機能を確実に動作させるために、高周波アプリ ケーションではリーケージ インダクタンスの低いトランス設計を推奨しています。 そうしないと、リーディング エッジ ブランキ ング時間内に過電流コンパレータをトリガするのにスイッチ電流が十分に上昇しない可能性があります。この条件により、 サイクル単位の電流制限コンパレータが継続的に周期的にトリガされますが、過電流コンパレータは発生しません。この 場合、スイッチング周波数におけるメイン コンバータの短時間の高い消費電力持続時間が得られます。過電流コンパレ ータの意図は、これらの条件における実効リトライレートを数ミリ秒に下げ、コンバータの短絡消費電力を大幅に低減する ことです。

図 7-18. 過電流保護の詳細なブロック図

図 7-19. CS で繰り返し故障が発生した場合のデバイス動作

#### 7.3.13 ソフトスタート

PWM 出力の内部ソフトスタートは、誤差増幅器 (E/A) の出力電圧 (COMP) を徐々に上昇させることによって行われます。電流モード制御で使用される場合、この実装により各 PWM サイクルごとにスイッチのピーク電流が徐々に上昇し、制御された立ち上がりが実現されます。電圧モード (デューティ サイクル) 制御では、この機能によりパルス幅が徐々に広がっていきます。

E/A アンプ出力 (COMP) を内部のソフトスタート コンデンサ ( $C_{SS}$ ) の電圧にクランプすることで、UCCx813-x デバイス内でソフトスタートを実行します。このコンデンサは電流源によって充電されます。低電圧誤動作防止の遷移後、または通常動作で基準電圧が最小値を下回った場合、 $C_{SS}$  は放電されます。また、故障によって過電流保護コンパレータがトリガされると常に  $C_{SS}$  の放電が発生します。通常の PWM 動作では、エラー アンプにより指示された電圧を上回る値を  $C_{SS}$  が充電されると、ソフトスタート クランプ回路がオーバーライドされます。

RC Soft Start O PWM CS O TO THE TOTAL OR THE

図 7-21. デバイスのソフトスタート動作

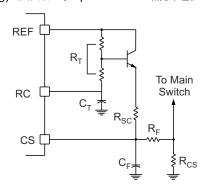

### 7.3.14 スロープ補償

すべての電流モード制御アプリケーションでスロープ補償を追加することで、ピーク間平均電流誤差をキャンセルできます。 デューティ サイクルが 50% を超えるアプリケーションでは、スロープ補償が必要ですが、50% を下回るアプリケーションでは性能も向上します。 1 次側電流は、コンバータ スイッチと直列に接続した抵抗 R<sub>CS</sub> を使用して測定します。 タイミ

ング抵抗は、図 7-22 に示すように、2 つの直列抵抗に分割して、NPN 電圧フォロワをバイアスできます。これは、特に連続電流コンバータでは、スイッチング サイクルの開始時にスロープ補償を十分に準拠させるために必要です。電圧フォロワはスロープ補償プログラミング抵抗 (R<sub>SC</sub>) を駆動し、C<sub>F</sub> にスロープ補償電流を供給します。

図 7-22. 外部スロープ補償の追加

#### 7.4 デバイスの機能モード

UCCx813-x ファミリの高速、低消費電力の電流モード PWM コントローラは、次の機能モードを備えています。

#### 7.4.1 通常動作

この動作モード中、IC は電圧モード制御または電流モード制御で電源コンバータを制御し、コンバータのデューティサイクルを通じて出力電圧または電流を制御・安定化させます。レギュレーションは、内蔵のエラー アンプまたは外部フィードバック回路により実現できます。

# 7.4.2 UVLO モード

システムのスタートアップ時に、 $V_{VCC}$  電圧は 0V から上昇を開始します。VCC 電圧が対応するターンオン スレッショルドに達するまで、IC は UVLO モードで動作します。このモードでは、REF ピンの電圧は生成されません。 $V_{VCC}$  が 1V を超え、ターンオン スレッショルドを下回っているとき、REF ピンは  $5k\Omega$  の抵抗によってアクティブに Low になります。これによって、 $V_{RFF}$  をロジック信号として使い、UVLO モードを示すことができます。

### 7.4.3 ソフトスタート モード

VCC 電圧が UVLO レベルを超えるか、デバイスが故障モードから復帰すると、ソフトスタート モードに移行します。ソフトスタート中は、内部のソフトスタート用コンデンサ C<sub>SS</sub> が誤差増幅器の出力電圧をクランプし、それにより出力電圧がゆっくりと上昇するよう制御されます。これにより、電源コンバータのピーク電流がゆっくりと上昇し、システムへの電圧および電流ストレスが軽減されます。 UCCx813-x ファミリは、4ms の固定ソフトスタート時間を内蔵しています。

#### 7.4.4 フォルト モード

UCCx813-x デバイス内には専用の過電流コンパレータが搭載されており、出力が短絡または深刻な過負荷状態になった場合の動作を処理します。この過電流コンパレータには 1.5 V のスレッショルドが設定されており、誤動作を防ぐためにリーディング エッジ ブランキング信号によってゲート制御もされています。異常を最初に検出すると、内部ソフトスタートコンデンサは即座に放電し、障害が解消されるまで放電を続けます。同時に、PWM 出力はオフに保持されます。これは一般的に「ヒカップ」と呼ばれます。この遅延時間は、メイン コンバータおよびスイッチング部品の入力電力および消費電力を大幅に低減するために使用されます。フルサイクル ソフトスタートにより、故障時に連続して動作を再試行する際には、3 ミリ秒以上の予測可能な遅延が確保されます。障害が解消されると、このコンデンサの充電はゆっくりと行われ、エラーアンプ出力 (COMP) が上昇します。COMP 電圧が十分に高くなって出力が有効になると、再び異常が発生し、PWM 出力はラッチオフされますが、ソフトスタート用コンデンサはそのまま 4V まで上昇を続け、その後に放電されて新しいサイクルの開始が可能になります。これは、深刻な故障が発生した場合、再試行の間隔はソフトスタート用コンデンサが完全に充電されるのに必要な時間によって決まることを意味します。

# 8アプリケーションと実装

注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

# 8.1 アプリケーション情報

UCCx813-x コントローラは、ピーク電流モード (PCM) パルス幅変調器 (PWM) です。これらのコントローラにはオンボード アンプが搭載されており、絶縁型および非絶縁型の電源設計に使用できます。オンボードのトーテムポール ゲートドライバは、最大±1A のピーク電流を供給できます。これらのコントローラは、最大 1MHz のスイッチング周波数で動作可能です。

# 8.2 代表的なアプリケーション

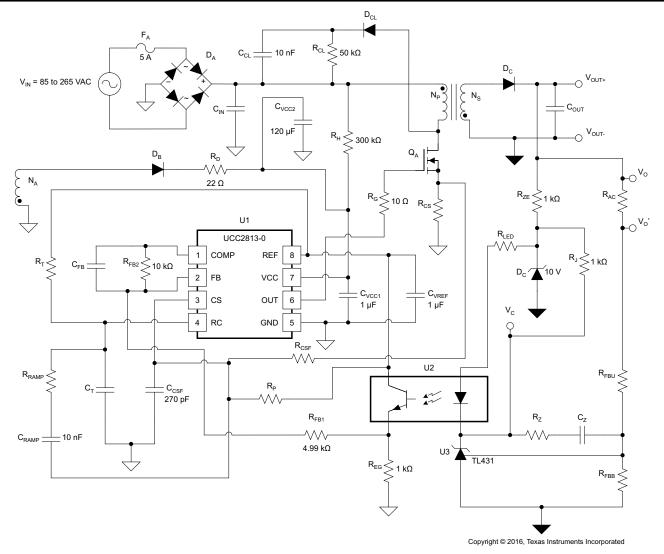

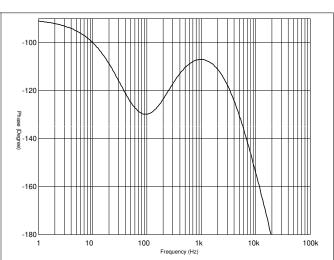

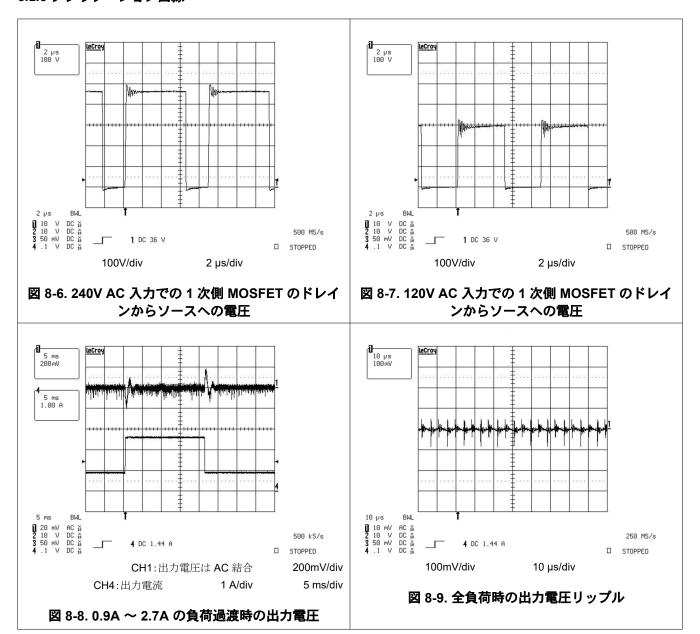

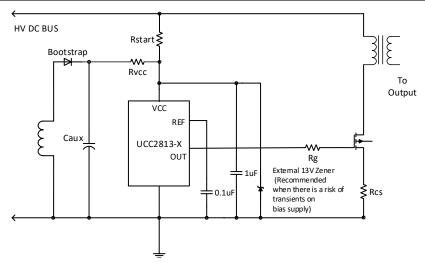

図 8-1 は、ピーク電流モード制御のフライバック方式で UCC2813-0 を使用した AC-DC コンバータの典型的な回路図を示しています。

図 8-1. 代表的なアプリケーション回路図

### 8.2.1 設計要件

表 8-1 のパラメータを使用して、UCC2813-0 PWM コントローラを使用した 12V、48W オフライン フライバック コンバータの設計を確認することができます。

表 8-1. 設計パラメータ

|                     | パラメータ      | テスト条件                     | 最小值   | 公称值 | 最大値   | 単位              |

|---------------------|------------|---------------------------|-------|-----|-------|-----------------|

| 入力特性                |            |                           |       |     |       |                 |

| V <sub>IN</sub>     | 入力電圧 (RMS) |                           | 85    |     | 265   | V               |

| f <sub>LINE</sub>   | ライン周波数     |                           | 47    |     | 63    | Hz              |

| 出力特性                |            |                           |       |     | •     |                 |

| V <sub>OUT</sub>    | 出力電圧       |                           | 11.75 | 12  | 12.25 | V               |

| V <sub>ripple</sub> | 出力リップル電圧   |                           |       |     | 120   | ${\rm mV_{PP}}$ |

| I <sub>OUT</sub>    | 出力電流       |                           |       | 4   | 4.33  | Α               |

| V <sub>tran</sub>   | 出力過渡応答     | 0A から 4A 負荷ステップで測定された出力電圧 | 11.75 |     | 12.25 | V               |

| システム特性              |            |                           |       |     |       |                 |

| η                   | 最大負荷効率     |                           | 85%   |     |       |                 |

#### 8.2.2 詳細な設計手順

#### 8.2.2.1 バルク キャパシタの計算

設計では、適切なバルクキャパシタの選定から始まります。

1 次側バルク キャパシタは、入力電力レベルと求められる最小バルク電圧レベルに基づいて選択します。 バルク キャパシタの値は式 5 で計算できます。

$$C_{BULK} = \frac{2P_{IN} \times \left[ 0.25 + \frac{1}{\pi} \times arcsin\left( \frac{V_{BULK(min)}}{\sqrt{2} \times V_{IN(min)}} \right) \right]}{\left( 2V^2_{IN(min)} - V^2_{BULK(min)} \right) \times f_{LINE}}$$

(5)

ここで、

- P<sub>IN</sub> は、最大負荷時の目標効率で最大出力電力を除算した値です

- V<sub>IN(min)</sub> は、最小 AC 入力電圧 (実効値: RMS) を指します。

- V<sub>BULK(min)</sub> は、目標とする最小バルク電圧を指します。

- f<sub>LINE</sub> はライン周波数です

この式に基づくと、75V の最小バルク電圧を達成するためには、コンバータの効率を 85%、最小ライン周波数を 47Hz と 仮定した場合、バルク キャパシタは 127 μF を超える必要があります。 バルク キャパシタの代表的な許容誤差を考慮し、この設計では 180 μF を選択しています。

#### 8.2.2.2 トランスの設計

トランスの設計は、適切なスイッチング周波数の選定から始まります。一般的に、スイッチング周波数の選定は、シンプルなフライバックトポロジに基づき、コンバータのサイズと効率とのトレードオフに基づいて行われます。通常、スイッチング周波数が高くなるとトランスのサイズが小さくなります。しかし、スイッチング損失が増加すると、効率が低下してしまいます。場合によっては、通信へのノイズ干渉を防ぐために、特定の通信帯域を避けるようスイッチング周波数が選定されることもあります。周波数の選定については、本データシートの範囲外となります。

トランスのサイズを最小化するために、スイッチング周波数は 110kHz を目標としています。 同時に、EMI 規制は 150kHz から伝導ノイズを制限し始めるため、スイッチング周波数を 110kHz に設定することで、EMI フィルタのサイズを小さく抑えるのに役立ちます。

トランスの巻線比は、目的とする MOSFET の耐圧およびダイオードの耐圧に基づいて選定することができます。 最大入力電圧は 265 V AC なので、式 6 に示すようにピーク バルク電圧を計算できます。

$$V_{BULK(max)} = \sqrt{2} \times V_{IN(max)} \approx 375 \text{ V}$$

(6)

システム コストを最小限に抑えるために、一般的な 650V MOSFET が選定されます。MOSFET ドレインの設計マージンと余分な電圧リンギングを考慮すると、反射出力電圧は 120V 未満とする必要があります。トランスの巻線比は、式 7 で選択できます。

$$n_{ps} = \frac{120V}{12V} = 10 \tag{7}$$

トランスのインダクタンスの選択は、連続導通モード (CCM) の条件に基づいて行われます。インダクタンスが大きいと、コンバータは CCM を長く維持できます。ただしトランスのサイズを大きくする傾向があります。通常、トランスの励磁インダクタンスは、最小入力電圧時にコンバータが約 50% の負荷で CCM 動作に入るように選定されます。これは、トランスのサイズと効率の間のトレードオフとなります。この特定の設計では、出力電流が大きいため、コンバータをより深く CCM で動作させ、導通損失と出力リップルを最小限に抑えることが望まれます。このコンバータは、最小バルク電圧において約10% 負荷で CCM 動作に移行します。

インダクタは式8のように計算できます。

$$L_{m} = \frac{1}{2} \frac{V_{BULK(min)}^{2} \times \left(\frac{n_{PS}V_{OUT}}{V_{BULK(min)} + n_{PS}V_{OUT}}\right)^{2}}{10 \% \times P_{IN} \times f_{SW}}$$

(8)

この式では、選択したスイッチング周波数は 110kHz です。したがって、トランスのインダクタンスは約 1.7mH である必要があります。 磁化インダクタンスの値として 1.5mH を選択します。

補助巻線は、UCC2813-0 の通常動作に対してバイアス電力を供給します。補助巻線の電圧は、1 次側に反映された出力電圧です。IC がトランスからエネルギーを迅速に取得し、重負荷の下で簡単に起動できるように、より高い反射電圧を用意することが必要です。ただし、反射電圧が高いほど、IC の消費電力は増加します。したがって、トレードオフが必要になります。

この設計では、補助巻線の電圧を出力電圧と同じに設定することで、UVLOレベルを上回りつつ、ICやドライバの損失を低く抑えるようにしています。したがって、出力巻線の巻線比は式9で選択します。

$$n_{as} = \frac{12 \text{ V}}{12 \text{ V}} = 1$$

(9)

計算された一次側インダクタンス値とスイッチング周波数に基づいて、MOSFET およびダイオードにかかる電流ストレスを算出できます。

### 8.2.2.3 MOSFET と出力ダイオードの選択

MOSFET のピーク電流は式 10 で計算されます。

$$I_{PK_{MOS}} = \frac{P_{IN}}{V_{BULK(min)} \times \frac{n_{PS}V_{OUT}}{V_{BULK(min)} + n_{PS}V_{OUT}}} + \frac{1}{2} \frac{V_{BULK(min)}}{L_{m}} \times \frac{\frac{n_{PS}V_{OUT}}{V_{BULK(min)} + n_{PS}V_{OUT}}}{f_{sw}}$$

$$(10)$$

**MOSFET** のピーク電流は **1.425A** です。

MOSFET の RMS 電流は、式 11 で計算できます。

$$I_{\text{RMS}_{\text{MOS}}} = \sqrt{\frac{1}{3}D^3 \times \left(\frac{V_{\text{BULK(min)}}}{L_{\text{m}} \times f_{\text{sw}}}\right)^2 - \frac{D^2 I_{\text{PK}_{\text{MOS}}} V_{\text{BULK(min)}}}{L_{\text{m}} \times f_{\text{sw}}} + D \times I^2_{\text{PK}_{\text{MOS}}}}$$

(11)

ここで、

D は最小バルク電圧での MOSFET のデューティ サイクルであり、式 12 のように計算できます

$$D = \frac{n_{ps}V_{OUT}}{V_{BULK(min)} + n_{ps}V_{OUT}}$$

(12)

MOSFET の RMS 電流は 0.75A です。オン抵抗は  $0.9\Omega$  未満で、1 次側 MOSFET として IRFB9N65A を選択しています。

ダイオードのピーク電流は、2次側に反映された MOSFET のピーク電流です。

$$I_{PK_{DIODE}} = n_{ps} \times I_{PK_{MOS}} = 14.25 \text{ A}$$

$$(13)$$

ダイオード電圧には、出力電圧に反射入力電圧を加えた値と等しい電圧ストレスが発生します。ダイオードの電圧ストレス は、式 14 で計算できます。

$$V_{DIODE} = \frac{V_{BULK(max)}}{n_{ps}} + V_{OUT} = \frac{375V}{10} + 12V \approx 50V$$

(14)

リンギング電圧スパイクと電圧ディレーティングを考慮して、ダイオードの定格電圧は 50V を超える必要があります ダイオードの平均電流が出力電流 (4A) であるため、60V 定格と 40A の平均電流能力を持つ 48CTQ060-1 を選択します。

## 8.2.2.4 出力コンデンサの計算

出力コンデンサは、出力電圧リップルの要件に基づいて選定されます。この設計では、0.1% の電圧リップルを想定しています。0.1% のリップル要件に基づいて、式 15 に基づいてコンデンサの値を選択できます。

$$C_{OUT} \ge \frac{I_{OUT} \times \frac{n_{ps}V_{OUT}}{V_{BULK(min)} + n_{ps}V_{OUT}}}{0.1\% \times V_{OUT} \times f_{sw}} = 2105\mu F$$

(15)

許容差や温度の影響、さらにコンデンサのリップル電流定格を考慮し、680μF のコンデンサを 3 個並列接続する構成が 出力用として選定されています。

基本的な電力段の設計が完了したら、周辺のコントローラ部品を選定することができます。

### 8.2.2.5 電流検出ネットワーク

電流センス ネットワークは  $R_{CS}$ 、 $R_{CSF}$ 、 $C_{CSF}$ 、オプションの  $R_P$  で構成されます。通常、直流検出信号には、メイン パワー MOSFET のターンオンに関連する大きな振幅のリーディング エッジ スパイク、出力整流器の逆回復、および寄生容量の充電と放電などの他の要因が含まれています。したがって、 $C_{CSF}$  と  $R_{CSF}$  はローパス フィルタを構成し、内部ブランキング時間を超える追加のノイズ耐性を提供することで、立ち上がり時のスパイクを抑制します。このコンバータでは、十分なフィルタリングを行うために  $C_{CSF}$  は 270 pF に設定されています。

$R_P$  を使用しない場合、 $R_{CS}$  は、1V に規定されている CS ピンの最大振幅に基づいて、トランスの 1 次側の最大ピーク電流を設定します。 1 次側のピーク電流を 1.425A にするには、 $R_{CS}$  に  $0.75\Omega$  の抵抗を選択します。

高い電流検出スレッショルドによりノイズ耐性が向上しますが、電流センス損失は増大します。これらの電流センス損失は、オフセット電圧を電流センス信号に注入することで最小化できます。Rp および R<sub>CSF</sub> は、電流センス電圧をオフセットするために、電流センス信号からデバイスのリファレンス電圧への抵抗分圧回路を構成します。この技法でも、サイクル単位の過電流保護を含めた電流モード制御を実現できます。必要なオフセット値 (Voffset) を計算するには、式 16 を使用します。

$$V_{\text{offset}} = \frac{R\text{CSF}}{R\text{CSF} + RP} V_{\text{REF}}$$

(16)

#### 8.2.2.6 ゲート ドライブ抵抗

$R_G$  は、パワー スイッチ  $Q_A$  のゲートドライバ抵抗です。この抵抗の値は、EMI 準拠テストや効率テストと合わせて選択する必要があります。大きい  $R_G$  と、MOSFET のターンオンとターンオフが低速になります。スイッチング速度が遅いと、EMI は減少しますが、スイッチング損失が増加します。スイッチング損失と EMI 性能との間のトレードオフは、慎重に検討する必要があります。この設計では、ゲートドライバ抵抗として  $10\Omega$  の抵抗が選択されています。

#### 8.2.2.7 REF バイパス コンデンサ

REF における高精度な 5V リファレンス電圧は、いくつかの重要な機能を果たすように設計されています。リファレンス電圧は内部で 2.5V に分圧され、エラー アンプの非反転入力に接続されることで、出力電圧を正確にレギュレートします。リファレンス電圧の他の役割には、内部バイアス電流の設定や、発振器の上限および下限しきい値、過電流制限しきい値などの機能のためのしきい値の設定が含まれます。このため、リファレンス電圧はセラミック コンデンサ (C<sub>VREF</sub>) を使用してバイパスする必要があります。このコンバータでは、1μF、16V のセラミック コンデンサが選択されています。このコンデンサをプリント基板の物理的なレイアウトに配置するときは、対応する REF ピンと GND ピンにできるだけ近づける必要があります。

#### 8.2.2.8 R<sub>T</sub> および C<sub>T</sub>

内部発振器は、タイミング コンデンサ ( $C_T$ ) とタイミング抵抗 ( $R_T$ ) を使用して、発振器の周波数と最大デューティ サイクル をプログラムします。動作周波数は、図 6-3 の曲線に基づいてプログラムできます。これらのグラフでは、タイミング コンデンサを選択すると、タイミング抵抗を見つけることができます。タイミング コンデンサの選択は、図 6-5 に示す最大デューティ サイクルにも影響します。タイミング コンデンサには温度係数がフラットなものを選択してください。ほとんどの COG や NPO タイプのコンデンサは、この条件を満たします。このコンバータでは、110kHz のスイッチング周波数で動作させるために、 $C_T$  に 1000 pF、 $R_T$  に 13.6 k $\Omega$  が選択されました。

### 8.2.2.9 スタートアップ回路

スタートアップ時に、IC は高電圧バルクから高電圧抵抗  $R_H$  を介して直接電力を受け取ります。スタートアップ抵抗の選択は、電力損失とスタートアップ時間との間のトレードオフです。最小入力電圧で  $R_H$  を流れる電流は、UVLO 条件での VCC 電流 (最大値で 0.2mA) を上回る必要があります。トレードオフの結果として、 $300k\Omega$  抵抗を選択します。

VCC が UVLO の立ち上がりしきい値を超えて充電されると、UCC2813-0 は動作を開始し、通常の動作電流を消費します。初期段階では、出力電圧が低いため、VCC は補助巻線からエネルギーを得ることができません。VCC コンデンサには、出力電圧が十分に高くなるまでの起動時間中に、UVLO を下回らないようにするための十分なエネルギーを保持しておく必要があります。大きなコンデンサはより多くのエネルギーを保持できますが、起動時間が長くなるというデメリットがあります。この設計では、起動時に十分なエネルギーを供給するために、120µF のコンデンサが選定されています。

#### 8.2.2.10 電圧帰還補償手順

帰還補償は閉ループ制御とも呼ばれ、定常状態の出力電圧誤差を低減して、排除し、パラメータ変動への感度を下げ、特定の周波数範囲でゲインや位相を調整し、小信号による負荷変動やノイズの影響を抑え、システムの安定性を確保します。このセクションでは、ピーク電流モード制御を用いた絶縁型フライバックコンバータの補償方法について説明します。

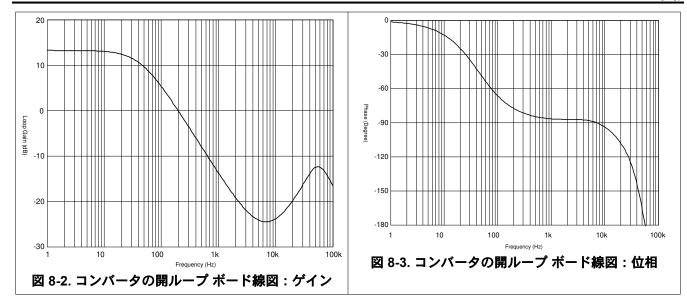

### 8.2.2.10.1 電力段のゲイン、ゼロ、極

固定周波数フライバックを保証するための最初のステップは、コンバータが連続導通モード (CCM) と不連続導通モード (DCM) のどちらで動作しているかを確認することです。1 次側インダクタンス (L<sub>P</sub>) が、DCM モード動作と CCM モード動作の境界のインダクタンスであるクリティカル インダクタンス (L<sub>Pcrit</sub>) より大きい場合、コンバータは CCM で動作します。 L<sub>Pcrit</sub> は式 17 で計算されます。

$$L_{Pcrit} = \frac{R_{OUT} \times N_{PS}^2}{2 \times f_{SW}} \times \left(\frac{V_{IN}}{V_{IN} + V_{OUT} \times N_{PS}}\right)^2$$

(17)

入力電圧範囲全体で P<sub>MAX</sub> の 10% を超える負荷の場合、選択する 1 次インダクタンスの値はクリティカル インダクタンスよりも大きくなります。したがって、コンバータは CCM で動作し、補償ループは CCM フライバックの式に基づいて設計する必要があります。

電流から電圧への変換は、グランド基準の電流検出抵抗 R<sub>CS</sub> と内部分圧抵抗を使用して外部で行われ、内部の電流検出ゲイン A<sub>CS</sub> = 1.65 が設定されます。IC テクノロジーを使用すると、実際の抵抗値の変動にかかわらず、抵抗分圧比を厳密に制御できます。

図 8-1 に示すピーク電流モード制御 CCM フライバック コンバータの固定周波数電圧制御ループの DC 開ループ ゲイン ( $G_O$ ) は、式 18 で示されているように出力負荷 ( $R_{OUT}$ )、1 次側と 2 次側の巻線比 ( $N_{PS}$ )、最大デューティ サイクル (D) を最初に使うことで概算されます。

$$G_{O} = \frac{R_{OUT} \times N_{PS}}{R_{CS} \times A_{CS}} \times \frac{1}{\frac{(1-D)^{2}}{\tau_{L}} + (2 \times M) + 1}$$

(18)

ここで、

- R<sub>OUT</sub> = V<sub>OUT</sub> / I<sub>OUT</sub>

- Dは式19で計算されます

- T<sub>1</sub> は、式 20 で計算されます

- M は式 21 で計算されます

$$D = \frac{N_{PS} \times V_{OUT}}{V_{IN} + (N_{PS} \times V_{OUT})}$$

(19)

$$\tau_{L} = \frac{2 \times L_{P} \times f_{SW}}{R_{OUT} \times N_{PS}^{2}}$$

(20)

$$M = \frac{V_{OUT} \times N_{PS}}{V_{IN}}$$

(21)

この設計では、出力電圧 ( $V_{OUT}$ ) が 12V で 48W のコンバータは、出力負荷 ( $R_{OUT}$ ) に対応し、全負荷時に 3 $\Omega$  と等しくなります。

最小入力バルク電圧 75V DC では、デューティサイクルは最大値 0.615 に達します。電流検出抵抗 ( $R_{CS}$ ) は 0.75  $\Omega$  で、1 次側と2 次側の巻線比 ( $N_{PS}$ ) は 10 です。 開ループ ゲインは 14.95dB です。

**CCM** フライバック伝達関数には注目対象として 2 つのゼロがあります。**ESR** と出力容量は、電力段に左半平面ゼロを生じさせ、ゼロの周波数  $f_{\mathsf{ESRz}}$  は式 22 で計算されます。

$$\omega_{\mathsf{ESRz}} = \frac{1}{\mathsf{R}_{\mathsf{ESR}} \times \mathsf{C}_{\mathsf{OUT}}} \tag{22}$$

3 つの 680- $\mu$ F コンデンサの容量バンク (合計出力容量 2040  $\mu$ F の場合) で、合計 ESR の 13  $m\Omega$  について、 $f_{ESRz}$  の ゼロは 6 kHz に配置されます。

CCM フライバック コンバータは、伝達関数の右半面 (RHP) にゼロが存在します。RHP のゼロは、周波数の増加による立ち上がりゲイン振幅が左半面のゼロと同じ 20dB/decade ですが、リードの代わりに位相ラグが追加されます。この位相ラグは、ループ全体の帯域幅を制限する傾向があります。式 23 の周波数位置 ( $f_{RHPz}$ ) は、出力負荷、デューティサイクル、1 次側インダクタンス ( $L_P$ )、1 次側の巻線比 ( $N_{PS}$ ) の関数です。

$$f_{RHPz} = \frac{R_{OUT} \times (1-D)^2 \times N_{PS}^2}{2 \times \pi \times L_P \times D}$$

(23)

RHP ゼロの周波数は、入力電圧が高くなり、負荷が軽くなるほど上昇します。設計では一般に、RHP のゼロ周波数が最も小さくなるワーストケースを考慮し、入力が最小で負荷が最大の状況でも、コンバータが補償を行える必要があります。 75V DC 入力で 1 次インダクタンスが 1.5 mH の場合、RHP のゼロ周波数 f<sub>RHPz</sub> は最大デューティサイクル、全負荷時で 7.65 kHz になります。

電力段には、1 つの支配的な極である  $\omega_{P1}$  が、低い周波数  $f_{P1}$  の対象領域に存在します。この周波数は、デューティサイクル (D)、出力負荷、出力容量に関係しています。また、コンバータのスイッチング周波数の半分に 2 極 ( $f_{P2}$ ) が存在します。これらの極は式 24 と式 25 で計算される周波数です。

$$f_{P1} = \frac{\frac{(1-D)^3}{\tau_L} + 1 + D}{2 \times \pi \times R_{OUT} \times C_{OUT}}$$

(24)

$$f_{P2} = \frac{f_{SW}}{2} \tag{25}$$

分数調波発振は、デューティサイクルが 50% を超えると CCM フライバック コンバータで発生する可能性がある大信号の不安定性です。サブハーモニック振動は出力電圧のリップルを増加させ、場合によってはコンバータの電力処理能力を制限してしまうこともあります。 CS 信号に対するスロープ補償は、不安定性を排除するために使用される手法です。

理想的には、勾配補償の目標は、品質係数 ( $Q_P$ ) を、スイッチング周波数の半分において 1 に等しくすることです。  $Q_P$  は式 26 で計算されます。

$$Q_{P} = \frac{1}{\pi \times \left[M_{C} \times (1-D) - 0.5\right]}$$

(26)

ここで、

- **D**は **1**次側スイッチのデューティサイクルです。

- M<sub>C</sub> は勾配補償係数であり、式 27 で定義されます

$$M_{C} = 1 + \frac{S_{e}}{S_{n}} \tag{27}$$

ここで、

- S<sub>e</sub> は補償ランプ勾配です。

- S<sub>n</sub>は、トランスの 1 次側インダクタンスの立ち上がり電流スロープを表します

勾配補償の最適な目標は、 $Q_P$  を 1 にすることです。これは、D が最大値の 0.615 に達したとき、 $M_C$  を 2.128 にする必要があることを意味します。

CS ピンでのインダクタンス電流スロープは、式 28 で計算されます。

$$S_{n} = \frac{V_{BULK(min)} \times R_{CS}}{L_{P}} = \frac{75V \times 0.75\Omega}{1.5mH} = 38mV/\mu s$$

(28)

補償スロープは、式29で計算されます。

$$S_{e} = (M_{C} - 1) \times S_{n} = (2.128 - 1) \times 38 \text{ mV} / \mu s = 46.3 \text{ mV} / \mu s$$

(29)

補償スロープは、 $R_{RAMP}$  と  $R_{CSF}$  によってシステムに追加されます。高周波短絡を近似するため、直列コンデンサ ( $C_{RAMP}$ ) を選択します。 $C_{RAMP}$  を開始点として 10 nF として選択し、必要に応じて調整を行います。 $R_{RAMP}$  と  $R_{CSF}$  は、分割電圧を形成して RC ピンのランプ電圧をスケーリングし、勾配補償を CS ピンに注入します。周波数の設定にあまり影響しないように、 $R_{T}$  抵抗よりもずっと大きく  $R_{RAMP}$  を選択します。デザインでは、 $R_{RAMP}$  には 24.9 k $\Omega$  を選択します。 RC ピンのランプの勾配は式 30 で計算されます。

$$S_{RC} = 2.4 \text{ V} \times 100 \text{ kHz} = 240 \text{ mV} / \mu \text{s}$$

(30)

46.3 mV/µs の補償勾配を実現するため、式 31 で抵抗 R<sub>CSF</sub> を計算します。

$$R_{CSF} = \frac{R_{RAMP}}{\frac{S_{RC}}{S_e} - 1} = \frac{\frac{24.9 \text{ k}\Omega}{\frac{240 \text{ mV/\mu s}}{46.3 \text{ mV/\mu s}} - 1}}{\frac{240 \text{ mV/\mu s}}{46.3 \text{ mV/\mu s}} - 1} = 5.95 \text{ k}\Omega$$

(31)

電力段の開ループ ゲインおよび位相は、周波数の関数としてプロットできます。合計開ループ伝達関数は、周波数の関数として、式 32 で特性化できます。

$$H_{0}(S) = G_{0} \times \frac{\left(1 + \frac{S}{\omega_{ESRz}}\right) \times \left(1 - \frac{S}{\omega_{RHPz}}\right)}{1 + \frac{S}{\omega_{P1}}} \times \frac{1}{1 + \frac{S}{\omega_{P2} \times Q_{P}} + \frac{S^{2}}{\omega_{P2}^{2}}}$$

(32)

ここで、

•  $\omega_{P1}$  および  $\omega_{P2}$  は、式 24 および式 25 で計算される周波数に基づきます

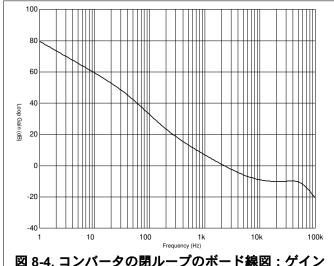

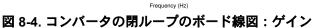

開ループ ゲインと位相ボード線図はそれに応じてグラフ化されています(図 8-3 と図 8-2 を参照)。

# 8.2.2.10.2 ループの補償

良好な過渡応答を得るためには、最終的な設計の帯域幅を可能な限り広く取る必要があります。 CCM フライバックの帯域幅 f<sub>BW</sub> は、RHP ゼロ周波数の 1/4 に制限されるか、式 33 を使用して約 1.9kHz と計算されます。

$$f_{BW} = \frac{f_{RHPz}}{4} \tag{33}$$

$f_{BW}$  における開ループ電力段のゲインは -22.4dB で、 $f_{BW}$  での位相は -87° です。最初の手順は、出力電圧検出抵抗の値を選択することです。出力検出抵抗は、許容される消費電力に基づいて選択し、この場合はセンシング電流の 1 mA を想定しています。

TL431 を帰還アンプとして使用します。2.5V 基準電圧により、電圧検出分圧器 R<sub>FBU</sub> および R<sub>FBB</sub> は式 34 および式 35 で選択できます。

$$R_{FBU} = \frac{V_{OUT} - 2.5 \text{ V}}{1 \text{ mA}} = 9.5 \text{ k}\Omega \tag{34}$$

$$R_{\text{FBB}} = \frac{2.5 \text{ V}}{1 \text{ mA}} = 2.5 \text{ k}\Omega \tag{35}$$

次に、補償回路のゼロ  $f_{CZ}$  を 190Hz に配置します。これは、目標のクロスオーバー周波数の 1/10 です。10 nF の固定値として  $C_Z$  を選択し、式 36 に従ってゼロ抵抗値を選択します。

$$R_{Z} = \frac{1}{2\pi \times f_{CZ} \times C_{Z}} = \frac{1}{2\pi \times 190 \text{ Hz} \times 10 \text{ nF}} = 83.77 \text{ k}\Omega$$

(36)

次に、RHP ゼロ周波数または ESR ゼロ周波数の低い方に極を配置します。前回の分析によれば、RHP ゼロは 7.65kHz、ESR ゼロは 6kHz であるため、補償ループの極は 6kHz に設定する必要があります。この極は、1 次側エラーアンプを介して追加できます。 $R_{FB}$  と  $C_{FB}$  は、必要な極を供給します。 $R_{FB}$  を 10 k $\Omega$  として選択すると、 $R_{FB}$  は式 37 で計算されます。

$$C_{FB} = \frac{1}{2\pi \times 10 \text{ k}\Omega \times 6 \text{ kHz}} = 2.65 \text{ nF}$$

(37)

補償ループの構造に基づいて、補償ループ全体の伝達関数は式38に示すように記述されます。

$$G(S) = \frac{1}{R_{FBU} \cdot R_{LED}} \cdot \frac{1 + S \cdot C_Z \cdot R_Z}{S \cdot C_Z} \cdot \frac{R_{FB2}}{R_{FB1}} \cdot \frac{1}{S \cdot C_{FB} \cdot R_{FB2} + 1} \cdot CTR \cdot R_{EG}$$

(38)

ここで、

- CTR は、フォトカプラの電流伝送比です。 CTR の公称値として 1 を選択します。

- $R_{EG}$  は光エミッタのプルダウン抵抗で、デフォルト値として  $1 k\Omega$  を選択します

この式で必要とされる残りの未知の値は RLED だけです。クロスオーバー周波数では、ループ ゲイン全体が 1 に等しい 必要があります。 $R_{LED}$  には 1.62 k $\Omega$  を選択します。

最終的な閉ループ ボード線図を、図 8-4 と図 8-5 に示します。このコンバータは、約 2kHz のクロスオーバー周波数と約 70°の位相マージンを実現しています。

TI はシステムの安定性を保証するため、部品の公差を含め、すべてのコーナー ケースにわたってループの安定性をチェ ックすることをお勧めします。

図 8-5. コンバータの閉ループのボード線図:位相

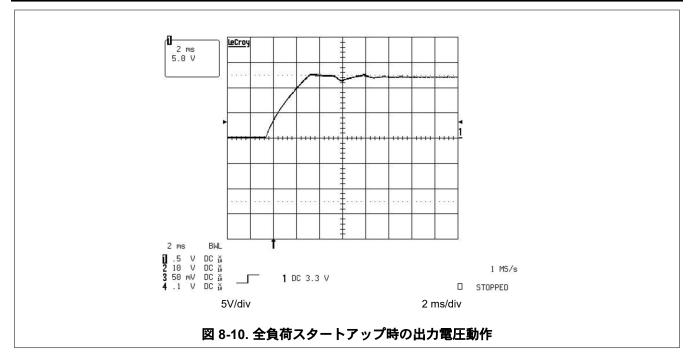

# 8.2.3 アプリケーション曲線

# 8.3 電源に関する推奨事項

UCCx813-x ファミリの各製品には内部 VCC シャント レギュレータが組み込まれており、電源電圧を約 13.5V に制限します。入力電圧が 12V を超える場合には、VCC と入力電源との間に直列抵抗を挿入して、シャント レギュレータに流れる電流を制限する必要があります。最大 10mA は、内部レギュレータを使用してグランドに接続できます。内部レギュレータは、デバイスの低い起動電流および動作電流と組み合わせることで、電源設計を大幅に簡素化でき、多くのアプリケーションにおいては、安定化されたブート ストラップ用の補助電源や巻線を不要にすることも可能です。この電源電圧はMOSFET のゲートレベルと互換性があり、入力電源が電流制限されている場合には、外付けのツェナーダイオードやレギュレータによる保護は不要です。UCCx813-[2,4] デバイスでは、確実な起動を確保するために、UVLO の起動しきい値がシャントレギュレータの電圧レベルよりも 1V 低く設定されています。デバイスの電源 (VCC) ピンとリファレンス電圧(REF) ピンを、0.1μF~1μF のセラミックコンデンサでグランドにバイパスすることが重要です。最適なノイズ フィルタリングを実現するには、コンデンサを実際のピン接続のできるだけ近くに配置する必要があります。また、オフライン アプリケーションでは、スタートアップ時に電源電圧 (Vvcc) を UVLO ターンオフ スレッショルドよりも高く保持するために、より大きなフィルタ コンデンサが必要な場合があります。

UCC2813-[2,4] デバイスの UVLO 起動しきい値は 11.5V ~ 13.5V の範囲にあり、保護用ツェナーダイオードの電圧は 12V ~ 15V の範囲で変動する可能性があります。ただし、この IC の絶対最大電源電圧は 12V に規定されています。この絶対最大値は、低インピーダンス (電圧) ソースから駆動された場合の最も低いツェナー電圧として定義されています。ツェナー電圧は常に UVLO 開始電圧より高くなっています。これら 2 つのパラメータは互いを追跡し、ツェナー電圧が開始電圧を下回ることがないことを保証するためにチップのテストが実施されます。内部クランプ ツェナーを流れる電流を制限するには、直列抵抗を追加する必要があります。補助電圧源とコントローラの Vcc ピンとの間に直列抵抗を接続しないと、Vcc ピンの定格レベル内に電流および電圧ストレスが制限され、コントローラに永続的な損傷を与える可能性があります。PWM コントローラに電力を供給する Vcc レールで過渡または電圧変動を引き起こす可能性がある、高電力負荷過渡が発生するリスクがある車載用または産業用アプリケーションでは、Vcc ピンの両端に外付けツェナー ダイオードを追加することを推奨します。外部ツェナーは、Vcc ソースと Vcc ピンとの間に直列抵抗によって生じるインピーダンスを保護するための追加の機能を果たします。

図 8-11. さまざまなデバイスの電源投入方法

MOSFET のゲートに直列に抵抗 Rg を配置することで、MOSFET のスイッチング速度を調整できるほか、ピーク ゲート 駆動電流をコントローラの規定範囲内に抑えることも可能になります。

### 8.4 レイアウト

### 8.4.1 レイアウトのガイドライン

一般的な電源管理 IC のレイアウト ガイドライン (スター グランディング、電流ループの最小化、適切なインピーダンス レベルなど) に従うことに加えて、UCCx813-x ファミリのレイアウトでは以下の点も考慮する必要があります。

- 可能であれば、グランドプレーンを使用することで、グランド回路の電圧降下や、個々の配線における寄生インダクタンスによるノイズの影響を最小限に抑えるべきです。

- VCC ピンおよび REF ピンにはそれぞれにデカップリング コンデンサが必要であり、どちらも IC の近くで GND に接続する必要があります。

- 最高の性能を得るには、タイミング コンデンサから GND へのリードをできるだけ短く、直線的にします。 可能であれば、タイミング コンデンサと他のすべての機能に別々のグランド配線を使用します。

- CS ピンのフィルタ用コンデンサは、IC のできるだけ近くに配置し、IC のグランド ピンに直接接続して接地する必要があります。これにより、最大限のフィルタ処理効果が保証され、電流センス ピンの誤動作の可能性を最小限に抑えることができます。

- ゲートドライブ ループの面積は、ループ内の電流の高い di/dt によって発生する EMI ノイズを低減するために、できる だけ小さくする必要があります。

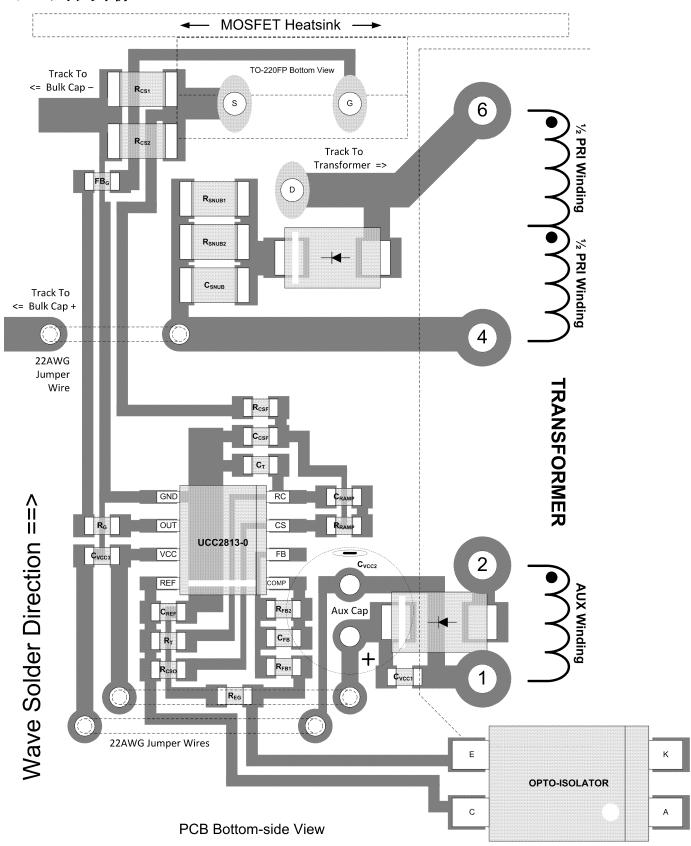

# 8.4.2 レイアウト例

# 9 デバイスおよびドキュメントのサポート 9.1 ドキュメントのサポート

#### 9.1.1 関連資料

関連資料については、以下を参照してください。

『UCC3813 および UCC3800 PWM ファミリの相違点』(SLUA247)

## 9.2 関連リンク

次の表に、クイック アクセス リンクを示します。カテゴリには、技術資料、サポートおよびコミュニティ リソース、ツールとソフトウェア、およびサンプル注文またはご購入へのクイック アクセスが含まれます。

製品 プロダクトフォルダ サンプルとご購入 技術資料 ツールとソフトウェア サポートとコミュニティ UCC2813-0 こちらをクリック こちらをクリック こちらをクリック こちらをクリック こちらをクリック UCC2813-1 こちらをクリック こちらをクリック こちらをクリック こちらをクリック こちらをクリック UCC2813-2 こちらをクリック こちらをクリック こちらをクリック こちらをクリック こちらをクリック UCC2813-3 こちらをクリック こちらをクリック こちらをクリック こちらをクリック こちらをクリック UCC2813-4 こちらをクリック こちらをクリック こちらをクリック こちらをクリック こちらをクリック UCC2813-5 こちらをクリック こちらをクリック こちらをクリック こちらをクリック こちらをクリック UCC3813-0 こちらをクリック こちらをクリック こちらをクリック こちらをクリック こちらをクリック UCC3813-1 こちらをクリック こちらをクリック こちらをクリック こちらをクリック こちらをクリック UCC3813-2 こちらをクリック こちらをクリック こちらをクリック こちらをクリック こちらをクリック UCC3813-3 こちらをクリック こちらをクリック こちらをクリック こちらをクリック こちらをクリック UCC3813-4 こちらをクリック こちらをクリック こちらをクリック こちらをクリック こちらをクリック UCC3813-5 こちらをクリック こちらをクリック こちらをクリック こちらをクリック こちらをクリック

表 9-1. 関連リンク

## 9.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、www.tij.co.jp のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。 変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

#### 9.4 サポート・リソース

テキサス・インスツルメンツ E2E<sup>™</sup> サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

#### 9.5 商標

テキサス・インスツルメンツ E2E<sup>™</sup> is a trademark of Texas Instruments. すべての商標は、それぞれの所有者に帰属します。

### 9.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 9.7 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

# 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision F (May 2020) to Revision G (April 2025)   | Page             |

|-----------------------------------------------------------------|------------------|

|                                                                 | 1                |

| • 「 <i>推奨動作条件」</i> 表における自由気流での動作温度を更新                           | 4                |

| • DとPW パッケージの熱抵抗を「熱に関する情報」に更新                                   | 5                |

| • 「Vref 対温度」および「エラー アンプ」を追加。「代表的特性」セクション内の「入力と温度の関係」の図          | ] <mark>7</mark> |

| Changes from Revision E (August, 2016) to Revision F (May 2020) | Page             |

| <ul><li>「絶対最大定格」セクションに注記を追加。</li></ul>                          | 4                |

| <ul><li>「電源」セクションを、デバイスの電源オンを反映するように変更</li></ul>                |                  |

|                                                                 |                  |

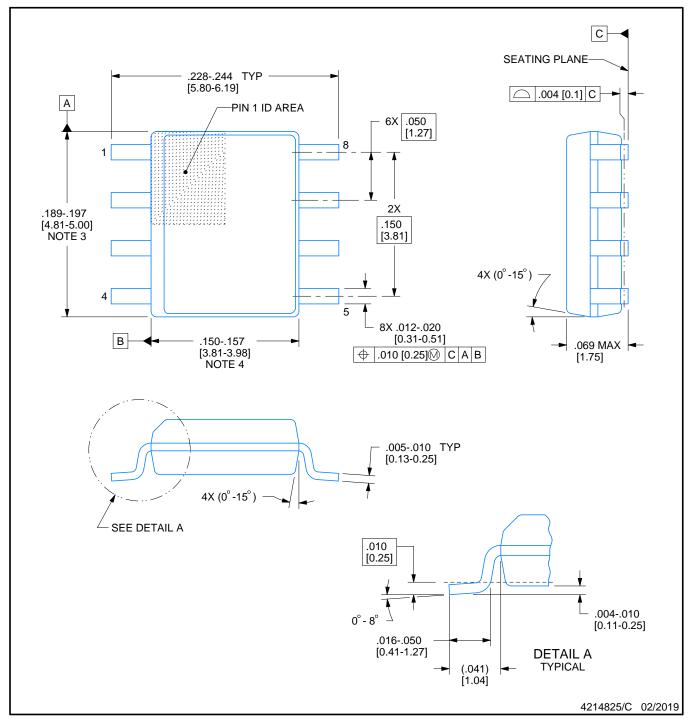

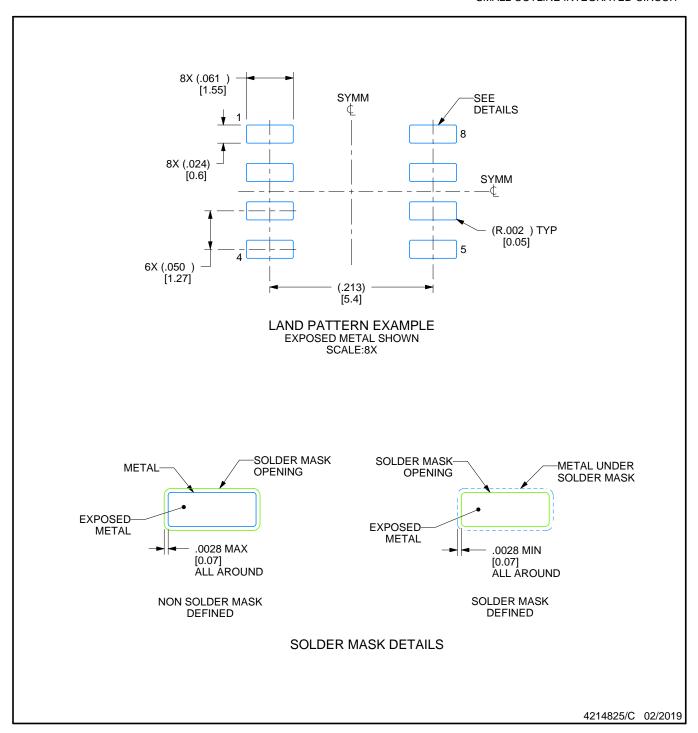

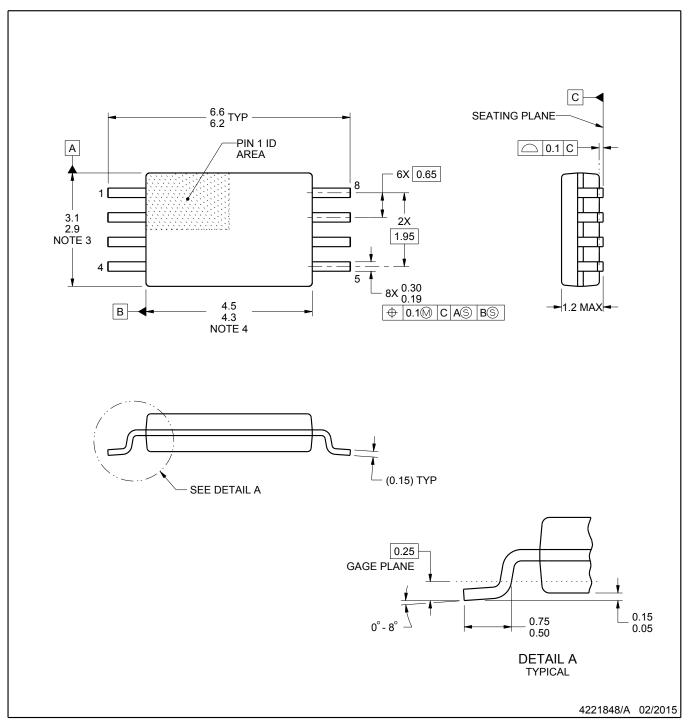

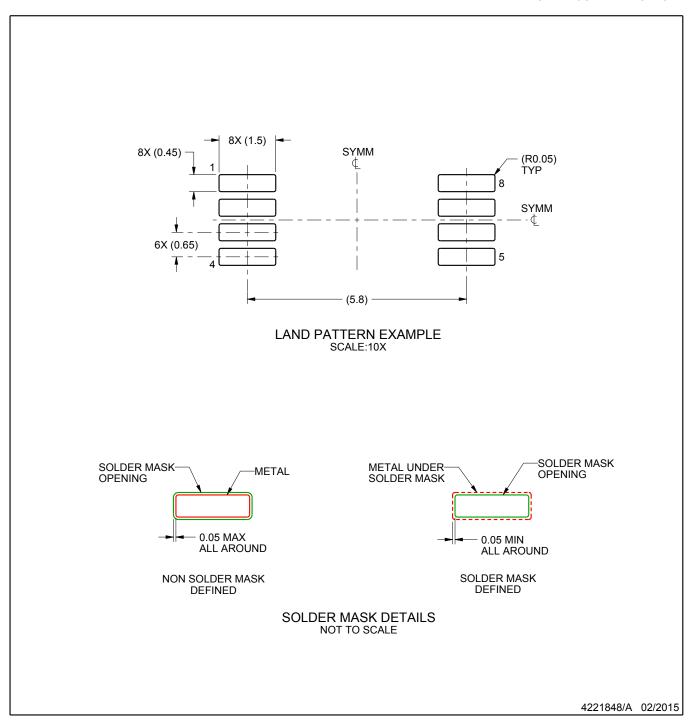

# 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

English Data Sheet: SLUS161

# 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated www.ti.com

7-Nov-2025

# **PACKAGING INFORMATION**

| Orderable part number | Status   | Material type | Package   Pins | Package qty   Carrier                                      | <b>RoHS</b> (3)                 | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C)   | Part marking (6) |

|-----------------------|----------|---------------|----------------|------------------------------------------------------------|---------------------------------|-------------------------------|----------------------------|----------------|------------------|

| UCC2813D-0            | Obsolete | Production    | SOIC (D)   8   | -                                                          | -                               | Call TI                       | Call TI                    | -40 to 85      | 2813D-0<br>D-0   |

| UCC2813D-1            | Obsolete | Production    | SOIC (D)   8   | -                                                          | -                               | Call TI                       | Call TI                    | -40 to 85      | 2813D-1<br>D-1   |

| UCC2813D-2            | Obsolete | Production    | SOIC (D)   8   | -                                                          | -                               | Call TI                       | Call TI                    | -40 to 85      | 2813D-2<br>D-2   |

| UCC2813D-3            | Obsolete | Production    | SOIC (D)   8   | -                                                          | -                               | Call TI                       | Call TI                    | -40 to 85      | 2813D-3<br>D-3   |

| UCC2813D-4            | Obsolete | Production    | SOIC (D)   8   | -                                                          | -                               | Call TI                       | Call TI                    | -40 to 85      | 2813D-4<br>D-4   |

| UCC2813D-5            | Obsolete | Production    | SOIC (D)   8   | -                                                          | -                               | Call TI                       | Call TI                    | -40 to 85      | 2813D-5<br>D-5   |

| UCC2813DTR-0          | Active   | Production    | SOIC (D)   8   | 2500   LARGE T&R                                           | Yes                             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85      | 2813D-0<br>D-0   |

| UCC2813DTR-0.A        | Active   | Production    | SOIC (D)   8   | 2500   LARGE T&R                                           | Yes                             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85      | 2813D-0<br>D-0   |

| UCC2813DTR-0G4        | Active   | Production    | SOIC (D)   8   | 2500   LARGE T&R                                           | Yes                             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85      | 2813D-0<br>D-0   |

| UCC2813DTR-1          | Active   | Production    | SOIC (D)   8   | 2500   LARGE T&R                                           | Yes                             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85      | 2813D-1<br>D-1   |

| UCC2813DTR-1.A        | Active   | Production    | SOIC (D)   8   | 2500   LARGE T&R                                           | Yes                             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85      | 2813D-1<br>D-1   |

| UCC2813DTR-2          | Active   | Production    | SOIC (D)   8   | 2500   LARGE T&R                                           | Yes                             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85      | 2813D-2<br>D-2   |

| UCC2813DTR-2.A        | Active   | Production    | SOIC (D)   8   | OIC (D)   8 2500   LARGE T&R Yes NIPDAU Level-1-260C-UNLIM |                                 | -40 to 85                     | 2813D-2<br>D-2             |                |                  |

| UCC2813DTR-3          | Active   | Production    | SOIC (D)   8   | 2500   LARGE T&R                                           | R Yes NIPDAU Level-1-260C-UNLIM |                               | -40 to 85                  | 2813D-3<br>D-3 |                  |

| UCC2813DTR-3.A        | Active   | Production    | SOIC (D)   8   | 2500   LARGE T&R                                           | Yes                             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85      | 2813D-3<br>D-3   |

| UCC2813DTR-4          | Active   | Production    | SOIC (D)   8   | 2500   LARGE T&R                                           | Yes                             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85      | 2813D-4<br>D-4   |

7-Nov-2025 www.ti.com

| Orderable part number | Status (1) | Material type | Package   Pins | Package qty   Carrier                          | (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|------------|---------------|----------------|------------------------------------------------|-----|-------------------------------|----------------------------|--------------|------------------|

| UCC2813DTR-4.A        | Active     | Production    | SOIC (D)   8   | 2500   LARGE T&R                               | Yes | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | 2813D-4<br>D-4   |

| UCC2813DTR-4G4        | Active     | Production    | SOIC (D)   8   | 2500   LARGE T&R                               | Yes | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | 2813D-4<br>D-4   |

| UCC2813DTR-5          | Active     | Production    | SOIC (D)   8   | 2500   LARGE T&R                               | Yes | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | 2813D-5<br>D-5   |

| UCC2813DTR-5.A        | Active     | Production    | SOIC (D)   8   | 2500   LARGE T&R Yes NIPDAU Level-1-260C-UNLIM |     | -40 to 85                     | 2813D-5<br>D-5             |              |                  |

| UCC2813PW-0           | Obsolete   | Production    | TSSOP (PW)   8 | -                                              | -   | Call TI                       | Call TI                    | -40 to 85    | 28130            |

| UCC2813PW-1           | Obsolete   | Production    | TSSOP (PW)   8 | -                                              | -   | Call TI                       | Call TI                    | -40 to 85    | 28131            |

| UCC2813PW-2           | Active     | Production    | TSSOP (PW)   8 | 150   TUBE                                     | Yes | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | 28132            |

| UCC2813PW-2.A         | Active     | Production    | TSSOP (PW)   8 | 150   TUBE                                     | Yes | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | 28132            |

| UCC2813PW-3           | Obsolete   | Production    | TSSOP (PW)   8 | -                                              | -   | Call TI                       | Call TI                    | -40 to 85    | 28133            |

| UCC2813PW-4           | Obsolete   | Production    | TSSOP (PW)   8 | -                                              | -   | Call TI                       | Call TI                    | -40 to 85    | 28134            |

| UCC2813PW-5           | Obsolete   | Production    | TSSOP (PW)   8 | -                                              | -   | Call TI                       | Call TI                    | -40 to 85    | 28135            |

| UCC2813PWTR-0         | Active     | Production    | TSSOP (PW)   8 | 2000   LARGE T&R                               | Yes | Call TI   Nipdau              | Level-2-260C-1 YEAR        | -40 to 85    | 28130            |

| UCC2813PWTR-0.A       | Active     | Production    | TSSOP (PW)   8 | 2000   LARGE T&R                               | Yes | Call TI                       | Level-2-260C-1 YEAR        | -40 to 85    | 28130            |

| UCC2813PWTR-1         | Active     | Production    | TSSOP (PW)   8 | 2000   LARGE T&R                               | Yes | Call TI   Nipdau              | Level-2-260C-1 YEAR        | -40 to 85    | 28131            |

| UCC2813PWTR-1.A       | Active     | Production    | TSSOP (PW)   8 | 2000   LARGE T&R                               | Yes | Call TI                       | Level-2-260C-1 YEAR        | -40 to 85    | 28131            |

| UCC2813PWTR-3         | Active     | Production    | TSSOP (PW)   8 | 2000   LARGE T&R                               | Yes | Call TI   Nipdau              | Level-2-260C-1 YEAR        | -40 to 85    | 28133            |

| UCC2813PWTR-3.A       | Active     | Production    | TSSOP (PW)   8 | 2000   LARGE T&R                               | Yes | Call TI                       | Level-2-260C-1 YEAR        | -40 to 85    | 28133            |

| UCC2813PWTR-4         | Active     | Production    | TSSOP (PW)   8 | 2000   LARGE T&R                               | Yes | Call TI   Nipdau              | Level-2-260C-1 YEAR        | -40 to 85    | 28134            |

| UCC2813PWTR-4.A       | Active     | Production    | TSSOP (PW)   8 | 2000   LARGE T&R                               | Yes | Call TI                       | Level-2-260C-1 YEAR        | -40 to 85    | 28134            |

| UCC2813PWTR-4G4       | Active     | Production    | TSSOP (PW)   8 | 2000   LARGE T&R                               | Yes | Call TI                       | Level-2-260C-1 YEAR        | -40 to 85    | 28134            |

| UCC2813PWTR-5         | Active     | Production    | TSSOP (PW)   8 | 2000   LARGE T&R                               | Yes | Call TI   Nipdau              | Level-2-260C-1 YEAR        | -40 to 85    | 28135            |

| UCC2813PWTR-5.A       | Active     | Production    | TSSOP (PW)   8 | 2000   LARGE T&R                               | Yes | Call TI                       | Level-2-260C-1 YEAR        | -40 to 85    | 28135            |

| UCC3813D-0            | Obsolete   | Production    | SOIC (D)   8   | -                                              | -   | Call TI                       | Call TI                    | 0 to 70      | 3813D-0<br>D-0   |

| UCC3813D-1            | Obsolete   | Production    | SOIC (D)   8   | -                                              | -   | Call TI                       | Call TI                    | 0 to 70      | 3813D-1<br>D-1   |

| UCC3813D-2            | Obsolete   | Production    | SOIC (D)   8   | -                                              | -   | Call TI                       | Call TI                    | 0 to 70      | 3813D-2<br>D-2   |

www.ti.com

7-Nov-2025

| Orderable part number | Status (1) | Material type (2) | Package   Pins | Package qty   Carrier    | <b>RoHS</b> (3)                                    | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C)   | Part marking (6) |

|-----------------------|------------|-------------------|----------------|--------------------------|----------------------------------------------------|-------------------------------|----------------------------|----------------|------------------|

| UCC3813D-3            | Obsolete   | Production        | SOIC (D)   8   | -                        | -                                                  | Call TI                       | Call TI                    | 0 to 70        | 3813D-3<br>D-3   |

| UCC3813D-4            | Obsolete   | Production        | SOIC (D)   8   | -                        | -                                                  | Call TI                       | Call TI                    | 0 to 70        | 3813D-4<br>D-4   |

| UCC3813D-5            | Obsolete   | Production        | SOIC (D)   8   | -                        | -                                                  | Call TI                       | Call TI                    | 0 to 70        | 3813D-5<br>D-5   |

| UCC3813DTR-0          | Active     | Production        | SOIC (D)   8   | 2500   LARGE T&R         | Yes                                                | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70        | 3813D-0<br>D-0   |

| UCC3813DTR-0.A        | Active     | Production        | SOIC (D)   8   | 2500   LARGE T&R         | Yes                                                | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70        | 3813D-0<br>D-0   |

| UCC3813DTR-1          | Active     | Production        | SOIC (D)   8   | 2500   LARGE T&R         | Yes                                                | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70        | 3813D-1<br>D-1   |

| UCC3813DTR-1.A        | Active     | Production        | SOIC (D)   8   | 2500   LARGE T&R Yes NIP |                                                    | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70        | 3813D-1<br>D-1   |

| UCC3813DTR-1G4        | Active     | Production        | SOIC (D)   8   | 2500   LARGE T&R         | 500   LARGE T&R Yes NIPDAU Level-1-260C-UNLIM 0 to |                               | 0 to 70                    | 3813D-1<br>D-1 |                  |

| UCC3813DTR-2          | Active     | Production        | SOIC (D)   8   | 2500   LARGE T&R         | Yes                                                | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70        | 3813D-2<br>D-2   |

| UCC3813DTR-2.A        | Active     | Production        | SOIC (D)   8   | 2500   LARGE T&R         | Yes                                                | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70        | 3813D-2<br>D-2   |

| UCC3813DTR-3          | Active     | Production        | SOIC (D)   8   | 2500   LARGE T&R         | Yes                                                | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70        | 3813D-3<br>D-3   |

| UCC3813DTR-3.A        | Active     | Production        | SOIC (D)   8   | 2500   LARGE T&R         | Yes                                                | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70        | 3813D-3<br>D-3   |

| UCC3813DTR-4          | Active     | Production        | SOIC (D)   8   | 2500   LARGE T&R         | Yes                                                | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70        | 3813D-4<br>D-4   |

| UCC3813DTR-4.A        | Active     | Production        | SOIC (D)   8   | 2500   LARGE T&R         | Yes                                                | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70        | 3813D-4<br>D-4   |

| UCC3813DTR-5          | Active     | Production        | SOIC (D)   8   | 2500   LARGE T&R         | Yes                                                | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70        | 3813D-5<br>D-5   |

| UCC3813DTR-5.A        | Active     | Production        | SOIC (D)   8   | 2500   LARGE T&R         | Yes                                                | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70        | 3813D-5<br>D-5   |

| UCC3813PW-0           | Obsolete   | Production        | TSSOP (PW)   8 | -                        | -                                                  | Call TI                       | Call TI                    | 0 to 70        | 38130            |

| UCC3813PW-1           | Obsolete   | Production        | TSSOP (PW)   8 | -                        | -                                                  | Call TI                       | Call TI                    | 0 to 70        | 38131            |

| UCC3813PW-2           | Active     | Production        | TSSOP (PW)   8 | 150   TUBE               | Yes                                                | NIPDAU                        | Level-2-260C-1 YEAR        | 0 to 70        | 38132            |

www.ti.com 7-Nov-2025

| Orderable part number | Status (1) | Material type | Package   Pins | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|------------|---------------|----------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

| UCC3813PW-2.A         | Active     | Production    | TSSOP (PW)   8 | 150   TUBE            | Yes             | (4)<br>NIPDAU                 | (5)<br>Level-2-260C-1 YEAR | 0 to 70      | 38132            |

| UCC3813PW-3           | Obsolete   | Production    | TSSOP (PW)   8 | -                     | -               | Call TI                       | Call TI                    | 0 to 70      | 38133            |

| UCC3813PW-4           | Obsolete   | Production    | TSSOP (PW)   8 | -                     | -               | Call TI                       | Call TI                    | 0 to 70      | 38134            |

| UCC3813PW-5           | Obsolete   | Production    | TSSOP (PW)   8 | -                     | -               | Call TI                       | Call TI                    | 0 to 70      | 38135            |