## **UCC28070-Q1 インターリープ連続導通モード PFC コントローラ**

### 1 特長

- 車載アプリケーション用に AEC-Q100 認定済み:

- 温度グレード 1,  $T_A: -40^\circ\text{C} \sim 125^\circ\text{C}$

- デバイス HBM ESD 分類レベル 2

- デバイス CDM ESD 分類レベル C4

- 独自の電流マッチングを用いたインターリープ動作で平均電流モードの PWM 制御

- 高度な電流シンセサイザを用いた電流検出による高効率の実現

- 外部クロックへの同期機能

- ユニティ PF に近づけるための、内部量子化電圧フィードフォワードを用いた直線性が高い乗算器

- 電圧アンプの出力電流のスルーレート補正により過渡応答を強化

- プログラマブルな周波数 (30kHz~300kHz)

- プログラム可能な最大デューティサイクル クランプ

- プログラム可能な周波数のディザリングレートと振幅(最大 30kHz)により EMI を低減

- プログラマブルソフトスタート

- ピーク電流制限をプログラム可能

- PFC ディスエーブルの外部インターフェイス

- 保護:バイアス電源 UVLO、出力過電圧、開ループ検出、VSENSE と VINAC の開回路検出、PFC イネーブル監視

### 2 アプリケーション

- 統合型高電圧 (OBC:オンボード チャージャと DC/DC)

- オンボード チャージャ

- バッテリ チャージャ

- AC 充電 (パイル) ステーション

- スタンダードアロン航空向け PFC

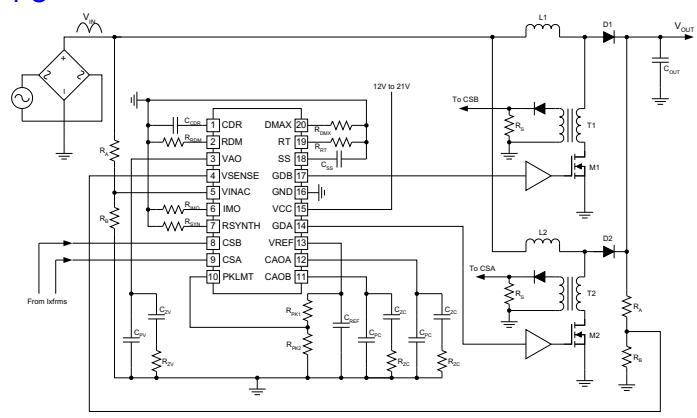

**アプリケーション概略図**

### 3 説明

UCC28070-Q1 は、連続導通モード (CCM) 昇圧の型で 180° インターリープ動作する 2 つのパルス幅変調 (PWM) を統合した、高度な力率補正 (PFC) コントローラです。UCC28070 から派生したこのデバイスは、30kHz~300kHz の周波数でスイッチングできます。

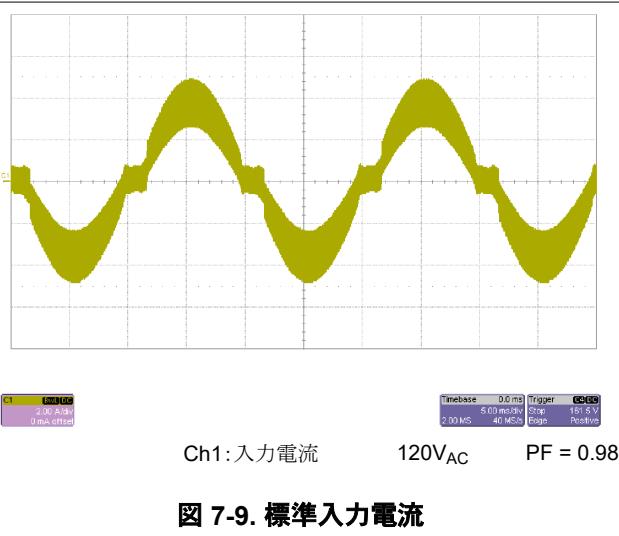

180° ずらしてインターリープ動作させることで、高周波の入力および出力リップル電流が大幅に低減され、伝導性 EMI フィルタリングが容易かつ低成本で実現できます。

UCC28070-Q1 は、電流合成や量子化電圧フィードフォワードなどの複数の新機能を備えており、力率 (PF)、効率、全高調波歪み (THD)、および過渡応答の性能向上を促進します。また、周波数ディザリング、クロック同期、スルーレート拡張により、性能向上の可能性がさらに広がります。保護機能には、出力過電圧検出、プログラム可能なピーク電流制限、低電圧誤動作防止、開ループ保護が搭載されています。

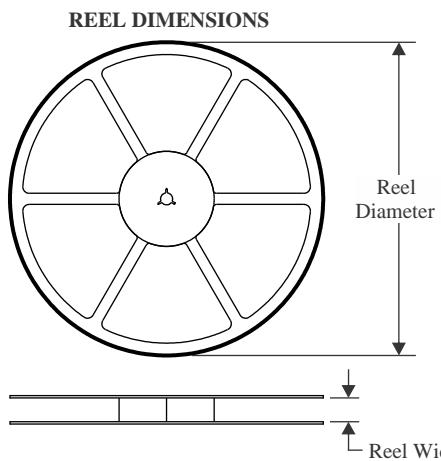

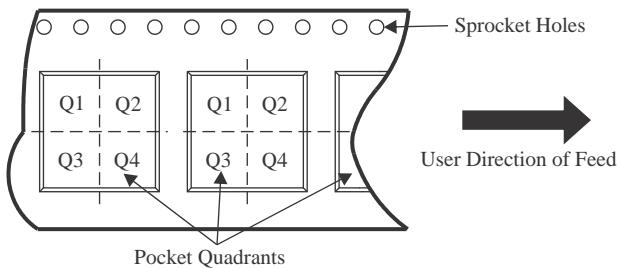

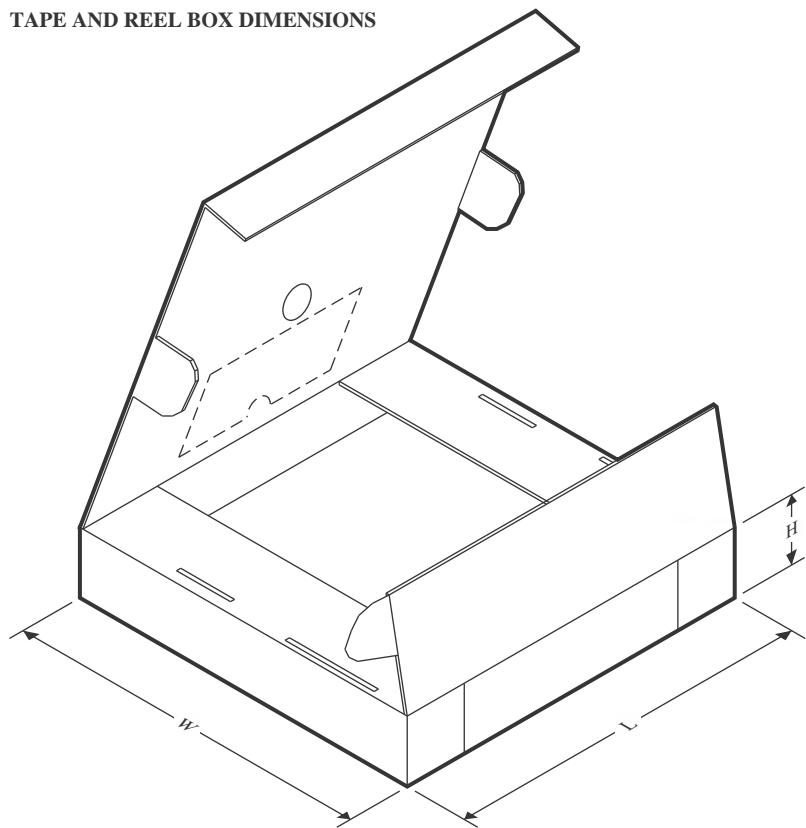

### パッケージ情報

| 部品番号        | パッケージ <sup>1</sup> | パッケージサイズ <sup>2</sup> |

|-------------|--------------------|-----------------------|

| UCC28070-Q1 | PW (TSSOP, 20)     | 6.50mm × 4.40mm       |

- (1) 利用可能なすべてのパッケージについては、「[メカニカル、パッケージ、および注文情報](#)」を参照してください。

(2) パッケージサイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                    |           |                               |           |

|--------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>        | <b>1</b>  | 6.4 デバイスの機能モード                | <b>31</b> |

| <b>2 アプリケーション</b>  | <b>1</b>  | <b>7 アプリケーションと実装</b>          | <b>32</b> |

| <b>3 説明</b>        | <b>1</b>  | 7.1 アプリケーション情報                | <b>32</b> |

| <b>4 ピン構成および機能</b> | <b>3</b>  | 7.2 代表的なアプリケーション              | <b>32</b> |

| <b>5 仕様</b>        | <b>5</b>  | 7.3 電源に関する推奨事項                | <b>41</b> |

| 5.1 絶対最大定格         | 5         | 7.4 レイアウト                     | <b>42</b> |

| 5.2 ESD 定格         | 5         | <b>8 デバイスおよびドキュメントのサポート</b>   | <b>43</b> |

| 5.3 推奨動作条件         | 6         | 8.1 ドキュメントのサポート               | <b>43</b> |

| 5.4 熱に関する情報        | 6         | 8.2 ドキュメントの更新通知を受け取る方法        | <b>43</b> |

| 5.5 電気的特性          | 7         | 8.3 サポート・リソース                 | <b>43</b> |

| 5.6 代表的特性          | 11        | 8.4 商標                        | <b>43</b> |

| <b>6 詳細説明</b>      | <b>14</b> | 8.5 静電気放電に関する注意事項             | <b>43</b> |

| 6.1 概要             | 14        | 8.6 用語集                       | <b>43</b> |

| 6.2 機能ブロック図        | 15        | <b>9 改訂履歴</b>                 | <b>44</b> |

| 6.3 機能説明           | 16        | <b>10 メカニカル、パッケージ、および注文情報</b> | <b>44</b> |

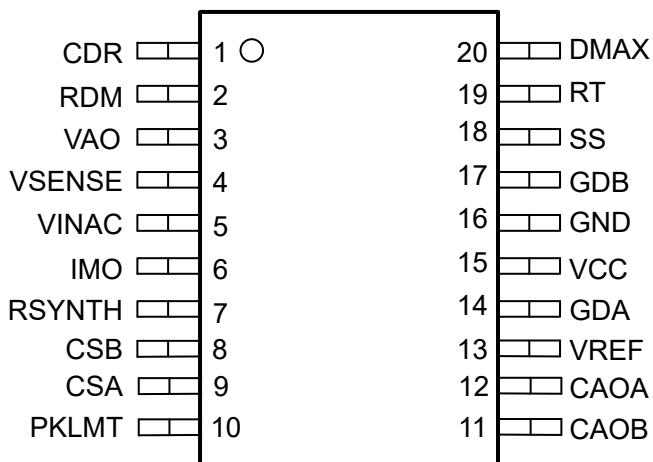

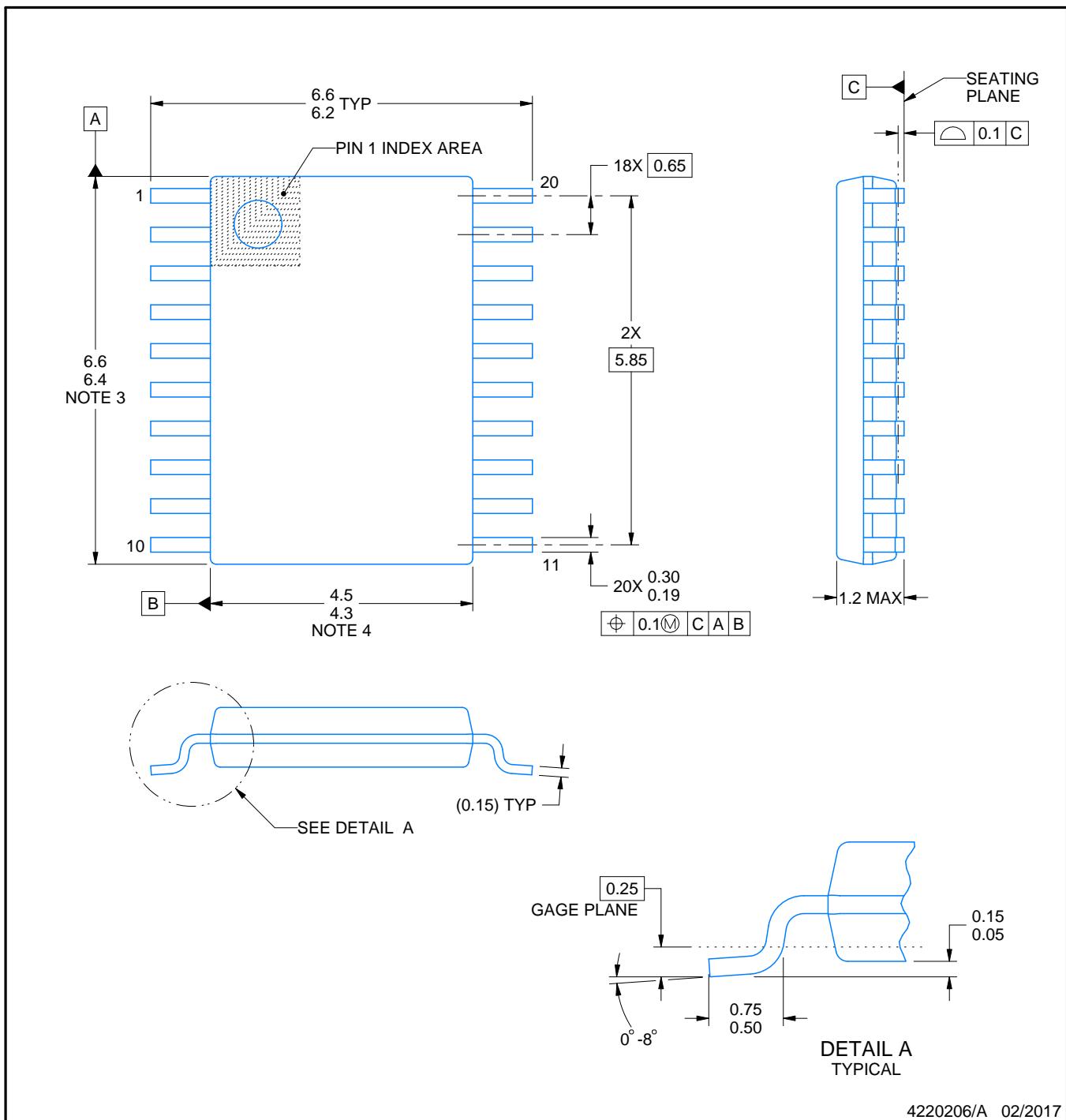

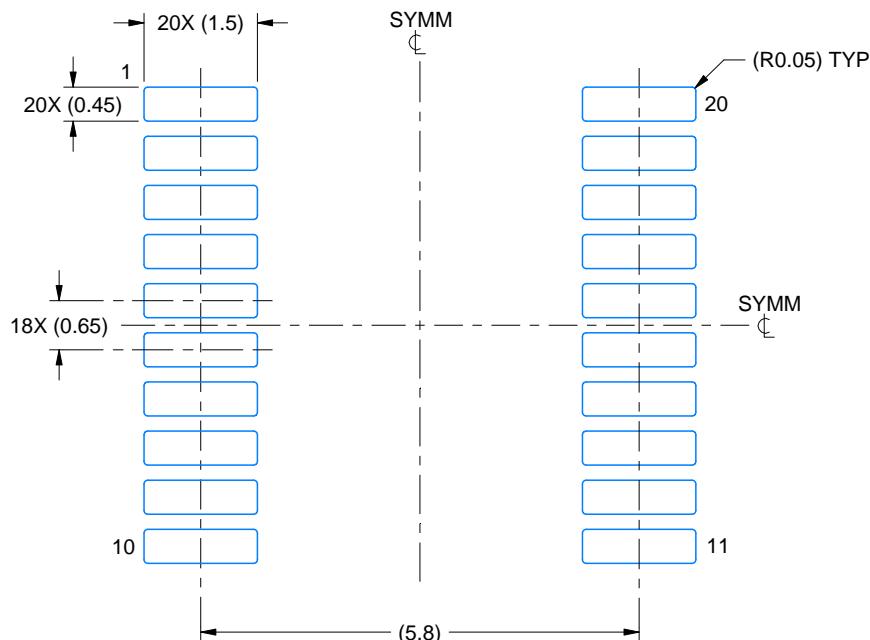

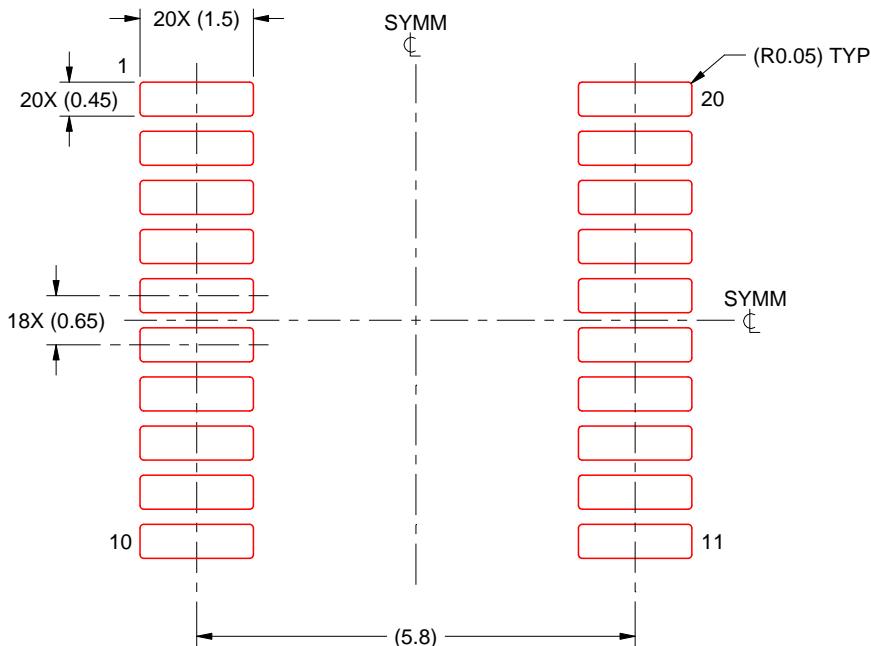

## 4 ピン構成および機能

図 4-1. PW パッケージ、20 ピン TSSOP (上面図)

表 4-1. ピンの機能

| 番号 | ピン<br>名称      | I/O | 説明                                                                                                                                                                                                                                                                                    |

|----|---------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | CDR           | I   | ディザレートコンデンサ。周波数ディザリングのタイミングピン。外付けコンデンサを GND に接続することで、発振器のディザレートが設定されます。ジッタリングを無効にするには、CDR ピンを VREF ピンに接続し、RDM ピンを GND に接続します。                                                                                                                                                         |

| 2  | RDM<br>(SYNC) | I   | ディザリング振幅抵抗。周波数ディザ量および外部同期ピン。外部抵抗を GND に接続することで、発振器周波数ジッタリングの振幅を設定できます。周波数ジッタリングが無効化されている場合 (CDR > 5V)、内部マスタクロックは RDM ピンに入力される立ち上がりエッジに同期します。ジッタリングを無効にし、同期を使用しない場合は、RDM をゼロオーム抵抗で GND に接続します。                                                                                         |

| 3  | VAO           | O   | 電圧アンプ出力。相互コンダクタンス電圧誤差アンプの出力。乗算器入力およびゼロパワー コンパレータに内部接続されています。このピンと GND の間に電圧制御ループ補償部品を接続します。                                                                                                                                                                                           |

| 4  | VSENSE        | I   | 出力電圧センス。相互コンダクタンス電圧誤差アンプの反転入力および電流合成差動アンプの正端子に内部接続。OVP、PFC イネーブル、スルーレートコンパレータにも接続されています。抵抗分圧回路を使用して PFC 出力に接続します。                                                                                                                                                                     |

| 5  | VINAC         | I   | スケーリングされた AC ライン入力電圧。乗算器および電流合成差動アンプの負端子に内部接続されています。VIN、VINAC、GND の間に、VSENSE に接続された PFC 出力分圧回路と同じ抵抗回路を接続します。                                                                                                                                                                          |

| 6  | IMO           | O   | 乗算器出力電流。乗算器ゲインを設定するため、このピンと GND の間に抵抗を接続します。                                                                                                                                                                                                                                          |

| 7  | RSYNTH        | I   | 電流合成ダウンスローププログラミング。このピンと GND の間に抵抗を接続することで、電流合成器の下降スロープ速度を設定できます。RSYNTH を VREF に接続すると電流合成が無効化され、CSA と CSB がそれぞれの電流アンプに内部的に直接接続されます。                                                                                                                                                   |

| 8  | CSB           | I   | 位相 B 電流検出入力。GDB のオン時間中、RSYNTH が VREF に接続されていない場合、CSB は電流合成段を介して内部的位相に B 電流アンプの反転入力に接続されます。                                                                                                                                                                                            |

| 9  | CSA           | I   | 位相 A 電流検出入力。GDA のオン時間中、RSYNTH が VREF に接続されていない場合、CSA は電流合成段を介して内部的位相 A 電流アンプの反転入力に接続されます。                                                                                                                                                                                             |

| 10 | PKLMT         | I   | ピーク電流制限のプログラミング。サイクルごとのピーク電流制限コンパレータの電圧スレッショルドを設定するため、VREF とこのピンの間に抵抗分圧ネットワークを接続します。目的の $\Delta I_{LB}$ に合わせて調整できます。                                                                                                                                                                  |

| 11 | CAOB          | O   | 位相 B 電流アンプ出力。位相 B の相互コンダクタンス電流アンプの出力。トレーリング エッジ変調用に、位相 B PWM コンパレータの反転入力に内部接続します。このピンと GND の間に電流制御ループ補償部品を接続します。                                                                                                                                                                      |

| 12 | CAOA          | O   | 位相 A 電流アンプ出力。位相 A の相互コンダクタンス電流アンプの出力。トレーリング エッジ変調用に、位相 A PWM コンパレータの反転入力に内部接続します。このピンと GND の間に電流制御ループ補償部品を接続します。                                                                                                                                                                      |

| 13 | VREF          | O   | 6V のリファレンス電圧と内部バイアス電圧。このピンと GND にできるだけ近接して、0.1μF のセラミックバイパスコンデンサを接続します。                                                                                                                                                                                                               |

| 14 | GDA           | O   | 位相 A のゲートドライブ。この電流制限付き出力は、フェーズ A のスイッチング素子を駆動するのに適した別個のゲートドライブデバイスに接続することを目的としています。出力電圧は通常 13.5V にクランプされます。                                                                                                                                                                           |

| 15 | VCC           | I   | バイアス電圧入力。このピンと GND にできるだけ近接して、0.1μF のセラミックバイパスコンデンサを接続します。                                                                                                                                                                                                                            |

| 16 | GND           | I/O | デバイスグランドリファレンス。すべての補償およびプログラミング用の抵抗、コンデンサネットワークをこのピンに接続します。大電流ノイズの絶縁のため、このピンを別のパターンを介してシステムに接続します。                                                                                                                                                                                    |

| 17 | GDB           | O   | 位相 B ゲートドライブ。この電流制限付き出力は、位相 B のスイッチング素子を駆動するのに適した別個のゲートドライブデバイスに接続することを目的としています。出力電圧は通常 13.5V にクランプされます。                                                                                                                                                                              |

| 18 | SS            | I   | ソフトスタートおよび外部フォルトインターフェイス。内部で固定された 10μA の電流源に基づきソフトスタートのスルーレートを設定するため、このピンにコンデンサを GND に接続します。VSENSE の制御リファレンス電圧は、V <sub>SS</sub> が 3V を超えるまで V <sub>SS</sub> にクランプされます。特定の故障状態から回復する際、SS ピンには 1mA の電流源が存在し、SS 電圧が VSENSE 電圧に達するまで流れます。SS ピンを 0.6V 未満にすると、GDA 出力と GDB 出力の両方が即座に無効化されます。 |

| 19 | RT            | I   | タイミング抵抗。発振周波数プログラミングピン。GND への抵抗によって、内部発振器の動作周波数が設定されます。                                                                                                                                                                                                                               |

| 20 | DMAX          | I   | 最大デューティサイクル抵抗。最大 PWM デューティサイクルプログラミングピン。GND との間に抵抗を接続することで、R <sub>DMX</sub> / R <sub>RT</sub> の比に基づいて、PWM の最大デューティサイクルが設定されます。                                                                                                                                                        |

## 5 仕様

### 5.1 絶対最大定格

外気温度範囲での動作時 (特に記述がない限り)<sup>(1) (2) (3) (4)</sup>

|                  |                                                                                    | 最小値  | 最大値            | 単位 |

|------------------|------------------------------------------------------------------------------------|------|----------------|----|

| 電源電圧             | VCC                                                                                |      | 22             | V  |

| 電源電流、 $I_{VCC}$  |                                                                                    |      | 20             | mA |

| ゲート駆動電流 - 連続     | GDA, GDB                                                                           |      | $\pm 0.25$     | A  |

| ゲート駆動電流 - パルス    | GDA, GDB                                                                           |      | $\pm 0.75$     | A  |

| 電圧               | GDA, GDB                                                                           | -0.5 | $V_{CC} + 0.3$ | V  |

|                  | DMAX, RDM, RT, CDR, VINAC, VSENSE, SS, VAO, IMO, CSA, CSB, CAOA, CAOB, PKLMT, VREF | -0.5 | 7              |    |

| 電流               | RT, DMAX, RDM, RSYNTH                                                              |      | -0.5           | mA |

|                  | VREF, VAO, CAOA, CAOB, IMO                                                         |      | 10             |    |

| リード温度 (10 秒)     |                                                                                    |      | 260            | °C |

| 動作時の接合部温度、 $T_J$ |                                                                                    | -40  | 125            | °C |

| 保管温度、 $T_{stg}$  |                                                                                    | -65  | 150            | °C |

- (1) 「絶対最大定格」を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これらはストレス評価のみであり、セクション 5.3 で示された条件を超えるこれらの条件またはその他の条件下でのデバイスの機能動作を保証するものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

- (2) すべての電圧は GND を基準にしています。

- (3) すべての電流は、端子に流れ込む方向が正、端子から流れ出る方向が負です。

- (4) 通常使用では、端子 GDA および GDB は外部ゲートドライバに接続され、出力電流が内部的に制限されています。

### 5.2 ESD 定格

|             |      | 値                                                       | 単位   |

|-------------|------|---------------------------------------------------------|------|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>    | 2000 |

|             |      | デバイス帯電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠 <sup>(2)</sup> | 500  |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 5.3 推奨動作条件

外気温度範囲での動作時 (特に記述がない限り)

|                            |  | 最小値        | 最大値 | 単位 |

|----------------------------|--|------------|-----|----|

| (低インピーダンスの電源からの) VCC 入力電圧  |  | v UVLO + 1 | 21  | V  |

| VREF への負荷電流                |  |            | 2   | mA |

| VINAC への入力電圧               |  | 0          | 3   | V  |

| IMO の電圧                    |  | 0          | 3.3 | V  |

| CSA、CSB、PKLMT への電圧         |  | 0          | 3.6 | V  |

| R <sub>SYN</sub> RSYNTH 抵抗 |  | 15         | 750 | kΩ |

| R <sub>RDM</sub> RDM 抵抗    |  | 30         | 330 | kΩ |

## 5.4 热に関する情報

| 熱評価基準 <sup>(1)</sup>                      | UCC28070-Q1   |  | 単位   |  |

|-------------------------------------------|---------------|--|------|--|

|                                           | PW<br>(TSSOP) |  |      |  |

|                                           | 20 ピン         |  |      |  |

| R <sub>θJA</sub> 接合部から周囲への熱抵抗             | 99.9          |  | °C/W |  |

| R <sub>θJC(top)</sub> 接合部からケース (上面) への熱抵抗 | 34.1          |  | °C/W |  |

| R <sub>θJB</sub> 接合部から基板への熱抵抗             | 50.8          |  | °C/W |  |

| Ψ <sub>JT</sub> 接合部から上面への特性パラメータ          | 1.9           |  | °C/W |  |

| Ψ <sub>JB</sub> 接合部から基板への特性パラメータ          | 50.3          |  | °C/W |  |

- (1) 従来および最新の熱測定基準の詳細については、アプリケーション レポート『半導体および IC パッケージの熱評価基準』、[SPRA953](#) を参照してください。

## 5.5 電気的特性

$T_J = T_A = -40^\circ\text{C} \sim 125^\circ\text{C}$ ,  $V_{CC} = 12\text{V}$ ,  $\text{GND} = 0\text{V}$ ,  $R_{RT} = 75\text{k}\Omega$ ,  $R_{DMX} = 68.1\text{k}\Omega$ ,  $R_{RDM} = R_{SYN} = 100\text{k}\Omega$ ,  $C_{CDR} = 2.2\text{nF}$ ,  $C_{SS} = C_{VREF} = 0.1\mu\text{F}$ ,  $C_{VCC} = 1\mu\text{F}$ ,  $I_{VREF} = 0\text{mA}$  (特に記載のない限り)

| パラメータ                                   |                                | テスト条件                                                                                                             | 最小値                                              | 標準値  | 最大値  | 単位            |  |

|-----------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------|------|---------------|--|

| <b>バイアス電源</b>                           |                                |                                                                                                                   |                                                  |      |      |               |  |

| $V_{CC(\text{SHUNT})}$                  | $V_{CC}$ シャント電圧 <sup>(1)</sup> | $I_{VCC} = 10\text{mA}$                                                                                           | 23                                               | 25   | 27   | V             |  |

| $I_{VCC}$                               | 電源電流                           | ディセーブル $V_{VSENSE} = 0\text{V}$                                                                                   | 7                                                |      |      | mA            |  |

|                                         |                                | イネーブル $V_{VSENSE} = 3\text{V}$ (スイッチング)                                                                           | 9                                                | 12   |      |               |  |

|                                         |                                | UVLO $V_{CC} = 7\text{V}$                                                                                         |                                                  | 200  |      | $\mu\text{A}$ |  |

|                                         |                                | $V_{CC} = 9\text{V}$                                                                                              | 4                                                | 6    |      | mA            |  |

| $V_{UVLO}$                              | UVLO ターンオン スレッショルド             | $V_{CC}$ (立ち上がり時) で測定                                                                                             | 9.8                                              | 10.2 | 10.6 | V             |  |

|                                         | UVLO ヒステリシス                    | $V_{CC}$ (立ち下がり時) で測定                                                                                             |                                                  | 1    |      |               |  |

| $V_{REF}$ イネーブルスレッショルド                  |                                | $V_{CC}$ (立ち上がり時) で測定                                                                                             | 7.5                                              | 8    | 8.5  | V             |  |

| <b>リニアレギュレータ</b>                        |                                |                                                                                                                   |                                                  |      |      |               |  |

| $V_{VREF}$                              | リファレンス電圧                       | 無負荷 $I_{VREF} = 0\text{mA}$                                                                                       | 5.82                                             | 6    | 6.18 | V             |  |

|                                         |                                | 負荷除去 $V_{VREF}$ の変化として測定 ( $I_{VREF} = 0\text{mA}$ および $-2\text{mA}$ )                                            | -12                                              | 12   |      | mV            |  |

|                                         |                                | ライン除去 $V_{VREF}$ の変化として測定 ( $V_{CC} = 11\text{V}$ および $20\text{V}$ , $I_{VREF} = 0\mu\text{A}$ )                  | $T_A = 25^\circ\text{C}$                         | -12  | 12   |               |  |

|                                         |                                |                                                                                                                   | $T_A = -40^\circ\text{C} \sim 125^\circ\text{C}$ | -16  | 16   |               |  |

| <b>PFC イネーブル</b>                        |                                |                                                                                                                   |                                                  |      |      |               |  |

| $V_{EN}$                                | イネーブル スレッショルド                  | $V_{SENSE}$ (立ち上がり時) で測定                                                                                          | 0.65                                             | 0.75 | 0.85 | V             |  |

|                                         | イネーブル ヒステリシス                   |                                                                                                                   |                                                  | 0.15 |      |               |  |

| <b>外部 PFC ディスエーブル</b>                   |                                |                                                                                                                   |                                                  |      |      |               |  |

| スレッショルドをディセーブル                          |                                | SS (立ち下がり時) で測定                                                                                                   | 0.5                                              | 0.6  |      | V             |  |

| ヒステリシス                                  |                                | $V_{SENSE} > 0.85\text{V}$                                                                                        |                                                  | 0.15 |      | V             |  |

| <b>発振器</b>                              |                                |                                                                                                                   |                                                  |      |      |               |  |

| 出力位相シフト                                 |                                | GDA と GDB の間で測定                                                                                                   | 179                                              | 180  | 181  | °             |  |

| $V_{DMAX}$ 、<br>$V_{RT}$ 、<br>$V_{RDM}$ | タイミング レギュレーション電圧               | DMAX、RT、RDM で測定                                                                                                   | 2.91                                             | 3    | 3.09 | V             |  |

| $f_{PWM}$                               | PWM スイッチング周波数                  | $R_{RT} = 75\text{k}\Omega$ , $R_{DMX} = 68.1\text{k}\Omega$ ,<br>$V_{RDM} = 0\text{V}$ , $V_{CDR} = 6\text{V}$   | 94                                               | 100  | 105  | kHz           |  |

|                                         |                                | $R_{RT} = 24.9\text{k}\Omega$ , $R_{DMX} = 22.6\text{k}\Omega$ ,<br>$V_{RDM} = 0\text{V}$ , $V_{CDR} = 6\text{V}$ | 270                                              | 290  | 330  |               |  |

| $D_{MAX}$                               | デューティサイクル クランプ                 | $R_{RT} = 75\text{k}\Omega$ , $R_{DMX} = 68.1\text{k}\Omega$ ,<br>$V_{RDM} = 0\text{V}$ , $V_{CDR} = 6\text{V}$   | 92%                                              | 95%  | 98%  |               |  |

| 最小プログラム可能 OFF 時間                        |                                | $R_{RT} = 24.9\text{k}\Omega$ , $R_{DMX} = 22.6\text{k}\Omega$ ,<br>$V_{RDM} = 0\text{V}$ , $V_{CDR} = 6\text{V}$ | 50                                               | 150  | 250  | ns            |  |

| $f_{DM}$                                | $f_{PWM}$ での周波数ディザリング振幅の変化     | $R_{RDM} = 316\text{k}\Omega$ , $R_{RT} = 75\text{k}\Omega$                                                       | 1                                                | 3    | 4.3  | kHz           |  |

|                                         |                                | $R_{RDM} = 31.6\text{k}\Omega$ , $R_{RT} = 24.9\text{k}\Omega$                                                    | 23                                               | 30   | 36   |               |  |

| $f_{DR}$                                | $f_{PWM}$ の変化による周波数ディザリング率     | $R_{RDM} = 100\text{k}\Omega$ , $C_{CDR} = 2.2\text{nF}$                                                          |                                                  | 3    |      | kHz           |  |

|                                         |                                | $R_{RDM} = 100\text{k}\Omega$ , $C_{CDR} = 0.3\text{nF}$                                                          |                                                  | 20   |      |               |  |

| $I_{CDR}$                               | ディザ レート電流                      | CDR (シンクおよびソース) で測定                                                                                               |                                                  | ±10  |      | $\mu\text{A}$ |  |

|                                         | ディザーのディセーブルのスレッショルド            | CDR (立ち上がり時) で測定                                                                                                  | 5                                                | 5.25 |      | V             |  |

## 5.5 電気的特性 (続き)

$T_J = T_A = -40^\circ\text{C} \sim 125^\circ\text{C}$ ,  $V_{CC} = 12\text{V}$ ,  $\text{GND} = 0\text{V}$ ,  $R_{RT} = 75\text{k}\Omega$ ,  $R_{DMX} = 68.1\text{k}\Omega$ ,  $R_{RDM} = R_{SYN} = 100\text{k}\Omega$ ,  $C_{CDR} = 2.2\text{nF}$ ,  $C_{SS} = C_{VREF} = 0.1\mu\text{F}$ ,  $C_{VCC} = 1\mu\text{F}$ ,  $I_{VREF} = 0\text{mA}$  (特に記載のない限り)

| パラメータ          | テスト条件                                 | 最小値                                                                 | 標準値  | 最大値  | 単位            |

|----------------|---------------------------------------|---------------------------------------------------------------------|------|------|---------------|

| <b>クロック同期</b>  |                                       |                                                                     |      |      |               |

| $V_{CDR}$      | SYNC イネーブルスレッショルド                     | CDR (立ち上がり時) で測定                                                    | 5    | 5.25 | V             |

|                | SYNC 伝搬遅延                             | $V_{CDR} = 6\text{V}$ 、RDM (立ち上がり) から GDx (立ち上がり) までの測定             | 50   | 100  | ns            |

|                | SYNC スレッショルド (立ち上がり)                  | $V_{CDR} = 6\text{V}$ 、RDM で測定                                      | 1.2  | 1.5  | V             |

|                | SYNC スレッショルド (立ち下がり)                  | $V_{CDR} = 6\text{V}$ 、RDM で測定                                      | 0.4  | 0.7  | V             |

| $t_{SYNC}$     | SYNC パルス幅、最小                          | 正のパルス                                                               | 0.2  |      | $\mu\text{s}$ |

|                | 最大 SYNC パルス デューティ サイクル <sup>(2)</sup> |                                                                     | 50%  |      |               |

| <b>電圧アンプ</b>   |                                       |                                                                     |      |      |               |

|                | VSENSE 電圧                             | レギュレーション中、 $T_A = 25^\circ\text{C}$                                 | 2.94 | 3    | 3.06 V        |

|                | VSENSE 電圧                             | レギュレーション中                                                           | 2.84 | 3    | 3.10 V        |

|                | VSENSE 入力バイアス電流                       | レギュレーション中                                                           | 250  | 500  | $\text{nA}$   |

|                | VAO high 電圧                           | $V_{VSENSE} = 2.9\text{V}$                                          | 4.8  | 5    | 5.2 V         |

|                | VAO low 電圧                            | $V_{VSENSE} = 3.1\text{V}$                                          | 0.05 | 0.5  | V             |

| $g_{MV}$       | VAO 相互コンダクタンス                         | $V_{VSENSE} = 2.8\text{V} \sim 3.2\text{V}$ , $V_{VAO} = 3\text{V}$ | 70   |      | $\mu\text{S}$ |

|                | VAO シンク電流、オーバードライブ制限値                 | $V_{VSENSE} = 3.5\text{V}$ , $V_{VAO} = 3\text{V}$                  | 30   |      | $\mu\text{A}$ |

|                | VAO ソース電流、オーバードライブ                    | $V_{VSENSE} = 2.5\text{V}$ , $V_{VAO} = 3\text{V}$ , SS = 3V        | -30  |      | $\mu\text{A}$ |

|                | VAO ソース電流、<br>オーバードライブ制限 + $I_{SRC}$  | $V_{VSENSE} = 2.5\text{V}$ , $V_{VAO} = 3\text{V}$                  | -130 |      | $\mu\text{A}$ |

|                | スルーレート補正スレッショルド                       | $V_{VSENSE}$ (下降時)/ $V_{VSENSE}$ (レギュレーション時) として測定                  | 92%  | 93%  | 95%           |

|                | スルーレート補正のヒステリシス                       | VSENSE (立ち上がり時) で測定                                                 | 3    | 9    | $\text{mV}$   |

| $I_{SRC}$      | スルーレート補正電流                            | VAO で測定 (<br>VAO ソース電流も含む)                                          | -100 |      | $\mu\text{A}$ |

|                | スルーレート補正電圧スレッショルド                     | SS (立ち上がり時) で測定                                                     | 4    |      | V             |

|                | VAO 放電電流                              | $V_{VSENSE} = 0.5\text{V}$ , $V_{VAO} = 1\text{V}$                  | 10   |      | $\mu\text{A}$ |

| <b>ソフトスタート</b> |                                       |                                                                     |      |      |               |

| $I_{SS}$       | SS ソース電流                              | $V_{VSENSE} = 0.9\text{V}$ , $V_{SS} = 1\text{V}$                   | -10  |      | $\mu\text{A}$ |

|                | 適応型電流源                                | $V_{VSENSE} = 2\text{V}$ , $V_{SS} = 1\text{V}$                     | -1.5 | -2.5 | $\text{mA}$   |

|                | 適応型 SS の無効化                           | $V_{VSENSE} - V_{SS}$ として測定                                         | -30  | 0    | $\text{mV}$   |

|                | SS シンク電流                              | $V_{VSENSE} = 0.5\text{V}$ , $V_{SS} = 0.2\text{V}$                 | 0.5  | 0.9  | $\text{mA}$   |

| <b>過電圧</b>     |                                       |                                                                     |      |      |               |

| $V_{OVP}$      | OVP スレッショルド                           | $V_{VSENSE}$ (立ち上がり時)/ $V_{VSENSE}$ (レギュレーション時) として測定               | 104% | 106% | 108%          |

|                | OVP ヒステリシス                            | VSENSE (立ち下がり時) で測定                                                 | 100  |      | $\text{mV}$   |

|                | OVP 伝搬遅延                              | VSENSE (立ち上がり) と<br>GDx (立ち下がり) 間で測定                                | 0.2  | 0.3  | $\mu\text{s}$ |

## 5.5 電気的特性 (続き)

$T_J = T_A = -40^\circ\text{C} \sim 125^\circ\text{C}$ ,  $V_{CC} = 12\text{V}$ ,  $\text{GND} = 0\text{V}$ ,  $R_{RT} = 75\text{k}\Omega$ ,  $R_{DMX} = 68.1\text{k}\Omega$ ,  $R_{RDM} = R_{SYN} = 100\text{k}\Omega$ ,  $C_{CDR} = 2.2\text{nF}$ ,  $C_{SS} = C_{VREF} = 0.1\mu\text{F}$ ,  $C_{VCC} = 1\mu\text{F}$ ,  $I_{VREF} = 0\text{mA}$  (特に記載のない限り)

| パラメータ                 |                                                       | テスト条件                                                | 最小値  | 標準値  | 最大値  | 単位            |

|-----------------------|-------------------------------------------------------|------------------------------------------------------|------|------|------|---------------|

| <b>ゼロ電力</b>           |                                                       |                                                      |      |      |      |               |

| $V_{ZPWR}$            | ゼロパワー検出スレッショルド                                        | $V_{AO}$ (立ち下がり時)で測定                                 | 0.65 | 0.75 |      | V             |

|                       | ゼロパワー ヒステリシス                                          |                                                      |      | 0.15 |      | V             |

| <b>乗算器</b>            |                                                       |                                                      |      |      |      |               |

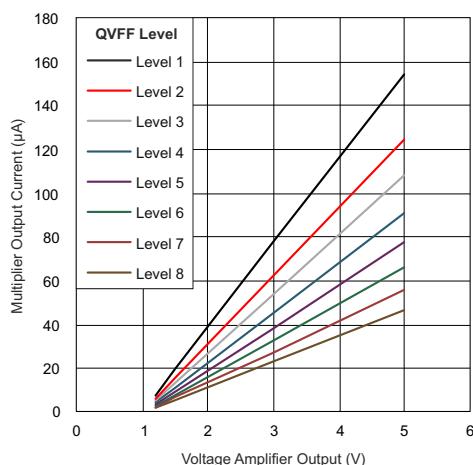

| $k_{MULT}$            | ゲイン定数                                                 | $V_{AO} \geq 1.5\text{V}$ , $T_A = 25^\circ\text{C}$ | 15.4 | 17   | 20   | $\mu\text{A}$ |

|                       |                                                       | $V_{AO} = 1.2\text{V}$ , $T_A = 25^\circ\text{C}$    | 13.5 | 17   | 20.5 |               |

|                       |                                                       | $V_{AO} \geq 1.5\text{V}$                            | 14   | 17   | 22   |               |

|                       |                                                       | $V_{AO} = 1.2\text{V}$                               | 12   | 17   | 22.5 |               |

| $I_{IMO}$             | 出力電流: ゼロ                                              | $V_{INAC} = 0.9V_{PK}$ , $V_{AO} = 0.8\text{V}$      | -0.2 | 0    | 0.2  | $\mu\text{A}$ |

|                       |                                                       | $V_{INAC} = 0\text{V}$ , $V_{AO} = 5\text{V}$        | -0.2 | 0    | 0.2  |               |

| <b>量子化電圧フィードフォワード</b> |                                                       |                                                      |      |      |      |               |

| $V_{LVL1}$            | レベル 1 スレッショルド <sup>(3)</sup>                          | $V_{INAC}$ (立ち上がり時) で測定                              | 0.6  | 0.7  | 0.8  | V             |

| $V_{LVL2}$            | レベル 2 スレッショルド                                         | $V_{INAC}$ (立ち上がり時) で測定                              |      | 1.0  |      | V             |

| $V_{LVL3}$            | レベル 3 スレッショルド                                         | $V_{INAC}$ (立ち上がり時) で測定                              |      | 1.2  |      | V             |

| $V_{LVL4}$            | レベル 4 スレッショルド                                         | $V_{INAC}$ (立ち上がり時) で測定                              |      | 1.4  |      | V             |

| $V_{LVL5}$            | レベル 5 スレッショルド                                         | $V_{INAC}$ (立ち上がり時) で測定                              |      | 1.65 |      | V             |

| $V_{LVL6}$            | レベル 6 スレッショルド                                         | $V_{INAC}$ (立ち上がり時) で測定                              |      | 1.95 |      | V             |

| $V_{LVL7}$            | レベル 7 スレッショルド                                         | $V_{INAC}$ (立ち上がり時) で測定                              |      | 2.25 |      | V             |

| $V_{LVL8}$            | レベル 8 スレッショルド                                         | $V_{INAC}$ (立ち上がり時) で測定                              |      | 2.6  |      | V             |

| <b>電流アンプ</b>          |                                                       |                                                      |      |      |      |               |

|                       | CAOx 高電圧                                              |                                                      | 5.75 | 6    |      | V             |

|                       | CAOx 低電圧                                              |                                                      |      |      | 0.1  | V             |

| $g_{MC}$              | CAOx 相互コンダクタンス                                        |                                                      |      | 100  |      | $\mu\text{S}$ |

|                       | CAOx シンク電流、オーバードライブ                                   |                                                      |      | 50   |      | $\mu\text{A}$ |

|                       | CAOx ソース電流、オーバードライブ                                   |                                                      |      | -50  |      | $\mu\text{A}$ |

|                       | 入力同相範囲                                                |                                                      | 0    | 3.6  |      | V             |

| 入力オフセット電圧             | $V_{RSYNTH} = 6\text{V}$ , $T_A = 25^\circ\text{C}$   |                                                      | -16  | -8   | 0    | $\text{mV}$   |

|                       |                                                       |                                                      | -50  | -8   | 40   |               |

| 入力オフセット電圧             |                                                       |                                                      | -50  | -8   | 40   | $\text{mV}$   |

| 位相ミスマッチ               | 位相 A の入力オフセットから位相 B<br>入力オフセットを<br>引いた値として測定します       | $T_A = 25^\circ\text{C}$                             | -12  | 0    | 12   | $\text{mV}$   |

|                       |                                                       | $T_A = -40^\circ\text{C} \sim 125^\circ\text{C}$     | -20  |      | 14   |               |

| CAOx プルダウン電流          | $V_{VSENSE} = 0.5\text{V}$ , $V_{CAOx} = 0.2\text{V}$ |                                                      | 0.5  | 0.9  |      | $\text{mA}$   |

| <b>電流シンセサイザ</b>       |                                                       |                                                      |      |      |      |               |

| $V_{RSYNTH}$          | レギュレーション電圧                                            | $V_{VSENSE} = 3\text{V}$ , $V_{INAC} = 0\text{V}$    | 2.91 | 3    | 3.09 | V             |

|                       |                                                       | $V_{VSENSE} = 3\text{V}$ , $V_{INAC} = 2.85\text{V}$ | 0.1  | 0.15 | 0.2  |               |

|                       | シンセサイザのディスエーブルのスレッショルド                                | $R_{SYNTH}$ (立ち上がり時) で測定                             |      | 5    | 5.25 | V             |

| VINAC 入力バイアス電流        |                                                       |                                                      |      | 0.25 | 0.5  | $\mu\text{A}$ |

## 5.5 電気的特性 (続き)

$T_J = T_A = -40^{\circ}\text{C} \sim 125^{\circ}\text{C}$ ,  $V_{CC} = 12\text{V}$ ,  $\text{GND} = 0\text{V}$ ,  $R_{RT} = 75\text{k}\Omega$ ,  $R_{DMX} = 68.1\text{k}\Omega$ ,  $R_{RDM} = R_{SYN} = 100\text{k}\Omega$ ,  $C_{CDR} = 2.2\text{nF}$ ,  $C_{SS} = C_{VREF} = 0.1\mu\text{F}$ ,  $C_{VCC} = 1\mu\text{F}$ ,  $I_{VREF} = 0\text{mA}$  (特に記載のない限り)

| パラメータ                  | テスト条件                                                    | 最小値                                                      | 標準値  | 最大値  | 単位    |

|------------------------|----------------------------------------------------------|----------------------------------------------------------|------|------|-------|

| <b>ピーク電流制限</b>         |                                                          |                                                          |      |      |       |

| ピーク電流制限スレッショルド         | $V_{PKLMT} = 3.3\text{V}$ , $CS_x$ (立ち上がり時) で測定          | 3.27                                                     | 3.3  | 3.33 | V     |

| ピーク電流制限の伝搬遅延           | $CS_x$ (立ち上がり) と $GD_x$ (立ち下がり) エッジ間で測定                  |                                                          | 60   | 100  | ns    |

| <b>PWM ランプ</b>         |                                                          |                                                          |      |      |       |

| $V_{RMP}$              | PWM ランプ振幅                                                | 3.8                                                      | 4    | 4.2  | V     |

|                        | $PWM$ ランプ オフセット電圧                                        | $T_A = 25^{\circ}\text{C}$ , $R_{RT} = 75\text{k}\Omega$ | 0.55 | 0.7  | V     |

|                        | PWM ランプ オフセット温度係数                                        |                                                          | -2   |      | mV/°C |

| <b>ゲートトライプ</b>         |                                                          |                                                          |      |      |       |

| GDA、GDB 出力電圧、High、クランプ | $V_{CC} = 20\text{V}$ , $C_{LOAD} = 1\text{nF}$          | 11.5                                                     | 13   | 15   | V     |

| GDA、GDB 出力電圧、High      | $C_{LOAD} = 1\text{nF}$                                  | 10                                                       | 10.5 |      | V     |

| GDA、GDB 出力電圧、Low       | $C_{LOAD} = 1\text{nF}$                                  |                                                          | 0.2  | 0.3  | V     |

| 立ち上がり時間 $GD_x$         | $1\text{V} \sim 9\text{V}$ , $C_{LOAD} = 1\text{nF}$     |                                                          | 18   | 30   | ns    |

| 立ち下がり時間 $GD_x$         | $9\text{V} \sim 1\text{V}$ , $C_{LOAD} = 1\text{nF}$     |                                                          | 12   | 25   | ns    |

| GDA、GDB 出力電圧、UVLO      | $V_{CC} = 0\text{V}$ , $I_{GDA}, I_{GDB} = 2.5\text{mA}$ |                                                          | 0.7  | 2    | V     |

| <b>サーマル シャットダウン</b>    |                                                          |                                                          |      |      |       |

| サーマル シャットダウンのスレッショルド   |                                                          |                                                          | 160  |      | °C    |

| サーマル シャットダウンからの復帰      |                                                          |                                                          | 140  |      | °C    |

- (1) VCC 入力電圧または電流が過大になると、デバイスが損傷する可能性があります。VCC クランプは、非安定化バイアス電源からデバイスを保護するものではありません。非安定化電源を使用する場合、TI は UA78L15A のような直列接続型固定正電圧レギュレータの使用を推奨しています。VCC の電圧と電流の制限値については、[セクション 5.1](#) を参照してください。

- (2) 同期パルス幅が、最大 PWM スイッチング デューティ サイクル ( $D_{MAX}$ ) のプログラム可能性に及ぼす影響から、TI は同期信号のデューティ サイクルを最小化することを推奨します。

- (3) レベル 1 スレッショルドは、VINAC が新しい入力半周期を開始するために上昇すべきゼロクロッシング検出スレッショルドであり、またその半周期を終了するために VINAC が下降すべきスレッショルドでもあります。

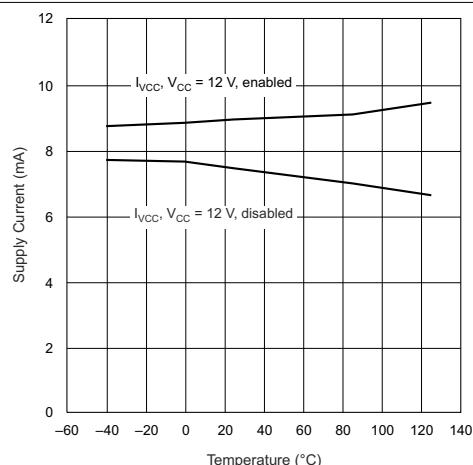

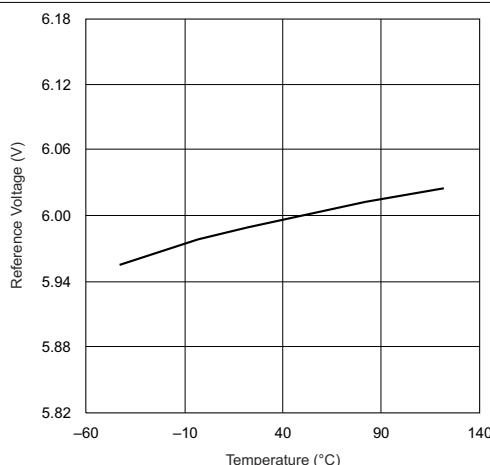

## 5.6 代表的特性

図 5-1. V<sub>CC</sub> 供給電流と接合部温度との関係

図 5-2. V<sub>VREF</sub> と接合部温度との関係

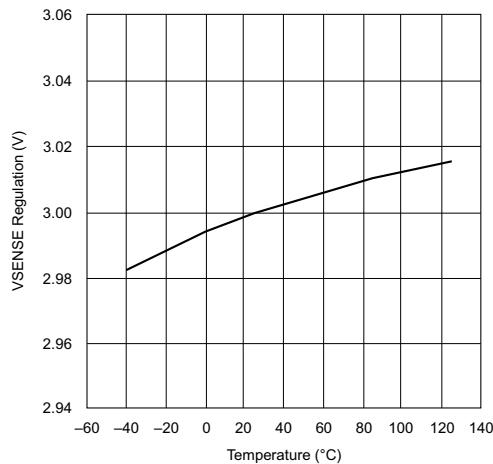

図 5-3. V<sub>VSENSE</sub> レギュレーション電圧と接合部温度との関係

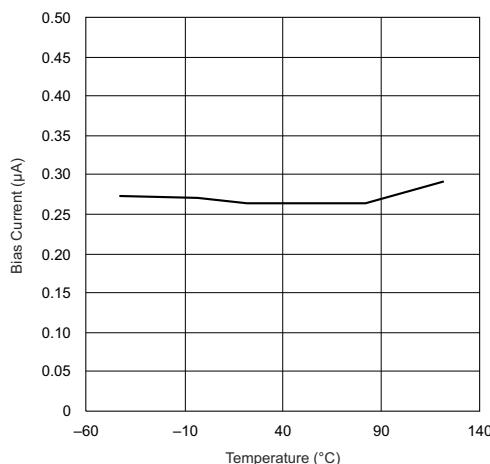

図 5-4. I<sub>VSENSE</sub> バイアス電流と接合部温度の関係

図 5-5. IMO、乗算器出力電流と V<sub>VAO</sub> との関係

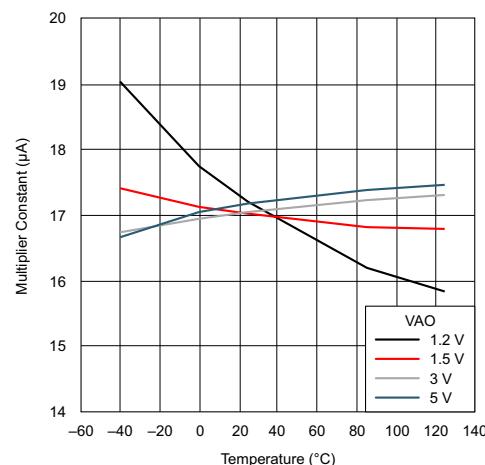

図 5-6. 乗算器定数と接合部温度との関係

## 5.6 代表的特性 (続き)

図 5-7.  $I_{\text{VINAC}}$  バイアス電流と接合部温度との関係

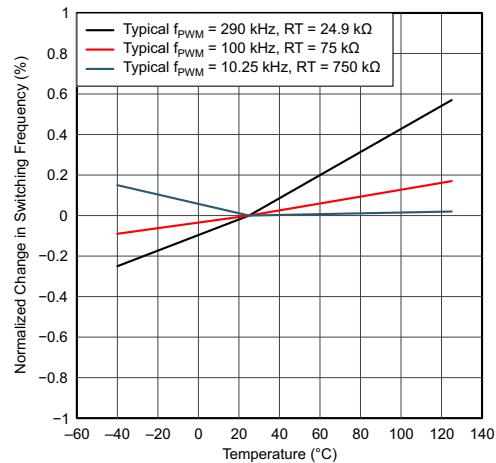

図 5-8. スイッチング周波数と温度との関係

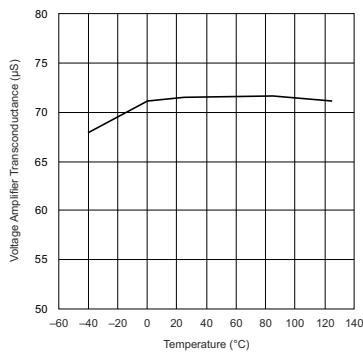

図 5-9. VAO、電圧アンプの相互コンダクタンス対と接合部温度との関係

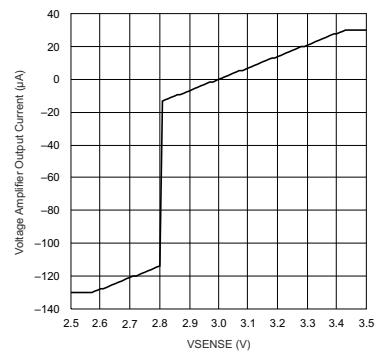

図 5-10. 電圧アンプの伝達関数と  $V_{\text{SENSE}}$  との関係

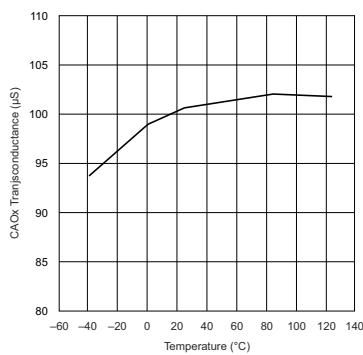

図 5-11. 電流アンプの相互コンダクタンスと接合部温度との関係

## 5.6 代表的特性 (続き)

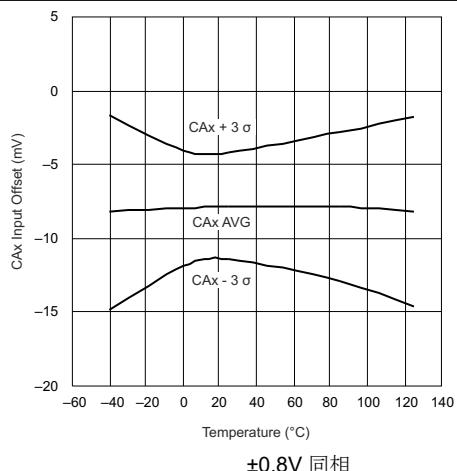

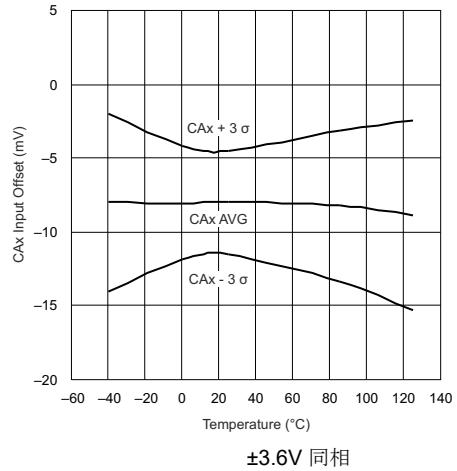

図 5-12. CAx 入力オフセット電圧と接合部温度との関係

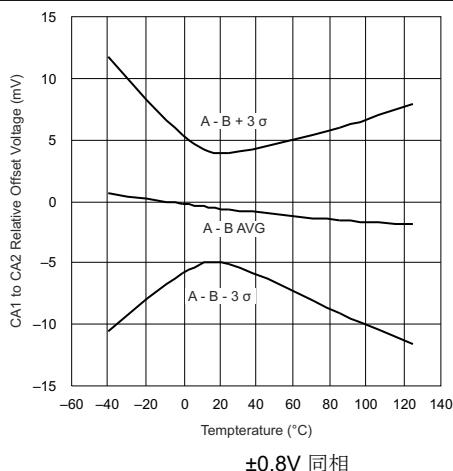

図 5-13. CA1~CA2 の相対オフセットと接合部温度との関係

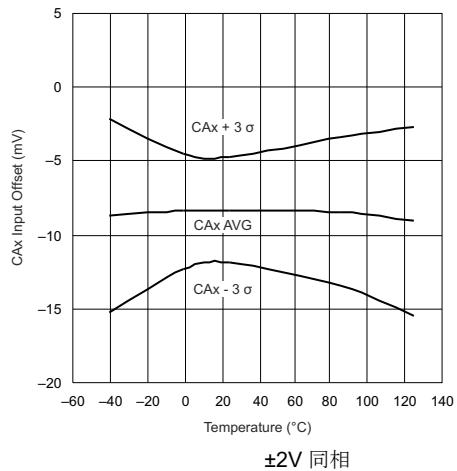

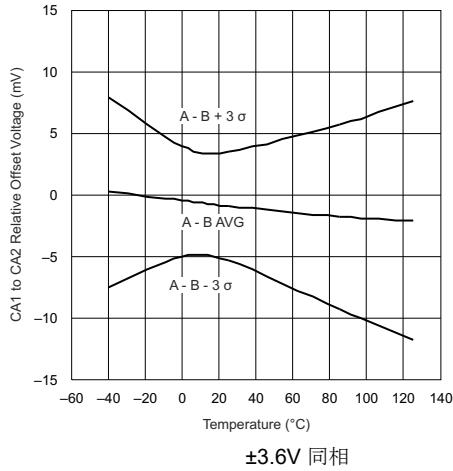

図 5-14. CAx 入力オフセット電圧と接合部温度との関係

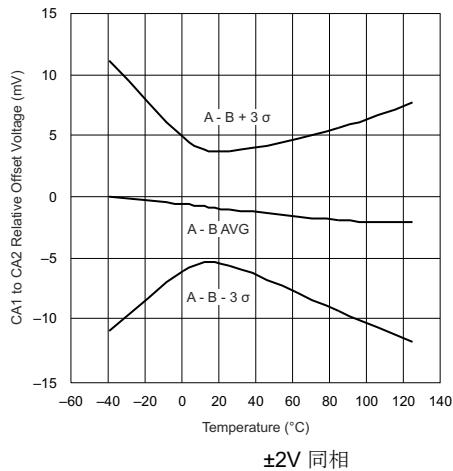

図 5-15. CA1~CA2 の相対オフセットと接合部温度との関係

図 5-16. CAx 入力オフセット電圧と接合部温度との関係

図 5-17. CA1~CA2 の相対オフセットと接合部温度との関係

## 6 詳細説明

### 6.1 概要

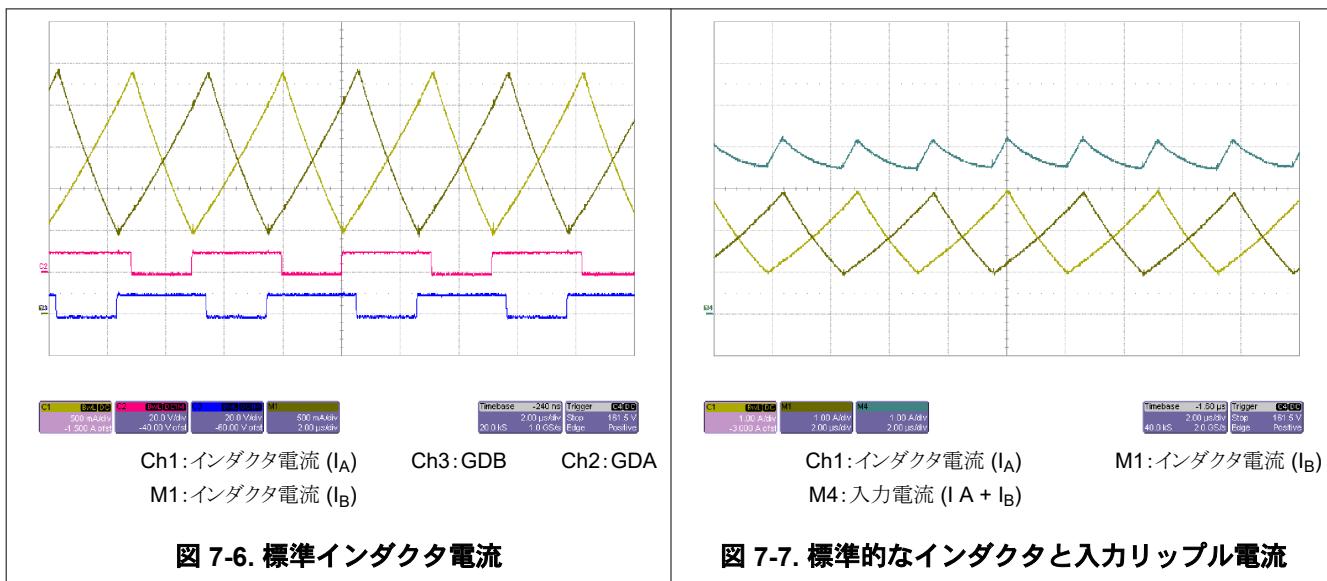

UCC28070-Q1 は、2 つの CCM (連続導通モード) 昇圧 PFC 電力段を制御する力率改善デバイスで、これらは互いに  $180^\circ$  位相をずらして動作します。このインターリープ動作により、入力および出力のリップル電流が低減され、EMI フィルタリングの必要性が少なくなるとともに、非インターリープ方式よりも高出力での動作が可能になります。

UCC28070-Q1 は、30kHz から 300kHz までの広いスイッチング周波数範囲で動作可能であり、MOSFET および IGBT 電力スイッチの両方での使用に適しています。

このデバイスは、平均電流モード PWM 制御を使用することで低い THDi を実現する、高性能かつ高出力の PFC アプリケーションに特に適しています。より高出力のアプリケーションで、2 つ以上のインターリープされた電力段が必要な場合、複数のコントローラを同期させて使用できます。

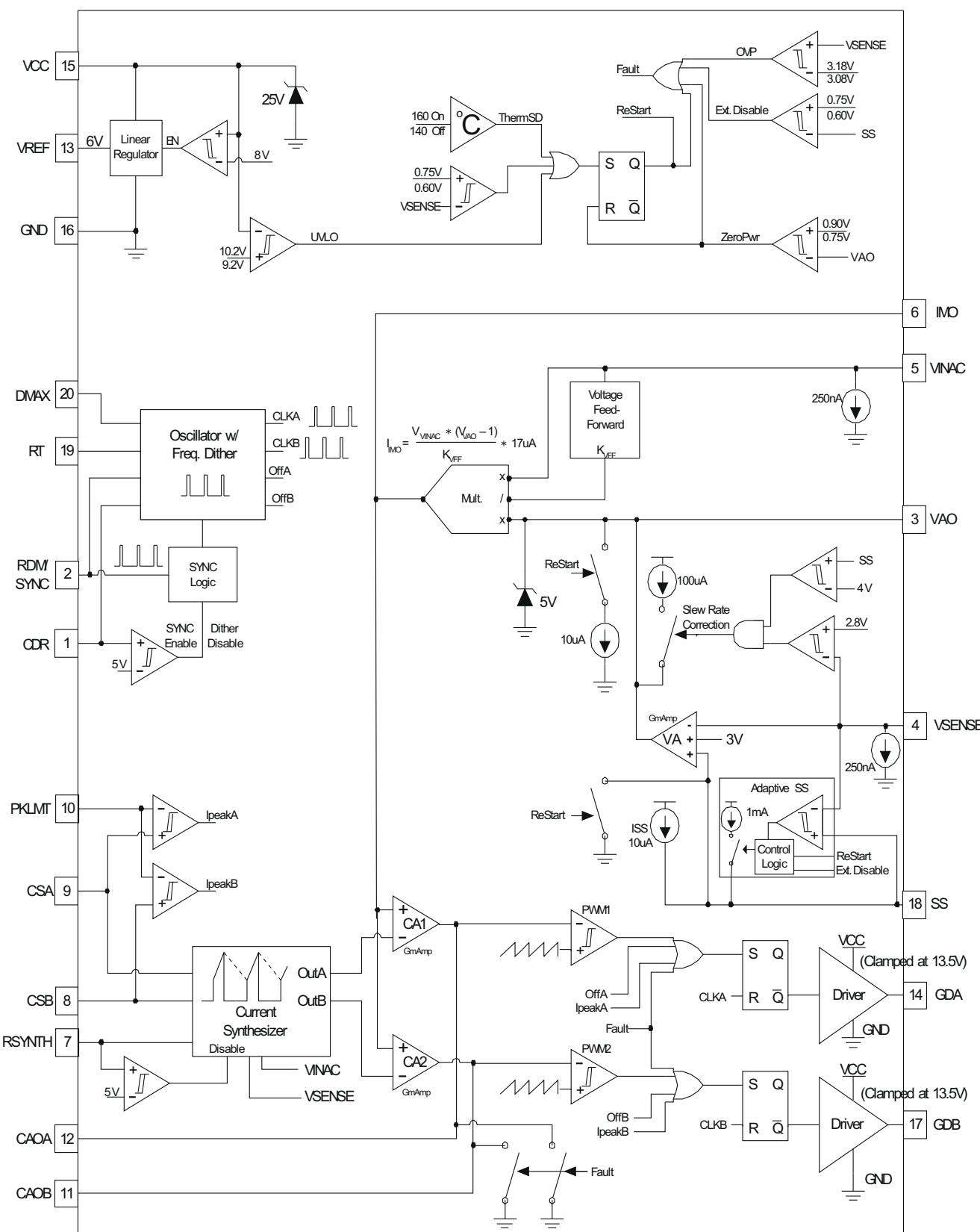

## 6.2 機能ブロック図

Copyright © 2016, Texas Instruments Incorporated

## 6.3 機能説明

### 6.3.1 インターリープ

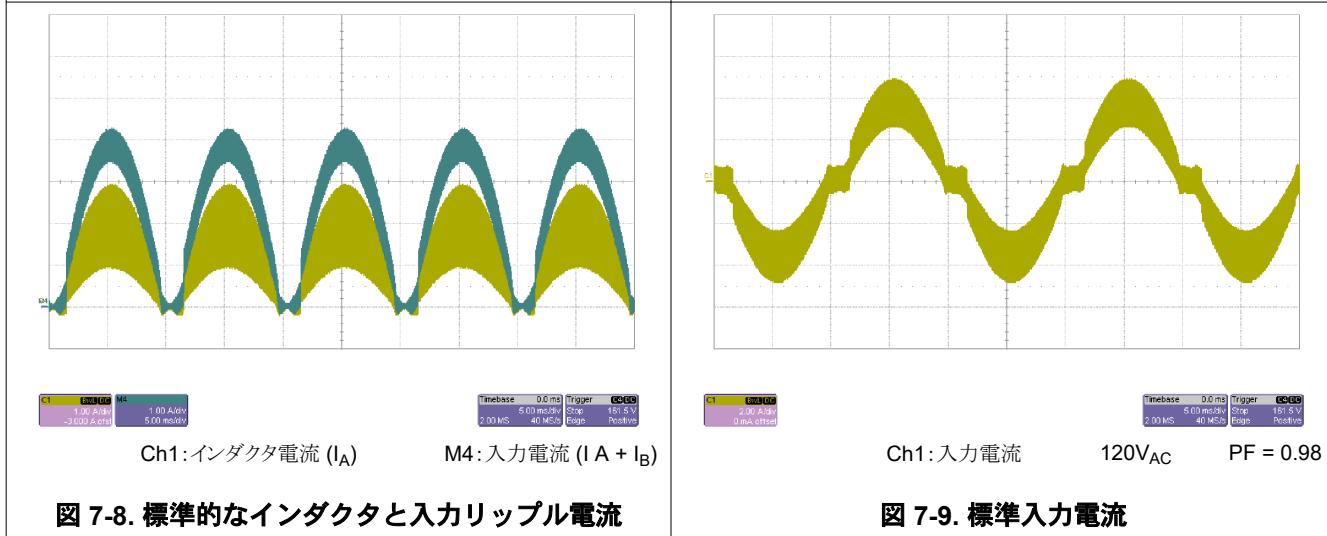

位相の  $180^\circ$  インターリープの主な利点の一つは、入力電流と PFC プリレギュレータの出力コンデンサに流れる電流の両方における高周波リップル成分を大幅に低減できることです。同等出力の単相 PFC 段と比較すると、入力電流のリップルが低減されることで、伝導性 EMI ノイズのフィルタリング負荷が軽減され、EMI フィルタや  $C_{IN}$  のサイズを小さくするのに役立ちます。さらに、PFC 出力コンデンサ  $C_{OUT}$  に流れ込む高周波リップル電流が低減した結果、サイズとコストを削減することができます。さらに、各相のリップルと平均電流が低減されることで、昇圧インダクタのサイズは単相設計よりも小さくすることができます [3]。

インターリープによるリップル電流の低減は、しばしばリップル相殺と呼ばれます。厳密に言えば、2 相システムではピークツーピーク リップルが完全に打ち消されるのはデューティー比 50% のときだけです。デューティサイクルが 50% 以外の場合、リップル低減は各相電流の重ね合わせによる部分的な打ち消しの形で生じます。それでも、同等出力の単相 PFC プリレギュレータのリップル電流と比べると、2 相インターリープ設計のリップル電流は格段に小さくなります [3]。リップルの相殺にかかわらず、入力と出力の両方でのインターリープ リップル電流の周波数は  $2 \times f_{PWM}$  です。

PFC 入力では、 $180^\circ$  インターリープにより、ピークツーピーク電流リップルの振幅が、同等出力の単相電流リップル振幅の  $1/2$  以下に低減されます。

PFC 出力では、PWM デューティサイクルが 50% を超える場合、 $180^\circ$  インターリープにより出力コンデンサに生じる PFC リップル電流の rms 値が  $\sqrt{2}$  よりわずかに大きい係数で低減されます。

これは、Erickson [4] による手法を応用した次の微分で見ることができます。

単相 PFC プリレギュレータでは、全てのデューティサイクルにおける PFC 段によって出力コンデンサに流れる総 rms 電流は、次の式で近似できることが示されます：

$$i_{CRMS1\phi} = \left( \frac{I_o}{\eta} \right) \sqrt{\left( \left( \frac{16 \times V_o}{3\pi \times V_M} \right) - \eta^2 \right)} \quad (1)$$

ここで、

- $I_o$  は PFC 出力負荷の平均電流です

- $V_o$  は平均 PFC 出力電圧です

- $V_M$  は、入力 AC ライン電圧のピークです

- $\eta$  はこれらの条件での PFC 段の効率です

2 相インターリープ PFC プリレギュレータでは、 $D > 50\%$  の場合に PFC 段が出力コンデンサに流す総 rms 電流は、次の式で近似できることが示されます：

$$i_{CRMS2\phi} = \left( \frac{I_o}{\eta} \right) \sqrt{\left( \left( \frac{16 \times V_o}{6\pi \times V_M} \right) - \eta^2 \right)} \quad (2)$$

$i_{CRMS2\phi}$  の平方根の中の量は、 $i_{CRMS1\phi}$  の平方根の中の量の  $1/2$  よりわずかに小さいことがわかります。ここで示した rms 電流には、PFC 出力電流の低周波成分と高周波成分の両方が含まれています。インターリープを行うと、高周波成分が低減されますが、低周波成分は低減されません。

### 6.3.2 PWM 周波数と最大デューティ サイクル クランプの設定

UCC28070-Q1 の GDA および GDB 出力の PWM 周波数と最大デューティ サイクルは、それぞれ RT ピンおよび DMAX ピンに接続された抵抗の選択によって設定されます。RT 抵抗 ( $R_{RT}$ ) の選択により、PWM 周波数 ( $f_{PWM}$ ) が直接設定されます。

$$R_{RT}(k\Omega) = \frac{7500}{f_{PWM}(kHz)}, \text{ therefore } f_{PWM}(kHz) = \frac{7500}{R_{RT}(k\Omega)} \quad (3)$$

$R_{RT}$  を決定してから、 $D_{MAX}$  抵抗 ( $R_{DMX}$ ) を求めることができます。

$$R_{DMX}(k\Omega) = R_{RT}(k\Omega) \times (2 \times D_{MAX} - 1), \text{ therefore } D_{MAX} = \frac{1}{2} \left( \frac{R_{DMX}(k\Omega)}{R_{RT}(k\Omega)} + 1 \right) \quad (4)$$

ここで、

- $D_{MAX}$  は設定したい最大 PWM デューティ サイクルであり、( $D_{MAX}$  は 0.50 より大きい必要があります)

### 6.3.3 周波数ディザリング(振幅およびレート)

周波数ディザリングとは、スイッチング周波数を変調させることで、ライン フィルタ単独では達成できない伝導性 EMI ノイズの低減を実現することを指します。UCC28070-Q1 は三角波変調方式を採用しており、スイッチング周波数範囲のすべての点で同じ時間を費やすことになります。最小周波数から最大周波数までの合計範囲は、ディザリング振幅として定義され、 $R_{RT}$  で設定された公称スイッチング周波数  $f_{PWM}$ を中心にしています。例えば、公称  $f_{PWM}$  が 100kHz の場合に 20kHz のジッタ振幅を設定すると、周波数範囲は 100kHz ± 10kHz となります。さらに、 $R_{DMX}$  で設定されるプログラムされたデューティ サイクル クランプは、周波数ディザリングの範囲全体にわたって、プログラムされた値で一定に保たれます。

$f_{PWM}$  が一方の極端からもう一方の極端へ、そして再び戻る速度をジッタレートと定義します。例えば、ジッタ レートが 1kHz の場合、公称周波数は 1ms ごとに 110kHz から 90kHz へ、そして再び 110kHz へと線形に変調されます。ディザリングの振幅についての適切な初期設計目標は、 $f_{PWM}$  の ±10% です。ほとんどの昇圧部品は、 $f_{PWM}$  での拡散に耐えられます。設計者はその後、この範囲内で反復的に調整を行い、EMI の低減、部品の許容差、ループの安定性との最適な妥協点を見つけることができます。

目的のディザリング振幅は、RDM ピンと GND の間の抵抗によって設定され、式 5 で計算されます：

$$R_{RDM}(k\Omega) = \frac{937.5}{f_{DR}(kHz)} \quad (5)$$

$R_{RDM}$  の値が決定したら、希望するジッタ レートは、CDR ピンと GND の間に接続するコンデンサによって設定できます。そのコンデンサの値は 式 6 で計算されます：

$$C_{CDR}(pF) = 66.7 \times \left( \frac{R_{RDM}(k\Omega)}{f_{DR}(kHz)} \right) \quad (6)$$

CDR ピンを 5V 超にするか、VREF (6V) に接続し、RDM ピンを直接 GND に接続することで、周波数ディザリングを完全に無効化できます。(実装されている場合、RDM 抵抗の比較的高いインピーダンスにより、ジッタリングを無効にした際に低インピーダンス経路でバイパスされていないと、システムのスイッチング ノイズが結合してコントローラのタイミング機能に干渉する可能性があります。)

$f_{PWM}$  と周波数ディザリングを同期するために外部周波数ソースを使用する場合、同期中に望ましくない性能を防ぐため、内部ディザリング回路がディスエーブルされているため、外部周波数ソースによってディザリング振幅とレート機能を提供する必要があります。(詳細については、[外部クロック同期](#)を参照してください。)

### 6.3.4 外部クロック同期

UCC28070-Q1 は、ほとんどすべての外部周波数源に容易に同期できるように設計されています。周波数ジッタリングを無効にすることで (CDR > 5 V に引き上げる)、SYNC 回路が有効になり、内部発振器を RDM ピンに入力されたパルスに同期させることができます。GDA 出力と GDB 出力の間で正確に 180° の位相差を維持するためには、RDM ピンに入力されるパルスの周波数 ( $f_{SYNC}$ ) を、目的とする  $f_{PWM}$  の 2 倍にする必要があります。たとえば、100kHz の PWM スイッチング周波数が必要な場合、 $f_{SYNC}$  を 200kHz にする必要があります。

$$f_{PWM} = \frac{f_{SYNC}}{2}, \text{ therefore } f_{SYNC} = 2 \times f_{PWM} \quad (7)$$

内部発振器が SYNC 機能に干渉しないように、内部発振器の周波数が予測される最小  $f_{SYNC}$  より約 10% 低い値に設定されるように、 $R_{RT}$  のサイズを設定する必要があります。

$$R_{RT} (\text{k}\Omega) = \frac{15000}{f_{SYNC} (\text{kHz})} \times 1.1 \quad (8)$$

PWM ランプ電流と  $R_{RT}$  との間に直接の相関があるため、PWM モジュレータのゲインは、スケーリングされた  $R_{RT}$  に相当する係数だけ低下することに注意する必要があります。電流ループ補償に示されている  $k_{SYNC}$  係数を使用して、それに応じて電流ループゲインを調整する必要があります。

また、外部同期中は最大デューティクラップのプログラム可能性にも影響があることに注意する必要があります。最大デューティサイクルを設定する内部タイミング回路は、同期パルスの立ち下がりエッジで開始されます。したがって、 $R_{DMX}$  の選択は、同期パルス幅 ( $t_{SYNC}$ ) に依存します。このコンテキストでは、 $t_{SYNC}$  はパルス幅であり、 $t_{SYNC}$  は  $f_{SYNC}$  の逆数ではありません。

$$D_{SYNC} = t_{SYNC} \times f_{SYNC} \text{ (For use in } R_{DMX} \text{ equation immediately below.)} \quad (9)$$

$$R_{DMX} (\text{k}\Omega) = \left( \frac{15000}{f_{SYNC} (\text{kHz})} \right) \times (2 \times D_{MAX} - 1 - D_{SYNC}) \quad (10)$$

そのため、 $t_{SYNC}$  の影響を最小限に抑えるため、実現可能な最小の同期パルス幅を使用することは明らかです（許容される最小パルス幅については、電気的特性表を参照してください）。

#### 注

外部同期を使用する場合、内部タイミング回路と SYNC 信号の立つ下がりエッジの間には約 50ns～100ns の伝搬遅延が存在し、これにより最も高いスイッチング周波数で OFF 時間が短くなる可能性があります。したがって、高周波数の SYNC では  $R_{DMX}$  値を  $(t_{SYNC}-0.1\mu\text{s}) / t_{SYNC}$  だけ下方にわずかに調整して補償する必要があります。より低い SYNC 周波数では、この遅延は PWM 周期に対して無視できるほど小さくなるため、考慮する必要はありません。

#### 注

UCC28070-Q1 の内部発振器は、外部 SYNC 周波数の大きな変動に対応するようには設計されていません。SYNC 周波数の変動が、式 8 で使用した公称  $f_{SYNC}$  の ±10% を超えないようにしてください。 $f_{SYNC}$  の過剰な変動は、コントローラの誤動作を発生させる可能性があります。 $R_{RT}$  値は、最小の  $f_{SYNC}$  で計算する必要があります。

### 6.3.5 マルチフェーズ動作

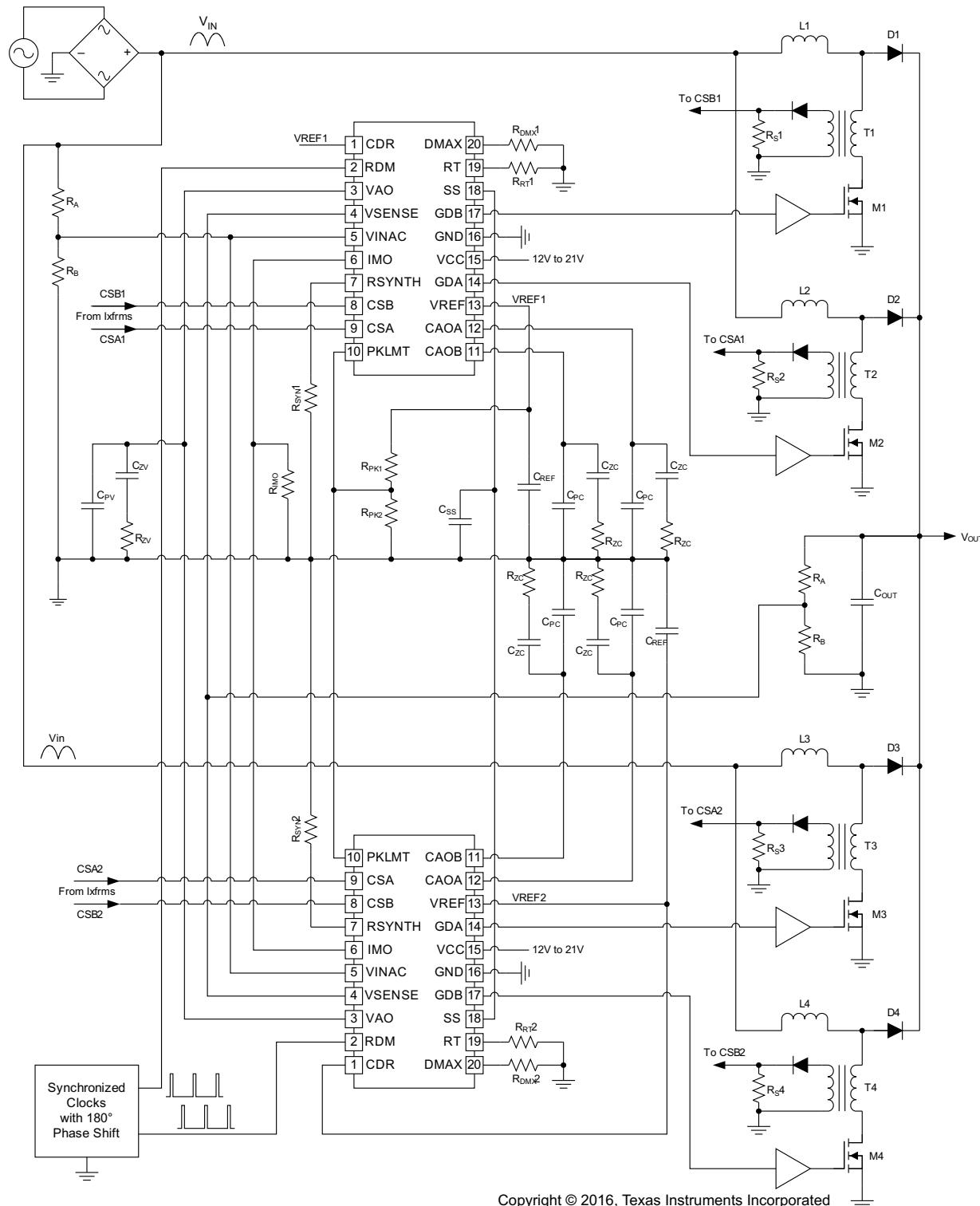

外部同期を使用すると、2相以上のインターリープ動作にも対応できます。複数の UCC28070-Q1 デバイスを並列接続することで、より高出力のアプリケーション向けに偶数の追加の位相を簡単に増設できます。同期信号の位相を適切にシフトさせることで、さらに入力電流および出力電流のリップル低減効果を得ることができます。(必要であれば奇数フェーズにも対応できますが、その場合はリップル低減効果は最適にはなりません。)4相、6相、または任意の  $2 \times n$  相 ( $n = UCC28070\text{-Q1}$  コントローラの数) の場合、それぞれのコントローラは互いに  $360/n$  度ずれた SYNC 信号を受け取る必要があります。

4相のアプリケーションで2台のコントローラを用いたインターリープの場合、最適なリップル低減を得るために SYNC1 は SYNC2 に対して  $180^\circ$  位相がずれている必要があります。同様に、6相のシステムでは、最適なリップル低減を得るために SYNC1、SYNC2、SYNC3 はそれぞれ  $120^\circ$  位相がずれている必要があります。

マルチフェーズのインターリープ システムでは、各電流ループは独立して個別に扱われます。ただし、電圧ループは1つの共通ループしかありません。単一の電圧制御ループを維持するために、すべての VSENSE、VINAC、SS、IMO、および VAO 信号は、それぞれ  $n$  台のコントローラ間で並列接続されます。電流源出力 (SS, IMO, VAO) が結合される場合、單一コントローラと同じ性能を維持するために、計算上の負荷インピーダンスは  $1/n$  倍に調整する必要があります。

図 6-1 に、4相、90度インターリープ PFC システム用の2つのコントローラを並列接続する方法を示します。

### 6.3.6 VSENSE と VINAC 抵抗の構成

VSENSE 入力の主な目的は、出力からの電圧フィードバックを電圧制御ループに供給することです。したがって、従来型の抵抗分圧ネットワークを出力コンデンサと VSENSE ピンの間に設け、VSENSE の 3V 制御電圧に基づいて所望の出力電圧を設定する必要があります。

UCC28070-Q1 には独自の特徴があり、インダクタの  $V_{IN}$  側に VINAC ピンに同じ分圧抵抗回路を配置する必要があります。これにより、リニア乗算器および電流合成回路に必要なスケーリングされた入力電圧の監視が提供されます。VINAC ネットワークの実際の抵抗が VSENSE ネットワークと同じであることは必要ありませんが、PFC を適切に動作させるためには、2つの分圧回路の減衰 ( $k_R$ ) が等価であることが必要です。

$$k_R = \frac{R_B}{(R_A + R_B)} \quad (11)$$

ノイズの多い環境では、VSENSE および VINAC 入力に小容量のフィルタ コンデンサを追加すると、これらの入力に過剰なノイズが作用して不安定化するのを防ぐのに有効です。もし追加する場合、出力の過渡応答に大きな遅延が生じないように、VSENSE 入力の RC 時定数は  $100\mu\text{s}$  を超えないようにする必要があります。波形のゼロクロスが劣化しないように、VINAC 入力の RC 時定数も  $100\mu\text{s}$  を超えないようにする必要があります。通常、VSENSE と VINAC の標準的なノイズをフィルタして除去するには、 $3/f_{PWM}$  の時定数で十分です。特定のアプリケーションで必要な最適なフィルタ量を見つけるためには、設計や試験の反復が必要になる場合があります。

### 6.3.7 VSENSE および VINAC 開路保護

VSENSE ピンおよび VINAC ピンには内部 250nA の電流シンクが設計されており、どちらかのピンがオープン回路になった場合でも電圧が不定にならず、UCC28070-Q1 が安全な動作モードを維持できるようになっています。

図 6-1. 2つの UCC28070-Q1 デバイスを使用した 4 相アプリケーションの概略図

### 6.3.8 電流シンセサイザ

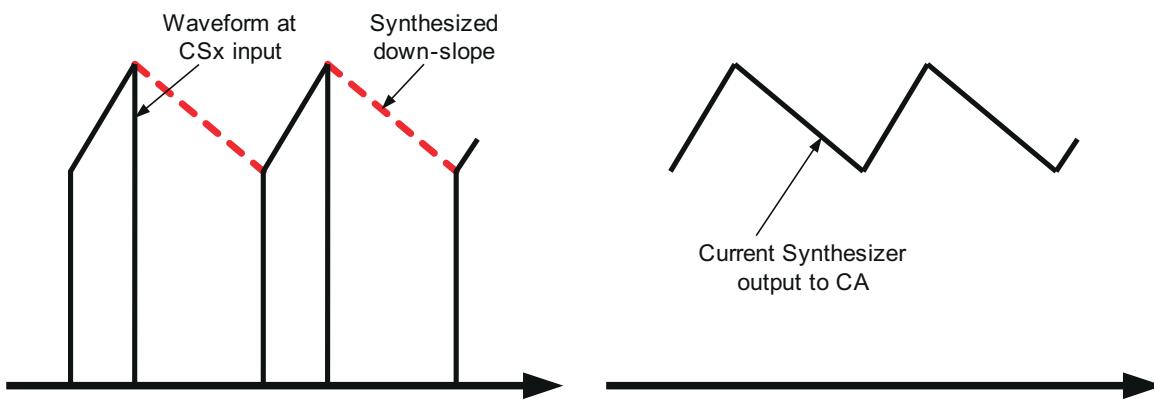

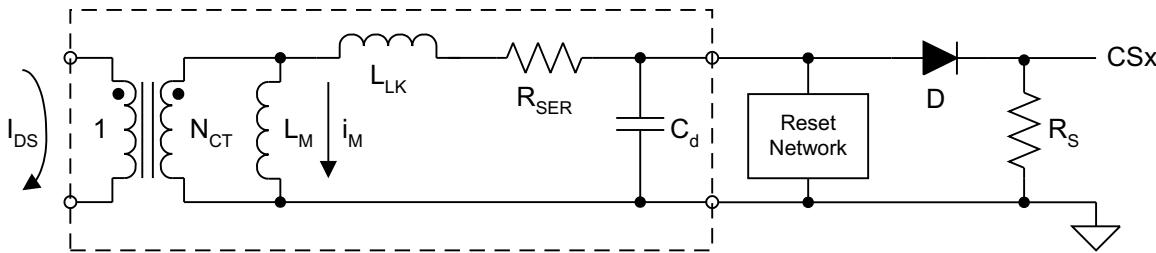

UCC28070-Q1 の設計における最も注目すべき革新のひとつは、電流合成回路です。この回路は、ON 時間のサンプリングと OFF 時間の下降傾斜の模擬を組み合わせることで、インダクタ電流を同期的に監視します。

GDA 出力および GDB 出力のオン時間中は、インダクタ電流がそれぞれ CSA ピンおよび CSB ピンに記録され、各出力相の電流変圧器ネットワークを介して記録されます。一方、VINAC および VSENSE ピンを通じて入力電圧と出力電圧を継続的に監視することで、UCC28070-Q1 は各出力の OFF 時間中のインダクタ電流の下降傾斜を内部的に再現することができます。RSYNTH 抵抗 ( $R_{SYN}$ ) の選択により、式 12に基づいて内部応答を調整し、さまざまなアプリケーションで予測される広範なインダクタンスに対応できます。

電源投入時や AC 停電復帰時の突入電流サーチでは、 $V_{VSENSE} < V_{VINAC}$  となり、合成された下降傾斜はゼロになります。この場合、合成されたインダクタ電流は IMO リファレンスを上回ったままとなり、電流ループはデューティサイクルをゼロに駆動します。これにより、サーチ時に MOSFET に過度の負荷がかかるのを防ぐことができます。 $V_{VINAC}$  が  $V_{VSENSE}$  を下回ると、定常状態動作が再開するまでデューティサイクルは増加します。

図 6-2. インダクタ電流の下降傾斜

$$R_{SYN} (\text{k}\Omega) = \frac{(10 \times N_{CT} \times L_B (\mu\text{H}) \times k_R)}{R_s (\Omega)} \quad (12)$$

ここで

- $L_B$  = 公称ゼロバイアス昇圧インダクタンス ( $\mu\text{H}$ )

- $R_s$  = センス抵抗 ( $\Omega$ )

- $N_{CT}$  = 電流センストラnsの巻線比

- $K_R = R_B / (R_A + R_B) = VSENSE$  および  $VINAC$  ピンでの分圧抵抗減衰

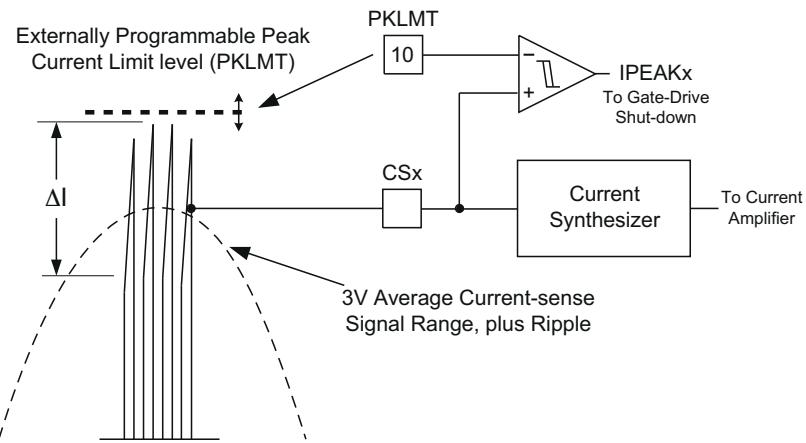

### 6.3.9 プログラム可能なピーク電流制限

UCC28070-Q1 は、対応する電流検出入力 (CSA または CSB) が PKLMT ピンで設定された電圧を超えた場合に、GDA または GDB 出力のいずれかを無効にするサイクルごとのピーク電流制限をプログラム可能に設計されています。一度ピーク電流制限の検出により出力が無効化されると、その出力は次のクロック サイクルで新しい PWM 期間が開始されるまで無効のまま保持されます。PKLMT 電圧の設定範囲は、3V の平均電流センス信号範囲をフルに利用できるように 4V まで拡張されています。ただし、注意点として、電流アンプの線形性は 3.6V を超えると圧縮が始まります。

VREF から GND への抵抗分圧ネットワークによって、PKLMT 上のピーク電流制限電圧を設定できます。ただし、VREF からの総電流が 2mA 未満である必要があります。これを超えると 6V の VREF 電圧が低下する可能性があります。TI は 0.5mA 未満の負荷を推奨しています。しかし、PKLMT 上の抵抗が非常に高い場合には、TI は高ノイズ環境での動作上の問題を避けるために、PKLMT に小さなフィルタコンデンサを使用することを推奨しています。

図 6-3. 外部プログラム可能なピーク電流制限

ピーク電流制限は保護機能であり、デューティサイクルが 0.5 を超える場合のスロープ補償は内蔵されていません。ピーク制限が発生すると、サブハーモニック発振が起こることがあり、その発振によって可聴ノイズが発生する可能性があります。もし PKLMT 機能を定常状態での出力電力制限に流用する場合は、適切なスロープ補償を外部で追加する必要があります。

### 6.3.10 リニアマルチプライヤおよび量子化電圧フィードフォワード

UCC28070-Q1 の乗算器は、所望の波形と AC 入力電流の比例した振幅を表す基準電流を生成します。この電流は  $R_{IMO}$  抵抗によって基準電圧信号に変換され、その値は電流検出信号の低周波平均電圧に一致するようスケーリングされています。瞬時マルチプライヤ電流は、整流されたスケーリングされた入力電圧  $V_{VINAC}$  と、電圧エラー アンプの出力  $V_{VAO}$  によって異なります。 $V_{VINAC}$  は、次の 3 つの情報を乗算器に伝達します：

- 入力電圧の全体的な波形 (通常は正弦波)。

- ラインサイクルの任意の時点における入力電圧の瞬時値。

- 入力電圧の rms レベル (仮定した正弦波のピークから推定)。

最大  $V_{VAO}$  は PFC プリレギュレータの合計出力電力を表します。

UCC28070-Q1 の乗算器アーキテクチャにおける大きな革新は、内部量子化  $V_{RMS}$  フィードフォワード ( $Q_{VFF}$ ) 回路です。この回路により、 $V_{VINAC}$  信号に対する外部フィルタリングの必要性と、それに伴う過渡的なライン変動への応答遅れが解消されます。独自の回路アルゴリズムにより、7 つのスレッショルドを通して  $V_{VINAC}$  のピークの遷移を検出し、8 $Q_{VFF}$  範囲を中心とした等価 VFF レベルを生成します。 $V_{IN}$  が増加すると範囲の境界が拡大し、レベル間の差がほぼ等しいパーセンテージに維持されます。これら 8-Q の  $Q_{VFF}$  レベルは、85V<sub>RMS</sub> から 265V<sub>RMS</sub> までのユニバーサルライン全体に対応できるように配置されています。

$Q_{VFF}$  アーキテクチャの大きな利点は、定数  $k_{VFF}$  ファクタによって乗算器出力への歪みの寄与が排除される点です。これは、必然的に 2 次高調波歪み成分を含む外部フィルタリングされた VINAC 信号のリップルとは異なります。さらに、 $Q_{VFF}$  アルゴリズムを使用すると、入力 rms 電圧の変化の増加と減少の両方に迅速に応答できるため、PFC 出力へ伝わる外乱を最小限に抑えることができます。レベル スレッショルドにおける 5% のヒステリシスは、 $V_{VINAC}$  電圧のピークが特定のしきい値付近にある場合や、軽度のリンギングや歪みを含む場合に、 $Q_{VFF}$  レベル間でのチャタリングを防ぐのに役立ちます。

$Q_{VFF}$  アーキテクチャでは、入力電圧がおおむね正弦波であることが要求され、入力電圧が低下する際にはゼロクロスを検出して  $Q_{VFF}$  を下降方向に調整します。ゼロクロスは、少なくとも  $50\mu s$  の間、 $V_{VINAC}$  が  $0.7V$  を下回ることとして定義されます。レベル変化におけるヒステリシスとして、立ち下がりスレッショルド電圧立ち上がりスレッショルド電圧の 95% に設定されています。

表 6-1 は、さまざまな  $V_{VINAC}$  のピーク電圧と、乗算器方程式に対応する  $k_{VFF}$  項との関係を示しています。

**表 6-1.  $V_{VINAC}$  のピーク電圧と  $Q_{VFF}$  レベル**

| レベル <sup>(1)</sup> | $V_{VINAC}$ ピーク電圧 (立ち上がりピーク)             | $V_{VINAC}$ ピーク電圧 (立ち下がりピーク)         | $k_{VFF} (V^2)$ | $V_{IN}$ ピーク電圧 <sup>(2)</sup> |

|--------------------|------------------------------------------|--------------------------------------|-----------------|-------------------------------|

| 8                  | $2.6V \leq V_{VINAC(pk)} < V_{VINAC(0)}$ | $2.47V < V_{VINAC(pk)} \leq 2.6V$    | 3.857           | $> 345V$                      |

| 7                  | $2.25V \leq V_{VINAC(pk)} < 2.6V$        | $2.138V < V_{VINAC(pk)} \leq 2.47V$  | 2.922           | $300V \sim 345V$              |

| 6                  | $1.95V \leq V_{VINAC(pk)} < 2.25V$       | $1.853V < V_{VINAC(pk)} \leq 2.138V$ | 2.199           | $260V \sim 300V$              |

| 5                  | $1.65V \leq V_{VINAC(pk)} < 1.95V$       | $1.568V < V_{VINAC(pk)} \leq 1.853V$ | 1.604           | $220V \sim 260V$              |

| 4                  | $1.4V \leq V_{VINAC(pk)} < 1.65V$        | $1.33V < V_{VINAC(pk)} \leq 1.568V$  | 1.156           | $187V \sim 220V$              |

| 3                  | $1.2V \leq V_{VINAC(pk)} < 1.4V$         | $1.14V < V_{VINAC(pk)} \leq 1.33V$   | 0.839           | $160V \sim 187V$              |

| 2                  | $1V \leq V_{VINAC(pk)} < 1.2V$           | $0.95V < V_{VINAC(pk)} \leq 1.14V$   | 0.600           | $133V \sim 160V$              |

| 1                  | $V_{VINAC(pk)} < 1V$                     | $V_{VINAC(pk)} \leq 0.95V$           | 0.398           | $< 133V$                      |

- (1) コントローラは起動時に常にレベル 8 にデフォルト設定されるため、 $V_{VINAC(pk)}$  が  $2.47V$  未満の場合、低いレベルを検出するにはゼロクロスが必要となります。 $V_{VINAC}$  が  $0.7V$  を少なくとも  $50\mu s$  下回ったとき、各 AC 半サイクルでゼロクロスが検出されます。

- (2) 上記に示した  $V_{IN}$  のピーク電圧境界値は、PFC 出力電圧  $400V$  と、VINAC および VSENSE 上に電流合成に必要なマッチングされた抵抗分圧ネットワーク ( $k_R = 3V / 400V = 0.0075$ ) を用いることに基づいて計算されています。 $V_{OUT}$  が  $400V$  より高く、または低く設計される場合、 $k_R = 3V / V_{OUT}$  となり、各  $Q_{VFF}$  レベルの  $V_{IN}$  ピーク電圧境界値は  $V_{VINAC(pk)} / k_R$  に調整されます。

任意のラインおよび負荷条件におけるマルチプライヤ出力電流  $I_{IMO}$  は、式 13 を使用して求めることができます：

$$I_{IMO} = \frac{17 \mu A \times (V_{VINAC}) \times (V_{VAO} - 1)}{k_{VFF}} \quad (13)$$

$k_{VFF}$  値はレベル中心におけるスケーリングされた  $(V_{RMS})^2$  を表すため、 $V_{VINAC(pk)}$  が  $Q_{VFF}$  電圧範囲の中心より低い場合または高い場合、差を補償するために  $V_{VAO}$  はわずかに上下に調整されます。これは、 $V_{IN}$  が一定のレベル内で変化したとき、およびレベル間の遷移後に、電圧ループ制御によって自動的に実行されます。

電圧エラー アンプ ( $V_{VAO}$ ) の出力は  $5V$  にクランプされ、これは最大 PFC 出力電力を表します。この値は IMO ピンでの最大基準電流を計算するために使用され、許容される最大入力電力の上限を設定します (その結果として、最大出力電力も制限されます)。

連続的な  $V_{FF}$  の場合 (任意の  $V_{RMS}$  入力に対して最大入力電力が一定となる場合) とは異なり、離散的な  $Q_{VFF}$  レベルでは、入力  $V_{RMS}$  が各レベル内で変動すると、それに応じて最大入力電力が制限された範囲内で変動することが可能です。

最大電力制限が最も低くなるのは  $V_{VINAC}$  電圧が  $0.76V$  のときであり、最大電力制限が最も高くなるのはレベル 1 からレベル 2 への上昇スレッショルドにおいてです。このパターンはすべてのレベル遷移スレッショルドで繰り返されます。これは、下降スレッショルドが上昇スレッショルドの 95% であることを考慮したもののです。 $V_{VINAC} = 0.76V$  を下回ると、 $P_{IN}$  は常に  $P_{IN(max)}$  より低く、入力電圧が低下するとゼロまで直線的に低下します。

例えば、許容される最小の最大電力を設計する場合、まず PFC プリレギュレータに必要な最大定常(平均)出力電力を算出し、ラインドロップアウト回復電力(全負荷で電力を供給しながら  $C_{OUT}$  を再充電するための電力)を考慮して、 $P_{OUT(max)}$  の 10% または 20% といった追加分を上乗せします。次に、想定される効率係数を適用して、許容される最小の最大入力電力を求めます:

$$P_{IN(max)} = 1.1 \times P_{OUT(max)} / \eta \quad (14)$$

$P_{IN(max)}$  設計スレッショルドでは、 $V_{VINAC} = 0.76V$ 、したがって  $Q_{VFF} = 0.398$ 、入力  $V_{AC} = 73V_{RMS}$  となります(プリッジ整流器の 2V ドロップを考慮)。これは公称 400V 出力システムに対応します。

$$I_{IN(rms)} = P_{IN(max)} / 73V_{RMS} \quad (15)$$

$$I_{IN(pk)} = 1.414 \times I_{IN(rms)} \quad (16)$$

この  $I_{IN(pk)}$  の値は、ライン電圧のピーク時に昇圧インダクタを流れる合計平均電流を表します。各インダクタ電流は、電流検出トランジスト(CT)によって検出され、スケーリングされます。各インターリープ位相を流れる電流が等しいと仮定すると、各電流検出入力ピン(CSA および CSB)の信号電圧は、 $\frac{1}{2} I_{IN(pk)} \times R_S / N_{CT}$  に基づいて約 3V を生成するように選定された検出抵抗により得られます。ここで、 $R_S$  は電流検出抵抗、 $N_{CT}$  は CT の巻数比です。

次に、同じ最小最大電力点で  $I_{IMO}$  が次のように計算されます:

$$I_{IMO(max)} = 17 \mu A \times \frac{(0.76 V)(5 V - 1 V)}{0.398} = 130 \mu A \quad (17)$$

$R_{IMO}$  は、次のように選択されます:

$$I_{IMO(max)} \times R_{IMO} = \left( \frac{\frac{1}{2} \times I_{IN(pk)}}{N_{CT}} \right) \times R_S \quad (18)$$

次のようにになります:

$$R_{IMO} = \left( \frac{\frac{1}{2} \times I_{IN(pk)} \times R_S}{N_{CT}} \right) / I_{IMO(max)} \quad (19)$$

レベル 1 からレベル 2 へのスレッショルドの上昇側では、IMO 電流により低いラインでより大きな入力電流が許容されることに注意してください:

$$I_{IMO(L1-L2)} = 17 \mu A \times \frac{(1 V)(5 V - 1 V)}{0.398} = 171 \mu A \quad (20)$$

しかし、この電流は、電力段の設計で必要とされる場合、UCC28070-Q1 のプログラマブルピーク電流制限(PKLMT)機能によって容易に制限できます。

同じ手順を使用して、各  $Q_{VFF}$  レベルの遷移スレッショルドにおいて、最小と最大の入力電力制限を見つけることができます。高ライン電圧では、インダクタリップルを含む平均電流は通常 PKLMT スレッショルドを下回るため、最大入力電力の変動全体が現れます。しかし入力電流は、本質的に電力段で許容される最大電流レベルを下回ります。

UCC28070-Q1 の乗算器の性能は、従来世代の PFC コントローラと比較して大幅に向上しており、ほとんどの入力範囲にわたって高い線形性と精度を備えています。 $V_{VAO}$  が 1V に近づくと精度は最も悪化します。これは  $(V_{VAO} - 1)$  の減算誤差が増大し、IMO 基準電流をより大きく歪ませ始めるためです。

### 6.3.11 拡張過渡応答(VA スルーレート補正)

適切な PFC を維持し、出力に現れるわずかな倍周波リップルを無視するために必要な電圧ループ帯域幅が低いため、通常の PFC コントローラは入力電圧や負荷の過渡変動に対する応答が一般的に遅くなります。ただし、UCC28070-Q1 では、 $Q_{VFF}$  機能によりライン過渡応答が実質的に処理されますが、 $Q_{VFF}$  レベル内で必要な小さな調整は例外です。

一方で、負荷の過渡変動は電圧ループのみで対応可能です。そのため、UCC28070-Q1 は過渡応答を改善するため、VSENSE の電圧が規定値の 93%(2.79V) を下回った場合、電圧増幅器出力 ( $V_{VAO}$ ) を追加の 100 $\mu$ A の電流でプルアップするよう設計されています。

ソフトスタートサイクル中、 $V_{VSENSE}$  が 0.75V の PFC 有効化のスレッショルドから立ち上がる際、100 $\mu$ A のスルーレート補正電流源は無効化され、出力電圧と入力電流が徐々かつ制御された速度で立ち上がるようになっています。

### 6.3.12 バイアス電圧(VCC および VREF)

UCC28070-Q1 は、VCC バイアス電源範囲 10V~21V で動作します。低電圧誤動作防止 (UVLO) スレッショルドにより、 $V_{VCC} > 10.2V$  になるまで PFC がアクティブになることが防止され、ヒステリシスが 1V である場合も、コンプライアンスが低い可能性があるバイアス電源からの信頼性の高いスタートアップが保証されます。VCC ピンには内部的に 25V 程度のツェナーのようなクランプが設けられていますが、これはあくまでバイアス電源からの一時的でエネルギーが限られたサージからデバイスを保護するためのものであり、電流制限付き電源のレギュレータとして使用することはできません。

最低でも、VCC ピンから GND への 0.1 $\mu$ F セラミック バイパス コンデンサをデバイスのピン付近に配置し、バイアス電源の局所的なフィルタリングを行う必要があります。VCC のリップル電圧を最小化するため、 $I_{VCC}$  のピーク電流の大きさと期間に応じて、より大きな値が必要とされる場合があります。

UVLO からスムーズに立ち上がり、6V の基準電圧をできるだけ早く利用できるようにするために、通常、 $V_{VCC}$  が 8V を超えると VREF からの出力が有効になります。

VREF 回路は、すべての内部制御回路にバイアスを供給し、外部での限定的な使用に適しています。回路の安定性を確保するため、最小でも 22nF のセラミック バイパス コンデンサを VREF から GND に、デバイス ピンの近くに接続する必要があります。VREF ピンにかかる外部負荷電流は 2mA 未満に制限する必要があります。さもないと、レギュレーション性能が低下する可能性があります。

### 6.3.13 PFC の有効化と無効化

UCC28070-Q1 には、VSENSE ピンまたは SS ピンのバイアス状態に基づき GDx 出力を無効化するための、2 つの独立した回路が内蔵されています。

1 番目は PFC イネーブルで、 $V_{VSENSE}$  を監視し、出力が公称設定点の約 25% にプリチャージされるまでソフトスタートおよび PFC 全体の機能を保持します。 $V_{VSENSE}$  が 0.75V に達する前に、ほとんどすべての内部回路がディスエーブルになります。 $V_{VSENSE}$  が 0.75V および  $V_{VAO} < 0.75V$  を超えると、発振器、マルチプライヤ、電流シンセサイザがイネーブルになり、SS 回路は SS ピンの電圧の上昇を開始します。

2 番目の回路は、内部の故障状態を外部から模擬して GDx 出力を無効化するためのインターフェースを提供します。このとき、電圧ループや乗算器全体は完全には無効化されません。外部から SS ピンを 0.6V 未満に引き下げると、GDx 出力は即座に無効化され、低レベルに保持されます。他の故障条件が存在しない場合、外部 SS ピンのプルダウンを解除すると、通常の PWM 動作が再開されます。外部プルダウンは、SS 電圧が無効化しきい値を下回ったときに、内部の 1.5mA アダプティブ SS プルアップを上書きできるように十分な大きさに設定する必要があります。TI では、SS ピンがディスエーブル スレッショルドよりも十分に低く保持されるように、 $R_{DS(on)} < 100\Omega$  の MOSFET を使用することを推奨しています。

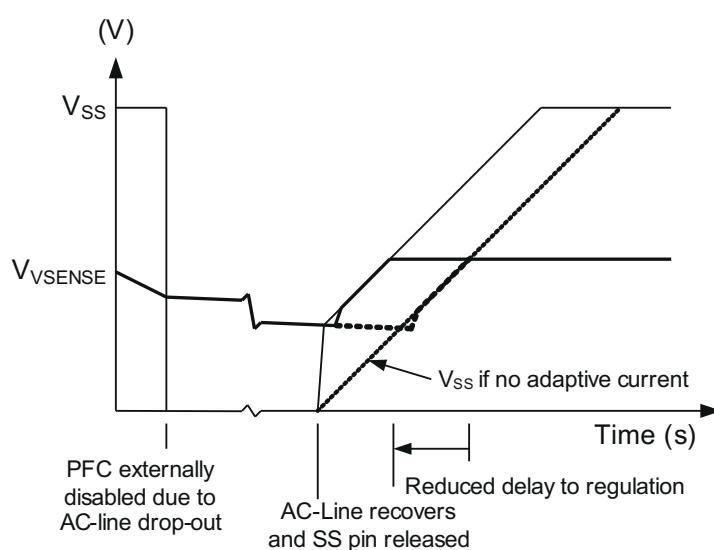

### 6.3.14 アダプティブソフトスタート

制御された電源投入を維持するために、UCC28070-Q1 にはアダプティブ ソフトスタート機能が設計されており、電源投入時に内部基準電圧を制御された電圧ランプでオーバーライドします。初回の電源投入時、 $V_{VSENSE}$  が 0.75V の有効化スレッショルド ( $V_{EN}$ ) を超えると、SS ピンの内部プルダウンが解除され、1.5mA のアダプティブ ソフトスタート電流源が動作します。この 1.5mA のプルアップは、SS ピンをほぼ瞬時に 0.75V ( $V_{VSENSE}$ ) まで引き上げ、従来の 0V から  $V_{REGULATION}$  までの SS ランプにおける初期 25% のデッドタイムをバイパスします。SS ピンが  $V_{VSENSE}$  の電圧に達すると、10μA のソフトスタート電流 ( $I_{SS}$ ) が制御を引き継ぎます。したがって、ソフトスタート用コンデンサ ( $C_{SS}$ ) を選定することで、有効ソフトスタート時間 ( $t_{SS}$ ) を式 21 に基づいて容易に設定できます。

$$t_{SS} = C_{SS} \times \left( \frac{2.25 \text{ V}}{10 \mu\text{A}} \right) \quad (21)$$

多くの場合、短時間のシャットダウン後にシステムを再起動する必要があります。このような場合、 $V_{OUT}$  が完全に放電されていない場合、または高いラインでピーク充電  $C_{OUT}$  が発生した場合でも、 $V_{VSENSE}$  には大きな電圧が印加されることがあります。 $C_{SS}$  を 0V から予め充電された  $V_{VSENSE}$  まで 10μA の電流源だけで充電することによる遅延を排除し、さらに出力電圧の低下を最小限に抑えるため、アダプティブ ソフトスタートでは 1.5mA の電流源を用いて  $C_{SS}$  を迅速に  $V_{VSENSE}$  まで充電し、その後に 10μA の電流源が所望のソフトスタートランプレートで  $V_{SS}$  の立ち上がりを制御します。この場合、 $t_{SS}$  は次のように推定されます：

$$t_{SS} = C_{SS} \times \left( \frac{3 \text{ V} - V_{VSENSE0}}{10 \mu\text{A}} \right) \quad (22)$$

ここで、

- $V_{VSENSE0}$  は、ソフトスタートまたは再起動が開始されたときの  $V_{VSENSE}$  の電圧です

#### 注

ソフトスタートを効果的にし、 $V_{OUT}$  のオーバーシュートを防止するには、SS ランプを電圧ループ制御応答よりも遅くする必要があります。これを確実にするために、 $C_{SS} \geq C_{VZ}$  を選択します。

図 6-4. ソフトスタート ランプレート

### 6.3.15 PFC スタートアップホールドオフ

UCC28070-Q1 に設計されている追加機能は、スタートアップ ホールドオフリックで、VAO ピンがゼロ電力スレッショルド (0.75V) を下回るまで、デバイスがソフトスタート サイクルの開始を阻止します。この機能により、SS サイクルはゼロ電力かつゼロ デューティ サイクルから開始され、VAO 補償ネットワークに蓄積された電荷による大きな突入電流の発生を防ぐことができます。

### 6.3.16 出力過電圧保護(OVP)

PFC 回路では、高電圧出力と出力コンデンサの設計マージンが限られているため、出力過電圧保護が不可欠です。UCC28070-Q1 は、 $V_{VSENSE}$  を継続的に監視することで OVP を実装しています。 $V_{VSENSE}$  が規定値の 106% (3.18V) を超えた場合、出力電圧が過大になるのを防ぐために、GDx 出力は直ちに無効化されます。OVP (過電圧保護) 故障が解除された後、0% のデューティ サイクルから制御された回復を行うために、同時に CAOx 出力は低レベルに引き下げられます。 $V_{VSENSE}$  が 3.08V を下回ると、PWM 動作は通常動作に戻ります。

### 6.3.17 ゼロ電力検出

無負荷やほぼ無負荷の状態での望ましくない性能を防止するため、UCC28070-Q1 ゼロパワー検出コンパレータは、 $V_{VAO}$  電圧が 0.75V を下回った場合に GDA と GDB の両方の出力を無効にするように設計されています。150mV のヒステリシスにより、 $V_{VAO}$  が乗算器の線形範囲 ( $V_{VAO} \geq 0.9V$ ) に戻るまで、出力は無効のままでです。

### 6.3.18 サーマルシャットダウン

UCC28070-Q1 には内部温度を検知するコンパレータが内蔵されており、シリコンが過熱による故障から電源を保護するため、ダイ温度が 160°C を超えるとほぼ全ての内部回路をシャットダウンし、GDA および GDB 出力を無効化します。ダイ温度が 140°C 未満に下がると、デバイスは典型的なソフトスタートで出力を復帰させます。

### 6.3.19 電流ループ補償

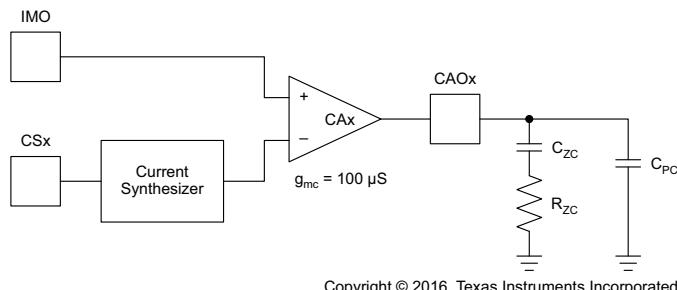

UCC28070-Q1 は、PFC 入力電流波形の整形を制御するために、2 つの同一かつ独立した相互コンダクタンス型電流誤差アンプ（各フェーズに 1 つ）を備えています。電流誤差アンプ（CA）は、ブースト PFC プリレギュレータに組み込まれた電流制御ループの中核を成し、ループ安定性のために一般的な原理 [7, 8] を用いて補償されています。位相 A の CA の出力は CAOA、位相 B の場合は CAOB です。両者の設計上の考慮事項は同じであるため、まとめて CAOx (x は A または B) と呼ばれます。

昇圧 PFC プリレギュレータ内の電流制御ループは、昇圧電力プラント段、電流センシング回路、波形形状のリファレンス、PWM 段、補償部品を備えた CA で構成されています。CA は、検出された昇圧インダクタの平均電流を乗算器ステージからの波形リファレンスと比較し、その差に比例した出力電流を生成します。

この CA 出力電流は補償ネットワークのインピーダンスを流れて出力電圧  $V_{CAO}$  を生成し、その後、周期電圧ランプと比較されて PFC を達成するために必要な PWM 信号を生成します。

Copyright © 2016, Texas Instruments Incorporated

図 6-5. 電流誤差アンプ、タイプ II 補償付き

昇圧 LC 共振より高く、 $f_{PWM}$  より低い周波数において、電流検出を含む昇圧段の小信号モデルは次のように簡略化できます：

$$\frac{V_{RS}}{V_{CA}} = \frac{V_{OUT} \times \frac{R_S}{N_{CT}}}{\Delta V_{RMP} \times k_{SYNC} \times s \times L_B} \quad (23)$$

ここで

- $L_B$  = 中値昇圧インダクタンス

- $R_S$  = CT 検出抵抗

- $N_{CT}$  = CT 卷数比

- $V_{OUT}$  = PFC コンバータの平均出力電圧

- $\Delta V_{RMP}$  = PWM 電圧ランプの  $4V_{pk-pk}$  振幅

- $k_{SYNC}$  = 外部同期周波数によるランプ減衰係数:  $k_{SYNC} = (15000 / R_{RT}(k\Omega)) / f_{SYNC}$ , ここで  $R_{RT}(k\Omega)$  は式 8 から得られます。外部同期を使用しない場合、 $k_{SYNC} = 1$  になります。

- $s$  = ラプラス複素変数

CAOx に  $R_{ZC}$ - $C_{ZC}$  ネットワークを導入することで、インダクタ電流信号の低周波成分に対して高ゲインを得る一方、ゼロ周波数から  $f_{PWM}$  までの範囲では平坦なゲインを低く抑え、信号の高周波スイッチングリップル成分を減衰させます（つまり平均化します）。

CAOx 出力のスイッチングリップル電圧は、無視できるリップルと見なすため、 $\Delta V_{RMP}$  振幅の 1/10 未満に減衰させる必要があります。

したがって、 $f_{PWM}$  での CAOx ゲインは次の式で表されます：

$$g_{mc} \times R_{ZC} \leq \frac{\frac{\Delta V_{RMP} \times k_{SYNC}}{10}}{\Delta I_{LB} \times \frac{R_S}{N_{CT}}} \quad (24)$$

ここで

- $\Delta I_{LB}$  は、昇圧インダクタにおける最大ピークツーピークリップル電流です

- $g_{mc} = CA$  の相互コンダクタンス、 $100\mu S$

$$R_{ZC} \leq \frac{4V \times N_{CT} \times k_{SYNC}}{10 \times 100\mu S \times \Delta I_{LB} \times R_S} \quad (25)$$

電流ループのクロスオーバー周波数は、開ループゲインを 1 に等しくして  $f_{CXO}$  を解くことで求められます：

$$f_{CXO} = \frac{V_{OUT} \times \frac{R_S}{N_{CT}}}{\Delta V_{RMP} \times k_{SYNC} \times 2\pi \times L_B} \times g_{mc} \times R_{ZC} \quad (26)$$

$C_{ZC}$  は、 $f_{ZC} = f_{CXO} = 1 / (2\pi \times R_{ZC} \times C_{ZC})$  と置き、 $C_{ZC}$  を解くことで決定されます。 $f_{ZC} = f_{CXO}$  のとき、 $f_{CXO}$  で位相マージンは  $45^\circ$  です。位相マージンを大きくしたい場合は、 $f_{ZC}$  を  $f_{CXO}$  より低く設定する ( $C_{ZC}$  を大きくする) といいます。

追加の高周波極は、一般に  $f_{PWM}$  または  $f_{PWM}/2$  に設けられ、 $f_{PWM}$  以上のリップルやノイズをさらに減衰させます。これは、 $R_{ZC}$ - $C_{ZC}$  ネットワークに並列して、より小さい値のコンデンサ  $C_{PC}$  を追加することで行われます。

$$C_{PC} = \frac{1}{2\pi \times \frac{f_{PWM}}{2} \times R_{ZC}} \quad (27)$$

上記の手順は、固定値のインダクタに有効です。

#### 注

もし「スイング チョーク」型昇圧インダクタ（電流が増えるとインダクタンスが徐々に減少する）を使用する場合、 $f_{CXO}$  はインダクタンスに反比例して変化するため、 $C_{ZC}$  は最大インダクタンス時に決定する必要があります。

### 6.3.20 電圧ループ補償

2 相 PFC コントローラの外部電圧制御ループは、単相コントローラと同じように機能し、ループ安定性の補償技法が標準的です[7]。出力電圧の歪みの原因となる歪みを避けるため、電圧ループの帯域幅は、出力コンデンサの 2 ラインリップル周波数 ( $f_{2LF}$ ) よりも大幅に低くする必要があります。電圧誤差アンプ ( $V_{VAO}$ ) の出力は乗算器への入力となり、必要な出力電力に応じて入力電流の振幅を調整します。電流ループの帯域幅内での  $V_{AO}$  の変動は、入力電流の波形に影響を与えます。 $C_{OUT}$  上の低周波リップルは入力電力のみに依存するため、そのピーク・ツー・ピーク振幅は、高ラインでも低ラインでも同じです。このリップルに対する電圧ループの応答は、低ライン電流よりも高ライン電流に対して大きな歪み効果を及ぼします。したがって、 $V_{AO}$  に起因する入力電流の 3 次高調波歪みの許容割合は、ハイライン条件を用いて決定する必要があります。

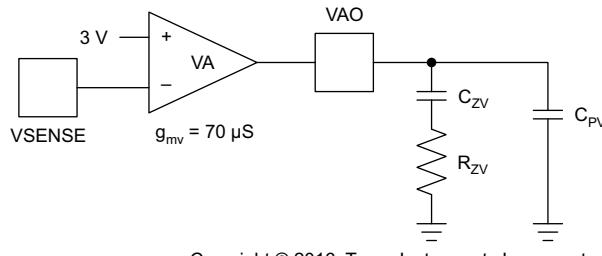

電圧誤差アンプ ( $VA$ ) は相互コンダクタンス型アンプであるため、その入力のインピーダンスはアンプゲインに影響を及ぼしません。アンプゲインは、相互コンダクタンス ( $g_{mv}$ ) と出力インピーダンス ( $Z_{ov}$ ) の積によってのみ決まります。そのため、**VSENSE** 入力分圧器ネットワークの値は、**VSENSE** および **VINAC 開路保護**で説明されている基準に基づいて個別に決定されます。その出力は  $V_{AO}$  ピンです。

Copyright © 2016, Texas Instruments Incorporated

図 6-6. タイプ II 换算付き電圧誤差アンプ

入力電流波形の 3 次高調波歪みを所望のレベルに抑えるために、 $V_{VSENSE}$  の 2 倍ラインリップル電圧成分は VAOにおいて十分に減衰され、位相シフトされる必要があります [4]。許容される入力の 3 次高調波歪み 1% ごとに、2 倍ライン周波数における小信号ゲイン  $G_{VEA} = V_{VAOpk} / V_{SENSEpk} = g_{mv} \times Z_{OV}$  は、 $V_{VAO}$  の全電圧範囲にわたって 2% を超えるリップルを許容してはなりません。UCC28070-Q1 では、 $V_{VAO}$  は無負荷時の 1V から全負荷時のおよそ 4.2V まで変化し、 $\Delta V_{VAO} = 3.2V$  となります。したがって、3.2V の 2% は 64mV のピークリップルとなります。

### 注

最大  $V_{VAO}$  は 5V にクランプされていますが、全負荷時には、乗算器ステージにおける量子化フィードフォワード電圧の影響を補償するため、 $V_{VAO}$  はおおよそ 4.2V の中心点付近で変動する場合があります(詳細は「[ニア乗算器と量子化フィードフォワード](#)」を参照してください)。したがって、電圧ループ ゲイン計算を行うときに最大出力電力を表すために、4.2V が適切な電圧です。

出力コンデンサの最大低周波ゼロ ツー ピークリップル電圧は、おおよそ次の式で表されます:

$$V_{0pk} = \frac{P_{IN(avg)} \times X_{Cout}}{V_{OUT(avg)}} = \frac{P_{IN(avg)}}{V_{OUT(avg)} \times 2\pi \times f_{2LF} \times C_{OUT}} \quad (28)$$

ここで

- $P_{IN(avg)}$  は、インターリープ PFC プリレギュレータの総最大入力電力です

- $V_{OUT(avg)}$  は平均出力電圧です

- $C_{OUT}$  は出力キャパシタンスです

$$V_{SENSEpk} = V_{0pk} \times k_R \quad (29)$$

ここで、

- $k_R$  は VSENSE 上の抵抗分圧ネットワークのゲインです

したがって、 $k_{3rd}$  は、VAO リップルに起因する入力電流の 3 次高調波歪みの許容割合 (%) を表します、

$$Z_{OV(f_{2LF})} = \frac{k_{3rd} \times 64 \text{ mV} \times V_{OUT(avg)} \times 2\pi \times f_{2LF} \times C_{OUT}}{g_{mv} \times k_R \times P_{IN(avg)}} \quad (30)$$

VAO 上のこのインピーダンスはコンデンサ ( $C_{PV}$ ) によって設定され、 $C_{PV} = 1 / (2\pi f_{2LF} \times Z_{OV}(f_{2LF}))$  で表されます。したがって、次のようにになります:

$$C_{PV} = \frac{g_{mv} \times k_R \times P_{IN(avg)}}{k_{3rd} \times 64 \text{ mV} \times V_{OUT(avg)} \times (2\pi \times f_{2LF})^2 \times C_{OUT}} \quad (31)$$

電圧ループのユニティ ゲイン クロスオーバ周波数 ( $f_{VXO}$ ) は、開ループ電圧伝達関数ゲインを 1 に設定することで解決できます：

$$TV(f_{VXO}) = G_{BST} \times G_{VEA} \times k_R = \left( \frac{P_{IN(avg)} \times X_{Cout}}{\Delta V_{VAO} \times V_{OUT(avg)}} \right) \times (g_{mv} \times X_{CPV}) \times k_R = 1 \quad (32)$$

$$so, f_{VXO}^2 = \frac{g_{mv} \times k_R \times P_{IN(avg)}}{\Delta V_{VAO} \times V_{OUT(avg)} \times (2\pi)^2 \times CPV \times C_{OUT}} \quad (33)$$

補償のゼロ配置ネットワークにおけるゼロ抵抗 ( $R_{ZV}$ ) をここで算出できます。 $R_{ZV}$  は  $C_{PV}$  とともに  $f_{VXO}$  に極を配置し、クロスオーバーで  $45^\circ$  の位相マージンを得ます。

$$R_{ZV} = \frac{1}{2\pi \times f_{VXO} \times CPV} \quad (34)$$

最後に、コンデンサ  $C_{ZV}$  によってゼロが  $f_{VXO} / 6$  かそれ以下に配置され、DC で高ゲインを得つつ、ブレーキポイントを  $f_{VXO}$  より十分低くすることで位相マージンを大きく損なわないようにします。 $f_{VXO} / 10$  を選ぶことで、 $C_{ZV}$  と  $C_{PV}$  の並列合 成値を  $C_{ZV}$  と近似でき、 $C_{ZV}$  を次のように簡単に求められます：

$$C_{ZV} = \frac{10}{2\pi \times f_{VXO} \times R_{ZV}} \approx 10 \times CPV \quad (35)$$

スプレッドシートや数値計算プログラムを用いることで、 $C_{ZV}$ 、 $R_{ZV}$ 、 $C_{PV}$  を操作して、それらが  $f_{VXO}$  や位相マージン、および 3 次高調波歪みへの寄与割合に及ぼす影響を確認できます。また、位相マージンは  $P_{IN(avg)}$  レベルとして確認でき、システムパラメータの許容誤差が変動することもあります。

#### 注

このセクションで計算される 3 次高調波歪みのパーセンテージは、 $C_{OUT}$  のみにおける  $f_{2LF}$  電圧リップルからの寄与を表します。電流検出トランジスタ、電流シンセサイザ段、過度に制限された  $D_{MAX}$  など、他の歪み発生源は、3 次およびより高い高調波歪みを増大させる可能性があります。

## 6.4 デバイスの機能モード

UCC28070-Q1 は平均電流モードで動作します。これにより、ピーク電流モード制御方式に固有のピーク電流と平均電流の誤差が解消され、ラインから取り込まれる電流の THD や高調波が低減されます。スロープ補償を必要とせず、ピーク電流制御方式よりもノイズ耐性が優れています。

## 7 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インストルメンツの製品仕様に含まれるものではなく、テキサス・インストルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

UCC28070-Q1 は、力率改善用のインターリーブ昇圧コンバータで使用されるスイッチモード コントローラです。UCC28070-Q1 デバイスは、アクティブ PFC プリレギュレータとして動作するために必要な外付け部品が少なくて済みます。このデバイスは、連続導通モードで固定周波数動作します。動作スイッチング周波数は、RT ピンからグランドへの単一の抵抗によって 30kHz ~ 300kHz の範囲で設定できます。任意の周波数ディザリングの振幅および変調速度も簡単に制御できます。

内部の 6V リファレンス電圧により、典型的な世界規模の入力電圧範囲 85V<sub>AC</sub>~265V<sub>AC</sub> およびゼロから定格出力までの負荷条件において、正確な出力電圧制御が可能です。このリファレンスは、ピーク電流制限の設定にも使用できます。レギュレーションは 2 つのループで実現します。内部の電流ループは、インダクタ電流が連続している条件下で、平均入力電流が正弦波状の入力電圧に一致するように形成します。単一の乗算器出力が 2 つの電流アンプ間で共有され、両相の電流が密接に一致するようにしています。ゼロパワー検出器により、軽負荷時には GDA 出力と GDB 出力の両方がディスエーブルになります。

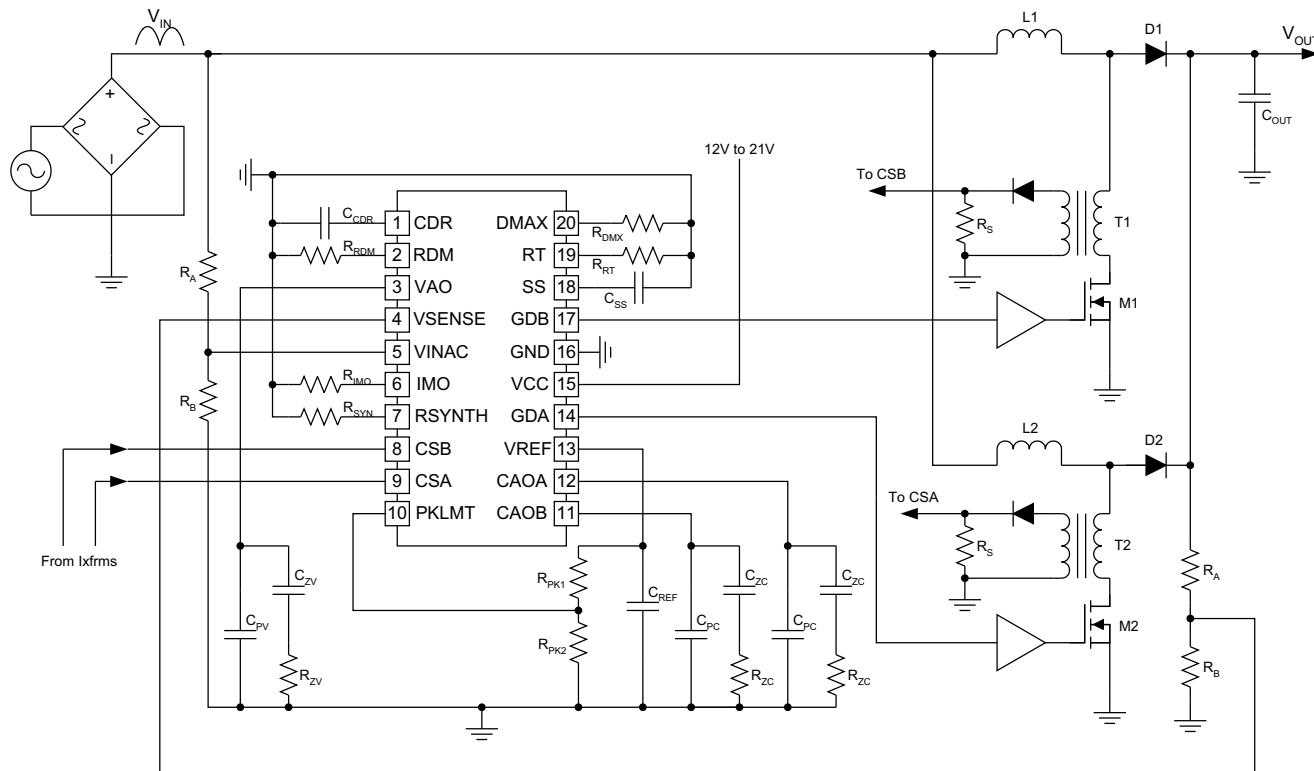

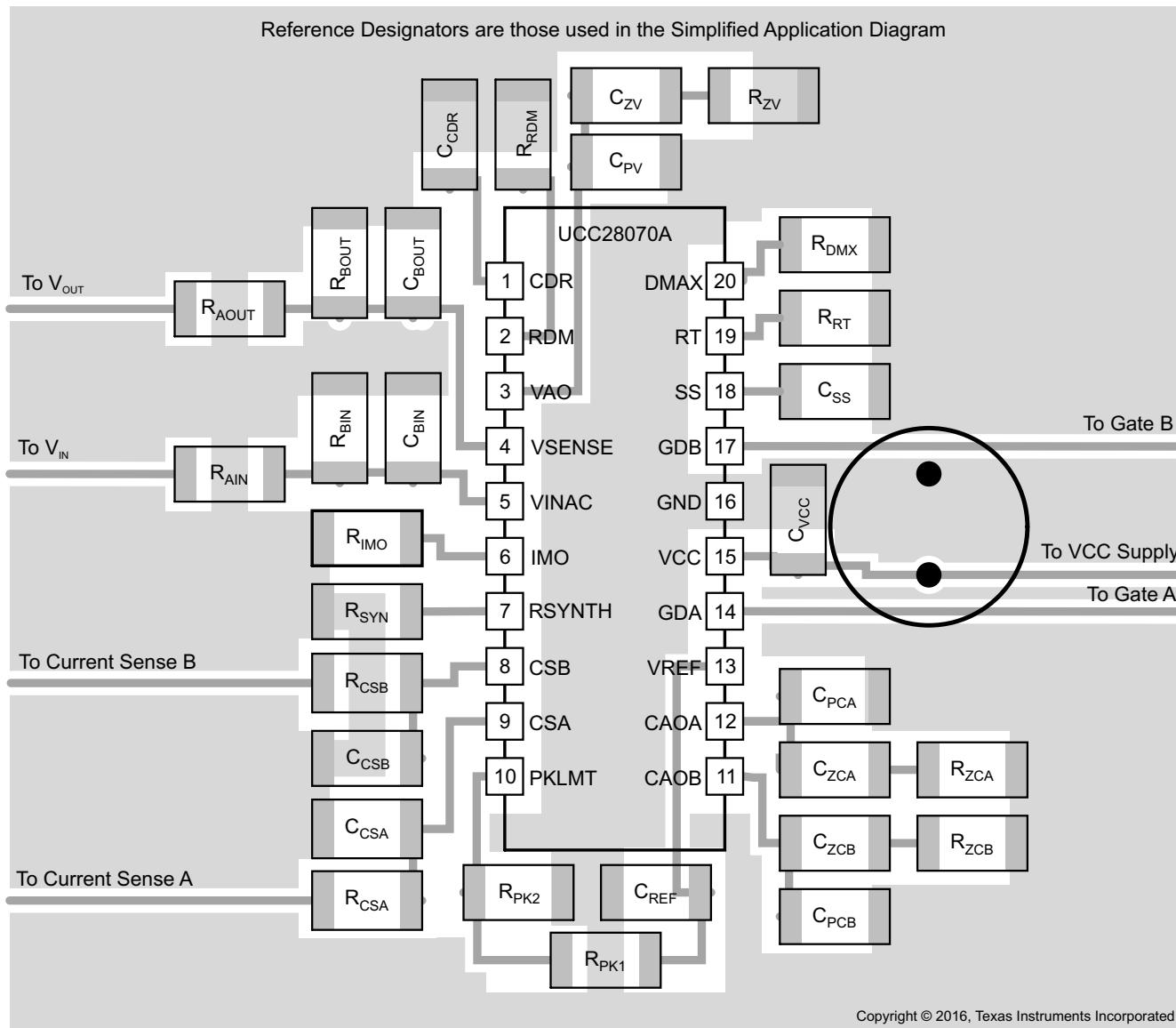

### 7.2 代表的なアプリケーション

Copyright © 2016, Texas Instruments Incorporated

図 7-1. 代表的なアプリケーションの図

## 7.2.1 設計要件

この設計例では、表 7-1 に記載されているパラメータを入力パラメータとして使用します。

**表 7-1. 設計パラメータ**

| 設計パラメータ                   | 最小値 | 標準値 | 最大値 | 単位  |

|---------------------------|-----|-----|-----|-----|

| V <sub>AC</sub> 入力電圧      | 85  |     | 265 | V   |

| V <sub>OUT</sub> 出力電圧     |     | 390 |     | V   |

| f <sub>LINE</sub> ライン周波数  | 47  |     | 63  | Hz  |

| f <sub>SW</sub> スイッチング周波数 |     | 200 |     | kHz |

| P <sub>OUT</sub> 出力電力     |     | 300 |     | W   |

| η 全負荷効率                   | 90% |     |     |     |

## 7.2.2 詳細な設計手順

### 7.2.2.1 出力電流の計算

最初のステップは、出力にかかる最大負荷電流を求めることです。

$$I_o = \frac{P_o}{V_o} = \frac{300W}{385V} = 0.78A \quad (36)$$

### 7.2.2.2 ブリッジ整流器

最大 RMS 入力ライン電流は、式 37 で求められます：

$$I_{line\_max} = \frac{P_o}{\eta V_{AC\_min}} = \frac{300W}{98\%(85V)} = 3.6A_{rms} \quad (37)$$

ピーク入力電流は式 38 で求められます：

$$I_{in\_pk} = \sqrt{2} \times I_{line\_max} = \sqrt{2} \times 3.6A = 5.1A \quad (38)$$

最大整流平均ライン電流は式 39 で求められます：

$$I_{in\_avg\_max} = \frac{2\sqrt{2}}{\pi} \times I_{line\_max} = \frac{2\sqrt{2}}{\pi} \times 3.6A = 3.25A \quad (39)$$

標準的なブリッジ整流器の順方向電圧降下 V<sub>F</sub> は、I<sub>in\_pk</sub> で 0.95V です。整流器ブリッジの最大電力損失は、式 40 で控えめに推定できます：

$$P_{BR\_max} = 2 \times V_F \times I_{in\_avg\_max} = 2 \times 0.95V \times 3.25A = 6.2W \quad (40)$$

ブリッジ整流器は、ラインの最大電流に加えて予想されるサージ電流ピークにも耐えられる定格である必要があります。また、ラインが接続されているときにバルクコンデンサー C<sub>OUT</sub> が充電されるため、ブリッジ整流器は大きな突入電流を流します。ブリッジ整流器の定格電圧は、AC ラインのサージなどを含む、予想される最大入力ピーク電圧に対して十分なマージンを確保できる値が推奨されます。

### 7.2.2.3 PFC インダクタ ( $L_1$ および $L_2$ )

PFC インダクタの値の選定は、通常、いくつかの異なる考慮事項に基づいて行われます。コスト、コアサイズ、EMI フィルタ、インダクタのリップル電流などが、影響を与える要因の一部です。このデータシートの以前のバージョンでは、インダクタの選定方法として、最小入力電圧時のインダクタのピークツーピークリップル電流 ( $\Delta I_L$ ) が各相の AC ライン電流のピークと同じ振幅になるように設計していました。ライン電流は 2 相で等しく流れるため、 $\Delta I_L$  は式 38 で計算される  $I_{in\_pk}$  の半分になります。この方法は、比較的低い最小入力電圧では良好に動作しますが、ピーク電圧が  $V_{OUT}$  に近い最小入力では過度に低いインダクタンスが発生することがわかりました。

このデータシートでは、新しい昇圧インダクタンスの計算方法が示されており、設計の主な基準は入力電流の歪みを低く抑えることです。近年では、軽負荷かつ高入力電圧時における低歪みが、多くの用途で重要な設計要件となっています。CCM 昇圧 PFC では、入力 AC ライン周期の大部分でインダクタ電流が DCM で動作すると、入力電流の総高調波歪み (THDi) が大きく増加します。任意のライン電圧および負荷条件で低い THDi を維持するには、その動作点で昇圧インダクタが CCM で動作するように維持する必要があります。PFC コンバータは AC ラインに対して等価または模擬抵抗  $R_e$  を提示することを目的としているため、次の条件下ではインダクタ電流がライン周期全体で CCM で動作することが示されます [5]:

$$R_e < \frac{2 \times L_B}{T_{PWM}}, \text{ where } R_e = \frac{V_{rms}^2}{P_{IN}} \text{ and } T_{PWM} = \frac{1}{f_{PWM}} \quad (41)$$

項を整理して代入することにより、CCM を維持するために必要な最小昇圧インダクタンスは次の式で計算されます：

$$L_1 = L_2 = L_B \geq \frac{V_{rms\_CCM(max)}^2}{2 \times (P_{O\_CCM(min)} / \eta) \times f_{PWM}} \quad (42)$$

ここで、

- $V_{rms\_CCM(max)}$  は、CCM 動作が維持される rms 入力電圧の最大値です

- $P_{O\_CCM(min)}$  は、CCM を維持する必要があるインダクタあたりの最小出力電力レベルです

- $\eta$  は、 $P_{O\_CCM(min)}$  および  $V_{rms\_CCM(max)}$  で期待される変換効率です

PFC では、式 42 で計算された値よりも小さい昇圧インダクタンスが使用できますが、ライン サイクルの DCM の量が増加すると、THDi は増加します。

前のデータシートでのインダクタ選定と一致させると、100Vrms 入力、各相 150W、効率 95%、PWM スイッチング周波数 200kHz の CCM 動作では、 $L_B$  は 158.333μH 以上である必要があることがわかります。

$L_1 = L_2 = 160\mu H$  を選択します。

このインダクタンスが与えられると、低ラインのピーク時の  $\Delta I_L$  は次のように計算できます：

$$\Delta I_L = \frac{(V_{OUT} - \sqrt{2} \times V_{AC\_min})}{L_B} \times \left( \frac{\sqrt{2} \times V_{AC\_min}}{V_{OUT}} \right) \times T_{PWM} = \frac{(385 V - 120 V)}{160 \mu H} \times \left( \frac{120 V}{385 V} \right) \times 5 \mu s = \sim 2.57 A \quad (43)$$

その後、各昇圧インダクタのピーク電流はおよそ次のようにになります：

$$I_{L\_pk} = \frac{I_{in\_pk}}{2} + \frac{\Delta I_L}{2} = \frac{5.1 A}{2} + \frac{2.57 A}{2} = \sim 3.8 A \quad (44)$$

この適用例における基本的なインダクタ仕様は以下の通りです：

- インダクタンス: 160μH

- ピーク電流: 4A

### 7.2.2.4 PFC MOSFET ( $M_1$ および $M_2$ )

PFC MOSFET の主な仕様は次のとおりです:

- $B_{V_{DSS}}$ 、ドレインソースブレークダウン電圧:  $\geq 650V$

- $R_{DS(on)}$ 、オン状態のドレインソース抵抗:  $25^{\circ}C$ で  $520m\Omega$  の抵抗が、 $125^{\circ}C$ ではおよそ  $1\Omega$  になると推定

- $C_{oss}$ 、出力キャパシタンス: 約  $400V$  で  $32pF$

- $t_r$ 、デバイスの立ち上がり時間:  $12ns$

- $t_f$ 、デバイスの立ち下がり時間:  $16ns$

デバイスでの損失は、式 45 と式 46 で計算されます。これらの計算は近似値です。損失は十分に管理されていないパラメータに依存するためです。例えば、MOSFET の  $R_{DS(on)}$  は  $25^{\circ}C$  から  $125^{\circ}C$  で 2 倍に増加することがあります。そのため、ここで示したものとは異なる用途に最適なデバイスを選定するには、何度か繰り返し検討する必要があります。

各相は負荷電力の半分を担うため、導通損失は次の式で推定されます:

$$P_{M\_cond} = \left( \frac{0.5 \times P_o}{\sqrt{2} \times V_{IN(min)}} \times \sqrt{2 - \frac{16}{3\pi} \times \frac{\sqrt{2} \times V_{IN(min)}}{V_{OUT}}} \right)^2 \times R_{DS(on)} = \left( \frac{150W}{\sqrt{2} \times 85V} \times \sqrt{2 - \frac{16}{3\pi} \times \frac{\sqrt{2} \times 85V}{385V}} \right)^2 \times 1.0 = 2.25W \quad (45)$$

各 MOSFET のスイッチング損失は次の式で推定されます:

$$P_{M\_sw} = \frac{1}{2} \times f_{SW} \left( V_o \times \frac{|I_{line\_max}|}{2} \times (t_r + t_f) + C_{oss} \times V_o^2 \right) = \frac{1}{2} \times 200kHz \left( 385V \times \frac{3.6A}{2} \times (12ns + 16ns) + 32pF \times 385V^2 \right) = 2.4W \quad (46)$$

その結果、各 MOSFET の総損失は次のようにになります:

$$P_M = P_{M\_cond} + P_{M\_sw} = 2.25W + 2.4W = 4.9W \quad (47)$$

### 7.2.2.5 PFC ダイオード

CCM 昇圧コンバータでは、逆回復損失が大きな場合があります。ここではシリコン カーバイド ダイオードが選ばれています。逆回復電荷 ( $Q_{RR}$ ) がなく、逆回復損失がゼロだからです。

$$P_D = V_f \times \frac{I_{OUT}}{2} = 1.5V \times \frac{0.78A}{2} = 580mW \quad (48)$$

### 7.2.2.6 PFC 出力コンデンサ

出力コンデンサの値は、必要なホールドアップ時間と、出力で許容されるリップル電圧によって決まります。

ホールドアップ時間は、負荷電流と出力で許容される最小電圧によって決まります。

出力コンデンサの容量は、要求されるホールドアップ時間を確保し、二倍線周波数でのリップル電圧を許容範囲内に収めるのに十分な大きさでなければなりません。通常、ホールドアップ時間が重要でない場合、出力電力 1Wあたり約 0.6μF (出力電圧約 400V) が妥当な妥協値となります。300W の場合、これは約 200μF の静電容量を示しています。

$V_{OUT}$  の低周波数 (ライン周波数が 2 倍のとき) rms 電圧リップルは、式 49 で求められます:

$$V_{0\_ripple} = \frac{1}{\sqrt{2}} \times \frac{I_0}{2\pi \times 2f_{line} \times C_0} = \frac{1}{\sqrt{2}} \times \frac{0.78A}{2\pi \times 100Hz \times 200\mu F} = 4.4V_{rms} \quad (49)$$

その結果、コンデンサに 2 本のラインの低周波電流が流れると以下のようになります:

$$I_{0\_ripple} = 2\pi \times 2f_{line} \times C_0 \times V_{0\_ripple} = 2\pi \times 100Hz \times 200\mu F \times 4.4V_{rms} = 0.55A_{rms} \quad (50)$$

### 7.2.2.7 電流ループ帰還構成

#### (電流トランスの巻線比 $N_{CT}$ と電流検出抵抗 $R_S$ の最適化)

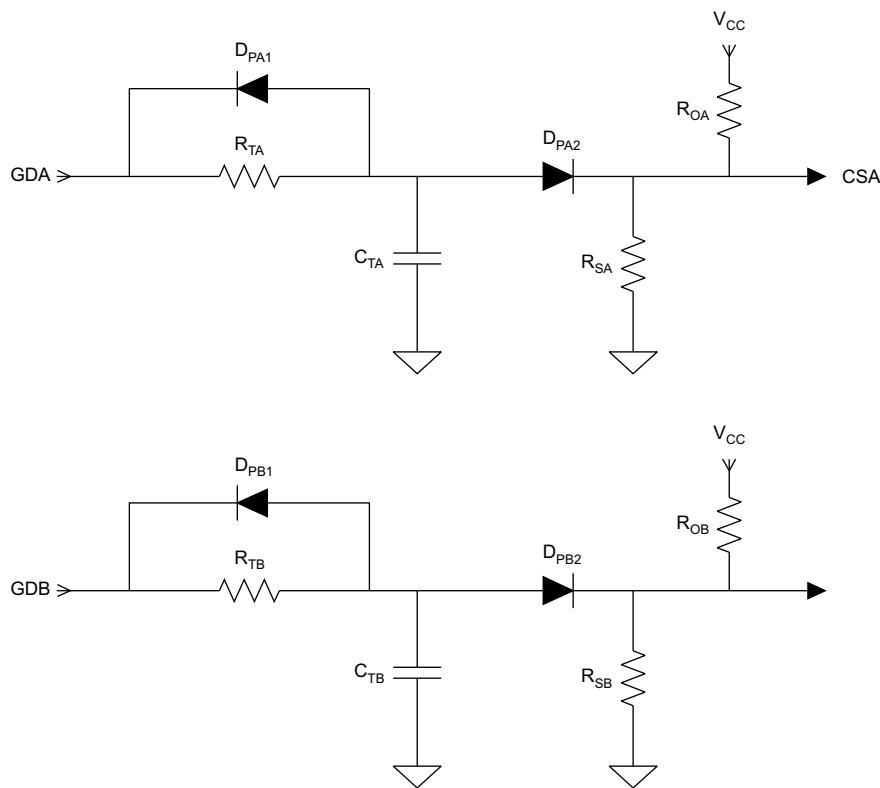

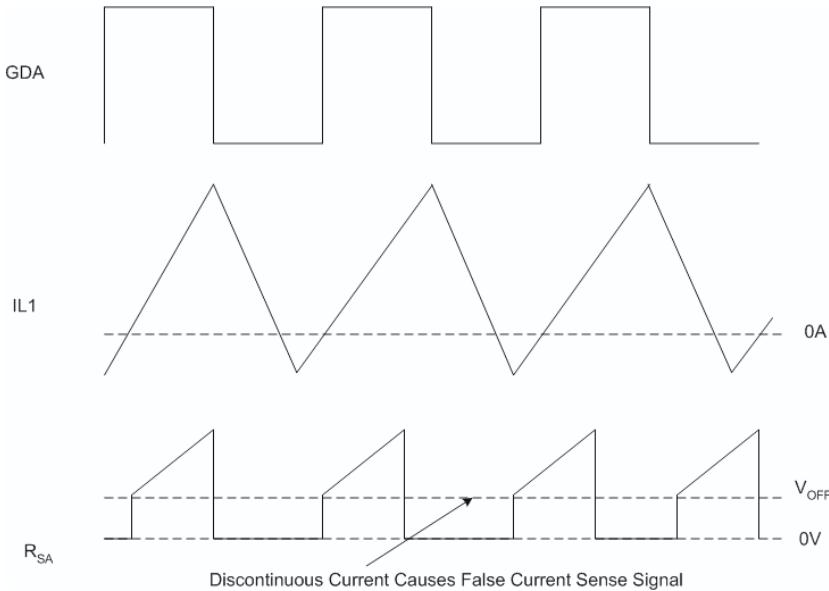

電流検出トランス (CT) は、高電力アプリケーションにおいてインダクタ電流を検出し、電流検出用抵抗の使用に伴う損失を回避するために一般的に使用されます。平均電流モード制御では、インダクタ電流の全波形が必要となります。しかし、低周波の CT を用いることは明らかに実用的ではありません。通常、2 つの高周波 CT が使用されます。1 つはスイッチング側に配置して立ち上がりスロープ電流を取得し、もう 1 つはダイオード側に配置して立ち下がりスロープ電流を取得します。これら 2 つの電流信号は合算されてインダクタ電流全体を構成しますが、UCC28070-Q1 では不要です。

UCC28070-Q1 の設計上の大きな利点は電流合成機能であり、この機能はスイッチング期間のオフ時間に、インダクタ電流の立ち下がりスロープを内部的に再現します。これにより、各相におけるダイオード側 CT の必要がなくなり、スペース、コスト、複雑さを大幅に削減できます。電流シーケンサセクションで説明したように、1 つの抵抗により、シーケンサのダウンスロープをプログラムします。

CT を選定する際には、いくつかのトレードオフを考慮する必要があります。さまざまな内部要因および外部要因が、CT のサイズ、コスト、性能、そして歪みへの寄与に影響を及ぼします。

これらの要因には、以下が含まれますが、これらに限定されるものではありません:

- 卷線比 ( $N_{CT}$ )

- 励磁インダクタンス ( $L_M$ )

- 漏れインダクタンス ( $L_{LK}$ )

- ポルト-マイクロ秒積 ( $V\mu s$ )

- 分布容量 ( $C_d$ )

- 直列抵抗 ( $R_{SER}$ )

- 外付けダイオード降下 ( $V_D$ )

- 外部電流センス抵抗 ( $R_S$ )

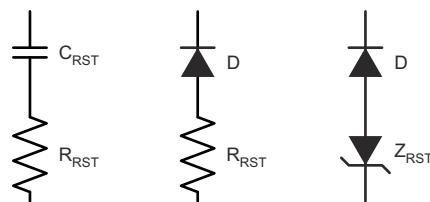

- 外部リセットネットワーク

従来は、巻数比と電流検出抵抗が最初に選定されていました。他の要因を考慮に入れると、選定を調整するためにいくつかの反復が必要になる場合があります。

一般に、 $50 \leq N_{CT} \leq 200$  を選択するのが妥当な範囲です。 $N_{CT}$  が低すぎると、 $R_S$  に電力損失が大きくなり、 $L_M$  が不十分になる可能性があります。高すぎると、 $L_{LK}$  と  $C_d$  が過剰になる可能性があります。(一次巻線は 1 ターンと仮定します。)

Copyright © 2016, Texas Instruments Incorporated

図 7-2. 電流検出トランジスタの等価回路

入力電流の歪みに寄与する主な要因は、CT 出力信号 ( $I_{RS}$ ) への磁化電流の影響です。巻線比が高いと、与えられたコアサイズで  $L_M$  が大きくなります。 $L_M$  は、生成される磁化電流 ( $i_M$ ) が全変換電流のごく一部になるよう、十分に高くする必要があります。これは、電流範囲全体にわたって維持するのは不可能な基準になります。入力電流がゼロに向かって減少すると、 $i_M$  が  $I_{RS}$  の一部より大きくなるのは避けられないからです。 $i_M$  の効果は、信号電流の一部を  $R_S$  から奪い、CSx 電圧を下げて、検出されている実際の電流を効果的に判断することです。低電流時には、この過小評価が大きな影響を及ぼす可能性があり、CAOx は CSx 入力を IMO リファレンス電圧に一致させようとして、電流ループのデューティサイクルを増加させます。この不要な補正により、CT の過小評価が顕著な領域、例えば AC ラインのゼロクロス付近では、入力波形上の電流が過大に表示される結果となります。高ラインかつ軽負荷の条件下では、波形全体にある程度の影響を及ぼす可能性があります。