# UCC28063 Natural Interleaving™ 遷移モード PFC コントローラ、可聴ノイズ耐性改善機能付き

## 1 特長

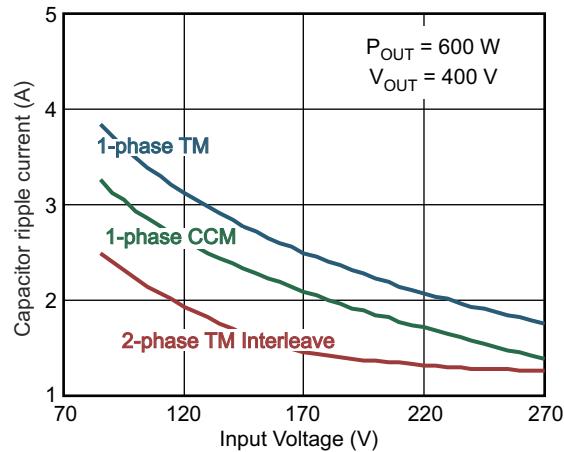

- 入力フィルタおよび出力コンデンサのリップル電流を解消

- 電流リップルの低減によるシステムの信頼性向上とバルクコンデンサの小型化

- EMI フィルタの小型化

- 位相管理機能

- 2つの経路を持つフェイルセーフ OVP により、電圧検出障害による出力過電圧状態を防止

- センサレス電流波形整形によるボードレイアウトの簡素化と効率の向上

- 先進の可聴ノイズ性能

- 非線形のエラー アンプ ゲイン

- 過電圧時のソフト回復

- ブラウンアウトおよびドロップアウト処理機能を内蔵

- 小さいバイアス電流

- 従来の単相連続導通モード (CCM) に比べて、効率と設計の柔軟性が向上

- 突入電流制限

- 突入電流時の MOSFET 導通を防止

- 出力整流器の逆方向回復動作を解消

- 大規模なスナバ回路を使わず、低コストのダイオードを使用可能

- 軽負荷時の効率向上

- 高速かつ滑らかな過渡応答

- 幅広いシステム レベル保護機能

- 1A ソース / 1.8A シンクのゲートドライバ

- -40°C~125°C の動作温度範囲、16 ピン SOIC パッケージ

## 2 アプリケーション

- 100W~800W 電源

- ゲーム

- D/A セットトップ ボックス

- アダプタ

- LCD、プラズマ、DLP™ テレビ

- ホーム オーディオ システム

## 3 概要

このソリューションは、可聴ノイズの除去が重要なコンシューマアプリケーション向けに最適化されており、遷移モードの利点(低成本の部品を使って高効率を実現)を、従来可能であった電力定格よりも高い電力定格まで拡張します。Natural Interleaving™ 手法を利用してすることで、両方のチャネルが同じ周波数に同期したマスタとして動作します(つまり、スレーブ チャネルは存在しません)。この手法を使うと、本質的に強力な整合性と高速な応答性を実現でき、各チャネルを遷移モードで確実に動作させることができます。

システム レベルの拡張保護機能には、入力ブラウンアウトおよびドロップアウト回復、出力過電圧、開ループ、過負荷、ソフトスタート、位相障害検出、サーマル シャットダウンがあります。さらにフェイルセーフ過電圧保護(OVP)機能により、検出されなければ壊滅的なデバイス破壊につながりかねない中間電圧への短絡を防止します。高度な非線形ゲインにより、ライン / 負荷過渡事象に対して迅速かつよりスムーズな応答を実現します。バイアス電流を低減することで、スタンバイ電力効率を向上させています。特殊なライン ドロップアウト処理により、大きな電流中断を回避し、可聴ノイズの発生を最小限に抑えています。

### 製品情報 (1)

| 部品番号     | パッケージ     | 本体サイズ(公称)         |

|----------|-----------|-------------------|

| UCC28063 | SOIC (16) | 9.90 mm × 3.91 mm |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあり、TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: SLUSA07

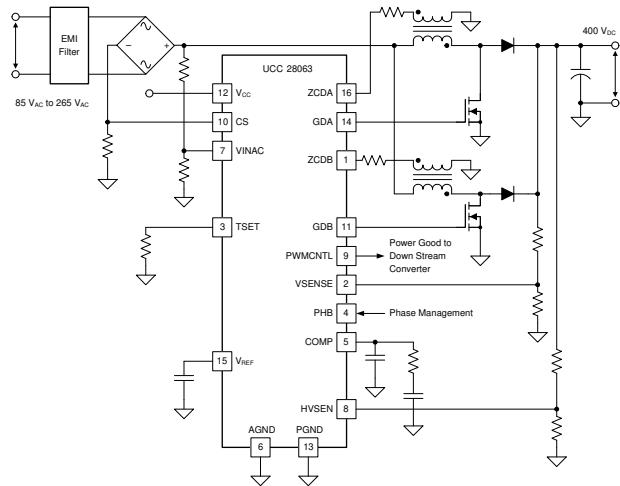

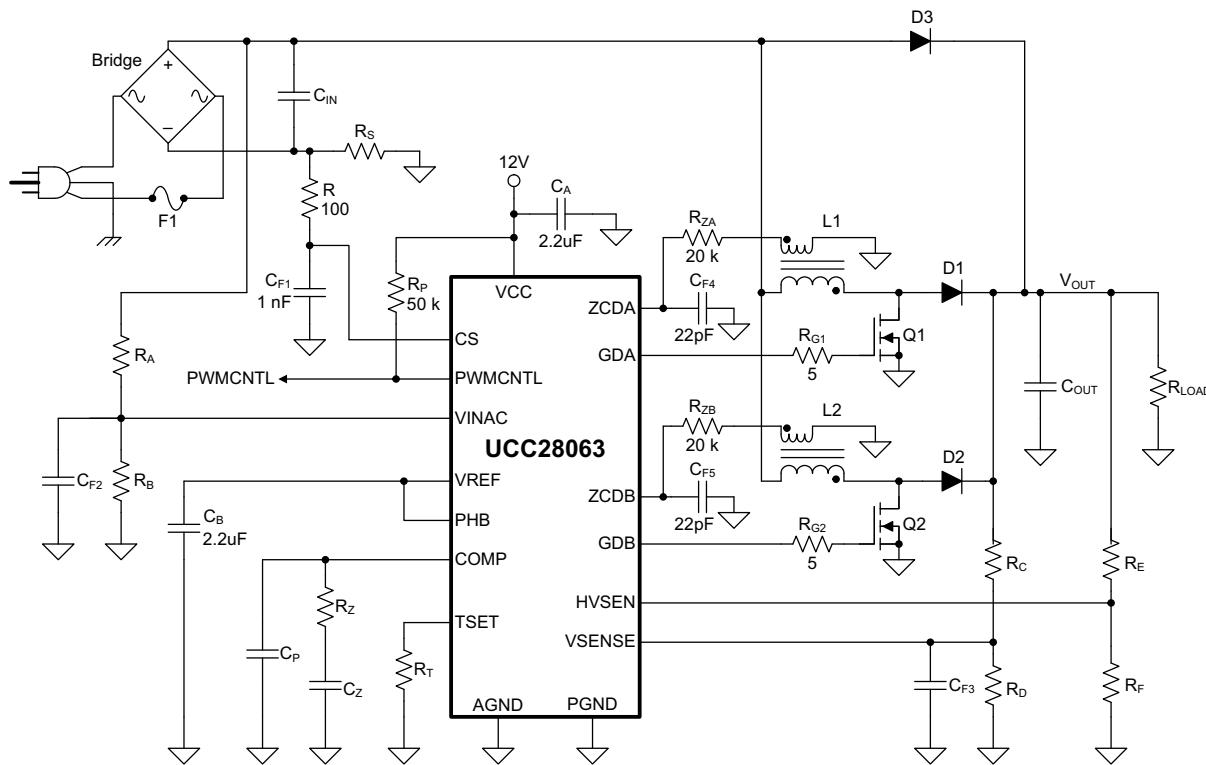

代表的なアプリケーションの図

インターリーブによる入力リップル電流の低減

## 目次

|                    |           |                               |           |

|--------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>        | <b>1</b>  | <b>7.4 デバイスの機能モード</b>         | <b>28</b> |

| <b>2 アプリケーション</b>  | <b>1</b>  | <b>8 アプリケーションと実装</b>          | <b>29</b> |

| <b>3 概要</b>        | <b>1</b>  | <b>8.1 アプリケーション情報</b>         | <b>29</b> |

| <b>4 改訂履歴</b>      | <b>3</b>  | <b>8.2 代表的なアプリケーション</b>       | <b>29</b> |

| <b>5 ピン構成および機能</b> | <b>4</b>  | <b>9 電源に関する推奨事項</b>           | <b>37</b> |

| <b>6 仕様</b>        | <b>5</b>  | <b>10 レイアウト</b>               | <b>38</b> |

| 6.1 絶対最大定格         | 5         | 10.1 レイアウトのガイドライン             | 38        |

| 6.2 ESD 定格         | 5         | 10.2 レイアウト例                   | 38        |

| 6.3 推奨動作条件         | 6         | <b>11 デバイスおよびドキュメントのサポート</b>  | <b>39</b> |

| 6.4 熱に関する情報        | 6         | 11.1 デバイス サポート                | 39        |

| 6.5 電気的特性          | 6         | 11.2 ドキュメントのサポート              | 41        |

| 6.6 代表的特性          | 11        | 11.3 商標                       | 41        |

| <b>7 詳細説明</b>      | <b>15</b> | 11.4 静電気放電に関する注意事項            | 41        |

| 7.1 概要             | 15        | 11.5 用語集                      | 41        |

| 7.2 機能ブロック図        | 16        | <b>12 メカニカル、パッケージ、および注文情報</b> | <b>41</b> |

| 7.3 機能説明           | 16        |                               |           |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <b>Changes from Revision B (November 2016) to Revision C (July 2024)</b> | <b>Page</b> |

|--------------------------------------------------------------------------|-------------|

| • ドキュメント全体にわたって表、図、相互参照の採番方法を更新。                                         | 1           |

| <b>Changes from Revision A (December 2014) to Revision B (November 2016)</b> | <b>Page</b> |

|------------------------------------------------------------------------------|-------------|

| • GDA、GDB の絶対最大定格を追加。                                                        | 5           |

| <b>Changes from Revision * (September 2011) to Revision A (July 2014)</b>                                                                                                  | <b>Page</b> |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| • 「ピン構成および機能」セクション、「取り扱いに関する定格」の表、「機能説明」セクション、「デバイスの機能モード」セクション、「アプリケーションと実装」セクション、「電源に関する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セクション、「メカニカル、パッケージ、および注文情報」セクションを追加。 | 1           |

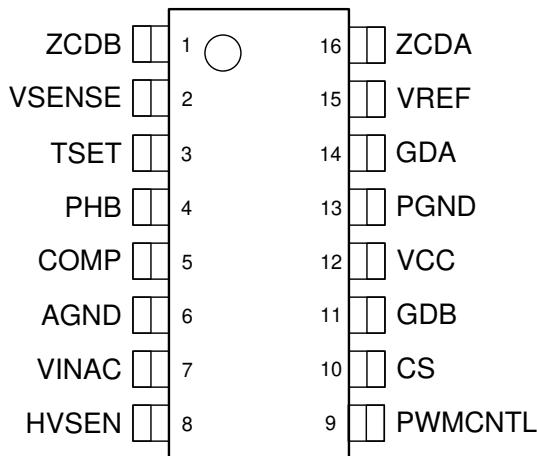

## 5 ピン構成および機能

図 5-1. D パッケージ 16 ピン SOIC 上面図

表 5-1. ピンの機能

| ピン      |    | I/O | 説明                      |

|---------|----|-----|-------------------------|

| 名称      | 番号 |     |                         |

| AGND    | 6  | -   | アナログ GND                |

| COMP    | 5  | O   | エラー アンプ出力               |

| CS      | 10 | I   | 電流検出入力                  |

| GDA     | 14 | O   | チャネル A とチャネル B のゲート駆動出力 |

| GDB     | 11 | O   |                         |

| HVSEN   | 8  | I   | 高電圧出力検出                 |

| PHB     | 4  | I   | 位相 B の有効化 / 無効化         |

| PWMCTRL | 9  | O   | PWM 制御出力                |

| TSET    | 3  | I   | タイミング設定                 |

| VCC     | 12 | -   | バイアス電源入力                |

| VINAC   | 7  | I   | 入力 AC 電圧検出              |

| VREF    | 15 | O   | 基準電圧出力                  |

| VSENSE  | 2  | I   | 出力 DC 電圧検出              |

| ZCDA    | 16 | I   |                         |

| ZCDB    | 1  | I   | ゼロ電流検出入力                |

## 6 仕様

### 6.1 絶対最大定格

特に記述のない限り、すべての電圧値は GND を基準にしており、 $-40^{\circ}\text{C} < T_J = T_A < 125^{\circ}\text{C}$  であり、電流は、指定されたピンに流れ込む方向が正、ピンから流れ出る方向が負です。

|                    |                                                                                            | 最小値  | 最大値     | 単位 |

|--------------------|--------------------------------------------------------------------------------------------|------|---------|----|

| 連続入力電圧範囲           | VCC <sup>(1)</sup>                                                                         | -0.5 | 21      | V  |

|                    | PWMCTL                                                                                     | -0.5 | 20      |    |

|                    | COMP <sup>(2)</sup> 、PHB、HVSEN <sup>(3)</sup> 、VINAC <sup>(3)</sup> 、VSENSE <sup>(3)</sup> | -0.5 | 7       |    |

|                    | ZCDA、ZCDB                                                                                  | -0.5 | 4       |    |

|                    | CS <sup>(4)</sup>                                                                          | -0.5 | 3       |    |

|                    | GDA、GDB <sup>(5)</sup>                                                                     | -0.5 | VCC+0.3 |    |

| 連続入力電流             | VCC                                                                                        |      | 20      | mA |

|                    | PWMCTL                                                                                     |      | 10      |    |

|                    | ZCDA、ZCDB                                                                                  |      | ±5      |    |

| ピーク入力電流            | CS                                                                                         |      | -30     |    |

| 出力電流               | VREF                                                                                       |      | -10     |    |

| 連続ゲート電流            | GDA、GDB <sup>(5)</sup>                                                                     |      | ±25     | °C |

| $T_J$<br>接合部温度     | 動作                                                                                         | -40  | 125     |    |

|                    | 保存                                                                                         | -65  | 150     |    |

| $T_{SOL}$<br>リード温度 | 10 秒間の半田付け                                                                                 |      | 260     |    |

| $T_{stg}$<br>保管温度  |                                                                                            | -40  | 125     |    |

- (1) VCC の電圧は内部でクランプされています。その電源が連続 VCC 入力電流レベルの絶対最大定格未満に電流制限されている場合、VCC は連続入力電圧の絶対最大定格を上回ることができます。

- (2) 通常の使用では、COMP はコンデンサと抵抗に接続されており、電圧スイングが内部的に制限されています。

- (3) 通常の使用では、VINAC、VSENSE、HVSEN は値の大きい抵抗に接続されており、負電圧スイング時に内部的に制限されます。長期間の使用は推奨しませんが、VINAC、VSENSE、HVSEN は、負の電圧源からの -10mA までの入力電流と、正の電圧源からの +0.5mA までの入力電流に耐えることができます。

- (4) 通常の使用では、短時間のシステムライン突入状態でのピーク入力電流を制限するため、CS には直列抵抗が接続されます。このような状況では、CS の負電圧は連続絶対最大定格を超えることができます。

- (5) パワー MOSFET のゲートを駆動する場合、GDA も GDB も電流制限は不要です。ただし、浮遊インダクタンスに起因する共振リングを減衰させるため、小さい値の直列抵抗が必要な場合があります。

### 6.2 ESD 定格

|                     |                                                         | 値     | 単位 |

|---------------------|---------------------------------------------------------|-------|----|

| $V_{(ESD)}$<br>静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>    | ±2000 | V  |

|                     | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠 <sup>(2)</sup> | ±500  |    |

- (1) JEDEC のドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

- (2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

## 6.3 推奨動作条件

特に記述のない限り、すべての電圧値は GND を基準にしており、 $-40^{\circ}\text{C} < T_J = T_A < 125^{\circ}\text{C}$  であり、電流は、指定されたピンに流れ込む方向が正、ピンから流れ出る方向が負です。

|                          | 最小値  | 最大値 | 単位 |

|--------------------------|------|-----|----|

| 低インピーダンスの電源からの VCC 入力電圧  | 14   | 21  | V  |

| 高インピーダンスの電源からの VCC 入力電流  | 8    | 18  | mA |

| VREF 負荷電流                | 0    | -2  |    |

| VINAC 入力電圧               | 0    | 6   | V  |

| ZCDA、ZCDB 直列抵抗           | 20   | 80  | kΩ |

| PWM オン時間を設定するための TSET 抵抗 | 66.5 | 400 |    |

| HVSEN 入力電圧               | 0.8  | 4.5 | V  |

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>        | UCC28063                         | 単位   |

|-----------------------------|----------------------------------|------|

|                             | SOIC (D)                         |      |

|                             | 16 ピン                            |      |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗 <sup>(2)</sup>      | °C/W |

| $R_{\theta JC(\text{top})}$ | 接合部からケース(上面)への熱抵抗 <sup>(3)</sup> |      |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗 <sup>(4)</sup>      |      |

| $\Psi_{JT}$                 | 接合部から上面への熱特性パラメータ <sup>(5)</sup> |      |

| $\Psi_{JB}$                 | 接合部から基板への熱特性パラメータ <sup>(6)</sup> |      |

|                             |                                  |      |

- (1) 従来および新しい熱評価基準値の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション・レポート (SPRA953) を参照してください。

- (2) 自然対流における、接合部と周囲の空気との間の熱抵抗は、JESD51-2a に記述されている環境において、JESD51-7 で規定されている JEDEC 標準の High-K ボード上でのシミュレーションによって求められます。

- (3) 接合部とケース(上面)との間の熱抵抗は、パッケージ上面での冷却板試験のシミュレーションによって求められます。JEDEC 規格試験では規定されていませんが、ANSI が策定した SEMI 規格の G30-88 に類似した記述があります。

- (4) 接合部と基板との間の熱抵抗は JESD51-8 で説明されているように、PCB 温度を制御するリング型冷却板治具で環境をシミュレーションすることにより求められます。

- (5) 接合部とケース上部との間の特性パラメータ  $\Psi_{JT}$  は、実際のシステムにおけるデバイスの接合部温度を推定するもので、JESD51-2a (セクション 6 および 7) に記述されている手順を用いて、 $R_{\theta JA}$  を求めるためのシミュレーションデータから抽出されます。

- (6) 接合部と基板との間の特性パラメータ  $\Psi_{JB}$  は、実際のシステムにおけるデバイスの接合部温度を推定するもので、JESD51-2a (セクション 6 および 7) に記述されている手順を用いて、 $R_{\theta JA}$  を求めるためのシミュレーションデータから抽出されます。

## 6.5 電気的特性

特に記述のない限り、 $VCC = 16\text{V}$ 、 $AGND = PGND = 0\text{V}$ 、 $VINAC = 3\text{V}$ 、 $VSENSE = 6\text{V}$ 、 $HVSEN = 3\text{V}$ 、 $PHB = 5\text{V}$ 、 $R_{TSET} = 133\text{k}\Omega$ 、すべての電圧値は GND を基準にしており、すべての出力は無負荷、 $-40^{\circ}\text{C} < T_J = T_A < 125^{\circ}\text{C}$  であり、電流は、指定されたピンに流れ込む方向が正、そのピンから流れ出る方向が負です。

| パラメータ                  | テスト条件                       | 最小値                            | 代表値  | 最大値   | 単位            |

|------------------------|-----------------------------|--------------------------------|------|-------|---------------|

| <b>VCC バイアス電源</b>      |                             |                                |      |       |               |

| $VCC_{\text{SHUNT}}$   | $VCC$ シャント電圧 <sup>(1)</sup> | $I_{VCC} = 10\text{mA}$        | 22   | 24    | V             |

| $I_{VCC(\text{ULVO})}$ | $VCC$ 電流、UVLO               | $VCC = 11.4\text{V}$ (ターンオンの前) | 95   | 200   | $\mu\text{A}$ |

| $I_{VCC(\text{stby})}$ | $VCC$ 電流、ディセーブル             | $VSENSE = 0\text{V}$           | 100  | 200   |               |

| $I_{VCC(\text{on})}$   | $VCC$ 電流、イネーブル              | $VSENSE = 2\text{V}$           | 5    | 8     |               |

| <b>低電圧誤動作防止 (UVLO)</b> |                             |                                |      |       |               |

| $VCC_{\text{ON}}$      | $VCC$ ターンオン スレッショルド         | $VCC$ 立ち上がり                    | 11.5 | 12.6  | 13.5          |

| $VCC_{\text{OFF}}$     | $VCC$ ターンオフ スレッショルド         | $VCC$ 立ち下がり                    | 9.5  | 10.35 | 11.5          |

|                        | UVLO ヒステリシス                 |                                | 1.85 | 2.15  | 2.45          |

## 6.5 電気的特性 (続き)

特に記述のない限り、 $V_{CC} = 16V$ 、 $AGND = PGND = 0V$ 、 $VINAC = 3V$ 、 $VSENSE = 6V$ 、 $HVSEN = 3V$ 、 $PHB = 5V$ 、 $R_{TSET} = 133k\Omega$ 、すべての電圧値は GND を基準にしており、すべての出力は無負荷、 $-40^\circ C < T_J = T_A < 125^\circ C$  であり、電流は、指定されたビンに流れ込む方向が正、そのビンから流れ出る方向が負です。

| パラメータ            | テスト条件                                                                                | 最小値                                                                                                | 代表値             | 最大値              | 単位           |

|------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------|------------------|--------------|

| <b>リファレンス</b>    |                                                                                      |                                                                                                    |                 |                  |              |

| $V_{REF}$        | $V_{REF}$ 出力電圧、無負荷<br>負荷による $V_{REF}$ の変化<br>$V_{CC}$ による $V_{REF}$ の変化              | $I_{VREF} = 0mA$<br>$0mA \leq I_{VREF} \leq -2mA$<br>$12V \leq V_{CC} \leq 20V$                    | 5.82<br>-1<br>2 | 6.00<br>-6<br>10 | V<br>mV      |

| <b>エラーアンプ</b>    |                                                                                      |                                                                                                    |                 |                  |              |

| $VSENSE_{reg25}$ | $VSENSE$ 入力レギュレーション電圧                                                                | $T_A = 25^\circ C$                                                                                 | 5.85            | 6                | 6.15         |

| $VSENSE_{reg}$   | $VSENSE$ 入力レギュレーション電圧                                                                |                                                                                                    | 5.82            | 6                | 6.18         |

| $I_{VSENSE}$     | $VSENSE$ 入力バイアス電流                                                                    | レギュレーション中                                                                                          | 50              | 100              | 150          |

| $V_{ENAB}$       | $VSENSE$ イネーブル スレッショルド、立ち上がり<br>$VSENSE$ イネーブル ヒステリシス                                |                                                                                                    | 1.15<br>0.02    | 1.25<br>0.07     | 1.35<br>0.15 |

| $V_{COMPCLMP}$   | COMP 高電圧、クランプ<br>COMP Low 電圧、飽和                                                      | $VSENSE = VSENSE_{reg} - 0.3V$<br>$VSENSE = VSENSE_{reg} + 0.3V$                                   | 4.70<br>0.03    | 4.95<br>0.125    | V            |

| $g_M$            | $VSENSE$ - COMP トランスクンダクタンス、小信号<br>COMP の大信号ゲインを有効化するための $VSENSE$ 立ち上がりスレッショルド、パーセント | $0.99(VSENSE_{reg}) < VSENSE < 1.01(VSENSE_{reg})$ , COMP = 3V<br>$VSENSE_{reg}$ に対する相対値、COMP = 3V | 40<br>3.25%     | 55<br>5%         | 70<br>6.75%  |

|                  | COMP の大信号ゲインを有効化するための $VSENSE$ 立ち下がりスレッショルド、パーセント                                    | $VSENSE_{reg}$ に対する相対値、COMP = 3V                                                                   | -3.25%          | -5%              | -6.75%       |

|                  | $VSENSE$ - COMP トランスクンダクタンス、大信号                                                      | $VSENSE = VSENSE_{reg} - 0.4V$ , COMP = 3V                                                         | 210             | 290              | 370          |

|                  | $VSENSE$ - COMP トランスクンダクタンス、大信号                                                      | $VSENSE = VSENSE_{reg} + 0.4V$ , COMP = 3V                                                         | 210             | 290              | 370          |

|                  | COMP 最大ソース電流                                                                         | $VSENSE = 5V$ , COMP = 3V                                                                          | -80             | -125             | -170         |

| $R_{COMPDCHG}$   | COMP 放電抵抗                                                                            | $HVSEN = 5.2V$ , COMP = 3V                                                                         | 1.6             | 2                | 2.4          |

| $I_{DODCHG}$     | ドロップアウト時の COMP 放電電流                                                                  | $VSENSE = 5V$ , $VINAC = 0.3V$                                                                     | 3.2             | 4                | 4.8          |

| $V_{LOW\_OV}$    | $VSENSE$ 過電圧スレッショルド、立ち上がり<br>$VSENSE$ 過電圧ヒステリシス                                      | $VSENSE_{reg}$ に対する相対値<br>$V_{LOW\_OV}$ に対する相対値                                                    | 7%<br>-1.5%     | 8%<br>-2%        | 10%<br>-3%   |

| $V_{HIGH\_OV}$   | $VSENSE$ 第 2 過電圧スレッショルド、立ち上がり                                                        | $VSENSE_{reg}$ に対する相対値                                                                             | 10.5%           | 11.3%            | 14%          |

| <b>ソフトスタート</b>   |                                                                                      |                                                                                                    |                 |                  |              |

| $V_{SSTHR}$      | COMP ソフトスタート スレッショルド、立ち下がり                                                           | $VSENSE = 1.5 V$                                                                                   | 15              | 23               | 30           |

| $I_{SS,FAST}$    | COMP ソフトスタート電流、高速                                                                    | ソフトスタート状態、 $V_{ENAB} < VSENSE < VREF/2$                                                            | -80             | -125             | -170         |

| $I_{SS,SLOW}$    | COMP ソフトスタート電流、低速                                                                    | ソフトスタート状態、 $VREF/2 < VSENSE < 0.88VREF$                                                            | -11.5           | -16              | -20          |

| $K_{EOSS}$       | $VSENSE$ ソフトスタート終了スレッショルド係数                                                          | $VSENSE_{reg}$ のパーセント                                                                              | 96.5%           | 98.3%            | 99.8%        |

| <b>出力監視</b>      |                                                                                      |                                                                                                    |                 |                  |              |

## 6.5 電気的特性 (続き)

特に記述のない限り、 $V_{CC} = 16V$ 、 $AGND = PGND = 0V$ 、 $VINAC = 3V$ 、 $VSENSE = 6V$ 、 $HVSEN = 3V$ 、 $PHB = 5V$ 、 $R_{TSET} = 133k\Omega$ 、すべての電圧値は GND を基準にしており、すべての出力は無負荷、 $-40^\circ C < T_J = T_A < 125^\circ C$  であり、電流は、指定されたピンに流れ込む方向が正、そのピンから流れ出る方向が負です。

| パラメータ                          | テスト条件                                             | 最小値                                               | 代表値        | 最大値       | 単位       |

|--------------------------------|---------------------------------------------------|---------------------------------------------------|------------|-----------|----------|

| $V_{PWMCNTL}$                  | PWMCNTL の HVSEN スレッショルド                           | HVSEN 立ち上がり                                       | 2.35       | 2.50      | 2.65     |

| $I_{HVSEN}$                    | HVSEN 入力バイアス電流、High                               | $HVSEN = 3V$                                      | $\pm 0.03$ | $\pm 0.5$ | $\mu A$  |

| $I_{HV\_HYS}$                  | HVSEN ヒステリシス バイアス電流、Low                           | $HVSEN = 2V$                                      | 9.2        | 11.4      | 14       |

| $V_{HV\_OV\_FLT}$              | 過電圧フォルトの HVSEN スレッショルド                            | HVSEN 立ち上がり                                       | 4.64       | 4.87      | 5.1      |

| $V_{HV\_OV\_CLR}$              | 過電圧クリアの HVSEN スレッショルド                             | HVSEN 立ち下がり                                       | 4.45       | 4.67      | 4.8      |

| $V_{COMP\_PHFOFF}$             | 位相障害監視無効化スレッショルド                                  | COMP 立ち下がり                                        | 0.21       | 0.225     | 0.25     |

| $V_{COMP\_PHFHYS}$             | 位相障害監視ヒステリシス                                      | COMP 立ち上がり                                        | 0.051      | 0.2       | $V$      |

| PWMCNTL 出力電圧 Low               | $HVSEN = 3V$ 、 $I_{PWMCNTL} = 5mA$ 、 $COMP = 0V$  |                                                   |            |           |          |

| $t_{PHFDLY}$                   | PWMCNTL High までの位相障害 フィルタ時間                       | $PHB = 5V$ 、ZCDA スイッチング、<br>ZCDB = 0.5V、COMP = 3V | 7.9        | 12        | 17       |

| $I_{PWMCNTL\_LEAK}$            | PWMCNTL リーク電流、High                                | $HVSEN = 2V$ 、PWMCNTL = 15V                       | $\pm 0.03$ | $\pm 0.5$ | $\mu A$  |

| <b>ゲート駆動 (2)</b>               |                                                   |                                                   |            |           |          |

| GDA、GDB 出力電圧、High              | $I_{GDA}, I_{GDB} = -100mA$                       | 11.5                                              | 12.4       | 15        | $V$      |

| GDA、GDB オン抵抗、High              | $I_{GDA}, I_{GDB} = -100mA$                       | 8.8                                               | 14         | $\Omega$  | $V$      |

| GDA、GDB 出力電圧、Low               | $I_{GDA}, I_{GDB} = 100mA$                        |                                                   |            |           |          |

| GDA、GDB オン抵抗、Low               | $I_{GDA}, I_{GDB} = 100mA$                        | 0.18                                              | 0.32       | $V$       | $\Omega$ |

| GDA、GDB 出力電圧 High、クランプ         | $VCC = 20V$ 、 $I_{GDA}, I_{GDB} = -5mA$           |                                                   |            |           |          |

| GDA、GDB 出力電圧 High、Low VCC      | $VCC = 12V$ 、 $I_{GDA}, I_{GDB} = -5mA$           | 12                                                | 13.5       | 15        | $V$      |

| 立ち上がり時間                        | $1V$ から $9V$ まで、 $C_{LOAD} = 1nF$                 | 10                                                | 10.5       | 11.5      |          |

| 立ち下がり時間                        | $9V$ から $1V$ まで、 $C_{LOAD} = 1nF$                 |                                                   |            | $ns$      |          |

| GDA、GDB 出力電圧、UVLO              | $VCC = 3.0V$ 、 $I_{GDA}, I_{GDB} = 2.5mA$         | 100                                               | 200        |           | 200      |

| <b>ゼロ電流検出器</b>                 |                                                   |                                                   |            |           |          |

| ZCDA、ZCDB 電圧スレッショルド、立ち下がり      |                                                   | 0.8                                               | 1          | 1.2       | $V$      |

| ZCDA、ZCDB 電圧スレッショルド、立ち上がり      |                                                   | 1.5                                               | 1.7        | 1.9       |          |

| ZCDA、ZCDB クランプ、High            | $I_{ZCDA} = +2mA$ 、 $I_{ZCDB} = +2mA$             | 2.6                                               | 3          | 3.4       | $ns$     |

| ZCDA、ZCDB クランプ、Low             | $I_{ZCDA} = -2mA$ 、 $I_{ZCDB} = -2mA$             | 0                                                 | -0.2       | -0.4      |          |

| ZCDA、ZCDB 入力バイアス電流             | $ZCDA = 1.4V$ 、 $ZCDB = 1.4V$                     | $\pm 0.03$                                        | $\pm 0.5$  | $\mu A$   | $ns$     |

| GDA、GDB 出力までの ZCDA、ZCDB 遅延 (2) | ZCDx 入力の立ち下がり (1V) から、対応する ゲート駆動出力の立ち上がり (10%) まで | 50                                                | 100        |           |          |

| ZCDA ブランкиング時間 (3)             | GDA 立ち上がりおよび GDA 立ち下がりから                          | 100                                               |            |           |          |

| ZCDB ブランкиング時間 (3)             | GDB 立ち上がりおよび GDB 立ち下がりから                          | 100                                               |            |           |          |

| <b>電流検出</b>                    |                                                   |                                                   |            |           |          |

| CS 入力バイアス電流、2 相                | 立ち上がりスレッショルド時                                     | -120                                              | -166       | -200      | $\mu A$  |

## 6.5 電気的特性 (続き)

特に記述のない限り、 $V_{CC} = 16V$ 、 $AGND = PGND = 0V$ 、 $VINAC = 3V$ 、 $VSENSE = 6V$ 、 $HVSEN = 3V$ 、 $PHB = 5V$ 、 $R_{TSET} = 133k\Omega$ 、すべての電圧値は GND を基準にしており、すべての出力は無負荷、 $-40^\circ C < T_J = T_A < 125^\circ C$  であり、電流は、指定されたピンに流れ込む方向が正、そのピンから流れ出る方向が負です。

| パラメータ                      | テスト条件                                          | 最小値    | 代表値    | 最大値    | 単位 |

|----------------------------|------------------------------------------------|--------|--------|--------|----|

| CS 電流制限立ち上がりスレッショルド、2 相    | $PHB = 5 V$                                    | -0.18  | -0.2   | -0.22  | V  |

| CS 電流制限立ち上がりスレッショルド、単相     | $PHB = 0 V$                                    | -0.149 | -0.166 | -0.183 |    |

| CS 電流制限リセット立ち下がりスレッショルド    |                                                | -0.003 | -0.015 | -0.025 |    |

| CS 電流制限応答時間 <sup>(2)</sup> | CS が (スレッショルド - 0.05V) を超えてから GDx が 10% 低下するまで | 60     | 100    | 100    |    |

| CS ブランкиング時間               | GDx の立ち上がりおよび立ち下がりエッジから                        | 100    |        |        |    |

### VINAC 入力

|             |                              |                                                   |            |           |         |

|-------------|------------------------------|---------------------------------------------------|------------|-----------|---------|

| $I_{VINAC}$ | VINAC 入力バイアス電流、プラウアウトの上      | $VINAC = 2 V$                                     | $\pm 0.03$ | $\pm 0.5$ | $\mu A$ |

| $V_{BODET}$ | VINAC ブラウンアウト検出スレッショルド       | VINAC 立ち下がり                                       | 1.33       | 1.39      | 1.44    |

| $t_{BODYL}$ | VINAC ブラウンアウト フィルタ時間         | ブラウンアウト フィルタ時間の間、VINAC はブラウンアウト検出スレッショルドを下回っています。 | 340        | 440       | 540     |

| $V_{BOHYS}$ | VINAC ブラウンアウト スレッショルドのヒステリシス | VINAC 立ち上がり                                       | 30         | 62        | 75      |

| $I_{BOHYS}$ | VINAC ブラウンアウト ヒステリシス電流       | $t_{BODYL}$ より長い間、 $VINAC = 1V$                   | 1.6        | 2         | 2.5     |

| $V_{DODET}$ | VINAC ドロップアウト検出スレッショルド       | VINAC 立ち下がり                                       | 0.315      | 0.35      | 0.38    |

| $t_{DODLY}$ | VINAC ドロップアウト フィルタ時間         | ドロップアウト フィルタ時間の間、VINAC はドロップアウト検出スレッショルドを下回っています。 | 3.5        | 5         | 7       |

| $V_{DOCLR}$ | VINAC ドロップアウト クリア スレッショルド    | VINAC 立ち上がり                                       | 0.67       | 0.71      | 0.75    |

### パルス幅変調器

|                      |                              |                                             |           |     |           |           |

|----------------------|------------------------------|---------------------------------------------|-----------|-----|-----------|-----------|

| $K_T$                | オン時間係数、位相 A および B            | $VSENSE = 5.8V$ <sup>(4)</sup>              | 3.6       | 4.0 | 4.4       | $\mu s/V$ |

| $K_{TS}$             | オン時間係数、単相、A                  | $VSENSE = 5.8V$ 、 $PHB = 0V$ <sup>(4)</sup> | 7.2       | 8.0 | 8.9       |           |

| 位相 B と位相 A のオン時間一致誤差 |                              | $VSENSE = 5.8 V$                            | $\pm 2\%$ |     | $\pm 6\%$ |           |

| ゼロクロス歪み補正による追加オン時間   | COMP = 0.25V、 $VINAC = 1V$   | 1.2                                         | 2         | 2.8 | $\mu s$   |           |

|                      | COMP = 0.25V、 $VINAC = 0.1V$ | 12.6                                        | 20        | 29  |           |           |

| $V_{PHBF}$           | PHB スレッショルド立ち下がり、単相動作まで      | GDB 出力シャットダウンまで、 $VINAC = 1.5V$             | 0.7       | 0.8 | 0.9       | V         |

| $V_{PHBR}$           | PHB スレッショルド立ち上がり、2 相動作まで     | GDB 出力動作まで、 $VINAC = 1.5V$                  | 0.9       | 1   | 1.1       |           |

| $T_{MIN}$            | 最小スイッチング周期                   | $R_{TSET} = 133k\Omega$ <sup>(4)</sup>      | 1.7       | 2.2 | 3         | $\mu s$   |

| $T_{START}$          | PWM 再起動時間                    | $ZCDA = ZCDB = 2V$ <sup>(5)</sup>           | 165       | 210 | 265       |           |

| サーマル シャットダウン         |                              |                                             |           |     |           |           |

## 6.5 電気的特性 (続き)

特に記述のない限り、 $V_{CC} = 16V$ 、 $AGND = PGND = 0V$ 、 $V_{INAC} = 3V$ 、 $V_{SENSE} = 6V$ 、 $HVSEN = 3V$ 、 $PHB = 5V$ 、 $R_{TSET} = 133k\Omega$ 、すべての電圧値は GND を基準にしており、すべての出力は無負荷、 $-40^\circ C < T_J = T_A < 125^\circ C$  であり、電流は、指定されたピンに流れ込む方向が正、そのピンから流れ出る方向が負です。

| パラメータ                   | テスト条件               | 最小値 | 代表値 | 最大値 | 単位 |

|-------------------------|---------------------|-----|-----|-----|----|

| $T_J$<br>サーマル シャットダウン温度 | 温度上昇 <sup>(6)</sup> |     | 160 |     |    |

| $T_J$<br>サーマル リスタート温度   | 温度低下 <sup>(6)</sup> |     | 140 |     | °C |

- (1) 過剰な  $V_{CC}$  入力電圧および電流は本デバイスを損傷させます。このクランプは、レギュレートされていないバイアス電源から本デバイスを保護することはありません。レギュレートされていないバイアス電源を使う場合、UA78L15A などの直列接続の固定正電圧レギュレータを使うことを推奨します。 $V_{CC}$  の電圧、電流、接合部温度の制限値については、「絶対最大定格」表を参照してください。

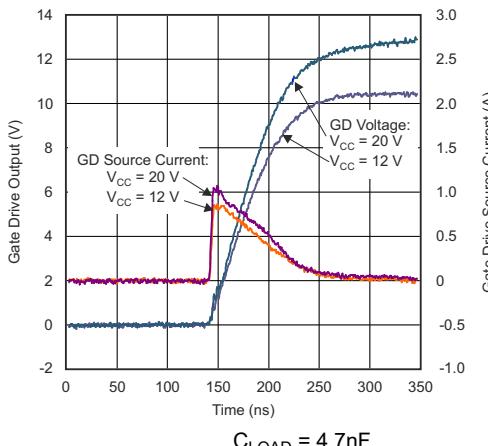

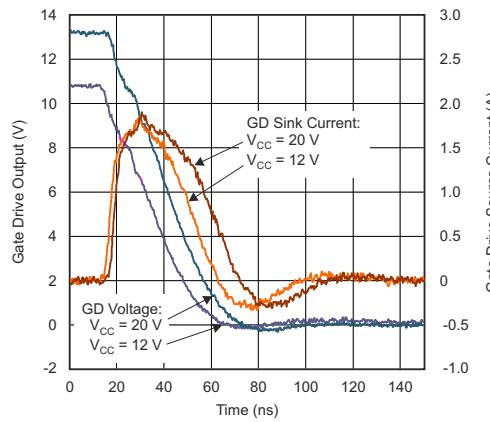

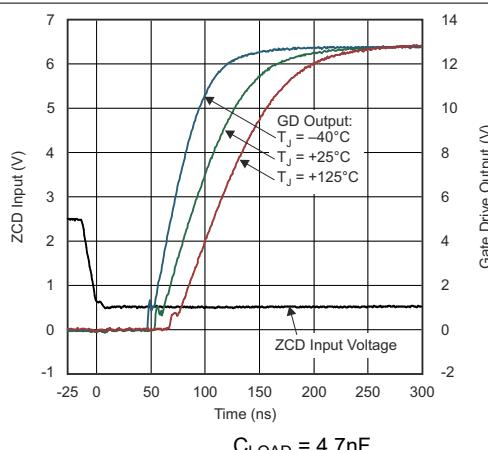

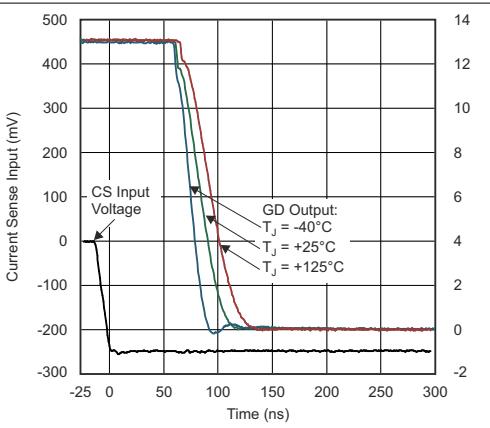

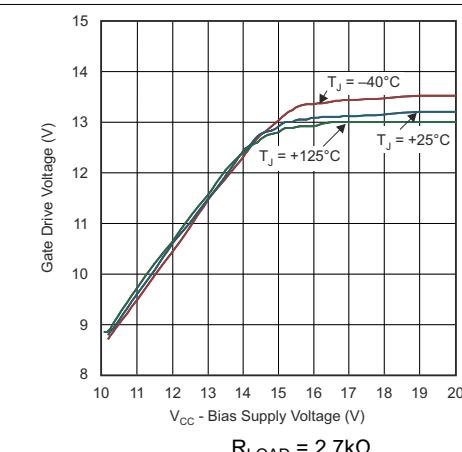

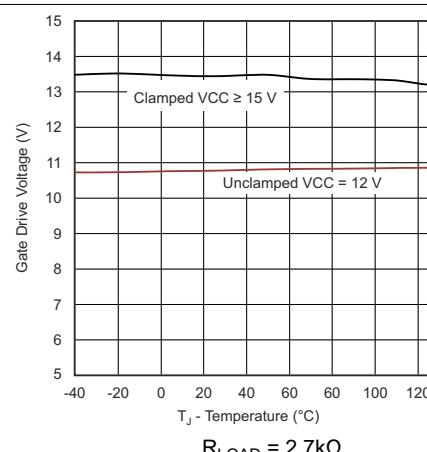

- (2) 代表的なゲート駆動波形については、「代表的特性」の [図 6-13](#)、[図 6-14](#)、[図 6-15](#)、[図 6-16](#) を参照してください。

- (3) ZCD ブランкиング時間は設計により保証されています。

- (4) ゲート駆動オン時間は ( $V_{COMP} - 0.125V$ ) に比例します。オン時間比例係数  $K_T$  は、 $R_{TSET}$  値で直線的にスケーリングされ、2 相モードと単相モードでは異なります。スイッチング周期の最小値は  $R_{TSET}$  に比例します。

- (5) ZCDA と ZCDB の両方の立ち下がりエッジが再起動時間の間検出されない場合、GDA と GDB の両方で出力オン時間が生成されます。単相モードでは、ZCDA 入力と GDA 出力に再起動時間が適用されます。

- (6) 通常の動作範囲より高い温度では、サーマル シャットダウンが作動します。通常動作温度を上回る温度でのデバイス性能は、規定も保証もされていません。

## 6.6 代表的特性

特に記述のない限り、 $V_{CC} = 16V$ 、 $AGND = PGND = 0V$ 、 $V_{INAC} = 3V$ 、 $V_{SENSE} = 6V$ 、 $HVSEN = 3V$ 、 $PHB = 5V$ 、 $R_{TSET} = 133k\Omega$ 、すべての電圧値は GND を基準にしており、すべての出力は無負荷、 $T_J = T_A = +25^{\circ}\text{C}$ であり、電流は、指定されたピンに流れ込む方向が正、そのピンから流れ出る方向が負です。

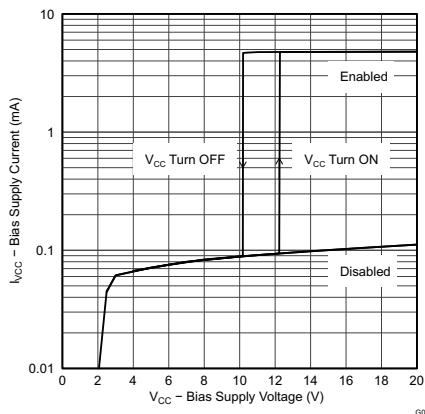

図 6-1. バイアス電源電流とバイアス電源電圧との関係

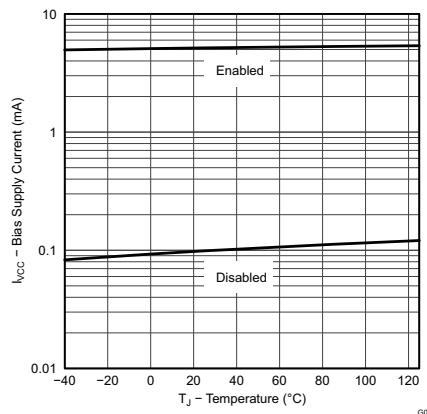

図 6-2. バイアス電源電流と温度との関係

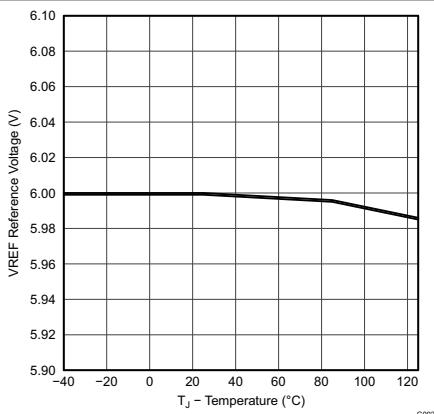

図 6-3. 基準電圧と温度との関係

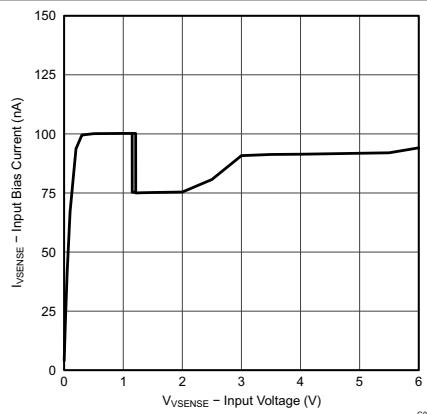

図 6-4. VSENSE の入力バイアス電流と入力電圧との関係

ソフトスタート完了

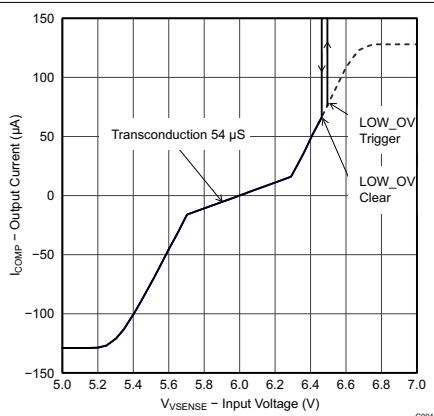

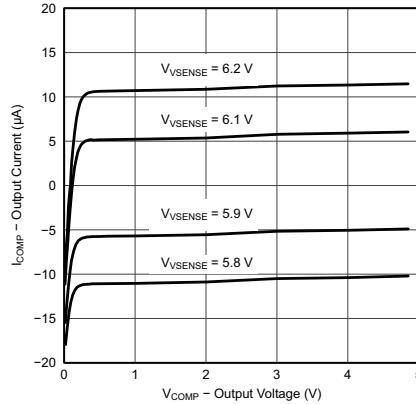

図 6-5. エラー アンプの出力電流と入力電圧との関係

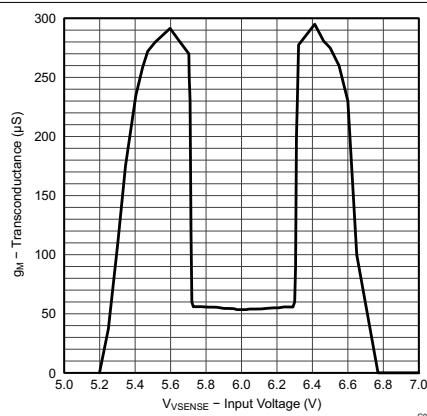

図 6-6. エラー アンプのトランスクンダクタンスと VSENSE との関係

## 6.6 代表的特性 (続き)

特に記述のない限り、 $V_{CC} = 16V$ 、 $AGND = PGND = 0V$ 、 $V_{INAC} = 3V$ 、 $V_{SENSE} = 6V$ 、 $HVSEN = 3V$ 、 $PHB = 5V$ 、 $R_{TSET} = 133k\Omega$ 、すべての電圧値は GND を基準にしており、すべての出力は無負荷、 $T_J = T_A = +25^{\circ}\text{C}$ であり、電流は、指定されたピンに流れ込む方向が正、そのピンから流れ出る方向が負です。

5.9V <  $V_{SENSE}$  < 6.1V

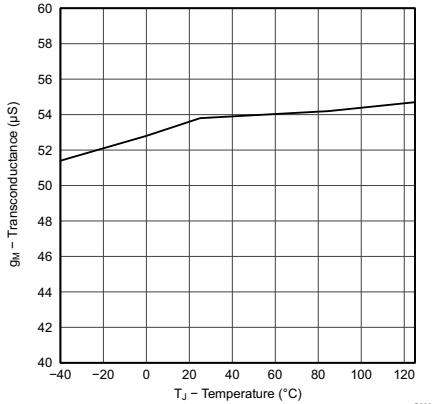

図 6-7. エラー アンプのトランスクンダクタンスと温度との関係

図 6-8. エラー アンプの出力電流と出力電圧との関係

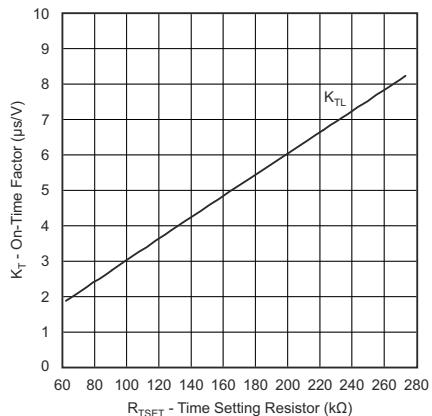

図 6-9. オン時間係数と時間設定抵抗との関係

図 6-10. オン時間係数(位相 A および B)と温度との関係

$$K_{TO} = \frac{2(K_{TA} \times K_{TB})}{K_{TA} + K_{TB}}$$

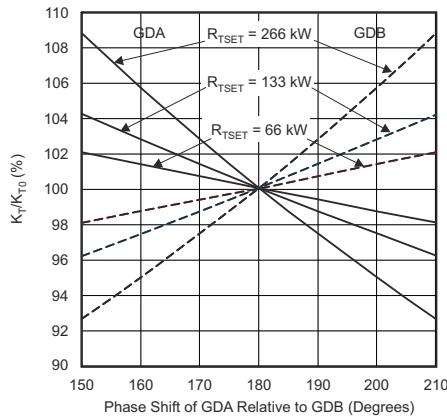

図 6-11. オン時間係数と位相誤差との関係

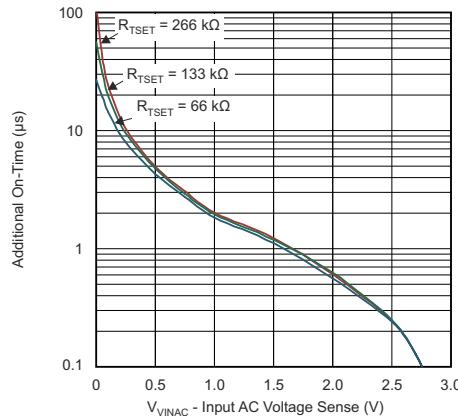

図 6-12. 追加オン時間と VINAC との関係

## 6.6 代表的特性 (続き)

特に記述のない限り、 $V_{CC} = 16V$ 、 $AGND = PGND = 0V$ 、 $V_{INAC} = 3V$ 、 $V_{SENSE} = 6V$ 、 $HVSEN = 3V$ 、 $PHB = 5V$ 、 $R_{TSET} = 133k\Omega$ 、すべての電圧値は GND を基準にしており、すべての出力は無負荷、 $T_J = T_A = +25^\circ C$  であり、電流は、指定されたピンに流れ込む方向が正、そのピンから流れ出る方向が負です。

図 6-13. ゲート駆動立ち上がりと時間との関係

図 6-14. ゲート駆動立ち下りと時間との関係

図 6-15. ゲート駆動立ち上がり / ZCD 入力からの遅延と時間との関係

図 6-16. ゲート駆動立ち下り / CS 入力からの遅延と時間との関係

図 6-17. ゲート駆動出力 High と VCC との関係

図 6-18. ゲート駆動 High 電圧と温度との関係

## 6.6 代表的特性 (続き)

特に記述のない限り、 $V_{CC} = 16V$ 、 $AGND = PGND = 0V$ 、 $V_{INAC} = 3V$ 、 $V_{SENSE} = 6V$ 、 $HVSEN = 3V$ 、 $PHB = 5V$ 、 $R_{TSET} = 133k\Omega$ 、すべての電圧値は GND を基準にしており、すべての出力は無負荷、 $T_J = T_A = +25^{\circ}\text{C}$  であり、電流は、指定されたピンに流れ込む方向が正、そのピンから流れ出る方向が負です。

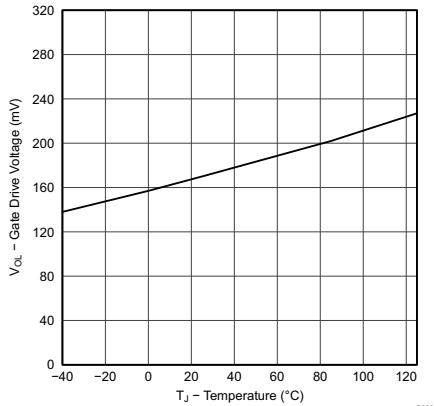

負荷 = 100mA

図 6-19. ゲート駆動 Low 電圧と温度との関係

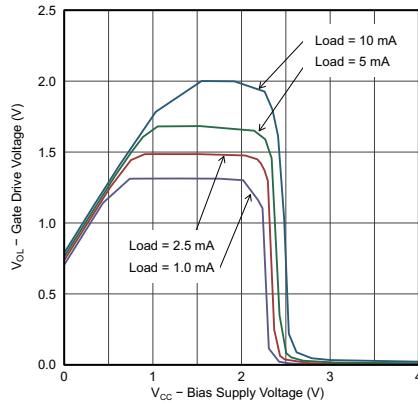

図 6-20. ゲート駆動 Low 電圧 (UVLO 時) とバイアス電源電圧との関係

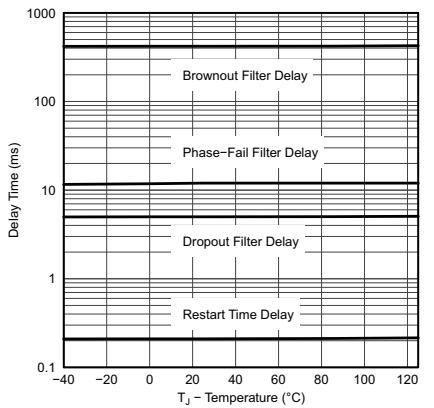

図 6-21. 各種遅延時間と温度との関係

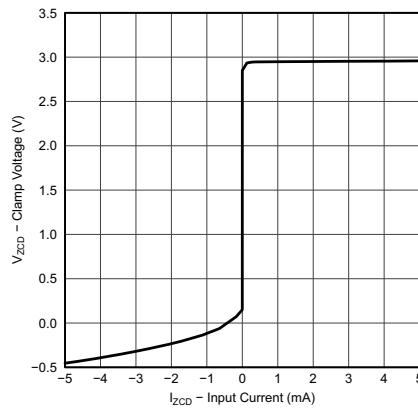

図 6-22. ゼロ電流検出クランプ電圧と入力電流との関係

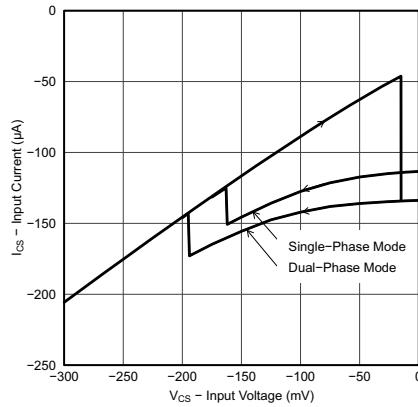

$V_{CS} = -195\text{mV}$

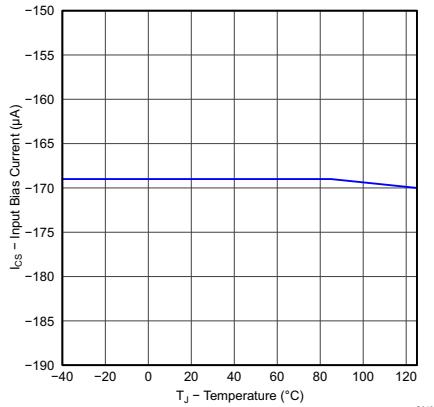

図 6-23. 電流検出入力バイアス電流と温度との関係

図 6-24. 電流検出入力バイアス電流と入力電圧との関係

## 7 詳細説明

### 7.1 概要

遷移モード制御は、単純な構成で高い効率を実現できると同時に、電力部品の仕様に厳しい要件を課さないため、低電力レベルの昇圧率補正方式として最も一般的な選択肢です。遷移モード昇圧では、たとえば、逆回復電流の仕様値がより大きい、より低成本の昇圧ダイオードを使用できます。インターリーブ遷移モード制御は、この利点はそのままにして、通常はより高い電力レベルまで適用できると同時に、入力および出力リップルの低減、位相管理による軽負荷効率向上、冗長性、システムの熱的最適化、低プロファイルまたは平面型ソリューションというインターリーブの利点をもたらします。

UCC28063 を使用すると、音響管理や高速過渡応答などの分野での耐久性、障害管理、障害回復、効率、より高い最終製品性能を特に重視した非常にコスト効率の高いソリューションを実現できます。本製品は、強化された新世代の UCC28061 と見なすことができます。

インターリーブ制御と位相管理は、80+ および Energy Star 設計と入出力リップルの低減を容易にします。Natural Interleaving 方式を使うと、TM 動作が可能であり、インダクタの厳しい許容誤差要件に頼らずに、オン時間管理によって相間 180 度を実現できます。歪みを低減し、効率を向上させるため、クロスオーバー ノッチ低減ブロックは瞬時電圧検出機能 (VINAC) に非線形電流成形特性を実装しています。突入サーボ中、またはインダクタ電流が実質的に連続的 (CCM) になり得るすべてのモードで MOSFET のスイッチングを防止する負電流検出機能が、MOSFET 電流だけではなく、総入力電流に対して、実装されています。これにより、MOSFET と出力整流器の間の逆回復導通イベントが防止されます。PWMCNTL 信号により、ダウンストリーム電力段管理を容易に行うことができます。PFC 段電圧が動作スレッショルドを上回っており、フェイルセーフ OV 保護が動作しておらず、位相障害フォルトが発生していない場合、このオープンドレイン信号は、ダウンストリーム コンバータのためのヒステリシス付きイネーブルとして機能します。

独立した出力電圧検出チェーンと、それらの独立したフォルト管理動作は、PFC 段の過電圧に対して高い冗長性を実現します。ブラウンアウト、HVSENSE OV、UVLO、TSET のオープン / フォルト検出、CS のオープン、IC 過熱はすべて、完全ソフトスタート サイクルの原因となります。その他のフォルト (短時間の AC ドロップアウト、軽微な過電圧、サイクル単位の過電流など) は、COMP ピンをプルダウンし、またはパルスを早期に終了させることでライブ回復プロセスを開始させる原因となります。

一般に、IC 動作は、滑らかで音響ノイズを発生させない起動、優れた過渡応答動作、障害からの適切な回復が確実に行われるよう設計されています。エラー アンプのトランスコンダクタンスは、より小さな補償部品が使えるように、またより大きな偏差に対して最適な過渡応答が得られるように設計されています。そのソフト スタート プロセスは慎重に最適化されています。整合性を保つため、すべての障害から回復する際の完全ソフトスタートが実装されています。低 AC ラインからの起動を高速化し、無負荷起動時の過剰な「COMP」の影響を最小化するため、ソフト スタート速度は出力電圧検出に依存します。この COMP の完全な放電は、AC ブラウンアウト イベントから回復する際の過剰な電流の防止に役立ちます。

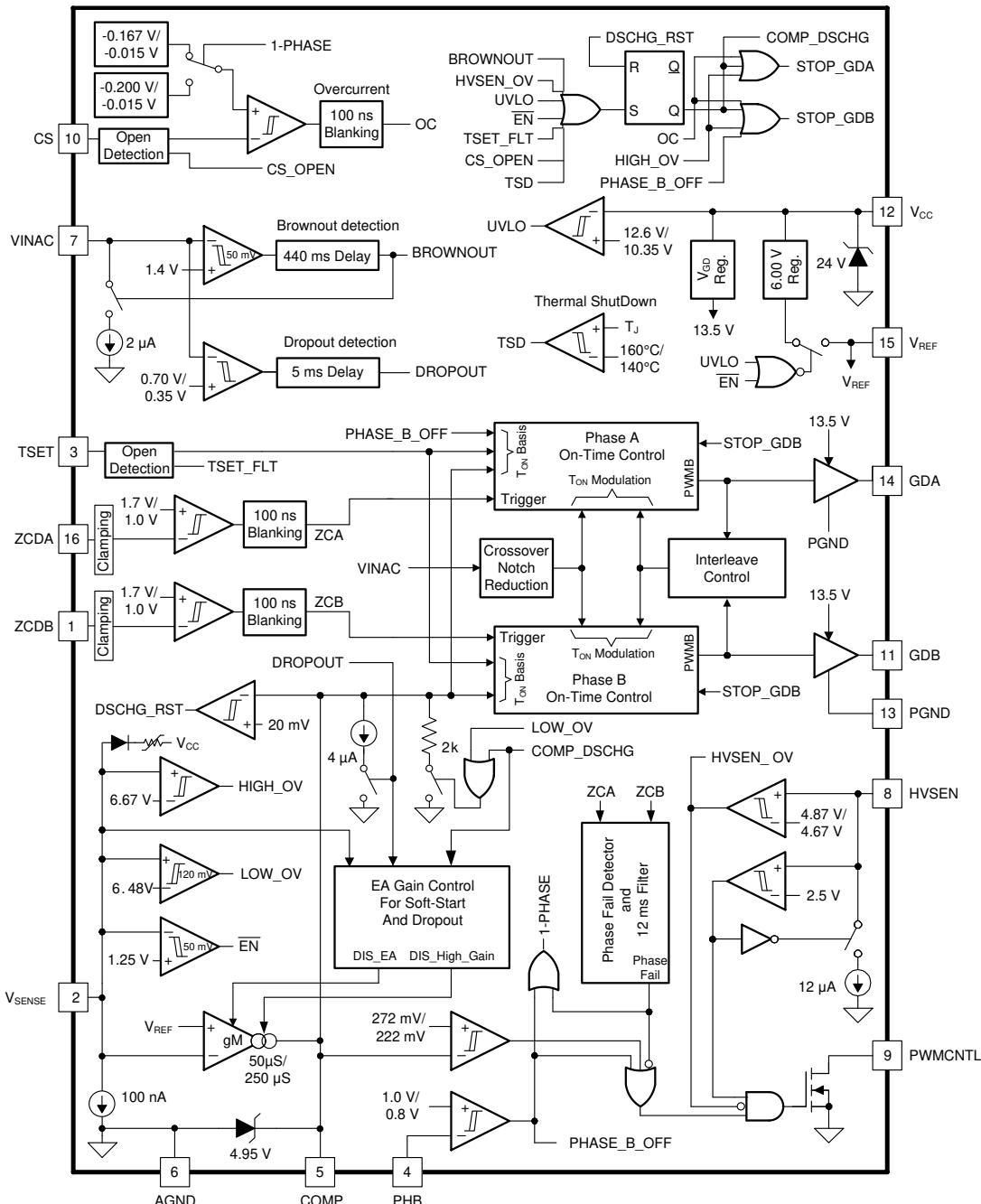

## 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 動作原理

UCC28063 は、並列接続された 2 つの昇圧パルス幅変調 (PWM) パワー コンバータのための制御回路を内蔵しています。これらの昇圧 PWM パワー コンバータは、エラー アンプ出力電圧に比例した時間の間、昇圧インダクタ内の電流を増加させます。その後、ゼロ電流検出入力 (ZCDA および ZCDB) で検出される昇圧インダクタ電流がゼロに減衰するまで、各パワー コンバータはパワー MOSFET をターンオフします。インダクタの電流がゼロになると、パワー コンバータは次のサイクルを開始します。このオン / オフ サイクルにより、オン時間と瞬時電源入力電圧  $V_{IN}(t)$  で設定されたピーク電流を持つ三角波電流が生成されます (式 1 を参照)。

$$I_{PEAK}(t) = \frac{V_{IN}(t) \times T_{ON}}{L} \quad (1)$$

平均ライン電流はピーク ライン電流の正確に半分に等しくなります (式 2 を参照)。

$$I_{AVG}(t) = \frac{V_{IN}(t) \times T_{ON}}{2 \times L} \quad (2)$$

AC ライン期間中、 $T_{ON}$  と  $L$  は本質的に一定であるため、各スイッチング サイクルで生成される三角波は、整流された AC ライン電圧の瞬間値に比例する平均値を持ちます。このアーキテクチャは、ライン周波数での抵抗性入力インピーダンス特性とほぼ 1 の力率をもたらします。

### 7.3.2 Natural Interleaving

通常の動作条件では、UCC28063 は、チャネル A とチャネル B のインダクタ電流の相対位相を  $180^\circ$  に非常に近い値にレギュレートします。この結果、ライン フィルタと出力コンデンサで観測されるスイッチング周波数のリップル電流が、各コンバータのリップル電流と比較して、大幅に低減されます。この設計を採用すると、入力および出力フィルタ回路のサイズとコストを低減できます。位相制御機能は、A チャネルと B チャネルの位相と周波数の関係に基づいて、A チャネルと B チャネルのオン時間を個別に調節します。Natural Interleaving 方式を使うと、昇圧インダクタの許容誤差に厳しい要求を課さなくとも、コンバータは両方の位相の  $180^\circ$  位相シフトと遷移モード動作を実現できます。

理想的には、両方のインダクタが正確に同じ値のときに、最良の電流共有が達成されます。通常、インダクタンスはまったく同じではないため、A チャネルと B チャネルの電流共有の程度は、インダクタの許容誤差に見合ったものになります。また、各チャネルのスイッチング遅延および共振は通常わずかに異なるため、コントローラは同じスイッチング周波数を維持するため、 $180^\circ$  からの必要な位相誤差の偏差を許容します。個別の電力段とオン時間が適切に整合した場合、最適な位相バランスが得られます。インダクタ値の不整合は位相関係に影響を与えません。

### 7.3.3 オン時間制御、最大周波数制限、再起動タイマ

ゲート駆動オン時間は、 $K_T$  と呼ばれる係数 ( $\mu\text{s}/\text{V}$  単位) によって、エラー アンプ出力電圧に比例して変化します (式 3 を参照)。

$$T_{ON} = K_T (V_{COMP} - 125\text{mV}) \quad (3)$$

ここで

- $V_{COMP}$  はエラー アンプの出力電圧であり、 $125\text{mV}$  は変調器のオフセット電圧です。

エラー アンプの最大出力は  $4.95\text{V}$  に制限されています。この値から  $125\text{mV}$  の変調器オフセットを減算した値により、最大オン時間が制限されます (式 4 を参照)。

$$T_{ON(max)} = K_T \times 4.825\text{V} \quad (4)$$

このオン時間制限により、与えられた入力電圧においてコンバータが供給できる最大電力が設定されます。

低消費電力時には、効率向上のために 1 つの昇圧チャネル (位相) をターンオフできます (以下の「位相管理」セクションを参照)。2 相動作と単相動作の間の滑らかな遷移を実現するため、単相モードでは  $K_T$  が 2 倍に増加します。

$$K_{TS} = 2 \times K_T; \text{ active during single-phase operation} \quad (5)$$

各相の最大スイッチング周波数は最小周期タイマによって制限されます。最小周期タイマが満了する前にインダクタ電流がゼロに減衰すると、次のターンオンが遅延し、位相電流が不連続になります。

再起動タイマは、いずれかの位相の ZCD 入力が約 200μs 以内に High から Low に遷移していない場合、両方の位相を再起動することで、確実に起動することを保証します。回路が連続導通モード (CCM) で動作しないようにするため、両方の相電流がゼロに戻るまで、再起動タイマはターンオンをトリガしません。

オン時間係数 ( $K_T$ ,  $K_{TS}$ ) と最小スイッチング周期 ( $T_{(MIN)}$ ) は、時間設定抵抗 ( $R_{TSET}$ , TSET ピンとグランドの間に接続された抵抗) に比例し、これらの係数は式 5、式 6、式 7 で計算できます。

$$K_T = \frac{R_{TSET}}{133\text{k}\Omega} \times 4.0 \frac{\mu\text{s}}{\text{volt}} \quad (6)$$

$$T_{(MIN)} = \frac{R_{TSET}}{133\text{k}\Omega} \times 2.2\mu\text{s} ; \text{Minimum Switching Period} \quad (7)$$

$R_{TSET}$  の適切な値により、最小入力ライン電圧および最大負荷で動作するコンバータに必要な、クランプされた最大オン時間 ( $T_{ON(max)}$ ) が得られます。

### 7.3.4 歪みの低減

スイッチング MOSFET のドレイン - ソース間容量と昇圧インダクタの寄生共振のため、従来型の遷移モード PFC 回路では、入力電圧がゼロに近い場合、入力ラインからの電力を吸収できない場合があります。この制限は、フラットスポットという形での AC ライン電流波形歪みの結果として、全高調波歪を増加させます。ライン電流の歪みを低減するため、入力電圧が 0V に近付くと、UCC28063 はスイッチング MOSFET のオン時間を延長して電力吸収能力を高め、この影響を補償します。

「代表的特性」セクションの 図 6-12 に、VINAC 電圧に対するオン時間の増加を示します。VINAC 信号の過剰なフィルタ処理はこの機能を無効化します。

### 7.3.5 ゼロ電流検出およびバレー スイッチング

遷移モード PFC 回路では、昇圧インダクタ電流が 0 になると、MOSFET がターンオンします。昇圧インダクタと MOSFET ドレインノードの寄生容量の共振により、MOSFET の接合容量に蓄積されたエネルギーの一部が回収され、スイッチング損失が低減されます。さらに、整流された入力電圧が output 電圧の半分未満の場合、MOSFET 接合容量に蓄積されたすべてのエネルギーが回収され、ゼロ電圧スイッチング (ZVS) が実現されます。適切な遅延を追加することで、共振ドレイン電圧の谷で MOSFET をターンオン (バレースイッチング) させることができます。このようにして、エネルギーの回収を最大化でき、スイッチング損失が最小化されます。

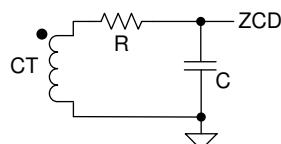

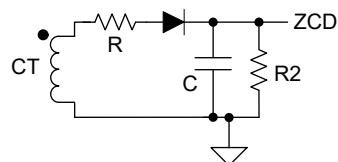

最適な時間遅延は通常、経験的に導出されますが、ドレン回路の共振周期の 25% に等しい値を出発点として使用することを推奨します。この遅延は、図 7-1 に示すような単純な RC フィルタで実現できますが、入力電圧が output 電圧に近くにつれて、遅延時間はわずかに増加します。ZCD ピンは内部でクランプされているため、図 7-2 に示す回路を使用することで、より精度の高い時間遅延を実現することもできます。

図 7-1. 単純な RC 遅延回路

図 7-2. より精度の高い時間遅延回路

### 7.3.6 位相管理と軽負荷動作

軽負荷状態では、導通損失よりスイッチング損失が支配的になる可能性があり、1つの位相（チャネル）をターンオフすると、効率が向上する場合があります。ある電力レベルでは、スイッチング損失の低下が導通損失の増加より大きくなります。軽負荷時に1つの位相をターンオフすることは、軽負荷時の効率に関する基準を満たす上で特に有益です。これは、インターリープ PFC の主な利点の1つであり、「80+」の設計要件を満たす上で特に有益です。

PHB 入力は、UCC28063 を強制的に単相モードで動作させるために使えます。PHB が 0.8V 未満に駆動されると、チャネル B はスイッチングを停止し、補償のため、チャネル A のオン時間が自動的に倍増されます。PHB が 1.0V を上回ると、本デバイスは2相モードを再開します。位相管理をカスタマイズする場合、単相動作への切り替え条件を外部回路で検出し、それに応じて PHB を駆動することができます。位相管理が不要な場合に2相モード（通常モード）で連続的に動作させるには、単純に PHB を VREF に接続します。

負荷電流が減少するにつれて、エラー アンプは COMP 電圧を下げることで、AC ライン入力電流を減少させるように指令します。AC ラインが低電圧範囲のみに制限されているアプリケーションでは、外部回路を追加しないで単相動作を自動的に選択できるように、PHB を COMP に直接接続することができます。位相管理が不要な場合に2相モード（通常モード）で連続的に動作させるには、単純に PHB を VREF に接続します。

### 7.3.7 外部ディセーブル

UCC28063 は、オープンドレインまたはオープンコレクタドライバによって VSENSE ピンを意図的にグランドに接続することで、外部的に無効化できます。無効化された場合、本デバイスの消費電流は大幅に減少し、COMP は Low を駆動します。この無効化方式は、本デバイスを強制的にスタンバイモードに移行させ、その消費電力を最小化します。これは、低スタンバイ電力が設計の重要な要素である場合に特に役立ちます。VSENSE が解放されると、本デバイスはソフトスタートモードに入ります。

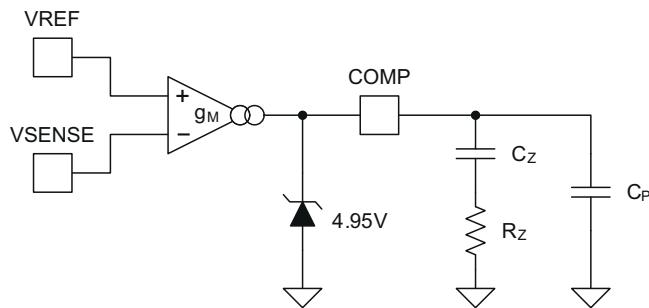

### 7.3.8 改良型エラー アンプ

電圧エラー アンプは、トランスコンダクタンスアンプです。電圧ループ補償はエラー アンプ出力（COMP）とアノログ グラウンド（AGND）との間に接続されます。推奨するタイプ2補償ネットワークを 図 7-3 に示します。ループ安定性を確保するため、 $55\mu\text{s}$ （公称値）のトランスコンダクタンス（ゲイン）を使用し、出力電圧の小信号変動に基づいて補償ネットワーク値が計算されます。

図 7-3. 標準的な補償ネットワークを備えたトランスコンダクタンスエラー アンプ

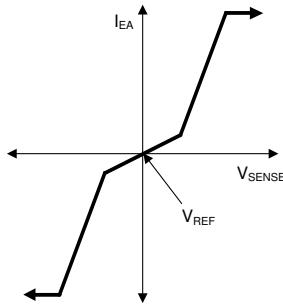

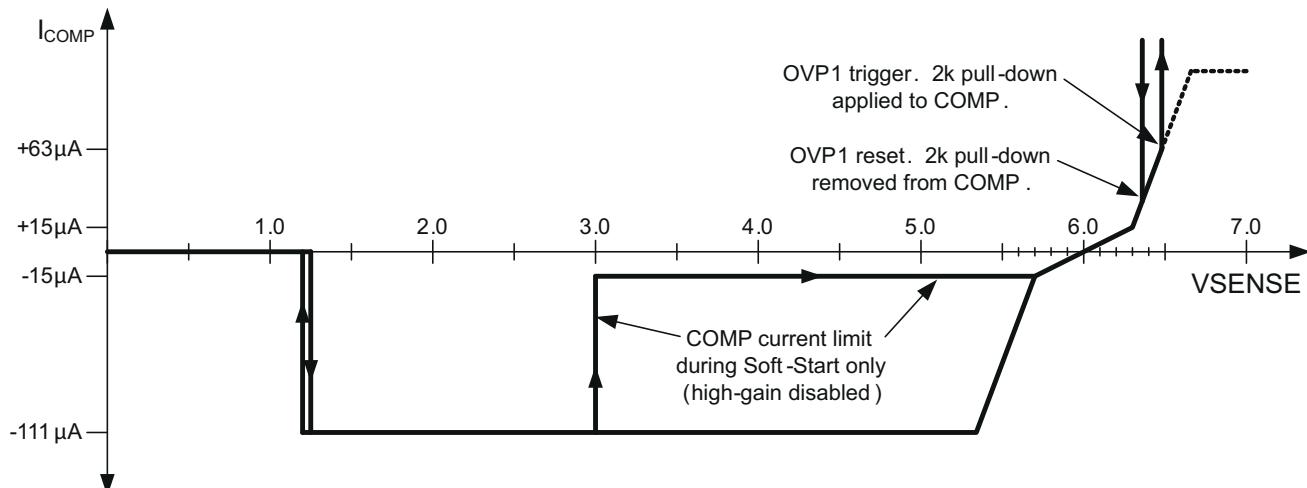

大きな変動に対する過渡応答性能を高めるため、エラー アンプ入力がレギュレーション電圧（VSENSEreg）の公称値から  $\pm 5\%$  を超えて逸脱すると、エラー アンプ ゲインが約 5 倍に増大します。このゲイン増加により、負荷電流が急増または急減した後、補償部品を素早く充電および放電できます（代表的特性セクションの 図 6-5 も参照）。

小信号および大信号ゲイン領域と最大電流制限値を示す、基本的な電圧エラー アンプのトランスクンダクタンス曲線。

図 7-4. 基本的な電圧エラー アンプのトランスクンダクタンス曲線

### 7.3.9 ソフトスタート

ソフトスタートは、制御された条件下で、AC ライン入力電圧のピークから目的のレギュレーション電圧まで、PFC コンバータの出力電圧を上昇させるプロセスです。UCC28063 は、専用のソフトスタートピンの代わりに電圧エラー アンプを制御された電流源として使って、COMP 電圧を上げることで PWM デューティサイクルを増加させます。AC ライン電圧が低いときの過剰な起動時間遅延を防止するため、VSENSE が 3V を超えるまでより大きな電流を印加し、3V を超えると電流を減少させ、無負荷での起動時に COMP 電圧が過剰になる傾向を最小限に抑えます。

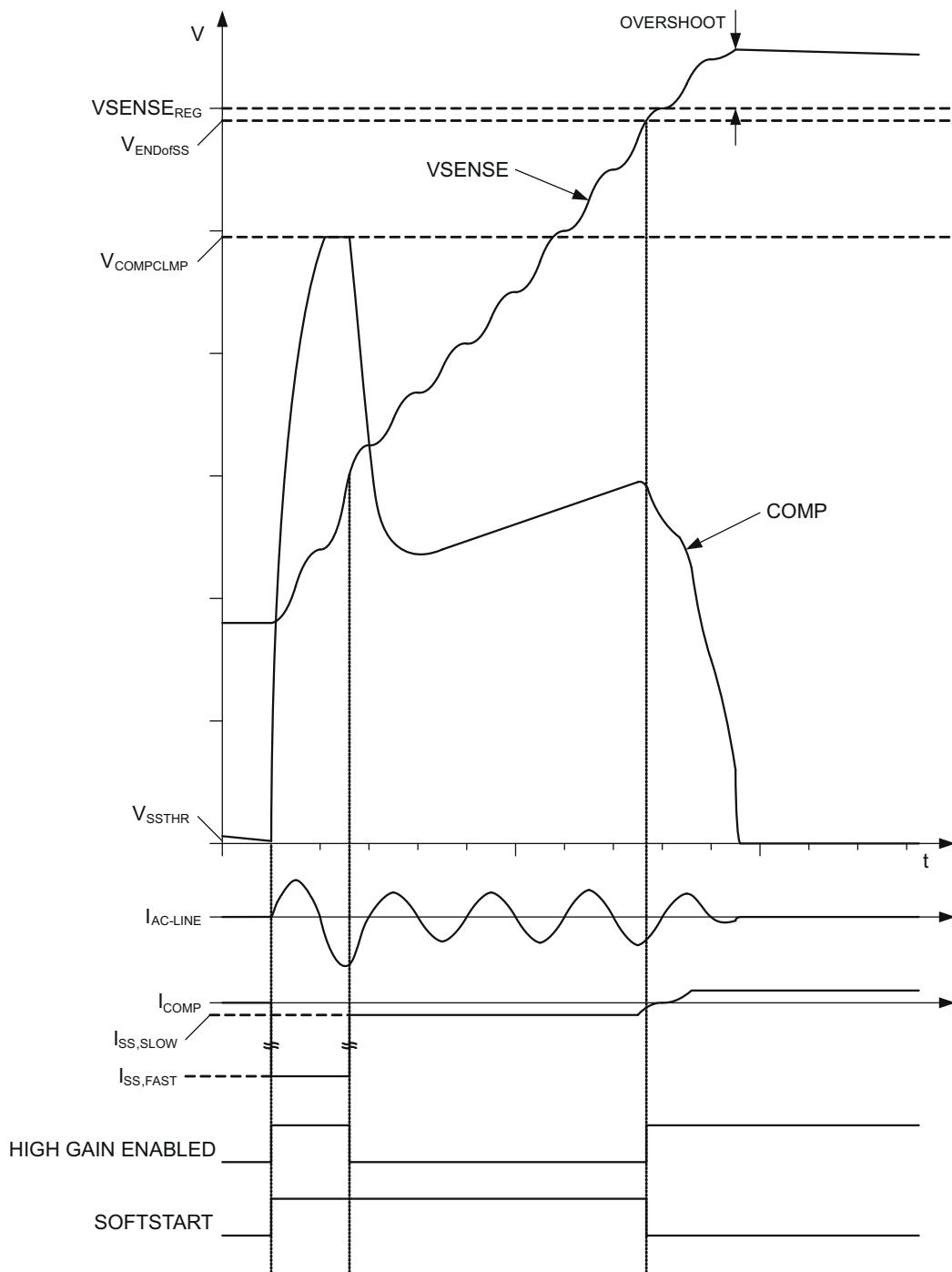

COMP と AGND の間に接続された補償コンデンサがゼロから最終値近くまで充電されるにつれて、PWM はゼロオン時間から通常のオン時間まで徐々に立ち上がります。このプロセスには、エラー アンプの出力電流と補償コンデンサの値で設定されたタイミングを持つソフトスタートが実装されています。HVSEN フェイルセーフ OVP、プラウンアウト、外部ディセーブル、UVLO フォルト、その他の保護フォルトが発生した場合、COMP は能動的に放電を行い、トリガしているイベントがクリアされた後、UCC28063 はソフトスタートします。フォルトイベントがごく短時間発生した場合でも、そのフォルトはソフトスタート状態に入るようLatchされ、COMP が 20mV まで完全に放電され、フォルトがクリアされるまでソフトスタートを遅らせた後、ソフトスタートします。COMP 電流の詳細については、図 7-5 を参照してください。図 7-6 に、ソフトスタート時の代表的なシステム動作例を示します。

電圧エラー アンプのトランスクンダクタンスを含む COMP 出力電流曲線の拡大図と、ソフトスタートおよび過電圧条件に適用可能な変更点

図 7-5. COMP 出力電流曲線の拡大図

図 7-6. ソフトスタートタイミングとシステム動作例

### 7.3.10 ブラウンアウト保護

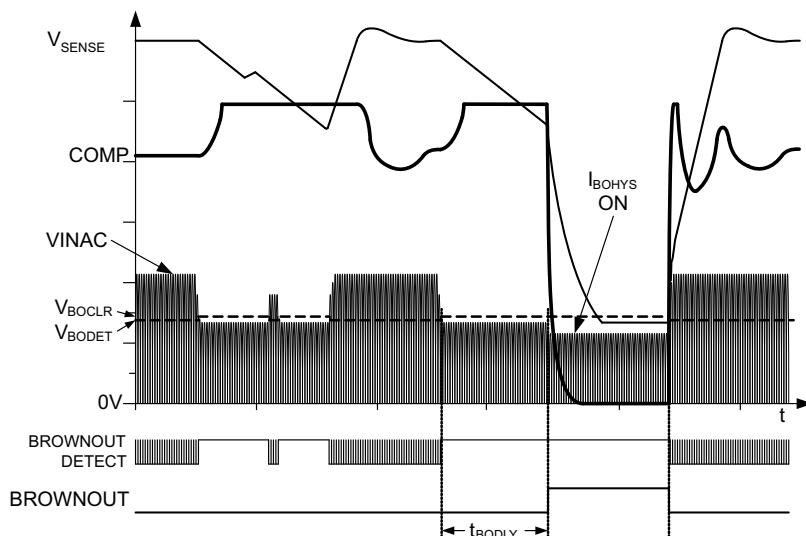

電源ラインの RMS 電圧が低下するにつれて、特定の負荷に対して一定の出力電圧を維持するために、RMS 入力電流が増加する必要があります。ブラウンアウト保護は、(RMS 入力電流の増加による) システムの過剰な熱ストレスが安全な動作レベルを超えないようにするのに有効です。電源ライン電圧は VINAC で検出されます。ブラウンアウトフィルタ時間の間、VINAC がブラウンアウトスレッショルドを超えた場合、ブラウンアウト条件が検出され、両方のゲート駆動出力がターンオフされます。ブラウンアウト中、COMP は Low を駆動し、ソフトスタート条件が開始されます。スレッショルド付近のチャタリングを防止するため、ブラウンアウト検出回路にはヒステリシスが組み込まれています。VINAC がブラウンアウトスレッショルドを上回ると、制御された電流によって COMP が立ち上がるにつれて、電力段はソフトスタートします。

ブラウンアウト検出スレッショルドとそのヒステリシスは、分圧器の比と抵抗値によって設定されます。ブラウンアウト保護は VINAC ピーク電圧に基づいており、スレッショルドとヒステリシスもラインピーク電圧に基づいています。VINAC がブラウンアウト検出スレッショルドを下回ると常に、 $2\mu\text{A}$  の電流シンク ( $I_{BOHYS}$ ) によって大きなヒステリシスが生成されます。VINAC 検出スレッショルドとクリアスレッショルドとの間にも、 $50\text{mV}$  のオフセット ( $V_{BOHYS}$ ) という形で小さなヒステリシスが存在します。VINAC 電圧のピーク値は簡単に RMS 値に変換できます。分圧器の抵抗値の例は、整流済み入力電圧と VINAC の間が  $8.61\text{M}\Omega \pm 1\%$ 、VINAC とグランドの間が  $133\text{k}\Omega \pm 1\%$  です。これらの抵抗は、RMS ライン電圧のスレッショルドの代表値を設定します (表 7-1 を参照)。

表 7-1. ブラウンアウトスレッショルド (本文に記載された条件の場合)

| スレッショルド | AC ライン電圧 (RMS) |

|---------|----------------|

| 立ち下がり   | 66 V           |

| 立ち上がり   | 78 V           |

式 8 と式 9 は、目的のブラウンアウト検出およびブラウンアウトクリア電圧レベルに基づいて VINAC 分圧抵抗値を計算するために使用できます。 $V_{AC\_OK}$  は RMS ターンオン電圧の目標値、 $V_{AC\_BO}$  は RMS ターンオフ ブラウンアウト電圧の目標値、 $V_{LOSS}$  は配線、EMI フィルタ、 $V_{AC\_BO}$  でのブリッジ整流器インピーダンスによる直列電圧降下の合計値です。 $V_{BODET}$ 、 $V_{BOHYS}$ 、 $I_{BOHYS}$  は、このデータシートのデータ表に記載されています。

$$R_A = \left( \frac{\sqrt{2}(V_{AC\_OK} - V_{AC\_BO}) - V_{BOHYS}}{I_{BOHYS}} \right) \left( 1 + \frac{V_{BOHYS}}{V_{BODET}} \right) \quad (8)$$

$$R_B = \frac{R_A}{\left( \frac{\sqrt{2}V_{AC\_BO} - V_{LOSS}}{V_{BODET}} - 1 \right)} \quad (9)$$

VINAC 分圧抵抗  $R_A$  および  $R_B$  の標準値を選択すると、式 10 と式 11 を使って、AC ラインの実際のターンオンおよびブラウンアウトスレッショルド RMS 電圧を逆算できます。

$$V_{AC\_BO} = \left( 1 + \frac{R_A}{R_B} \right) \frac{V_{BODET}}{\sqrt{2}} + \frac{V_{LOSS}}{\sqrt{2}} \quad (10)$$

$$V_{AC\_OK} = V_{AC\_BO} + \frac{R_A I_{BOHYS}}{\sqrt{2} \left( 1 + \frac{V_{BOHYS}}{V_{BODET}} \right)} + \frac{V_{BOHYS}}{\sqrt{2}} \quad (11)$$

図 7-7 に、ブラウンアウト機能のタイミング例を示します。

ターンオンおよびブラウンアウト電圧を簡単に見積もるには、 $V_{LOSS}$  と  $V_{BOHYS}$  の項を 0 に設定して上記の式を単純化します。

### 7.3.11 ドロップアウト検出

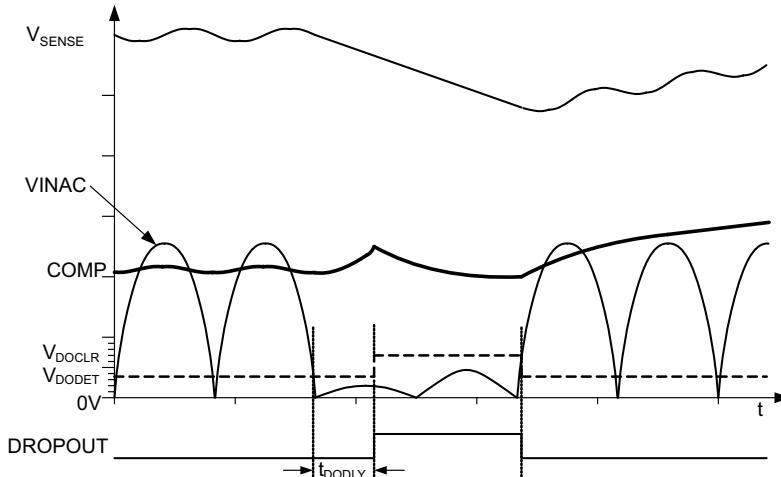

地域の AC 配電ネットワークに影響を与える過渡的な異常事象に起因して、AC ライン電圧が瞬間にゼロまたはほぼゼロに低下することはよくあります。AC ラインドロップアウト（またはライン ディップ）と呼ばれるこのようなイベントの持続時間は、通常、わずか 1 または 2 ライン サイクルまでです。ドロップアウト中、ダウンストリームの電力変換段は PFC 出力容量の十分なエネルギー蓄積に頼ります。この PFC 出力容量は、規定されたホールドアップ時間にわたってライドスルー エネルギーを供給するようなサイズに設定されています。通常、PFC 出力電圧が低下している間、レギュレーションを維持しようとして、電圧ループ エラー アンプ出力は上昇します。その結果、AC ライン電圧が戻ると、過剰なデューティ サイクルが指示されることで、大きなピーク電流サージが昇圧インダクタを飽和させ、過大な応力と可聴ノイズを発生させる可能性があります。

UCC28063 は、ドロップアウト中、エラー アンプの動作を一時停止させるドロップアウト検出機能を内蔵しています。5ms より長い間 VINAC 電圧が 0.35V を下回ると、ドロップアウト状態が検出され、エラー アンプ出力がターンオフされます。また、補償ネットワークコンデンサを穏やかに放電するため、COMP に 4 $\mu$ A のプルダウン電流が適用されます。このようにして、AC ライン電圧が復帰した際、COMP 電圧（と対応するデューティ サイクル設定）はドロップアウトが発生する前のレベルに非常に近い、またはわずかに下回るレベルに維持されます。過剰なデューティ サイクルによる電流サージと、それらに伴う副作用が防止されます。VINAC が 0.71V を上回ると、ドロップアウト状態は解消され、エラー アンプは通常動作に復帰します。

前のセクションでブラウンアウトのために計算された VINAC 分圧抵抗値に基づいて、ドロップアウト検出 ( $V_{AC\_DO}$ ) とドロップアウトクリア ( $V_{DO\_CLR}$ ) の入力 RMS 電圧スレッショルドは、以下の 式 12 と 式 13 を使用して決定できます。

$$V_{AC\_DO} = \frac{V_{DODET} \left( \frac{R_A}{R_B} + 1 \right) + V_{LOSS}}{\sqrt{2}} \quad (12)$$

$$V_{DO\_CLR} = \frac{V_{DOCLR} \left( \frac{R_A}{R_B} + 1 \right) + V_{LOSS}}{\sqrt{2}} \quad (13)$$

VINAC 信号を過度にフィルタ処理することは避けてください。さもないと、ドロップアウト検出が遅延し、または無効化される可能性があります。100 $\mu$ s 以下の RC 時定数は良好な性能をもたらすはずです。図 7-8 に、ドロップアウト機能のタイミングの例を示します。

図 7-7. AC ライン ブラウンアウト タイミングとシステム動作例

図 7-8. AC ライン ドロップアウト タイミングとシステム動作例

### 7.3.12 VREF

$V_{REF}$  は、外部回路用の制限された電圧源として機能する出力であるとともに、適切にレギュレートされた基準電圧を本デバイス内の回路に供給します。 $V_{REF}$  および  $GND$  ピンのできるだけ近くに配置された低インピーダンスの  $0.1\mu F$  以上のコンデンサを使って、この出力を  $GND$  にバイパスする必要があります。外部回路によって消費される電流は数ミリアンペアを超えないようにする必要があります、かつ脈動させないようにする必要があります。

$V_{CC}$  が UVLO 状態のとき、または  $V_{SENSE}$  がイネーブル スレッショルドを下回ったとき、 $V_{REF}$  出力は無効化されます。この出力は電流をソースできるのみであり、ピンに流れ込もうとする電流を受け入れることはできません。

### 7.3.13 VCC

$V_{CC}$  は通常、13V と 21V の間のバイアス電源に接続されます。 $V_{CC}$  でのスイッチング リップル電圧を最小限に抑えるため、低インピーダンスのコンデンサを  $V_{CC}$  および  $GND$  ピンのできるだけ近くに配置して、 $V_{CC}$  をバイパスする必要があります。この容量は、最高の動作周波数でのゲート駆動スイッチングによるピーク電流が十分にデカッピングされるように、大きさを決定する必要があります。レギュレーションが不十分な低インピーダンス電源から電力を供給する場合、 $V_{CC}$  に過剰な電流が流れるのを防止するため、ツエナーダイオードを外付けすることを推奨します。

低電圧誤動作防止 (UVLO) 状態とは、 $V_{CC}$  電圧がターンオン スレッショルドにまだ達していない状態、またはすでにターンオンされていた  $V_{CC}$  電圧が、ターンオフ スレッショルドを下回った状態のことです。UVLO 中、 $V_{REF}$  出力と本デバイス内のほとんどの回路は無効化され、 $V_{CC}$  電流は通常動作レベルより大幅に小さくなります。 $V_{SENSE}$  がイネーブル スレッショルドを下回った場合も、同じ状況が当てはまります。これは、電源投入前およびスタンバイ状態での電力損失を最小化するのに役立ちます。

### 7.3.14 ダウンストリーム コンバータの制御

UCC28063 では、 $PWMCTRL$  ピンを使って、PFC 段をダウンストリーム コンバータと連携させることができます。 $HVSEN$  ピンにより、PFC 出力電圧が監視されます。設定されたスレッショルドを出力電圧が下回っている限り、 $12\mu A$  の電流源 ( $I_{HV\_HYS}$ ) が有効化されています。出力電圧がこのスレッショルドを上回ると、 $PWMCTRL$  ピンが内部でグランドにプルされるため、このピンを使ってダウンストリーム コンバータを有効化できます。同時に、この電流源が無効化されることで、ダウンストリーム コンバータがターンオフする下側スレッショルドのヒステリシスが生じます。有効化 / 無効化のヒステリシスは、 $HVSEN$  の分圧器の比と抵抗値によって調整されます。 $HVSEN$  ピンは、フェイルセーフ過電圧保護 (OVP) にも使用されます。分圧器を設計する際は、このフェイルセーフ OVP レベルが通常の  $V_{SENSE}$  OVP レベルよりも確実に高く設定されるようにします。

1 つの抵抗分圧器によって検出される、 $HVSEN$  入力に関連するスレッショルドは 2 つ存在するため、 $PWMCTRL$  ターンオフ電圧 ( $V_{PWM-OFF}$ ) はフェイルセーフ OVP 電圧 ( $V_{FLSF\_OV}$ ) とリンクしています (式 14 を参照)。

$$\frac{V_{\text{PWM-OFF}}}{2.5\text{V}} = \frac{V_{\text{FLSF\_OV}}}{4.87\text{V}} \quad (14)$$

最初にどちらか一方を任意に選択すると、他方が決定されるため、トレードオフが必要になる場合があります。PWMCTRL ターンオン電圧 ( $V_{\text{PWM-ON}}$ ) は、HVSEN ヒステリシス電流を考慮して、分圧器の上側の抵抗値を選択することで設定されます (式 15 と 式 16 を参照)。次に、分圧器の下側の抵抗が計算されます (式 17 を参照)。

$$V_{\text{PWM-ON}} = V_{\text{PWM-OFF}} + I_{\text{HV-HYS}} R_{\text{HV-UPPER}} \quad (15)$$

$$R_{\text{HV-UPPER}} = \frac{V_{\text{PWM-ON}} - V_{\text{PWM-OFF}}}{I_{\text{HV-HYS}}} \quad (16)$$

$$R_{\text{HV-LOWER}} = \frac{R_{\text{HV-UPPER}}}{\left( \frac{V_{\text{PWM-OFF}}}{2.5\text{V}} - 1 \right)} \quad (17)$$

### 7.3.15 システム レベルの保護

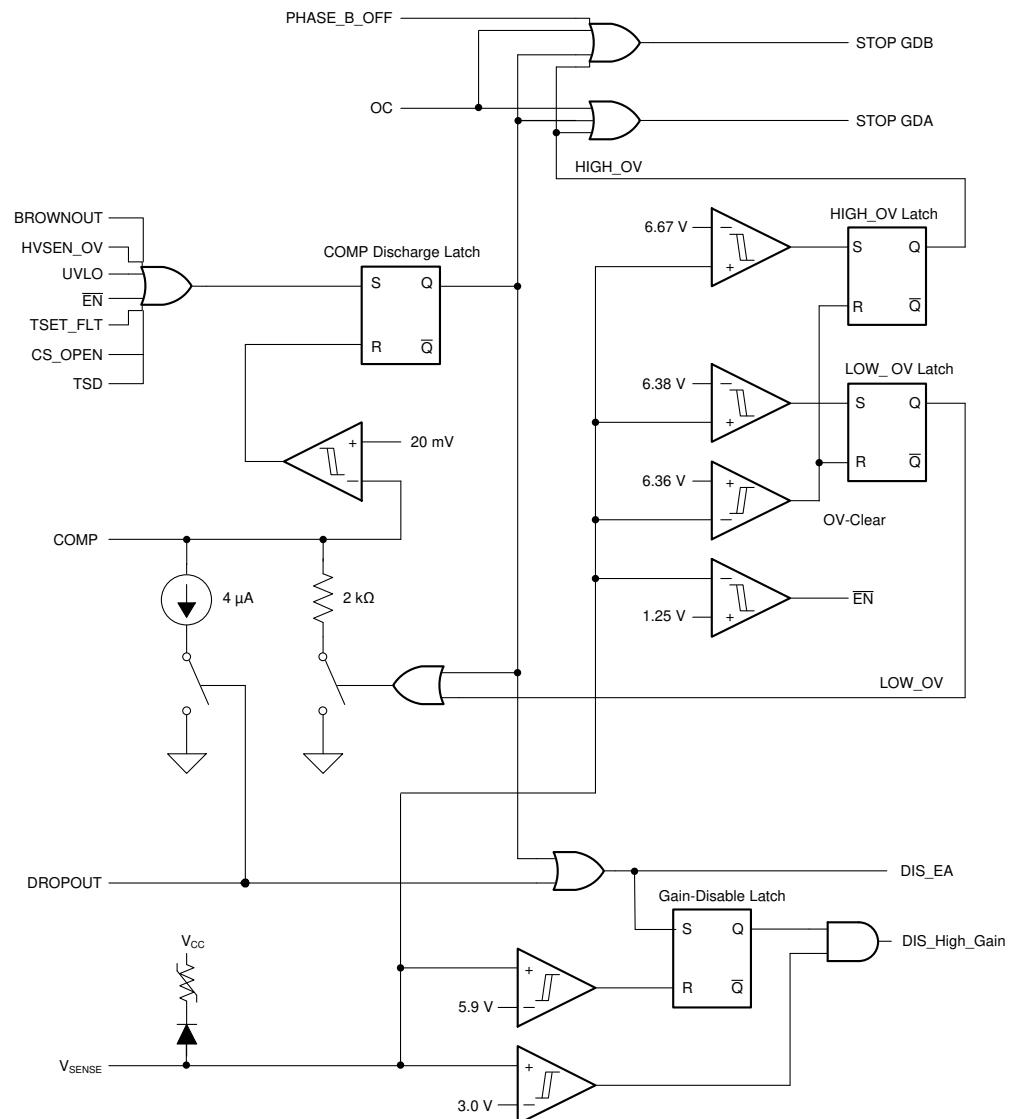

#### 7.3.15.1 フェイルセーフ OVP - 出力過電圧保護

フェイルセーフ OVP は、障害が発生しても、出力が安全なレベルを超えて昇圧されることを防止します。出力電圧検出のための冗長な経路を備えることで、出力過電圧に対する保護をさらに強化しています。過電圧保護は 2 つの独立した経路(VSENSE と HVSEN)を使って実装されています。どちらかの入力が重大な過電圧条件を検出すると、コンバータはシャットダウンします。どちらかの検出経路に障害が発生しても、出力電圧は依然として安全な限界値を下回った状態を維持できます。両方の検出入力が通常範囲に戻ると、本デバイスは再び有効化されます。この時点で、ゲート駆動出力は PWM 制御の下でスイッチングを再開します。VSENSE の低レベルの過電圧はソフトスタートをトリガしませんが、2% のヒステリシスを持つ OV クリア スレッショルドを出力電圧が下回るまで、内部 2kΩ 抵抗によって COMP ピンが放電されます。VSENSE の高レベルの過電圧は、OV がクリアされるまで、ゲート駆動出力をも遮断しますが、依然としてソフトスタートはトリガしません。しかし、HVSEN で過電圧が検出されると、完全ソフトスタートがトリガされ、COMP ピンを 20mV まで完全に放電してから、ソフトスタートが開始されます。

#### 7.3.15.2 過電流保護

特定の条件 (突入、ブランアウト回復、出力過負荷など) の下で、PFC 電力段には大きな電流が流れます。これらの条件の間、パワー デバイスをスイッチングから保護することが重要です。

従来型の電流検出方式では、各 MOSFET のソース レグと直列に接続したシャント抵抗を使用してコンバータの電流を検出するため、複数のグランド ポイントが形成され、消費電力が増大します。さらに、MOSFET がオフの際は電流情報が得られないため、ソース抵抗電流検出方式では、過電流 (OC) 条件の間、MOSFET が繰り返しターンオンします。その結果、コンバータは一時的に連続導通モード (CCM) で動作し、昇圧ダイオード内の過剰な逆回復電流またはその他の異常なストレスによって障害が発生する可能性があります。

UCC28063 は 1 本の抵抗を使って、総インダクタ (入力) 電流を連続的に検出します。これにより、過剰なインダクタ電流が流れた際の MOSFET のターンオンを完全に回避できます。MOSFET に対するゲート駆動は、総インダクタ電流がゼロに近づくまで禁止され、逆回復に起因する障害 (これらの障害は、AC ラインがブランアウト状態から回復した際に発生する可能性が最も高い) を防止します。

2 相動作時の OC スレッショルド電圧の公称値は -200mV であるため、損失の最小化に有利です。単相動作中、位相障害の検出によって、または PHB が 0.8V 未満に駆動されたという理由で、このスレッショルドは自動的に -166mV に低減されます。単相ピーク電流のインターリーブ ピーク電流に対する比が 1/2 より大きいため、単相スレッショルドは 2 相スレッショルドの単純に 1/2 ではないことに注意します。

OC 条件が発生すると、両方のゲート駆動出力が直ちにターンオフされますが、ソフトスタートはトリガされず、エラー アンプの動作も変更されません。総インダクタ電流検出電圧が OC クリア スレッショルド (-15mV) を下回ると、過電流状態は解消されます。

過電流状態の後、入力電流がゼロに近づくと、両方の MOSFET が同時にターンオンされます。2 つの相電流は一時的に同相で動作しているため、過電流イベント後に迅速に通常動作に復帰できるようにするため、どちらの相のピーク電流が最大値の 2 倍になっても OC 保護がトリガされないように電流検出抵抗を選択する必要があります。自動位相シフト制御は、数スイッチング サイクル以内にインターリーブを再確立します。

### 7.3.15.3 開ループ保護

帰還ループが本デバイスから切り離された場合、UCC28063 が内蔵する 100nA 電流源が VSENSE ピンの電圧をグランドにプルします。VSENSE が 1.20V を下回ると、本デバイスは無効化されます。本デバイスが無効化されると、バイアス電源電流が減少し、両方のゲート駆動出力と COMP は Low を駆動し、ソフトスタート条件が開始されます。VSENSE が 1.25V を上回ると、本デバイスは再び有効化されます。この時点で、ゲート駆動出力はソフトスタート PWM 制御の下でスイッチングを開始します。

帰還ループがグランドから切り離されると、VSENSE 電圧は High にプルされます。VSENSE が第 2 レベル過電圧保護スレッショルドを上回ると、両方のゲート駆動出力は遮断され、COMP は Low を駆動します。VSENSE が OV クリア スレッショルドを下回ると、本デバイスは再び有効化されます。入力電圧が異常に高い状況では、VSENSE 入力は、本デバイスに流れ込む一定限度の量の電流に耐えることができます。詳細については、このデータシートの冒頭付近にある「絶対最大定格」表を参照してください。

### 7.3.15.4 VCC 低電圧誤動作防止 (UVLO) 保護

PWM が機能し始めるには、VCC がターンオン スレッショルドを上回る必要があります。動作中に VCC が UVLO スレッショルドを下回ると、両方のゲート駆動出力と COMP は Low を駆動し、ソフトスタート条件がトリガされます。ソフトスタートモードで PWM 機能が再起動するには、VCC が再びターンオン スレッショルドを上回る必要があります。

### 7.3.15.5 位相障害保護

UCC28063 は、ZCD パルスのシーケンスを監視することで、両方の位相の障害を検出します。通常の 2 相動作中、一方の ZCD 入力が正常にスイッチングしているのに、もう一方の ZCD 入力が約 12ms 以上アイドル状態を維持した場合、過電流スレッショルドが低減され、PWMCNTL が高インピーダンス状態に移行し、PFC 電力段が正常に動作していないことを示します。通常の単相動作中 ( $\text{PHB} < 0.8\text{V}$ )、位相障害は監視されません。また、UCC28063 では、COMP が約 222mV を下回っている場合、位相障害は監視されません。

### 7.3.15.6 CS 開放、TSET 開放および短絡保護

CS 入力がオープンになった場合、UCC28063 はこの状態を検出し、出力をシャットダウンして、完全ソフトスタート条件をトリガします。TSET 入力がオープンになった場合または GND に短絡した場合、UCC28063 はこれらの状態を検出し、出力をシャットダウンして、完全ソフトスタート条件をトリガします。フォルトが解消されると、(ソフトスタートによって) 通常動作が再開されます。

### 7.3.15.7 サーマル シャットダウン保護

ゲート駆動出力と VREF の一方または両方が過負荷になると、安全なレベルを超えて回路の内部温度を上昇させ得る過剰な電力が、本デバイス内で消費される可能性があります。熱インピーダンスが高すぎる場合、または周囲温度が高すぎる場合、通常の電力消費であっても、過剰な熱が発生する可能性があります。UCC28063 は内部過熱条件を検出すると、出力をシャットダウンし、完全ソフトスタート条件をトリガします。内部デバイス接合部温度が熱ヒステリシス温度を下回ると、ソフトスタート制御の下で動作を再開します。

### 7.3.15.8 AC ライン ブラウンアウトおよびドロップアウト保護

このデータシート内の前のセクションの、各トピックに固有の説明を参照してください。

### 7.3.15.9 フォルト論理図

図 7-9 に、VSENSE、COMP、各種内部状態に関するフォルト処理ロジックを示します。

図 7-9. VSENSE 検出とエラー アンプ制御を備えたフォルト ロジック

## 7.4 デバイスの機能モード

本コントローラは、スイッチング サイクルの開始をトリガするために ZCDA と ZCDB に入力されたインダクタ検出巻線電圧に基づくインダクタ消磁情報を利用する 2 相インターリープ PFC として構成することを主な目的としています。

この機能は、2 つの方法で拡張できます。

- **位相 B の有効化と無効化:** 位相 B は、明示的なユーザー制御によってシェディング (無効化) することも、自動軽負荷効率管理機能として設定することもできます。PHB ピンに印加されている電圧が VPHBF スレッショルドを下回ると、位相 B および位相障害検出器が無効化されます。出力電圧過渡を最小限に抑えるため、位相 A に対して指令されるオン時間は 2 倍になります。PHB ピンの電圧が VPHBR スレッショルドを上回ると、2 相モードが継続的に有効化されます。このモードにするには、PHB を VREF ピンに接続します。または、軽負荷時の自動位相シェディング (無効化) のため、PHB を COMP ピンに接続することもできます。

- **PFC 段有効化 / 無効化制御:** VSENSE 電圧が 1.25V のイネーブル スレッショルドを上回ると、コントローラ動作が有効化されます。基本的な無効化方法は、オープンドレインまたはオープンコレクタロジック出力により VSENSE を Low にプルすることです。これにより、出力が無効化され、VCC 電流が大幅に減少します。VSENSE を解放すると、ソフトスタートが開始されます。このノードに何らかのノイズを結合させるようないかなる PCB パターンも配置しないようにします。

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

この制御 IC は、汎用 AC ラインのアクティブ力率補正を必要とする AC/DC 電源の制御に広く適用できます。この IC を使用するアプリケーションは通常、EN61000-3-2 に準拠した Class-D 機器入力電流高調波規格に適合します。この規格は、定格電力が 75W を超える機器に適用されます。本 IC は、遷移モード昇圧で 2 相インターリーブ制御機能を実現できるため、通常 150W~800W のコスト最適化されたアプリケーションに最適です。または、小さいフィルタ部品サイズ、低プロファイル ソリューション、分散型熱管理というインターリーブの利点を活用する必要がある、より小さい電力のアプリケーションにも適しています。

『UCC28063EVM-723 300W インターリーブ PFC プリレギュレータ ユーザー ガイド』(SLUU512) には、300W アプリケーションの EVM 設計について記載されています。

この EVM に関連して、部品選択のための自動計算に役立つ Excel ファイルを提供しています (SLUC292 で入手できます)。

### 8.2 代表的なアプリケーション

図 8-1 に、2 相インターリーブ遷移モード PFC プリレギュレータにおける UCC28063 PFC コントローラの例を示します。

Copyright © 2016, Texas Instruments Incorporated

図 8-1. 代表的なインターリーブ遷移モード PFC プリレギュレータ

### 8.2.1 設計要件

この設計の仕様は、代表的な 300W LCD TV の電源要件に基づいて選択されました。表 8-1 に、これらの仕様を示します。

表 8-1. 設計仕様

| 設計パラメータ           |             | 最小値             | 代表値              | 最大値  | 単位 |

|-------------------|-------------|-----------------|------------------|------|----|

| V <sub>IN</sub>   | RMS 入力電圧    | 85<br>(VIN_MIN) | 265<br>(VIN_MAX) | VRMS |    |

| V <sub>OUT</sub>  | 出力電圧        |                 | 390              | V    |    |

| f <sub>LINE</sub> | AC ライン周波数   | 47              | 63               | Hz   |    |

| PF                | 最大負荷時の力率    | 0.90            |                  |      |    |

| P <sub>OUT</sub>  |             |                 | 300              | W    |    |

| η                 | 全負荷効率       | 92%             |                  |      |    |

| f <sub>MIN</sub>  | 最小スイッチング周波数 | 45              |                  | kHz  |    |

### 8.2.2 詳細な設計手順

#### 8.2.2.1 インダクタの選択

昇圧インダクタは、低ラインのピーク時のインダクタリップル電流要件に基づいて選択します。インダクタを選択するには、低ラインのピーク時の昇圧コンバータ デューティ サイクル ( $D_{PEAK\_LOW\_LINE}$ ) を計算する必要があります (式 18 を参照)。

$$D_{PEAK\_LOW\_LINE} = \frac{V_{OUT} - V_{IN\_MIN}\sqrt{2}}{V_{OUT}} = \frac{390V - 85V\sqrt{2}}{390V} \approx 0.69 \quad (18)$$

低ライン状態でのコンバータの最小スイッチング周波数 ( $f_{MIN}$ ) は、低ラインのピーク時に発生し、可聴ノイズを防止するため、25kHz~50kHz に設定されます。この設計例では、 $f_{MIN}$  を 45kHz に設定しています。2 相インターリープ設計の場合、L1 と L2 は、式 19 に示すように決定されます。

$$L1 = L2 = \frac{\eta \times V_{IN\_MIN}^2 \times D_{PEAK\_LOW\_LINE}}{P_{OUT} \times f_{MIN}} = \frac{0.92(85V)^2 0.69}{300W \times 45kHz} \approx 340\mu H \quad (19)$$

この設計のインダクタのピーク電流 ( $I_{LPK}$ ) は 5.4A (式 20 を参照)、RMS 電流 ( $I_{LRMS}$ ) は 2.2A (式 21 を参照) となります。

$$I_{LPK} = \frac{P_{OUT}\sqrt{2}}{V_{IN\_MIN} \times \eta} = \frac{300W\sqrt{2}}{85V \times 0.92} \approx 5.4A_{pk} \quad (20)$$

$$I_{LRMS} = \frac{I_{LPK}}{\sqrt{6}} = \frac{5.4A}{\sqrt{6}} \approx 2.2A_{rms} \quad (21)$$

このコンバータは、コンバータタイミングを設定するために、一定のオン時間 ( $T_{ON}$ ) とゼロ電流検出 (ZCD) を使っています。L1 と L2 の補助巻線は、インダクタ電流がゼロになる瞬間を検出します。スイッチング サイクルごとに ZCD コンバータをリセットするため、式 22 を使用して巻線比を選択することで、高ラインのピーク時に最低 2V の電圧が発生するようになります。

各補助巻線の巻線比は次のようにになります。

$$\frac{N_p}{N_s} = \frac{V_{OUT} - V_{IN\_MAX}\sqrt{2}}{2V} = \frac{390V - 265V\sqrt{2}}{2V} \approx 8 \quad (22)$$

### 8.2.2.2 ZCD 抵抗の選択 ( $R_{ZA}$ , $R_{ZB}$ )

ZCD 抵抗の最小値は、内部クランプ電流の最大定格 (3mA) に基づいて選択します (式 23 を参照)。

$$R_{ZA} = R_{ZB} \geq \frac{V_{OUT} N_s}{N_p \times 3mA} = \frac{390V}{8 \times 3mA} \approx 16.3k\Omega \quad (23)$$

この設計では、ZCD 抵抗は 20kΩ に設定されています (式 24 を参照)。

$$R_{ZA} = R_{ZB} = 20k\Omega \quad (24)$$

### 8.2.2.3 HVSEN

HVSEN ピンは UCC28063 の PWMCTL 出力を設定します。PWMCTL オープンドレイン出力は、PFC 出力コンデンサの充電中、ダウンストリーム コンバータを無効化するために使用できます。PWMCTL は、最初は高インピーダンスですが、HVSEN が 2.5V を超えるとグランドにプルします。PWMCTL がアクティブになる点を設定するには、HVSEN ピンの昇圧電圧とグランドとの間に分圧器が必要になります。式 25～式 30 に、出力電圧がその公称値の 90% 以内になったときに PWMCTL ピンがターンオンするように設定する方法を示します。

$$V_{OUT\_OK} = V_{OUT} \times 0.90 \approx 351V \quad (25)$$

抵抗  $R_E$  は分圧器の高電圧側に配置され、PWMCTL 信号のヒステリシスを設定します。この例の場合、99V のヒステリシスが得られるように  $R_E$  が選択されました (式 26 を参照)。電圧要件を満たすため、直列接続された 3 本の抵抗が使われました。

$$R_E = \frac{\text{Hysteresis}}{12\mu A} = \frac{99V}{12\mu A} = 8.25M\Omega \approx 3 \times 2.74M\Omega \quad (26)$$

抵抗  $R_F$  は、PWMCTL アクティブ (ターンオン) スレッショルドを設定するために使われます (式 27 を参照)。

$$R_F = \frac{\frac{2.5V}{V_{OUT\_OK} - 2.5V} - 12\mu A}{R_E} = \frac{\frac{2.5V}{351V - 2.5V} - 12\mu A}{8.22M\Omega} = 82.25k\Omega \quad (27)$$

$R_F$  として標準抵抗値を選択します。

$$R_F = 82.5k\Omega \quad (28)$$

この PWMCTL 出力は、最小出力電圧 ( $V_{OUT\_MIN}$ ) に達するまで、ターンオンしたままになります (式 29 を参照)。

$$V_{OUT\_MIN} = \frac{2.5V(R_E + R_F)}{R_F} = \frac{2.5V(8.22M\Omega + 82.5k\Omega)}{82.5k\Omega} \approx 252V \quad (29)$$

これらの抵抗値に応じて、フェイルセーフ OVP スレッショルドが設定されます (式 30 を参照)。

$$V_{OV\_FAILSAFE} = \frac{4.87V(R_E + R_F)}{R_F} = \frac{4.87V(8.22M\Omega + 82.5k\Omega)}{82.5k\Omega} \approx 490V \quad (30)$$

### 8.2.2.4 出力コンデンサの選択

出力コンデンサ ( $C_{OUT}$ ) は、ホールドアップ要件に基づいて選択します (式 31 を参照)。

$$C_{OUT} \geq \frac{2 \frac{P_{OUT}}{\eta} \frac{1}{f_{LINE}}}{V_{OUT}^2 - (V_{OUT\_MIN})^2} = \frac{2 \frac{300W}{0.92} \frac{1}{47Hz}}{390V^2 - (252V)^2} \approx 156\mu F \quad (31)$$

出力コンデンサとして、2 つの 100 $\mu F$  コンデンサを並列にして使用しました。

$$C_{OUT} = 200\mu F \quad (32)$$

このサイズのコンデンサの場合、低周波数のピーク ツー ピーク出力電圧リップル ( $V_{RIPPLE}$ ) は約 14V です (式 33 を参照)。

$$V_{RIPPLE} = \frac{2 \times P_{OUT}}{\eta} \frac{1}{V_{OUT} \times 4\pi \times f_{LINE} \times C_{OUT}} = \frac{2 \times 300W}{0.92 \times 390V \times 4\pi \times 47Hz \times 200\mu F} \approx 14V_{ppk} \quad (33)$$

ホールドアップ要件に加えて、低周波数 RMS 電流 ( $I_{COUT\_100Hz}$ ) と高周波数 RMS 電流 ( $I_{COUT\_HF}$ ) に耐えるコンデンサを選択する必要があります (式 34 と 式 36 を参照)。高電圧電解コンデンサの製品データシートには通常、低周波数と高周波数の両方の RMS 電流定格が記載されています。

$$I_{COUT\_100Hz} = \frac{P_{OUT}}{V_{OUT} \times \eta \times \sqrt{2}} = \frac{300W}{390V \times 0.92 \times \sqrt{2}} = 0.591\text{ Arms} \quad (34)$$

$$I_{COUT\_HF} = \sqrt{\left( \frac{P_{OUT} 2\sqrt{2}}{2 \times \eta \times V_{IN\_MIN}} \sqrt{\frac{4\sqrt{2}V_{IN\_MIN}}{9\pi V_{OUT}}} \right)^2 - (I_{COUT\_100Hz})^2} \quad (35)$$

$$I_{COUT\_HF} = \sqrt{\left( \frac{300W \times 2\sqrt{2}}{2 \times 0.92 \times 85V} \sqrt{\frac{4\sqrt{2} \times 85V}{9\pi \times 390V}} \right)^2 - (0.591A)^2} \approx 0.966\text{ Arms} \quad (36)$$

### 8.2.2.5 ピーク電流制限のための $R_s$ の選択

UCC28063 のピーク制限コンパレータは、入力電流の合計値を検出し、突入および過負荷状態時に MOSFET を保護するために使用されます。信頼性を確保するため、この設計のピーク電流制限 ( $I_{PEAK}$ ) スレッショルドは、電源投入時に観測される公称最大電流の 120% に設定されています (式 37 を参照)。

$$I_{PEAK} = \frac{2P_{OUT}\sqrt{2}(1.2)}{\eta \times V_{IN\_MIN}} = \frac{2 \times 300W \sqrt{2} \times 1.2}{0.92 \times 85V} \approx 13A \quad (37)$$

電流検出のために標準的な 15mΩ 金属皮膜電流検出抵抗を使用します (式 38 を参照)。通常動作時の電流検出抵抗の電力損失の推定値 ( $P_{RS}$ ) は 0.25W 未満です (式 39 を参照)。

$$R_s = \frac{200mV}{I_{PEAK}} = \frac{200mV}{13A} \approx 15m\Omega \quad (38)$$

$$P_{RS} = \left( \frac{P_{OUT}}{V_{IN\_MIN} \times \eta} \right)^2 R_S = \left( \frac{300W}{85V \times 0.92} \right)^2 \times 15m\Omega \approx 0.22W \quad (39)$$

電流検出抵抗を選択する際の最も重要なパラメータは、サージ定格です。この抵抗は、ヒューズの溶断に必要な電流 ( $F_1$ ) よりも大きい短絡電流に耐える必要があります。 $I^2t$  (アンペア 2 乗秒) は、ヒューズの溶断に必要な電流に起因する熱エネルギーの測定値です。ここで、 $I^2t$  は、RMS 電流の 2 乗に電流の持続時間 (秒) を乗じた値です。設計を短絡状態から保護するため、 $I^2t$  が  $14A^2s$  である 4A ヒューズを選択しました。電流検出抵抗のサージ保護耐性が十分高くなるように、この設計では  $15m\Omega$ 、500mW の金属ストリップ抵抗が選択されました。この抵抗のサージ定格は  $2.5W$  (5 秒間) です。この結果は  $833A^2s$  に相当し、ヒューズが溶断する前の短絡に耐えるのに十分な大きさの  $I^2t$  定格を持っています (式 40 を参照)。

$$I^2t = \frac{2.5W}{0.015\Omega} \times 5s = 833A^2s \quad (40)$$

#### 8.2.2.6 パワー半導体の選択 (Q1、Q2、D1、D2)

Q1、Q2、D1、D2 は、設計の電力要件に基づいて選択します。アプリケーション ノート SLUU138、『UCC38050 100W 臨界導通力率補正 (PFC) プリレギュレータ』では、遷移モード PFC プリレギュレータ用パワー半導体部品を選択する方法を説明しています。

MOSFET (Q1、Q2) のパルスドレイン電流の最大値を 式 41 に示します。

$$I_{DM} \geq I_{PEAK} = 13A \quad (41)$$

MOSFET (Q1、Q2) の RMS 電流の計算値を 式 42 に示します。

$$I_{DS} = \frac{I_{PEAK}}{2} \sqrt{\frac{1}{6} - \frac{4\sqrt{2}V_{IN\_MIN}}{9\pi \times V_{OUT}}} = \frac{13A}{2} \sqrt{\frac{1}{6} - \frac{4\sqrt{2} \times 85V}{9\pi \times 390V}} \approx 2.3A \quad (42)$$

この設計の電力要件を満たすため、Q1 と Q2 に IRFB11N50A 500V MOSFET を選択しました。

昇圧ダイオード (D1、D2) の RMS 電流を 式 43 に示します。

$$I_D = \frac{I_{PEAK}}{2} \sqrt{\frac{4\sqrt{2} \times V_{IN\_MIN}}{9\pi \times V_{OUT}}} = \frac{13A}{2} \sqrt{\frac{4\sqrt{2} \times 85V}{9\pi \times 390V}} \approx 1.4A \quad (43)$$

この設計の電力要件を満たすため、D1 と D2 に MURS360T3 600V ダイオードを選択しました。

#### 8.2.2.7 ブラウンアウト保護

規定された最小動作入力電圧の約 75% でブラウンアウト保護が作動するように、抵抗  $R_A$  および  $R_B$  を選択します。抵抗  $R_A$  はブラウンアウトヒステリシス コンパレーターを設定します。この抵抗は、ヒステリシスが  $17V$  (約  $12V_{RMS}$ ) になるように選択されます。式 44～式 47 に、 $R_A$  と  $R_B$  の計算式を示します。

$$R_A = \frac{\text{Hysteresis}}{2\mu A} = \frac{17V}{2\mu A} = 8.5M\Omega \quad (44)$$

電圧要件を満たすため、 $R_A$  として 3 本の  $2.87M\Omega$  抵抗を直列にして使用しました。

$$R_A = 3 \times 2.87 M\Omega = 8.61 M\Omega \quad (45)$$

$$R_B = \frac{1.4V \times R_A}{V_{IN\_MIN} \times 0.75\sqrt{2} - 1.4V} = \frac{1.4V \times 8.61 M\Omega}{85V \times 0.75\sqrt{2} - 1.4V} = 135.8 k\Omega \quad (46)$$

$R_B$  として標準値を選択します。

$$R_B = 133 k\Omega \quad (47)$$

この設計例では、440ms より長い間入力が 66V<sub>RMS</sub> を下回ると、ブラウンアウトが作動 (PFC がシャットダウン) し、入力が 78V<sub>RMS</sub> に達すると、ブラウンアウトは停止 (完全ソフトスタートで再起動) します。

### 8.2.2.8 コンバータのタイミング

最大オン時間  $T_{ON}$  は、式 48 で決定される  $f_{MIN}$  に依存します。確実に正常動作するように、昇圧インダクタンスの最大値 ( $L_{1MAX}$ ) と出力電力 ( $P_{OUT}$ ) に基づいてタイミングを設定する必要があります。この設計例では、昇圧インダクタを最大 390μH に設定できます。式 49 に示すように、タイミング抵抗  $R_T$  を計算します。

$$f_{MIN} = \frac{\eta \times (V_{IN\_MIN})^2 \left(1 - \frac{V_{IN\_MIN} \times \sqrt{2}}{V_{OUT}}\right)}{P_{OUT} \times L_{1MAX}} = \frac{0.92 \times (85V)^2 \left(1 - \frac{85V \times \sqrt{2}}{390V}\right)}{300W \times 390\mu H} = 39.2 kHz \quad (48)$$

$$R_T = \frac{133 k\Omega \left(1 - \frac{V_{IN\_MIN} \times \sqrt{2}}{V_{OUT}}\right)}{4.85V \times \frac{4\mu s}{V} \times f_{MIN}} = \frac{133 k\Omega \left(1 - \frac{85V \times \sqrt{2}}{390V}\right)}{4.85V \times \frac{4\mu s}{V} \times 39.2 kHz} \approx 121 k\Omega \quad (49)$$

この結果、式 50 に示すように、最大周波数クランプ ( $f_{MAX}$ ) が設定され、軽負荷時の効率が向上します。

$$f_{MAX} = \frac{133 k\Omega}{2\mu s \times R_T} = \frac{133 k\Omega}{2\mu s \times 121 k\Omega} \approx 550 kHz \quad (50)$$

### 8.2.2.9 $V_{OUT}$ の設定

PFC が無効化されたときの電源ラインの負荷を最小化するため、抵抗  $R_C$  を選択します。高電圧要件を満たすため、2 本以上の抵抗を直列にして抵抗  $R_C$  を構成します。次に、 $R_C$ 、基準電圧  $V_{REF}$ 、目標出力電圧  $V_{OUT}$  に基づいて、抵抗  $R_D$  を計算します。式 51～式 54 に示す値に基づき、1 次側出力過電圧保護スレッショルドを、式 55 に示すように設定します。

$$R_C = 2.74 M\Omega + 2.74 M\Omega + 3.01 M\Omega = 8.49 M\Omega \quad (51)$$

$$V_{REF} = 6 V \quad (52)$$

$$R_D = \frac{V_{REF} \times R_C}{V_{OUT} - V_{REF}} = \frac{6V \times 8.49 M\Omega}{390V - 6V} = 132.7 k\Omega \quad (53)$$

$R_D$  として標準値を選択します。

$$R_D = 133 k\Omega \quad (54)$$

$$V_{OVP} = 6.48V \frac{R_C + R_D}{R_D} = 6.48V \frac{8.49M\Omega + 133k\Omega}{133k\Omega} = 420.1V \quad (55)$$

### 8.2.2.10 電圧ループ補償

抵抗  $R_Z$  は、低周波数リップルが電圧アンプの出力範囲の 2% 未満に減衰するように、値を設定します。この値により、効率の向上と入力電流の高調波歪みの低減が確保されます。

式 56 に、トランスコンダクタンスアンプの小信号ゲインを示します。

$$g_m = 50\mu S \quad (56)$$

式 57 に、分圧器の帰還ゲインを示します。

$$H = \frac{V_{REF}}{V_{OUT}} = \frac{6V}{390V} \approx 0.015 \quad (57)$$

$R_Z$  の値は、式 58 に示すように計算されます。

$$R_Z = \frac{100mV}{V_{RIPPLE} \times H \times g_m} = \frac{100mV}{14V \times 0.015 \times 50\mu S} = 9.52 k\Omega \quad (58)$$

次に、ライン周波数の 1/5 で 45° の位相マージンが加算されるように  $C_Z$  を設定します（式 59 を参照）。

$$C_Z = \frac{1}{2\pi \times \frac{f_{LINE}}{5} \times R_Z} = \frac{1}{2\pi \times \frac{47Hz}{5} \times 9.52k\Omega} = 1.78\mu F \quad (59)$$

$C_P$  は、高周波数スイッチングノイズが減衰するように、値を設定します（式 60 を参照）。

$$C_P = \frac{1}{2\pi \times \frac{f_{MIN}}{2} \times R_Z} = \frac{1}{2\pi \times \frac{45kHz}{2} \times 9.52k\Omega} = 770pF \quad (60)$$

$R_Z$ 、 $C_Z$ 、 $C_P$  として標準値を選択します（式 61～式 63 を参照）。

$$R_Z = 9.53k\Omega \quad (61)$$

$$C_Z = 2.2\mu F \quad (62)$$

$$C_P = 820pF \quad (63)$$

### 8.2.3 アプリケーション曲線

実装の詳細とアプリケーション曲線については、『UCC28063EVM-723 300W インターリーブ PFC プリレギュレータ EVM ユーザー ガイド』、[SLUU512](#) を参照してください。

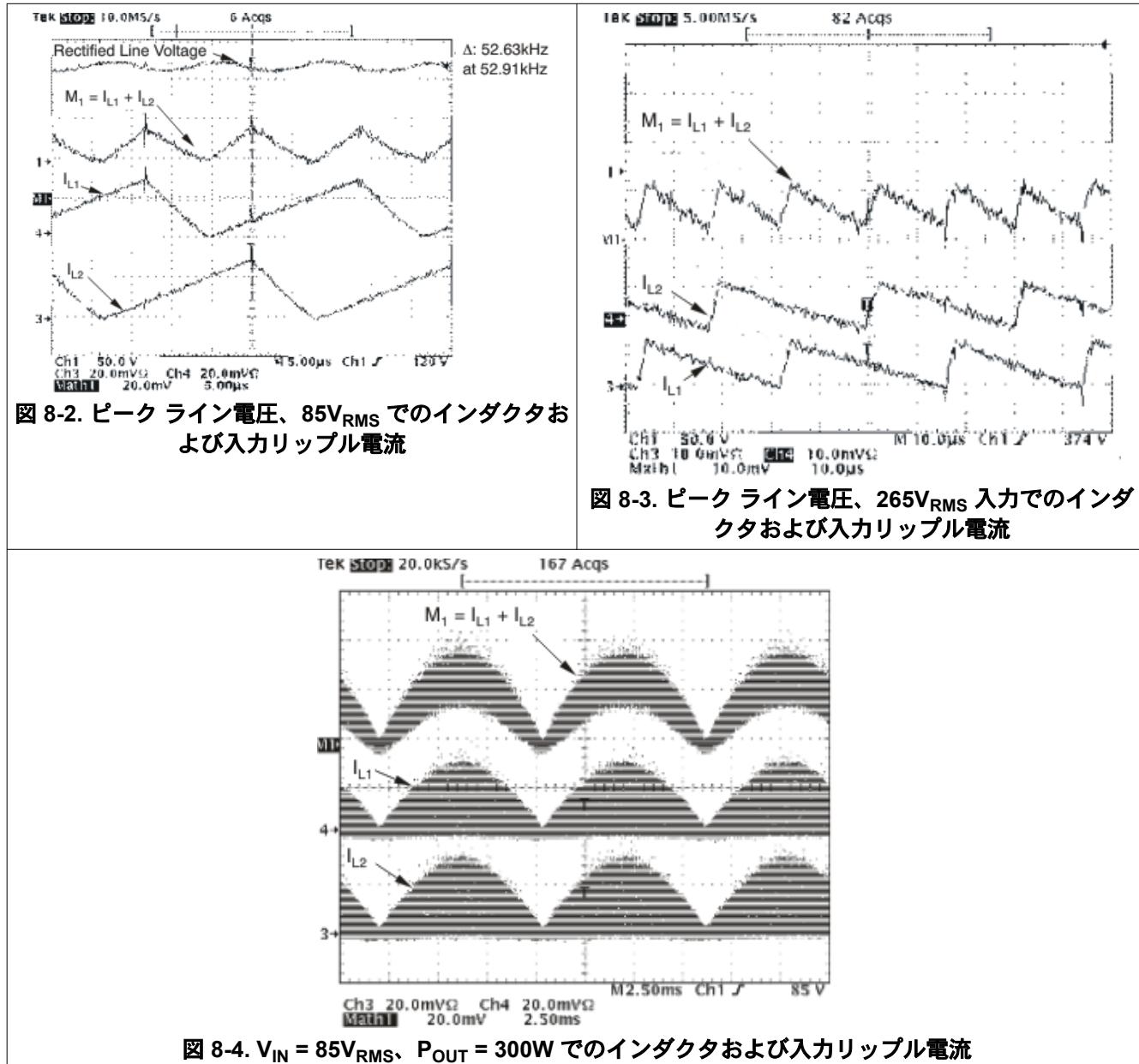

#### 8.2.3.1 Natural Interleaving による入力リップル電流の相殺

図 8-2～図 8-4 に、入力電流 ( $M_1 = I_{L1} + I_{L2}$ )、インダクタのリップル電流 ( $I_{L1}, I_{L2}$ ) と整流済みライン電圧との関係を示します。これらのグラフから、Natural Interleaving により、個々のインダクタの電流リップルに起因する入力 (および出力) リップル電流全体の大きさが低減されることがわかります。

### 8.2.3.2 ブラウンアウト保護

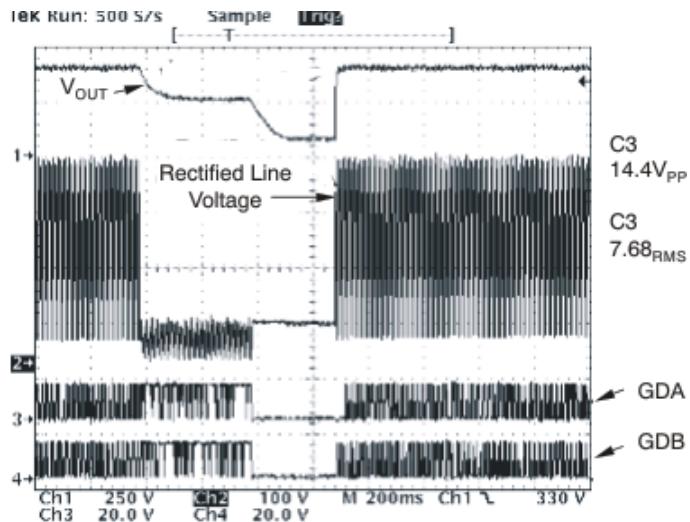

UCC28063 は、VINAC ピンが RMS 入力電圧が低すぎることを検出すると両方のゲート駆動 (GDA と GDB) を遮断するブラウンアウト保護機能を備えています。この評価基板は、ラインが 64VRMS を下回るとブラウンアウト状態に移行するように設計されています。UCC28063 制御デバイスが、入力がブラウンアウト状態にあると判断すると、ゲートドライバをシャットダウンする前にラインが回復できるように、400ms のタイマが起動します。400ms のブラウンアウトの後、両方のゲートドライバがターンオフします (図 8-5 を参照)。

図 8-5. 265V<sub>RMS</sub> でのライン ブラウンアウト イベントに対する UCC28063A の応答

## 9 電源に関する推奨事項

本 IC は、その電力のすべてを VCC ピン経由で受け取ります。PFC 段のすべての動作条件を通じて、この電圧は可能な限り安定化されている必要があります。通常、非常に良好に安定化された電圧をバイアス巻線に供給できるダウンストリーム DC/DC 段から、この段のための定常バイアスを生成することを検討します。この手法により、バイアス生成の総合的な効率が向上します。効率がより低い代替手段として、UA78L15A などの直列接続の固定正電圧レギュレータを検討します。

すべての通常および異常動作条件において、VCC 電圧と入力電流の両方が推奨動作範囲内に維持されることが非常に重要です。VCC 過電圧は内部電圧クランプでの過剰な電力消費の原因となる可能性があり、低電圧はパワー MOSFET の不適切な駆動レベル、UVLO イベント (PFC 動作の中止の原因)、各種オンチップ リニア レギュレータおよび基準電圧のヘッドラーム不足の原因となる可能性があります。

また、MOSFET のゲート駆動に必要な大きな RMS およびピーク電流が 13.5V リニア レギュレータ IC によって供給され、このリニア レギュレータには、外部デカップリング容量を追加する必要がないことにも注意します。より大きい電力、Q<sub>G</sub> が非常に大きいパワー MOSFET、高いスイッチング周波数が必要な場合、パワー MOSFET を駆動するための外付けトランジスタの使用を検討します。これらの外付けトランジスタは、IC の動作温度を低下させ、VCC の入力電流が最大定格を超えないようにするのに役立ちます。

VREF と AGND の間と、VCC と PGND の間に、IC にできる限り近付けてデカップリング コンデンサを配置します。これらのデカップリング コンデンサには、ESR が非常に小さいセラミック コンデンサを使用する必要があります。PGND と AGND の間の DC または高周波 AC 電圧の差が無視できる程度になるように、PGND と AGND を制御 IC とスター接続するのが理想的です。EVM で使用されているデカップリング コンデンサの値と同等、またはそれより少し大きい値のデカップリング コンデンサを使用します。

適切にレギュレートされたバイアス電力が、電源投入時にはできるだけ早く、電源切断時にはできるだけ遅くまで供給されるように、VCC バイアス ブートストラップ装置の起動およびシャットダウンには細心の注意を払います。これらの起動バイアス ブートストラップ回路が、定常状態での不必要的電力消費の原因にならないことを確認します。

## 10 レイアウト

## 10.1 レイアウトのガイドライン

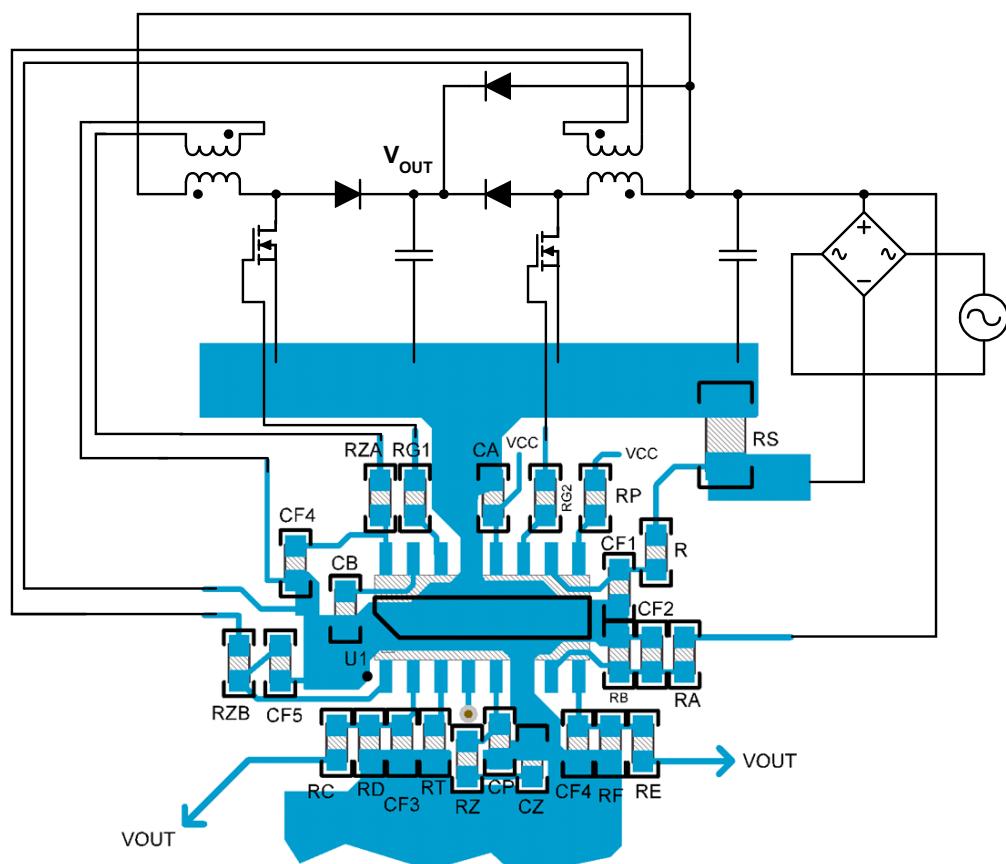

インターリープ遷移モード PFC システム アーキテクチャでは、入力および出力リップル電流が大幅に低減されるため、回路ではより小型で安価なフィルタが使用できます。インターリープの利点を最大化するため、2 つの相電流を結合した後に入力および出力フィルタコンデンサを配置する必要があります。その他のパワー マネージメント デバイスと同様に、プリント基板 (PCB) をレイアウトする際はスター グラウンド手法を使い、フィルタコンデンサをデバイス グラウンドのできるだけ近くに配置することが重要です。昇圧インダクタからの容量結合に起因する干渉を最小限に抑えるため、本デバイスを昇圧インダクタから 1 インチ (25.4mm) 以上離して配置する必要があります。また、本デバイスを磁気素子の下に配置しないことも推奨します。正確なタイミングが求められるため、タイミング設定抵抗  $R_T$  を TSET ピンのできるだけ近くに配置し、可能な限り短い経路でアナログ グラウンド ピンに接続する必要があります。推奨される部品の配置とレイアウトについては、[図 10-1](#) を参照してください。

## 10.2 レイアウト例

PHB ピンと VREF ピンは、ボードの裏面でジャンパを使って接続します。

図 10-1. 推奨される PCB レイアウト

## 11 デバイスおよびドキュメントのサポート

### 11.1 デバイス サポート

#### 11.1.1 開発サポート

##### 11.1.1.1 関連製品

表 11-1 に、UCC28063 と特性が類似する各種のテキサス・インストルメンツ製品を示します。

**表 11-1. テキサス・インストルメンツの関連製品**

| デバイス        | 説明                                               |

|-------------|--------------------------------------------------|

| UCC28050/51 | 低～中電力アプリケーション向け遷移モード PFC コントローラ                  |

| UCC28019    | 8 ピン、連続導通モード (CCM) PFC コントローラ (スルーレート補正電流機能付き)   |

| UCC28019A   | 8 ピン、連続導通モード (CCM) PFC コントローラ (2 レベル電圧誤差ゲイン機能付き) |

| UCC28060    | 2 相インターリーブ遷移モード PFC コントローラ (入力電圧範囲ゲイン変更機能付き)     |

| UCC28061    | 2 相インターリーブ遷移モード PFC コントローラ (入力電圧ゲイン変更機能なし)       |

| UCC28070    | 2 相インターリーブ CCM (平均電流モード) PFC コントローラ              |

#### 11.1.2 デバイスの命名規則

##### 11.1.2.1 ピンの詳細説明

**アナログ グランド:** アナログ信号のバイパスコンデンサ、補償部品、アナログ信号のリターンをこのピンに接続します。低電流アナログ回路に干渉しないように、電源部品の大電流ノイズ信号を分離するため、アナログ グランドと電源グランドを 1 点で接続します。

**エラー アンプ出力:** エラー アンプはトランスクンダクタンス アンプであるため、この出力は高インピーダンスの電流源です。このピンと AGND との間に電圧レギュレーション ループ補償部品を接続します。ゲート駆動出力で観測されるオン時間は、このピンの電圧から約 125mV のオフセットを減算した値に比例します。通常動作中、エラー アンプは VSENSE の小信号外乱に対して 55μS のトランスクンダクタンスを保ち、VSENSE が VSENSEreg から ±5% 以上逸脱すると、約 290μS に変化します。AC ラインドロップアウト状態では、エラー アンプ出力は無効化され、ドロップアウト状態が続く間、内部 4μA 電流源が COMP を放電します。VSENSE に基づく OV イベント中、OV 状態が解消されるまで、COMP から GND に内部 2kΩ 抵抗が接続されています。ソフト スタート トリガ イベント (UVLO、ディセーブル、ブラウンアウト、HVSEN 過電圧、TSET フォルト、CS オープン、サーマル シャットダウン) の間、エラー アンプ出力は無効化され、COMP は内部 2kΩ 抵抗によって Low にプルされています。このソフト スタート条件は、トリガ イベントが解消され、COMP が 20mV 未満に放電された後にのみ開始されるため、低い COMP 電圧と短いオン時間で回路は確実に再起動します。(COMP が 20mV 未満に低下するのを妨げるような低インピーダンスの電源に COMP を接続しないでください。)ソフト スタート中、VSENSE < VREF/2 である限り、エラー アンプの高トランスクンダクタンスは有効化され、COMP 電流は -125μA になります。VSENSE が VREF/2 を超えると、高ゲインは無効化され、最大 COMP 電流が約 -16μA である小信号ゲイン機能のみが利用できます。VSENSE > 0.983VREF (約 5.9V) になると、通常動作に復帰します。

**電流検出入力:** 電流検出抵抗と、ダイオード ブリッジの負端子を、このピンに接続します。電流検出抵抗のリターンは、独立したパターンで AGND ピンに接続します。入力電流が増加するにつれて、CS の電圧はより負方向に変化します。このサイクル単位の過電流保護機能は、CS の立ち上がりスレッショルド (2 相動作で約 -200mV、単相および位相フェイル状態で約 -167mV) を横切って、CS が負方向に変化すると、両方のゲートドライバ出力 (GDx) をターンオフすることで入力電流を制限します。ゲート駆動出力は、CS の立ち下がりスレッショルド (約 -15mV) まで CS が低下するまで、Low に維持されます。電流検出は、どちらかの GDx 出力の立ち上がりおよび立ち下がりエッジの後、約 100ns にわたってブランкиングされます。これは、ゲート駆動電流から発生する可能性があるノイズと、インダクタ電流がパワー FET から昇圧ダイオードに切り替わるときに発生する可能性があるノイズをフィルタ処理します。ほとんどの場合、電流検出の追加のフィルタ処理は不要です。外部フィルタ処理が必要と判断される場合、または AC 突入状態時に CS ピンに過剰な負電圧が印加されるのを防ぐため、直列抵抗を介して電流検出抵抗を CS ピンに接続することを推奨します。CS バイアス電流が原因で、精度を維持するには、この外付け抵抗を 100Ω 未満にする必要があります。CS ピンがオープンになると、CS の電

圧は約 +1.5V まで上昇します。この条件は、ソフトスタートトリガ フォルト条件 (CS オープン) として検出および処理されます。

**チャネル A とチャネル B のゲート駆動出力:**これらのピンは、実現可能な最短の接続を使用して、各相のパワー FET のゲートに接続します。この接続に 0.5 インチ (12.6mm) より長いパターンを使用する必要がある場合、パターンの直列インダクタンスによって何らかのリギングが発生することがあります。GDA と GDB に直列に小さい値の抵抗を追加することで、このリギングを減衰させることができます。

**高電圧出力検出:** UCC28063 は、单一故障が発生しても出力が安全なレベルを超えて昇圧されないように、フェイルセーフ OVP を内蔵しています。出力過電圧は、VSENSE と HVSEN の両方によって監視されていますが、どちらかのピンがそれぞれの過電圧レッショルドを超えた場合のそれらの動作は異なります。2 本のピンを使用して過電圧を監視することで、冗長保護と耐故障性が実現できます。HVSEN が過電圧レッショルドを上回ると、コントローラの完全ソフトスタートがトリガされます。HVSEN の電圧が動作領域内にある際に、ダウンストリーム パワー コンバータを有効化するために HVSEN を使うこともできます。HVSEN が 2.5V を超えると、PWMCTL 出力は Low に駆動されます (その他の障害が存在しない限り)。HVSEN が 2.5V を下回ると、PWMCTL 出力は高インピーダンスになります。目的の過電圧およびパワー グッド レッショルドになるように HVSEN 分圧比を選択します。ヒステリシス電流に基づいて、目的のパワー グッド ヒステリシスになるように HVSEN 分圧器のインピーダンスを選択します。動作中、HVSEN は 0.8V を下回ることはできません。HVSEN を 0.8V 未満に低下させると、UCC28063 は、出荷時テスト専用の特殊なテスト モードに入ります。ノイズをフィルタ処理し、過電圧シャットダウンの誤動作を防止するため、HVSEN と AGND の間にバイパス コンデンサを接続することを推奨します。

**位相 B の有効化 / 無効化:**このピンに印加される電圧が位相 B イネーブル レッショルドを下回ると、昇圧コンバータの位相 B と位相障害検出器が無効化されます。位相 B が無効化されると、位相 A に対して指令されたオン時間が即座に倍増するため、位相管理過渡時に COMP 電圧を一定に保つことができます。必要に応じて、PHB ピンを使って外部位相管理制御回路を追加できます。位相管理を無効化にするには、PHB ピンを VREF ピンに接続します。

**PWM 制御出力:**HVSEN が HVSEN グッド領域内 ( $HVSEN > 2.5V$ ) に入り、かつフェイルセーフ OV が発生しておらず、かつ 2 相モードで動作中の位相障害状態が発生していない場合、このオープンドレイン出力は Low に遷移します (PHB ピンを参照)。それ以外の場合、PWMCTL は高インピーダンスです。

**タイミング設定:**PWM オン時間設定入力。オン時間と COMP 電圧の関係と、ゲート駆動出力の最小スイッチング周期を設定するため、TSET と AGND の間に抵抗を接続します。TSET 入力がオープンまたはショート状態にある場合、保護回路によりコントローラは動作しないようになっています。このピンがオープンである限り、完全ソフトスタート条件がトリガされます。このピンが GND に短絡された場合、その電流は制限され、ソフトスタート条件もトリガされます。

**バイアス電源入力:**このピンを、14V~21V の制御されたバイアス電源に接続します。また、このピンと PGND との間に  $0.1\mu F$  以上のセラミック バイパス コンデンサを最短の基板パターンで接続します。このバイアス電源は、本デバイス内のすべての回路に電力を供給し、定常的な DC 電流と過渡的なパワー MOSFET ゲート充電電流の合計を供給できる必要があります。低電圧誤動作防止 (UVLO) またはスタンバイ状態 ( $VSENSE < 1.25V$ ) 中、入力バイアス電流は非常に小さくなります。

**入力 AC 電圧検出:**通常動作の場合、整流された入力商用電源の両端に接続された分圧器に、このピンを接続します。VINAC の電圧がブラウンアウト フィルタ時間よりも長くブラウンアウト レッショルドを下回ると、本デバイスはブラウンアウト モードに入り、両方の出力ドライバが無効化され、完全ソフト スタートがトリガされます。目的のブラウンアウト レッショルドになるように、入力分圧比を選択します。ヒステリシス電流に基づいて、目的のブラウンアウト ヒステリシスになるように分圧器のインピーダンスを選択します。VINAC がドロップアウト フィルタ時間よりも長くドロップアウト レッショルドを下回ると、ドロップアウト 条件がトリガされます。エラー アンプは無効化され、ドロップアウト 状態が続く間、内部  $4\mu A$  電流源が COMP を放電します。VINAC がドロップアウト クリアしきい値を超えると、ドロップアウト 条件は即座にクリアされ、通常動作が再開されます。

**基準電圧出力:**このピンと AGND との間に  $0.1\mu F$  以上のセラミック バイパス コンデンサを接続します。UVLO および VSENSE ディセーブルの間、バイアス電流を節約し、スタンバイ効率を向上させるため、VREF はターンオフします。必要な非パルス電源電流の合計が数ミリアンペア未満であるその他の回路にバイアス電圧を印加するために、この基準出力を使うことができます。

**出力 DC 電圧検出:**このピンは、パワー コンバータの出力に接続された分圧器に接続します。閉ループ システムでは、VSENSE の電圧はエラー アンプの基準電圧にレギュレートされます。目的の出力電圧が得られるように、出力の分圧比を選択します。最良の出力レギュレーション精度とノイズ耐性を実現するため、この分圧器のグランド側を、独立した短いパターンでアナログ グラント (AGND) に接続します。VSENSE 電圧が 1.25V のイネーブル スレッショルドを上回ると、コントローラの動作が有効化されます。VSENSE は、出力を無効化して VCC 電流を低減するため、オープン ドレインのロジック出力、または低リーケ ダイオードと直列に接続した 6V 超のロジック出力で Low にプルできます。出力過電圧の 2 つのレベルがこの入力で検出されます。VSENSE が第 1 レベルの過電圧保護スレッショルド  $V_{LOW\_OV}$  を上回ると、ゲート駆動オン時間を素早く短縮するため、COMP に内部  $2k\Omega$  抵抗が接続されます。VSENSE が引き続き第 2 レベルのスレッショルド  $V_{HIGH\_OV}$  を超えて上昇すると、GDA と GDB は即座にオフにラッチされます。VSENSE が OV クリア スレッショルドを下回ると、このラッチはクリアされます。VSENSE が切り離された場合、VSENSE を Low にプルする内部電流源が開ループ保護によって提供されるため、コントローラが無効化され、ソフトスタート条件がトリガされます。

**ゼロ電流検出入力:**これらの入力は、各相の昇圧インダクタ電流がゼロになる際の立ち下がりエッジを検出するために使われます。これらの入力は 0V~3V の範囲でクランプされます。対応する昇圧インダクタのゼロクロス検出 (ZCD) 卷線に、電流制限抵抗を介して各ピンを接続します。この抵抗値は、クランプ電流が  $\pm 3mA$  未満に制限されるように選択する必要があります。インダクタの巻線の極性は、インダクタ電流がゼロまで減衰するとき、この ZCD 電圧が低下するように設定する必要があります。インダクタ電流がゼロまで低下したとき、ゲート駆動出力を立ち上げるには、ZCD 入力を立ち下がりスレッショルド (約 1V) よりも下げる必要があります。その後、パワー MOSFET がターンオフすると、次の ZCD 立ち下がりエッジにロジックが対応できるように、ZCD 入力を立ち上がりスレッショルド (約 1.7V) よりも上げる必要があります。

## 11.2 ドキュメントのサポート

### 11.2.1 関連資料

以下の参考文献、設計ツール、および設計ソフトウェアを含む他の参考資料へのリンクが、

[www.ti.com/power-management](http://www.ti.com/power-management) で提供されています。

- 評価基板、『UCC28063EVM 300W インターリーブ PFC プリレギュレータ』([SLUU512](#))

- アプリケーション ノート、『UCC38050 100W 臨界導通力率補正 (PFC) プリレギュレータ』([SLUU138](#))

### 11.3 商標

DLP™ and Natural Interleaving™ are trademarks of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 11.4 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 11.5 用語集

### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報はそのデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、左側のナビゲーションを参照してください。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](#) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2024, Texas Instruments Incorporated

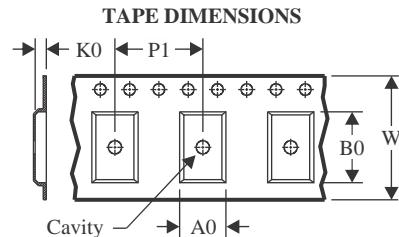

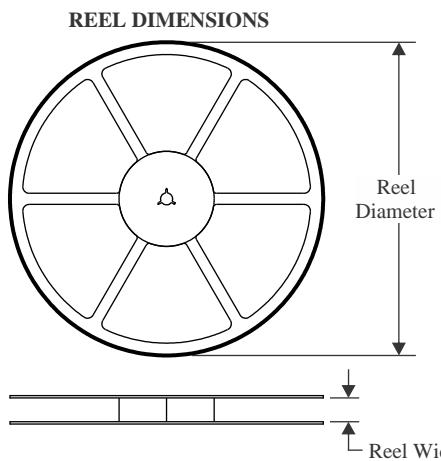

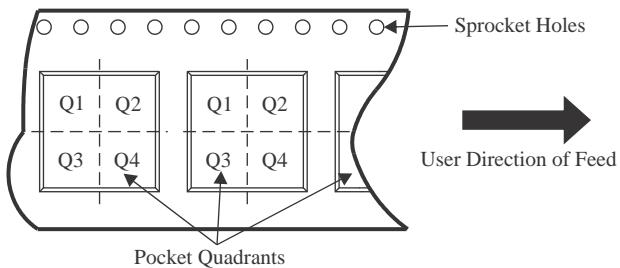

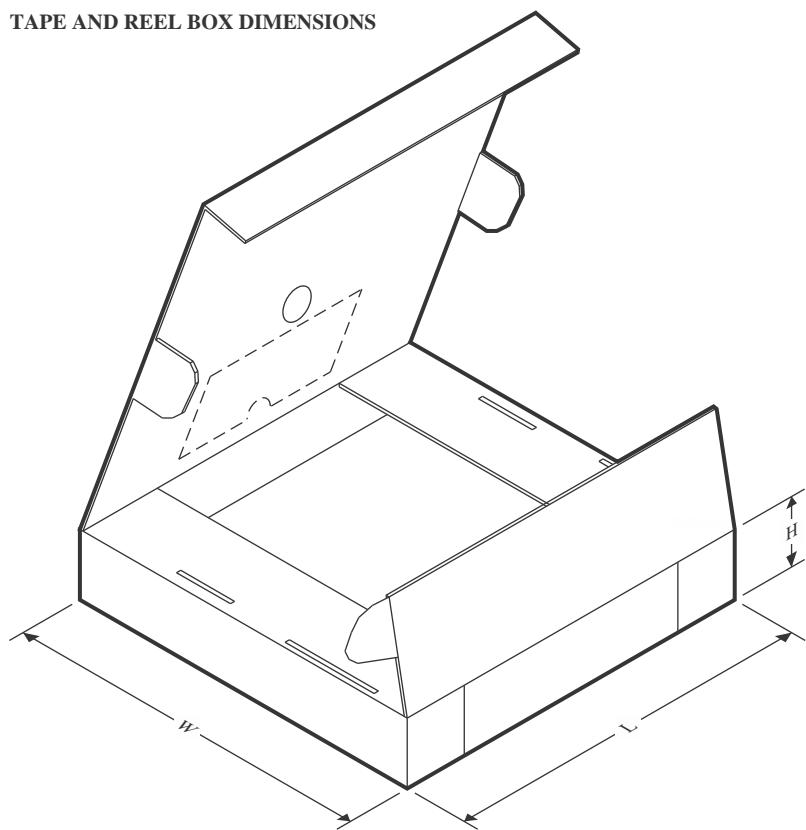

**PACKAGING INFORMATION**

| Orderable part number      | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|----------------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| <a href="#">UCC28063D</a>  | Active        | Production           | SOIC (D)   16  | 40   BULK             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | UCC28063            |

| UCC28063D.A                | Active        | Production           | SOIC (D)   16  | 40   BULK             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | UCC28063            |

| UCC28063D.B                | Active        | Production           | SOIC (D)   16  | 40   BULK             | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | UCC28063            |

| <a href="#">UCC28063DR</a> | Active        | Production           | SOIC (D)   16  | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | UCC28063            |

| UCC28063DR.A               | Active        | Production           | SOIC (D)   16  | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | UCC28063            |

| UCC28063DR.B               | Active        | Production           | SOIC (D)   16  | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | UCC28063            |

| UCC28063DRG4               | Active        | Production           | SOIC (D)   16  | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | UCC28063            |

| UCC28063DRG4.A             | Active        | Production           | SOIC (D)   16  | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | UCC28063            |

| UCC28063DRG4.B             | Active        | Production           | SOIC (D)   16  | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | UCC28063            |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.