# UCC27301A-Q1 車載用、8V UVLO、インターロックおよびイネーブル機能搭載、120V、3.7A/4.5A、ハーフブリッジ ドライバ

## 1 特長

- ハーフブリッジ構成の 2 つの N チャネル MOSFET を駆動

- 車載アプリケーション用に AEC-Q100 認定済み:

- デバイス温度グレード 1

- 接合部温度範囲: -40°C ~ +150°C

- HB ピンで 120V の絶対最大電圧

- 3.7A シンク、4.5A ソース出力電流

- VDD 動作範囲: 8V ~ 17V (絶対最大定格 20V)、UVLO 付き

- HS ピンの負の絶対最大過渡耐性: -(28 - VDD)V (100ns 未満のパルス)

- 入力ピンの絶対最大耐性: -10V ~ +20V、電源電圧範囲にかかわらず (TTL 互換)

- スイッチング パラメータ:

- 伝搬遅延時間 (標準値): 20ns

- 立ち上がり時間 7.2ns、立ち下がり時間 5.5ns (1000pF 負荷時)

- 遅延マッチング: 4ns (標準値)

- ブートストラップ ダイオードを内蔵

- 入力インターロック

- イネーブル / ディセーブル機能、ディセーブル時の低消費電流 (標準値 3µA) (DRC パッケージのみ)

- 機能安全対応**

- 機能安全システムの設計に役立つ資料を利用可能

## 2 アプリケーション

- 車載用 DC/DC コンバータと OBC

- 2 輪車と 3 輪車のトラクション ドライブとバッテリ パック

- 電動パワー ステアリング (EPS)

- ワイヤレス充電

- スマート ガラス モジュール

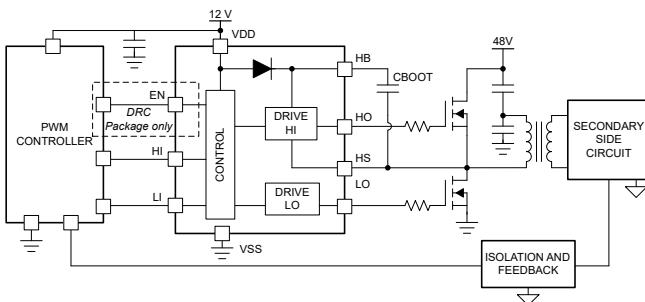

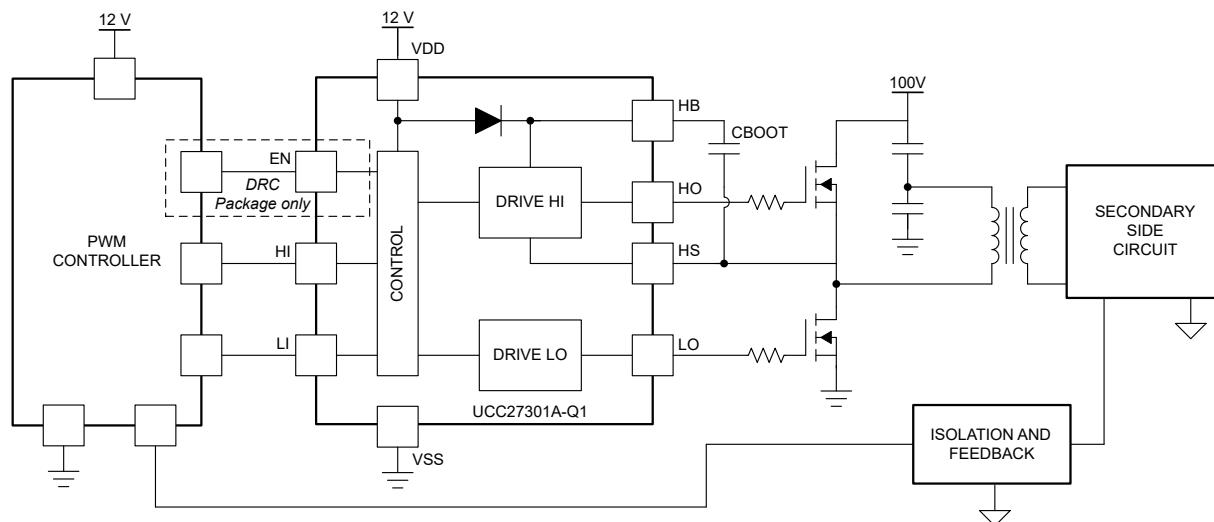

代表的なアプリケーションの図

## 3 概要

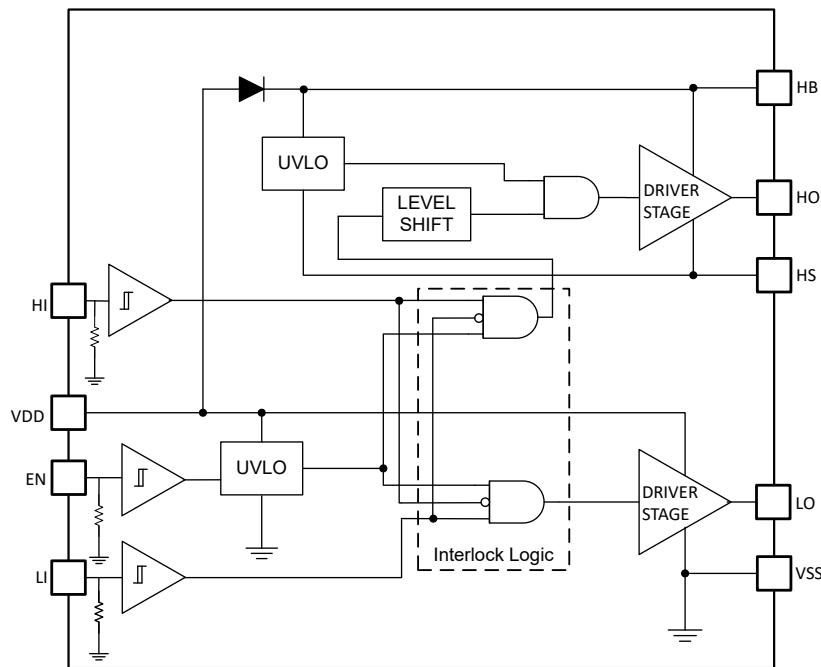

UCC27301A-Q1 は、ハーフブリッジまたは同期整流降圧構成の 2 つの N チャネル MOSFET を駆動するよう設計された堅牢なゲート ドライバで、絶対最大ブートストラップ電圧は 120V です。UCC27301A-Q1 はピーク ソース電流能力が 3.7A、ピーク シンク電流能力が 4.5A であるため、ミラー プラトー通過時のスイッチング損失を最小限に抑えて大電力 MOSFET を駆動できます。スイッチングノード (HS ピン) の負の過渡電圧を処理できるため、寄生インダクタンスや浮遊容量によって生じる固有の負電圧からハイサイド チャネルを保護できます。

入力は電源電圧に依存せず、-10V および +20V の絶対最大定格に対応できます。ローサイドとハイサイドのゲート ドライバは、お互いにターンオン / ターンオフ間 4ns でマッチングされ、それぞれ LI および HI 入力ピンで制御されます。ただし、入力インターロック ロジックは、LI 入力と HI 入力の両方が同時に High になると、両方のドライバ出力が Low になります。120V 定格のブートストラップ ダイオードが内蔵されているため、ディスクリート ブートストラップ ダイオードは必要はありません。ハイサイド ドライバとローサイド ドライバの両方に低電圧誤動作防止機能 (UVLO) が搭載され、対称的なオン/オフ動作を実現しながら、駆動電圧が規定のスレッショルド未満の場合は出力が強制的に Low になります。

### パッケージ情報

| 部品番号                            | パッケージ (1)               | イネーブルピン | 本体サイズ (公称)    |

|---------------------------------|-------------------------|---------|---------------|

| UCC27301AQDDARQ1                | DDA (PowerPAD™ SOIC, 8) | なし      | 4.9mm × 3.9mm |

| UCC27301AQDRCRQ1 <sup>(2)</sup> | DRC (VSON, 10)          | あり      | 3mm × 3mm     |

(1) 供給されているすべてのパッケージについては、[セクション 12](#) を参照してください。

(2) 事前情報

## 目次

|                      |           |                               |           |

|----------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>          | <b>1</b>  | 7.1 アプリケーション情報                | <b>16</b> |

| <b>2 アプリケーション</b>    | <b>1</b>  | 7.2 代表的なアプリケーション              | <b>16</b> |

| <b>3 概要</b>          | <b>1</b>  | <b>8 電源に関する推奨事項</b>           | <b>20</b> |

| <b>4 ピン構成および機能</b>   | <b>3</b>  | <b>9 レイアウト</b>                | <b>20</b> |

| <b>5 仕様</b>          | <b>4</b>  | 9.1 レイアウトのガイドライン              | <b>20</b> |

| 5.1 絶対最大定格           | 4         | 9.2 レイアウト例                    | <b>21</b> |

| 5.2 ESD 定格           | 4         | 9.3 熱に関する注意事項                 | <b>22</b> |

| 5.3 推奨動作条件           | 4         | <b>10 デバイスおよびドキュメントのサポート</b>  | <b>23</b> |

| 5.4 熱に関する情報          | 4         | 10.1 デバイス サポート                | <b>23</b> |

| 5.5 電気的特性            | 5         | 10.2 ドキュメントのサポート              | <b>23</b> |

| 5.6 スイッチング特性         | 6         | 10.3 ドキュメントの更新通知を受け取る方法       | <b>23</b> |

| 5.7 タイミング図           | 7         | 10.4 サポート・リソース                | <b>23</b> |

| 5.8 代表的特性            | 8         | 10.5 商標                       | <b>23</b> |

| <b>6 詳細説明</b>        | <b>11</b> | 10.6 静電気放電に関する注意事項            | <b>23</b> |

| 6.1 概要               | 11        | 10.7 用語集                      | <b>23</b> |

| 6.2 機能ブロック図          | 12        | <b>11 改訂履歴</b>                | <b>23</b> |

| 6.3 機能説明             | 12        | <b>12 メカニカル、パッケージ、および注文情報</b> | <b>25</b> |

| 6.4 デバイスの機能モード       | 15        | 12.1 テープおよびリール情報              | <b>25</b> |

| <b>7 アプリケーションと実装</b> | <b>16</b> | 12.2 メカニカル データ                | <b>27</b> |

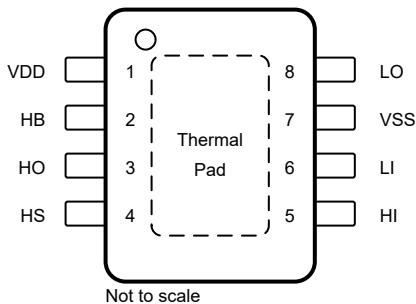

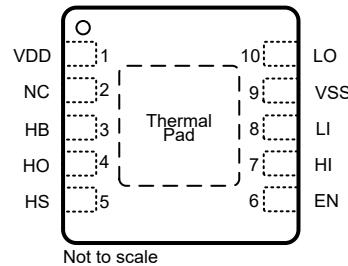

## 4 ピン構成および機能

図 4-1. DDA パッケージ 8 ピン SOIC (PowerPad™ 付き) 上面図

図 4-2. DRC パッケージ 10 ピン SON 上面図

表 4-1. ピンの機能

| ピン                   |      | 種類 <sup>(3)</sup> | 説明  |                                                                                                                                                                                              |

|----------------------|------|-------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                   | DDA  |                   | DRC |                                                                                                                                                                                              |

| EN                   | 該当なし | 6                 | I   | イネーブル入力。このピンを High にすると、ドライバはイネーブルになります。フローティング状態または Low にプルされると、ドライバはディセーブルになります。影響を受けやすいアプリケーションでノイズ耐性を高めるため、EN と VSS の間にフィルタコンデンサ (通常は 1~10nF) を配置することを推奨します。                             |

| HB                   | 2    | 3                 | P   | ハイサイドブートストラップ電源。ブートストラップダイオードはオンチップですが、外部ブートストラップコンデンサが必要です。ブートストラップコンデンサの正側をこのピンに接続します。HB バイパスコンデンサの標準範囲は 0.022μF~0.1μF です。コンデンサの値はハイサイド MOSFET のゲート電荷に依存しており、速度およびリップルの条件に基づいて選択する必要があります。 |

| HI                   | 5    | 7                 | I   | ハイサイド入力。 <sup>(1)</sup>                                                                                                                                                                      |

| HO                   | 3    | 4                 | O   | ハイサイド出力。ハイサイドパワー MOSFET のゲートに接続します。                                                                                                                                                          |

| HS                   | 4    | 5                 | P   | ハイサイドソース接続。ハイサイドパワー MOSFET のソースに接続します。ブートストラップコンデンサの負側をこのピンに接続します。                                                                                                                           |

| LI                   | 6    | 8                 | I   | ローサイド入力。 <sup>(1)</sup>                                                                                                                                                                      |

| LO                   | 8    | 10                | O   | ローサイド出力。ローサイドパワー MOSFET のゲートに接続します。                                                                                                                                                          |

| VDD                  | 1    | 1                 | P   | ローサイドゲートドライバへの正電源。このピンを V <sub>SS</sub> (GND) にデカッピングします。デカッピングコンデンサの標準範囲は 0.22μF~4.7μF です ( <sup>(2)</sup> を参照)。                                                                            |

| VSS                  | 7    | 9                 | G   | デバイスの負電源端子で、通常は接地されています。                                                                                                                                                                     |

| 放熱パッド <sup>(4)</sup> | パッド  | パッド               | —   | 熱性能を向上させるため、大きな熱質量パターンおよび GND プレーンに接続します。                                                                                                                                                    |

- (1) HI, LI, EN の各入力は、低インピーダンスのソース信号に接続されていると想定されます。ソース出力のインピーダンスは、100Ω 未満であると想定されています。ソースインピーダンスが 100Ω を超える場合は、HI と VSS の間、LI と VSS の間、EN と VSS の間にそれぞれバイパスコンデンサを追加します。追加コンデンサの値は、ピン上のノイズレベルによって異なります。ノイズの影響を効果的に除去するために、通常は 1nF~10nF が使用されます。HI または LI の 2 つのピンにノイズが存在すると、HO および LO の誤動作によってロジック出力が誤ったものになります。

- (2) 低温アプリケーションでは、上部範囲の容量を使用することを推奨します。PCB レイアウトについては、「レイアウトのガイドライン」に従ってください。

- (3) G = グラウンド、I = 入力、O = 出力、P = 電源。

- (4) ピン VSS と露出したサーマルパッドは、DRC パッケージのみに内部接続されています。DDA パッケージでは、サーマルパッドはパッケージのどのリードにも直接は接続されていませんが、デバイスのグラウンドである基板に電気的、熱的に接続されています。

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内、すべての電圧は  $V_{SS}$  基準 (特に記述のない限り)。<sup>(1)</sup>

|                     |                        |                                | 最小値              | 最大値            | 単位 |

|---------------------|------------------------|--------------------------------|------------------|----------------|----|

| $V_{DD}$            | 電源電圧                   |                                | -0.3             | 20             | V  |

| $V_{HI}$ 、 $V_{LI}$ | HI および LI の入力電圧        |                                | -10              | 20             | V  |

| $V_{EN}$            | EN の入力電圧 (DRC パッケージのみ) | EN の入力電圧                       | -10              | 20             | V  |

| $V_{LO}$            | LO の出力電圧               | DC                             | -0.3             | $V_{DD} + 0.3$ | V  |

|                     |                        | 繰り返しパルス < 100ns <sup>(2)</sup> | -2               | $V_{DD} + 0.3$ |    |

| $V_{HO}$            | HO の出力電圧               | DC                             | $V_{HS} - 0.3$   | $V_{HB} + 0.3$ | V  |

|                     |                        | 繰り返しパルス < 100ns <sup>(2)</sup> | $V_{HS} - 2$     | $V_{HB} + 0.3$ |    |

| $V_{HS}$            | HS の電圧                 | DC                             | -1               | 120            | V  |

|                     |                        | 繰り返しパルス < 100ns <sup>(2)</sup> | $-(28 - V_{DD})$ | 120            |    |

| $V_{HB}$            | HB の電圧                 |                                | -0.3             | 120            | V  |

|                     | HB-HS の電圧              |                                | -0.3             | 20             | V  |

| $T_J$               | 動作時接合部温度               |                                | -40              | 150            | °C |

| $T_{stg}$           | 保存温度                   |                                | -65              | 150            | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

- (2) 値は特性評価によって検証されたものであり、出荷時のテストは行っていません。

### 5.2 ESD 定格

|             |      |                                            | 値          | 単位 |

|-------------|------|--------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、AEC Q100-002 準拠 <sup>(1)</sup> | $\pm 2000$ | V  |

|             |      | デバイス帶電モデル (CDM)、AEC Q100-011 準拠            | $\pm 1500$ |    |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI/ESDA/JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内、すべての電圧は  $V_{SS}$  基準 (特に記述のない限り)。

|           |              | 最小値                            | 公称値 | 最大値                    | 単位   |

|-----------|--------------|--------------------------------|-----|------------------------|------|

| $V_{DD}$  | 電源電圧         | 8                              | 12  | 17                     | V    |

| $V_{HS}$  | HS の電圧       | -1                             |     | 105                    | V    |

| $V_{HB}$  | HB の電圧       | $V_{HS} + 8$ 、<br>$V_{DD} - 1$ |     | $V_{HS} + 17$ 、<br>115 | V    |

| $SR_{HS}$ | HS の電圧スルーレート |                                |     | 50                     | V/ns |

| $T_J$     | 動作時接合部温度     | -40                            |     | 150                    | °C   |

### 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup> |                     | UCC27301A-Q1         |            | 単位   |

|----------------------|---------------------|----------------------|------------|------|

|                      |                     | DDA (PowerPad™ SOIC) | DRC (VSON) |      |

|                      |                     | 8 ピン                 | 10 ピン      |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 47.1                 | 51.9       | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 60.8                 | 58.3       | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 21.3                 | 24.6       | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 6.3                  | 1.7        | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 21.3                 | 24.6       | °C/W |

## 5.4 热に関する情報 (続き)

| 热評価基準 <sup>(1)</sup> |                   | UCC27301A-Q1         |            | 単位   |

|----------------------|-------------------|----------------------|------------|------|

|                      |                   | DDA (PowerPad™ SOIC) | DRC (VSON) |      |

|                      |                   | 8 ピン                 | 10 ピン      |      |

| $R_{\theta JC(bot)}$ | 接合部からケース(底面)への热抵抗 | 6.2                  | 9.2        | °C/W |

(1) 従来および新しい热評価基準値の詳細については、アプリケーションレポート『半導体およびICパッケージの热評価基準値』、SPRA953を参照してください。

## 5.5 電気的特性

$V_{DD} = V_{HB} = 12V$ 、 $V_{HS} = V_{SS} = 0V$ 、 $LO$  または  $HO$  は無負荷、 $T_A = T_J = -40^{\circ}C \sim +150^{\circ}C$  (特に記述のない限り)。

| パラメータ                 | テスト条件                                | 最小値                                           | 標準値 | 最大値    | 単位            |

|-----------------------|--------------------------------------|-----------------------------------------------|-----|--------|---------------|

| <b>供給電流</b>           |                                      |                                               |     |        |               |

| $I_{DD}$              | $V_{DD}$ 静止電流                        | $V_{LI} = V_{HI} = 0V$ 、 $V_{EN} = 3V$        |     | 0.11   | 0.19 mA       |

| $I_{DDO}$             | $V_{DD}$ 動作電流                        | $f = 500kHz$ 、 $C_{LOAD} = 0$ 、 $V_{EN} = 3V$ |     | 1.4    | 3 mA          |

| $I_{HB}$              | ブート電圧の静止電流                           | $V_{LI} = V_{HI} = 0V$ 、 $V_{EN} = 3V$        |     | 0.065  | 0.12 mA       |

| $I_{HBO}$             | ブート電圧動作電流                            | $f = 500kHz$ 、 $C_{LOAD} = 0$ 、 $V_{EN} = 3V$ |     | 1.3    | 3 mA          |

| $I_{HBS}$             | HB から VSS への静止電流                     | $V_{HS} = V_{HB} = 105V$ 、 $V_{EN} = 3V$      |     | 0.0005 | 1 $\mu A$     |

| $I_{HBSO}$            | HB から VSS への動作電流                     | $f = 500kHz$ 、 $C_{LOAD} = 0$ 、 $V_{EN} = 3V$ |     | 0.03   | 1 mA          |

| $I_{DD\_DIS}$         | EN ピンが Low (ディセーブル) になったときのドライバ電流    | DRC パッケージのみ、 $V_{EN} = 0$                     |     | 3      | $\mu A$       |

| <b>入力</b>             |                                      |                                               |     |        |               |

| $V_{HIT\_HI}$         | 入力電圧 high スレッショルド                    |                                               | 1.7 | 2.3    | 2.55 V        |

| $V_{HIT\_LI}$         | 入力電圧 high スレッショルド                    |                                               | 1.7 | 2.3    | 2.55 V        |

| $V_{LIT\_HI}$         | 入力電圧 Low スレッショルド                     |                                               | 1.2 | 1.6    | 1.9 V         |

| $V_{LIT\_LI}$         | 入力電圧 Low スレッショルド                     |                                               | 1.2 | 1.6    | 1.9 V         |

| $V_{IHYS\_HI}$        | 入力電圧ヒステリシス                           |                                               |     | 0.7    | V             |

| $V_{IHYS\_LI}$        | 入力電圧ヒステリシス                           |                                               |     | 0.7    | V             |

| $R_{IN\_HI}$          | 入力プルダウン抵抗                            | $V_{IN} = 3V$                                 |     | 68     | $k\Omega$     |

| $R_{IN\_LI}$          | 入力プルダウン抵抗                            | $V_{IN} = 3V$                                 |     | 68     | $k\Omega$     |

| <b>イネーブル</b>          |                                      |                                               |     |        |               |

| $V_{EN}$              | ドライバをイネーブルにするための EN ピンの電圧スレッショルド     | DRC パッケージのみ                                   | 1.7 | 2.3    | 2.55 V        |

| $V_{DIS}$             | ドライバをディセーブルにするための EN ピンの電圧スレッショルド    | DRC パッケージのみ                                   | 1.2 | 1.6    | 1.9 V         |

| $V_{ENHYS}$           | イネーブル ピンのヒステリシス                      | DRC パッケージのみ                                   |     | 0.7    | V             |

| $R_{EN}$              | EN ピンの内部プルダウン抵抗                      | DRC パッケージのみ、 $V_{EN} = 3V$                    |     | 80     | $k\Omega$     |

| $T_{EN}$              | EN ピンが High になってからドライバがイネーブルになるまでの時間 | DRC パッケージのみ、 $V_{EN} = 3V$                    |     | 10     | $\mu s$       |

| $T_{DIS}$             | EN ピンが Low になってからドライバがディセーブルになるまでの時間 | DRC パッケージのみ、 $V_{EN} = 0V$                    |     | 0.1    | $\mu s$       |

| <b>低電圧保護 (UVLO)</b>   |                                      |                                               |     |        |               |

| $V_{DDR}$             | $V_{DD}$ 上昇スレッショルド                   |                                               | 6.2 | 7      | 7.8 V         |

| $V_{DDHYS}$           | $V_{DD}$ スレッショルド ヒステリシス              |                                               |     | 0.5    | V             |

| $V_{HBR}$             | $V_{HB}$ 上昇スレッショルド                   |                                               | 5.6 | 6.7    | 7.9 V         |

| $V_{HBHYS}$           | $V_{HB}$ スレッショルド ヒステリシス              |                                               |     | 1.1    | V             |

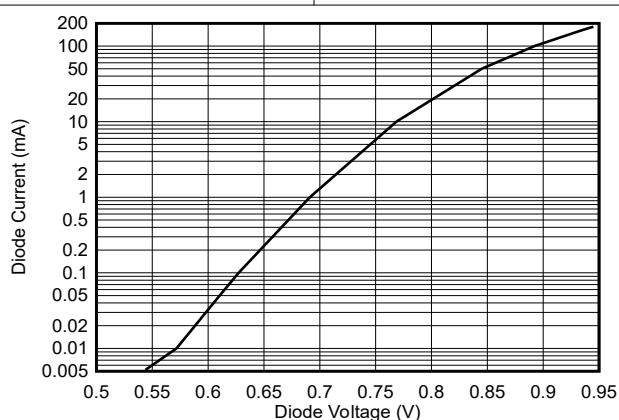

| <b>ブートストラップ ダイオード</b> |                                      |                                               |     |        |               |

| $V_F$                 | 低電流順方向電圧                             | $ V_{DD - HB} = 100\mu A$                     |     | 0.65   | 0.85 V        |

| $V_{FI}$              | 高電流順方向電圧                             | $ V_{DD - HB} = 100mA$                        |     | 0.9    | 1.05 V        |

| $R_D$                 | 動的抵抗、 $\Delta V_F / \Delta I$        | $ V_{DD - HB} = 160mA$ および $180mA$            |     | 0.3    | 0.55 $\Omega$ |

| <b>LO ゲートドライバ</b>     |                                      |                                               |     |        |               |

## 5.5 電気的特性 (続き)

$V_{DD} = V_{HB} = 12V$ 、 $V_{HS} = V_{SS} = 0V$ 、 $LO$  または  $HO$  は無負荷、 $T_A = T_J = -40^{\circ}C \sim +150^{\circ}C$  (特に記述のない限り)。

| パラメータ             |                 | テスト条件                                           | 最小値 | 標準値  | 最大値  | 単位 |

|-------------------|-----------------|-------------------------------------------------|-----|------|------|----|

| $V_{LOL}$         | Low レベル出力電圧     | $I_{LO} = 100mA$                                |     | 0.07 | 0.19 | V  |

| $V_{LOH}$         | High レベル出力電圧    | $I_{LO} = -100mA$ 、 $V_{LOH} = V_{DD} - V_{LO}$ |     | 0.11 | 0.29 | V  |

|                   | ピーク ブルアップ電流 (1) | $V_{LO} = 0V$                                   |     | 3.7  |      | A  |

|                   | ピーク ブルダウン電流 (1) | $V_{LO} = 12V$                                  |     | 4.5  |      | A  |

| <b>HO ゲートドライバ</b> |                 |                                                 |     |      |      |    |

| $V_{HOL}$         | Low レベル出力電圧     | $I_{HO} = 100mA$                                |     | 0.07 | 0.19 | V  |

| $V_{HOH}$         | High レベル出力電圧    | $I_{HO} = -100mA$ 、 $V_{HOH} = V_{HB} - V_{HO}$ |     | 0.11 | 0.29 | V  |

|                   | ピーク ブルアップ電流 (1) | $V_{HO} = 0V$                                   |     | 3.7  |      | A  |

|                   | ピーク ブルダウン電流 (1) | $V_{HO} = 12V$                                  |     | 4.5  |      | A  |

(1) 量産品のパラメータはテストしていません。

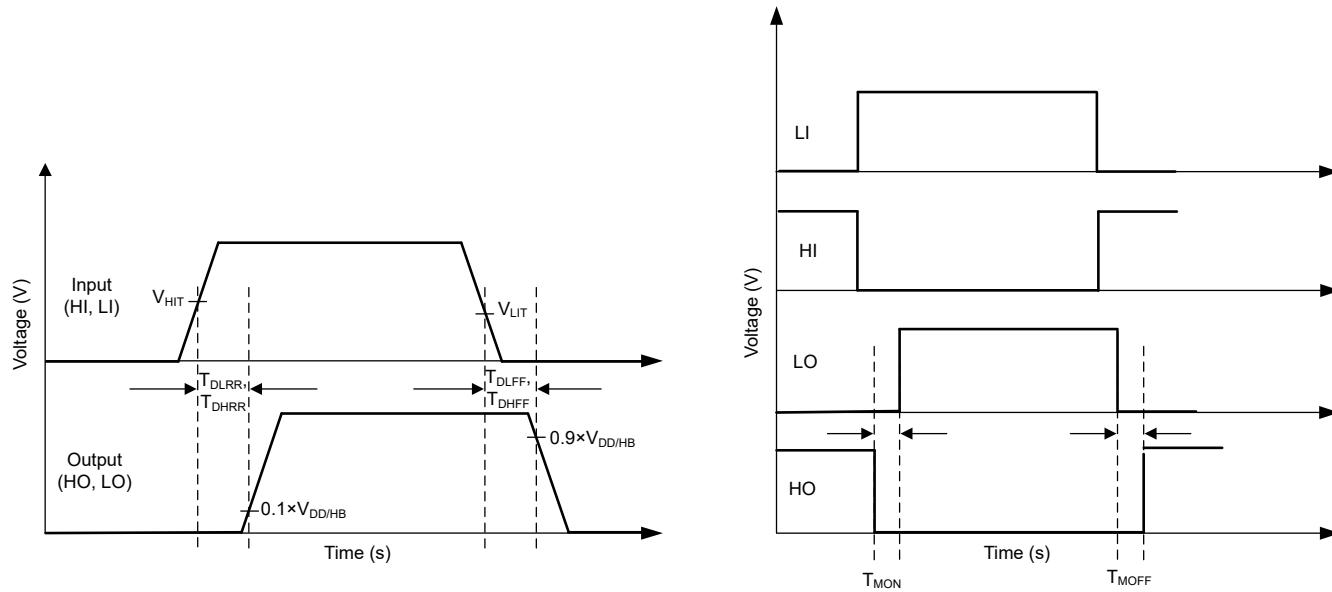

## 5.6 スイッチング特性

$V_{DD} = V_{HB} = 12V$ 、 $V_{HS} = V_{SS} = 0V$ 、 $LO$  または  $HO$  は無負荷、 $T_A = T_J = -40^{\circ}C \sim +150^{\circ}C$  (特に記述のない限り)。

| パラメータ                     |                                | テスト条件                                                                     | 最小値 | 標準値  | 最大値 | 単位 |

|---------------------------|--------------------------------|---------------------------------------------------------------------------|-----|------|-----|----|

| <b>伝搬遅延</b>               |                                |                                                                           |     |      |     |    |

| $t_{DLFF}$                | VLI 立ち下がりから VLO 立ち下がりまで        | $C_{LOAD} = 0pF$ 、LI の $V_{LIT}$ から LO 立ち下がりの 90% まで                      | 10  | 19   | 30  | ns |

| $t_{DHFF}$                | VHI 立ち下がりから VHO 立ち下がりまで        | $C_{LOAD} = 0pF$ 、HI の $V_{LIT}$ から HO 立ち下がりの 90% まで                      | 10  | 19   | 30  | ns |

| $t_{DLRR}$                | VLI 立ち上がりから VLO 立ち上がりまで        | $C_{LOAD} = 0pF$ 、LI の $V_{HIT}$ から LO 立ち上がりの 10% まで                      | 10  | 20   | 42  | ns |

| $t_{DHRR}$                | VHI 立ち上がりから VHO 立ち上がりまで        | $C_{LOAD} = 0pF$ 、 $C_{LOAD} = 0pF$ 、HI の $V_{HIT}$ から HO 立ち上がりの 10% まで   | 10  | 20   | 42  | ns |

| <b>遅延マッチング</b>            |                                |                                                                           |     |      |     |    |

| $t_{MON}$                 | LI ON、HI OFF                   | $T_J = 25^{\circ}C$ 、LO 立ち上がりの 10% から HO 立ち下がりの 90% まで                    |     | 4    | 9.5 | ns |

| $t_{MON}$                 | LI ON、HI OFF                   | $T_J = -40^{\circ}C \sim 150^{\circ}C$ 、LO 立ち上がりの 10% から HO 立ち下がりの 90% まで |     | 4    | 17  | ns |

| $t_{MOFF}$                | LI OFF、HI ON                   | $T_J = 25^{\circ}C$ 、LO 立ち下がりの 90% から HO 立ち上がりの 10% まで                    |     | 4    | 9.5 | ns |

| $t_{MOFF}$                | LI OFF、HI ON                   | $T_J = -40^{\circ}C \sim 150^{\circ}C$ 、LO 立ち下がりの 90% から HO 立ち上がりの 10% まで |     | 4    | 17  | ns |

| <b>出力の立ち上がりおよび立ち下がり時間</b> |                                |                                                                           |     |      |     |    |

| $t_{R\_LO}$               | LO の立ち上がり時間                    | $C_{LOAD} = 1000pF$ 、10% から 90%                                           |     | 7.2  |     | ns |

| $t_{R\_HO}$               | HO の立ち上がり時間                    | $C_{LOAD} = 1000pF$ 、10% から 90%                                           |     | 7.2  |     | ns |

| $t_{F\_LO}$               | LO の立ち下がり時間                    | $C_{LOAD} = 1000pF$ 、90% から 10%                                           |     | 5.5  |     | ns |

| $t_{F\_HO}$               | HO の立ち下がり時間                    | $C_{LOAD} = 1000pF$ 、90% から 10%                                           |     | 5.5  |     | ns |

| $t_{R\_LO\_p1}$           | LO の立ち上がり時間 (3V から 9V)         | $C_{LOAD} = 0.1\mu F$ (3V から 9V)                                          |     | 0.27 | 0.6 | μs |

| $t_{R\_HO\_p1}$           | HO の立ち上がり時間 (3V から 9V)         | $C_{LOAD} = 0.1\mu F$ (3V から 9V)                                          |     | 0.27 | 0.6 | μs |

| $t_{F\_LO\_p1}$           | LO の立ち下がり時間 (9V から 3V)         | $C_{LOAD} = 0.1\mu F$ (9V から 3V)                                          |     | 0.16 | 0.4 | μs |

| $t_{F\_HO\_p1}$           | HO の立ち下がり時間 (9V から 3V)         | $C_{LOAD} = 0.1\mu F$ (9V から 3V)                                          |     | 0.16 | 0.4 | μs |

| <b>その他</b>                |                                |                                                                           |     |      |     |    |

| $t_{IN\_PW}$              | 出力 LO を変化させる最小入力パルス幅           |                                                                           |     | 40   |     | ns |

| $t_{IN\_PW}$              | 出力 HO を変化させる最小入力パルス幅           |                                                                           |     | 40   |     | ns |

| $t_{OFF\_BSD}$            | ブートストラップ ダイオードのターンオフ時間 (1) (2) | $I_F = 20mA$ 、 $I_{REV} = 0.5A^{(3)}$                                     |     | 20   |     | ns |

(1) 量産品のパラメータはテストしていません。

(2) 標準値、 $T_A = 25^{\circ}C$

(3)  $I_F$ : ブートストラップダイオードに印加される順方向電流  $I_{REV}$ : ブートストラップダイオードに印加される逆方向電流。

## 5.7 タイミング図

図 5-1. タイミング図

## 5.8 代表的特性

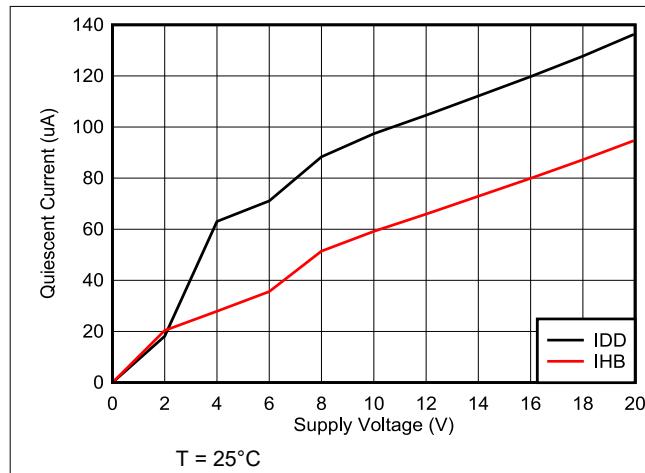

図 5-2. 静止電流と電源電圧との関係

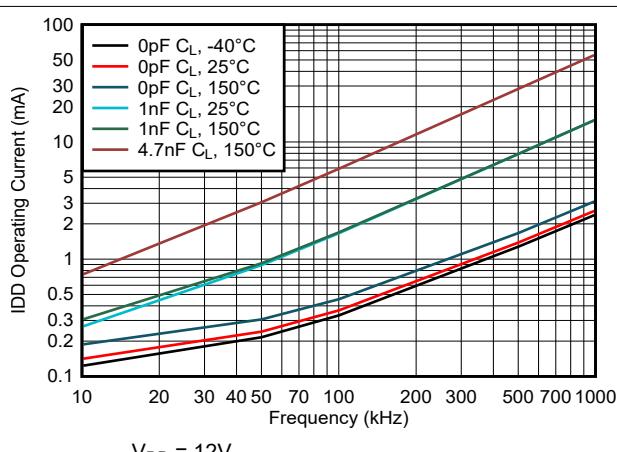

図 5-3. IDD の動作電流と周波数との関係

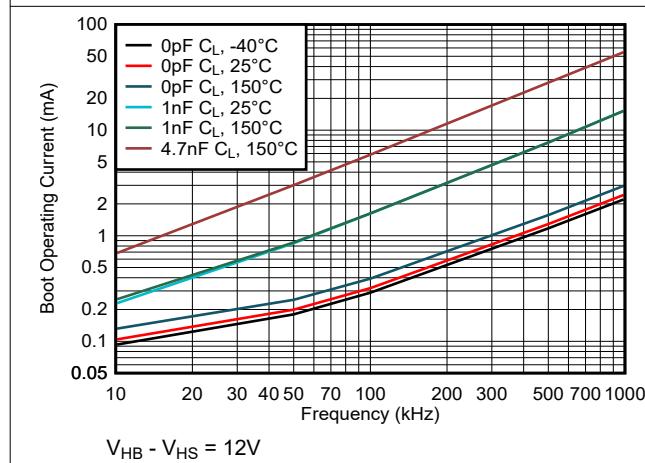

図 5-4. ブート電圧動作電流と周波数との関係 (HB から HS)

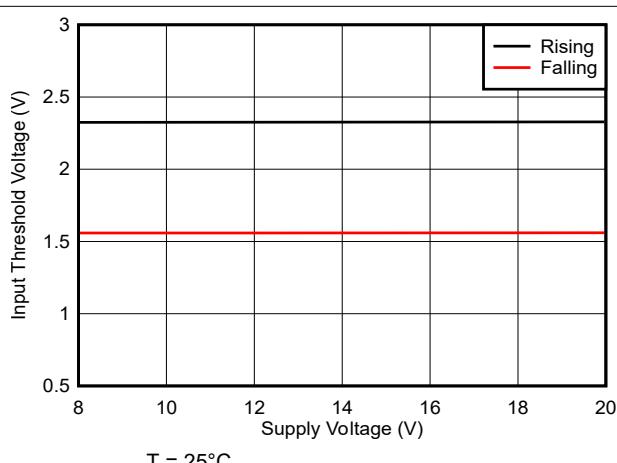

図 5-5. 入力スレッショルドと電源電圧との関係

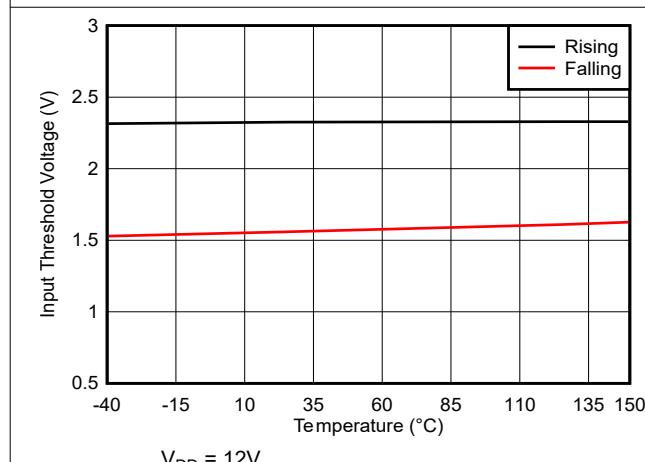

図 5-6. 入力スレッショルドと温度との関係

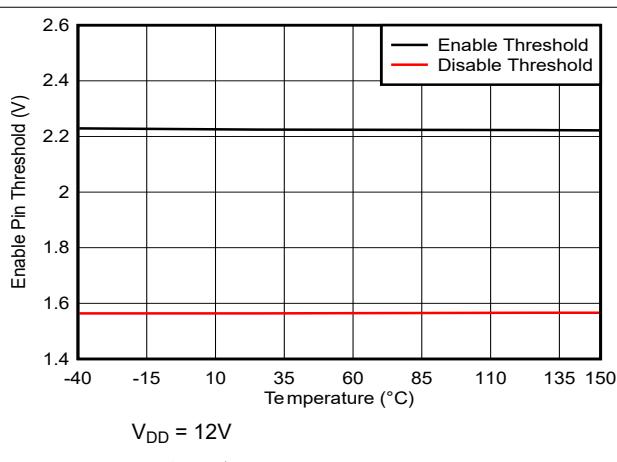

図 5-7. イネーブルスレッショルドと温度との関係

## 5.8 代表的特性 (続き)

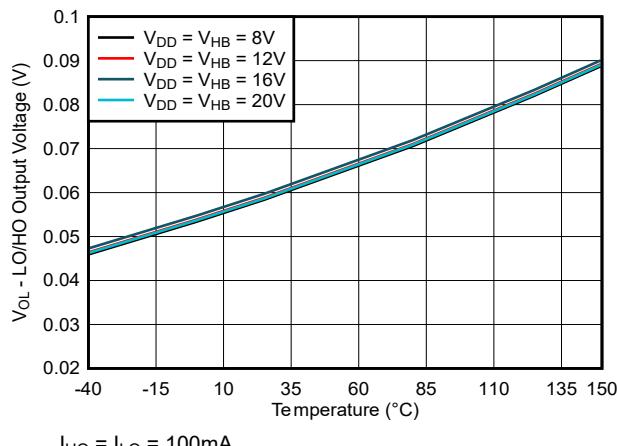

$I_{HO} = I_{LO} = 100\text{mA}$

図 5-8. LO および HO の Low レベル出力電圧と温度との関係

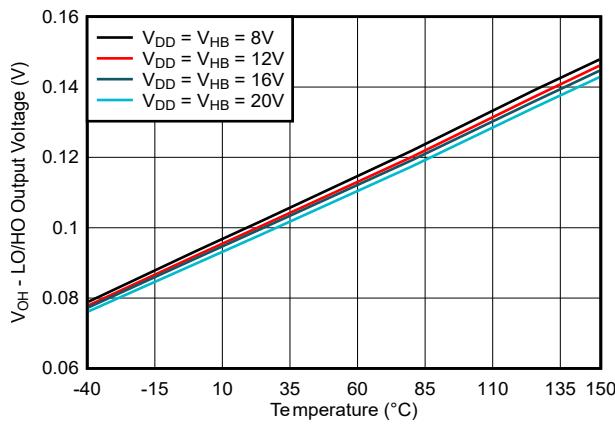

$I_{HO} = I_{LO} = 100\text{mA}$

図 5-9. LO および HO の High レベル出力電圧と温度との関係

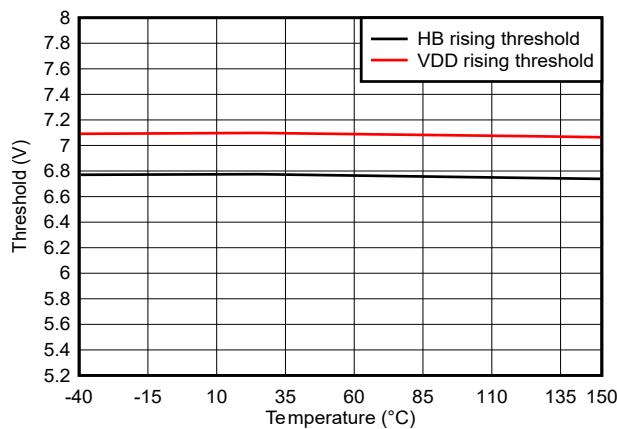

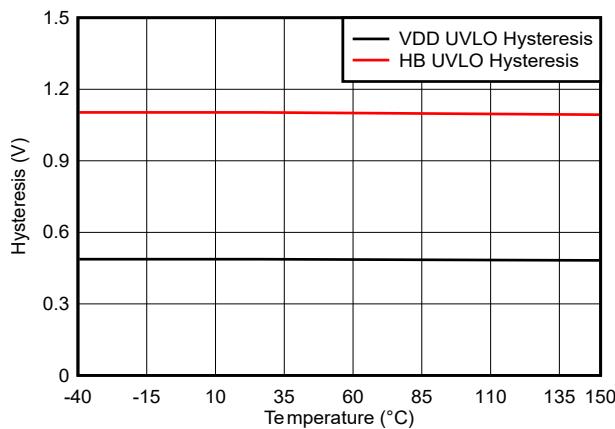

図 5-10. 低電圧誤動作防止スレッショルドと温度との関係

図 5-11. 低電圧誤動作防止スレッショルドのヒステリシスと温度との関係

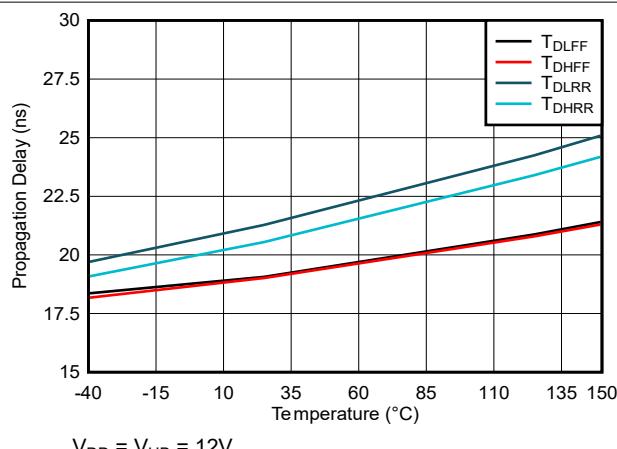

$V_{DD} = V_{HB} = 12V$

図 5-12. 伝搬遅延と温度との関係

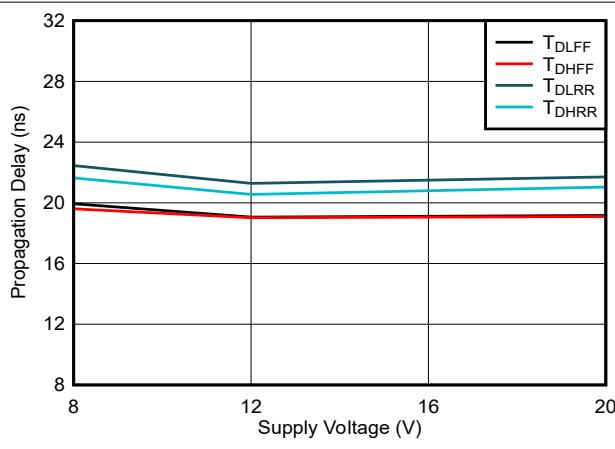

$T = 25^{\circ}\text{C}$

図 5-13. 伝搬遅延と電源電圧との関係 ( $V_{DD} = V_{HB}$ )

## 5.8 代表的特性 (続き)

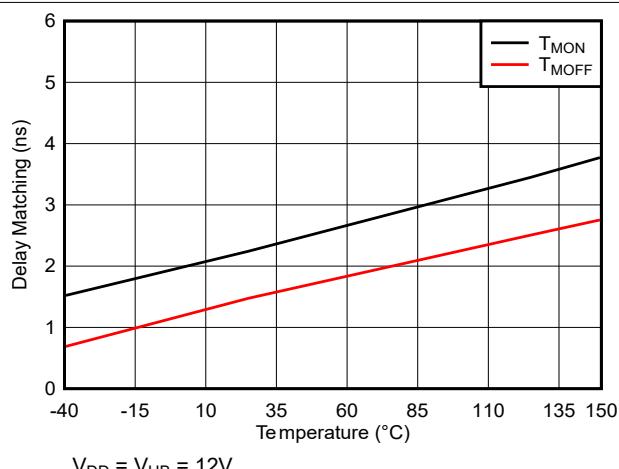

図 5-14. 遅延マッチングと温度との関係

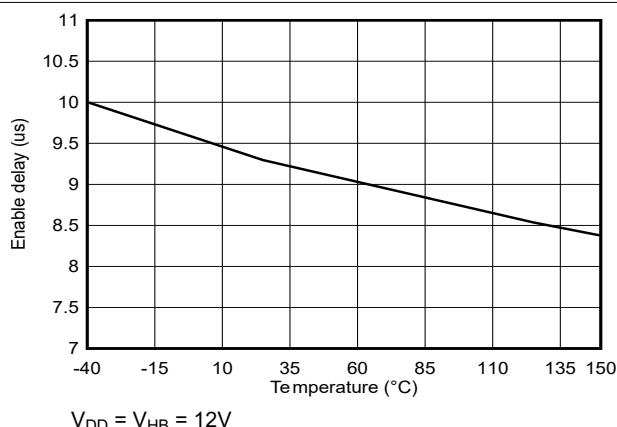

図 5-15. イネーブル遅延と温度との関係

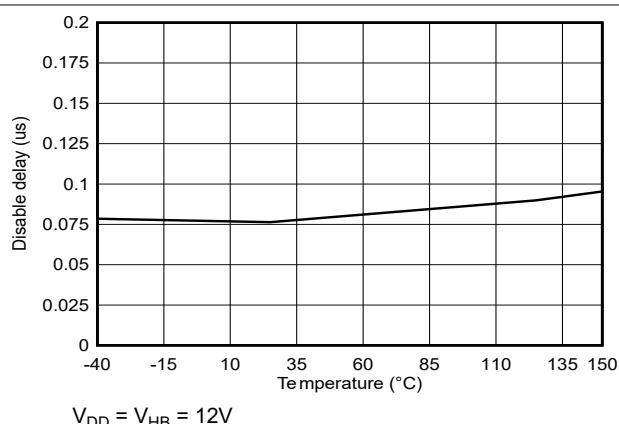

図 5-16. ディセーブル遅延と温度との関係

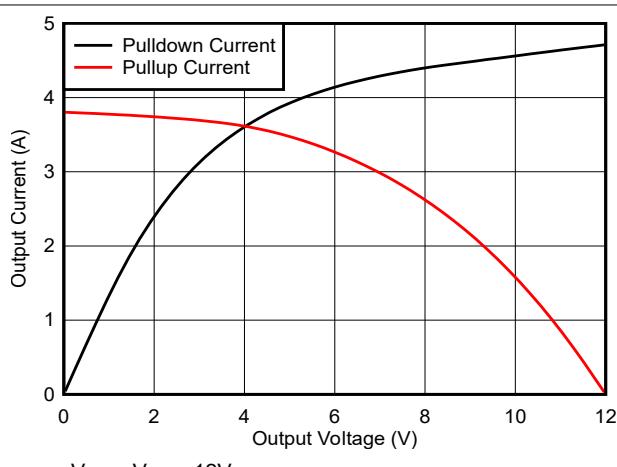

図 5-17. 出力電流と出力電圧との関係

図 5-18. ダイオード電流とダイオード電圧との関係

## 6 詳細説明

### 6.1 概要

UCC27301A-Q1 は、同期整流式降圧型またはハーフブリッジの構成においてハイサイドとローサイド両方の N チャネル MOSFET を駆動するよう設計された高電圧ゲートドライバです。2 つの出力は、TTL 互換の入力信号によって独立して制御されます。また、信号がデバイスのターンオンおよびターンオフのスレッショルド仕様を満たしている限り、デバイスは CMOS タイプの制御信号を入力として使用しても動作できます。フローティング ハイサイド ドライバは、V<sub>SS</sub> に対して最大 115V の HB 電圧で動作できます。UCC27301A-Q1 デバイスには、ハイサイド ゲートドライブのブートストラップ コンデンサを充電するための 120V ブートストラップ ダイオードが内蔵されています。堅牢なレベル シフタにより、消費電力を抑えながら高速で動作し、制御ロジックからハイサイド ゲートドライバへのクリーンなレベル遷移を実現します。ローサイドとハイサイド両方の電源レールに低電圧誤動作防止機能 (UVLO) が搭載されています。ドライバをイネーブルまたはディセーブルするための EN ピン (DRC パッケージ部品内) が備わっています。ドライバには入力インターロック機能もあり、2 つの入力がオーバーラップすると両方の出力がオフになります。

UCC27301A-Q1 デバイスには、ハイサイドとローサイドに個別のインターロック入力があり、アプリケーションの入力制御信号を最大限に柔軟に調整できます。ハイサイド ドライバのバイアス電源用のブート ダイオードは、UCC27301A-Q1 に内蔵されています。ハイサイド ドライバはスイッチ ノード (HS) を基準としており、通常はハイサイド MOSFET のソース ピンおよびローサイド MOSFET のドレイン ピンです。ローサイド ドライバは V<sub>SS</sub> を基準としており、通常はグランドです。UCC27301A-Q1 の機能は、入力段、UVLO 保護、レベル シフト、ブート ダイオード、出力ドライバ段に分割されています。

**表 6-1. UCC27301A-Q1 の特長**

| 機能                                                     | 利点                                                                           |

|--------------------------------------------------------|------------------------------------------------------------------------------|

| 3.7A ソースおよび 4.5A シンク電流                                 | 最小の電力損失で大電力 MOSFET を駆動するのに理想的な大ピーカ電流 (ミラー プラトーで高速駆動可能)                       |

| 入力ピン (HI および LI) は -10VDC~20VDC を直接処理可能                | 堅牢性およびアンダーシュート / オーバーシュート対処能力の向上により、整流ダイオードの使用を必要とせずにゲート駆動トランジスト直接インターフェイス可能 |

| 120V 内部ブートダイオード                                        | サージ要件を満たす電圧マージン                                                              |

| スイッチ ノード (HS ピン) は -(28-VDD)V の絶対最大電圧に 100ns 間耐えることが可能 | ハイサイド チャネルに対して寄生インダクタンスや浮遊容量によって生じる固有の負電圧からの追加保護が可能                          |

| 電圧スパイクに対する堅牢な ESD 回路                                   | dV/dT が大きい条件に対する優れた耐性                                                        |

| 伝搬遅延 20ns、立ち上がり時間 7.2ns、立ち下がり時間 5.5ns                  | クラス最高のスイッチング特性と非常に小さいパルス伝送歪み                                                 |

| クロス導通保護                                                | 入力のインターロックにより貫通電流を防止                                                         |

| イネーブル / ディセーブル機能                                       | 各種のシステム状態 (電源オン シーケンシングなど) に対してドライバをさらに制御し、ディセーブル時の低静止電流消費を実現                |

| チャネル間遅延マッチング: 4ns (標準値)                                | ブリッジ内のトランジストのボルト秒オフセットを回避                                                    |

| ヒステリシスが大きい TTL 最適化スレッショルド                              | アナログまたはデジタル PWM コントローラを補完、ヒステリシスの増大によりノイズ耐性を向上                               |

## 6.2 機能ブロック図

Copyright © 2018, Texas Instruments Incorporated

## 6.3 機能説明

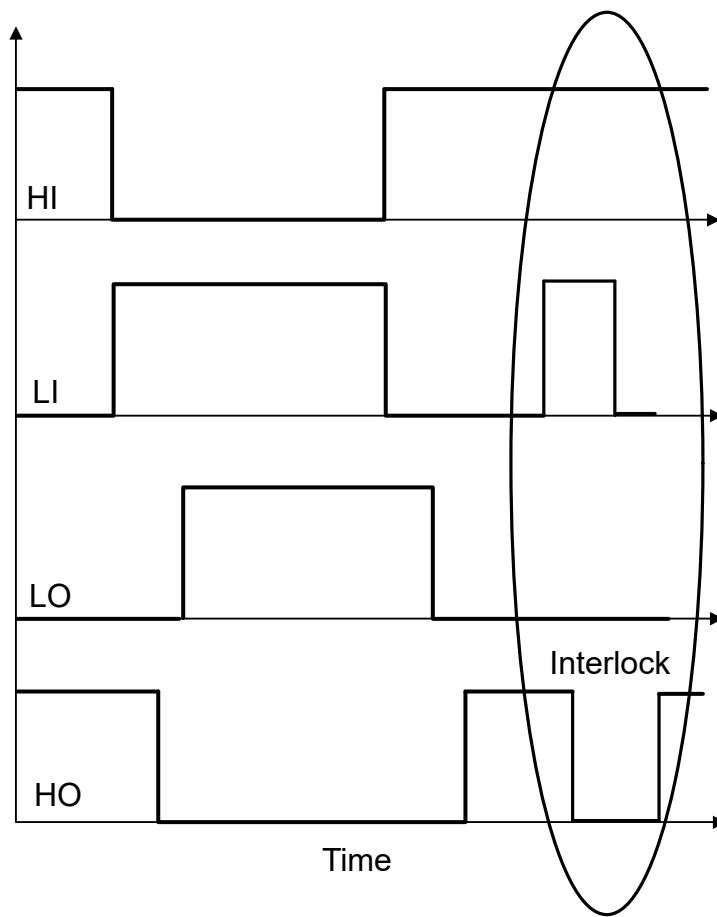

### 6.3.1 入力段とインターロック

2つの入力は独立して動作しますが、両方の入力が **High** またはオーバーラップすると、両方の出力が **Low** になります。独立しているため、単一入力のゲートドライバに比べて 2つの出力を完全に制御できます。このデバイスは、入力インターロックまたはクロス導通保護機能を備えています。両方の入力が **High** のときは、内部ロジックによって両方の出力がオフになります。デバイスがこのモードになると、いずれかの入力が **Low** になったとき、出力は入力ロジックに追従します。このデバイスには他に固定時間グリッチ除去フィルタが実装されていないため、伝搬遅延と遅延マッチングが犠牲になることはありません。つまり、インターロック機能のため、デッドタイムは組み込まれていません。出力に貫通電流を引き起こす可能性のある入力上のノイズはこの機能によってフィルタ処理され、システムの保護状態が確保されます。

入力は TTL ロジック互換です。また、信号がデバイスのターンオンおよびターンオフのスレッショルド仕様を満たしている限り、デバイスは CMOS タイプの制御信号を入力として使用しても動作できます。各入力は電源電圧と無関係であるため、デジタル コントローラとアナログ コントローラのどちらの出力にも接続できます。入力は広いスルーレートの信号を受け付け、入力は負電圧に耐えられるため、堅牢性が向上します。ドライバの入力に小さなフィルタを配置すると、ノイズが発生しやすいアプリケーションでシステムの堅牢性をさらに向上させることができます。入力には、標準値  $68\text{k}\Omega$  のプルダウン抵抗が内蔵されています。したがって、入力がフローティングのとき、出力は **Low** に保持されます。

図 6-1. インターロックまたは入力貫通電流保護

### 6.3.2 イネーブル

DRC パッケージのデバイスにはイネーブル (EN) ピンがあります。EN ピンの電圧がスレッショルド電圧を上回っている場合のみ、出力がアクティブになります。EN ピンがフローティング状態のままになっているか、グランドにプルダウンされている場合、出力は Low に保持されます。内部  $80\text{k}\Omega$  抵抗により、EN ピンが VSS にプルダウンされます。そのため、EN ピンをフローティングにすると、デバイスはディセーブルされます。また、EN ピンを外部でグランドにプルダウンすると、デバイスはディセーブルされます。EN ピンを使用しない場合は、VDD ピンに接続することを推奨します。プルアップ抵抗を使用する必要がある場合は、強力なプルアップ抵抗を推奨します。12V の電源電圧の場合、 $10\text{k}\Omega$  のプルアップをお勧めします。ノイズが発生しやすいアプリケーションでは、 $1\text{nF} \sim 10\text{nF}$  の小さなフィルタコンデンサを、EN ピンと VSS ピンの間にデバイスにできる限り近づけて接続する必要があります。EN ピンにアナログまたはデジタルコントローラの出力ピンを接続して、デバイスをイネーブルまたはディセーブルできます。ヒステリシスが組み込まれているため、わずらわしい出力のトリップやチャタリングを防止できます。

### 6.3.3 低電圧誤動作防止 (UVLO)

ハイサイドおよびローサイドのドライバ段は、電源電圧 (VDD) およびブートストラップコンデンサ電圧 ( $V_{HB}$  から  $V_{HS}$ ) を監視する UVLO 保護回路を備えています。UVLO 回路は、外部 MOSFET をターンオンするのに十分な電源電圧が得られるまで、各出力を禁止します。UVLO ヒステリシスが組み込まれており、電源電圧変動時のチャタリングを防止します。デバイスの VDD ピンに電源電圧が印加されると、VDD が UVLO スレッショルドを超えるまで、両方の出力が Low に保持されます。ブートストラップコンデンサの UVLO 条件 ( $V_{HB-HS}$ ) が発生すると、ハイサイド出力 (HO) のみがディセーブルされます。

### 6.3.4 レベルシフタ

レベルシフト回路は、VSSを基準とする信号であるハイサイド入力から、スイッチノード(HSピン)を基準とするハイサイドドライバ段へのインターフェイスです。レベルシフトにより、HSピンを基準とするHO出力を制御できます。レベルシフタによって生じる遅延は可能な限り低く保たれており、このデバイスは、優れた伝搬遅延特性、およびローサイドドライバ出力との遅延マッチングを実現します。遅延マッチングが小さいため、電力段は、より短いデッドタイムで動作できます。デッドタイムの短縮は、高い効率が必要なアプリケーションでは非常に重要です。

### 6.3.5 ブートダイオード

ハイサイドバイアスを生成するために必要なブートダイオードは、UCC27301A-Q1ドライバファミリに内蔵されています。ダイオードアノードをV<sub>DD</sub>に、カソードをV<sub>HB</sub>に接続します。V<sub>HB</sub>コンデンサをHBとHSピンに接続すると、HSがグランドに遷移したときに、V<sub>HB</sub>コンデンサの電荷がスイッチングサイクルごとにリフレッシュされます。ブートダイオードにより、高速な回復時間、低いダイオード抵抗、電圧定格マージンが可能になり、効率的で信頼性の高い動作を実現できます。

### 6.3.6 出力段

出力段は、パワートレイン内のパワーMOSFETへのインターフェイスです。両方の出力ドライバで高いスルーレート、低い抵抗、高いピーク電流能力を実現しているため、パワーMOSFETの効率的なスイッチングが可能です。ローサイド出力段はV<sub>DD</sub>とV<sub>SS</sub>間の電圧を基準とし、ハイサイドはV<sub>HB</sub>とV<sub>HS</sub>間の電圧を基準とします。このデバイスの出力段は、プルアップ構造を採用しており、パワー スイッチのターンオン遷移のミラー プラトー領域において、最も必要なときに最大のピークソース電流を供給します。デバイスの出力プルアップおよびプルダウン構造は、トーテムポール NMOS-PMOS構造です。

### 6.3.7 負の電圧過渡

ほとんどのアプリケーションでは、外部ローサイドパワーMOSFETのボディダイオードがHSノードをグランドにクランプします。場合によっては、基板の容量とインダクタンスに起因して、HSノードがグランドより数V低い電圧まで過渡的にスイングする可能性があり、外部ローサイドMOSFETのボディダイオードがこのスイングをクランプするのが間に合わないこともあります。このデバイスのHSピンは、仕様に違反せず、またこのセクションで説明している条件に従っている限り、グランドを下回る値までスイングできます。

HBとHSの間の動作電圧は、推奨動作条件内にする必要があります。したがって、HSピンの過渡電圧が-5Vの場合、VDD(およびHB)は12Vに理想的に制限され、HBとHSの間の電圧が17V未満に維持されます。一般に、HSが負にスイングすると、HBは瞬時にHSに追従するため、HBとHSの間の電圧は大きくオーバーシュートしません。

HSは常にHOより低い電位にする必要があります。HOを規定の条件よりも負にすると、寄生トランジスタがアクティブになります。HB電源から過剰な電流が流れ、デバイスが損傷する可能性があります。LOとVSSについても同じ関係があります。必要に応じて、HOとHSの間、またはLOとVSSの間にショットキーダイオードを外部に配置することにより、この種の過渡現象からデバイスを保護できます。ダイオードを有効にするために、デバイスのピンのできるだけ近くにダイオードを配置する必要があります。

ゲートドライバデバイスを適切に動作させるには、HBからHSへ、およびVDDからVSSへの低ESRバイパスコンデンサが必須です。直列インダクタンスを最小限に抑えるため、コンデンサはデバイスのリード直近に配置する必要があります。LOとHOからのピーク電流はかなり大きくなります。バイパスコンデンサと直列インダクタンスは、デバイスのリードに電圧リングを引き起こすため、信頼性の高い動作を実現するには、このリングを回避する必要があります。

アプリケーションボードの設計やその他の動作パラメータによっては、HSピンだけでなく、HIやLI入力ピンなどの他のピンも、過渡的にグランドを下回る値までスイングする場合があります。このような動作条件に対応するため、このデバイスの入力ピンは-10Vの絶対最大電圧を処理できます。レイアウトやその他の設計上の制約によって、出力HOおよびLOでも過渡電圧が短時間発生することがあります。このデバイスは、HOおよびLO出力ピン上で発生する持続時間が100ns未満の-2Vの過渡電圧にも対応できます。

## 6.4 デバイスの機能モード

このデバイスは、イネーブルのときは通常モードおよび UVLO モードで動作します。UVLO の動作モードの詳細については、[セクション 6.3.3](#) を参照してください。通常モードでは、VDD および VVHB-HS が UVLO スレッショルドを上回っているとき、出力段は EN、HI、および LI ピンの状態に依存します。入力状態がフローティングの場合、出力 HO および LO は LOW になります。

**表 6-2. デバイス ロジック表**

| <b>EN<sup>(1)</sup></b> | <b>HI</b> | <b>LI</b> | <b>HO<sup>(2)</sup></b> | <b>LO<sup>(3)</sup></b> |

|-------------------------|-----------|-----------|-------------------------|-------------------------|

| L                       | X         | X         | L                       | L                       |

| H                       | L         | L         | L                       | L                       |

| H                       | L         | H         | L                       | H                       |

| H                       | H         | L         | H                       | L                       |

| H                       | H         | H         | L                       | L                       |

(1) EN ピンは DRC パッケージでのみ利用できます。

(2) HO は HS を基準として測定されます。

(3) LO は VSS を基準として測定されます。

## 7 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

パワー デバイスの高速なスイッチングを可能にし、関連するスイッチング電力損失を低減するため、コントローラの PWM 出力とパワー 半導体デバイスのゲートとの間には、強力なゲートドライバが使用されています。また、PWM コントローラがスイッチング デバイスのゲートを直接駆動できない場合、ゲートドライバが不可欠です。デジタル電源の登場に伴って、デジタル コントローラからの PWM 信号は多くの場合 3.3V のロジック信号であり、パワー スイッチを正常にターンオンできないので、この状況がよく発生します。パワー デバイスを完全にターンオンし、導通損失を最小限に抑えるには、3.3V の信号をゲート駆動電圧 (12V など) まで昇圧するためにレベル シフト回路が必要です。トーテムポール配置の NPN/PNP バイポーラトランジスタをベースとする従来のバッファ駆動回路は、エミッタ フォロワ構成であり、レベル シフト機能がないため、デジタル電源においては不十分であることがわかっています。ゲートドライバは、レベル シフト機能とバッファードライバ機能の両方を効果的に組み合わせています。また、ゲートドライバには、大電流ドライバを物理的にパワー スイッチの近くに配置することにより高周波スイッチング ノイズの影響を最小化する、ゲートドライブトランジスを駆動する、フローティング パワー デバイスのゲートを制御する、ゲート電荷の電力損失をコントローラからドライバに移動することによりコントローラの消費電力と熱ストレスを低減するなど、他のニーズも満たします。

### 7.2 代表的なアプリケーション

図 7-1. UCC27301A-Q1 の代表的なアプリケーション図 1

#### 7.2.1 設計要件

この設計例では、表 7-1 に記載されているパラメータを使用します。

表 7-1. 設計仕様

| 設計パラメータ    | 数値の例     |

|------------|----------|

| 電源電圧、VDD   | 12 V     |

| HS、VHS の電圧 | 0V~100V  |

| HB、VHB の電圧 | 12V~112V |

**表 7-1. 設計仕様 (続き)**

| 設計パラメータ   | 数値の例       |

|-----------|------------|

| 出力電流定格、IO | -4.5A～3.7A |

| 動作周波数     | 500 kHz    |

## 7.2.2 詳細な設計手順

### 7.2.2.1 入力スレッショルドのタイプ

UCC27301A-Q1 デバイスの入力絶対最大電圧範囲は -10V～20V です。堅牢性が向上しているため、両方の部品をゲート駆動トランジストに直接接続できます。このデバイスには、広いヒステリシスの TTL 互換入力スレッショルド ロジックが搭載されています。スレッショルド電圧レベルは低電圧で、VDD 電源電圧から独立しているため、マイクロコントローラからのロジックレベル入力信号だけでなく、アナログ コントローラからの高電圧入力信号とも互換性があります。デバイスの実際の入力スレッショルド電圧レベルとヒステリシスの仕様については、「電気的特性」セクションを参照してください。

### 7.2.2.2 V<sub>DD</sub> バイアス電源電圧

デバイスの VDD ピンに印加するバイアス電源電圧は、「電気的特性」表に記載されている値を超えないようにする必要があります。ただし、パワー スイッチによって、効果的なターンオンとターンオフを実現するためにゲート端子に印加する電圧レベルは異なります。特定のパワー スイッチでは、ターンオンに正のゲート電圧、ターンオフに負のゲート電圧が必要な場合があります。この場合、VDD バイアス電源は電圧差と等しくなります。8V～17V の広い動作範囲に対応するこのデバイスは、Si MOSFET、IGBT、ワイドバンドギャップ パワー半導体など、さまざまなパワー スイッチの駆動に使用できます。

### 7.2.2.3 ソースおよびシンク ピーク電流

一般に、スイッチング電力損失を最小限に抑えるため、ターンオン時およびターンオフ時のパワー スイッチのスイッチング速度はできるだけ高速にする必要があります。ゲートドライバ デバイスは、ターゲットのパワー MOSFET で目標のスイッチング速度を達成するために必要なピーク電流を供給できる必要があります。スイッチング速度のシステム要件は一般に、パワー MOSFET のドレイン-ソース間電圧 ( $dV_{DS}/dt$  など) のスルーレートとして記述されます。たとえば、連続導通モード (CCM) 昇圧 PFC コンバータ アプリケーションにおいて、SPP20N60C3 パワー MOSFET を DC バス電圧 400V を使用して 20V/ns 以上の  $dV_{DS}/dt$  でターンオンする必要があるというシステム要件がある場合があります。この種のアプリケーションは誘導性ハード スイッチング アプリケーションであり、スイッチング電力損失を低減することが重要です。この要件は、パワー MOSFET のターンオン イベント時のドレイン-ソース間電圧スイング全体 (オフ状態の 400V からオン状態の  $V_{DS(on)}$ ) が約 20ns 以内に完了する必要があることを意味します。ドレイン-ソース間の電圧スイングが発生すると、パワー MOSFET のミラー電荷 (SPP20N60C3 データシートに記載されている  $Q_{GD}$  パラメータの標準値は 33nC) がゲートドライバのピーク電流によって供給されます。パワー MOSFET の誘導性スイッチング メカニズムによれば、この時点でのパワー MOSFET のゲート-ソース間電圧はミラー プラート電圧であり、通常はパワー MOSFET のスレッショルド電圧  $V_{GS(TH)}$  よりも数ボルト高い値です。

目標の  $dV_{DS}/dt$  を達成するには、ゲートドライバが  $Q_{GD}$  の充電量を 20ns 以内で供給できる必要があります。つまり、ゲートドライバが 1.65A (= 33nC/20ns) 以上のピーク電流を供給する必要があります。UCC27301A-Q1 ゲートドライバは、3.7A のピーク ソーシング電流を供給でき、設計要件を明確に上回るとともに、必要なスイッチング速度を満たすことができます。オーバードライブ機能により、パワー MOSFET の  $Q_{GD}$  パラメータの部品間変動に対して追加マージンが得られるほか、外部ゲート抵抗を挿入し、スイッチング速度を効率と EMI の最適化のバランスを取って柔軟に調整できます。ただし、実用的な設計では、PCB のゲートドライバ回路の寄生配線インダクタンスが、パワー MOSFET のスイッチング速度に対して決定的な役割を果たします。この寄生配線インダクタンスには、ゲートドライバの出力電流パルスの  $di/dt$  を制限する効果があります。これを説明するため、ゲートドライバからの出力電流パルスの波形が三角波プロファイルに近似できるとします。このプロファイルでは、三角波下の面積

( $\frac{1}{2} \times I_{PEAK} \times \text{時間}$ ) が、パワー MOSFET の総ゲート電荷 (SPP20N60C3 パワー MOSFET のデータシートの  $Q_G$  パラメータ = 87nC (標準値)) に等しくなります。寄生配線インダクタンスにより  $di/dt$  が制限されると、パワー MOSFET のスイッチングに必要な  $Q_G$  を供給する必要のある時間内に、ゲートドライバの最大ピーク電流能力が完全に達成されない状況が発生する可能性があります。つまり、必要な  $Q_G$  は依然として供給されますが、式の時間パラメータが支配的であり、電流パルスの  $I_{PEAK}$  値はデバイスの真のピーク電流能力よりもはるかに小さくなります。このため、理論的な計算でゲート

ドライバが目標のスイッチング速度を達成できることが示されても、目的のスイッチング速度を達成できない場合があります。そのため、ゲートドライバ デバイスをパワー MOSFET の非常に近くに配置し、PCB の配線インダクタンスを最小限に抑えて厳密なゲート駆動ループを設計することが、ゲートドライバのピーク電流能力を最大限に実現するために重要です。

#### 7.2.2.4 伝搬遅延

許容されるゲートドライバからの伝搬遅延は、使用されるスイッチング周波数と、システムで許容されるパルス歪みレベルに依存します。UCC27301A-Q1 デバイスの伝搬遅延は 20ns (標準値) であるため、パルス歪みが非常に小さく、非常に高い周波数での動作が可能です。デバイスの伝搬特性およびスイッチング特性については、「スイッチング特性」表を参照してください。

#### 7.2.2.5 電力散逸

ゲートドライバの消費電力には、式 1 に示すように 2 つの部分があります。

$$P_{DISS} = P_{DC} + P_{SW} \quad (1)$$

消費電力 (PDC) の DC 部分を計算するには、式 2 を使用します。

$$P_{DC} = I_Q \times V_{DD} \quad (2)$$

ここで、

- $I_Q$  はドライバの静止電流です。

静止電流は、入力段、リファレンス電圧、ロジック回路、保護機能、さらにドライバの出力状態が変化したときの内部デバイスのスイッチングに関連する電流 (寄生容量の充電と放電、寄生貫通電流など) などのすべての内部回路をバイアスするためにデバイスが消費する電流です。UCC27301A-Q1 は、静止電流が非常に低く、出力ドライバ段での貫通電流を排除するためのロジックが内蔵されています。したがって、PDC がゲートドライバ内の総消費電力に及ぼす影響は、無視できるレベルであると想定できます。スイッチング (PSW) 時にゲートドライバ パッケージで消費される電力は、以下の要因によって決まります。

- 電源デバイスに必要なゲート電荷 (通常は駆動電圧  $VG$  の関数で、入力バイアス電源電圧  $VDD$  に非常に近い値)

- スイッチング周波数

- 外部ゲート抵抗の使用。ディスクリートの容量性負荷でドライバ デバイスをテストする場合、バイアス電源から必要となる電力を計算するのはかなり簡単です。バイアス電源からコンデンサを充電するために転送する必要があるエネルギーは、式 3 で求められます。

$$EG = \frac{1}{2}C_{LOAD} \times V_{DD}^2 \quad (3)$$

- ここで、

- $C_{LOAD}$  は負荷コンデンサです。

- $V_{DD}$  はドライバに供給されるバイアス電圧です。

コンデンサの充電時と放電時には、等しい量のエネルギーが消費されます。これから、総電力損失は式 4 で求められます。

$$PG = C_{LOAD} \times V_{DD}^2 \times f_{SW} \quad (4)$$

ここで、

- $f_{SW}$  はスイッチング周波数

パワー MOSFET/IGBT で生成されるスイッチング負荷は、デバイスのスイッチングに必要なゲート電荷を調べることにより、等価容量に変換されます。このゲート電荷には、入力静電容量の影響と、オン状態とオフ状態を切り替えるパワー デバイスのドレイン電圧をスイッチングするために必要な追加電荷が含まれます。ほとんどのメーカーは、指定された条件でデバイスをスイッチングするための標準および最大ゲート電荷 ( $nC$  単位) の仕様を提供しています。ゲート電荷  $Qg$  を使用

して、コンデンサのスイッチング時に消費される必要のある電力を決定します。これは、式  $P_G = C_{LOAD} \times V_{DD}^2 \times f_{SW} = Q_G \times V_{DD} \times f_{SW}$  で計算され、式 5 が得られます。

$$P_G = C_{LOAD} \times V_{DD}^2 \times f_{SW} = Q_G \times V_{DD} \times f_{SW} \quad (5)$$

この電力  $P_G$  は、MOSFET/IGBT がオン / オフになるときに、回路の抵抗性素子で消費されます。総電力の半分はターンオン中に負荷コンデンサが充電されるときに消費され、残りの半分はターンオフ中に負荷コンデンサが放電されるときに消費されます。ドライバと MOSFET/IGBT の間に外部ゲート抵抗が取り付けられていない場合、この電力はドライバパッケージ内で完全に消費されます。外部ゲートドライブ抵抗を使用すると、ドライバの内部抵抗と外部ゲート抵抗との間で消費電力が共有されます。

### 7.2.3 アプリケーション曲線

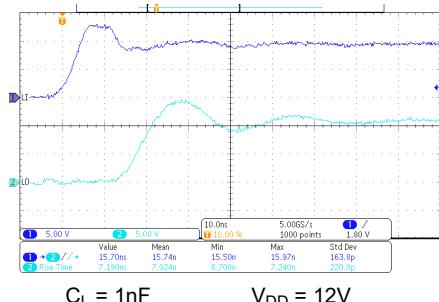

図 7-2. LO 立ち上がり時間と LI から LO へのターン

オン伝搬遅延

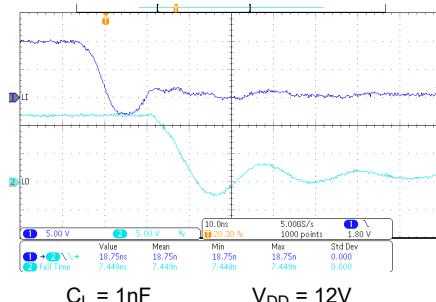

図 7-3. LO 立ち下がり時間と LI から LO へのターン

オフ伝搬遅延

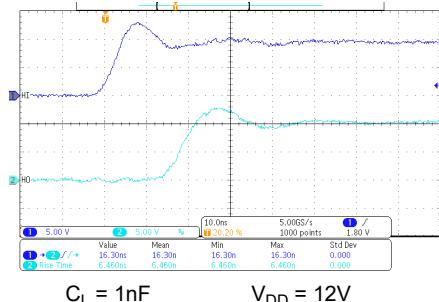

図 7-4. HO 立ち上がり時間と HI から HO へのターン

オン伝搬遅延

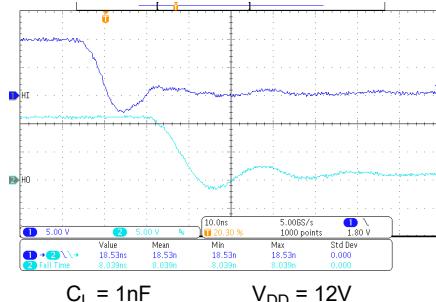

図 7-5. HO 立ち下がり時間と HI から HO へのターン

オフ伝搬遅延

## 8 電源に関する推奨事項

デバイスの動作に推奨されるバイアス電源電圧範囲は 8V～17V です。この範囲の下限は、 $V_{DD}$  ピンの電源回路ブロックに内蔵されている低電圧誤動作防止 (UVLO) 保護機能によって制御されます。 $V_{DD}$  ピンの電圧が  $V_{(on)}$  電源スタートスレッショルドを下回ってドライバが UVLO 状態になると、入力の状態にかかわらず、出力が Low に保持されます。この範囲の上限は、デバイスの  $V_{DD}$  ピンの絶対最大電圧定格 (ストレス評価) である 20V によって決まります。過渡電圧スパイクを許容するため 3V のマージンを維持すると、 $V_{DD}$  ピンの最大推奨電圧は 17V です。UVLO 保護機能にはヒステリシス機能も含まれています。つまり、 $V_{DD}$  ピンのバイアス電圧がスレッショルド電圧を超えてデバイスが動作を開始した後に電圧が低下すると、電圧降下がヒステリシス仕様  $V_{DD(hys)}$  を超えない限り、デバイスは通常の動作を継続します。したがって、8V またはそれに近い範囲の電圧で動作しているときは、デバイスのシャットダウンがトリガされないように、補助電源出力の電圧リップルをデバイスのヒステリシス仕様値よりも小さくすることが重要です。システムのシャットダウン中は、デバイスの動作は  $V_{DD}$  ピンの電圧が  $V_{(OFF)}$  のスレッショルドを下回るまで継続されます。これを考慮して、システムのシャットダウンのタイミング設計要件を評価する必要があります。同様に、システムのスタートアップ時には、 $V_{DD}$  ピンの電圧が  $V_{(on)}$  のスレッショルドを超えるまで、デバイスは動作を開始しません。

デバイスの内部回路ブロックで消費される静止電流は、 $V_{DD}$  ピンから供給されます。この事実はよく知られていますが、 $LO$  ピンから供給されるソース電流パルスの電荷も同じ  $V_{DD}$  ピンを通して供給されることを認識することが重要です。その結果、電流が  $LO$  ピンからソースされるたびに、対応する電流パルスが  $V_{DD}$  ピン経由でデバイスに供給されます。そのため、デカップリングの目的で、 $V_{DD}$  ピンと  $GND$  ピンの間にローカルバイパスコンデンサを配置し、デバイスにできる限り近づけて配置してください。低 ESR の表面実装型セラミックコンデンサが必要です。 $V_{DD}$  と  $GND$  の間に  $0.22\mu F$ ～ $4.7\mu F$  のコンデンサを使用することをお勧めします。同様に、 $HO$  ピンから供給される電流パルスは  $HB$  ピンから電源を得ています。したがって、 $HB$  ピンと  $HS$  ピンの間に  $0.022\mu F$ ～ $0.1\mu F$  のローカルデカップリングコンデンサを配置することを推奨します。

## 9 レイアウト

### 9.1 レイアウトのガイドライン

設計のスイッチング特性と効率を向上させるには、以下のレイアウト規則に従う必要があります。

- ドライバは、MOSFET のできるだけ近くに配置します。

- $V_{DD}$  -  $V_{SS}$  および  $V_{HB}$ - $V_{HS}$  (ブートストラップ) コンデンサは、デバイスにできるだけ近づけて配置します。

- $GND$  パターンに細心の注意を払います。DRM パッケージのサーマルパッドを  $VSS$  ピン ( $GND$ ) に接続し、 $GND$  として使用します。ドライバからの  $GND$  パターンは MOSFET のソースに直接接続されますが、MOSFET のドレインまたはソース電流の大電流パスには配置しないでください。

- $HS$  ノードには、ハイサイドドライバの  $GND$  と同様のルールを使用します。

- 複数の UCC27301A-Q1 デバイスを使用するシステムでは、各デバイスの  $V_{DD}$ - $V_{SS}$  に専用のデカップリングコンデンサを配置することをお勧めします。

- $VDD$  パターンは、 $LO$ 、 $HS$ 、 $HO$  信号の近くに配置しないように注意する必要があります。

- $LO$  および  $HO$  には幅広いパターンを使用し、関連する  $GND$  または  $HS$  パターンに沿って近づけて配置します。可能であれば、60～100mil の幅をお勧めします。

- ドライバ出力または  $SW$  ノードがある層から別の層に配線する必要がある場合は、少なくとも 2 つ以上のビアを使用します。 $GND$  に対しては、サーマルパッドの要件でビア数と寄生インダクタンスを考慮する必要があります。

- $LI$  と  $HI$  (ドライバ入力) が  $HS$  ノードやその他の高い  $dV/dt$  パターンの近くになると、比較的高インピーダンスのリード線に大きなノイズを引き起こす可能性があるため、避けてください。

レイアウトが不適切な場合、効率の大幅な低下やシステムの誤動作が発生し、システム全体の信頼性の低下につながる可能性もあります。

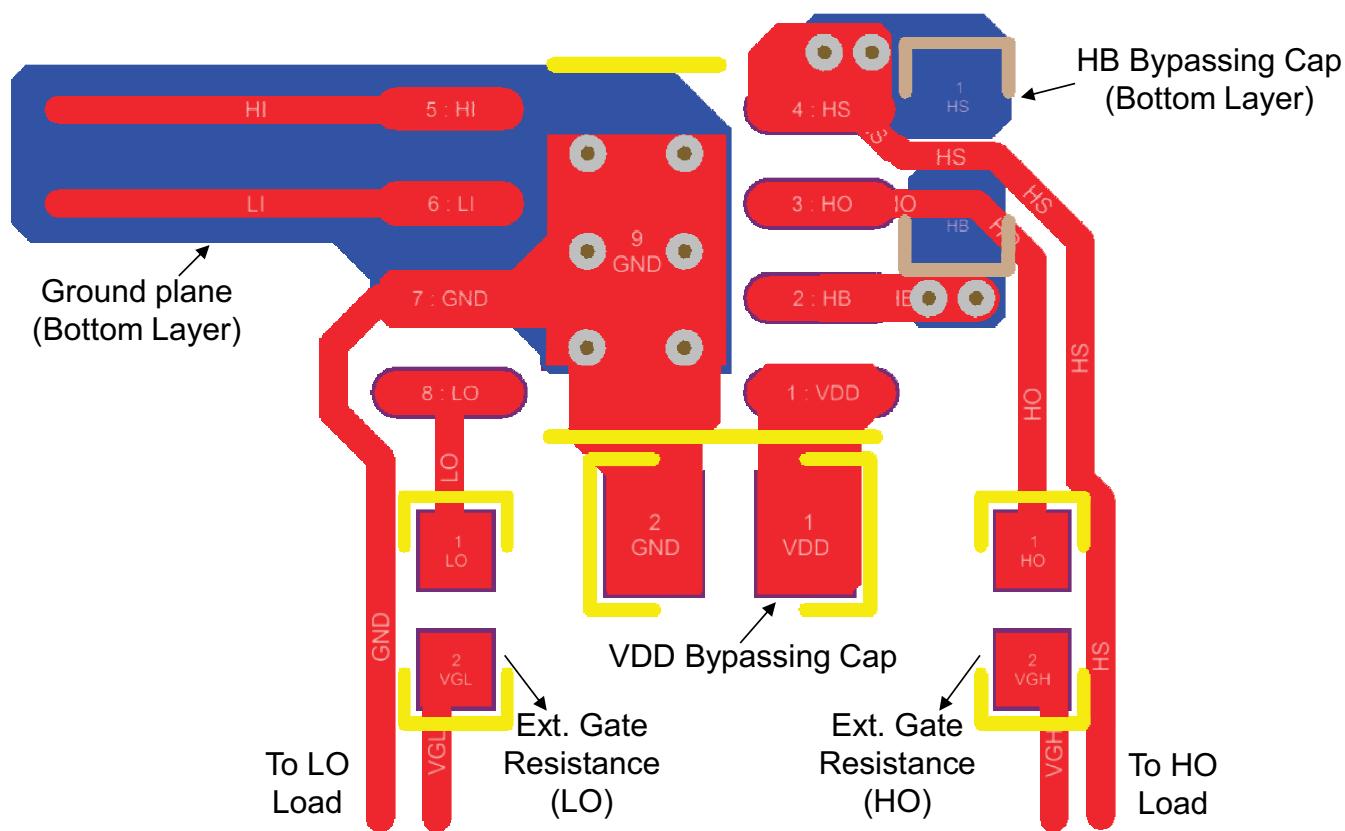

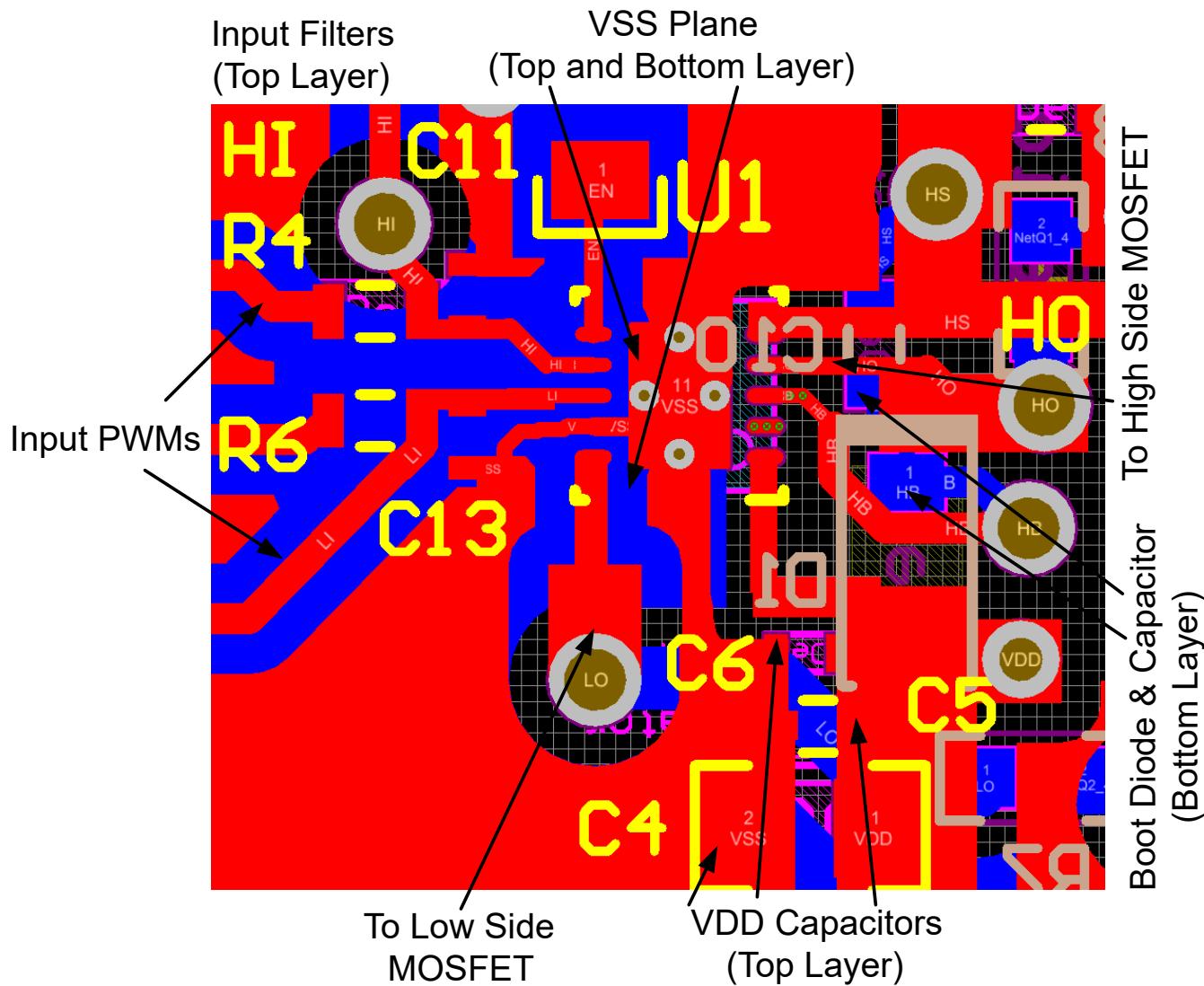

## 9.2 レイアウト例

図 9-1. UCC27301A-Q1 の PCB レイアウト例 (SOIC パッケージ)

図 9-2. UCC27301A-Q1 の PCB レイアウト例 (VSON パッケージ)

### 9.3 热に関する注意事項

ドライバの有効範囲は、負荷の駆動電力要件とパッケージの熱特性に大きく影響されます。特定の温度範囲で有効になるゲートドライバの場合、パッケージは接合部温度を定格制限内に維持しながら、発生する熱を効率的に除去する必要があります。ドライバパッケージの熱評価基準は、「熱に関する情報」セクションに記載されています。表の詳細については、テキサス・インスツルメンツの『半導体および IC パッケージの熱評価基準』アプリケーションノート (SPRA953) を参照してください。UCC27301A-Q1 デバイスは、10 ピンの VSON パッケージ (DRC) で供給されます。

## 10 デバイスおよびドキュメントのサポート

### 10.1 デバイス サポート

#### 10.1.1 サード・パーティ 製品に関する免責事項

サード・パーティ 製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ 製品またはサービスの適合性に関する是認、サード・パーティ 製品またはサービスの是認の表明を意味するものではありません。

### 10.2 ドキュメントのサポート

#### 10.2.1 関連資料

『熱特性強化型パッケージ PowerPAD™』、アプリケーション レポート ([SLMA002](#))

『PowerPAD™ 入門』、アプリケーション レポート ([SLMA004](#))

### 10.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品 フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 10.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの [使用条件](#) を参照してください。

### 10.5 商標

PowerPAD™ is a trademark of Texas Instruments.

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 10.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 10.7 用語集

テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 11 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision B (August 2023) to Revision C (July 2024) | Page              |

|-----------------------------------------------------------------|-------------------|

| • DDA パッケージを「事前情報」から「量産データ」に変更.....                             | <a href="#">1</a> |

| • 表現を大幅に更新し、一部の標準値を修正。.....                                     | <a href="#">1</a> |

| <b>Changes from Revision A (May 2023) to Revision B (August 2023)</b> | <b>Page</b> |

|-----------------------------------------------------------------------|-------------|

| • UCC27301A および UCC27311A の両方の製品とリビジョン互換.....                         | 1           |

| • 「非公開」から「公開」リリースに変更.....                                             | 1           |

| <b>Changes from Revision * (April 2023) to Revision A (May 2023)</b> | <b>Page</b> |

|----------------------------------------------------------------------|-------------|

| • DRC パッケージを「製品レビュー」から「事前情報」に変更.....                                 | 1           |

## 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

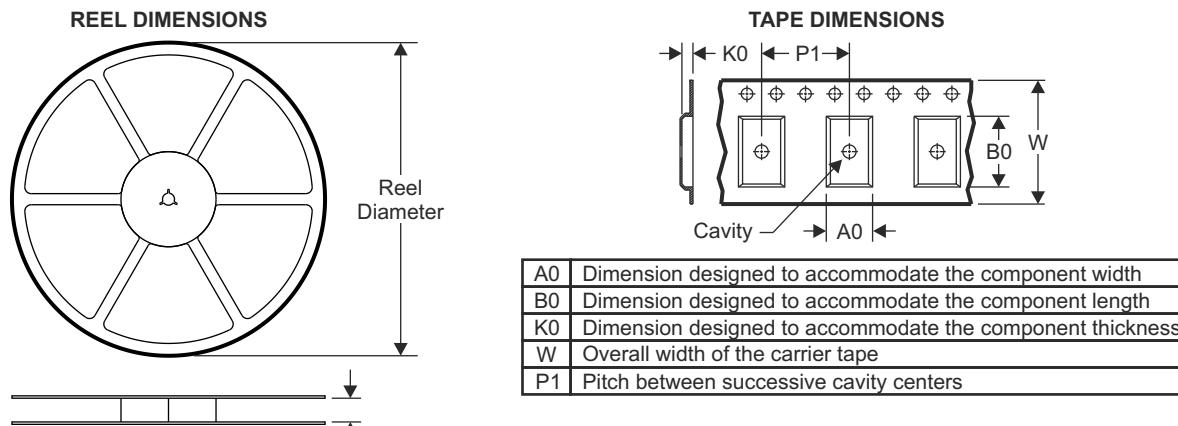

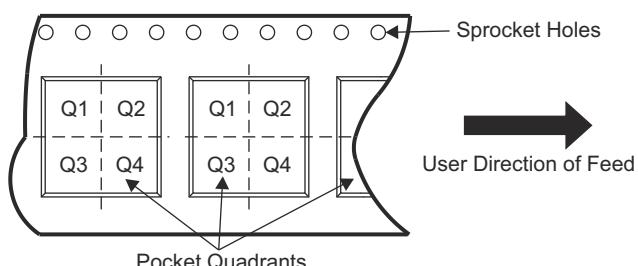

### 12.1 テープおよびリール情報

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| デバイス              | パッケージ<br>タイプ | パッケージ<br>図 | ピン<br>数 | SPQ  | リール<br>直径 (mm) | リール<br>幅 W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | ピン 1 の<br>象限 |

|-------------------|--------------|------------|---------|------|----------------|------------------|------------|------------|------------|------------|-----------|--------------|

| PUCC27301AQDDARQ1 | SO           | DDA        | 8       | 3000 | 330.0          | 12.5             | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1           |

| PUCC27301AQDRCRQ1 | VSON         | DRC        | 10      | 3000 | 330.0          | 12.4             | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2           |

| UCC27301AQDDARQ1  | SO           | DDA        | 8       | 3000 | 330.0          | 12.5             | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1           |

| UCC27301AQDRCRQ1  | VSON         | DRC        | 10      | 3000 | 330.0          | 12.4             | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2           |

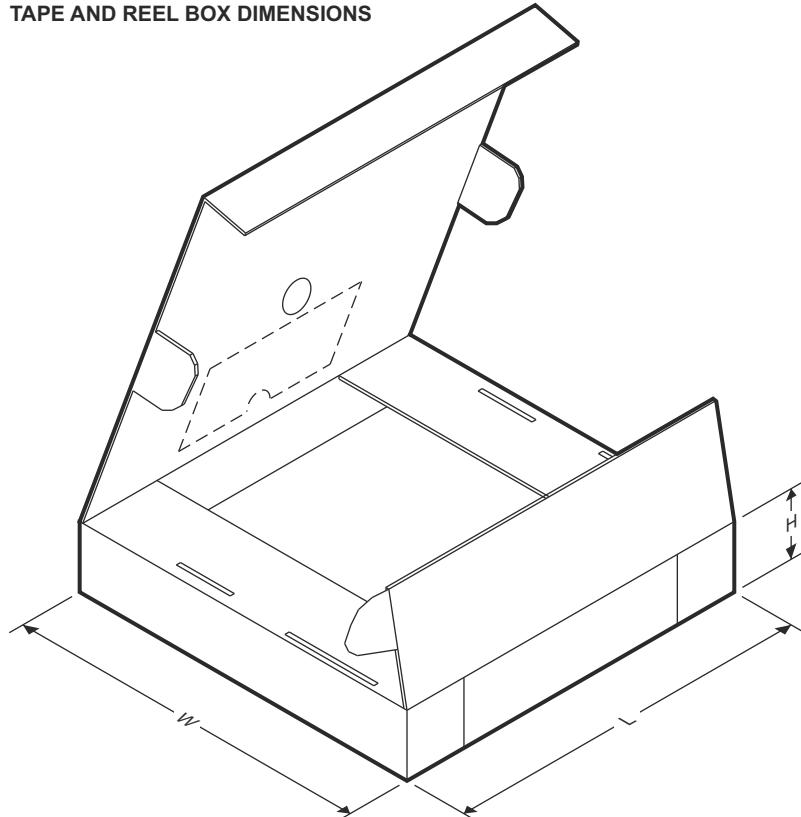

## TAPE AND REEL BOX DIMENSIONS

| デバイス              | パッケージタイプ | パッケージ図 | ピン数 | SPQ  | 長さ (mm) | 幅 (mm) | 高さ (mm) |

|-------------------|----------|--------|-----|------|---------|--------|---------|

| PUCC27301AQDDARQ1 | SO       | DDA    | 8   | 3000 | 340.5   | 336.1  | 25      |

| PUCC27301AQDRCRQ1 | VSON     | DRC    | 10  | 3000 | 367.0   | 367.0  | 35      |

| UCC27301AQDDARQ1  | SO       | DDA    | 8   | 3000 | 340.5   | 336.1  | 25      |

| UCC27301AQDRCRQ1  | VSON     | DRC    | 10  | 3000 | 367.0   | 367.0  | 35      |

## 12.2 メカニカル データ

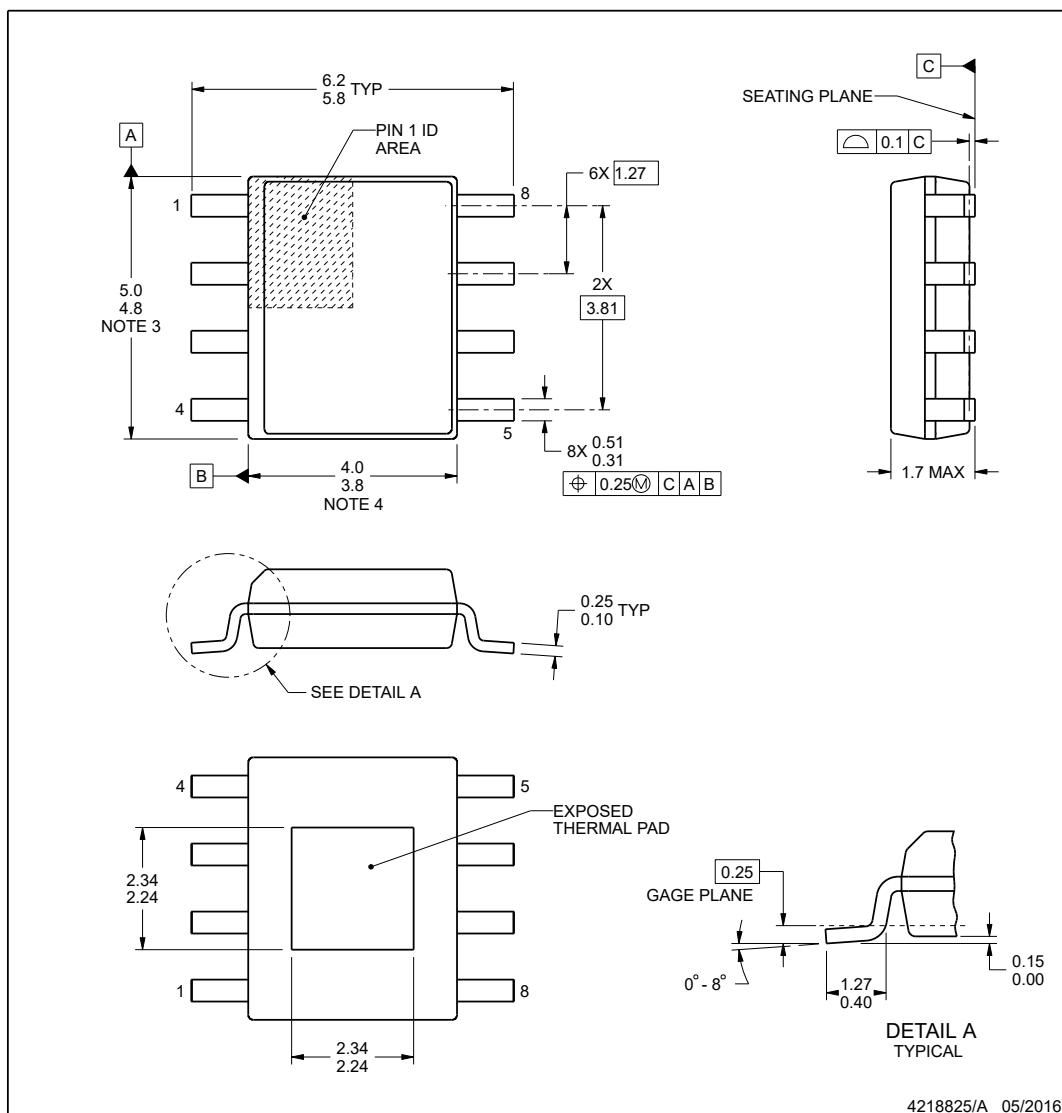

**DDA0008A**

## PACKAGE OUTLINE

PLASTIC SMALL OUTLINE

PowerPAD is a trademark of Texas Instruments

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

5. Reference JEDEC registration MS-012.

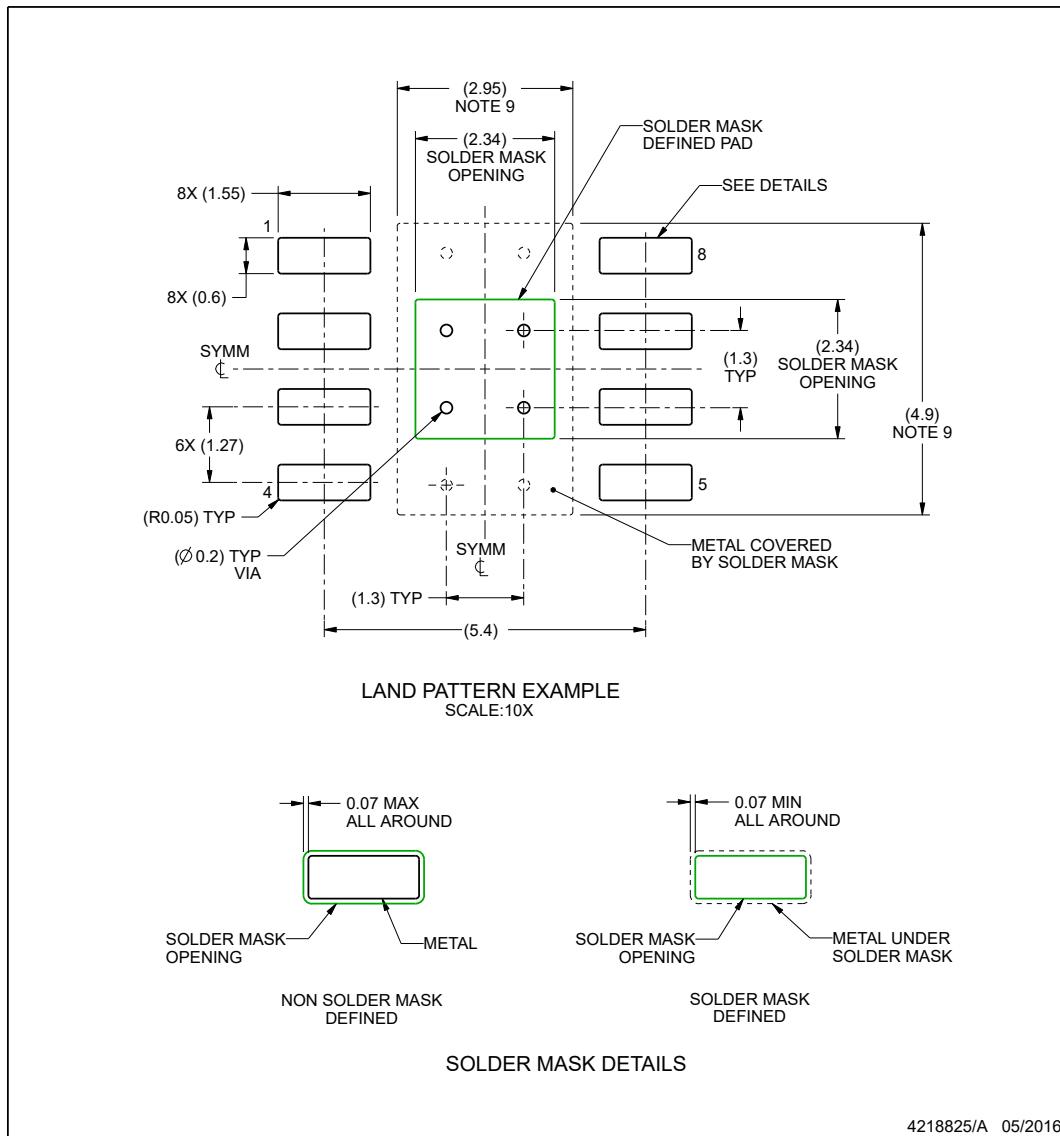

EXAMPLE BOARD LAYOUT

DDA0008A

PowerPAD™ SOIC - 1.7 mm max height

PLASTIC SMALL OUTLINE

4218825/A 05/2016

NOTES: (continued)

- Publication IPC-7351 may have alternate designs.

- Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 ([www.ti.com/lit/slma002](http://www.ti.com/lit/slma002)) and SLMA004 ([www.ti.com/lit/slma004](http://www.ti.com/lit/slma004)).

- Size of metal pad may vary due to creepage requirement.

- Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

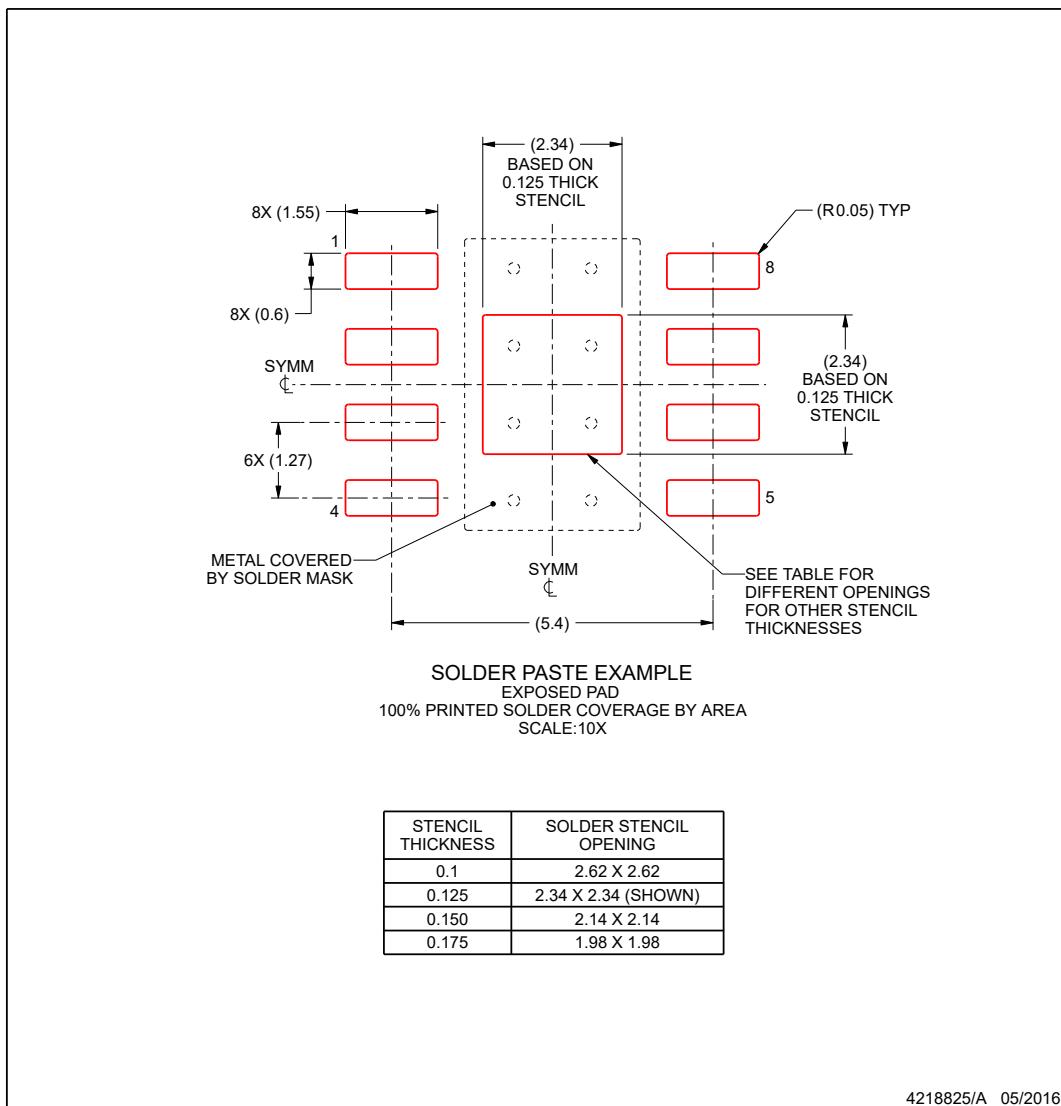

## EXAMPLE STENCIL DESIGN

**DDA0008A**

**PowerPAD™ SOIC - 1.7 mm max height**

PLASTIC SMALL OUTLINE

4218825/A 05/2016

NOTES: (continued)

11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

12. Board assembly site may have different recommendations for stencil design.

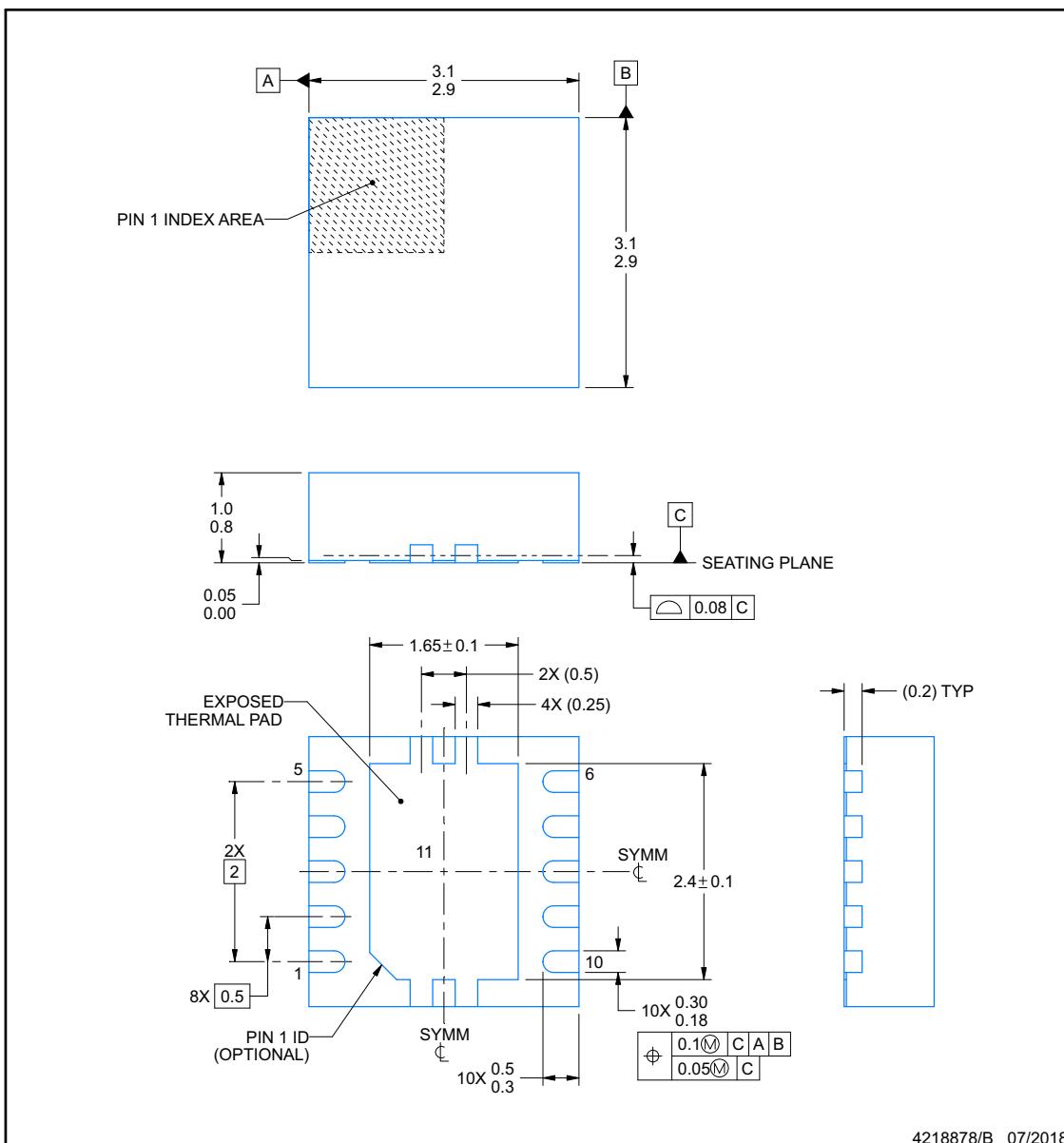

DRC0010J

PACKAGE OUTLINE

VSON - 1 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

4218878/B 07/2018

NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

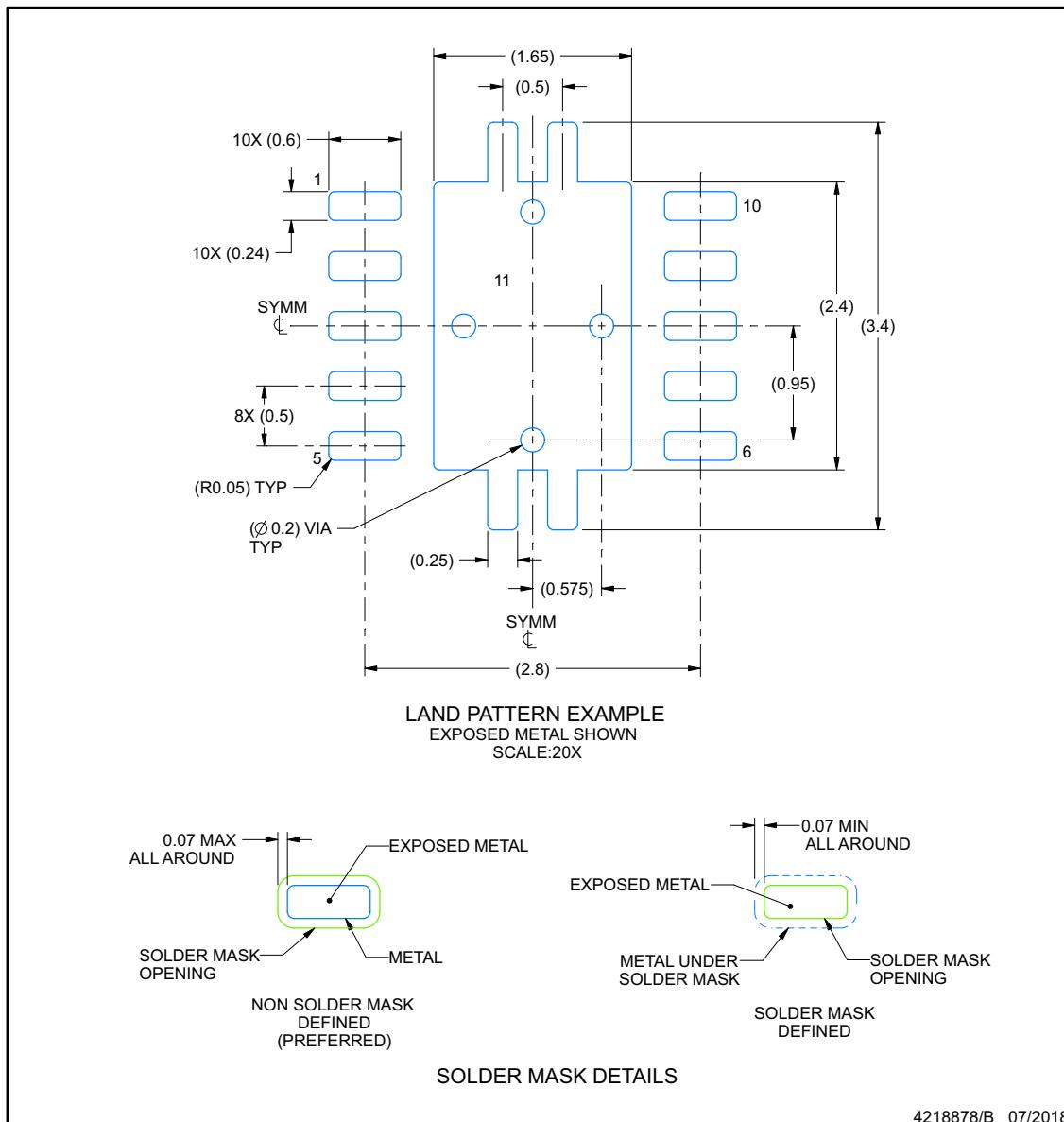

## EXAMPLE BOARD LAYOUT

**DRC0010J**

**VSON - 1 mm max height**

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

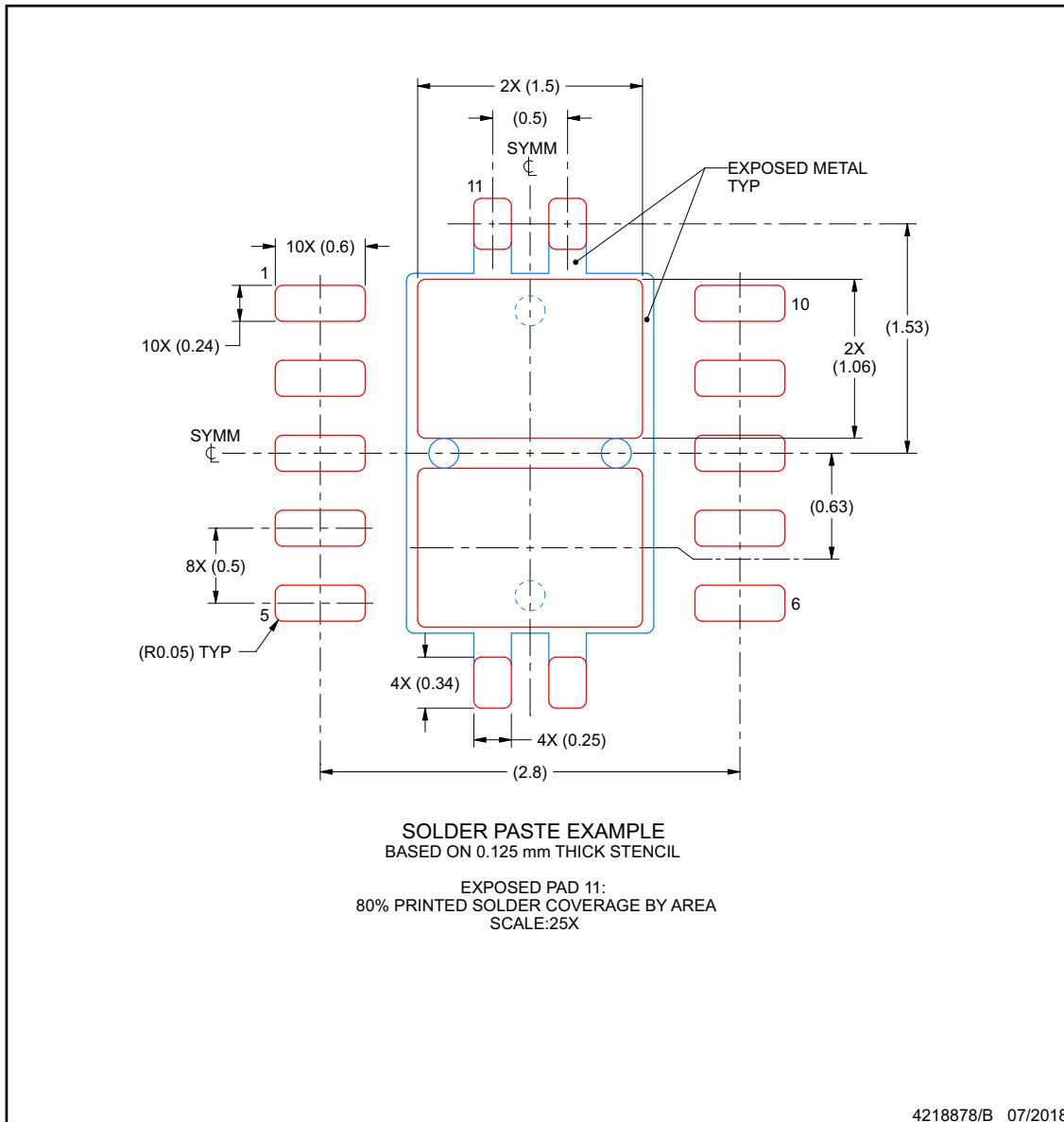

## EXAMPLE STENCIL DESIGN

DRC0010J

VSON - 1 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins           | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|--------------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| UCC27301AQDDARQ1      | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | U27301Q             |

| UCC27301AQDDARQ1.B    | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | U27301Q             |

| UCC27301AQDRCRQ1      | Active        | Production           | VSON (DRC)   10          | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 150   | 27301Q              |

| UCC27301AQDRCRQ1.B    | Active        | Production           | VSON (DRC)   10          | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 150   | 27301Q              |

| UCC27301AQDRQ1        | Active        | Production           | SOIC (D)   8             | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 150   | 27301Q              |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF UCC27301A-Q1 :**

- Catalog : [UCC27301A](#)

NOTE: Qualified Version Definitions:

- Catalog - TI's standard catalog product

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月