# UCC25661 軽負荷時の効率が最適化され、 $V_{IN}/V_{OUT}$ 範囲が広い 750kHz LLC コントローラ

## 1 特長

- 全負荷スイッチング周波数: 50kHz ~ 750kHz

- IPPC 制御による広い入力または広い出力 LLC (WLLC) 動作

- 強化された軽負荷管理機能:

- 高周波数パルス スキップによる軽負荷時の効率向上

- 可聴周波数範囲をスキップすることで、可聴ノイズを低減し、ソフト オン/オフ バースト モードを実現

- 低周波数バーストによるスタンバイ電力の低減と、PFC (力率補正) のオン/オフ制御機能の内蔵

- 内蔵共振コンデンサ電圧シンセサイザによる、信号の信頼性の向上と高い起動周波数のサポート

- 容量性領域動作を排除するためのゼロ電流スイッチング (ZCS) 防止

- 適応型ソフトスタートにより突入電流を最小限に抑え、スタートアップ時の逆回復が不要

- 統合された高電圧スタートアップ

- 内蔵ゲートドライブ: +0.6/-1.2A

- 保護機能を完備

- 50ns の過電流保護 (OCP)、サイクルごとの電流制限

- 過電圧保護 (OVP)、出力電圧ラッチ

- 内部および外部の過熱保護 (OTP)

- 19V VCCP クランプを内蔵した入力および VCCP UVLO

- 個別に構成した OCP および過負荷保護機能

- 高電圧部の間隔を確保するためにピンを削除した SOIC-14 パッケージ

## 2 アプリケーション

- テレビ向け SMPS 電源

- 産業用 AC/DC アダプタ

- 電動工具

- 医療用電源

- マルチファンクション プリンタ

- エンタープライズ/シネマ プロジェクタ

- PC 電源

- ゲーム コンソール電源

- 照明器具

## 3 説明

UCC25661 は、強化された軽負荷管理機能と複数の保護機能に加えて、入力電力比例制御 (IPPC) 方式を実装した高周波数 LLC コントローラです。

IPPC は LLC コンバータの制御範囲を拡大し、LED ドライバやバッテリ充電器など、入力または出力電圧範囲が広いアプリケーションの設計を簡素化します。IPPC は、非汎用入力アプリケーションでは、PFC を使わなくても動作させることができます。

UCC25661 の強化された軽負荷管理機能は、可聴ノイズを最小限に抑えながら、効率を改善します。バースト モードで動作する場合、スタンバイ消費電力を最小化するため、UCC25661 は PFC コントローラを直接無効化します。

適応型ソフトスタートおよび逆方向回復回避方式に加えて、自動容量性領域回避方式により、FET を損傷させる可能性があるモードで本デバイスが動作しないことが検証されます。容量性領域の自動回避方式により、本コントローラはプライバイスされた負荷を使用した動作に適しています。

UCC25661 は、信頼性の高い電源の設計に役立つ堅牢な保護機能を備えています。UCC25661 には、高電圧のスタートアップと OVP 応答をサポートするオプションがあります。「デバイス比較」表の詳細を参照してください。

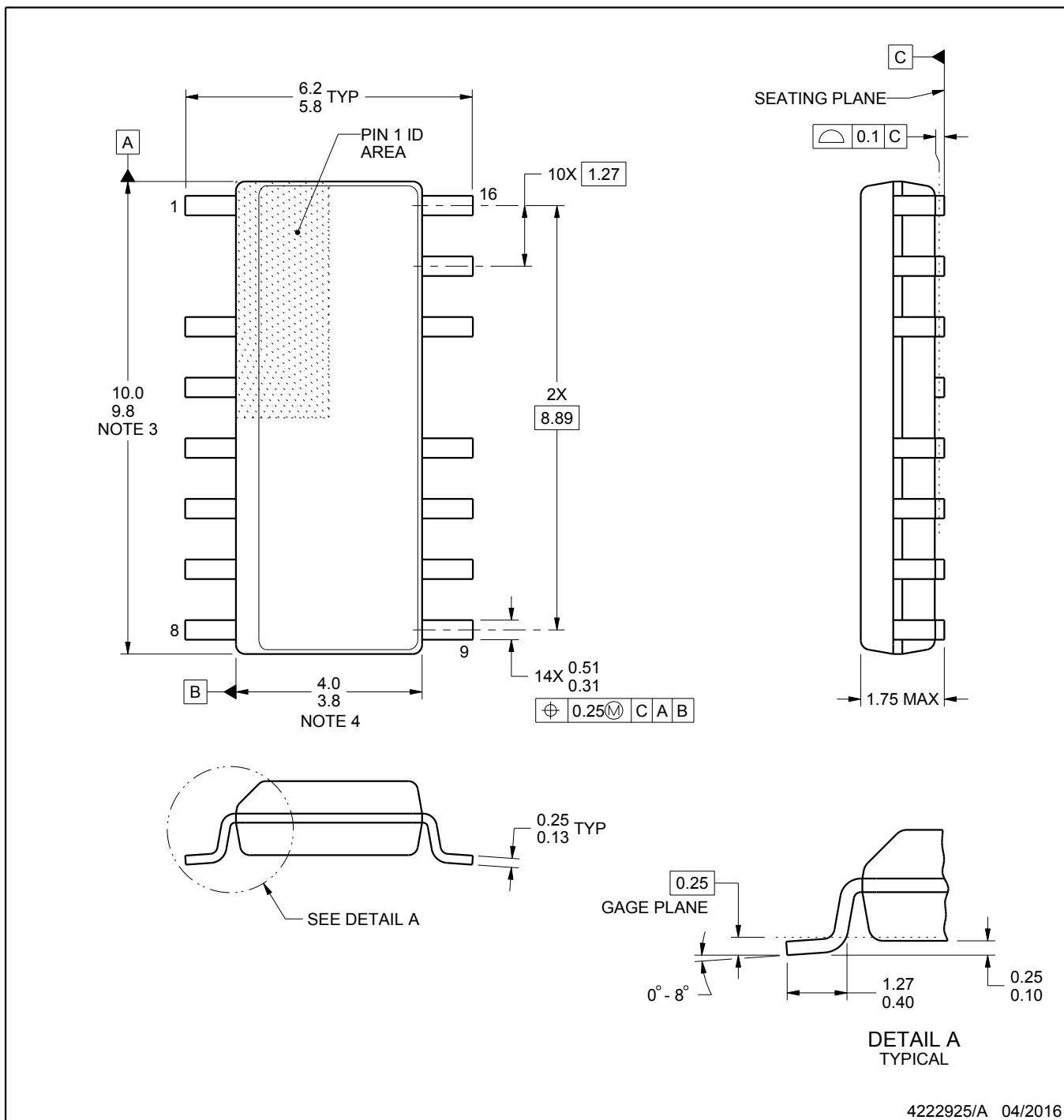

### パッケージ情報

| 部品番号     | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|----------|----------------------|--------------------------|

| UCC25661 | DDB (SOIC, 16)       | 9.9mm × 3.9mm            |

(1) 供給されているすべてのパッケージについては、[セクション 11](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンを含みます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、[ti.com](http://ti.com) で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|              |    |                        |    |

|--------------|----|------------------------|----|

| 1 特長         | 1  | 7.3 機能説明               | 19 |

| 2 アプリケーション   | 1  | 7.4 保護                 | 27 |

| 3 説明         | 1  | 7.5 デバイスの機能モード         | 30 |

| 4 デバイス比較表    | 4  | 8 アプリケーションと実装          | 36 |

| 5 ピン構成および機能  | 5  | 8.1 アプリケーション情報         | 36 |

| 6 仕様         | 7  | 8.2 代表的なアプリケーション       | 36 |

| 6.1 絶対最大定格   | 7  | 8.3 電源に関する推奨事項         | 49 |

| 6.2 ESD 定格   | 7  | 8.4 レイアウト              | 49 |

| 6.3 推奨動作条件   | 8  | 9 デバイスおよびドキュメントのサポート   | 54 |

| 6.4 熱に関する情報  | 8  | 9.1 ドキュメントの更新通知を受け取る方法 | 54 |

| 6.5 電気的特性    | 8  | 9.2 サポート・リソース          | 54 |

| 6.6 スイッチング特性 | 10 | 9.3 商標                 | 54 |

| 6.7 代表的特性    | 12 | 9.4 静電気放電に関する注意事項      | 54 |

| 7 詳細説明       | 16 | 9.5 用語集                | 54 |

| 7.1 概要       | 16 | 10 改訂履歴                | 54 |

| 7.2 機能ブロック図  | 18 | 11 メカニカル、パッケージ、および注文情報 | 56 |

## 4 デバイス比較表

| 発注用型番               | UCC25661          |

|---------------------|-------------------|

| IPPC                | •                 |

| 高電圧スタートアップを内蔵       | •                 |

| X コンデンサ放電機能を内蔵      |                   |

| 拡張ゲイン範囲 (EGR)       |                   |

| 出力 – 電圧 (OVP) ラッチ   | •                 |

| 出力 – 電流 (OCP) ラッチ   | •                 |

| ソフトオン/オフ バースト モード   |                   |

| OCP/OLP デカップリング     | •                 |

| LF バースト中の PFC オン/オフ |                   |

| ZCS フォルト            | •                 |

| BLK OVP イネーブル       | •                 |

| LF バースト周波数          | 1.6kHz～<br>3.2kHz |

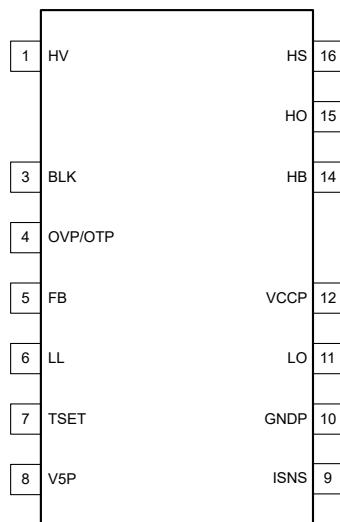

## 5 ピン構成および機能

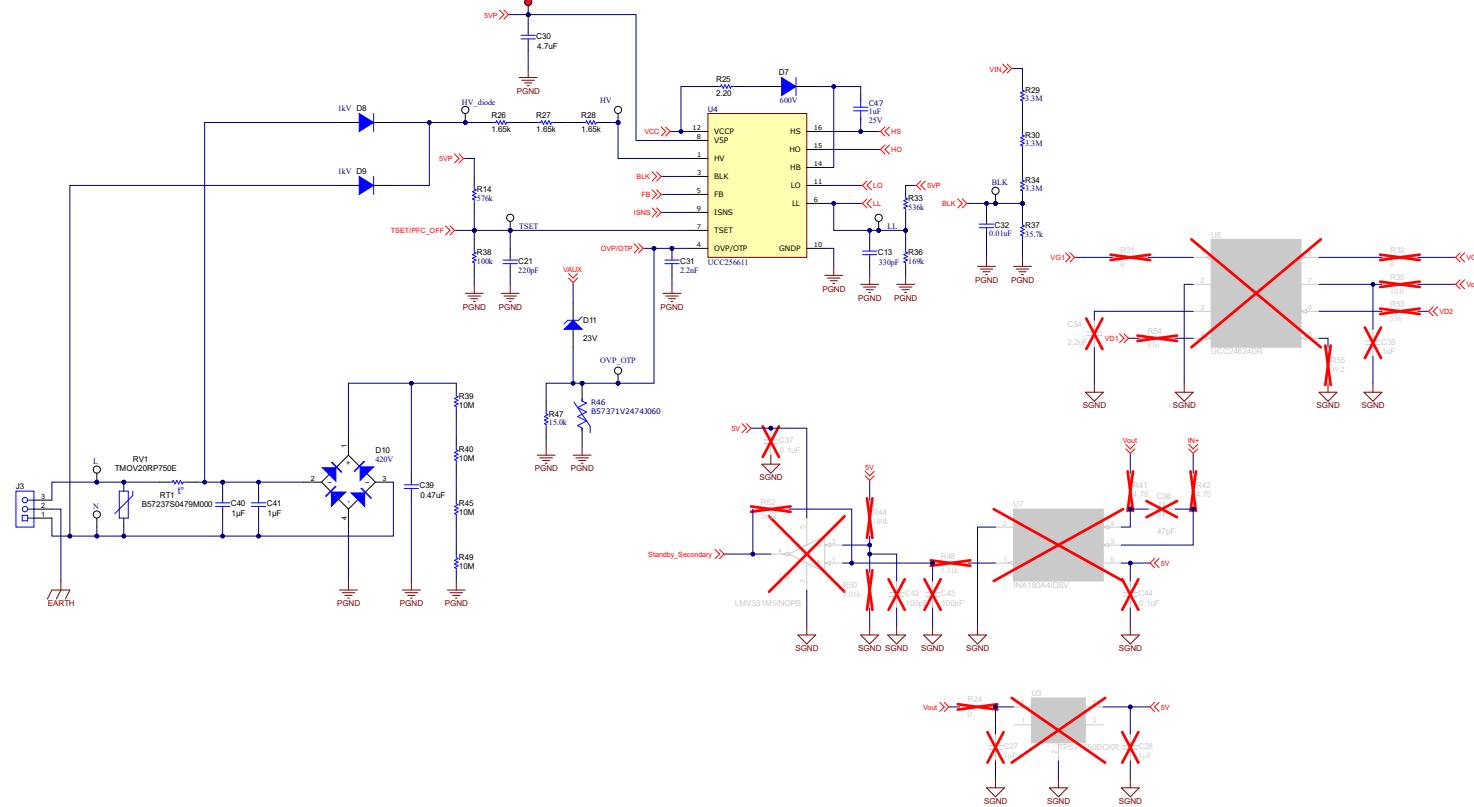

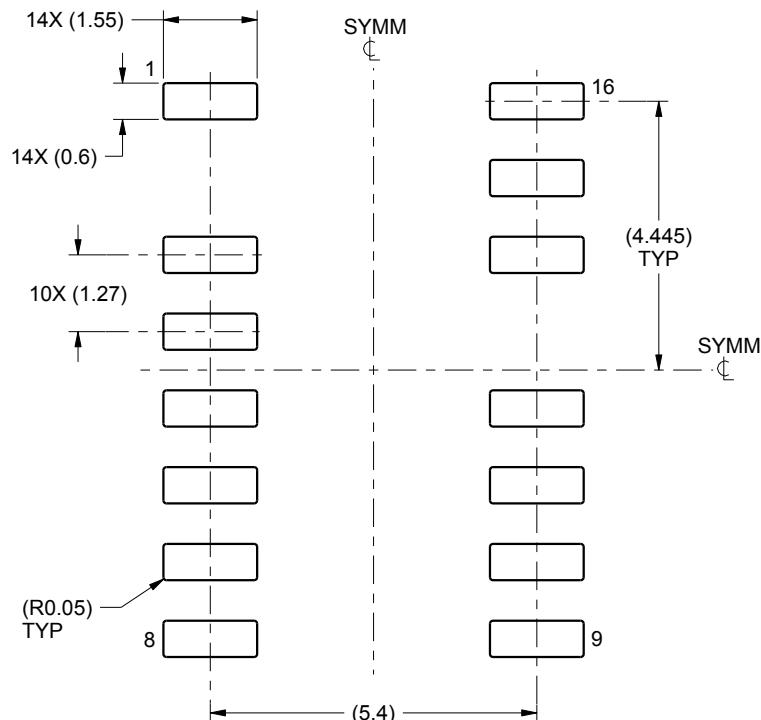

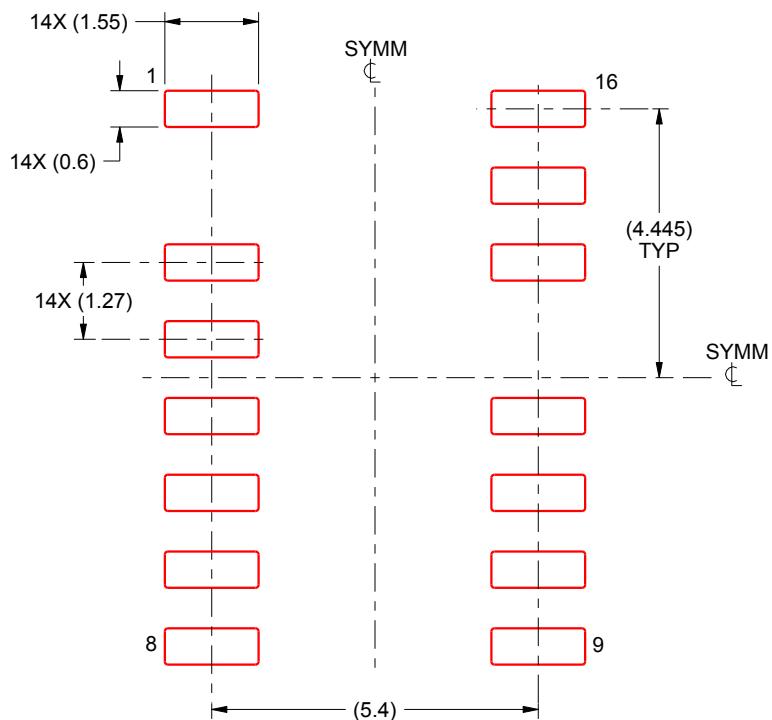

図 5-1. DDB パッケージ 16 ピン SOIC、ピン 2 および 13 を削除 (上面図)

表 5-1. ピンの機能

| ピン      |    | I/O | 説明                                                                                                                                                                                                                                                      |

|---------|----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称      | 番号 |     |                                                                                                                                                                                                                                                         |

| HV      | 1  | I   | 高電圧 (HV) 起動と X コンデンサ放電。<br>HV ピンは、HV 起動を実行するために使用されます。起動完了後、HV ピンは AC 存在検出および X コンデンサ放電に使用されます。このピンは整流された AC ラインまたは入力バルクコンデンサに接続されます。                                                                                                                   |

|         | 2  | —   | なし。高電圧ピンと低電圧ピンの間の沿面距離に対応する HV スペーサー                                                                                                                                                                                                                     |

| BLK     | 3  | I   | フィードフォワード制御用のバulk DC 電圧検出と入力。<br>バulk コンデンサの正端子と GNDP の間の分圧抵抗を介して BLK を接続し、LLC コンバータの開始電圧と停止電圧スレッショルドを設定します。詳細については、 <a href="#">セクション 7.3.5.1</a> を参照してください。                                                                                           |

| OVP/OTP | 4  | I   | 過電圧保護および外部過熱保護入力。<br>OVP/OTP を NTC 抵抗を介して GNDP に、ツェナー ダイオードを介して VCCP に接続します。詳細については、 <a href="#">セクション 7.3.5.3</a> を参照してください。                                                                                                                           |

| FB      | 5  | I   | 帰還制御入力。<br>絶縁型帰還回路のフォトカプラのコレクタピンに FB を接続します。詳細については、 <a href="#">セクション 7.3.3</a> を参照してください。                                                                                                                                                             |

| LL      | 6  | I   | 軽負荷動作とバースト モード スレッショルド設定入力。<br>LL は、V5P と GNDP の間の分圧抵抗の中心ノードに接続します。LL ピンのインピーダンスと電圧を使用して、高周波および低周波数のバーストモード動作のスレッショルドを選択します。詳細については、 <a href="#">セクション 7.5.3</a> を参照してください。                                                                             |

| TSET    | 7  | I/O | VCR シンセサイザの時間定数が入力と PFC オン / オフ出力を設定。<br>TSET は、 <a href="#">セクション 8.2.2.18</a> で定義されている抵抗デバイダを使用して、IPPC モードで最小 VCR 時定数と最小スイッチング周波数を設定します。また、TSET は PFC ディセーブルピンにデュアル機能を配置し、入力として低周波バーストモードを強制することもできます。詳しくは、 <a href="#">セクション 8.2.2.18</a> を参照してください。 |

表 5-1. ピンの機能 (続き)

| ピン   |    | I/O  | 説明                                                                                                                                                                                                                                                                                                  |

|------|----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称   | 番号 |      |                                                                                                                                                                                                                                                                                                     |

| V5P  | 8  | P    | 5V 内部レギュレータ出力。<br>V5P と GNDP の間にデカップリング コンデンサ ( $1\mu\text{F} \sim 4.7\mu\text{F}$ を推奨) を接続します。このコンデンサは、V5P に近づけて配置します。アプリケーションのニーズに基づいて誘電体を選択します。                                                                                                                                                  |

| ISNS | 9  | I    | 共振回路電流検出入力。<br>ISNS ピンを、直列微分コンデンサと電流センス抵抗を経由して GNDP へ共振コンデンサに接続します。<br>このピンは、微分共振コンデンサ電圧を検出します。この信号は内部で次の目的で使用されます。 <ul style="list-style-type: none"><li>• 制御信号の生成</li><li>• OCP とサイクル単位の電流制限</li><li>• 静電容量性領域の回避</li></ul><br>詳細については、 <a href="#">セクション 8.2.2.17</a> を参照してください。                 |

| GNDP | 10 | P    | グランド リファレンス ピン。GNDP を 1 次側バルク コンデンサの負端子に接続します。                                                                                                                                                                                                                                                      |

| LO   | 11 | O    | ローサイド スイッチ ゲートドライバ出力。ローサイド スイッチのゲート端子を最小のゲートドライブ回路のループ面積で接続します。                                                                                                                                                                                                                                     |

| VCCP | 12 | P    | IC 電源電圧 ピン。<br>VCCP と GNDP の間に、低 ESR のセラミック $2.2\mu\text{F}$ デカップリング コンデンサを接続します。これに加えて、エネルギー蓄積の電解コンデンサとフィルタ コンデンサを並列に組み合わせて使用するのが通常です。<br>LLC トランジスの補助バイアス巻線などのアプリケーションでは、VCCP ピンをダイオードを介してバイアス巻線に接続します。HV スタートアップがディスエーブルになっているアプリケーションでは、VCCP は補助バイアス電源から供給されます。<br>VCCP ピンは内部で 19V にクランプされています。 |

|      | 13 | 該当なし | ピンの欠落。高電圧ピンと低電圧ピンの間の沿面距離に対応する高電圧スペーサー。                                                                                                                                                                                                                                                              |

| HB   | 14 | P    | ハイサイド ゲートドライバのバイアス入力。HB ピンと HS ピンの間にコンデンサ (最小値 $0.1\mu\text{F}$ 、最大値 $5\mu\text{F}$ ) を接続します。詳細については、 <a href="#">セクション 8.3.2</a> を参照してください。                                                                                                                                                        |

| HO   | 15 | O    | ハイサイド スイッチ ゲートドライバ出力。最小のゲートドライブ回路のループ面積でハイサイド スイッチのゲート端子に接続します。                                                                                                                                                                                                                                     |

| HS   | 16 | P    | ハイサイド ゲートドライバのリターン パスおよびスイッチング ノード接続の入力。LLC コンバータのハーフ ブリッジ構造のスイッチング ノードに接続します。このピンの電圧によって、アダプティブ ディード タイムを決定します。詳細については、 <a href="#">セクション 7.3.4</a> を参照してください。                                                                                                                                     |

詳細については、セクション [セクション 8.2](#) を参照してください。

## 6 仕様

### 6.1 絶対最大定格

動作自由空気温度範囲全体で(特に記述のない限り)、すべての電圧値は GND を基準にしています。電流は指定されたピンに流れ込む方向が正、ピンから流れ出る方向が負です。<sup>(1)</sup>

|                         |                         | 最小値      | 最大値        | 単位   |

|-------------------------|-------------------------|----------|------------|------|

| 入力電圧                    | HV、HB                   | -0.3     | 700        | V    |

|                         | ISNS                    | -6.5     | 6.5        | V    |

|                         | BLK、LL、TSET             | -0.55    | 5.5        | V    |

|                         | HB - HS                 | -0.3     | 25         | V    |

|                         | VCCP                    | -0.55    | 30         | V    |

|                         | OVP/OTP                 | -0.55    | 5.5        | V    |

| 5V                      | DC                      | -0.55    | 5.5        | V    |

| HO 出力電圧                 | DC                      | HS - 0.3 | HB + 0.3   | V    |

|                         | 過渡応答、100ns 未満           | HS - 2   | HB + 0.3   |      |

| LO 出力電圧                 | DC                      | -0.3     | VCCP+ 0.3  | V    |

|                         | 過渡応答、100ns 未満           | -2       | VCCP + 0.3 |      |

| フローティング グランド スルーレート     | dV <sub>HS</sub> /dt    | -200     | 200        | V/ns |

| HO、LO パルス電流             | I <sub>OUT_PULSED</sub> | -0.6     | 1.2        | A    |

| 接合部温度範囲                 | T <sub>J</sub>          | -40      | 150        | °C   |

| 保管温度範囲、T <sub>stg</sub> | T <sub>stg</sub>        | -65      | 150        |      |

| リード温度                   | 半田付け、10 秒               |          | 300        |      |

|                         | リフロー                    |          | 260        |      |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスに恒久的な損傷を与える可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

### 6.2 ESD 定格

|                    |      |                                                                      | 値     | 単位 |

|--------------------|------|----------------------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001、HV、HO、HS、HB ピン <sup>(1)</sup> に準拠 | ±1000 | V  |

|                    |      | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、他すべてのピン <sup>(1)</sup>        | ±2000 |    |

|                    |      | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠、すべてのピン <sup>(2)</sup>       | ±500  |    |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 6.3 推奨動作条件

特に記述のない限り、すべての電圧値は GND を基準にしており、 $-40^{\circ}\text{C} < T_J = T_A < 125^{\circ}\text{C}$  であり、電流は、指定されたピンに流れ込む方向が正、ピンから流れ出る方向が負です。

|                     |                         | 最小値 | 公称値 | 最大値  | 単位 |

|---------------------|-------------------------|-----|-----|------|----|

| HV, HS              | 入力電圧                    |     |     | 640  | V  |

| V <sub>VCCP</sub>   | 電源電圧                    |     | 15  | 18.5 | V  |

| HB - HS             | ドライバ ブートストラップ電圧         | 10  | 14  | 17.5 | V  |

| C <sub>B</sub>      | HB から HS へのセラミック バイパス容量 | 0.1 |     | 5    | μF |

| C <sub>VCCP</sub>   | VCCP ピン デカップリング容量       | 33  |     | 470  | μF |

| I <sub>VCCPMA</sub> | VCCP の最大入力電流            |     |     | 100  | mA |

| T <sub>A</sub>      | 動作時の周囲温度                | -40 |     | 125  | °C |

## 6.4 热に関する情報

| 熱評価基準 <sup>(1)</sup>  |                     | UCC25661 | 単位   |

|-----------------------|---------------------|----------|------|

|                       |                     | D (SOIC) |      |

|                       |                     | 14 ピン    |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 74.7     | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 30.7     | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 31.8     | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 4.4      | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ    | 31.4     | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 6.5 電気的特性

特に記述のない限り、すべての電圧値は GND を基準にしており、 $-40^{\circ}\text{C} < T_J < 125^{\circ}\text{C}$ 、VCC = 15V であり、電流は、指定されたピンに流れ込む方向が正、ピンから流れ出る方向が負です。

| パラメータ                        |                                               | テスト条件                   | 最小値  | 標準値  | 最大値  | 単位 |

|------------------------------|-----------------------------------------------|-------------------------|------|------|------|----|

| <b>電源電圧</b>                  |                                               |                         |      |      |      |    |

| VCC <sub>Short</sub>         | このスレッショルドを下回ると、低減起動電流を使用                      |                         | 0.6  | 1    | 1.4  | V  |

| VCC <sub>ReStartJfet</sub>   | このスレッショルドを下回ると、JFET を再有効化。                    |                         |      | 10.2 |      | V  |

| VCC <sub>ReStart</sub>       | 起動フェーズ中に VCC がこのレベルを下回ると、HV 起動が再度イネーブルになります   |                         | 12.5 | 13   | 13.5 | V  |

| VCC <sub>StartSelf</sub>     | VCC がこのレベルを上回っている場合に起動します                     |                         | 13.5 | 14   | 14.5 | V  |

| VCC <sub>StartExt</sub>      | VCC がこのレベルを上回っている場合に起動します                     |                         | 10.5 | 10.9 | 11.3 | V  |

| VCC <sub>StopSwitching</sub> | スイッチングはこのスレッショルドを下回ると停止します                    |                         | 9    | 9.5  |      | V  |

| VCC <sub>UVLor</sub>         | VCC 低電圧誤動作防止電圧 (立ち上がり)                        |                         | 7.25 | 7.5  | 7.82 | V  |

| VCC <sub>UVLof</sub>         | VCC 低電圧誤動作防止電圧ヒステリシス                          |                         | 6.5  | 6.8  | 7.1  | V  |

| VCC <sub>Hold_r</sub>        | 起動プログラミング フェーズ中の Jfet ストップ電圧                  |                         | 7.9  | 8.2  | 8.5  | V  |

| VCC <sub>Hold_f</sub>        | スタートアップ プログラミング フェーズ中の Jfet 開始電圧              |                         | 7.65 | 7.9  | 8.15 | V  |

| VCC <sub>Shunt</sub>         | VCC 内部クランプ電圧                                  |                         |      | 19   |      | V  |

| I <sub>VCC_Clamp</sub>       | VCC 内部クランプ電流                                  |                         |      | 15   |      | mA |

| VCC <sub>OV</sub>            | VCC OVP スレッショルド                               |                         |      | 20.5 |      | V  |

| <b>電源電流</b>                  |                                               |                         |      |      |      |    |

| I <sub>CCSleep</sub>         | バースト オフ期間に VCC レールから引き出される電流                  |                         | 800  |      |      | μA |

| I <sub>CCRun</sub>           | ゲートがスイッチング動作中に VCC ピンから引き込まれた電流。ゲート電流を除く      | デッド タイム = 1μs 最大デッド タイム |      | 8    |      | mA |

| I <sub>CCLatchFault</sub>    | ラッチされたフォルト状態で VCC ピンから引き込まれた電流 <sup>(1)</sup> |                         |      |      | 1    | mA |

## 6.5 電気的特性 (続き)

特に記述のない限り、すべての電圧値は GND を基準にしており、 $-40^{\circ}\text{C} < T_{\text{J}} < 125^{\circ}\text{C}$ 、 $\text{VCC} = 15\text{V}$  であり、電流は、指定されたピンに流れ込む方向が正、ピンから流れ出る方向が負です。

| パラメータ                            | テスト条件                                                                                                                                  | 最小値                                                                                                | 標準値  | 最大値  | 単位   |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------|------|------|

| <b>安定化電源</b>                     |                                                                                                                                        |                                                                                                    |      |      |      |

| V5P                              | 安定化電源電圧 <sup>(1)</sup>                                                                                                                 | 無負荷                                                                                                | 4.75 | 5    | 5.25 |

|                                  | 安定化電源電圧                                                                                                                                | 10mA 負荷                                                                                            | 4.75 | 5    | 5.25 |

| V5P <sub>UVLO</sub>              | V5P 低電圧誤動作防止電圧 <sup>(1)</sup>                                                                                                          |                                                                                                    | 4    |      | V    |

| I <sub>V5PStartupCurrLimit</sub> | $\text{VCCP} < \text{VCC}_{\text{StartSelf}}$ のときに、ピンに引き込むことができる最大電流 <sup>(1)</sup>                                                    | $\text{VCCP} = 15\text{V}$                                                                         | 6    |      | mA   |

| I <sub>V5PCurrLimit</sub>        | V5P (IV5P = 15mA の場合)                                                                                                                  | $\text{VCCP} = 15\text{V}$                                                                         | 10.2 |      | mA   |

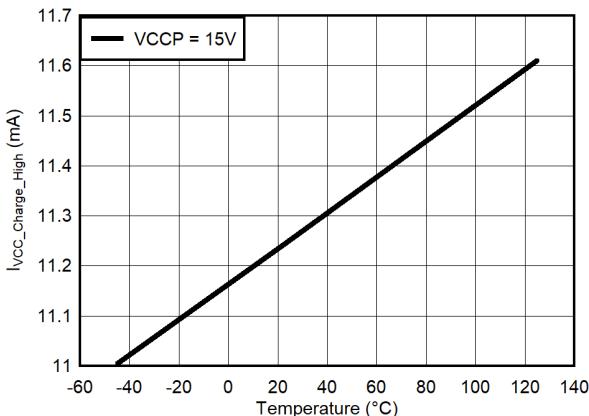

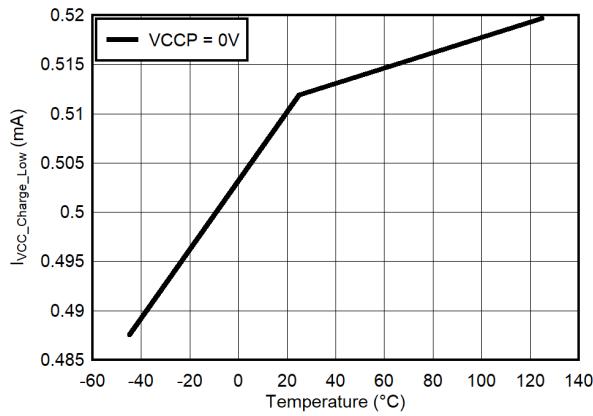

| <b>高電圧起動</b>                     |                                                                                                                                        |                                                                                                    |      |      |      |

| I <sub>VCC_Charge_Low</sub>      | HV ピンからの VCCP 充電電流の低減                                                                                                                  | $\text{V}_{\text{HV}} = 20\text{V}$ 、 $\text{VCC} = 0\text{V}$ 、                                   | 0.23 | 0.44 | 0.65 |

| I <sub>VCC_Charge_High</sub>     | VCCP 完全充電電流                                                                                                                            | $\text{V}_{\text{HV}} = 20\text{V}$ 、 $\text{VCC} = 4\text{V}$ 、                                   | 7.5  | 10   | 13.8 |

| <b>パルク電圧検知</b>                   |                                                                                                                                        |                                                                                                    |      |      |      |

| V <sub>BLKStartHys</sub>         | BLK 電圧コンバレータのヒステリシス <sup>(1)</sup>                                                                                                     |                                                                                                    | 0.09 | 0.1  | 0.11 |

| V <sub>BLKStop</sub>             | LLC の動作を停止させる BLK 電圧                                                                                                                   |                                                                                                    | 0.98 | 1    | 1.02 |

| I <sub>BLKHys</sub>              | BLK ヒステリシス電流 (パルク電圧低下 Isink)                                                                                                           |                                                                                                    | 5    |      | μA   |

| <b>フィードバックピン</b>                 |                                                                                                                                        |                                                                                                    |      |      |      |

| R <sub>FBInternal</sub>          | 内部ブルダウン抵抗値                                                                                                                             |                                                                                                    | 42.5 | 50   | 57.5 |

| I <sub>FB</sub>                  | FB 内部電流源                                                                                                                               |                                                                                                    | 136  | 160  | 184  |

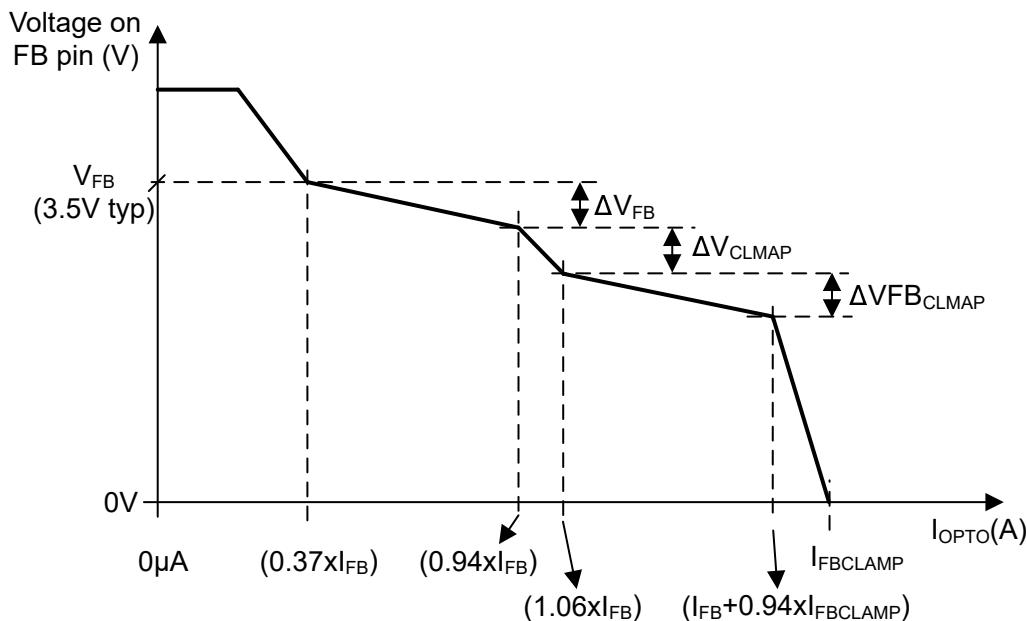

| V <sub>FB</sub>                  | FB ピンのシンク電流が ( $I_{\text{FB}} = 50\mu\text{A}$ ) であるときの FB ピンの電圧                                                                       | $I_{\text{lopt}} = 0.37 \times I_{\text{FB}}$                                                      | 3.3  | 3.5  | 3.7  |

| ΔV <sub>FB</sub>                 | FB ピンのシンク電流範囲 ( $I_{\text{lopt}} = 0.37 \times I_{\text{FB}}$ から $I_{\text{lopt}} = 0.94 \times I_{\text{FB}}$ ) での FB ピン電圧変動          |                                                                                                    |      | 0.6  | V    |

| ΔV <sub>clamp</sub>              | FB ピンのシンク電流範囲が ( $I_{\text{lopt}} = 0.94 \times I_{\text{FB}}$ ) から ( $I_{\text{lopt}} = 1.06 \times I_{\text{FB}}$ ) までのときの FB ピン電圧変動 | $(I_{\text{lopt}} = 0.94 \times I_{\text{FB}}) \sim (I_{\text{lopt}} = 1.06 \times I_{\text{FB}})$ | 0.3  |      | V    |

| I <sub>FBclamp</sub>             | FB がクランプされているときの最大 FB 内部電流源                                                                                                            |                                                                                                    | 150  | 175  | 200  |

| f <sub>3dB</sub>                 | 帰還信号経路 -3dB カットオフ周波数 <sup>(2)</sup>                                                                                                    | VFBReplica (4.5V ~ 0.5V)                                                                           | 1    |      | MHz  |

| V <sub>FBOLP</sub>               | OLP 保護 <sup>(1)</sup>                                                                                                                  |                                                                                                    | 4.75 |      | V    |

| TOLP <sub>Fault</sub>            | OLP 保護時間 <sup>(1)</sup>                                                                                                                |                                                                                                    | 100  |      | ms   |

| <b>共振電流検知</b>                    |                                                                                                                                        |                                                                                                    |      |      |      |

| V <sub>ISNS_OCP</sub>            | 定常状態での OCP スレッショルド                                                                                                                     |                                                                                                    | 3.4  | 3.5  | 3.6  |

| V <sub>ISNS_OCPn</sub>           | 定常状態での OCP の負のスレッショルド                                                                                                                  |                                                                                                    | -3.6 | -3.5 | -3.4 |

| V <sub>ISNS_OCP_SS</sub>         | ソフトスタート中の OCP スレッショルド                                                                                                                  |                                                                                                    | 2.9  | 3    | 3.1  |

| V <sub>ISNS_OCP_SSn</sub>        | ソフトスタート中の OCP の負のスレッショルド                                                                                                               |                                                                                                    | -3.1 | -3   | -2.9 |

| n <sub>OCP</sub>                 | OCP フォルトがトリップされる前の OCP サイクル数 <sup>(1)</sup>                                                                                            |                                                                                                    | 7    |      |      |

| n <sub>OCP_SS</sub>              | スタートアップ時に OCP フォルトがトリップされるまでの OCP サイクル数 <sup>(2)</sup>                                                                                 |                                                                                                    | 50   |      |      |

| V <sub>IpolarityHyst</sub>       | ISNS 極性コンバレータのヒステリシス                                                                                                                   |                                                                                                    | 40   |      | mV   |

| V <sub>ISNS_ZCS</sub>            | ソフトスタート後の ZCS コンバレータ + Ve スレッショルド                                                                                                      |                                                                                                    | 150  |      | mV   |

| V <sub>ISNS_ZCSn</sub>           | ZCS コンバレータ - Ve スレッショルド、ソフトスタート後                                                                                                       |                                                                                                    | -150 |      | mV   |

| V <sub>ISNS_MINCURR_SS</sub>     | ソフトスタート中の +Ve ISNS スレッショルド                                                                                                             |                                                                                                    | 50   |      | mV   |

| V <sub>ISNS_MINCURR_SS_n</sub>   | ソフトスタート時の -Ve ISNS スレッショルド                                                                                                             |                                                                                                    | -50  |      | mV   |

| t <sub>leb</sub>                 | ZCS および OCP コンバレータ用のリーディング エッジ ブランкиング <sup>(1)</sup>                                                                                  |                                                                                                    | 298  |      | ns   |

| TZCS <sub>Fault</sub>            | ZCS イベントが一定時間存在する場合に検出された障害 <sup>(2)</sup>                                                                                             | ZCS イベントは継続します                                                                                     | 10   |      | ms   |

| <b>ゲートドライバ</b>                   |                                                                                                                                        |                                                                                                    |      |      |      |

| V <sub>LOL</sub>                 | LO 出力の Low 電圧                                                                                                                          | $I_{\text{sink}} = 20\text{mA}$                                                                    |      | 0.12 | V    |

| V <sub>RVCC - VLOH</sub>         | LO 出力 high 電圧                                                                                                                          | $I_{\text{source}} = 20\text{mA}$                                                                  |      | 0.3  | V    |

| V <sub>HOL - VHS</sub>           | HO 出力の Low 電圧                                                                                                                          | $I_{\text{sink}} = 20\text{mA}$                                                                    |      | 0.12 | V    |

| V <sub>HB - VHOH</sub>           | HO 出力 high 電圧                                                                                                                          | $I_{\text{source}} = 20\text{mA}$                                                                  |      | 0.35 | V    |

| V <sub>HB-HSUVLOFall</sub>       | ハイサイド ゲートドライバ UVLO 立ち下がりスレッショルド                                                                                                        |                                                                                                    | 6.4  | 7.25 | 8    |

## 6.5 電気的特性 (続き)

特に記述のない限り、すべての電圧値は GND を基準にしており、 $-40^{\circ}\text{C} < T_J < 125^{\circ}\text{C}$ 、 $\text{VCC} = 15\text{V}$  であり、電流は、指定されたピンに流れ込む方向が正、ピンから流れ出る方向が負です。

| パラメータ                          |                                                  | テスト条件                                | 最小値                          | 標準値 | 最大値  | 単位                 |

|--------------------------------|--------------------------------------------------|--------------------------------------|------------------------------|-----|------|--------------------|

| $V_{\text{HB-HSUVLOHys}}$      |                                                  | ハイサイド ゲート ドライバ UVLO スレッショルド ヒステリシス   | 0.78                         | 0.9 | 1.05 | V                  |

| $I_{\text{source_pk_HO}}$      |                                                  | HO ピーク ソース電流 <sup>(2)</sup>          | $\text{VCCP} = 12\text{V}$ で |     | -0.6 | A                  |

| $I_{\text{source_pk_LO}}$      |                                                  | LO ピーク ソース電流 <sup>(2)</sup>          | $\text{VCCP} = 12\text{V}$ で |     | -0.6 | A                  |

| $I_{\text{sink_pk_HO}}$        |                                                  | HO ピーク シンク電流 <sup>(2)</sup>          | $\text{VCCP} = 12\text{V}$ で |     | 1.2  | A                  |

| $I_{\text{sink_pk_LO}}$        |                                                  | LO ピーク シンク電流 <sup>(2)</sup>          | $\text{VCCP} = 12\text{V}$ で |     | 1.2  | A                  |

| <b>ブートストラップ</b>                |                                                  |                                      |                              |     |      |                    |

| $I_{\text{BOOT QUIESCENT}}$    | (HB - HS) 静止電流                                   | $\text{HB} - \text{HS} = 12\text{V}$ | 60                           | 70  | 70   | $\mu\text{A}$      |

| $I_{\text{BOOT LEAK}}$         | HB から GND へのリーク電流                                | $V_{\text{HB}} = 600\text{V}$        | 0.045                        | 20  | 20   | $\mu\text{A}$      |

| $t_{\text{ChargeBoot}}$        | 充電ブート状態の長さ <sup>(1)</sup>                        |                                      | 230                          | 265 | 300  | $\mu\text{s}$      |

| <b>ソフトスタート</b>                 |                                                  |                                      |                              |     |      |                    |

| $SSRamp$                       | ソフトスタート ランプ時間 <sup>(1)</sup>                     |                                      | 25                           |     |      | ms                 |

| <b>OVP/OTP</b>                 |                                                  |                                      |                              |     |      |                    |

| $V_{\text{clamp_otp1}}$        | 0mA でのクランプ電圧 <sup>(1)</sup>                      | クランプに流れる電流が 0mA の場合                  | 1.35                         | 1.5 | 1.65 | V                  |

| $V_{\text{clamp_otp2}}$        | 1mA でのクランプ電圧 <sup>(1)</sup>                      | クランプに流れる電流が 1mA の場合                  | 2.9                          | 3.5 | 4.1  | V                  |

| $I_{\text{OTP}}$               | BW/OTP ピンの電流ソース                                  |                                      | 100                          |     |      | $\mu\text{A}$      |

| $V_{\text{OVPpos}}$            | 出力電圧 OVP — 立ち上がりスレッショルド                          |                                      | 3.5                          |     |      | V                  |

| $V_{\text{OTP Neg}}$           | OTP — 立ち下がりスレッショルド                               |                                      | 0.8                          |     |      | V                  |

| $OTP_{\text{Comphys}}$         | OTP コンバレータのヒステリシス                                |                                      | 60                           | 90  | 130  | mV                 |

| $OVP_{\text{Comphys}}$         | OVP コンバレータのヒステリシス                                |                                      | 60                           | 100 | 145  | mV                 |

| $OTP_{\text{Blankingstartup}}$ | 起動時の OTP ブランкиング時間                               |                                      | 50                           |     |      | ms                 |

| $TOTP_{\text{Fault}}$          | OTP フォルト検出時間                                     |                                      | 330                          |     |      | us                 |

| $TOVP_{\text{Fault}}$          | OVP フォルト検出時間 <sup>(2)</sup>                      |                                      | 40                           |     |      | us                 |

| <b>TSET</b>                    |                                                  |                                      |                              |     |      |                    |

| $I_{\text{TSETPrgm}}$          | プログラミング用の TSET ピンのソース電流                          |                                      | 10                           |     |      | $\mu\text{A}$      |

| <b>LL</b>                      |                                                  |                                      |                              |     |      |                    |

| $I_{\text{LLPrgm}}$            | ベースト モード遷移スレッショルド設定用の LL ピン ソース電流 <sup>(2)</sup> |                                      | 10                           |     |      | $\mu\text{A}$      |

| $t_{\text{LLPrgm}}$            | ベースト モード遷移スレッショルドのプログラミング時間 <sup>(2)</sup>       |                                      | 2                            |     |      | ms                 |

| <b>アダプティブ デッドタイム</b>           |                                                  |                                      |                              |     |      |                    |

| $dV_{\text{HS}}/dt$            | 検出可能なスルーレート (立ち下がりスロープ) <sup>(2)</sup>           |                                      | 0.1                          | 200 | 200  | V/ns               |

| <b>FAULT 回復</b>                |                                                  |                                      |                              |     |      |                    |

| $t_{\text{PauseTimeOut}}$      | 一時停止タイム <sup>(1)</sup>                           |                                      | 1                            |     |      | s                  |

| <b>サーマル シャットダウン</b>            |                                                  |                                      |                              |     |      |                    |

| $T_{\text{J_r}}$               | サーマル シャットダウン温度 <sup>(1)</sup>                    | 温度上昇                                 | 125                          | 150 | 150  | $^{\circ}\text{C}$ |

| $T_{\text{J_H}}$               | サーマル シャットダウン ヒステリシス <sup>(1)</sup>               |                                      | 20                           |     |      | $^{\circ}\text{C}$ |

(1) 量産時にはテストを行っていません。特性により検証されています

(2) 量産時にはテストを行っていません。設計により検証済み

## 6.6 スイッチング特性

特に記述のない限り、すべての電圧値は GND を基準にしており、 $-40^{\circ}\text{C} < T_J = T_A < 125^{\circ}\text{C}$ 、 $\text{VCC} = 15\text{V}$  であり、電流は、指定されたピンに流れ込む方向が正、ピンから流れ出る方向が負です。

| パラメータ              |  | テスト条件   | 最小値              | 標準値 | 最大値 | 単位 |

|--------------------|--|---------|------------------|-----|-----|----|

| $t_{\text{r(LO)}}$ |  | 立ち上がり時間 | 10% ~ 90%、1nF 負荷 |     | 30  | 60 |

| $t_{\text{r(LO)}}$ |  | 立ち下がり時間 | 10% ~ 90%、1nF 負荷 |     | 20  | 30 |

| $t_{\text{r(HO)}}$ |  | 立ち上がり時間 | 10% ~ 90%、1nF 負荷 |     | 30  | 60 |

| $t_{\text{r(HO)}}$ |  | 立ち下がり時間 | 10% ~ 90%、1nF 負荷 |     | 15  | 50 |

## 6.6 スイッチング特性 (続き)

特に記述のない限り、すべての電圧値は GND を基準にしており、 $-40^{\circ}\text{C} < T_J = T_A < 125^{\circ}\text{C}$ 、 $\text{VCC} = 15\text{V}$  であり、電流は、指定されたピンに流れ込む方向が正、ピンから流れ出る方向が負です。

| パラメータ               |                                      | テスト条件                 | 最小値  | 標準値 | 最大値 | 単位            |

|---------------------|--------------------------------------|-----------------------|------|-----|-----|---------------|

| $t_{DT(\min)}$      | 最小デッド タイム <sup>(1)</sup>             |                       | 60   |     |     | ns            |

| $t_{DT(\max)}$      | 最大デッド タイム (デッド タイム異常) <sup>(1)</sup> | ZCS スレッシュホールドは検出されません | 1.2  |     |     | $\mu\text{s}$ |

| $t_{DT(\max\_ZCS)}$ | 最大デッド タイム (デッド タイム異常) <sup>(1)</sup> | ZCS スレッシュホールドが検出されました | 1.31 |     |     | $\mu\text{s}$ |

| $t_{ON(\min)}$      | 最小ゲート オン時間                           |                       | 300  |     |     | ns            |

| $t_{ON(\max)}$      | 最大ゲート オン時間                           |                       | 11.9 |     |     | $\mu\text{s}$ |

| $t_{IPOL(ZCS)}$     | DT を終端するため IPOL 信号を使用できるブランкиング時間    | ZCS スレッシュホールドが検出されました | 595  |     |     | ns            |

(1) 量産時にはテストを行っていません。設計により保証されています

## 6.7 代表的特性

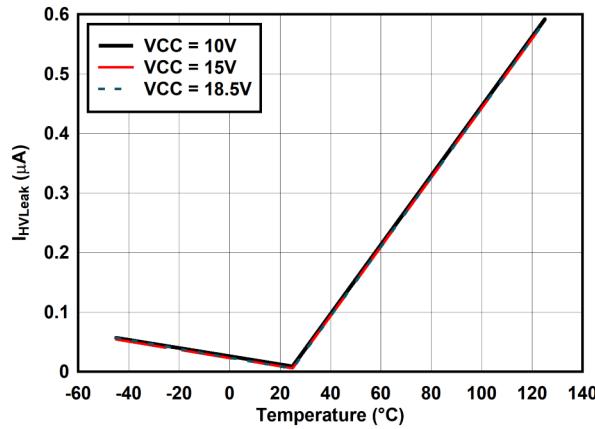

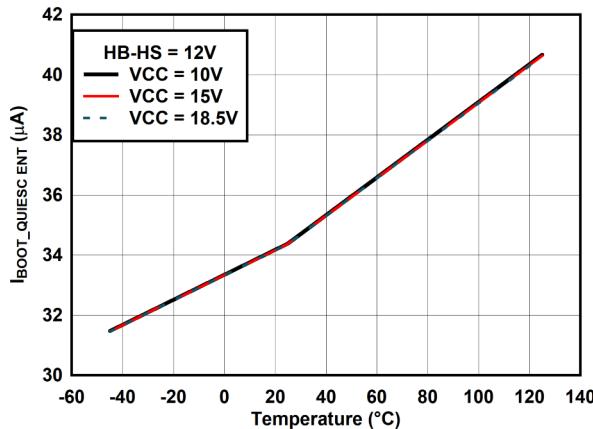

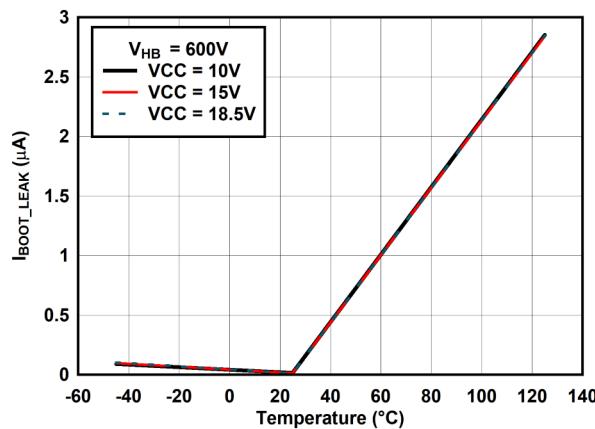

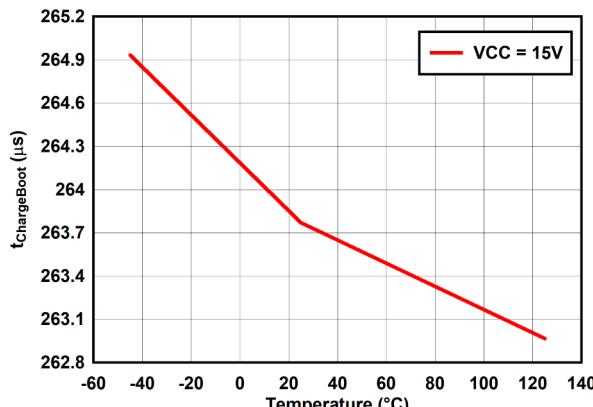

図 6-1.  $I_{VCC\_Charge\_High}$  と温度との関係図 6-2.  $I_{VCC\_Charge\_low}$  と温度との関係図 6-3.  $I_{HVLeak}$  と温度との関係図 6-4.  $I_{BOOT\_QUIESCENT}$  と温度との関係図 6-5.  $I_{BOOT\_LEAK}$  と温度との関係図 6-6.  $t_{chargeBoot}$  と温度との関係

## 6.7 代表的特性 (続き)

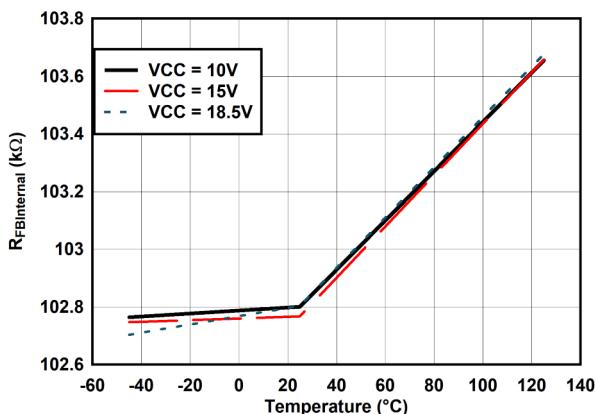

図 6-7.  $R_{FBinternal}$  と温度との関係

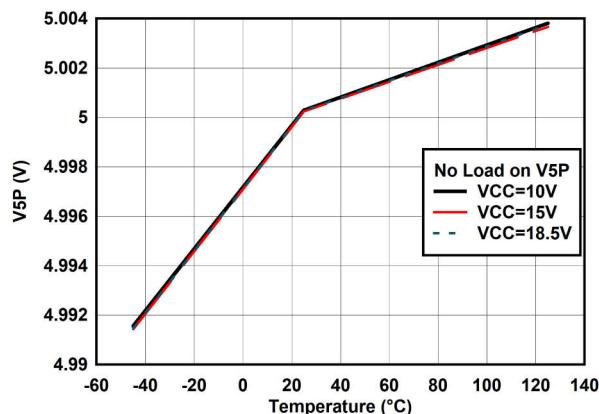

図 6-8.  $V_{5P}$  (無負荷) と温度との関係

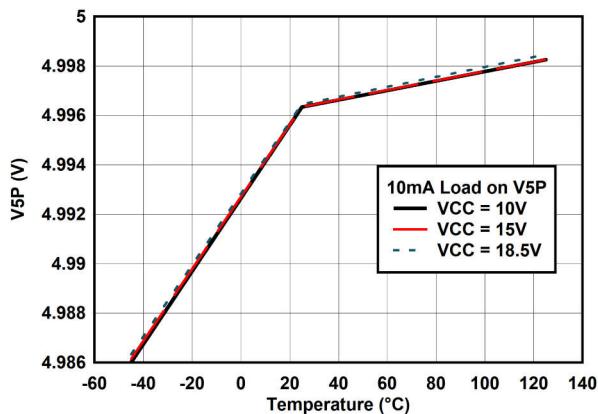

図 6-9.  $V_{5P}$  (10mA 無負荷) と温度との関係

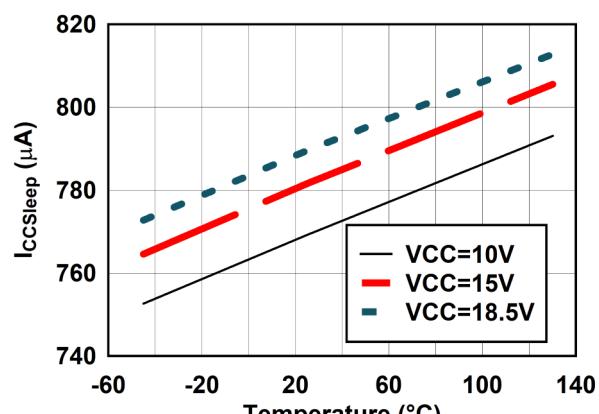

図 6-10.  $I_{CCSleep}$  と温度との関係

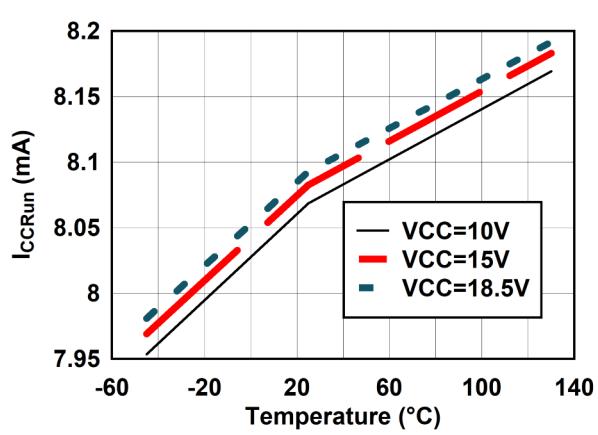

図 6-11.  $I_{CCRun}$  と温度との関係

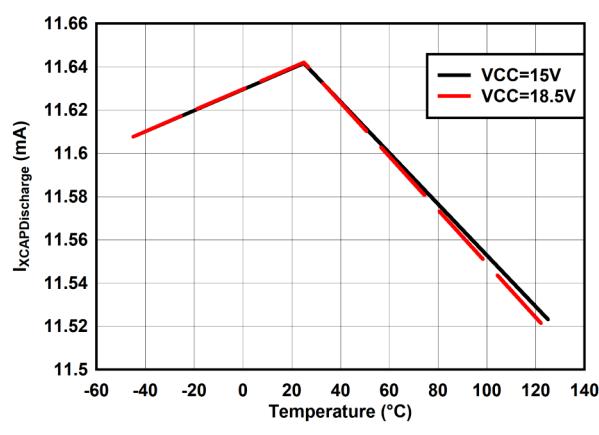

図 6-12.  $I_{XCAPDischarge}$  と温度との関係

## 6.7 代表的特性 (続き)

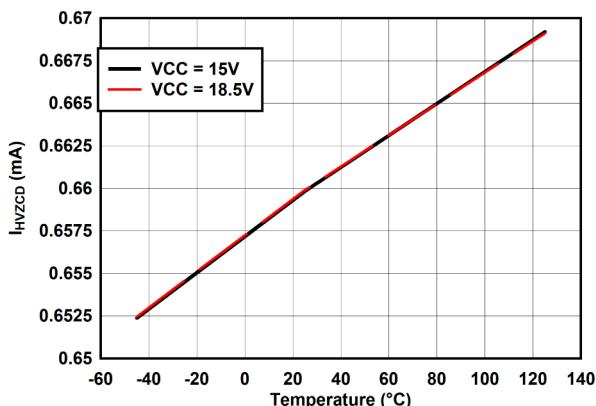

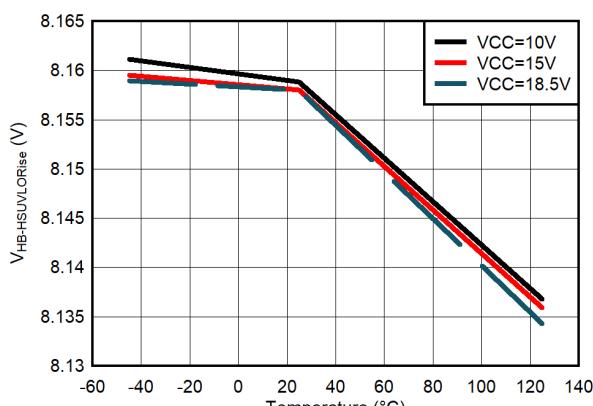

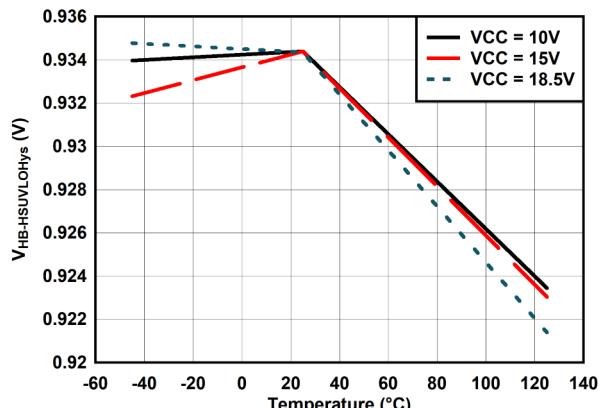

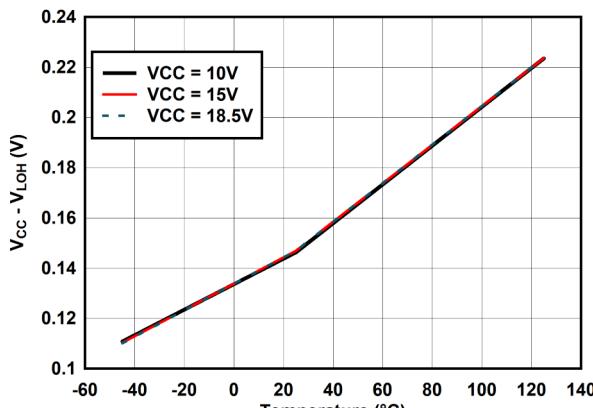

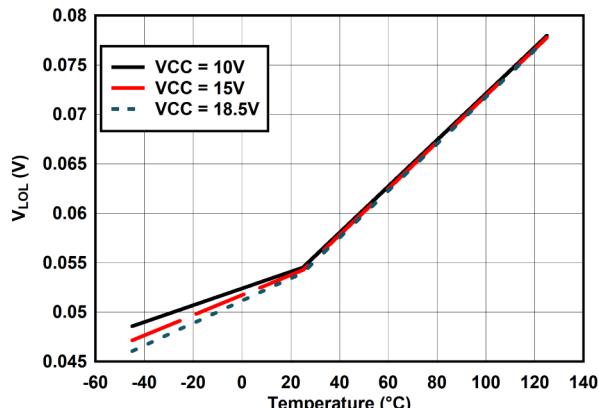

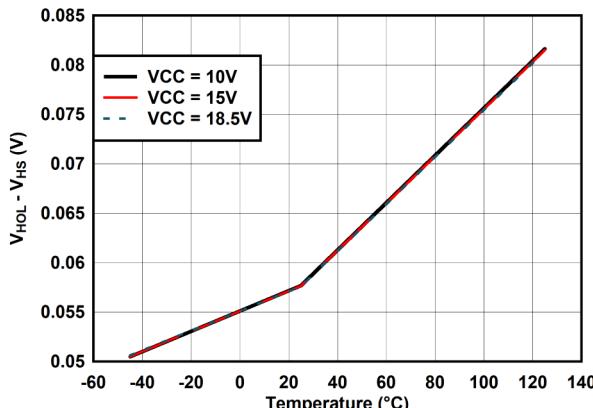

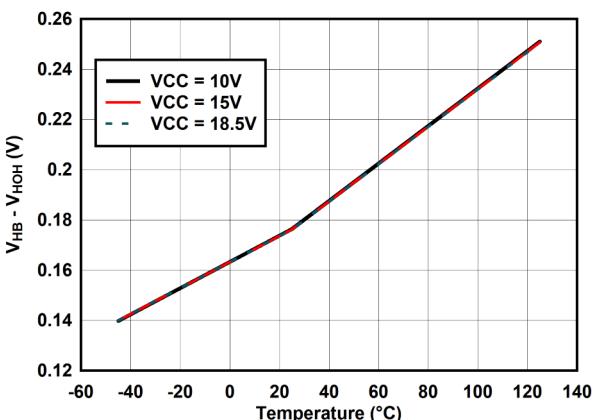

図 6-13.  $I_{HVZCD}$  vs 温度図 6-14.  $V_{HB-HSUVLORise}$  と温度との関係図 6-15.  $I_{HB-HSUVLOHys}$  と温度との関係図 6-16.  $(V_{RVCC} - V_{LOH})$  と温度との関係図 6-17.  $V_{LOL}$  と温度との関係図 6-18.  $(V_{HOL} - V_{HS})$  と温度との関係

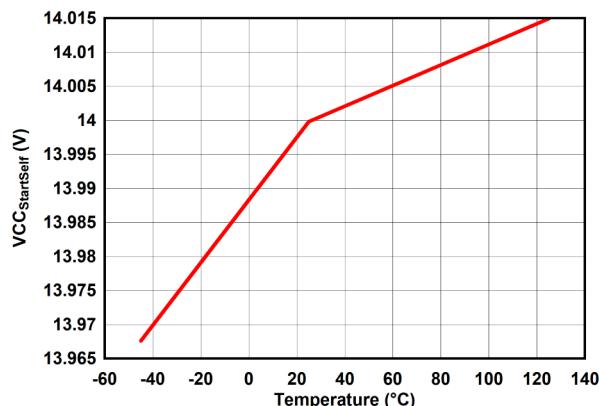

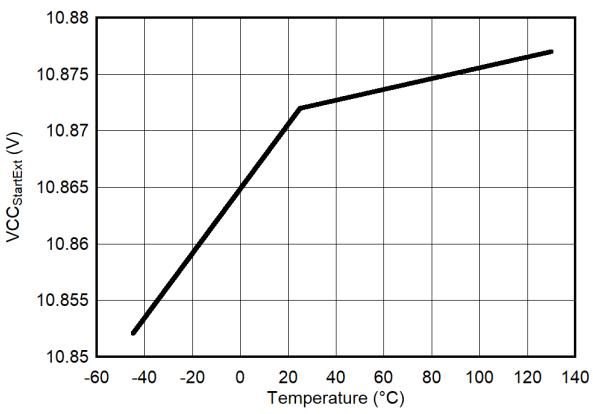

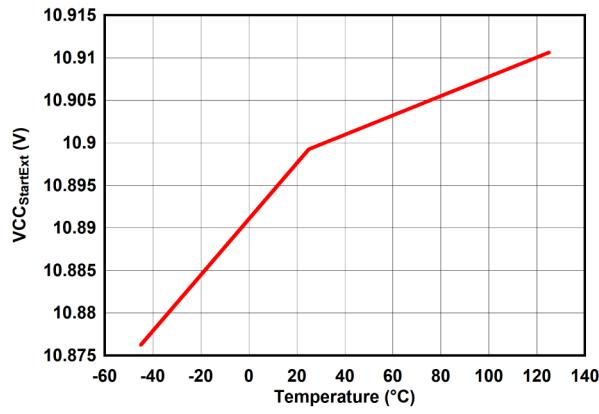

## 6.7 代表的特性 (続き)

図 6-19. ( $V_{HB} - V_{HOH}$ ) と温度との関係

図 6-20.  $VCC_{StartSelf}$  と温度との関係

図 6-21.  $VCC_{StartExt}$  と温度との関係

図 6-22.  $VCC_{StartExt}$  と温度との関係

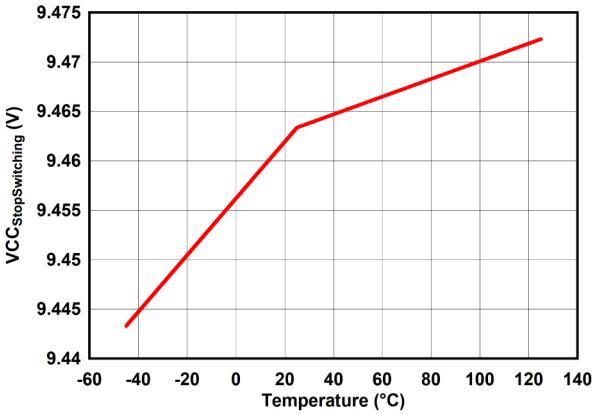

図 6-23.  $VCC_{StopSwitching}$  と温度との関係

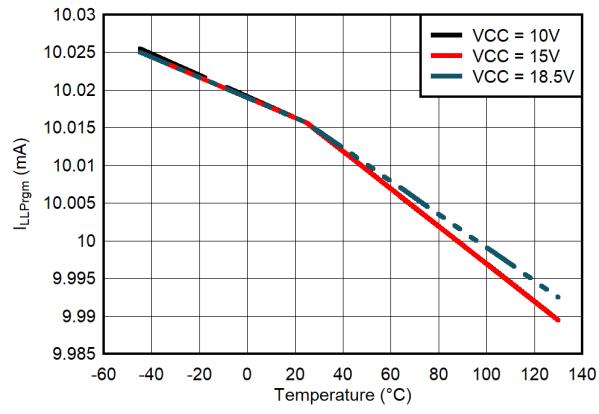

図 6-24.  $I_{LLPrgm}$  と温度との関係

## 7 詳細説明

### 7.1 概要

UCC25661 は、絶縁型電源向けのフル機能 LLC 共振コントローラです。UCC25661 は、高度な統合と、広い入出力電圧動作、高い電力密度、LLC 電力段の信頼性向上に対応できるように、いくつかの設計機能を搭載しています。

このデバイスの新しい制御方式入力電力比例制御 (IPPC) は、電流モード制御に固有の優れた過渡性能を提供すると同時に、広い入力および出力電圧変動に対して入力電力と制御信号との線形関係を実現します。IPPC 制御により、広い入出力電圧変動にわたって、安定した軽負荷およびバースト モード性能での動作が可能になります。

UCC25661 の一部の新機能は、以下のように規定されています。

- IPPC 制御により、幅広い入出力電圧動作で、より安定したバースト モードと動的応答を実現。

- 可聴ノイズを低減しながら軽負荷の効率を向上させる新しい動作モード

- 高周波数 (HF) パルス スキップによる軽負荷時の効率向上

- スタンバイ時の消費電力を低減するための低周波数 (LF) バースト モード

- 出力リップルと効率のバランスを確保できるように、プログラマブルな軽負荷/バースト モード スレッショルド

- 入力電圧の変化に対応する、適応型のバースト モード スレッショルド調整

- 広いバースト モード ヒステリシスにより、バースト モードの開始と終了の発振を防止

- ソフトインとバースト モードのソフトアウトにより、可聴ノイズをさらに最小化するとともに、バースト モードを強制的に保持するオプションも用意しています

- 最大 750kHz の全負荷スイッチング周波数により、電力密度の高い設計が可能

- 共振電流検出と内部制御電圧生成を組み合わせることで、制御の堅牢性が向上

- 入力電圧フィード フォワード

- 以下の保護機能を内蔵しています。

- 高速なサイクルごとの電流制限。50ns

- OCP フォルト検出により、短絡状態で保護

- 過電力保護 (OPP) により、ピーク入力電力を制限

- 容量性領域動作を排除するためのゼロ電流スイッチング (ZCS) 回避方式

- 適応型ソフトスタートにより突入電流を低減し、スタートアップ時の逆回復が不要

- 外部 OVP/OTP 保護

- 入力およびバイアス電源 (VCCP) UVLO

- 入力電圧フィード フォワード

- OCP/OLP デカップリングにより、保護スレッショルドを個別に設定できます

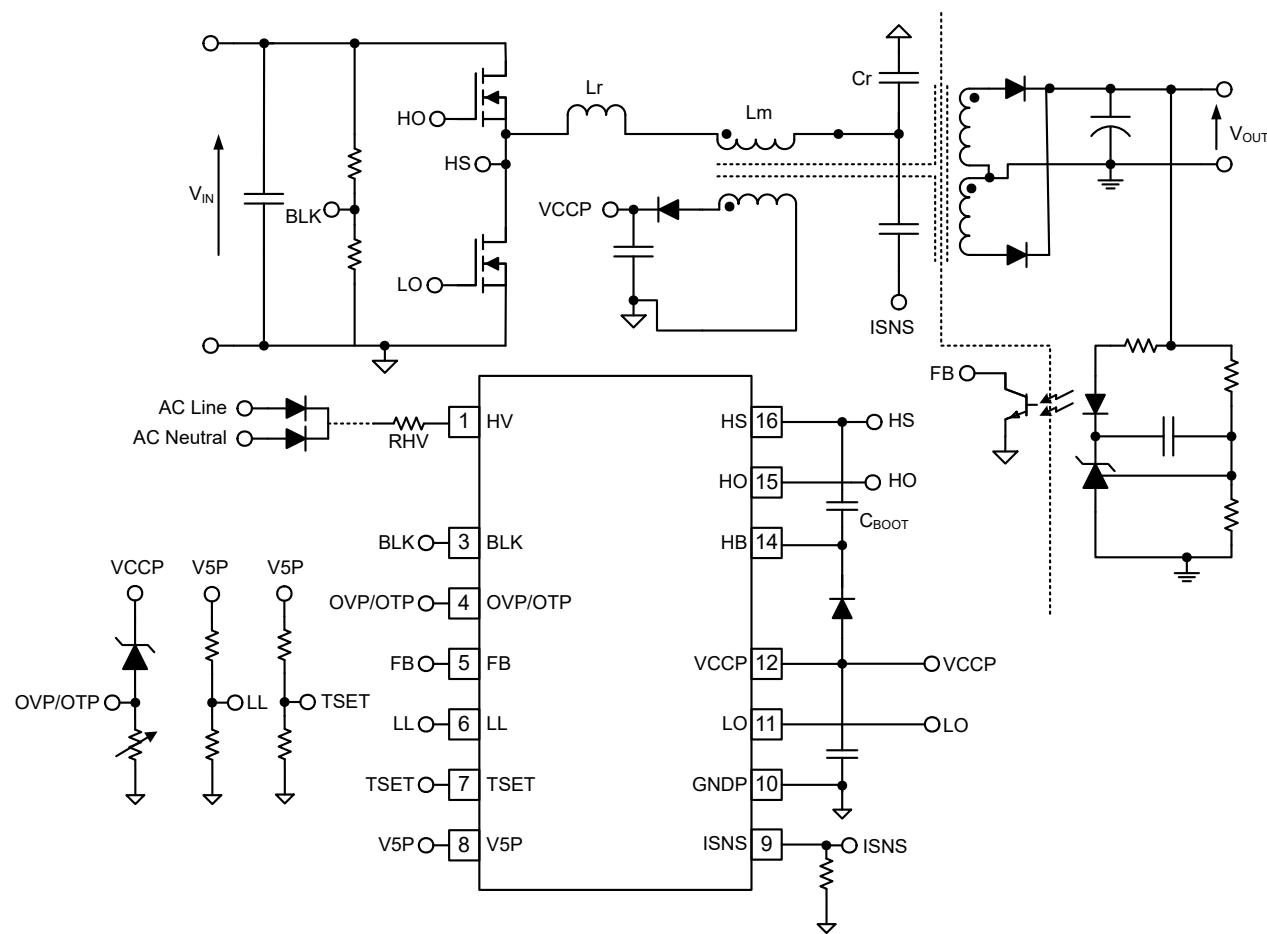

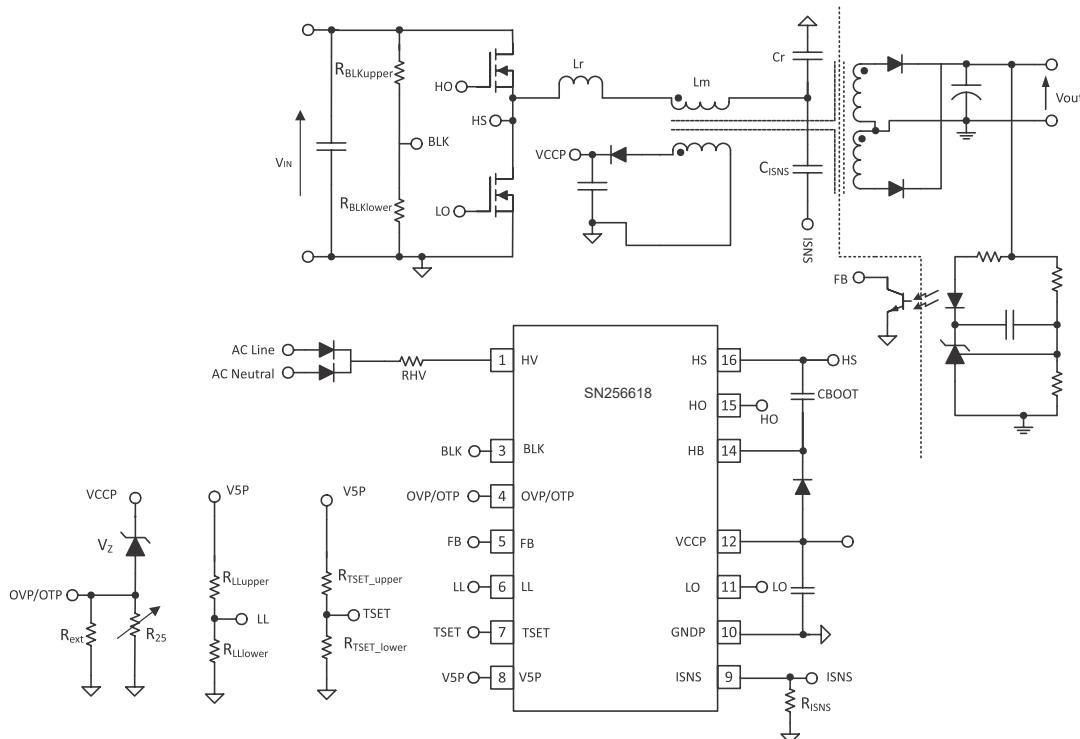

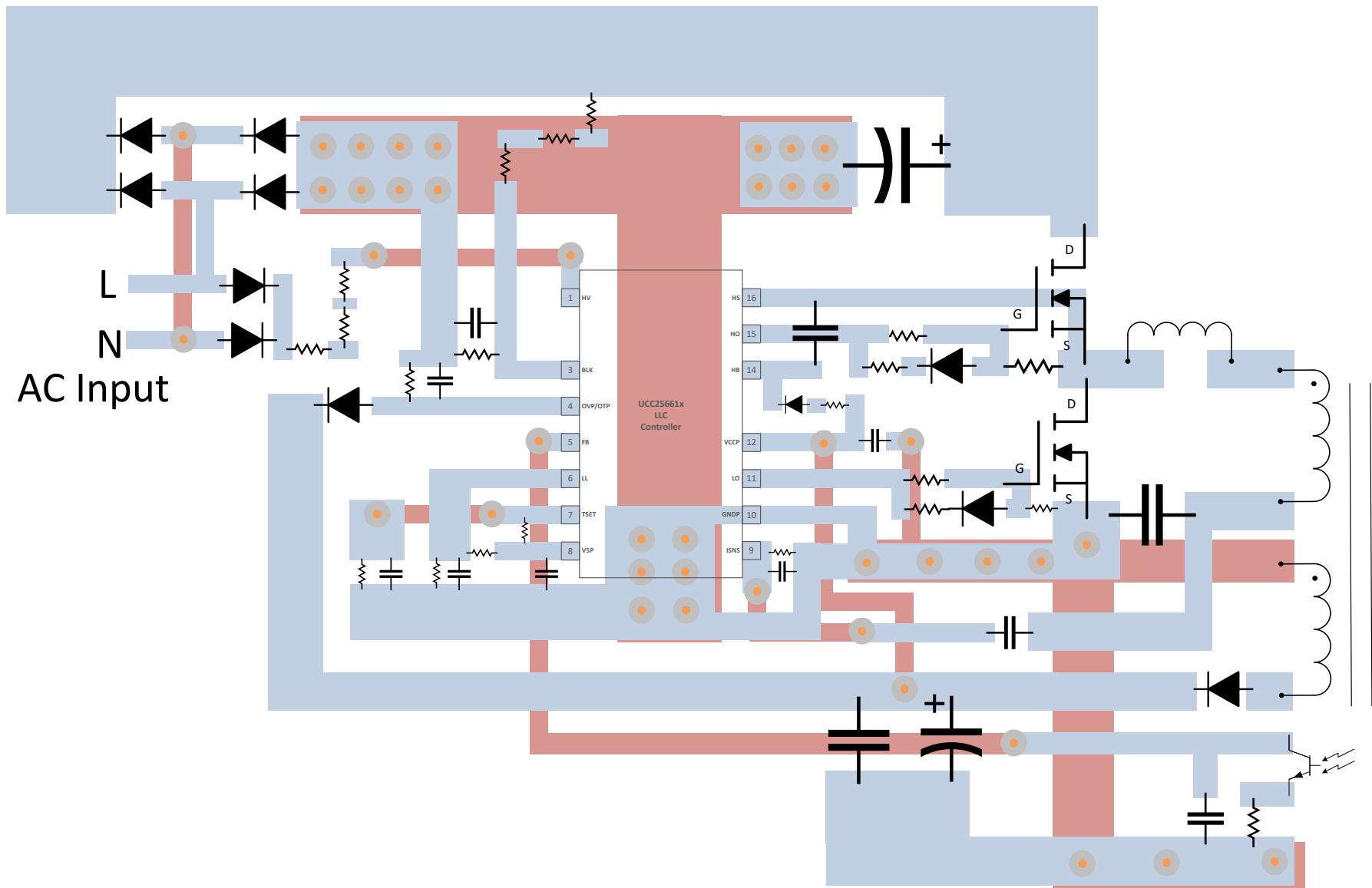

図 7-1. アプリケーション概略回路図

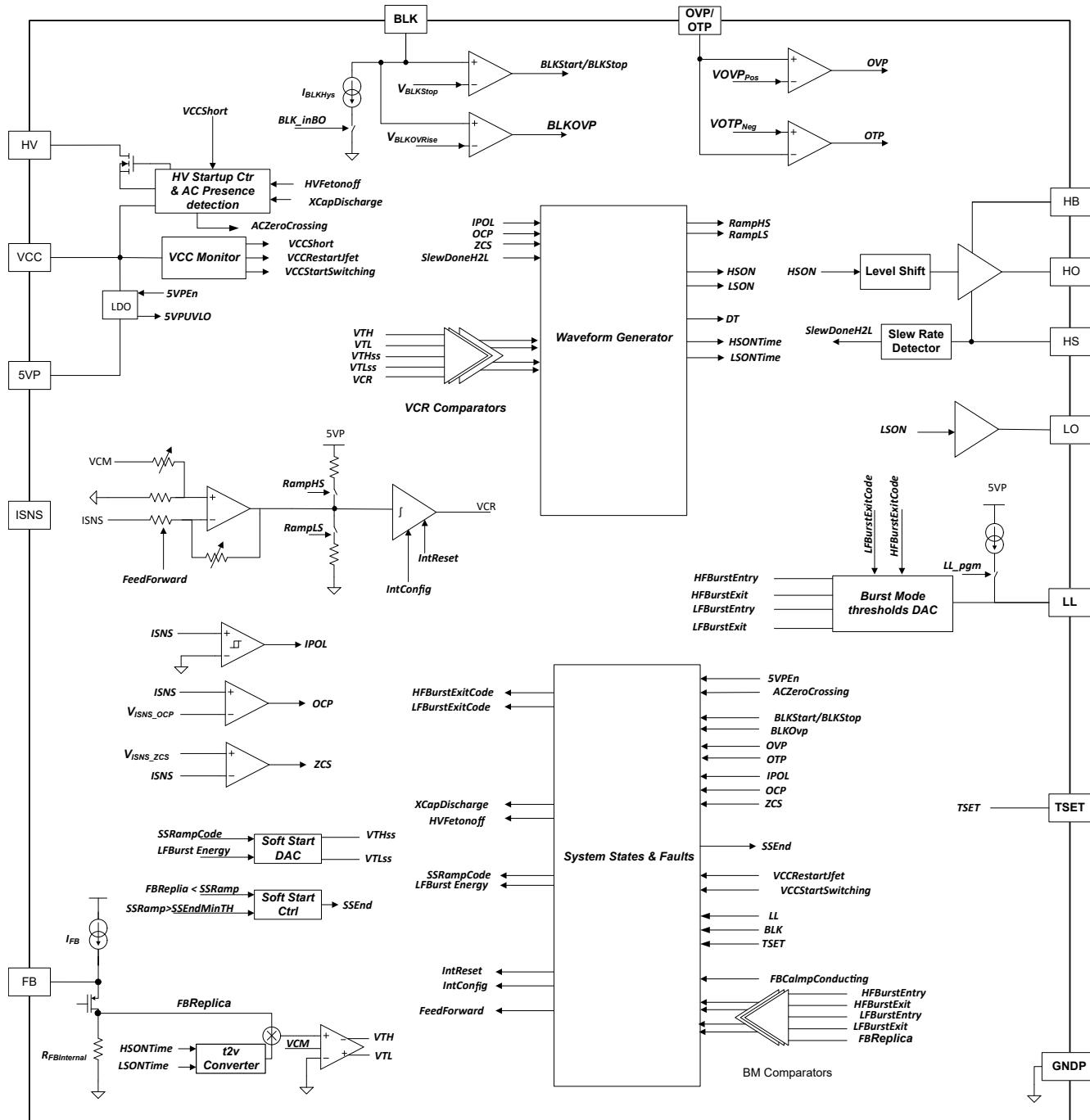

## 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 入力電力比例制御

TI の LLC コントローラは、ヒステリシス ハイブリッド制御 (HHC) と呼ばれるバージョンの充電制御を使用しています。UCC25661 LLC コントローラには、入力電力比例制御 (IPPC) と呼ばれる HHC の改良版が使用されています。制御信号がスイッチング周波数に比例する従来の直接周波数制御と比較すると、従来の電荷制御方式では過渡応答を高速化しながら、電力段の伝達関数が 1 次システムになるため補償回路設計が簡単になります。従来の充電制御では、制御信号は入力電流とスイッチング周波数の両方によって決定されます。IPPC は、制御信号がスイッチング周波数に依存することを大幅に低減し、入力と出力の電圧変動の影響を最小限に抑えることができます。

IPPC には次のような利点があります。

- 制御信号を入力電力に比例させる。

- 広い LLC (WLLC) 動作アプリケーションで一貫したバースト モードと全負荷性能。

- 高速な負荷過渡性能を維持し、ライン過渡特性を改善。

UCC25661 は、コンデンサ  $C_{ISNS}$  と抵抗  $R_{ISNS}$  からなる外付け微分器により ISNS ピンの共振タンク電流を測定します。ISNS ピンの電圧は VCR シンセサイザ ブロックに組み込まれ、内部 VCR 信号  $VCR_{synth}$  を形成します。VCR シンセサイザ ブロックは、BLK ピン電圧に基づいてフィード フォワード ゲインを適用し、ランプ補償を適用して、補償された内部 VCR 信号を生成します。次に、補償された内部 VCR 信号を 2 組のスレッショルドと比較し、ハイサイド スイッチのターンオフ ( $V_{TH}$ ) およびローサイド スイッチのターンオフ ( $V_{TL}$ ) を制御します。スレッショルド  $V_{TH}$  および  $V_{TL}$  は、内部制御信号 FBReplica と、前の半スイッチング サイクルからのハイサイドおよびローサイド スイッチのオン時間から生成されます。ソフトスタート中は、内部のソフトスタートランプに基づいて  $V_{TH}$  および  $V_{TL}$  スレッショルドが生成され、スタートアップ時の共振タンク突入電流を最小限に抑えます。

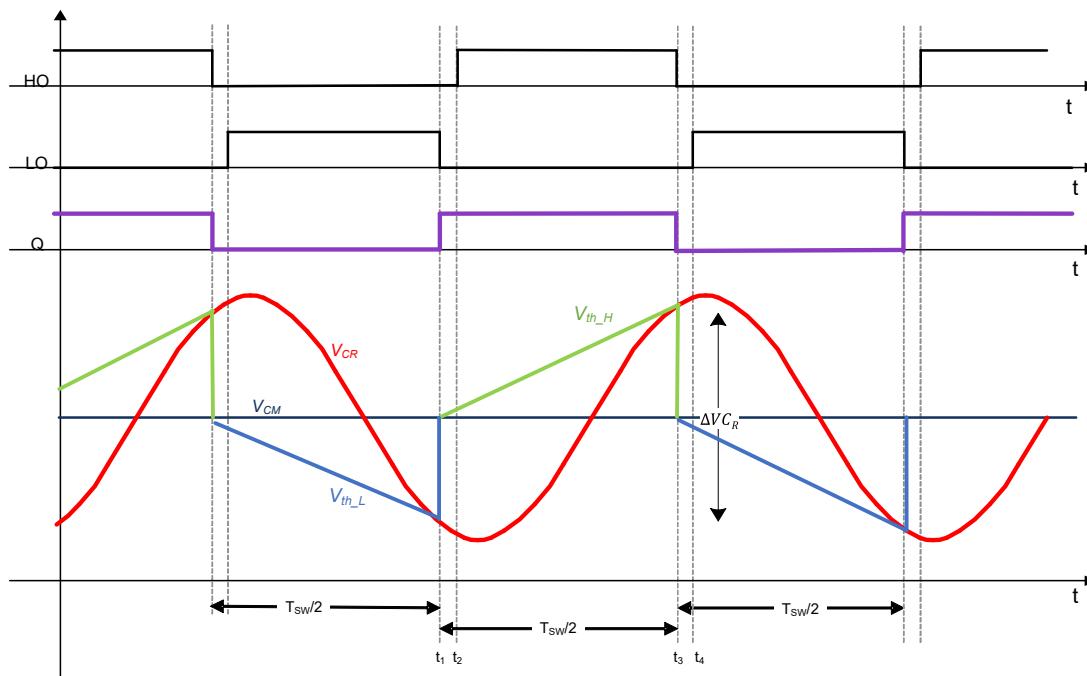

図 7-2 では、内部 VCR 信号とコンパレータ スレッショルド電圧  $V_{TH}$  および  $V_{TL}$  に基づいて、ハイサイドおよびローサイドのスイッチが制御されます。VCR が  $V_{TH}$  を上回ると、ハイサイド スイッチがオフになります。VCR が  $V_{TL}$  を下回ると、ローサイド スイッチはオフになります。

図 7-2. IPPC の基本波形

コンパレータのスレッショルド  $V_{TH}$  および  $V_{TL}$  は、以下の式で計算します。FBReplica は、フィードバックピン (FB) 電流の内部電圧表現です。セクション 7.3.3 は、フィードバック チェーンを定義します。 $t_{sw}$  はスイッチング サイクルの周期です。 $k$  は一定です。

$$V_{TH} = (V_{CM} + k \times \text{FBReplica} \times T_{sw} \div 2) \quad (1)$$

$$V_{TL} = (V_{CM} - k \times \text{FBReplica} \times T_{sw} \div 2) \quad (2)$$

$$V_{TH} - V_{TL} = \Delta V_{CR} = k \times \text{FBReplica} \times T_{sw} \quad (3)$$

### 7.3.1.1 電圧フィードフォワード

入力電圧フィード フォワードを実装すると、FBReplica は入力電力に比例し、共振タンク容量の大きさに反比例します。入力電圧フィードフォワードが適用されている状態で式 4 を書き換えます。

$$\text{FBReplica} = \frac{2}{C_r} \times K_1 \times P_{in,avg} + K_2 \times I_{RAMP} \quad (4)$$

ここで、 $K_1$  と  $K_2$  は内部シンセサイザのゲインです。LLC 電力段への入力電圧は、BLK ピンで定期的に検出されます。その後、この入力電圧に対して周期的な平均値を使用してフィード フォワード ゲインを調整し、制御信号が入力電力に比例するようにします。詳細については、セクション 7.3.2 を参照してください。

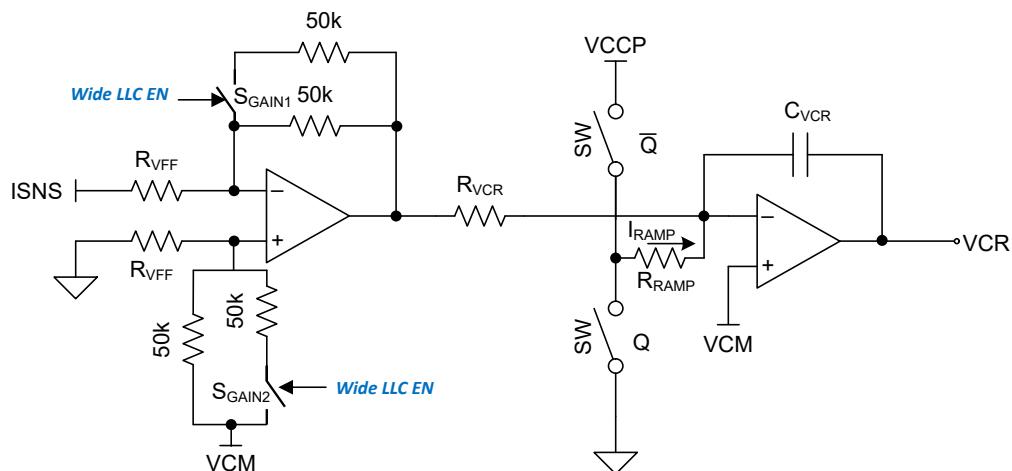

### 7.3.2 VCR シンセサイザ

UCC25661 には VCR シンセサイザが実装されており、共振タンク電流が内蔵されているため、共振容量電圧の内部表現が形成されます。VCR シンセサイザを内部に実装することで、UCC25661 は突入電流の制御とフィードフォワード ゲイン段により、超高周波のスタートアップをサポートします。内蔵の VCR シンセサイザにより、コントローラが ISNS 端子で拾った外部ノイズの影響を受けにくくなるため、コントローラはより堅牢になります。

図 7-3. VCR シンセサイザのブロック図

VCR シンセサイザの最初の段はプログラム可能なゲイン段で構成されており、入力電圧のフィード フォワード機能を実装するために使用されます。

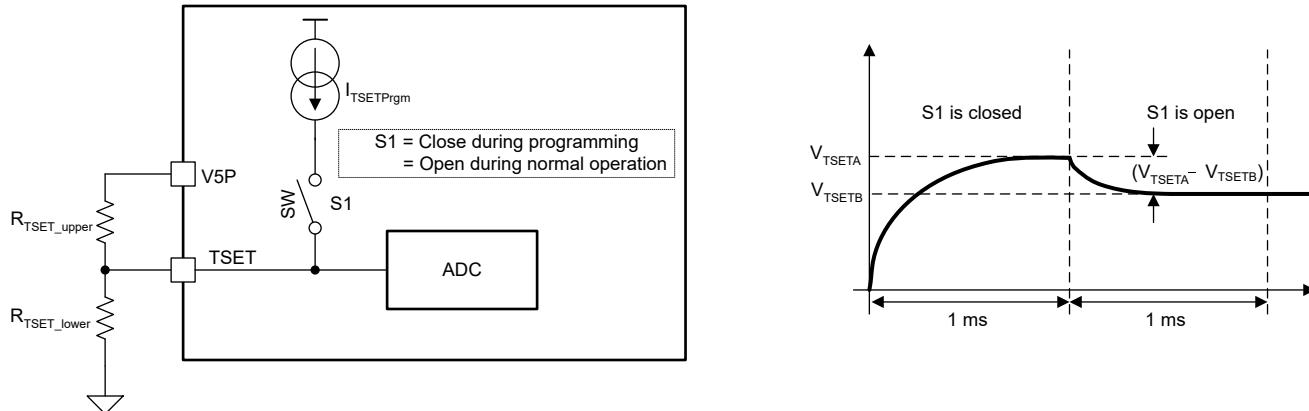

2 段目は、ランプ補償付きのプログラム可能な積分器で構成されます。広い周波数範囲の LLC 電力段に対応できるよう、TSET ピンを使用した設計の要求を満たすため、積分器の時定数はスタートアップ時に外部で設定可能です。起動時は、V5P と GNDP の間に接続された外付け分圧抵抗によって、TSET のプログラミングが行われます。外部分圧器のセンターノードを TSET ピンに接続します。プログラミング フェーズ中に、定電流  $I_{TSETPrgm}$  が TSET ピンに供給され、その結果として得られる電圧は ADC ( $V_{TSETA}$ ) によって測定されます。 $I_{TSETPrgm}$  がオフになってから、TSET 分圧抵抗の電圧 ( $V_{TSETB}$ ) が測定されます。

図 7-4. TSET ピンのプログラミング

### 7.3.2.1 TSET のプログラミング

VTSETB 電圧にプログラムされた電圧は、IPPC 動作の最小周波数とデッド タイムを設定します。VTSETA と VTSETB の差によって、与えられた電力出力に対して FBReplica 振幅を設定する積分器の時定数が設定され、過負荷電力 (OLP) と過電流保護 (OCP) スレッショルドを別々に設定できます。表で、TSET 電圧の値は公称値です。各 TSET 設定で使用可能な最大および最小範囲は、公称値から  $\pm 48\text{mV}$  以内です。

表 7-1. TSET プログラミング オプション

| TSET オプション番号     | 3.5V OCP の場合の TSET 電圧 (V) | IPPC 動作 (kHz) の最低周波数 | 積分器の時定数 (ns) | 最大デッドタイム (μs) |

|------------------|---------------------------|----------------------|--------------|---------------|

| 17               | 2.295                     | 698.6                | 68           | 0.5           |

| 16               | 2.168                     | 591.6                | 80           | 0.5           |

| 15               | 2.041                     | 501                  | 93           | 0.5           |

| 14               | 1.914                     | 424.3                | 112          | 0.5           |

| 13               | 1.787                     | 359.3                | 132          | 1             |

| 12               | 1.66                      | 304.3                | 156          | 1             |

| 11               | 1.533                     | 256.7                | 184          | 1             |

| 10               | 1.416                     | 218.2                | 214          | 1             |

| 9                | 1.299                     | 184.8                | 257          | 1             |

| 8                | 1.182                     | 156.5                | 304          | 1             |

| 7                | 1.074                     | 132.5                | 359          | 1             |

| 6                | 0.967                     | 112.2                | 424          | 1             |

| 5                | 0.850                     | 95                   | 490          | 1             |

| 4                | 0.742                     | 80.5                 | 588          | 1             |

| 3                | 0.644                     | 68.1                 | 694          | 1             |

| 2                | 0.547                     | 57.7                 | 820          | 1             |

| 1                | 0.450                     | 48.9                 | 968          | 1             |

| X <sup>(1)</sup> | < 0.392                   | —                    | X            | —             |

(1) 使用をお勧めしません。

### 7.3.3 帰還チェーン (制御入力)

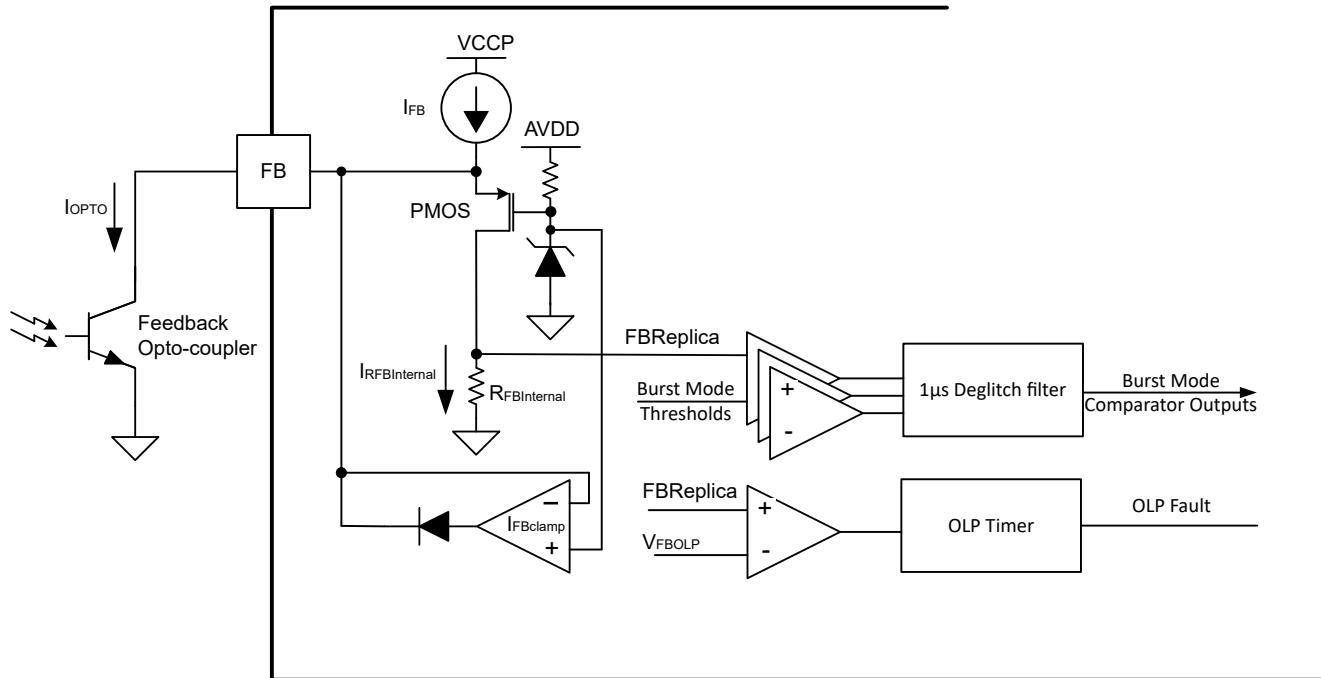

出力電圧の制御は、絶縁膜の 2 次側にある電圧レギュレータ回路により提供されます。2 次側レギュレータ回路からの要求信号は、フォトカプラーを使用して絶縁バリアを通過します。

定電流源  $I_{FB}$  が、VCCP 電圧から生成され、FB ピンに接続されます。抵抗器 RFB も PMOS と直列に定電流源に接続されます。通常動作中は、FB ピンの電圧がツェナー ダイオード基準電圧に PMOS のソース — ゲート間電圧降下を加えた値と等しくなるように、PMOS は常時オンになります。

図 7-5. 帰還信号経路 ブロック図

$$I_{FBInternal} = I_{FB} - I_{OPTO} \quad (5)$$

制御信号  $FBReplica$  は、式 6 を使用して表します。

$$FBReplica = I_{FBInternal} \times R_{FBInternal} \quad (6)$$

式 6 から、 $I_{OPTO}$  が増加すると、 $I_{FBInternal}$  が減少し、 $FBReplica$  が減少します。このように制御信号が反転します。 $I_{OPTO}$  が増加し続け、 $I_{FB}$  の値に達すると、PMOS を流れる電流が十分にないため、FB ピンの電圧は低下し始めます。FB ピンが low になると、フォトカプラの寄生コンデンサを充電して FB ピンの電圧をプルアップすることに起因する余分な遅延が発生し、システムの過渡応答に影響を及ぼします。FB ピンの電圧クランプ回路を使用して、この状況を防止します。FB ピンの電圧が FB ピンのクランプ電圧レッショルドを下回ると、追加の電流源がオンになり、FB の電圧をクランプします。クランプの強度は  $I_{FBclamp}$  です。FB ピンクランプ回路により、軽負荷から重負荷までのシステム過渡性能が向上します。FB ピンのクランプ動作を下図に示します。

図 7-6. FB ピン電圧と FB ピン電流との関係

#### 7.3.4 アダプティブ デッドタイム

UCC25661 には、ハイサイド パルスとローサイド パルス間のデッド タイムを最適化するため、高速な低レイテンシ スルーレート検出ブロックが実装されています。アダプティブ デッド タイム ブロックは、貫通電流および過剰なボディ ダイオード導通を防止するためにデッド タイムを調整します。

アダプティブ デッド タイム ブロックのコアには、最大 200V/ns のスルーレートを検出できるスルーレート検出器ブロックがあり、UCC25661 は高周波共振コンバータでの使用に最適です。

バースト モードでは、ZCS 防止動作中、またはスルーレートが低速になる可能性のある電力段で、共振タンクの電流極性信号 (極性コンパレータ出力) を使用してスルーレート検出器を強化します。

LLC の自然な対称動作を利用することで、スルーレート検出器によって決定されるのは、ハイサイド スイッチのオフとローサイド スイッチのオン間のデッド タイムのみです。このデッド タイムはコピーされ、ローサイド MOSFET のターン オフとハイサイド MOSFET のターン オン間のデッド タイムに適用されます。デッド タイムがコピーされないいくつかの例外があります。条件は以下のとおりです。

- 直前の *High* から *Low* への遷移でスルーレート検出器信号が見つからない場合。

- 前のサイクルでの ZCS 検出。

上記の条件では、ISNS 信号に基づく *Ipolarity* コンパレータを使用して、*low* から *high* への遷移中のデッド タイムを調整します。

#### 7.3.5 入力電圧検出

BLK ピンによる入力電圧検出を使用して、以下に示す複数の機能を実装します。

- 入力電圧のブラウンインおよびブラウンアウト

- 入力フィードフォワード (セクション 7.3.1 で説明)

- 入力電圧 OVP

##### 7.3.5.1 ブラウンインおよびブラウンアウトのスレッショルドとオプション

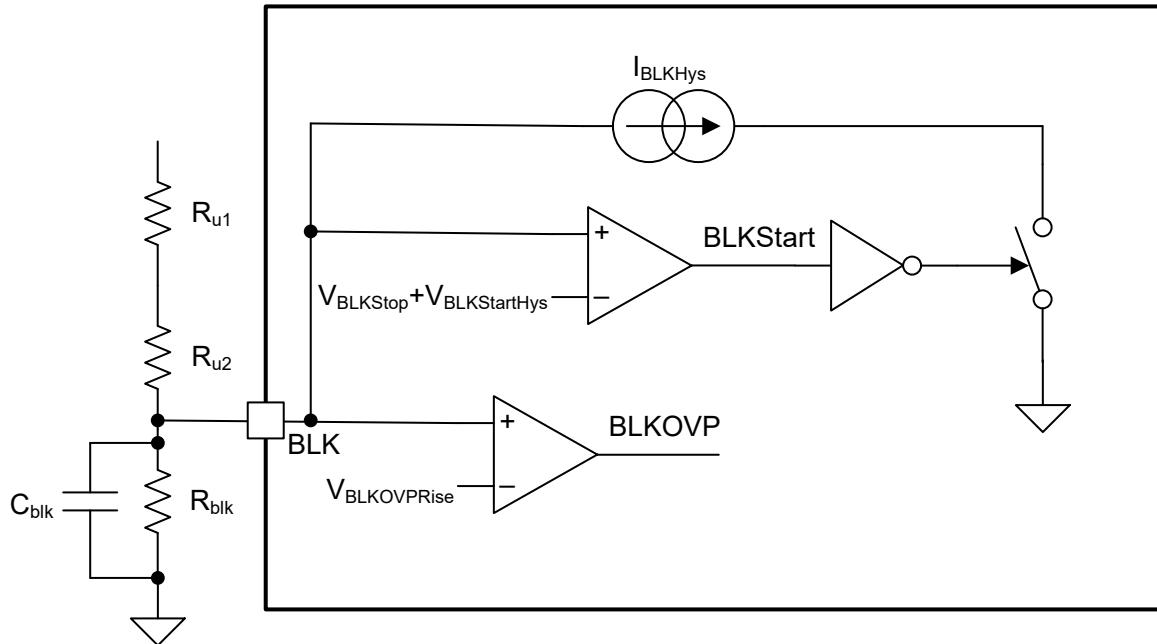

UCC25661 は、ブラウンアウトおよびブラウンアウトのスレッショルドをプログラム可能です。BLK ピンの電圧が V<sub>BLKStop</sub> を下回ると、コントローラはブラウンアウト状態に移行し、スイッチングを停止します。ブラウンアウト状態では、追加の電流

シンクがオンになり、BLK ピンから  $I_{BLKHys}$  を引きます。ピンに外部接続された等価抵抗を変更して、実際のブラウンイン電圧を設定します。

図 7-7. BLK ピンの入力電圧検出アーキテクチャ

ブラウンアウトが検出されると、コントローラはスイッチングを停止します。BLK 電圧がブラウンイン電圧を上回ると、コントローラはすぐにソフトスタートを開始し、フォルトのアイドル時間を待ちません。

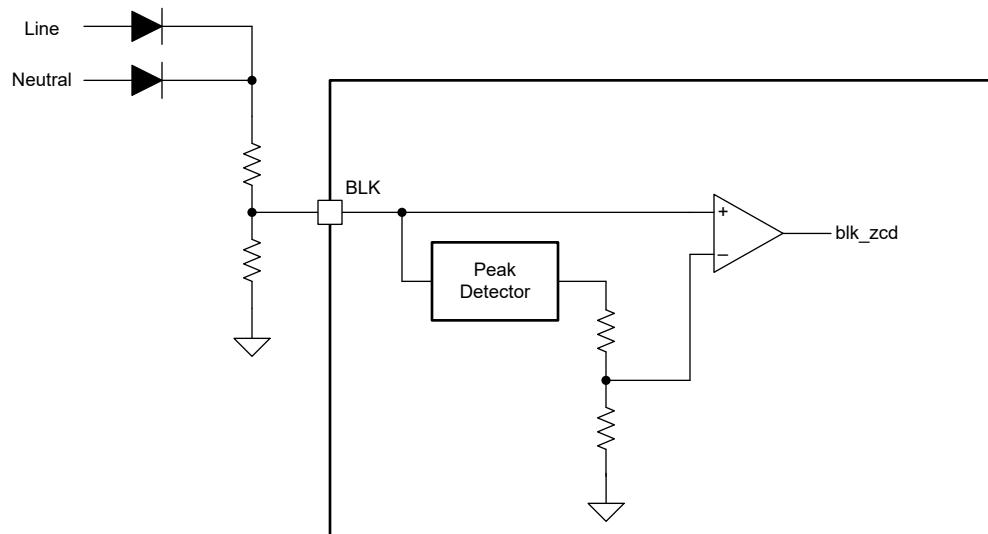

### 7.3.5.2 AC 入力のゼロ交差検出

入力ゼロ交差検出は、BLK ピン検出用に AC ブラウンアウト オプションが選択されている場合のみイネーブルになります。この方法では、BLK ピンで分圧抵抗回路によって HV ピン電圧が検出されます。期待される波形は、分割した整流 AC 電圧です。70Vac 入力および 265Vac 入力時の BLK 抵抗デバイダに対して  $8\text{M}\Omega$  と  $100\text{k}\Omega$  を使用する例を示します。

図 7-8. BLK ピンを使用した入力 AC ゼロ交差検出

AC 存在を判定するには、瞬時 BLK 電圧と BLK ピーク検出器出力の  $\frac{1}{2}$  を調べるコンパレータを使用します。瞬間的な BLK 電圧がピーク BLK 電圧の  $\frac{1}{2}$  を下回り、その後、 $\frac{1}{2}$  BLK ピーク電圧を(ヒステリシス付きで)上回ると、AC 存在が検出されます。X コンデンサ放電アルゴリズムは実質的に、AC の有無を検出するために、BLK コンパレータ出力の立ち上がりエッジ (blk\_zcd) を探します。

図 7-9. BLK ZCD 検出のブロック図

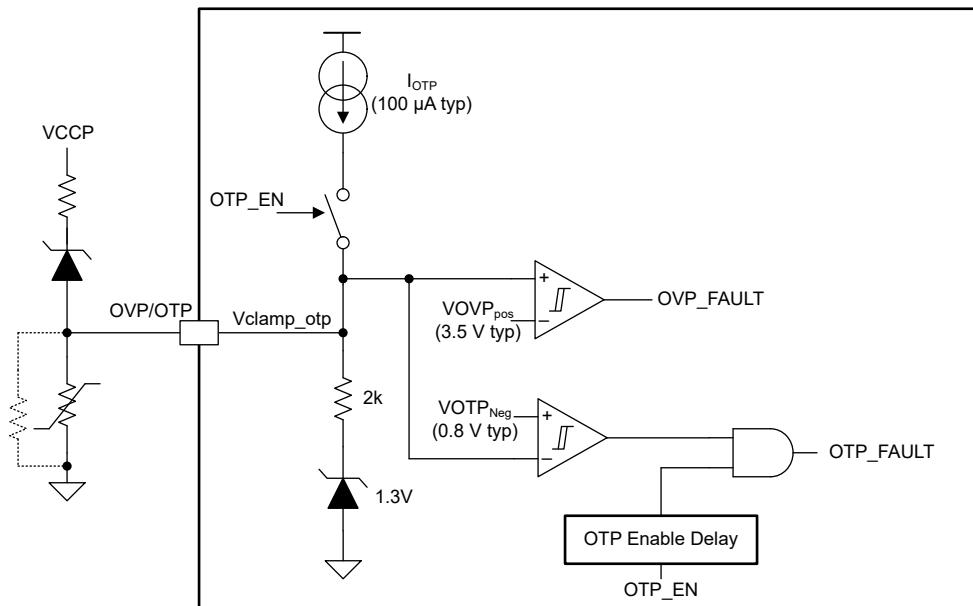

### 7.3.5.3 出力 OVP および外部 OTP

UCC25661 はマルチファンクション ピン (OVP/OTP) を備えており、出力過電圧と外部過熱状態を監視します。出力電圧はバイアス巻線および電源電圧 VCCP に反映される電圧によって監視されます。

VCCP と OVP/OTP ピンの間にツェナー ダイオードを接続します。通常の動作条件では、ツェナーは導通せず、OVP/OTP ピンの電圧は NTC 抵抗と  $I_{OTP}$  のソース電流の結果となります。VCCP がツェナー ブレークダウン電圧を超えるのに十分な大きさになった場合、ツェナー電流により OVP/OTP ピンの電圧が high になります。OVP/OTP の電圧が  $VOVP_{pos}$  スレッショルドを 40us 上回ると、コントローラは障害を検出し、スイッチングを停止します。

図 7-10. OVP/OTP 保護アーキテクチャ

NTC は OVP/OTP から GNDP に接続します。内部の電流源  $I_{OTP}$  は、OVP/OTP ピンから流れ出し、NTC 抵抗に流れます。NTC の温度に基づいて、外部過熱フォルトが発生したかどうかを判断するために、ピンの結果として得られた電圧が  $VOTP_{Neg}$  と比較されます。外部過熱保護が検出されると、UCC25661 はフォルト状態に移行します。1 秒の待機時間後に、UCC25661 は OVP/OTP ピンの電圧を確認します。OVP/OTP ピンの電圧が  $VOVP_{Pos}$  よりも高い場合、UCC25661 は再起動を試みます。再起動できない場合、UCC25661 はフォルトアイドル状態で継続して待機します。バースト モード中は、静止電流を最小化するため、過熱保護機能が無効化されます。バースト モードから通常スイッチングに遷移するとき、OTP 機能が再度イネーブルされます。

### 7.3.6 共振タンク電流検出

ISNS ピンは微分器により共振タンク電流を検知します。過電流保護ピンとしてだけでなく、ISNS ピンも制御機能の重要な部分です。

ISNS ピンの機能は次のとおりです

- 制御電圧を発生させ、IPPC 制御に使用する積分器への入力

- OCP (サイクル単位) 保護

- 共振電流極性検出

- ZCS (ゼロ電流スイッチング) 防止とデッドタイム管理

- 起動時の逆回復回避

## 7.4 保護

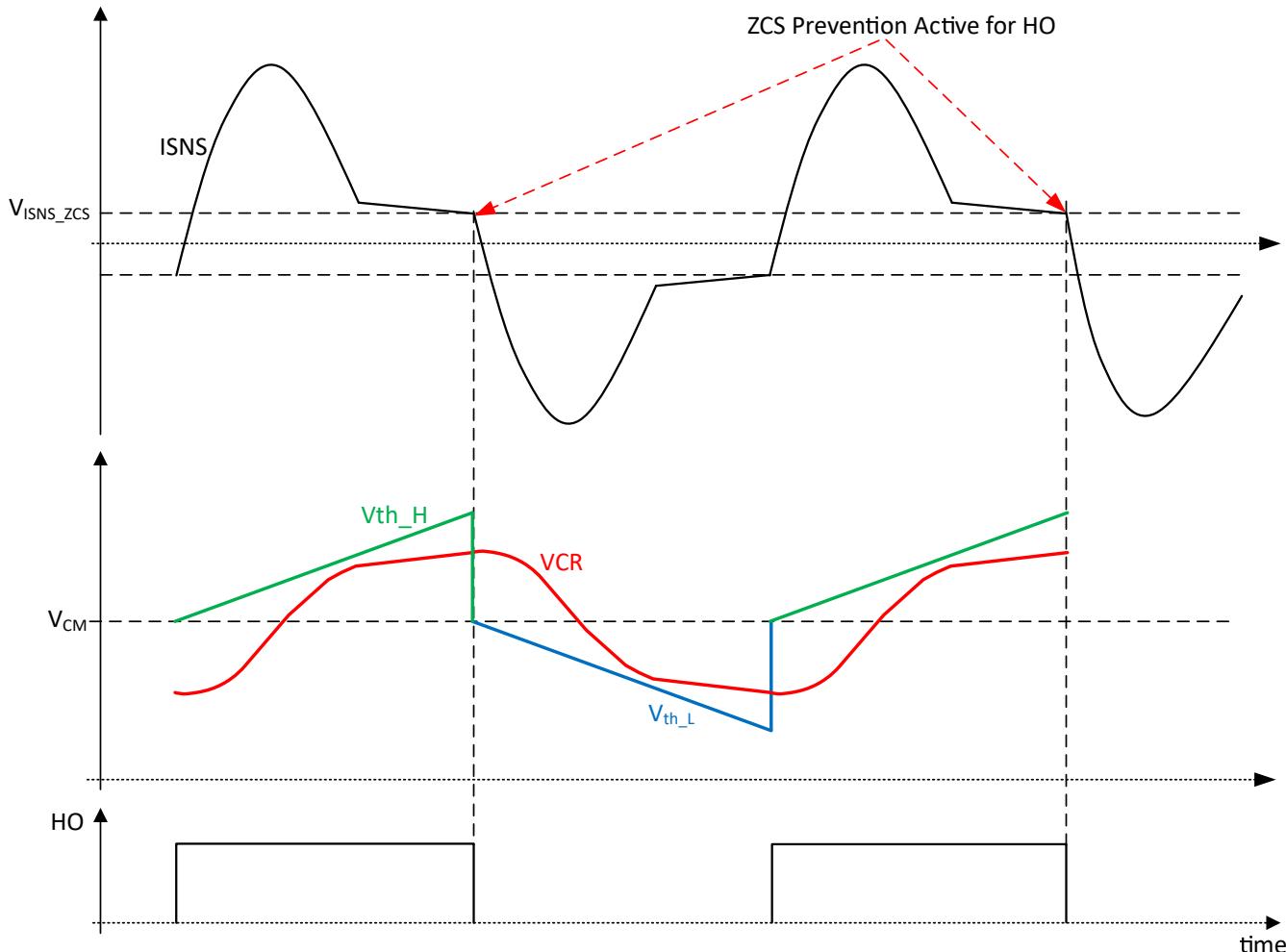

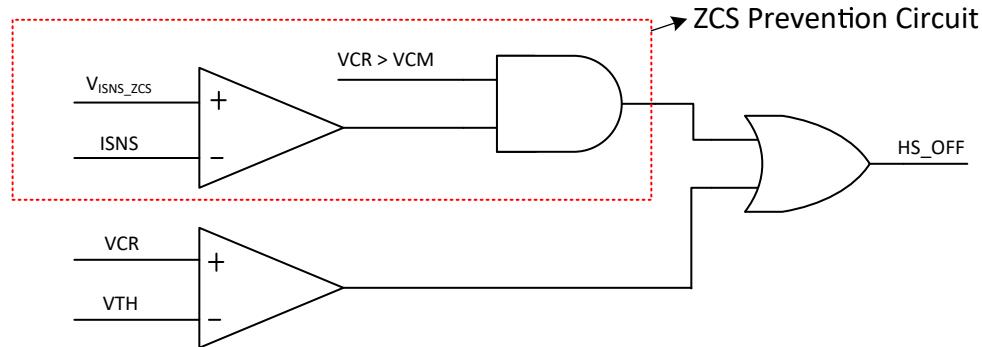

### 7.4.1 ゼロ電流スイッチング (ZCS) 保護

ZCS 保護は、LLC コンバータが容量性動作領域に上回らないようにするために必要な機能です。容量性領域では、ボディダイオードの逆回復により、両方のスイッチに短時間電流が流れたために MOSFET が損傷する可能性があります。さらに、ゲインと周波数の関係は容量性領域で反転し、コンバータが電力段のレギュレーションを完全に失う可能性があります。ZCS 保護の目標は、電流が反転する前に MOSFET を確実にオフにできるようにすることで、MOSFET のボディダイオードがハード逆回復する可能性をなくすことです。これにより、出力段の信頼性が向上します。最小ターンオフ電流はスレッショルドに設定されます。これにより、この状況でのスイッチに対する ZVS または ZVS スイッチングの可能性が高くなります。デッドタイムエンジンを組み合わせると、スルー完了信号と IPOL 信号の両方を考慮しているため、 $V_{DS}$  電圧のバレーポイントで逆方向の MOSFET が確実にオンになり、スイッチング損失を最小限にお会えるようになります。

図 7-11. ZCS 保護

誘導性/容量性の境界で動作が成立しない場合は、ゲートがオフになる前に共振電流が減少します。 $ISNS$  波形が  $V_{ISNS\_ZCS}$  スレッショルドよりも低い場合、 $VCR$  波形が  $V_{TH}$  境界を超えるのを待たず、ゲートパルス  $HO$  は早期終了します。この早期のゲート終端方法では、ゲートターンオフエッジで十分な共振電流を残して、デッドタイム中に ZVS 遷移を駆動できます。 $LO$  ゲートパルスについても同様の説明が有効です。

図 7-12. ハイサイド MOSFET がオンのときの ZCS 防止方式

共振周波数よりも共振電流の形状が十分低い場合、共振電流波形の正しい立ち下がりエッジを検出するにはいくつかの課題が生じます。UCC25661 には、ISNS 信号の正しい立ち下がりエッジを確実に検出して、誤トリップを防止するため、追加のロジックが実装されています。ノイズに対する堅牢性を高めるため、HO または LO ゲートの立ち上がりエッジで ISNS ZCS コンパレータがブランкиングされます。VCR コンパレータと ISNS ZCS コンパレータの両方で、同じブランкиング時間  $tleb$  が使用されます。ZCS イベントが検出されると、内部ソフトスタートランプ電圧がゆっくりと低下します。内部ソフトスタートが下降すると、スイッチング周波数も強制的に上昇し、コンバータの容量性領域から強制的に逸脱します。TZCSFault が一定時間持続した ZCS 条件が発生した場合、UCC25661 コントローラはスイッチングを停止し、フォルト状態に移行します。

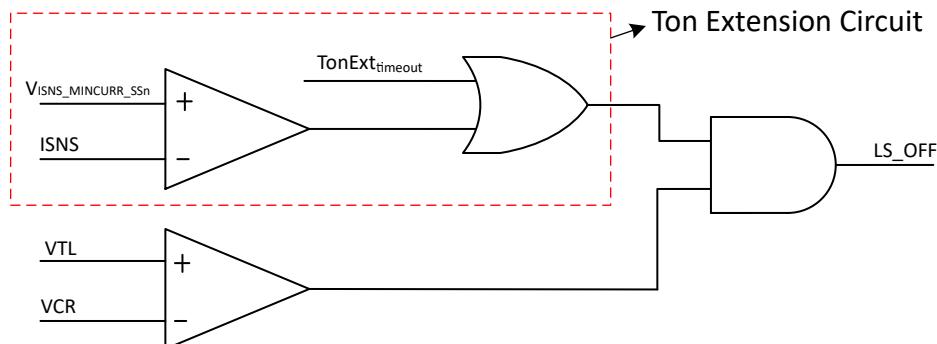

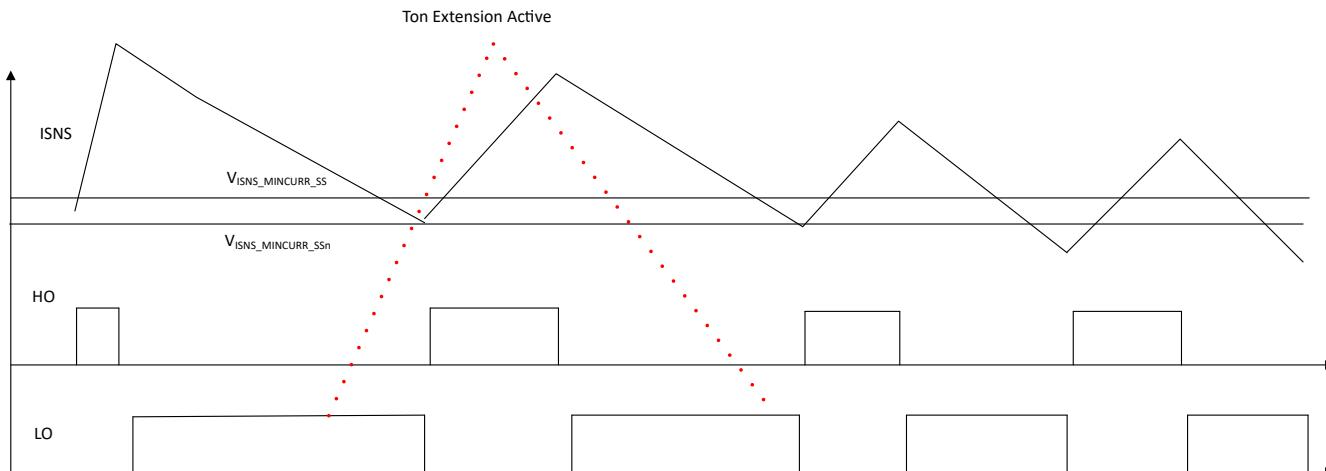

#### 7.4.2 ソフトスタート中の最小電流ターンオフ

起動時および 1 次側の最初の MOSFET 数スイッチングサイクルでは、ボディダイオードの逆回復とハードスイッチングが行われることがあります。この経験は主に、起動時に、 $V_{in}/2$  の定常状態動作電圧から共振コンデンサが DC バイアス電圧を生じる可能性があることによるものです。これにより、起動時の共振タンク電流が非対称になります。最初の数サイクルでは、非対称性が十分に高く、スイッチターンオフの時点の電流が逆極性になることがあります。

その例については、図 7-13 を参照してください。

図 7-13. Ton 拡張方式

図 7-14. 起動時の ZCS 防止

#### 7.4.3 サイクル単位の電流制限と短絡保護

UCC25661 ファミリの OCP およびサイクル単位の電流制限機能は、短絡に対して高速 (50ns 未満) 応答を実現しています。サイクル単位の保護機能は、電力段のピーク ストレスを制限するのに役立ちます。ISNS 電圧が  $V_{ISNS\_OCP}$  を上回ると、現在の HO ゲート パルスは終了します。それに応じて、後半サイクルで、対応する過電流制限が検出されると、現在の LO パルスが終了します。7 回のスイッチング サイクル ( $n_{OCP}$ ) 連続での状態で OCP が検出されると、デバイスはフォルト状態に移行します。50 回のスタートアップ中、連続スイッチング サイクルの ( $n_{OCP\_ss}$ ) で OCP 状態が検出されると、デバイスはフォルト状態に移行します。

#### 7.4.4 過負荷 (OLP) 保護

フィード フォワードを備えた IPPC は、Pout と内部制御信号 FBReplica の間に密接な相関関係を得ます。

FBReplica が  $V_{FBOLP}$  を上回ると (すなわち、 $I_{opto}$  が  $0\mu A$  に低下すると)、システムは入力電力の制限を開始し、OLP タイマ カウントが増加します。FBReplica が ( $T_{OLP}$ ) を上回る間  $V_{FBOLP}$  を上回ると、OLP フォルトが検出され、システムはフォルト再起動シーケンスに移行します。

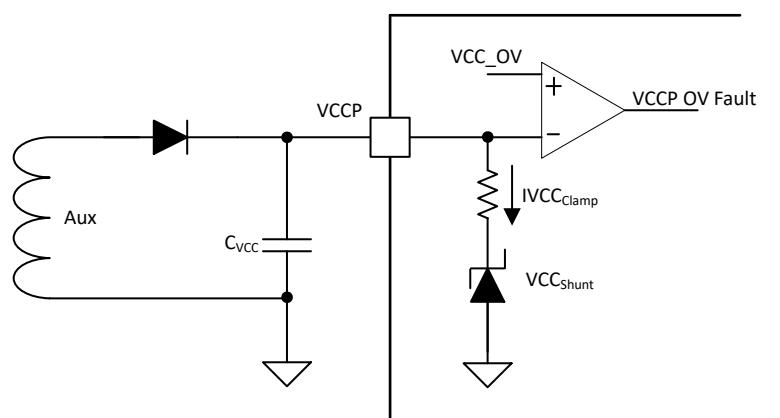

#### 7.4.5 VCC OVP 保護

VCCP ピンの内部電流制限クランプにより、VCCP ピンを保護し、VCCP ピンに印加される電圧が推奨最大電圧を超えると、ゲート駆動出力電圧をクランプします。クランプには最大シンク電流  $IVCC_{Clamp}$  があります。VCCShunt を流れる電流が  $IVCC_{Clamp}$  を超えると、VCCP ピンの電圧が VCC\_OV を超えてさらに上昇します。上昇する場合、UCC25661 はフォルト状態に移行し、1 秒のフォルトアイドル時間後に再試行します。

図 7-15. VCC クランプ

## 7.5 デバイスの機能モード

### 7.5.1 スタートアップ

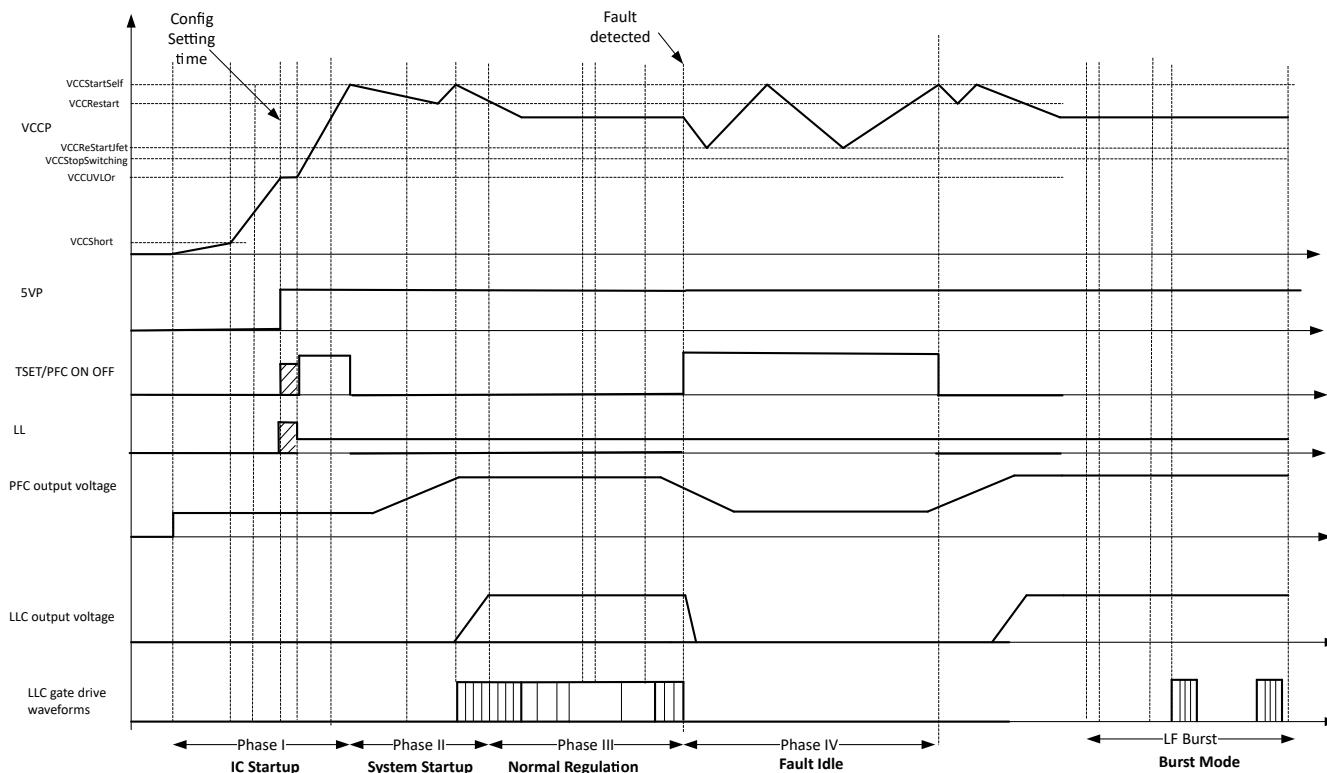

#### 7.5.1.1 HV スタートアップ内蔵

##### 7.5.1.1.1 最初の起動シーケンス

1. AC プラグを差し込むと、HV ピンに電圧が印加されます。VCCP 電圧が  $VCC_{Short}$  を下回ると、VCCP ピンは  $I_{VCC\_Charge\_Low}$  で充電されます。VCCP 電圧が  $VCC_{Short}$  より高い場合は、VCCP ピンが  $I_{VCC\_Charge\_High}$  で充電されます。

2. VCCP 電圧が  $VCC_{UVLor}$  を上回ると、デバイスの初期化が完了するまで、内部 LDO が V5P 電圧をレギュレートします。

3. V5P が確立されます。LL ピンと TSET ピンは、バーストモードと内部 VCR シンセサイザのプログラミングに使用します。

4. HV スタートアップオプションがイネーブルの場合、VCCP が完全に確立される前に PFC がオンになるのを防ぐため、TSET ピンは high (PFC オフを意味します) を出力します。

5. VCCP が  $VCC_{StartSelf}$  を上回ると、HV 充電電流は停止します。LLC のスタートアッププロセスが開始されます。TSET 電圧は 1V 未満に維持され、PFC が起動することができます。

6. ステージ 3 と 4 の間に、VCCP 電圧が  $VCC_{ReStartJfet}$  を下回ると、HV 充電電流が再度イネーブルになり、VCCP は  $I_{VCC\_Charge\_High}$  で充電されます。

7. LLC の起動が完了すると、VCCP が  $VCC_{ReStartJfet}$  を下回るまでの間、HV 充電電流はディスエーブルになります。

8. 通常動作中に、VCCP 電圧が  $VCC_{StopSwitching}$  を下回ると、異常が発生し、UCC25661 はシャットダウンします。その後、通常の再起動シーケンスが実行されます。

図 7-16. 「HV スタートアップ」機能の起動シーケンスを有効化

### 7.5.1.1.2 シーケンスを再起動します

- 異常が検出されると、UCC25661 はシャットダウンします。フルトライモードの場合、1秒間のアイドル時間の後、UCC25661 は再試行します (VCCP が  $VCC_{UVLOf}$  を上回っているとき、TSET 出力は high)。

- VCCP 電圧が  $VCC_{Short}$  を下回ると、VCCP ピンは  $I_{VCC\_Charge\_Low}$  で充電されます。VCCP 電圧が  $VCC_{Short}$  より高い場合は、VCCP ピンが  $I_{VCC\_Charge\_High}$  で充電されます。VCCP ピンの電圧が  $VCC_{StartSelf}$  より高い場合、HV 起動はイネーブルではありません (位相 I がスキップされます)。V5P が確立され、バーストモード設定用に LL ピンが解放されます。

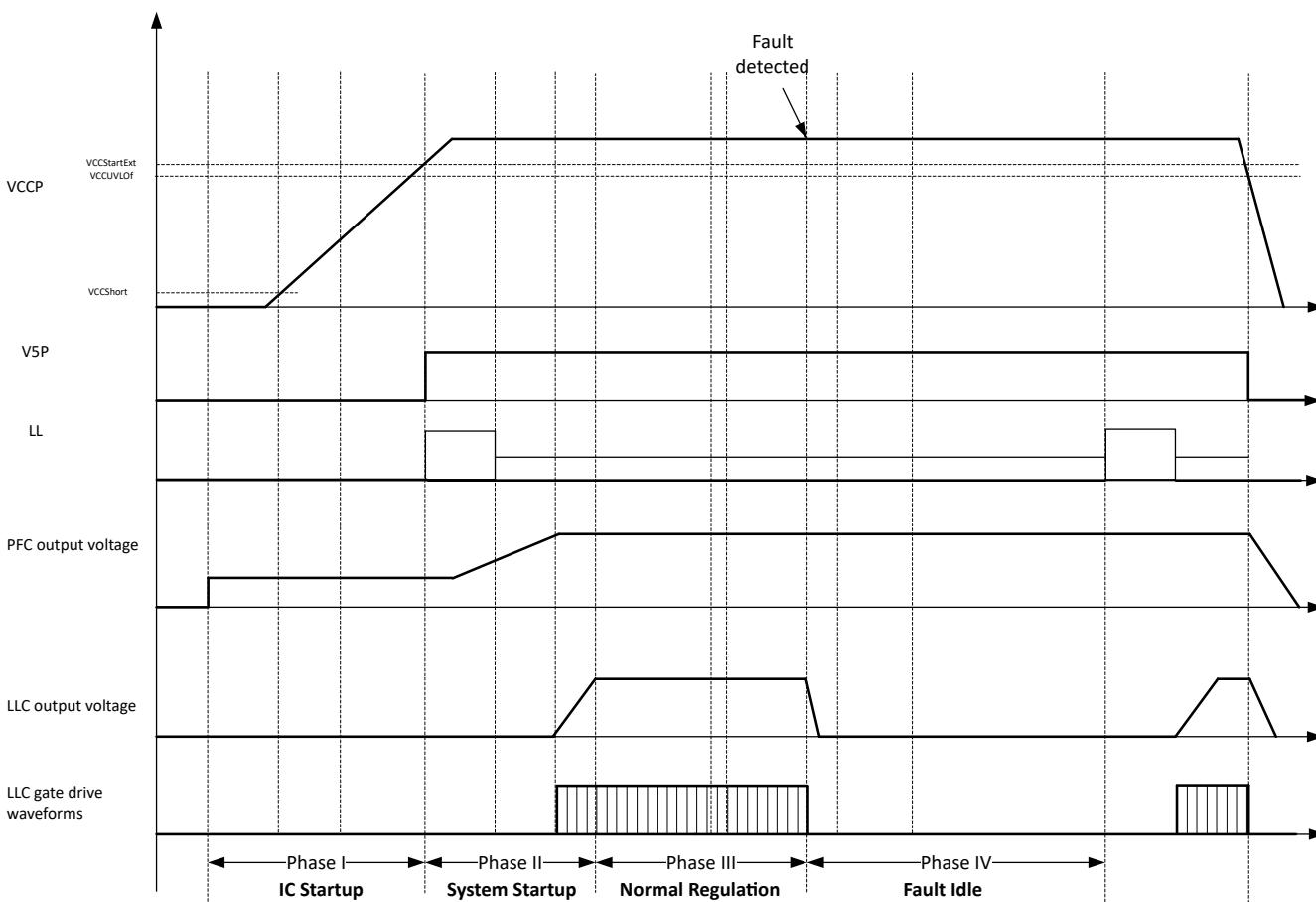

### 7.5.1.2 HV スタートアップなし

HV スタートアップが無効になると、PFC オン/オフ信号も無効化されます。スタートアップシーケンスは、次のとおりです。

- VCCP 電圧が  $VCC_{UVLOf}$  を上回ると、V5P が確立されます。

- LL ピンと TSET ピンは、バーストモードおよび内部 VCR 積分器の設定に使用されます。

- VCC が  $VCC_{UVLOf}$  を下回ると、V5P はオフになり、システムはシャットダウンされます。

図 7-17. 「HV スタートアップ」機能の起動シーケンスを無効にしました

### 7.5.2 ソフトスタートランプ

ソフトスタートランプは、UCC25661 に内蔵されています。内部で 25ms の固定最大ソフトスタート時間が生成されるため、出力電圧の高速上昇を可能にしながら、スタートアップ時の突入電流を低減します。

### 7.5.2.1 スタートアップからレギュレーションへの遷移

UCC25661 には、新しいソフトスタートが実装されているため、スタートアップ時の突入電流を制御できます。この新しい方式により、早期のソフトスタートの終了を回避でき、ソフトスタートと閉ループ レギュレーションとの間をスムーズな遷移を確率するのに役立ちます。

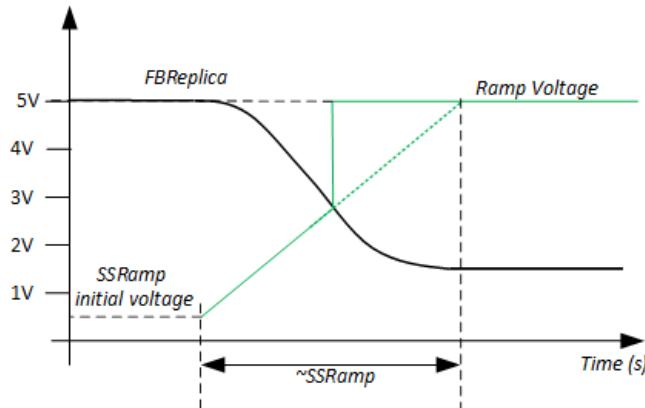

スタートアップ時に、定義されたスロープを使用して内部ソフトスタート電圧 (**SSRamp**) が上昇し、**FBReplica** は出力電圧がレギュレーション電圧を下回っていることから **high** になります。ピックの下型ブロックはこれら 2 つの信号を識別し、より小さい方の信号を使用して、電力段スイッチのターンオフを制御します。

ソフトスタートは、**SSRamp** が最小スレッショルドを上回った後にのみ終了し、図 7-18 に示すように、早期のソフトスタート終了を回避します。

図 7-18. ソフトスタート動作

### 7.5.3 軽負荷効率の管理

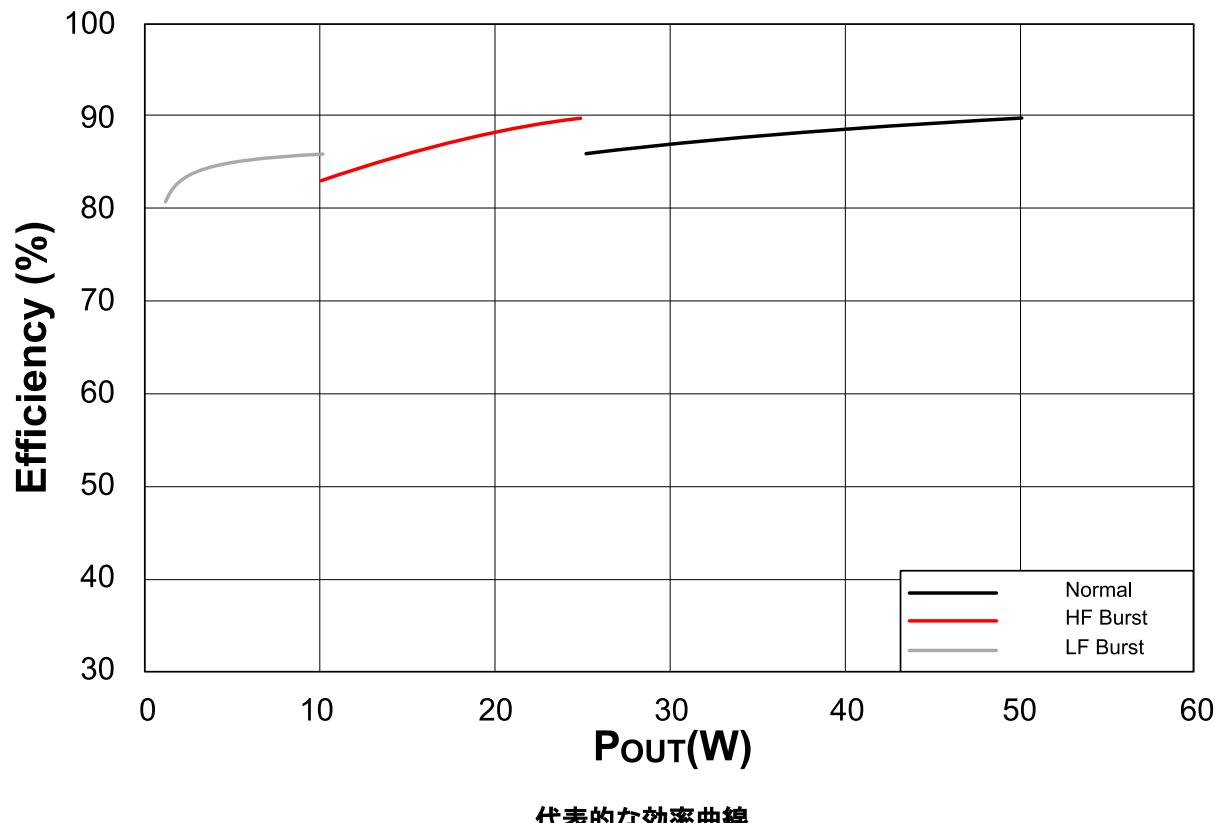

#### 7.5.3.1 動作モード (バーストパターン)

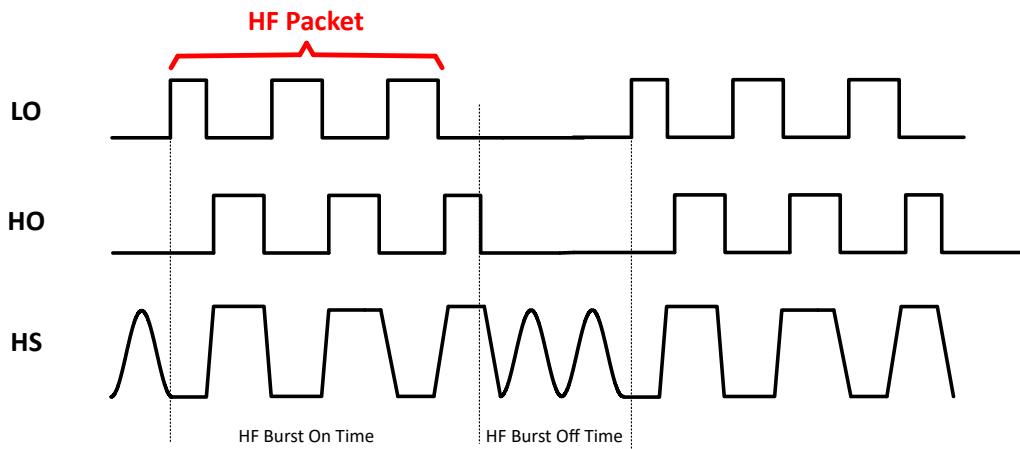

UCC25661 バーストモードアルゴリズムは、可聴ノイズを最小限に抑えながら、軽負荷時の効率を向上させます。これは、バーストパケットの周波数を可聴範囲を上回る (25kHz 超) ように維持するか、またはバーストパケットの周波数を可聴領域の非常に低い端 (400Hz 未満) に維持することで実現されます。UCC25661 は 2 つのバーストモードパターンである、高周波 (HF) パルススキップと低周波数 (LF) バーストを採用しています。

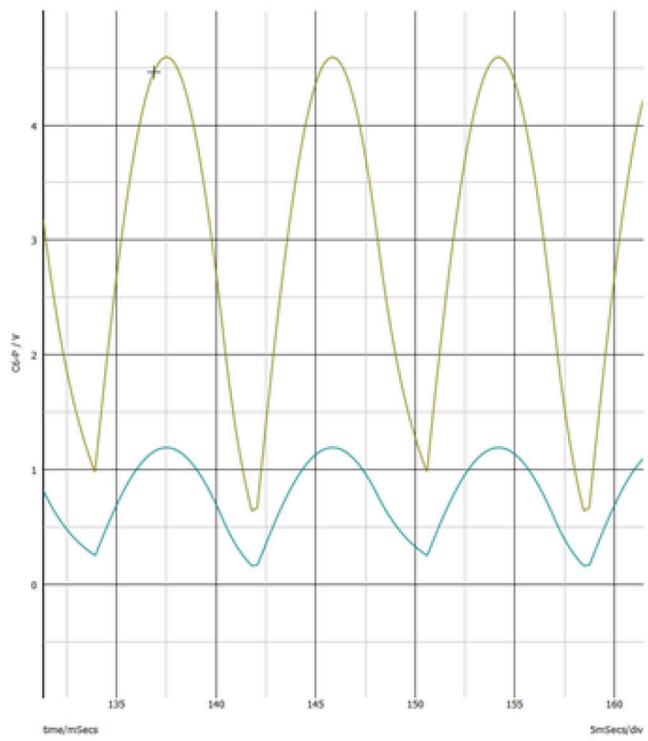

HF バーストパケットには、固定数の LO および HO パルスが含まれます。HF バーストの目的は、バースト周波数を可聴周波数範囲よりも高く維持することです。下の図では、スイッチノードの 2 番目のバーでローサイドゲートがイネーブルになり、次の HF バーストパケットの配信を開始します。

図 7-19. 高周波数パルススキップパケット

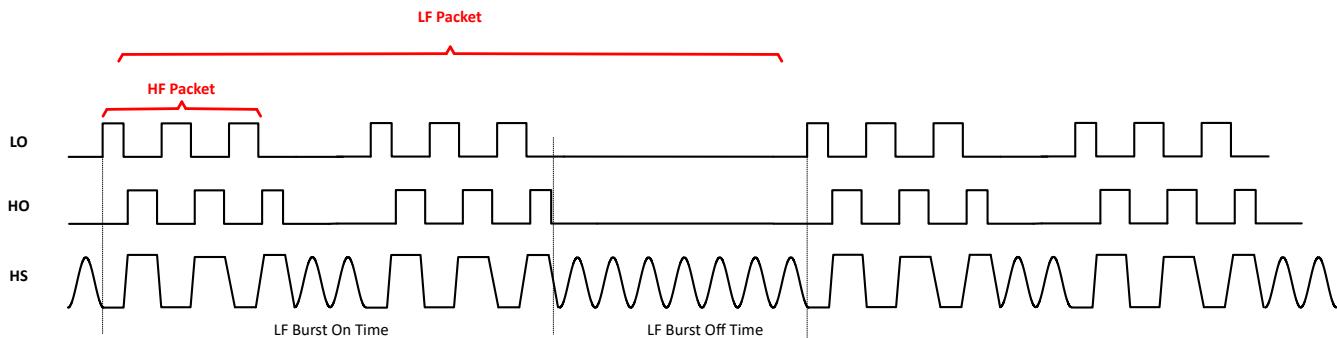

LF バーストには、多数の HF バーストパケットと LF バーストオフ期間が含まれます。

図 7-20. 低周波数のバースト パケット

LF バースト周波数を周波数範囲内に維持するために、HF バーストパケットの数が計算されます。目標周波数範囲のセットを内部的に用意しており、デフォルトオプションは、200Hz 付近で LF バーストを制御することです。

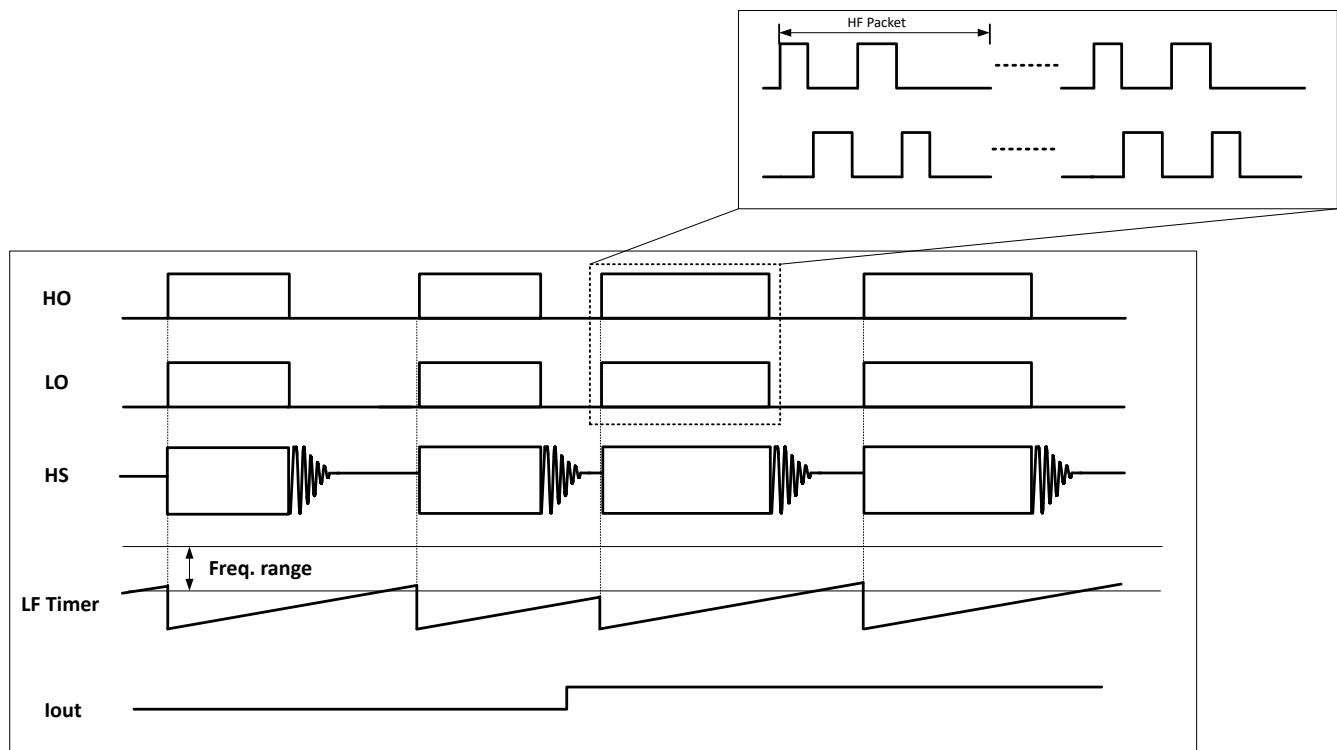

図 7-21. LF バースト内のパケット サイズ レギュレーション

### 7.5.3.2 モード遷移の管理

LL ピンを使用して、UCC25661 が HF パルススキップおよび LF バーストモードに移行する電力レベルを設定できます。設定可能な 2 つのスレッショルドは、*HFBurstEntry* と *LFBurstEntry* です。電力レベルの構成方法の詳細については、[セクション 7.5.3.3](#) を参照してください。

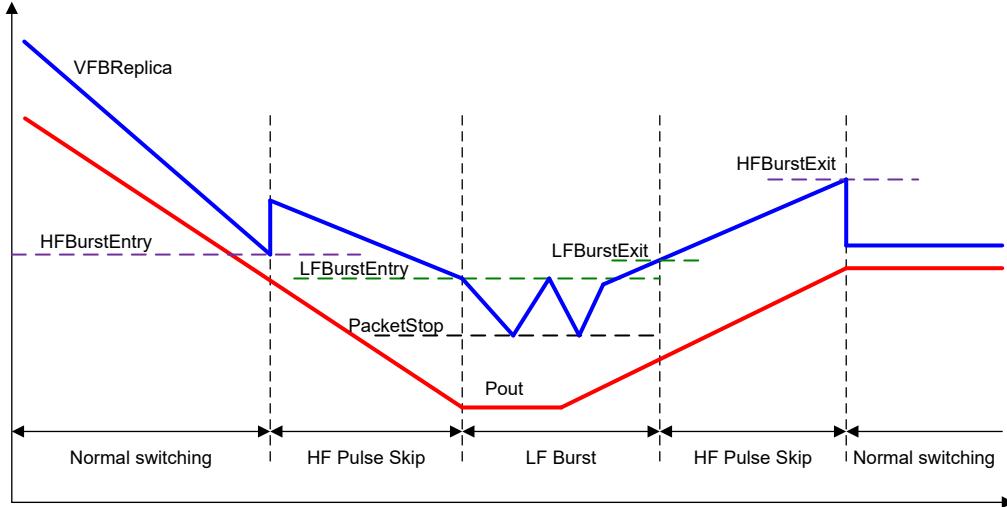

図 7-22 に、バーストモードでの UCC25661 の開始および終了動作を示します。

- *HFBurstEntry* は、システムが HF パルススキップに入る目的の電力レベルにおける *FBReplica* 電圧に対応します。

- *LFBurstEntry* は、システムが LF Burst に移行する修正 *FBReplica* 電圧に対応します。

- *FBreplica* が *HFBurstEntry* を上回ると、UCC25661 は通常スイッチングで動作します。

- *FBreplica* が *HFburstEntry* 未満で、*LFburstEntry* より大きい場合、UCC25661 は HF パルススキップモードで動作します。HF パルススキップモードでは、各パケットのエネルギーは引き続き制御信号 *FBReplica* によって制御されます。

- *FBreplica* が *LFburstEntry* を下回ると、UCC25661 は LF バーストモードで動作します。LF バーストモードでは、各パケットのエネルギーは *LFburstEntry* スレッショルドに固定されます。

- LF バーストモードで動作しているときは、*FBReplica* が *LFburstEntry* スレッショルドを上回ると、新しい LF バーストセグメントが開始されます。セグメントは、目的の数のパケットが配信され、*FBReplica* が *PacketStop* スレッショルドを下回ると終了します。

- LF バーストセグメント内の必要なパケット数が計算され、LF バースト動作周波数が 200Hz ~ 400Hz 以内に調整されます。

- 急激な負荷降下が発生した場合、出力の過電圧状態を回避するために LF バーストセグメントはただちに終端されます。

- *LFburst*において、*LFburstExit* および *HFburstExit* スレッショルドは連続的に計算されます。[式7](#) および [式8](#) では、これについて説明します。

- *FBReplica* が *LFburstExit* を上回ると、UCC25661 は HF バーストモードでの動作に戻ります。

- *FBReplica* が *HFburstExit* を上回ると、UCC25661 は *HFburst*を終了し、通常スイッチングに戻ります。

- コントローラが *HFburst*を終了するたびに、コントローラが再びバーストモードにならないように、2ms のブランкиング時間が追加されます。このブランкиング期間中に、*FBReplica* が *PacketStop* スレッショルドを下回ると、コントローラは再び *LFburst*に入ります。

$$LFburstExit = LFburstEntry \times \frac{(LF\ Burst\ On\ Time + LF\ Burst\ Off\ Time)}{(LF\ Burst\ On\ Time)} \quad (7)$$

$$HFburstExit = HFburstEntry \times \frac{(HF\ Burst\ On\ Time + HF\ Burst\ Off\ Time)}{(HF\ Burst\ On\ Time)} \quad (8)$$

図 7-22. *FBReplica* コンパレータからのバーストモードの決定

### 7.5.3.3 バーストモードスレッショルドプログラミング

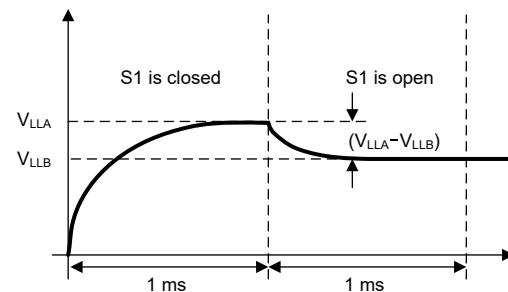

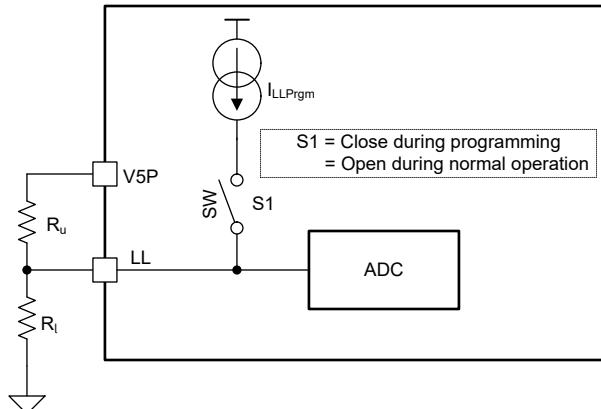

バーストモードスラッシュは、V5P と GNDP の間に接続された外付け抵抗分圧器によって行われます。外部分圧器のセンターノードを LL ピンに接続します。プログラミングフェーズ中に、定電流  $I_{LLPrgm}$  が LL ピンに供給され、その結果得られる電圧は、 $T_{LLPrgm}$  の時点で ADC ( $V_{LLA}$ ) を介して測定されます。 $T_{Prgm}$  の後、 $I_{LLPrgm}$  がオフになり、LL 分圧抵抗の電圧 ( $V_{LLB}$ ) が測定されます。

図 7-23. LL ピンのプログラミング

スイッチ S1 がオフになった後の LL ピンの電圧 ( $V_{LLB}$ ) は、システムが LF バースト セグメントを停止する入力電力を設定するために直接使用されます (*PacketStop* =  $V_{LLB}$ )。

測定された  $V_{LLB}$  電圧、および  $V_{LLA}$  と  $V_{LLB}$  の電圧差に基づいて、コントローラが HF バーストに入る *FBReplica* 電圧を決定します。詳細については、[設計計算機](#)を参照してください。

コントローラが LF バーストセグメントを開始する *FBReplica* は、[式 9](#) を使用して計算されます。

$$LFBurstEntry = \text{PacketStop} \div 0.6 \quad (9)$$

*HFBurstexit* および *LFBurstexit* スレッショルドには、それぞれ *HFBurstentry* および *LFBurstentry* からのヒステリシスがあります。2 つのヒステリシスはユーザー定義のパラメータではありません。これら 2 つのヒステリシスは、コンバータの動作ポイントに基づいて内部で動的に推定されます。

バーストモード機能は、 $(V_{LLA} - V_{LLB})$  を適切にプログラムすることで無効化できます。

表 7-2. バーストモードを外部でプログラム可能な設定

| ( $V_{LLA} - V_{LLB}$ ) (V) | $a = (\text{PacketStop} \div \text{HFBurstEntry})$ 比率 | 備考                      |

|-----------------------------|-------------------------------------------------------|-------------------------|

| >2.41                       | 該当なし                                                  | バースト無効化                 |

| 2.185                       | 0.45                                                  | LF 周波数範囲: 200Hz ~ 400Hz |

| 1.754                       | 0.50                                                  | LF 周波数範囲: 200Hz ~ 400Hz |

| 1.391                       | 0.55                                                  | LF 周波数範囲: 200Hz ~ 400Hz |

| 1.087                       | 0.60                                                  | LF 周波数範囲: 200Hz ~ 400Hz |

| 0.833                       | 0.65                                                  | LF 周波数範囲: 200Hz ~ 400Hz |

| 0.617                       | 0.70                                                  | LF 周波数範囲: 200Hz ~ 400Hz |

| 0.441                       | 0.75                                                  | LF 周波数範囲: 200Hz ~ 400Hz |

| 0.176                       | 0.80                                                  | LF 周波数範囲: 200Hz ~ 400Hz |

システムがさまざまな低消費電力モードに移行する入力電力を直接設定できるため、バーストモードを動的に無効にすることで、システム設計の自由をさらに高めることができます。

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

UCC25661 は、LLC 方式が実装されている幅広いアプリケーションに使用できます。より簡単に使用できるよう、TI は次のようなツールを用意して、製品の機能を紹介しています。

- フル機能の評価基板ハードウェア

- Excel 設計計算ツール

- Simplis モデル

以下に代表的な設計例を記載します。

### 8.2 代表的なアプリケーション

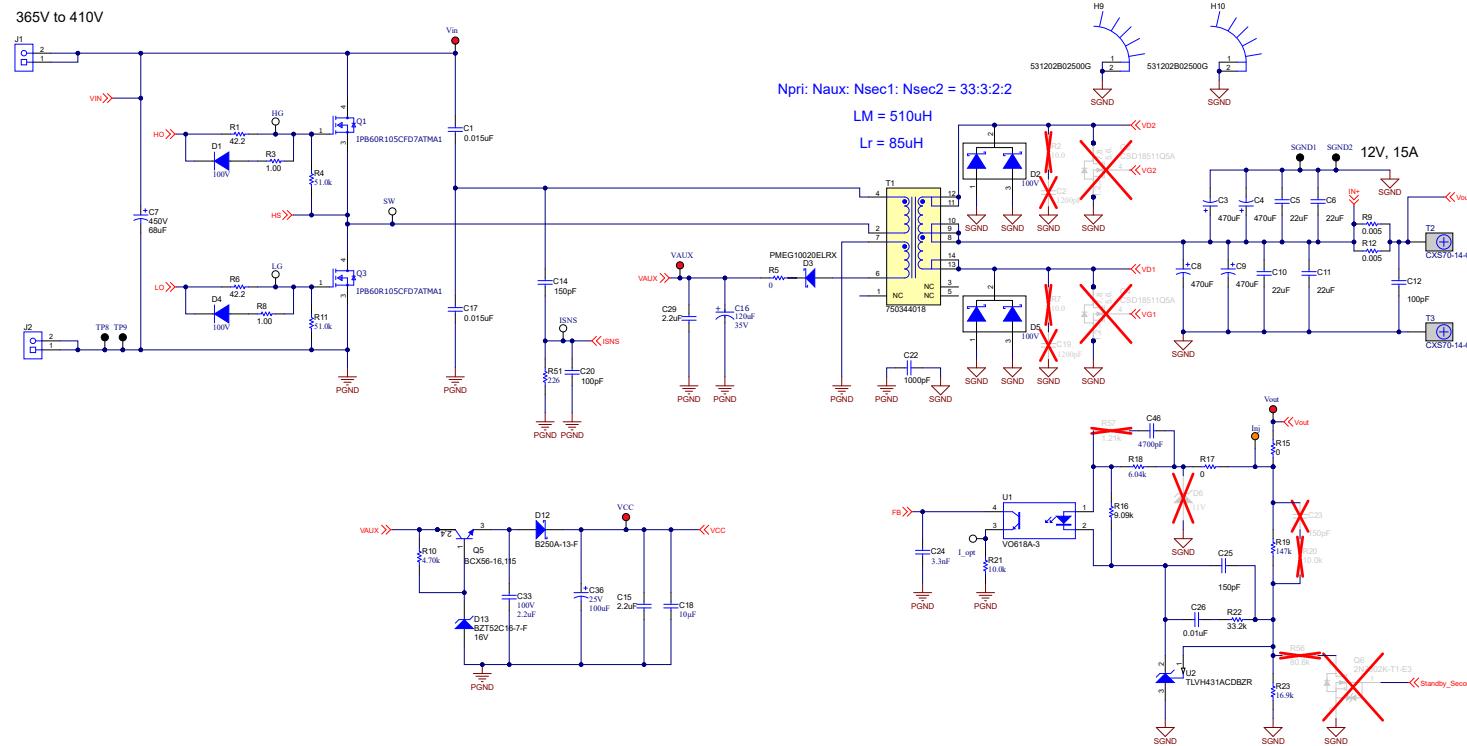

以下に UCC25661 をコントローラとする代表的なハーフ ブリッジ LLC アプリケーションを示します。

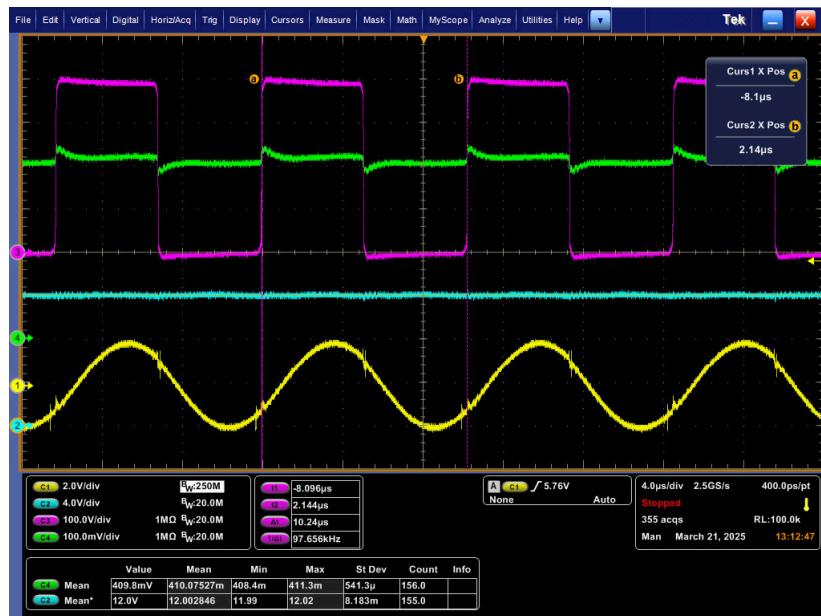

### 8.2.1 設計要件

設計仕様の概要を [表 8-1](#) に示します。

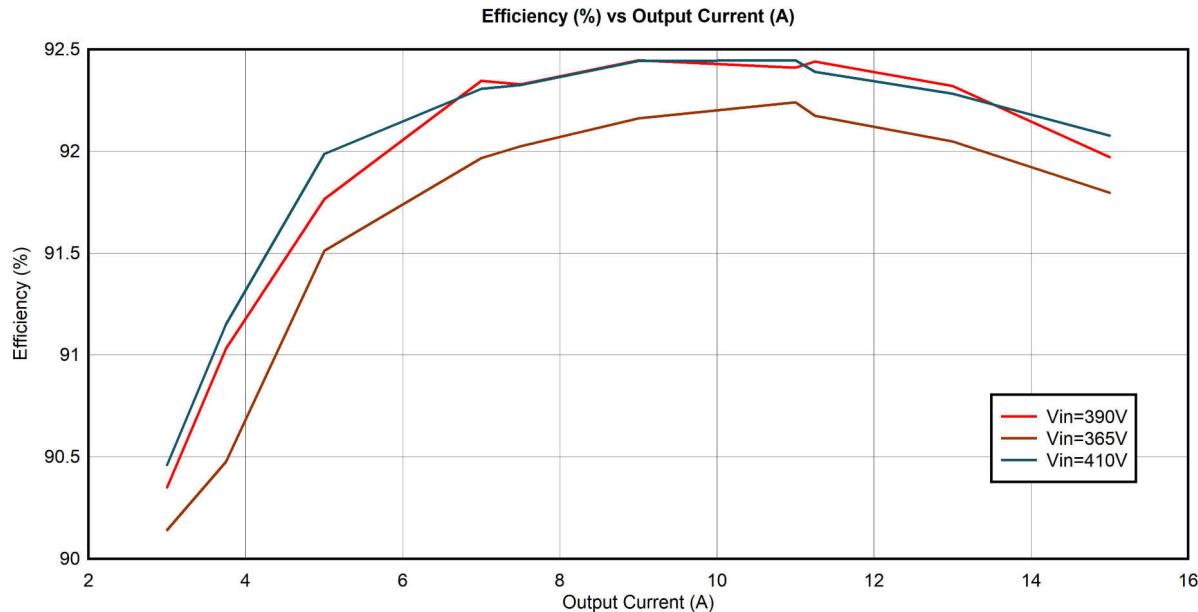

**表 8-1. システム設計仕様**

| パラメータ                   | テスト条件            | 最小値 | 標準値 | 最大値 | 単位   |

|-------------------------|------------------|-----|-----|-----|------|

| <b>入力特性</b>             |                  |     |     |     |      |

| DC 電圧範囲                 |                  | 365 | 390 | 410 | VDC  |

| AC 電圧範囲                 |                  | 85  |     | 264 | VAC  |

| AC 電圧周波数                |                  | 47  |     | 63  | Hz   |

| 入力 DC UVLO オン           |                  |     | 365 |     | VDC  |

| 入力 DC UVLO オフ           |                  |     | 315 |     | VDC  |

| <b>出力特性</b>             |                  |     |     |     |      |

| 出力電圧、V <sub>OUT</sub>   | 無負荷 ~ 全負荷        |     | 12  |     | VDC  |

| 出力負荷電流、I <sub>OUT</sub> | 360VDC~410VDC    |     |     | 15  | A    |

| 出力電圧リップル                | 390VDC、全負荷 = 15A |     | 120 |     | mVpp |

| <b>システム特性</b>           |                  |     |     |     |      |

| 共振周波数                   |                  |     | 100 |     | kHz  |

| ピーク効率                   | 390VDC           |     | 92  |     |      |

| 動作温度                    | 自然対流             |     | 25  |     | °C   |

### 8.2.2 詳細な設計手順

#### 8.2.2.1 LLC 電力段要件

設計は、LLC 電力段コンポーネントの各値を設定することから始まります。ここに述べる LLC 電力段の設計手順は、[『LLC 共振ハーフブリッジパワー コンバータの設計』アプリケーションノート](#)から引用したものです。このアプリケーションノートでは、使用する各式の由来が十分に説明されています。以下の式は、LLC 方式の解析によく用いられる FHA (First Harmonic Approximation) 法に基づきます。この手法は、あらゆる設計の出発点には適しているものの、最終設計には FHA の結果、回路シミュレーション、ハードウェア テストを組み合わせる反復アプローチが必要です。別の設計手法は、[『UCC29950 の LLC 設計』アプリケーションノート](#)です。

#### 8.2.2.2 LLC のゲイン範囲

まず、公称入力電圧と公称出力電圧から変圧器の巻数比を求めます。

$$N_{PS} = \frac{V_{IN(nom)} \div 2}{V_{OUT(nom)}} = \frac{390 \div 2}{12} = 16.25 \Rightarrow 16.5 \quad (10)$$

次に、LLC のゲイン範囲  $M_{G(min)}$  と  $M_{G(max)}$  を決定します。同期整流器を使用しない場合、他の損失 ( $V_{loss}$ ) により 0.5V と整流ダイオードに 0.5V の電圧降下 ( $V_f$ ) があると仮定します。

$$M_{G(min)} = N_{PS} \frac{V_{OUT(min)} + V_f}{V_{IN(min)} \div 2} = 16.5 \frac{12 + 0.5}{410 \div 2} = 1.006 \quad (11)$$

$$M_{G(max)} = N_{PS} \frac{V_{OUT(max)} + V_f + V_{loss}}{V_{IN(min)} \div 2} = 16.5 \frac{12 + 0.5 + 0.5}{365 \div 2} = 1.175 \quad (12)$$

#### 8.2.2.3 $L_n$ と $Q_e$ の選択

$L_n$  は、磁化インダクタンスと共振インダクタンスとの比率を意味します。

$$L_n = \frac{L_M}{L_R} \quad (13)$$

$Q_E$  は共振タンクの品質係数です。

$$Q_E = \frac{\sqrt{L_R \div C_R}}{R_E} \quad (14)$$

式 14 において、 $R_E$  は等価負荷抵抗です。

$L_N$  と  $Q_E$  の値を選択すると、LLC ゲイン曲線が描かれ、 $M_{G(\min)}$  および  $M_{G(\max)}$  のパターンと交差します。結果として描かれる曲線のピーク ゲインは、 $M_{G(\max)}$  より大きくなります。 $L_N$  と  $Q_E$  の選択方法の詳細については、ここでは説明しておりません、[設計カリキュレータ](#)を参照してください。

選択した  $L_N$  と  $Q_E$  の値は次のとおりです。

$$L_N = 6 \quad (15)$$

$$Q_E = 0.3 \quad (16)$$

#### 8.2.2.4 等価負荷抵抗の選定

式 17 により等価負荷抵抗を求めます。

$$R_E = \frac{8 \times N_{PS}^2}{\pi^2} \times \frac{V_{OUT(nom)}}{I_{OUT(nom)}} = \frac{8 \times 16.5^2}{\pi^2} \times \frac{12}{15} = 176.5\Omega \quad (17)$$

### 8.2.2.5 LLC 共振回路の部品パラメータの決定

共振タンク コンポーネント パラメータを求める前に、公称スイッチング周波数(共振周波数)を選択してください。この設計では、共振周波数として 100kHz を選択します。

$$f_0 = 100\text{kHz} \quad (18)$$

式 19、式 20 および 式 21 を使用して共振タンクパラメータを計算します。

$$C_R = \frac{1}{2\pi \times Q_E \times f_0 \times R_E} = \frac{1}{2\pi \times 0.3 \times 100\text{kHz} \times 176.5\Omega} = 30.0\text{nF} \quad (19)$$

$$L_R = \frac{1}{(2\pi \times f_0)^2 C_R} = \frac{1}{(2\pi \times 100\text{kHz})^2 \times 30.0\text{nF}} = 84.4\mu\text{H} \quad (20)$$

$$L_M = L_N \times L_R = 6 \times 84.4\mu\text{H} = 506.4\mu\text{H} \quad (21)$$

予備パラメータを選択したら、最も近い実際の部品の値で利用できるものを見つけ、選択したパラメータでゲイン曲線を再評価し、時間ドメイン シミュレーションを実行して回路動作を検証します。

次の共振タンク パラメータは以下のとおりです。

$$C_R = 30\text{nF} \quad (22)$$

$$L_R = 85\mu\text{H} \quad (23)$$

$$L_M = 510\mu\text{H} \quad (24)$$

最終共振タンク パラメータに基づき、共振周波数を計算します。

$$f_0 = \frac{1}{2\pi\sqrt{L_R C_R}} = \frac{1}{2\pi\sqrt{30\text{nF} \times 85\mu\text{H}}} = 99.7\text{kHz} \quad (25)$$

新しい LLC ゲイン曲線に基づき、最大および最小ゲインでの正規化したスイッチング周波数は次のように計算されます。

$$f_{N(\text{Mgmax})} = 0.7 \quad (26)$$

$$f_{N(\text{Mgmin})} = 1.0 \quad (27)$$

最大および最小スイッチング周波数は次のとおりです。

$$f_{SW(\text{Mgmax})} = 69.8\text{kHz} \quad (28)$$

$$f_{SW(\text{Mgmin})} = 99.7\text{kHz} \quad (29)$$

### 8.2.2.6 LLC の 1 次側の電流

コンポーネントを選択するために、1 次側電流を計算します。この電流は 110% の過負荷条件に基づいて計算します。

1 次側 RMS 負荷電流は次の式で計算されます。

$$I_{OE} = \frac{\pi}{2\sqrt{2}} \times \frac{I_0}{n} = \frac{\pi}{2\sqrt{2}} \times \frac{1.1 \times 15\text{A}}{16.5} = 1.111\text{A} \quad (30)$$

最小スイッチング周波数での RMS 磁化電流は次の式で計算されます。

$$I_M = \frac{\pi}{2\sqrt{2}} \times \frac{N_{PS} V_{OUT}}{\omega L_M} = \frac{\pi}{2\sqrt{2}} \times \frac{16.5 \times 12}{2\pi \times 64.8\text{kHz} \times 510\mu\text{H}} = 0.797\text{A} \quad (31)$$

共振タンクの総電流は次の式で計算されます。

$$I_R = \sqrt{I_M^2 + I_{OE}^2} = \sqrt{(1.111A)^2 + (0.797A)^2} = 1.367A \quad (32)$$

### 8.2.2.7 LLC の 2 次側の電流

2 次側の総 RMS 負荷電流は、1 次側電流 ( $I_{OE}$ ) から 2 次側に換算した電流です。

$$I_{OES} = N_{PS} \times I_{OE} = 16.5 \times 1.111A = 18.327A \quad (33)$$

この設計では、変圧器の 2 次側にセンタータップ (巻線の中間を引き出した端子) が付いています。各 2 次側変圧器巻線の電流は次の式で計算できます。

$$I_{WS} = \frac{\sqrt{2} \times I_{OES}}{2} = \frac{\sqrt{2} \times 18.327A}{2} = 12.959A \quad (34)$$

該当する半波平均電流は次のとおりです。

$$I_{SAV} = \frac{\sqrt{2} \times I_{OES}}{\pi} = \frac{\sqrt{2} \times 18.327A}{\pi} = 8.250A \quad (35)$$

### 8.2.2.8 LLC 変圧器

効率を最大化するには、HV スタートアップ機能を使用するバイアス巻線を使用します。VCCP 電圧が 12V を上回るよう にバイアス巻線を設計します。

以下の仕様に従って、トランスを製作または購入します。

- 卷数比: 1 次側:2 次側:バイアス = 33:2:3

- 1 次端子電圧: 450V<sub>PK</sub>

- 1 次側磁化インダクタンス:  $L_M = 510\mu H$

- 1 次側巻線定格電流:  $I_R = 1.367A$

- 2 次端子電圧: 36V<sub>PK</sub>

- 2 次巻線定格電流:  $I_{WS} = 12.959A$

- 最小スイッチング周波数: 69.8kHz

- 最大スイッチング周波数: 99.7kHz

- 1 次側と 2 次側の絶縁: IEC60950 強化絶縁

広い入力範囲の LLC として動作する一部のアプリケーションでは、スタンバイ モードで PFC がシャットオフされる可能性があるため、重負荷シャットダウン中は動作周波数が大幅に低下する可能性があり、LLC は ZCS 境界をわずかに上回る、低い周波数で動作します。共振回路、変圧器インダクタ、共振インダクタ内の磁気部品を、より低い周波数で動作するように定格します。

バイアス電圧は、巻線比に従って 18V となります。コントローラの電圧を 15V に下げるには、コントローラの VCCP に供給する前に、[UCC25661EVM-128](#) のような電圧レギュレータ回路を使用します。

### 8.2.2.9 LLC 共振インダクタ

共振インダクタの両端の AC 電圧は、AC 電圧インピーダンスと電流を乗じて計算されます。

$$V_{LR} = \omega L_R I_R = 2\pi \times 69.8\text{kHz} \times 85\mu H \times 1.367A = 50.946V \quad (36)$$

次の仕様に従って、インダクタを構築または購入します。

- インダクタンス:  $L_R = 85\mu H$

- 定格電流:  $I_R = 1.367A$

- 端子 AC 電圧: 50.946V

- 周波数範囲: 69.8kHz ~ 99.7kHz

一部の設計では、トランジスタの漏れインダクタンスを共振インダクタンスとして利用しており、外部共振インダクタを必要としない場合があります。

### 8.2.2.10 LLC 共振コンデンサ

LLC 共振コンデンサはスイッチング周波数でフル 1 次電流を伝導します。過熱を防止するため、散逸係数の小さいコンデンサを使用してください。

共振コンデンサの AC 電圧は、AC 電圧インピーダンスに電流を掛けた値で求められます。

$$V_{CR} = \frac{I_R}{\omega C_R} = \frac{1.367A}{2\pi \times 69.8\text{kHz} \times 30\text{nF}} = 104.0\text{V} \quad (37)$$

$$V_{CR(\text{RMS})} = \sqrt{\left(\frac{V_{IN(\text{max})}}{2}\right)^2 + V_{CR}^2} = \sqrt{\left(\frac{410}{2}\right)^2 + 104.0^2} = 229.9\text{V} \quad (38)$$

ピーク電圧:

$$V_{CR(\text{peak})} = \frac{V_{IN(\text{max})}}{2} + \sqrt{2}V_{CR} = \frac{410}{2} + \sqrt{2} \times 104.0 = 352.0\text{V} \quad (39)$$

谷電圧:

$$V_{CR(\text{valley})} = \frac{V_{IN(\text{max})}}{2} - \sqrt{2}V_{CR} = \frac{410}{2} - \sqrt{2} \times 104.0 = 58.0\text{V} \quad (40)$$

定格電流:

$$I_R = 1.367\text{A} \quad (41)$$

### 8.2.2.11 LLC の 1 次側 MOSFET

各 MOSFET は、入力電圧をそれぞれの最大印加電圧と認識します。次のように MOSFET の定格電圧は最大バルク電圧の 1.5 倍に設定します。

$$V_{QLLC(\text{peak})} = 1.5 \times V_{IN(\text{max})} = 615\text{V} \quad (42)$$

次のように MOSFET の定格電流は最大 1 次側 RMS 電流の 1.1 倍に設定します。

$$I_{QLLC} = 1.1 \times I_R = 1.504\text{A} \quad (43)$$

### 8.2.2.12 アダプティブ デッドタイムの設計における考慮事項

共振タンクを設計して、1 次側 MOSFET を選定したら、コンバータの ZVS 動作を再確認してください。ZVS は、ゲートターンオフ エッジで、スイッチ ノードの容量を放電するのに十分な電流が共振インダクタに残っている場合、または  $L(I \times I)$  が  $COSS(V \times V)$  より大きい場合、ZVS は実現しません。 $COSS$  は、2 つのスイッチ段 MOSFET のドレイン-ソース間の実効容量です。UCC25661 は、スイッチのスルーリングに基づくアダプティブ デッドタイムを実装しています。スルーリング回路の検出範囲は 0.1V/ns ~ 200V/ns です。

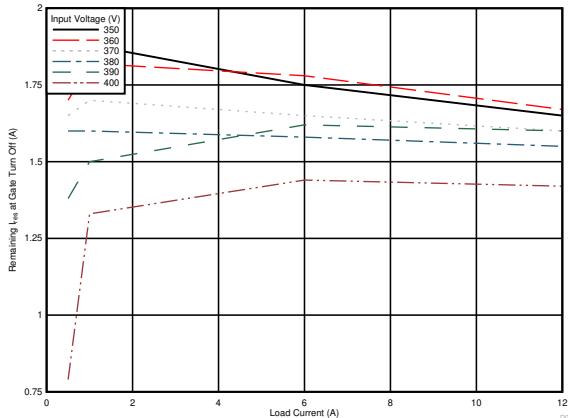

ZVS 動作を確認するには、図 8-1 に示されているように、コントローラーは、一連の時間領域シミュレーションを実行し、ゲートオフ エッジでの共振電流を捕捉します。

図 8-1. アダプティブ デッドタイム

上記の 図 8-1 は、5% 負荷で最大スイッチング周波数が生じ、5% 負荷でシステムがバーストを開始すると仮定したものです。

図 8-1 を使用すると、当該動作範囲で、タンクに残っている最小共振電流は  $I_{min} = 0.8A$  になります。スルーレートを計算するため、1 次側スイッチノードの寄生容量を把握してください。MOSFET データシートに記載されている COSS の値から低速レートを推定します。この場合、各 MOSFET が  $200\text{pF}$  であるため、合計  $C_{switchnode} = 400\text{pF}$  となります。最小スルーレートは次の式で計算されます。

$$\frac{I_{MIN}}{C_{switchnode}} = \frac{0.8A}{400\text{pF}} = 2\text{V/ns} \quad (44)$$

### 8.2.2.13 LLC 整流ダイオード

出力ダイオードの電圧定格は、次のように計算されます。

$$V_{DD} = 1.2 \times \frac{V_{IN(\max)}}{N_{PS}} = 1.2 \times \frac{410}{16.5} = 29.82\text{V} \quad (45)$$

出力ダイオードの電流定格は、次のように計算されます。

$$I_{SAV} = \frac{\sqrt{2} \times I_{OES}}{\pi} = \frac{\sqrt{2} \times 18.329}{\pi} = 8.250\text{A} \quad (46)$$

### 8.2.2.14 LLC 出力コンデンサ

LLC コンバータトポロジには、出力フィルタは必要ありません。ピークツーピークの出力リップルを低減するため、小型の 2 段目フィルタ インダクタを使用します。出力コンデンサが整流器の全波出力電流を流すと仮定すると、コンデンサのリップル電流定格は次のようになります。

$$I_{RECT} = \frac{\pi}{2\sqrt{2}} I_{OUT} = \frac{\pi}{2\sqrt{2}} \times 15 = 16.66\text{A} \quad (47)$$

12V の出力電圧に対して定格 20V を採用します。

$$V_{LLCcap} = 20\text{V} \quad (48)$$

このコンデンサの RMS 定格電流は次のとおりです。

$$I_{C(out)} = \sqrt{\left(\frac{\pi}{2\sqrt{2}} I_{OUT}\right)^2 - I_{OUT}^2} = \sqrt{\left(\frac{\pi}{2\sqrt{2}} \times 15\right)^2 - 15^2} = 7.251\text{A} \quad (49)$$

導電性高分子技術を採用した固体アルミニウムコンデンサは、定格リップル電流が高いため、特に設計がより低い温度で動作する必要がある場合には、良い選択肢となります。1つのコンデンサのリップル電流定格が不十分な場合は、複数のコンデンサを並列に接続します。

LLC段の出力時のリップル電圧は、コンデンサに流れるAC電流量の関数です。このリップル電圧を推計するため、負荷のDC電流を含むすべての電流がフィルタコンデンサに流れるものと仮定します。

$$ESR_{max} = \frac{V_{OUT(pk-pk)}}{I_{RECT(pk)}} = \frac{0.12V}{2\frac{\pi}{4} \times 15A} = 5.1m\Omega \quad (50)$$

コンデンサの仕様は次のとおりです。

- 定格電圧: 20V

- 定格リップル電流: 7.251A

- 実効 ESR: < 5.1mΩ

### 8.2.2.15 HV ピン直列抵抗

HVピンに複数の抵抗を直列に接続することで、各抵抗器の消費電力を制限できます。HVピンの標準的な直列抵抗は5kΩであり、各アプリケーションに直列抵抗値を最適化する必要があります。たとえば、より高いバス電圧を使用する場合は、より高い値の直列抵抗を選択します。

### 8.2.2.16 BLK ピン分圧器

BLKピンは LLC DC入力電圧を検知して、LLCコンバータをオンおよびオフにするタイミングを決定します。また、BLKピンの電圧はフィードフォワード補償にも使用されます。

UCC25661EVM-128のBLKピン抵抗分割器の電力バジェットは15mWです。BLKが検知する抵抗の合計値は次の式で計算されます。

$$R_{BLKsns} = R_{BLKupper} + R_{BLKlower} = \frac{V_{IN(nom)}^2}{P_{BLKsns}} = \frac{390^2}{0.015} = 10M\Omega \quad (51)$$

LLCスタートアップ電圧を365Vに選択します。次に、以下のように  $V_{BLKstop}$ 、 $V_{BLKstartHys}$ 、 $I_{BLKSink}$  に関する  $V_{BLKstart}$  を示します。

$$V_{BLKstart} = 365 \left( \frac{R_{BLKlower}}{R_{BLKupper} + R_{BLKlower}} \right) = V_{BLKstop} + V_{BLKstartHys} + I_{BLKSink} \left( \frac{R_{BLKupper}R_{BLKlower}}{R_{BLKupper} + R_{BLKlower}} \right) \quad (52)$$

$V_{BLKstop} = 1V$ 、 $V_{BLKstartHys} = 0.1V$ 、 $I_{BLKSink} = 5\mu A$ 、 $R_{BLKupper}$  は  $10M\Omega$ 、 $R_{BLKlower}$  は  $35.4k\Omega$  です。

$R_{BLKlower}$  には標準値  $35.4k\Omega$  が選択され、 $R_{BLKupper}$  には標準値として  $\times 3 3.3M\Omega$  が直列として選択されます。

実際のスタートアップ電圧は、以下を使用して計算します

$$V_{BLKstart} \left( \frac{R_{BLKupper} + R_{BLKlower}}{R_{BLKlower}} \right) = \left( \frac{V_{BLKstop} + V_{BLKstartHys} + I_{BLKSink} \left[ \frac{R_{BLKupper}R_{BLKlower}}{R_{BLKupper} + R_{BLKlower}} \right]}{R_{BLKupper} + R_{BLKlower}} \right) \times \left( \frac{R_{BLKupper} + R_{BLKlower}}{R_{BLKlower}} \right) = 358V \quad (53)$$

BLK抵抗の消費電力は、以下で計算されます

$$P_{BLKsns} = \frac{V_{IN(nom)}^2}{(R_{BLKupper} + R_{BLKlower})} = \frac{390^2}{(10M\Omega + 35.4k\Omega)} = 15.3mW \quad (54)$$

LLCターンオフ電圧は、以下で計算されます

$$V_{BLKStop} \left( \frac{R_{BLKupper} + R_{BLKlower}}{R_{BLKlower}} \right) = 280.6V \quad (55)$$

### 8.2.2.17 ISNS ピン微分器

ISNS ピンは微分器により共振電流を検出します。ISNS ピンを TSET、BLK ピンの抵抗と組み合わせることで、過負荷保護レベルを設定できます。過負荷保護 ( $V_{FBOLP}$ ) の標準スレッショルド電圧は 4.75V です。ISNS ピンは過電流保護レベル (OCP1) の設定にも使用できます。OCP1 のスレッショルド値は、使用している TSET ピンの抵抗とバリアントに応じて 3.5V または 4V です。この評価基板の場合、UCC256611 を使用しています。そのため、このバリアントでは、OCP1 スレッショルド値電圧は 3.5V です。

全負荷時のピーク共振インダクタ電流

$$I_{R\_PEAK} = \sqrt{2} I_R = \sqrt{2} \times 1.367 = 1.933A \quad (56)$$

抵抗に比べて高電圧コンデンサの選択肢は少ないため、まず電流検出コンデンサを選定します。

$$C_{ISNS} = 150pF \quad (57)$$

この設計では、UCC256611 を使用します。そのため、このバリアントでは、OCP1 スレッショルド値電圧は 3.5V です。

$$OCP1\_Threshold = 3.5V \quad (58)$$

それから必要な ISNS 抵抗値を計算します。

$$R_{ISNS} < \frac{OCP1\_Threshold \cdot C_r}{I_{R\_PEAK} \cdot C_{ISNS}} = \frac{3.5V \cdot 30nF}{1.933A \cdot 150pF} = 329\Omega \quad (59)$$

$$R_{ISNS} = 226\Omega \quad (60)$$

式 60 が選択されます。

OCP1 レベルでのピーク共振電流は次の式で求められます。

$$I_{R\_PEAK\_OCP1} = \frac{OCP1\_Threshold \times C_r}{R_{ISNS} \times C_{ISNS}} = \frac{3.5 \times 30nF}{226 \times 150pF} = 3.097A \quad (61)$$

### 8.2.2.18 TSET ピン

TSET ピン抵抗は、VCR 積分器の時定数 (タイマ ゲイン ( $[k_s]$ )、 $R_{VCR}$ 、 $R_{RAMP}$ 、 $C_{VCR}$ )、および IPPC モードの最小スイッチング周波数を設定します。TSET ピンの抵抗は、特定の出力電力に対する  $V_{FBreplica}$  電圧も決定します。

以下の情報は、OCP/OLP デカップリングがイネーブルのデバイスに関するものです。

最小入力電圧および最大出力電力時に  $f_{SW(Mgmin)}$  と全負荷動作周波数に基づいて  $V_{TSETB}$  電圧オプションを選択します。この設計では、最小入力電圧 365V、定格出力電力において、観測される全負荷動作周波数が 89kHz であるため、設計計算機オプション #4 を選択します。オプション #4 の場合、表 7-1 に示すように、 $V_{TSETB}$  電圧は 0.742V ~ 48mV の範囲にする必要があります。

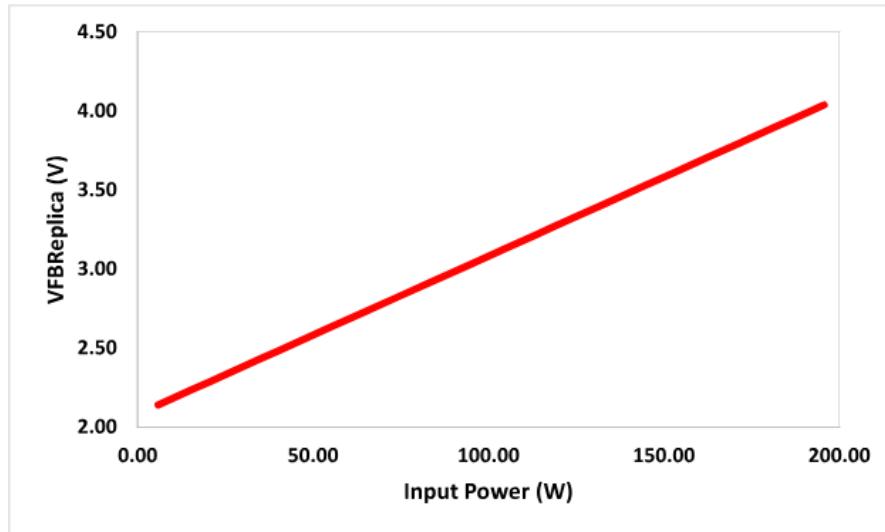

特定の電力出力に対して FBReplica の振幅を設定するために、( $V_{TSETA} - V_{TSETB}$ ) 電圧を選択します。図 8-2 に示すように、最大出力電力で FBReplica 振幅が  $V_{FBOLP}$  を下回るように、差電圧を選択し、ワースト ケースとして必要なマージンを確保します。この設計では、VCR 積分器の時定数と、選択した ISNS および BLK 抵抗によって、最大入力電力時の FBReplica 振幅が 4V に近くなり、( $V_{TSETA} - V_{TSETB}$ ) 電圧を 0.850V ~ 48mV の範囲に設定できるように、表 7-1 表からオプション #5 を選択しています。表 7-1

$$V_{TSETB} = \frac{R_{TSET\_lower} \cdot V5P}{R_{TSET\_lower} + R_{TSET\_upper}} \quad (62)$$

$$V_{TSETA} = V_{TSETB} + \frac{R_{TSET\_lower} \cdot R_{TSET\_upper}}{R_{TSET\_lower} + R_{TSET\_upper}} \cdot I_{TSETPrgm} \quad (63)$$

式 62 と式 63 を解くと、 $R_{TSET\_upper}$  は  $572.78\text{k}\Omega$ 、 $R_{TSET\_lower}$  は  $99.81\text{k}\Omega$  です。

最後に、 $R_{TSET\_upper} = 576\text{k}\Omega$  かつ  $R_{TSET\_lower} = 100\text{k}\Omega$  を選択します。

最終的な  $V_{TSETB}$  および  $(V_{TSETA} - V_{TSETB})$  は式 64 と式 65 を使用して計算できます。

$$V_{TSETB} = \frac{100\text{k} \cdot 5\text{V}}{100\text{k} + 576\text{k}} = 0.74\text{V} \quad (64)$$

$$(V_{TSETA} - V_{TSETB}) = \frac{100\text{k} \cdot 576\text{k}}{100\text{k} + 576\text{k}} \cdot 10\mu\text{A} = 0.852\text{V} \quad (65)$$

図 8-2 に、LLC の入力電力に対する FBReplica 電圧を示します。

$P_{in}$  を計算するために、次の式で 92% の効率を使用します。

$$P_{in} = \frac{P_{out}}{\eta} \quad (66)$$

図 8-2. FBReplica と  $P_{in}$  の比較

FBReplica 電圧は、帰還オプトカプラ エミッタとグランドの間に  $10\text{k}\Omega$  の抵抗を入れることによって測定します。 $10\text{k}\Omega$  抵抗で測定された電圧が  $V_{10\text{k}\Omega}$  であると仮定します。FBReplica 電圧を計算するには、式 67 を使用します。

$$\text{FBReplica} = \left( I_{FB} - \frac{V_{10\text{k}\Omega}}{10\text{k}\Omega} \right) \times R_{FBInternal} \quad (67)$$

#### 8.2.2.19 OVP/OTP ピン

OVP/OTP ピンは、パワー ステージを過電圧から保護するために使用されます。OVP/OTP ピンは、負の温度係数 (NTC) サーミスタを使用した過熱保護のために同じピンが使用されます。バイアス巻線電圧は、トランスの巻線比による出力電圧のミラーイメージであるため、このピンをツェナーダイオードでプルアップすると、OVP を 1 次側に設定するのに便利です。このデザインで、公称出力電圧は  $12\text{V}$  です。出力電圧と推奨されるバイアス電圧の比に基づいて、バイアス巻線と 2 次側巻線との巻線比は  $1.5$  です。整流ダイオードが存在する場合、 $0.5\text{V}$  の電圧降下 ( $V_f$ ) が発生すると仮定します。同期整流を使用する場合、その他の損失 ( $V_{loss}$ ) による  $0.5\text{V}$  の電圧降下のみを推定できるため、バイアス巻線の公称電圧はを使って計算できます。

$$V_{BiasWindingNom} = (12 + 0.5 + 0.5) \times \frac{N_{aux}}{N_2} = (12 + 0.5 + 0.5) \times \frac{3}{2} = 19.5V \quad (68)$$

この設計に望ましい OVP スレッショルドは、公称値の 140% です。UCC25661 デバイスの OVP スレッショルド レベル ( $V_{OVPpos}$ ) は 3.5V です。ツエナー ダイオードに必要な電圧定格は次の式で計算されます。

$$V_z = (1.4 \times V_{out} + V_{drop}) \times \frac{N_{aux}}{N_2} - V_{OVPpos} = (1.4 \times 12 + 0.5 + 0.5) \times \frac{3}{2} - 3.5 = 23.2V \quad (69)$$

使用されるツエナーの実際の電圧定格は 23V と仮定します。次に OVP がトリガされる実際の出力電圧が決まります。

$$V_{out\_ovp} = (V_z + V_{OVPpos}) \times \frac{N_2}{N_{aux}} - V_{drop} = (23 + 3.5) \times \frac{2}{3} - 1 = 16.67V = 139\% \times V_{out} \quad (70)$$

通常動作時、OVP/OTP ピンの標準電圧は 0.8V ~ 3.5V の動作範囲内です。過熱保護のため、OVP/OTP ピンを OTP スレッショルド 0.8V 未満にプルダウンします。室温では、OVP/OTP ピンの電圧は 1.4V と見なされます。室温でのこのピンの実効抵抗値は以下のとおりです。

$$R_{OVP/OTP\_25} = \frac{1.4V}{I_{OVP\_OTP}} = \frac{1.4V}{100 \times 10^{-6}A} = 14k\Omega \quad (71)$$

$$R_{OVP/OTP\_25} = \frac{R_{ext} \times R_{NTC\_25}}{R_{ext} + R_{NTC\_25}} = 14k\Omega \quad (72)$$

$R_{ext}$  はサーミスタと並列に接続された外付け抵抗です。 $R_{NTC\_25}$  は室温でのサーミスタの抵抗値です。

この設計では、過熱保護を 110°C に設定します。NTC の利用可能性と温度係数に基づいて、式 73 を選択します。

$$\frac{R_{NTC\_110}}{R_{NTC\_25}} = 0.035263 \quad (73)$$