# UCC256301 スタンバイ時電力の非常に低い、ハイブリッドヒステリシス・モード、広V<sub>IN</sub>、LLC共振コントローラ

## 1 特長

- ハイブリッドヒステリシス制御(HHC)

- クラス最高の過渡応答

- 容易な補償設計

- 最適化された低消費電力機能により、PFCオンで75mWのスタンバイ消費電力設計が可能に

- 高度なバースト・モード

- オプトカプラの低消費電力動作

- CoC Tier II標準への準拠を支援

- バースト・モードの高速な終了

- 容量性領域回避手法の改良

- アダプティブデッドタイム制御

- ハイサイドゲート・ドライバ内蔵(0.6Aおよび1.2Aの能力)

- ハードスイッチングなしの堅牢なソフトスタート

- 3値の過電流保護による過熱、出力過電圧、入力過電圧および低電圧からの保護

- 広い動作周波数範囲(35kHz～1MHz)

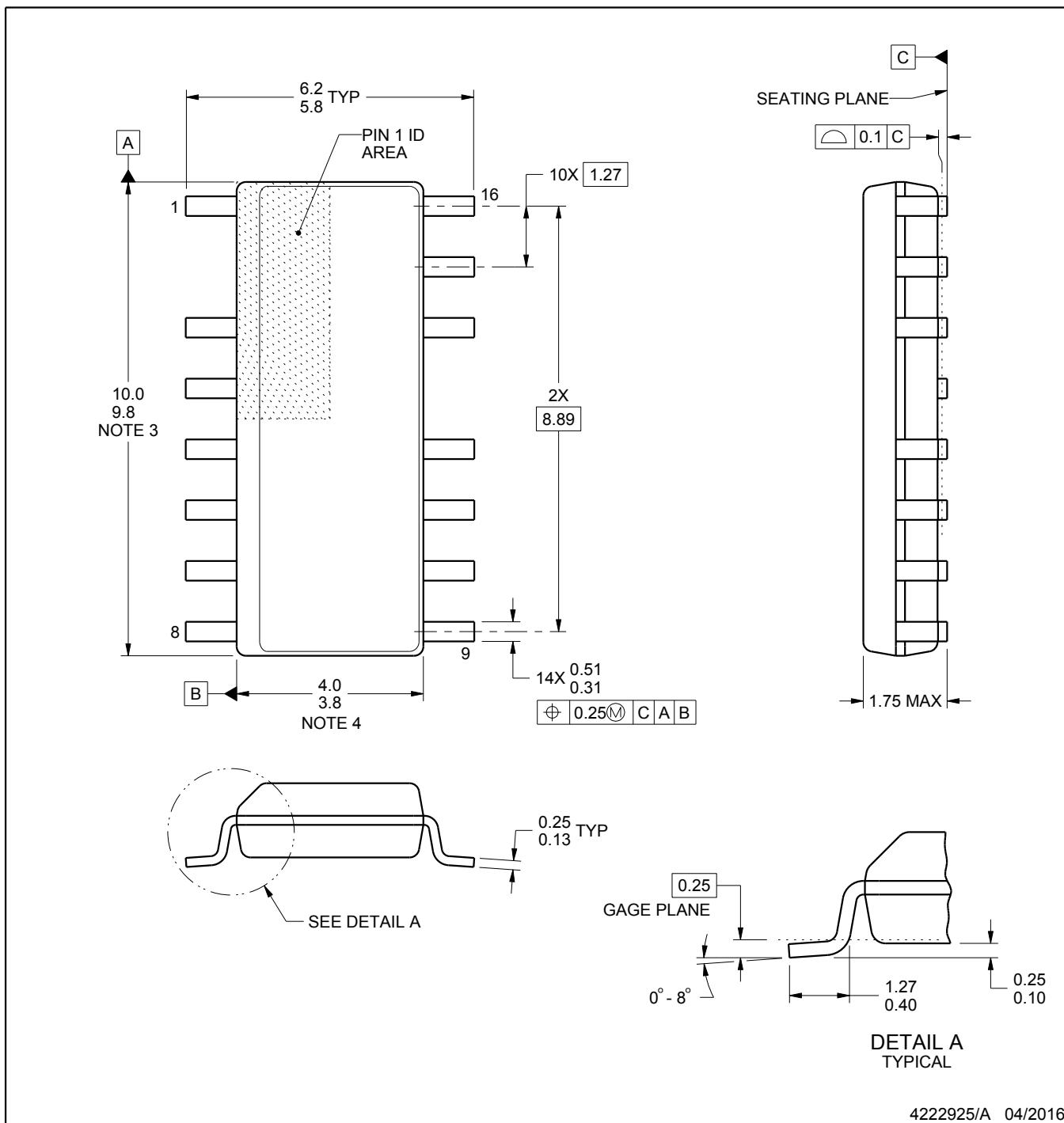

- 高電圧クリアランスを持つSOIC16にLLC共振コントローラを内蔵

- WEBENCH® Power DesignerによるUCC256301を使用するカスタム設計の作成

## 2 アプリケーション

- デジタル・テレビ用SMPS

- AC/DCアダプタ

- パワー・ツール

- LED照明アプリケーション

## 3 概要

UCC256301は充実した機能を持つLLCコントローラで、高電圧ゲート・ドライバが内蔵されています。PFC段と共に最小の外部部品点数で電源システムを構築できるよう設計されています。また電力コンバータを必要とせずPFC段が常時実行された状態でも、スタンバイ電力の最も厳格な要件を満たすよう設計されています。UCC256301には、LLCコンバータの動作を十分に制御された堅牢なものとするよう設計された、広範な機能が搭載されています。このデバイスは、LLC設計者の負担を減らし、主用途でもLLC方式の効率性の利点を得られることを目的としています。

UCC256301はハイブリッドヒステリシス制御により、クラス最高のラインおよび負荷過渡応答を実現しています。この制御動作はほぼ線形で、1サイクル内の平均入力電流に比例します。この制御動作では、開ループの伝達関数を1次システムとしているため、補償が非常に簡単です。正しい周波数補償により、システムは常時安定します。

UCC256301には高効率のバースト・モードがあり、サイクルの各バースト中でバースト電力レベルが一定しています。バースト電力レベルはプログラム可能で、入力電圧に応じて適合的に変化するため、容易に効率を最適化できます。

### 製品情報<sup>(1)</sup>

| 型番        | パッケージ     | 本体サイズ(公称)   |

|-----------|-----------|-------------|

| UCC256301 | SOIC (16) | 9.9mmx3.9mm |

(1) 提供されているすべてのパッケージについては、卷末の注文情報をお参照ください。

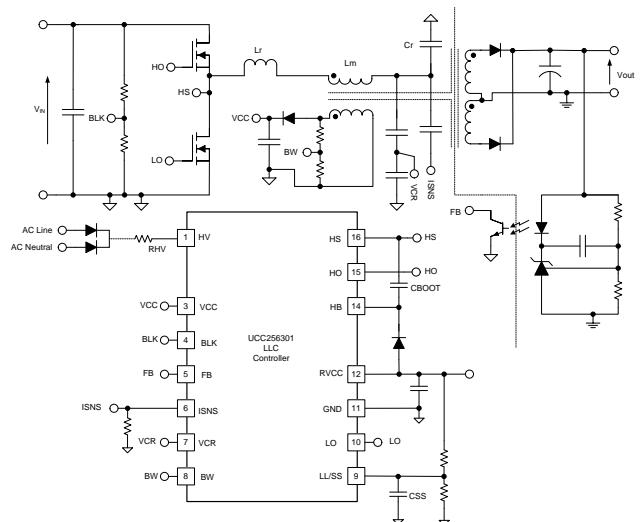

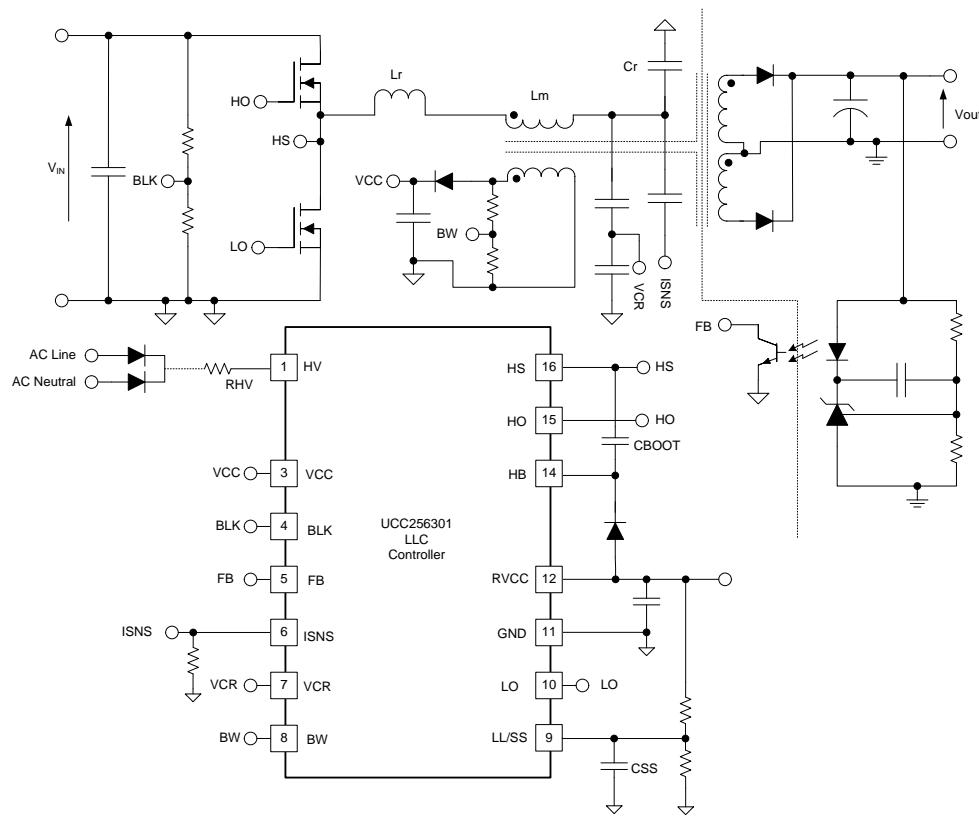

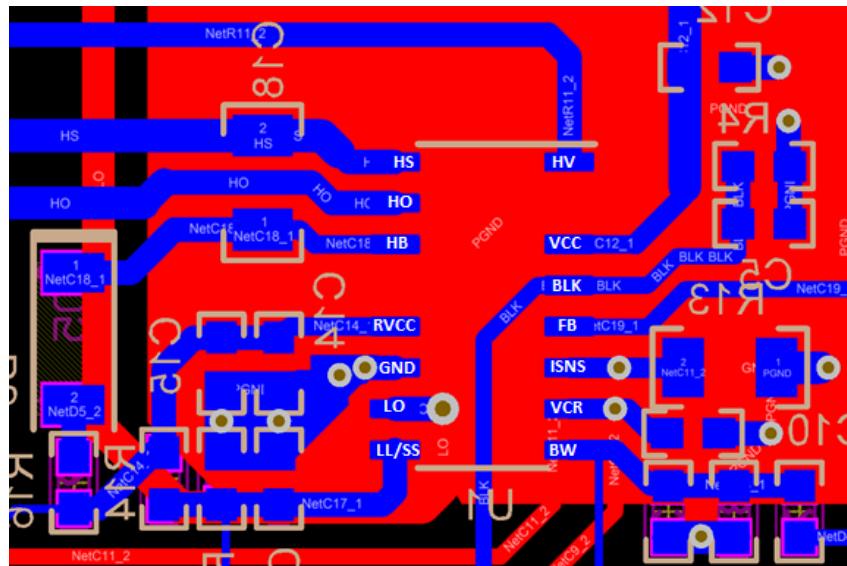

### 概略回路図

Copyright © 2017, Texas Instruments Incorporated

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、www.ti.comで閲覧でき、その内容が常に優先されます。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず最新版の英語版をご参照くださいますようお願いいたします。

English Data Sheet: SLUSCU6

## 目次

|          |                  |    |           |                           |    |

|----------|------------------|----|-----------|---------------------------|----|

| <b>1</b> | 特長 .....         | 1  | <b>8</b>  | アプリケーションと実装 .....         | 46 |

| <b>2</b> | アプリケーション .....   | 1  | 8.1       | アプリケーション情報 .....          | 46 |

| <b>3</b> | 概要 .....         | 1  | 8.2       | 代表的なアプリケーション .....        | 46 |

| <b>4</b> | 改訂履歴 .....       | 3  | <b>9</b>  | 電源に関する推奨事項 .....          | 61 |

| <b>5</b> | ピン構成および機能 .....  | 4  | 9.1       | VCC容量 .....               | 61 |

| <b>6</b> | 仕様 .....         | 5  | 9.2       | ブート・キャパシタ .....           | 61 |

| 6.1      | 絶対最大定格 .....     | 5  | 9.3       | RVCC容量 .....              | 62 |

| 6.2      | ESD定格 .....      | 5  | <b>10</b> | レイアウト .....               | 63 |

| 6.3      | 推奨動作条件 .....     | 5  | 10.1      | レイアウトの注意点 .....           | 63 |

| 6.4      | 熱特性 .....        | 6  | 10.2      | レイアウト例 .....              | 63 |

| 6.5      | 電気的特性 .....      | 6  | <b>11</b> | デバイスおよびドキュメントのサポート .....  | 64 |

| 6.6      | スイッチング特性 .....   | 8  | 11.1      | デバイス・サポート .....           | 64 |

| 6.7      | 代表的特性 .....      | 9  | 11.2      | ドキュメントのサポート(該当する場合) ..... | 64 |

| <b>7</b> | 詳細説明 .....       | 14 | 11.3      | ドキュメントの更新通知を受け取る方法 .....  | 64 |

| 7.1      | 概要 .....         | 14 | 11.4      | コミュニティ・リソース .....         | 64 |

| 7.2      | 機能ブロック図 .....    | 16 | 11.5      | 商標 .....                  | 64 |

| 7.3      | 機能説明 .....       | 17 | 11.6      | 静電気放電に関する注意事項 .....       | 64 |

| 7.4      | デバイスの機能モード ..... | 31 | 11.7      | Glossary .....            | 65 |

|          |                  |    | <b>12</b> | メカニカル、パッケージ、および注文情報 ..... | 65 |

## 4 改訂履歴

| Revision A (August 2017) から Revision B に変更                                                        | Page |

|---------------------------------------------------------------------------------------------------|------|

| • 箇条書き「CoC Tier II標準に合致」を「CoC Tier II標準への準拠を支援」に 変更.....                                          | 1    |

| • 内蔵X-Capacitor放電の箇条書き 削除 .....                                                                   | 1    |

| • IEC60950およびIEC60065標準に合致の箇条書き 削除.....                                                           | 1    |

| • UL60950-1に合致の箇条書き 削除 .....                                                                      | 1    |

| • Changed 接合部温度範囲の最大値を150°Cから125°Cに。.....                                                         | 5    |

| • Changed 高電圧起動、最終テスト電流段のACゼロクロス検出期間の長さの値を最小46.704、標準48.313、最大50.096から最小43ms、標準46ms、最大52msに。..... | 7    |

| • Changed パルク電圧検知、LLCがスイッチングを開始できる入力電圧の最小値を2.99msから2.969msに。.....                                 | 7    |

| 2017年8月発行のものから更新                    | Page |

|-------------------------------------|------|

| • 削除「安全な」および「安全(性)」という文言を3カ所で。..... | 14   |

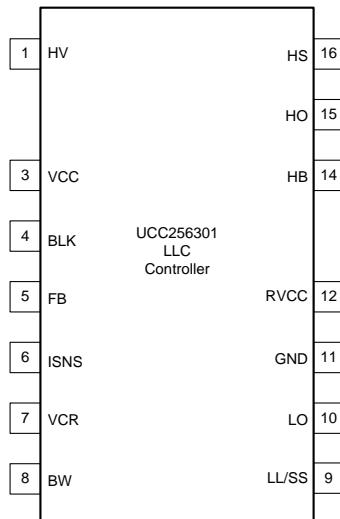

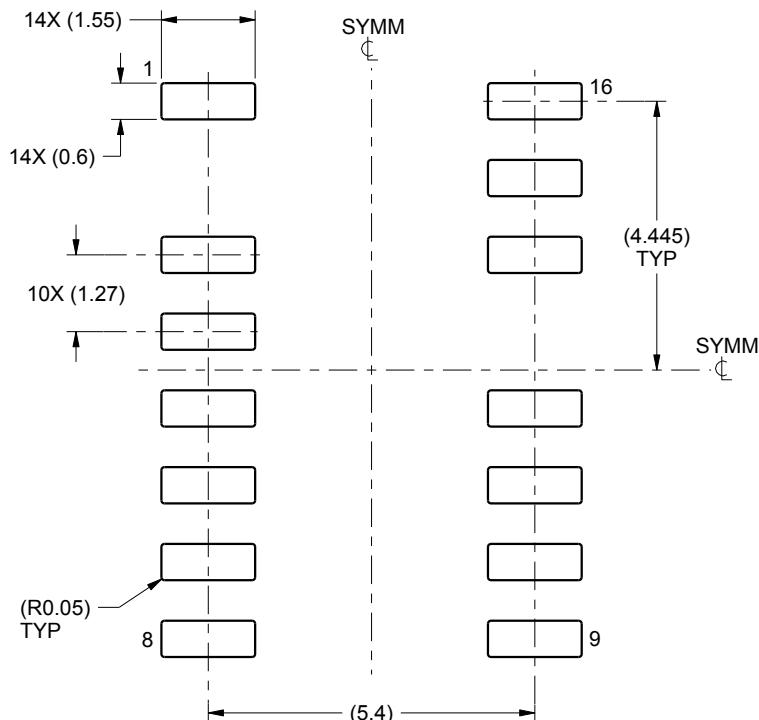

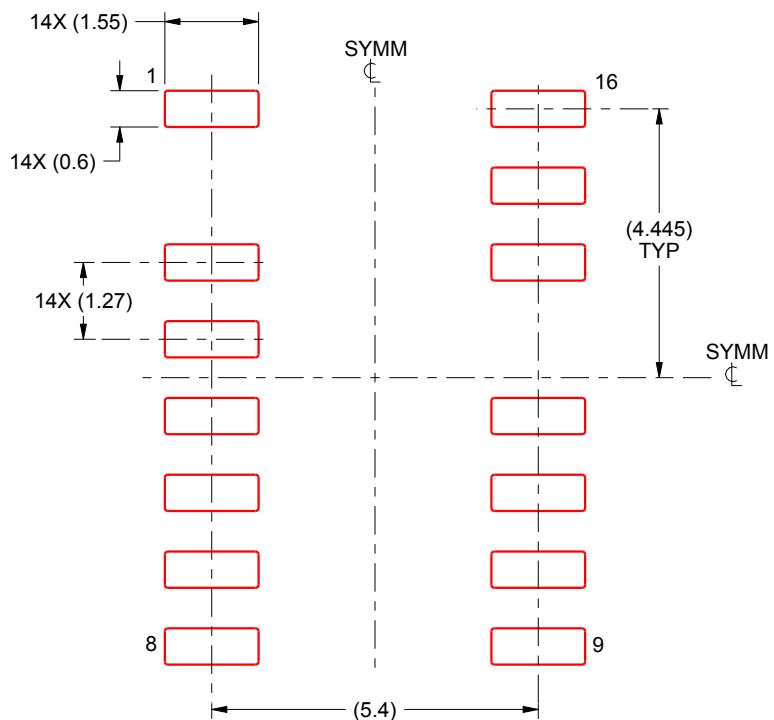

## 5 ピン構成および機能

**DDB/パッケージ

16ピンSOIC

上面図**

**ピン機能**

| ピン    |    | I/O | 説明                                                                                                                                                                    |

|-------|----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名前    | 番号 |     |                                                                                                                                                                       |

| BLK   | 4  | I   | このピンを使用してPFC出力電圧レベルを検知します。分圧抵抗を使用して信号を減衰してから、このピンに印加する必要があります。このピンの電圧レベルによって、LLCコンバータがスイッチングを開始/停止するタイミングが決まります。また、検知したBLK電圧に基づいてバースト・モード閾値を調整し、入力電圧範囲全体にわたって効率を高めます。 |

| BW    | 8  | I   | このピンを使用して、バイアス巻線により出力電圧を検知します。検知した電圧を用いて、出力過電圧保護を実現します。                                                                                                               |

| FB    | 5  | I   | LLC段制御帰還入力。このピンから供給される電流の量で、LLC入力電力レベルが決まります。                                                                                                                         |

| GND   | 11 | G   | 全信号の接地基準電圧。                                                                                                                                                           |

| HB    | 14 | I   | 1次側ゲート・ドライブのフローティング電源電圧。ブーストストラップ容量をこのピンとピンHSの間に接続します。2次側MOSFETの導通中に1次側MOSFETドライバに電力を供給するため、RVCCからこのピンへ高電圧・高速ダイオードを接続する必要があります。                                       |

| HO    | 15 | O   | 1次側フローティング・ゲート・ドライブ出力。                                                                                                                                                |

| HS    | 16 | I   | 1次側ゲート・ドライブのフローティング・グランド。1次側ゲート・ドライブ電流用の電流リターン。                                                                                                                       |

| HV    | 1  | I   | 内部HV起動JFETに接続します。このピンはPFC段とLLC段の両方に起動電力を供給します。また、このピンはXコンデンサ放電機能用のAC入力電圧も監視します。                                                                                       |

| ISNS  | 6  | I   | 共振電流検知。共振容量電圧を1次フィルタで微分して、共振電流を測定します。                                                                                                                                 |

| LL/SS | 9  | I   | このピンからGNDへ接続される容量値により、ソフトスタート期間が設定されます。また、このピンを使用してバースト・モード閾値を調整します。このピンの分圧抵抗が、BLKピン電圧により、バースト・モード閾値と閾値倍率を調整します。                                                      |

| LO    | 10 | O   | 2次側ゲート・ドライブ出力。                                                                                                                                                        |

| N/A   | 2  | N/A | 沿面距離と空間距離                                                                                                                                                             |

| N/A   | 13 | N/A | 沿面距離と空間距離                                                                                                                                                             |

| RVCC  | 12 | P   | RVCC 12V電源。このピンを使用して、ゲート・ドライバとPFCコントローラに電力を供給します。                                                                                                                     |

| VCC   | 3  | P   | 電源入力。                                                                                                                                                                 |

| VCR   | 7  | I   | 共振容量電圧検知                                                                                                                                                              |

## 6 仕様

### 6.1 絶対最大定格

動作自由空間温度範囲全体で(特に記述のない限り)、すべての電圧値はGNDを基準にしています。電流は指定されたピンに流れ込む方向が正、ピンから流れ出る方向が負です。<sup>(1)</sup>

|                                       |                | 最小        | MAX        | UNIT |

|---------------------------------------|----------------|-----------|------------|------|

| Input voltage                         | HV, HB         | - 0.3     | 640        | V    |

|                                       | BLK, FB, LL/SS | -0.3      | 7          | V    |

|                                       | VCR            | -0.3      | 7          | V    |

|                                       | HB - HS        | - 0.3     | 17         | V    |

|                                       | VCC            | -0.3      | 30         | V    |

|                                       | BW、ISNS        | - 5       | 7          | V    |

| RVCC出力電圧                              | DC             | - 0.3     | 17         | V    |

| HO出力電圧                                | DC             | HS - 0.3  | HB + 0.3   | V    |

|                                       | 過渡応答、100ns未満   | HS - 2    | HB + 0.3   |      |

| LO出力電圧                                | DC             | - 0.3     | RVCC + 0.3 | V    |

|                                       | 過渡応答、100ns未満   | - 2       | RVCC + 0.3 |      |

| フローティング・グランド・スルーレート <sub>HS</sub> /dt |                | -50       | 50         | V/ns |

| HO、LOパルス電流、I <sub>OUT_PULSED</sub>    |                | - 0.6     | 1.2        | A    |

| 接合部温度範囲、T <sub>J</sub>                |                | - 40      | 125        | °C   |

| 保管温度範囲、T <sub>stg</sub>               |                | -65       | 150        |      |

| Lead temperature                      |                | ハンダ付け、10秒 | 300        |      |

| Reflow                                |                |           | 260        |      |

(1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を超える状態で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

### 6.2 ESD定格

|                    |       | 値                                                                                        | 単位 |

|--------------------|-------|------------------------------------------------------------------------------------------|----|

| V <sub>(ESD)</sub> | 静電気放電 | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all HV pins <sup>(1)</sup>           | V  |

|                    |       | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all other pins <sup>(1)</sup>        |    |

|                    |       | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> |    |

(1) JEDECのドキュメントJEP155に、500V HBMでは標準のESD管理プロセスで安全な製造が可能であると規定されています。

(2) JEDECのドキュメントJEP157に、250V CDMでは標準のESD管理プロセスで安全な製造が可能であると規定されています。

### 6.3 推奨動作条件

特に記述のない限り、すべての電圧値はGNDを基準にしており、-40°C < T<sub>J</sub> = T<sub>A</sub> < 125°Cです。電流は指定されたピンに流れ込む方向が正、ピンから流れ出る方向が負です。

|                        | 最小                         | 標準  | 最大  | 単位 |

|------------------------|----------------------------|-----|-----|----|

| V <sub>IN</sub>        | 入力電圧、HV、HS                 |     | 600 | V  |

| V <sub>CC</sub>        | 電源電圧                       | 13  | 15  | 26 |

| V <sub>BOOT</sub>      | ドライバ・ブートストラップ電圧、HB - HS    | 10  | 12  | 16 |

| C <sub>B</sub>         | HBからHSへのセラミック・バイパス容量       | 0.1 | 5   | μF |

| C <sub>RVCC</sub>      | RVCC端子デカップリング容量            | 4.7 |     | μF |

| I <sub>RVCC(max)</sub> | RVCCの最大出力電流 <sup>(1)</sup> |     | 100 | mA |

(1) 実製品の検査は行っていません。特性により保証されています。

## 推奨動作条件 (continued)

特に記述のない限り、すべての電圧値はGNDを基準にしており、 $-40^{\circ}\text{C} < T_J = T_A < 125^{\circ}\text{C}$ です。電流は指定されたピンに流れ込む方向が正、ピンから流れ出る方向が負です。

|              | 最小  | 標準 | 最大  | 単位 |

|--------------|-----|----|-----|----|

| $T_A$ 動作周囲温度 | -40 |    | 125 | °C |

## 6.4 熱特性

| 熱特性 <sup>(1)</sup>                            | UCC256301 | 単位   |

|-----------------------------------------------|-----------|------|

|                                               | D (SOIC)  |      |

|                                               | 14ピン      |      |

| $R_{\theta JA}$ 接合部から周囲温度への熱抵抗                | 74.7      | °C/W |

| $R_{\theta JC(\text{top})}$ 接合部からケース(上面)への熱抵抗 | 30.7      | °C/W |

| $R_{\theta JB}$ 接合部から基板への熱抵抗                  | 31.8      | °C/W |

| $\Psi_{JT}$ 接合部から上面への熱特性                      | 4.4       | °C/W |

| $\Psi_{JB}$ 接合部から基板への熱特性                      | 31.4      | °C/W |

(1) 従来および新しい熱測定値の詳細については、アプリケーション・レポート『半導体およびICパッケージの熱測定値』、SPRA953を参照してください。

## 6.5 電気的特性

特に記述のない限り、すべての電圧値はGNDを基準にしており、 $-40^{\circ}\text{C} < T_J = T_A < 125^{\circ}\text{C}$ 、 $V_{CC} = 15\text{V}$ です。電流は指定されたピンに流れ込む方向が正、ピンから流れ出る方向が負です。

| PARAMETER                  | TEST CONDITIONS                            | MIN                             | TYP   | MAX   | UNIT  |

|----------------------------|--------------------------------------------|---------------------------------|-------|-------|-------|

| <b>電源電圧</b>                |                                            |                                 |       |       |       |

| $V_{CC\text{Short}}$       | この閾値を下回ると、低減起動電流を使用                        |                                 | 0.5   | 0.6   | 0.7   |

| $V_{CC\text{ReStartJfet}}$ | この閾値を下回ると、JFETを再度オンにする。                    |                                 | 10.2  | 10.5  | 10.8  |

| $V_{CC\text{StartSelf}}$   | 自己バイアス・モードで、このレベルを上回るとゲートがスイッチングを開始        |                                 | 25    | 26    | 28    |

| $V_{CC\text{Latch}}$       | ラッチ状態におけるVCC電圧                             |                                 | 13.5  | 14.3  | 15.0  |

| <b>消費電流</b>                |                                            |                                 |       |       |       |

| $I_{CC\text{Sleep}}$       | バースト・オフ期間にVCCレールから引き出される電流                 | $V_{CC} = 15\text{V}$           | 475   | 565   | 700   |

| $I_{CC\text{Run}}$         | ゲートがスイッチング動作中にVCC端子から引き出される電流。ゲート電流を除く     | $V_{CC} = 15\text{V}$ 、最大デッドタイム | 1.75  | 2.2   | 2.65  |

| $I_{CC\text{Latch}}$       | ラッチ状態でVCC端子から引き出される電流                      | $V_{CC} = 15\text{V}$           | 150   | 330   | 777   |

| <b>電圧が制御された電源</b>          |                                            |                                 |       |       |       |

| $V_{RVCC}$                 | 電圧が制御された電源電圧                               | $V_{CC} = 15\text{V}$           | 11.60 | 12    | 12.40 |

|                            |                                            | $V_{CC} = 13\text{V}$           | 11.2  | 11.8  | 12.25 |

| $V_{RVCCUVLO}$             | RVCC低電圧誤動作防止電圧 <sup>(1)</sup>              |                                 |       | 7     | ✓     |

| <b>高電圧起動</b>               |                                            |                                 |       |       |       |

| $I_{HVLow}$                | 低減起動ピン電流                                   |                                 | 0.28  | 0.41  | 0.54  |

| $I_{HVIHigh}$              | フル起動ピン電流                                   |                                 | 7.6   | 10.20 | 12.6  |

| $I_{HVLeak}$               | HV電流源漏れ電流                                  |                                 | 1.40  | 3.37  | 7.55  |

| $I_{HVZCD}$                | 最も高いACゼロクロス検出テスト電流                         |                                 | 0.63  | 0.77  | 0.89  |

| $I_{XCAPDischarge}$        | Xコンデンサ放電電流                                 |                                 | 9.6   | 11.47 | 13.5  |

| $t_{XCAPZCD}$              | 最初の3つのテスト電流段のACゼロクロス検出期間の長さ <sup>(1)</sup> |                                 | 10    | 11.85 | 14    |

|                            |                                            |                                 |       |       | ms    |

(1) 実製品の検査は行っていません。特性により保証されています。

## 電気的特性 (continued)

特に記述のない限り、すべての電圧値はGNDを基準にしており、 $-40^{\circ}\text{C} < T_J = T_A < 125^{\circ}\text{C}$ 、VCC = 15Vです。電流は指定されたピンに流れ込む方向が正、ピンから流れ出る方向が負です。

| PARAMETER           | TEST CONDITIONS                                        | MIN        | TYP   | MAX   | UNIT  |     |

|---------------------|--------------------------------------------------------|------------|-------|-------|-------|-----|

| $t_{XCAPZCDLast}$   | 最終テスト電流段のACゼロクロス検出期間の長さ <sup>(1)</sup>                 | 43         | 46    | 52    | ms    |     |

| $t_{XCAPIdle}$      | ACゼロクロス検出アイドル期間の長さ <sup>(1)</sup>                      | 635        | 704   | 772   | ms    |     |

| $t_{XCAPDischarge}$ | Xコンデンサ放電電流アクティブの時間 <sup>(1)</sup>                      | 327        | 358   | 390   | ms    |     |

| <b>バルク電圧検知</b>      |                                                        |            |       |       |       |     |

| $V_{BLKStart}$      | LLCがスイッチングを開始できる入力電圧                                   | 電圧立ち上がり    | 2.969 | 3.05  | 3.095 | V   |

| $V_{BLKStop}$       | LLCの動作を停止させる入力電圧                                       | 電圧立ち下がり    | 0.85  | 0.87  | 0.93  | V   |

| $V_{BLKOVRIse}$     | スイッチングを停止させる入力電圧                                       | 電圧立ち上がり    | 3.94  | 4.03  | 4.11  | V   |

| $V_{BLKOVFall}$     | スイッチングをリストートさせる入力電圧                                    | 電圧立ち下がり    | 3.64  | 3.76  | 3.86  | V   |

| <b>帰還ピン</b>         |                                                        |            |       |       |       |     |

| $R_{FBInternal}$    | 内蔵プルダウン抵抗値                                             |            | 90.7  | 101.5 | 112.3 | kΩ  |

| $I_{FB}$            | FB内部電流源                                                |            | 76.5  | 85.1  | 93.6  | μA  |

| $f_{-3dB}$          | 帰還信号経路 - 3dBカットオフ周波数 <sup>(2)</sup>                    |            | 1     |       |       | MHz |

| <b>共振電流検知</b>       |                                                        |            |       |       |       |     |

| $V_{ISNS\_OCP1}$    | OCP1閾値                                                 |            | 3.97  | 4.03  | 4.07  | V   |

| $V_{ISNS\_OCP1\_S}$ | ソフトスタート時のOCP1閾値 <sup>(1)</sup>                         |            | 5     |       |       | V   |

| $V_{ISNS\_OCP2}$    | OCP2閾値                                                 |            | 0.68  | 0.84  | 0.99  | V   |

| $V_{ISNS\_OCP3}$    | OCP3閾値                                                 |            | 0.49  | 0.64  | 0.79  | V   |

| $T_{ISNS\_OCP2}$    | OCP2が検出される前に平均入力電流がOCP2閾値を上回ったままであるべき時間 <sup>(1)</sup> |            | 2     |       |       | ms  |

| $T_{ISNS\_OCP3}$    | OCP3が検出される前に平均入力電流がOCP3閾値を上回ったままであるべき時間 <sup>(1)</sup> |            | 50    |       |       | ms  |

| $V_{IpolarityHyst}$ | 共振電流極性検出ヒステリシス                                         |            | 16.9  | 30.7  | 44.7  | mV  |

| $n_{OCP1}$          | OCP1異常が検出される前のOCP1サイクル数 <sup>(1)</sup>                 |            | 4     |       |       |     |

| <b>共振容量電圧検知</b>     |                                                        |            |       |       |       |     |

| $V_{CM}$            | 内部同相電圧                                                 |            | 2.91  | 3.02  | 3.14  | V   |

| $I_{RAMP}$          | 周波数補償ランプ電流源の値                                          |            | 1.63  | 1.84  | 2.10  | mA  |

| $I_{Mismatch}$      | プルアップおよびプルダウン・ランプ電流源の不整合 <sup>(3)</sup>                |            | -1.25 |       | 1.25  | %   |

| <b>ソフトスタート</b>      |                                                        |            |       |       |       |     |

| $I_{SSUp}$          | ソフトスタート容量を充電するためのSSピンからの電流出力                           |            | 21.8  | 25.8  | 29.8  | μA  |

| $R_{SSDown}$        | SSピン・プルダウン抵抗                                           | ZCSまたはOCP1 | 222   | 401   | 580   | Ω   |

(2) 実製品の検査は行っていません。設計により保証されています。

(3)  $I_{Mismatch}$ は $(I_{PD} - (I_{PD} + I_{PU}) / ((I_{PD} + I_{PU}) / 2))$ と $(I_{PU} - (I_{PD} + I_{PU}) / ((I_{PD} + I_{PU}) / 2))$ の平均として計算

## 電気的特性 (continued)

特に記述のない限り、すべての電圧値はGNDを基準にしており、 $-40^{\circ}\text{C} < T_J = T_A < 125^{\circ}\text{C}$ 、VCC = 15Vです。電流は指定されたピンに流れ込む方向が正、ピンから流れ出る方向が負です。

| PARAMETER               | TEST CONDITIONS               | MIN                        | TYP     | MAX      | UNIT   |

|-------------------------|-------------------------------|----------------------------|---------|----------|--------|

| <b>ゲート・ドライバ</b>         |                               |                            |         |          |        |

| $V_{LOL}$               | LO出力低電圧                       | $I_{sink} = 20\text{mA}$   | 0.027   | 0.052    | 0.087  |

| $V_{RVCC} - V_{LOH}$    | LO出力高電圧                       | $I_{source} = 20\text{mA}$ | 0.113   | 0.178    | 0.263  |

| $V_{HOL} - V_{HS}$      | HO出力低電圧                       | $I_{sink} = 20\text{mA}$   | 0.027   | 0.053    | 0.087  |

| $V_{HB} - V_{HOH}$      | HO出力高電圧                       | $I_{source} = 20\text{mA}$ | 0.113   | 0.173    | 0.263  |

| $V_{HB-}$<br>HSUVLORise | 1次側ゲート・ドライバUVLO立ち上がり閾値        |                            | 7.35    | 7.94     | 8.70   |

| $V_{HB-}$<br>HSUVLOFall | 1次側ゲート・ドライバUVLO立ち下がり閾値        |                            | 6.65    | 7.25     | 7.76   |

| $I_{source\_pk}$        | HO、LOピーク・ソース電流 <sup>(2)</sup> |                            | - 0.6   |          | A      |

| $I_{sink\_pk}$          | HO、LOピーク・シンク電流 <sup>(2)</sup> |                            | 1.2     |          | A      |

| <b>ブートストラップ</b>         |                               |                            |         |          |        |

| $I_{BOOT\_QUIESC\_ENT}$ | (HB - HS)待機時消費電流              | HB - HS = 12V              | 51.10   | 74.40    | 97.70  |

| $I_{BOOT\_LEAK}$        | HBからGNDへの漏れ電流                 |                            | 0.02    | 0.40     | 5.40   |

| $t_{ChargeBoot}$        | 充電ブート状態の長さ                    |                            | 234     | 267      | 296    |

| <b>バイアス巻線</b>           |                               |                            |         |          |        |

| $V_{BWOVRise}$          | 出力電圧OVP                       |                            | - 4.1   | - 3.97   | - 3.86 |

| <b>バースト・モード</b>         |                               |                            |         |          |        |

| $R_{LL}$                | LL電圧スケーリング抵抗値                 |                            | 240     | 250      | 258    |

| <b>アダプティブデッドタイム</b>     |                               |                            |         |          |        |

| $dV_{HS}/dt$            | 検出可能なPSNスルーレート <sup>(1)</sup> |                            | $\pm 1$ | $\pm 50$ | V/ns   |

| <b>障害回復</b>             |                               |                            |         |          |        |

| $t_{PauseTimeOut}$      | 一時停止タイマ <sup>(1)</sup>        |                            | 1       |          | s      |

| <b>サーマル・シャットダウン</b>     |                               |                            |         |          |        |

| $T_{J\_r}$              | サーマル・シャットダウン温度 <sup>(1)</sup> | 温度立ち上がり                    | 125     | 140      | °C     |

## 6.6 スイッチング特性

特に記述のない限り、すべての電圧値はGNDを基準にしており、 $-40^{\circ}\text{C} < T_J = T_A < 125^{\circ}\text{C}$ 、VCC = 12Vです。電流は指定されたピンに流れ込む方向が正、ピンから流れ出る方向が負です。

| PARAMETER            | TEST CONDITIONS           | MIN             | TYP  | MAX | UNIT |

|----------------------|---------------------------|-----------------|------|-----|------|

| $t_{r(LO)}$          | 立ち上がり時間                   | 10% ~ 90%、1nF負荷 | 18   | 35  | 50   |

| $t_{f(LO)}$          | 立ち下がり時間                   | 10% ~ 90%、1nF負荷 | 15   | 25  | 50   |

| $t_{r(HO)}$          | 立ち上がり時間                   | 10% ~ 90%、1nF負荷 | 18   | 35  | 50   |

| $t_{f(HO)}$          | 立ち下がり時間                   | 10% ~ 90%、1nF負荷 | 15   | 25  | 50   |

| $t_{DT(min)}$        | 最小デッドタイム <sup>(1)</sup>   |                 | 100  |     | ns   |

| $t_{DT(max)}$<br>(1) | 最大デッドタイム(デッドタイム異常)        |                 | 150  |     | μs   |

| $t_{ON(min)}$        | 最小ゲート・オン時間 <sup>(1)</sup> |                 | 250  |     | ns   |

| $t_{ON(max)}$        | 最大ゲート・オン時間 <sup>(1)</sup> |                 | 14.5 |     | μs   |

(1) 実製品の検査は行っていません。設計により保証されています。

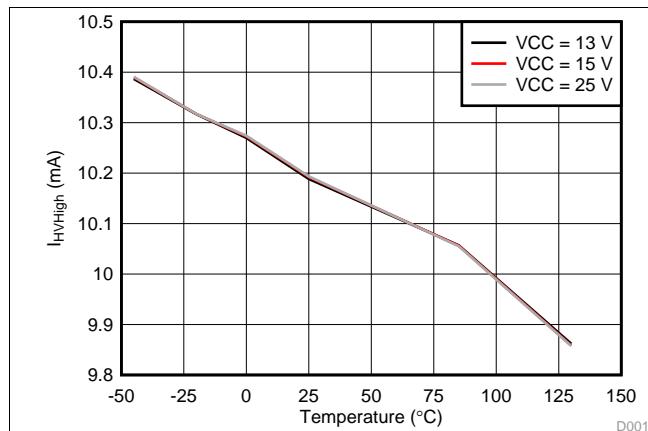

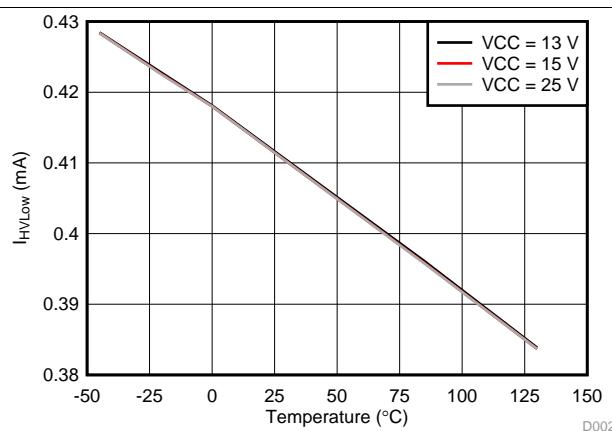

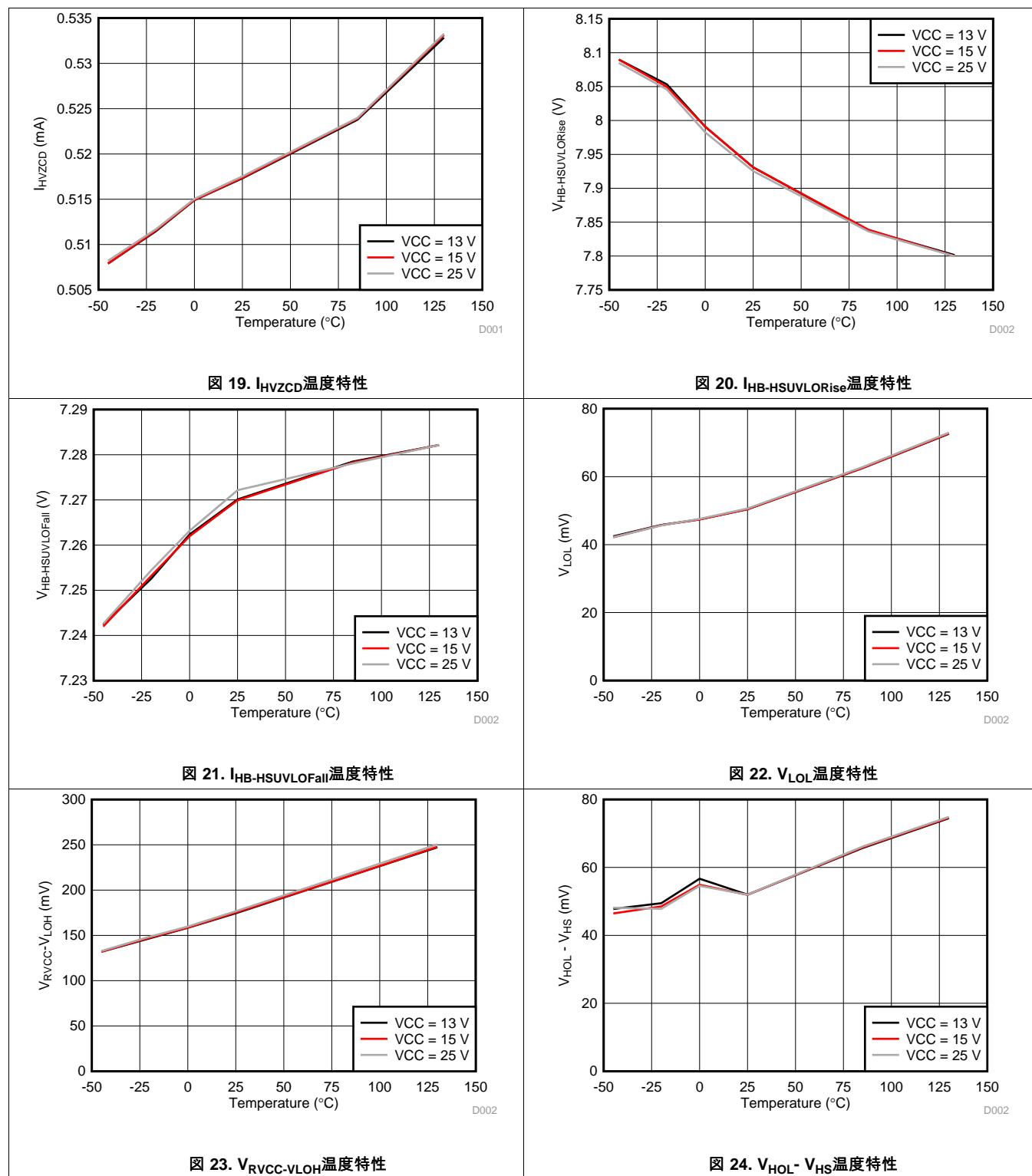

## 6.7 代表的特性

図 1.  $I_{HVHigh}$  温度特性

図 2.  $I_{HVLow}$  温度特性

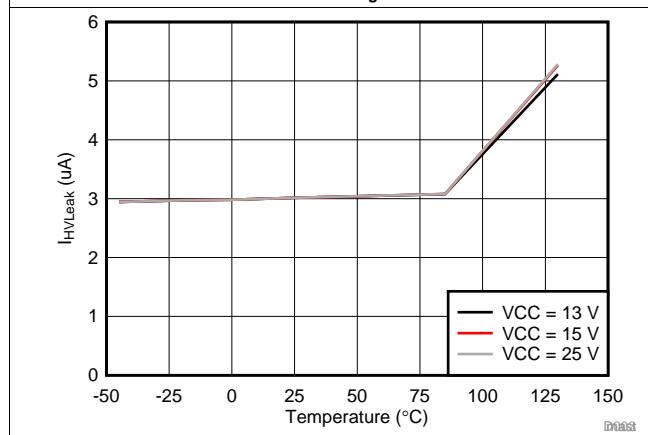

図 3.  $I_{HVLeak}$  温度特性

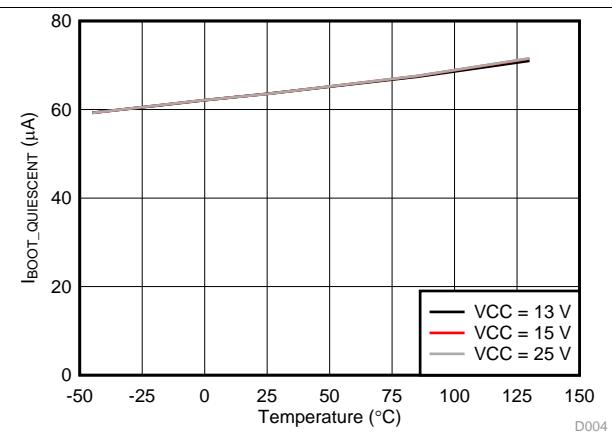

図 4.  $I_{BOOT\_QUIESCENT}$  温度特性

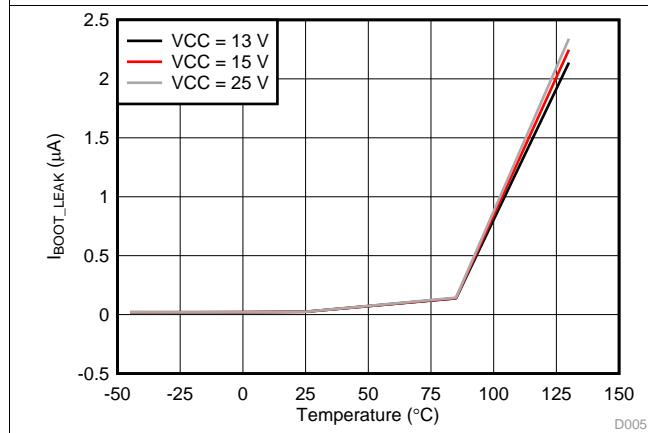

図 5.  $I_{BOOT\_LEAK}$  温度特性

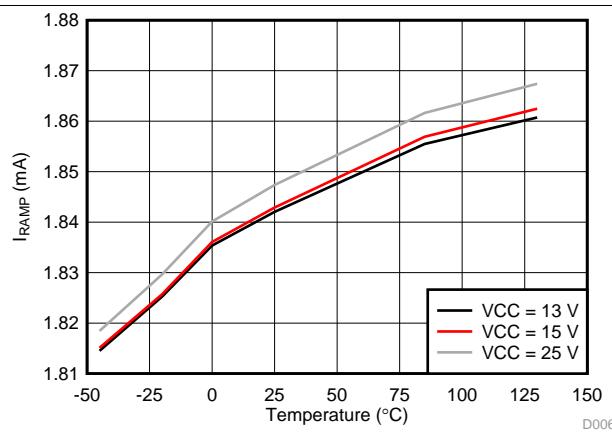

図 6.  $I_{RAMP}$  温度特性

### 代表的特性 (continued)

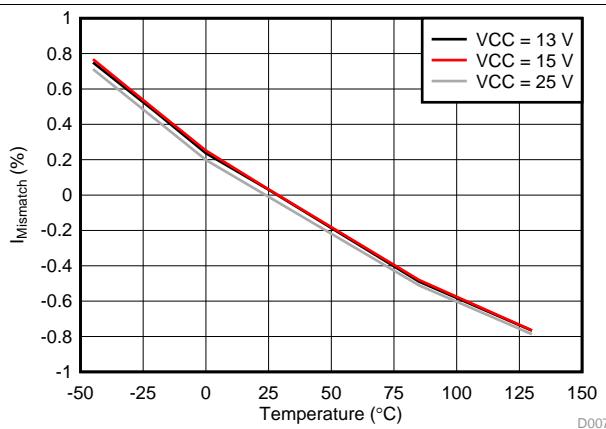

図 7.  $I_{MISMATCH}$  温度特性

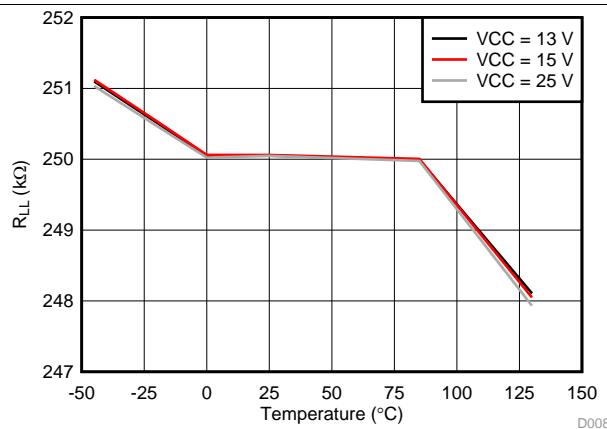

図 8.  $R_{LL}$  温度特性

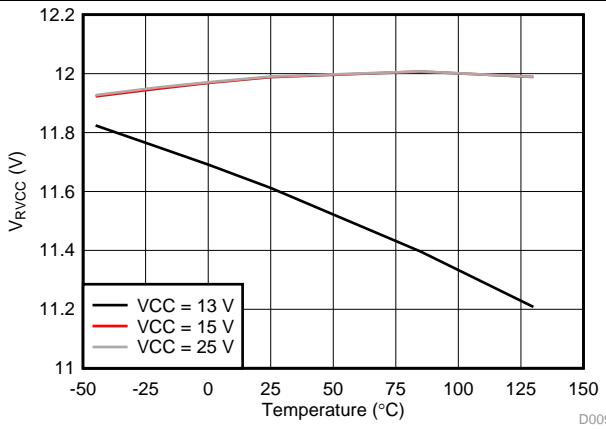

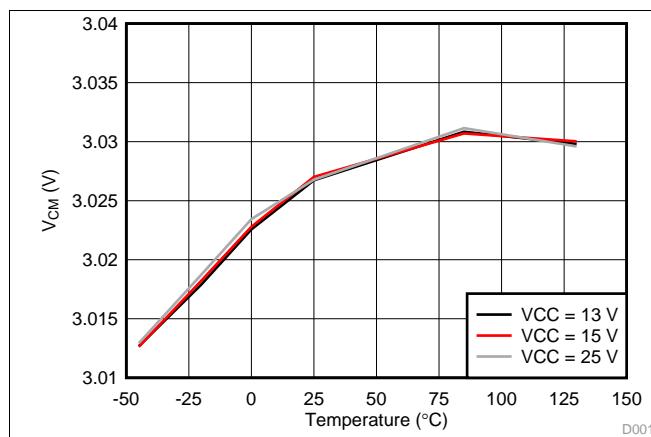

図 9.  $V_{RVCC}$  温度特性

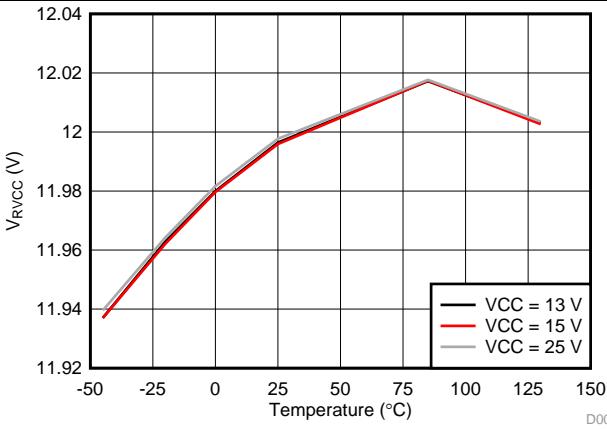

図 10.  $V_{RVCC}$  温度特性

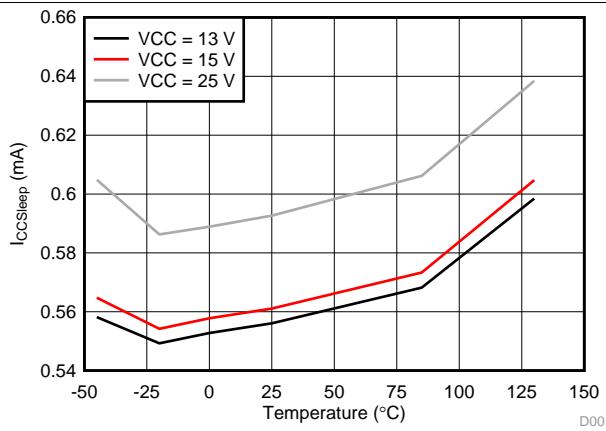

図 11.  $i_{CCSleep}$  温度特性

図 12.  $I_{CCRun}$  温度特性

**代表的特性 (continued)**

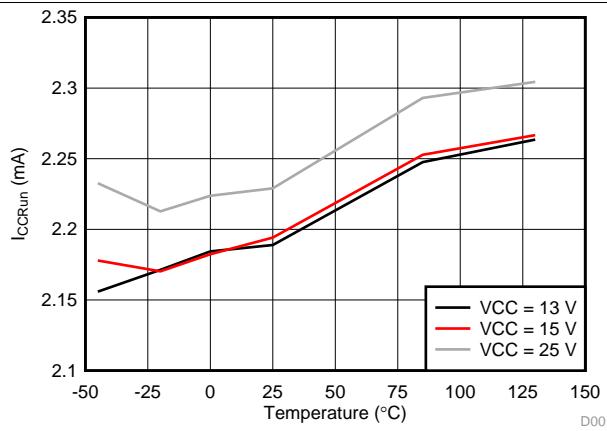

**図 13.  $V_{CM}$ 温度特性**

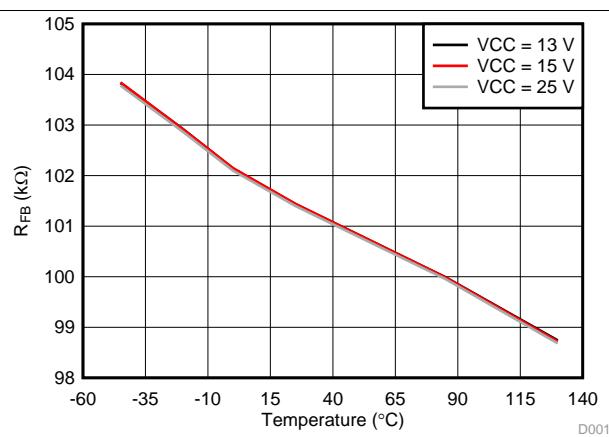

**図 14.  $R_{FB}$ 温度特性**

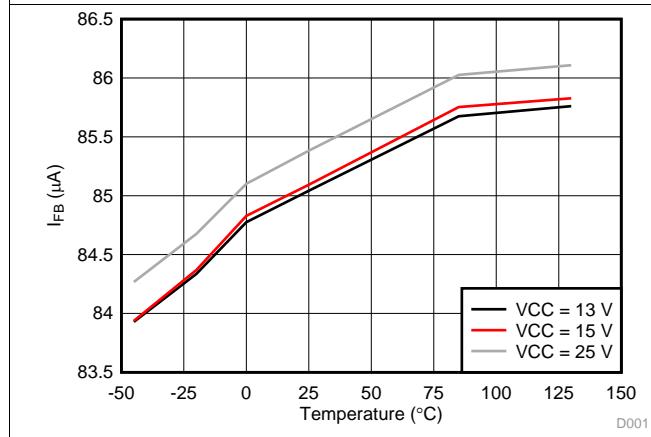

**図 15.  $I_{FB}$ 温度特性**

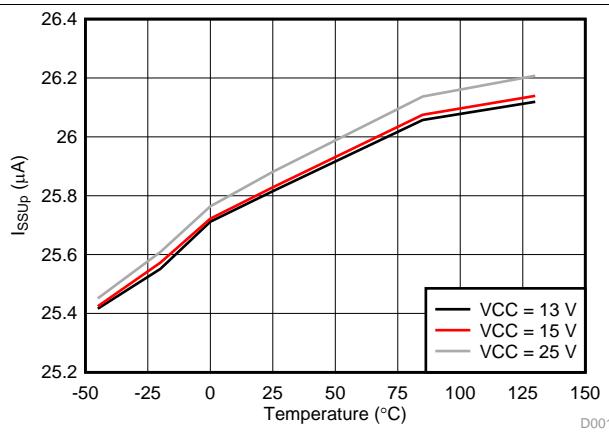

**図 16.  $I_{SSUp}$ 温度特性**

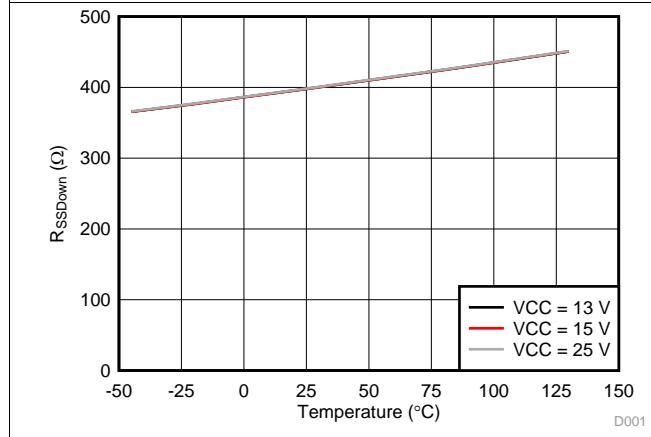

**図 17.  $R_{SSDown}$ 温度特性**

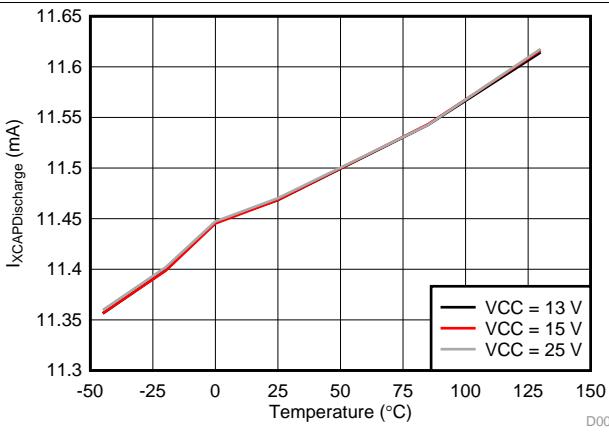

**図 18.  $I_{XCAPDischarge}$ 温度特性**

**代表的特性 (continued)**

代表的特性 (continued)

## 7 詳細説明

### 7.1 概要

高度に統合されたUCC256301では、機能を犠牲にすることなく、部品数を大幅に減らし小型化することができます。UCC256301は、バースト・モードにより、極めて低いスタンバイ消費電力を達成しています。また新しい制御方式により、優れた過渡応答性能を提供し、補償の簡素化を実現します。

大画面テレビやAC/DCアダプタ、サーバー電源、LEDドライバなど、消費電力が比較的高い多くの民生用途には、PFC + フライバック方式に比べて効率が高く、小型であることから、PFC + LLC電源が採用されています。PFC + LLC電源システムの欠点は、レギュレーションを維持するためにLLC段に最小限の循環電流が必要になるため、必然的に軽負荷時の効率が悪くなり、無負荷時消費電力も多くなることです。このため、軽負荷時効率と無負荷時消費電力の要件を満たすには、連続的に動作し、システムが低消費電力モードやスタンバイ・モードに移行した時点でメインのPFC + LLC電源システムを停止できる補助フライバック・コンバータを使用する必要があります。UCC256301 LLCコントローラは、高度な制御アルゴリズムと高効率のバースト・モードを備えたLLC電源システムを構築できるように設計されています。UCC256301には、高い軽負荷時効率と低い無負荷時消費電力を実現する、数多くの新機能が搭載されています。このため、補助フライバック・コンバータなしで、無負荷時消費電力の目標値150mWを達成する電源システムを設計することができます。UCC256301は、高電圧起動JFETを搭載しており、最初にVCC容量を充電してから、PFCおよびLLC電源システムの起動に必要な電力を供給します。動作した時点で、PFCおよびLLCコントローラ用の電力がLLC変圧器のバイアス巻線から引き出されます。

UCC256301は、新しい制御アルゴリズムであるハイブリッドヒステリシス制御(HHC)を採用することにより、レギュレーションを実現しています。この制御アルゴリズムでは、共振容量電圧によってスイッチング周波数が設定されるため、正確な入力電流情報を伝達できます。したがって、この制御動作では入力電流を直接制御できます。これにより、優れた負荷/入力電圧過渡応答と高効率のバースト・モードが実現します。また、従来の直接周波数制御(DFC)に比べて、HHCではシステムが1次システムに変わります。このため、補償設計がずっと簡単になり、ループ帯域を拡大することができます。

UCC256301には、ZCS動作領域を回避するための有効なアルゴリズムが内蔵されています。ZCSに近い動作が検出されると、UCC256301は帰還信号は無視され、動作が回復するまでスイッチング周波数を上げます。その後、スイッチング周波数はソフトスタート容量が決定した速度に戻され、制御は電圧制御ループに返されます。

UCC256301は、ハーフブリッジ・スイッチ・ノードを監視して、出入電力スイッチに必要なゲート信号のデッドタイムを決定します。このようにデッドタイムが自動的に調整され、動作効率およびセキュリティが最適化されます。UCC256301には、アダプティブデッドタイムのアルゴリズムが内蔵されているため、代替部品に比べて、その動作は本質的に安定したものとなります。

## 概要 (continued)

UCC256301には、1次側および2次側ドライバが搭載されていることから、LLC電力段を直接駆動して、最大1kWのピーク電力/500Wの連続電力を供給できます。これにより、最小限の部品で、十分な機能を備えた電源システムが実現します。

統合された高電圧JFETにより、電源システムはその出力電圧を、PFC段の入力時に表示される電源電圧の1/2以内に制御することができます。UCC256301は、LLC段とPFC段の両方に起動電力を供給します。動作した時点でJFETはオフになり、パッケージの消費電力を制限し、スタンバイ消費電力を削減します。

低出力電力レベル時には、UCC256301は自動的に軽負荷バースト・モードに移行します。バースト・オン期間中のLLC等価負荷電流レベルは、調整可能な値です。バーストからバーストまでのスペース期間は、FBピン電圧に基づき、2次電圧レギュレータ・ループによって終了します。バースト・モード中は、共振容量電圧を監視して、最初と最後のバースト・パルス幅が最高効率に最適化されるようにします。この方法により、代替部品に比べて、UCC256301では軽負荷時効率を高め、無負荷時消費電力を削減することができます。

また、オプトカプラを低消費電力モードで動作させることができたため、従来の方式に比べて、スタンバイ・モード時の消費電力を最大20mW削減することもできます。

UCC256301の追加保護機能には、3値の過電流保護、出力過電圧保護、入力電圧OVPおよびUVP、ゲート・ドライバUVLO保護、および過熱保護があります。

UCC256301の主な特長は以下のとおりです。

- 高電圧起動および高電圧ゲート・ドライバを内蔵

- ハイブリッドヒステリシス制御により、クラス最高の負荷/入力電圧過渡応答の実現を支援

- 最適化された軽負荷バースト・モードにより、スタンバイ消費電力150mWの設計を実現

- 容量性領域動作回避手法の改良

- アダプティブデッドタイム

- Xコンデンサ放電

- 広い動作周波数範囲(35kHz ~ 1MHz)

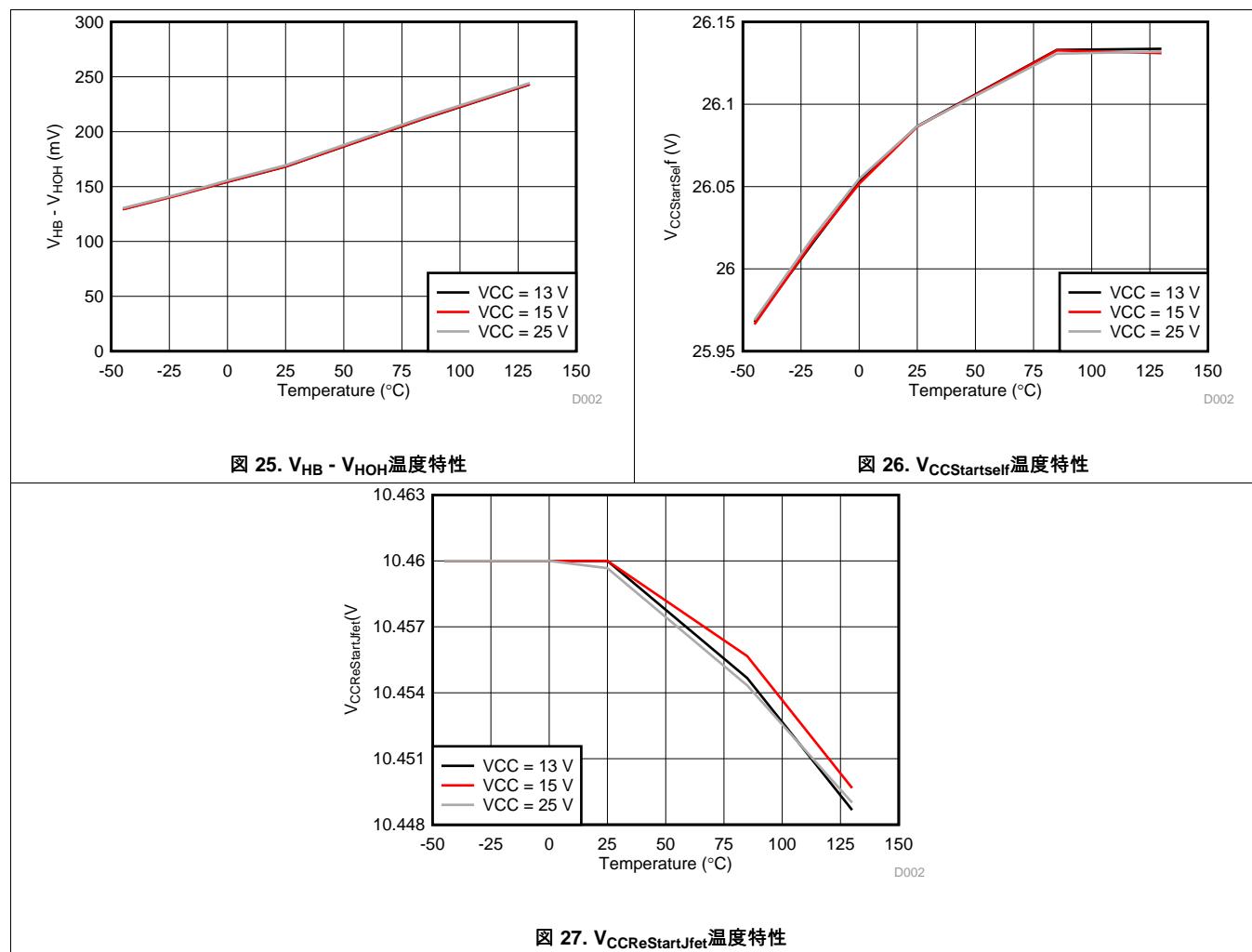

## 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 ハイブリッドヒステリシス制御

UCC256301は、新しい制御方式であるハイブリッドヒステリシス制御(HHC)を採用して、クラス最高の入力電圧/負荷過渡応答を実現しています。この制御方式により、補償を非常に設計しやすくなります。また、軽負荷管理もより簡単に効率よく行うことができます。入力電圧過渡応答特性の向上により、バルク容量/出力容量の値を低減し、システム・コストを削減できます。

HHCは、従来の周波数制御と電荷制御を組み合わせた制御方式であり、いわば周波数補償ランプを追加した電荷制御です。従来の周波数制御に比べて、電力段の伝達関数が2次系から1次系に変わるために、補償が非常に簡単です。この制御動作は入力電流に直接関係するため、入力電圧/負荷過渡応答はクラス最高のものとなります。電荷制御に比べて、ハイブリッドヒステリシス制御では、周波数補償ランプが追加されることにより、不安定な状態を回避できます。この周波数補償により、システムは常時安定し、出力インピーダンスも低減します。出力インピーダンスが低いため、電荷制御に比べて過渡応答性能は向上します。

要約すると、HHCによって解決される問題は次のとおりです。

- LCCコンバータによるクラス最高の負荷/入力電圧過渡応答の実現を支援

- 小信号伝達関数が1次系に変わるために、補償が非常に簡単であり、極めて広い帯域を確保できる

- 周波数補償により本質的に安定

- バースト・モード制御の高効率最適化がはるかに簡単になる

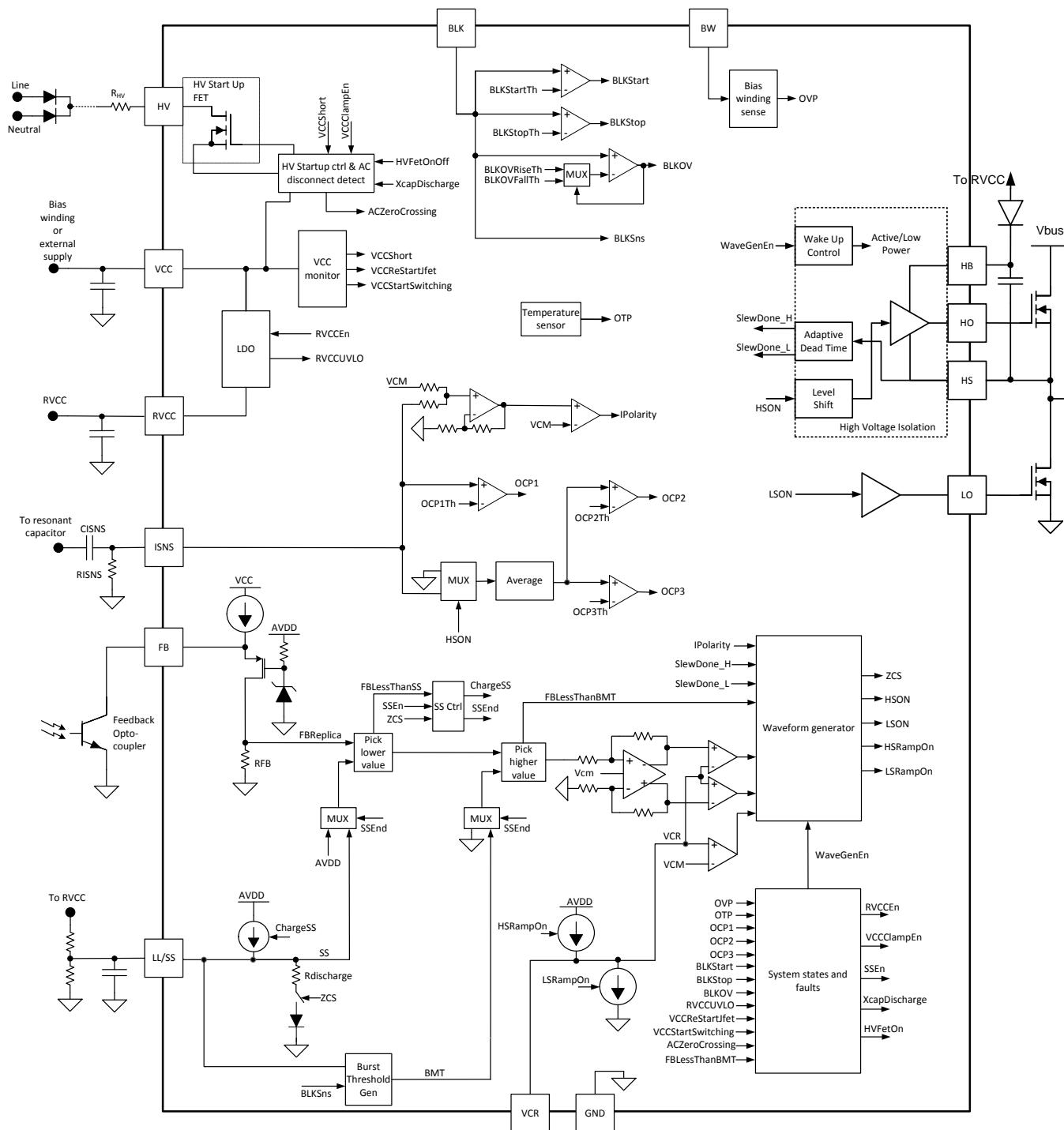

図 28 にUCC25630におけるHHCの実装一分圧容量(C1およびC2)と2つの整合する制御電流源を示します。

図 28. UCC256301におけるHHCの実装例

## 機能説明 (continued)

共振容量電圧は、C1およびC2からなる分圧容量によって分割されます。電流源はゲート・ドライブ信号によって制御されます。1次側スイッチがオンのときには、1次電流源をオンにして、定電流を分圧容量に注入し、2次側スイッチがオンのときには、2次電流源をオンにして、同量の定電流を分圧容量から引き出します。この2つの電流源が、三角波形を形成する補償ランプをV<sub>CR</sub>ノードに追加します。電流源は、基準電圧V<sub>ref</sub>により供給されます。この電圧は同相電圧V<sub>CM</sub>の2倍に等しいか、それを上回る必要があります。分割された共振容量電圧と補償ランプ電圧が、その後合わせてVCR電圧が得られます。周波数補償ランプが大半を占めれば、VCR電圧は三角波のように見え、制御は直接周波数制御と同様になります。共振容量電圧が大半を占めれば、VCR電圧の形状は実際の共振容量電圧のように見え、制御は電荷制御と同様になります。このため、この制御方式は「ハイブリッド」と呼ばれ、補償ランプは周波数補償と呼ばれています。

この方式には固有の負帰還があり、1次側と2次側を定時にバランスのとれた状態に保ち、またV<sub>CR</sub>ノードの同相電圧をV<sub>CM</sub>に維持できます。

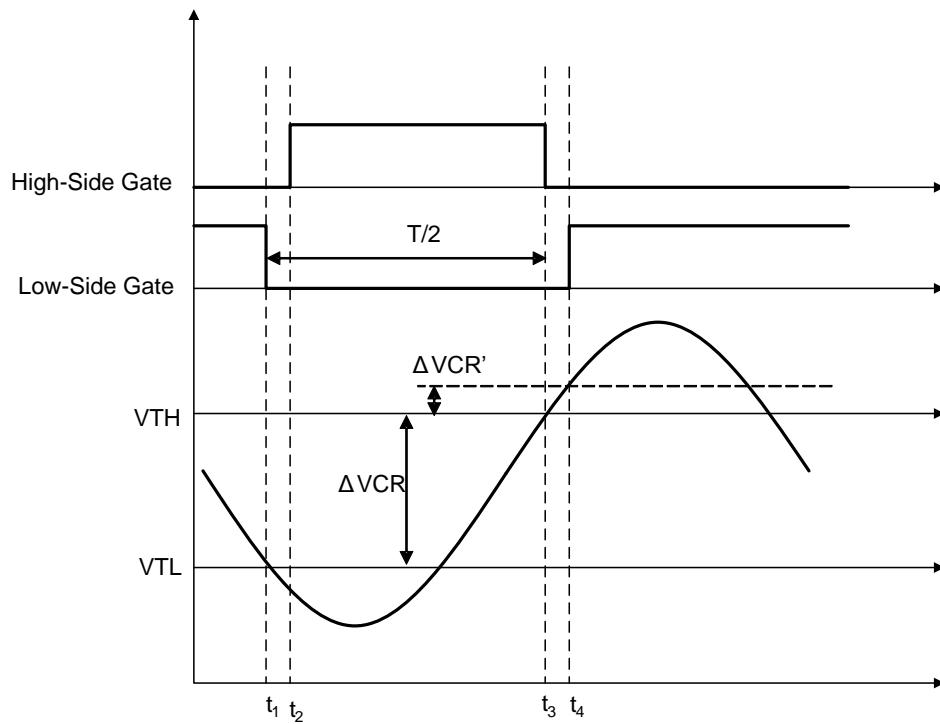

この新しい制御方式には、V<sub>CR</sub>とV<sub>COMP</sub>という2つの入力信号が必要です。V<sub>CR</sub>は、スケールダウンした共振容量電圧と周波数補償ランプの和です。V<sub>COMP</sub>は電圧ループ補償出力です。以下の波形は、VCRおよびV<sub>COMP</sub>に基づく1次側および2次側スイッチの制御を示しています。VCRの同相電圧はV<sub>CM</sub>です。

図 29. HHCのゲート・オン/オフ制御原理

V<sub>COMP</sub>とV<sub>CM</sub> (3V)に基づき、V<sub>thh</sub>とV<sub>thl</sub>という2つの閾値が作成されます。

$$V_{thh} = V_{CM} + \frac{V_{comp}}{2} \quad (1)$$

$$V_{thl} = V_{CM} - \frac{V_{comp}}{2} \quad (2)$$

VCR電圧をこの2つの閾値と比較します。VCR > V<sub>thh</sub>であれば1次側スイッチをオフにし、VCR < V<sub>thl</sub>であれば2次側スイッチをオフにします。HOおよびLOのオン・エッジは、アダプティブデッドタイム回路により制御されます。

## 機能説明 (continued)

### 7.3.2 RVCC 12V電源

RVCCピンは電圧が制御された12V電源であり、最大100mAの電流を供給できます。この電源で、PFCおよびLLCゲート・ドライバに給電します。RVCCは低電圧誤動作防止(UVLO)機能を備えています。通常動作中にRVCCの電圧がRVCCUVLOの閾値を下回ると、異常デバイスの機能モードとみなされ、システムはFAULT状態に入ります。FAULT処理については、「」節に詳述します。

### 7.3.3 帰還信号経路

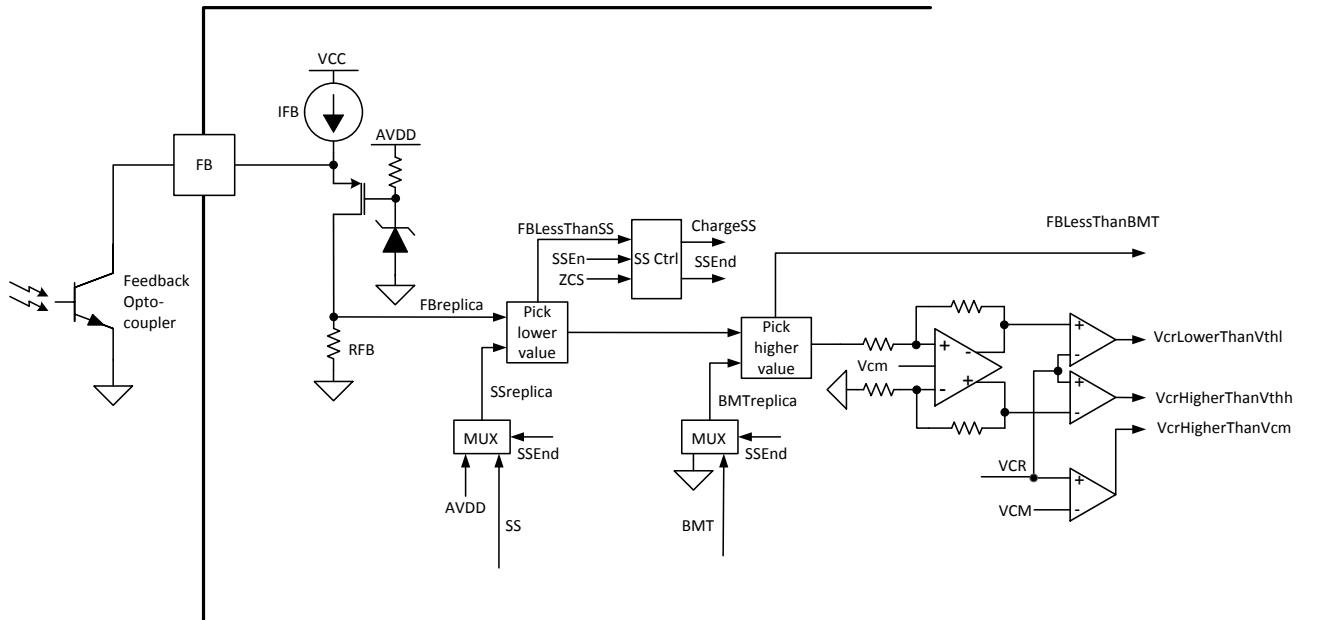

出力電圧の制御は、絶縁膜の2次側にある電圧レギュレータ回路により提供されます。2次レギュレータ回路からの要求信号は、オプトカプラーにより絶縁膜を通過して伝達され、UCC25630のFBピンに送り込まれます。この節に帰還信号経路の概要を述べます。

帰還信号経路には次の機能があります。

- オプトカプラーによる帰還信号入力およびバイアス

- システム外部停止機能

- ピック・ロワー・ブロックによるソフトスタート機能

- ピック・ハイヤー・ブロックによるバースト・モードの選択

- シングルエンドの帰還信号を2つの閾値 $V_{thh}$ と $V_{thl}$ に変換し、 $V_{CR}$ をこの閾値ならびに同相電圧 $V_{CM}$ と比較する

図 30. 帰還信号経路ブロック図

## 機能説明 (continued)

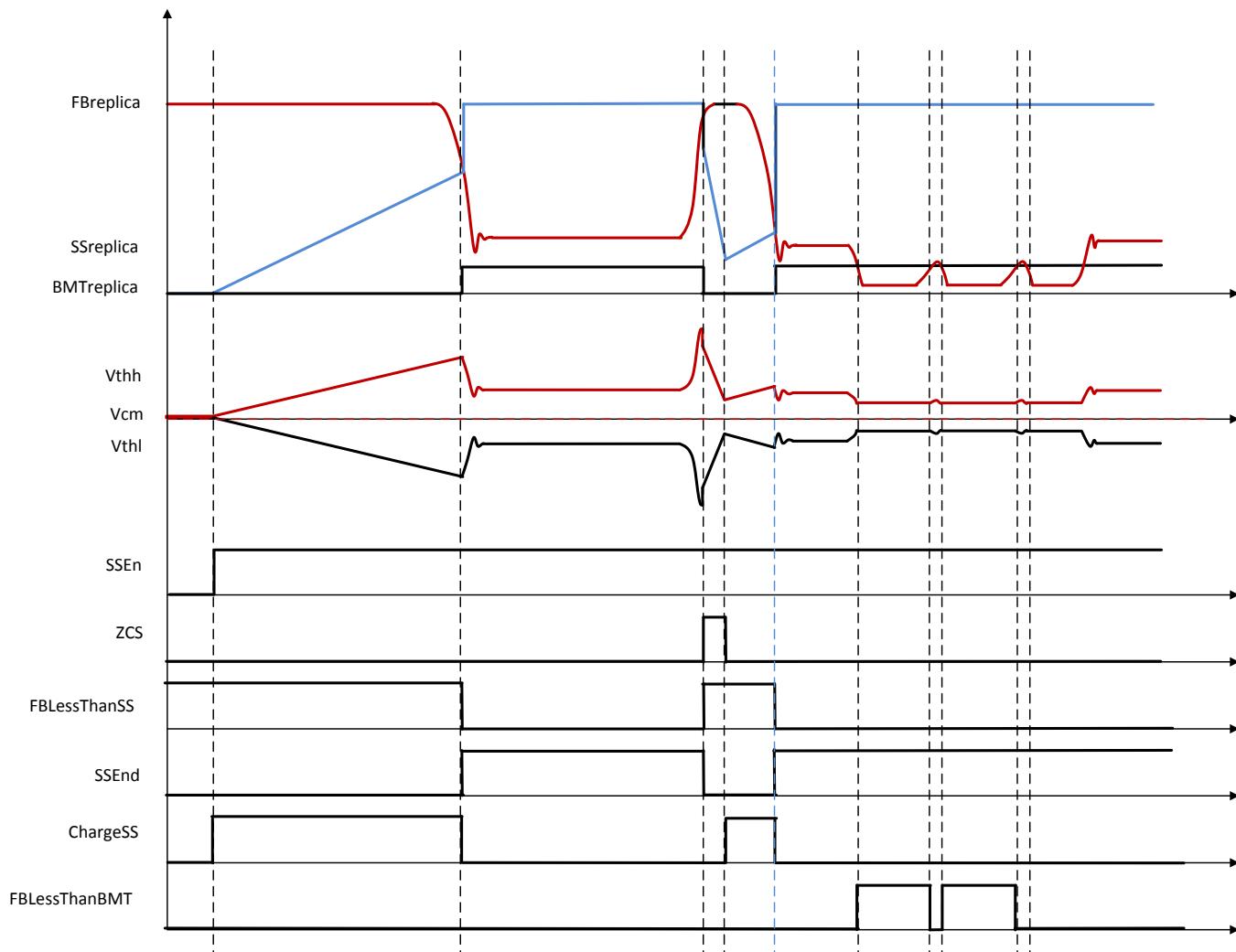

以下のタイミング・チャートは、FBチェーンの波形を示しています。このシーケンスは、ZCS事象が発生した後の通常のソフトスタートで、負荷はバースト・モードに入り、その後バースト・モードから脱しています。

図 31. 帰還信号経路タイミング・チャート

### 7.3.4 オプトカプラ帰還信号入力およびバイアス

2次レギュレータ回路とオプトカプラ帰還回路は、いずれもシステムの無負荷時消費電力を直接的に増大させます。無負荷時消費電力を極めて低く抑えるには、低電流モードでオプトカプラを駆動する必要があります。

図 31に示すとおり、定電流源IFBはVCC電圧から生じて、FBピンに接続されます。またPMOSを介して、抵抗RFBもこの電流源に接続されます。通常動作中は、PMOSは常時オンとなります。PMOSはFBreplicaの最大電圧を制限します。

$$I_{FB} = I_{opto} + I_{RFB} \quad (3)$$

この式から、 $I_{opto}$ が上昇すると、 $I_{RFB}$ が低下し、FBreplicaが低下することになります。このように制御動作は反転します。この回路は、 $I_{FB}$ となるオプトカプラの最大電流を制限することもできます。オプトカプラをバイアスする従来の方法は、オプトカプラ出力のコレクタでプルアップ抵抗を使用するものです。消費電力を削減するには、プルアップ抵抗を大きくして、ループ帯域を制限する必要があります。UCC25630に採用されているバイアス電流方式では、オプトカプラ電流が制限されるため、ループ帯域の問題はありません。

## 機能説明 (continued)

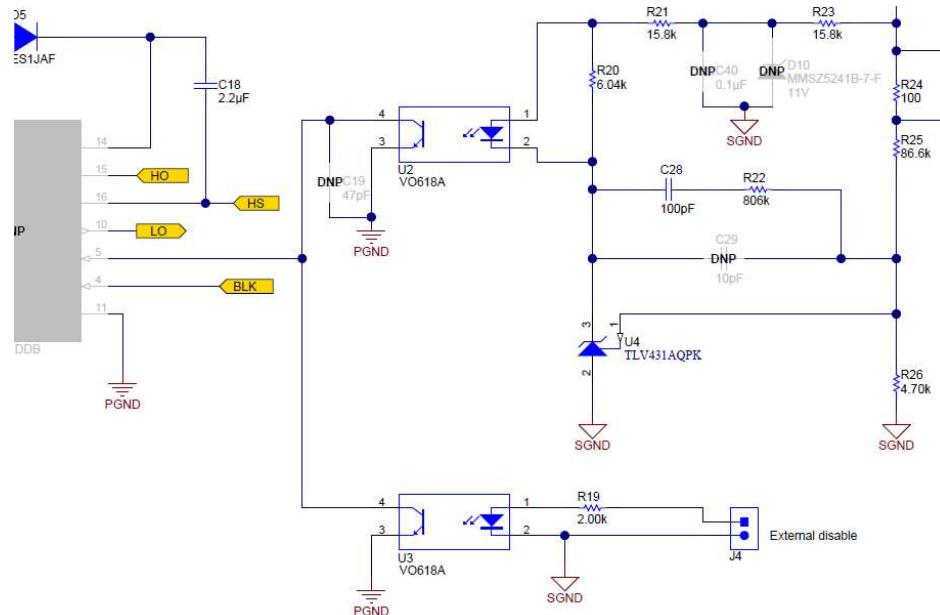

### 7.3.5 システム外部停止機能

これは、外部信号によってシステムを停止できる機能です。FBreplicaがバースト・モード閾値を下回ると、LLCスイッチングを停止します。FBLessThanBMTが200msを超えて真であれば、1秒間一時停止状態に移行し、リスタートを試みます。LLCがスイッチングを開始する前に、システムはFBLessThanBMTが真ではないことを確認する必要があります。FBreplicaが外部信号により絶えず低く保たれていれば、システムがリスタートすることはありません。

この機能は、システム・オン/オフ制御など、UCC25630には内蔵されていない異常検出時の停止機能に使用できます。この機能を実装するには、外部バイアス・オプトカプラが必要です。以下の回路図はその実装の一例です。

図 32. 外部部品を使用した停止回路例

## 機能説明 (continued)

### 7.3.6 ピック・ロワー・ブロックとソフトスタート・マルチプレクサ

回路のこの部分は、次の3つの要素で構成されています。

- ピック・ロワー・ブロック

- ピック・ロワー・ブロックへの2次入力としてAVDDまたはSS信号を選択するMUX

- ZCS異常の際にSS容量の充電/放電を処理するSS制御ブロック

ピック・ロワー・ブロックには2つの入力があります。1つ目の入力はFBreplicaです。もう1つの入力はAVDDピンとSSピンの電圧から選択されます。その他の出力は、この2つの入力のうち低いほうになります。

MUXはSSとAVDDから選択します。この選択は、SS Ctrlブロックの出力であるSSEn (ソフトスタート終了)信号に基づきます。SSがFBreplicaより高いとSSEnは高く、ソフトスタートがステートマシンによって起動されているため、ZCS状態はありません。ソフトスタートが終了した後AVDDにスイッチングすれば、ソフトスタートやZCS異常でない状態の間は、ピック・ロワー・ブロックから常にFBreplica信号が送信されていることを確認できます。また、SSピンを他の機能、すなわち軽負荷閾値の調整に使用することもできます。

SS制御ブロックは、ZCS異常発生時にSS容量の充電/放電を処理します。ZCSが発生するとSSEn信号がリセットされるため、スイッチング周波数を上げるためのSSピンのプルダウン効果がピック・ロワー・ブロックを通過できます。SS制御ブロックの入力と出力の関係は次のとおりです。

$$\text{SSEn} = \text{SSEn} \& (\text{!ZCS}) \& (\text{!FBLessThanSS}) \quad (4)$$

$$\text{ChargeSS} = \text{SSEn} \& (\text{!SSEn}) \& (\text{!ZCS}) \quad (5)$$

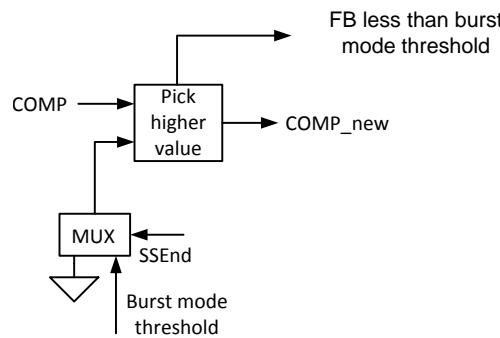

### 7.3.7 ピック・ハイヤー・ブロックとバースト・モード・マルチプレクサ

ピック・ロワー・ブロックの出力はピック・ハイヤー・ブロックに送り込まれ、ここでピック・ロワー・ブロックの出力とバースト・モード閾値設定のうち高いほうが選択されます。

バースト・モード・マルチプレクサはBMTとGNDから選択します。ソフトスタート時には、マルチプレクサはGNDを選択します。起動プロセスは開ループで、ソフトスタート・ランプによって制御されます。ソフトスタート中は、バースト・モードはオンになりません。

ソフトスタートの後、2つの入力のうち高いほうが差動アンプに入力されます。その他の出力はコンバレータ出力FBLessThanBMTです。これを波形発生器のステートマシンに入力して、バースト・モードとシステム外部停止機能を制御します。

### 7.3.8 VCRコンバレータ

ピック・ハイヤー・ブロックの出力は差動アンプに入力され、信号はVcmと対称をなす2つの閾値に変換されます。2つの閾値VthhとVthlの差は、入力振幅と等しくなります。それからVCRピン電圧をVthh、Vthl、およびVcmと比較します。その結果が波形発生器に入力されます。

## 機能説明 (continued)

### 7.3.9 共振容量電圧検知

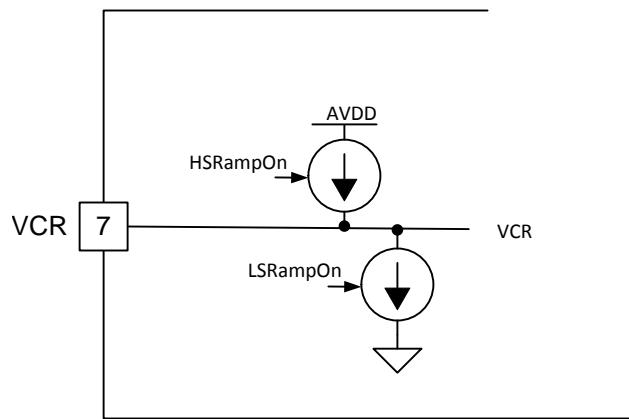

共振容量電圧検知ピンは、分圧容量を通じて共振容量電圧を検知します。デバイス内部で、2つの整合する制御電流源がVCRピンに接続されて、周波数補償ランプが生成されます。2つの電流源のオン/オフ制御信号は、波形発生器ブロックから発生します。

波形発生器のIDLE状態時や起動前には、VCRノードをV<sub>cm</sub>に短絡します。この操作により、起動時のピーク電流を削減し、バースト・モード中に素早くVCR電圧を安定させることができます。

図 33. VCRブロック図

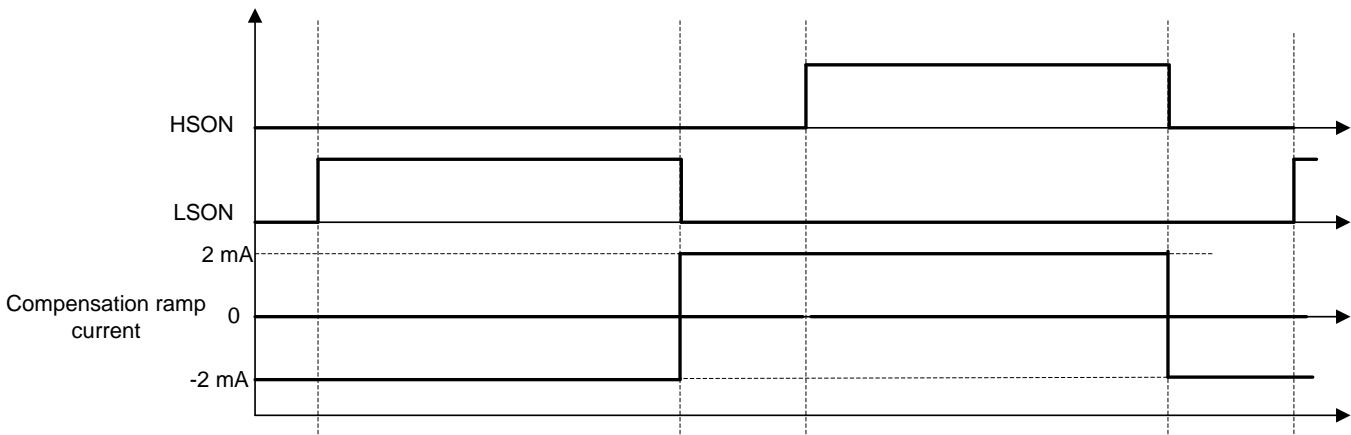

ランプ電流のオン/オフ・シーケンスを図 34に示します。ランプ電流は常時オンになっています。これにより、1次側オンまたは2次側オン信号の立ち下がりエッジで方向が変わります。

図 34. VCR補償ランプ電流のオン/オフ

VCRピンでは、分圧容量を使用して、共振容量の波形と補償ランプの波形を組み合わせます。外付け容量のサイズを調整することにより、電荷制御と直接周波数制御の分担量を変更できます。分圧容量によって分割された共振容量の電圧をV<sub>div</sub>とすると、補償ランプ電流から生じるVCRピンの電圧はV<sub>ramp</sub>となります。V<sub>div</sub>がV<sub>ramp</sub>よりもずっと大きい場合には、制御方式が電荷制御と同様になり、制御動作は1スイッチング・サイクルの入力電荷に比例します。V<sub>ramp</sub>がV<sub>div</sub>よりもずっと大きい場合には、制御方式が直接周波数制御と同様になり、制御動作はスイッチング周波数に比例します。V<sub>div</sub>とV<sub>ramp</sub>の比率を調整することによって、最適な過渡応答を実現できます。

## 機能説明 (continued)

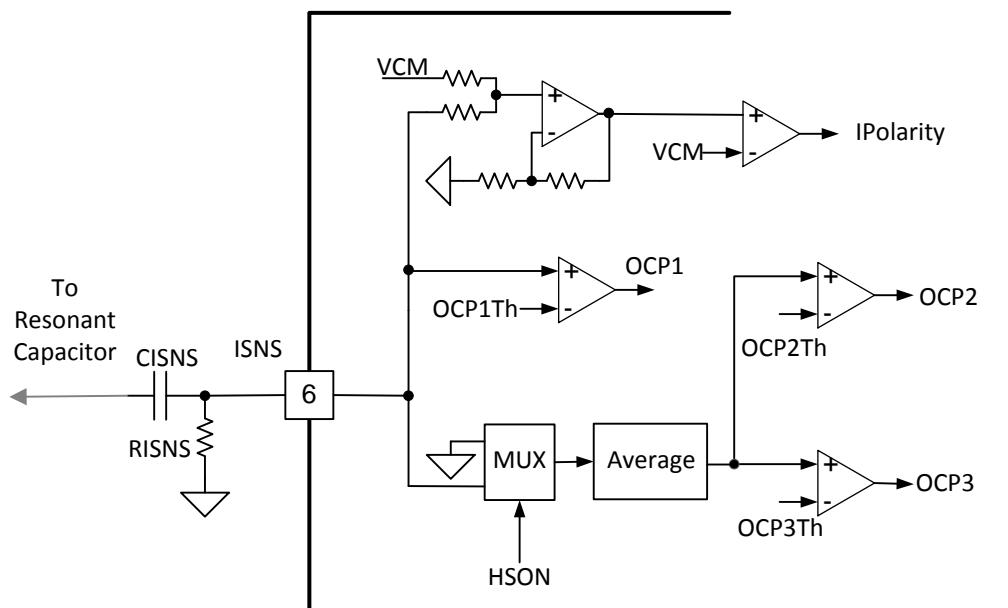

### 7.3.10 共振電流檢知

ISNSピンは、高電圧容量を使用して共振容量に接続されます。容量CISNSと抵抗RISNSが微分器を形成します。共振容量電圧を微分することにより、共振電流が得られます。この微分信号がACであり、正にも負にもなります。ゼロクロスを検知するために、オペアンプ加算器を使用して信号をレベル・シフトします。IPolarityコンパレータが共振電流の方向を検出します。デジタル・ステートマシンがIPolarityにブランкиング時間を実装し、デッドタイムの最初の400ns間のIPolarityエッジは無視されます。

OCP2の閾値とOCP3の閾値は、平均入力電流に基づいています。平均入力電流を導き出すには、微分器出力を1次側スイッチオン信号HS0Nで多重化します。HSがオンであればMUX出力は微分器出力となり、HSがオフであればMUX出力は0となります。それからローパス・フィルタを使用して、MUX出力を平均化します。フィルタの出力が、検知された平均入力電流となります。なお、MUXは正の電圧も負の電圧も通過する必要があります。OCP2異常とOCP3異常には、それぞれ2msと50msのタイマがあります。OCP2/OCP3コンパレータ出力が2msまたは50msの間、連続して高い場合にのみ、異常検知状態になります。

OCP1の閾値は、ピーク共振電流に設定されます。ISNSピンの電圧はOCP1の閾値OCP1Thと直接比較されます。正の半サイクルで、1サイクルにつき1回、ピーク共振電流を確認します。4サイクル連続でOCP1事象が検出された場合にのみ、OCP1異常検知状態になります。起動時には、最初の15サイクルのOCP1コンパレータ出力が無視されます。

図 35. ISNS ブロック図

## 機能説明 (continued)

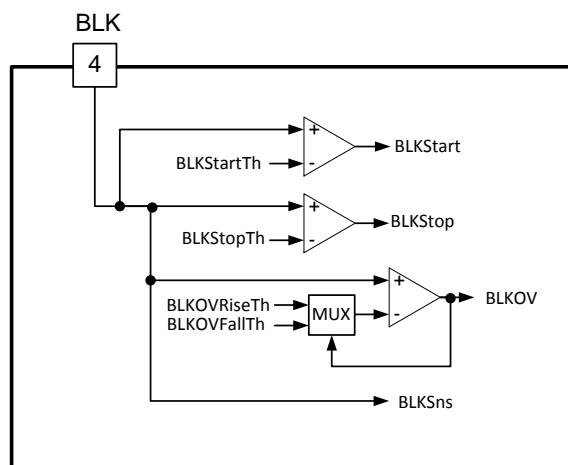

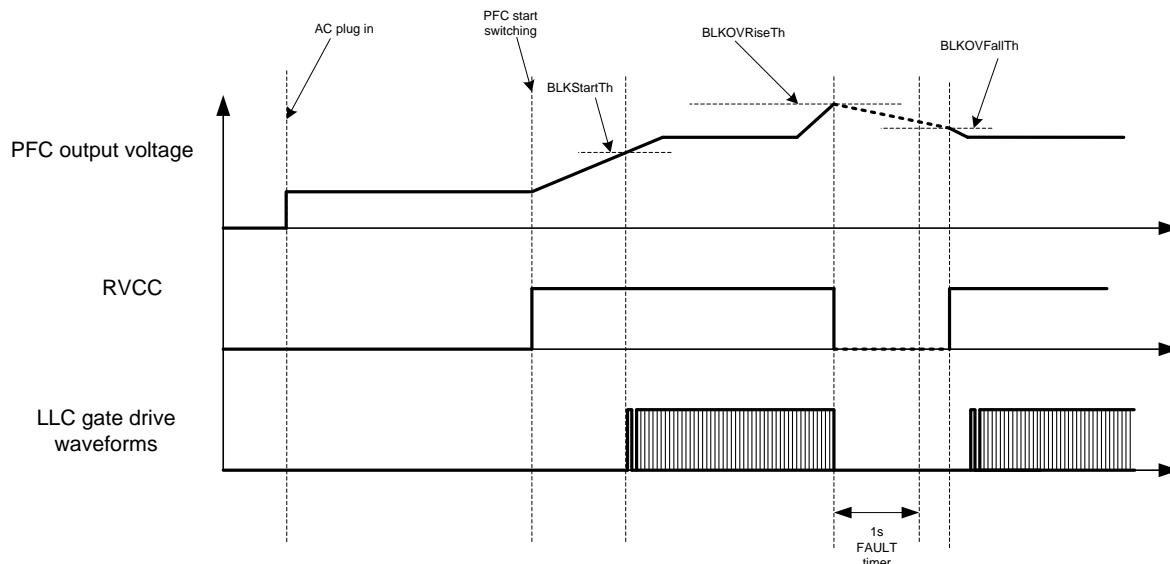

### 7.3.11 バルク電圧検知

BLKピンを使用して、LLC DC入力電圧(バルク電圧)レベルを検知します。BLKピンのコンパレータにより、次の閾値が設定されます。

- LLCがスイッチングを開始したときのバルク電圧レベル – BLKStartTh

- LLCがスイッチングを停止したときのバルク電圧レベル – BLKStopTh

- バルク過電圧異常が生成されたときのバルク電圧レベル – BLKOVRIseTh

- バルク過電圧異常が解消したときのバルク電圧レベル – BLKOVFallTh

1つのコンパレータからBLKOV信号が生成され、MUXにより2つの閾値が選択されます。これは、BLKOV異常に必要なヒステリシスを作成するためです。BLKSns信号をバッファし、バースト・モード閾値生成ブロックに入力することにより、適応型のバースト・モード閾値が実装されます。

図 36 にBLKピンのブロック図を示します。

図 36. VCR補償ランプ電流のオン/オフ

図 37. BLK動作のタイミング・チャート

## 機能説明 (continued)

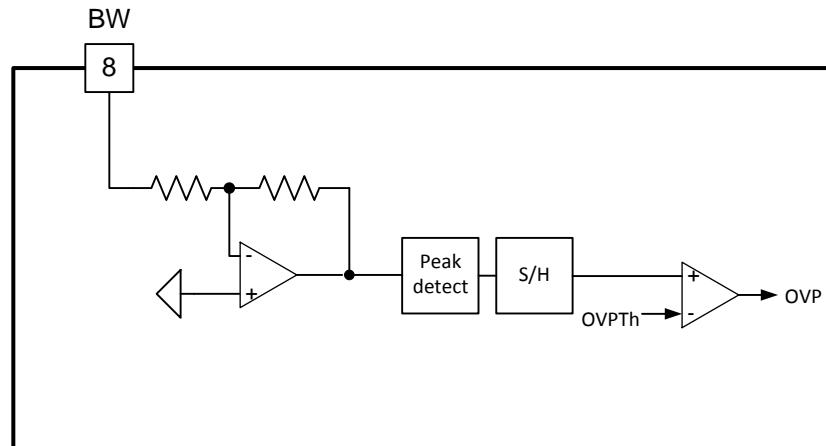

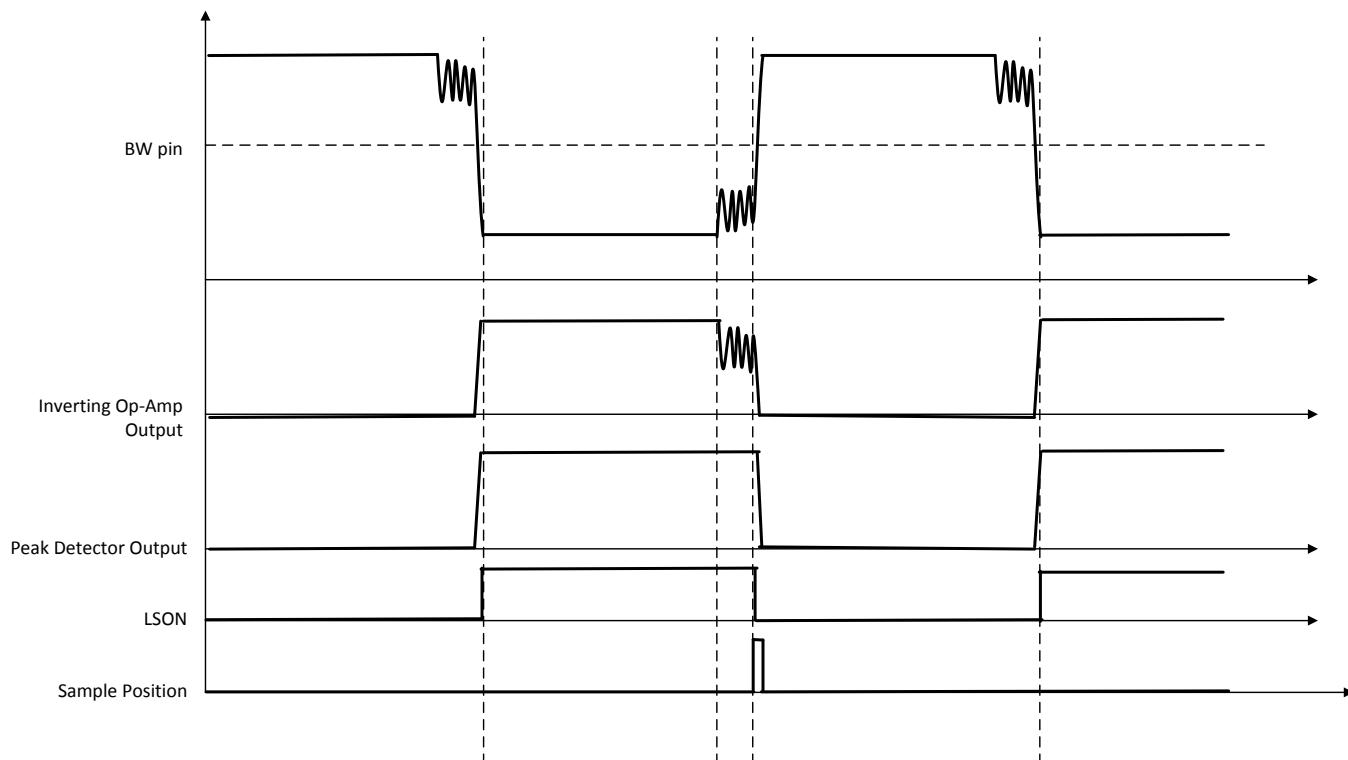

### 7.3.12 出力電圧検知

出力電圧は、バイアス巻線(BW)電圧検知ピンにより検知されます。検知された出力電圧を固定閾値と比較して、出力OVP異常を生成します。バイアス巻線電圧検知ブロックのブロック図を以下に示します。

図 38. バイアス巻線電圧検知ブロック図

バイアス巻線電圧検知ブロックは、反転オペアンプで構成され、BW信号を反転させます。それから反転したBW信号をピーク検出し、2次側ターンオフ・エッジでサンプリングします。サンプリングされた電圧が、このサイクルにおける出力電圧となります。それからS/H出力をOVPコンパレータと比較します。以下にBW検知ブロックのタイミング・チャートを示します。

図 39. BW検知ブロックのタイミング・チャート

## 機能説明 (continued)

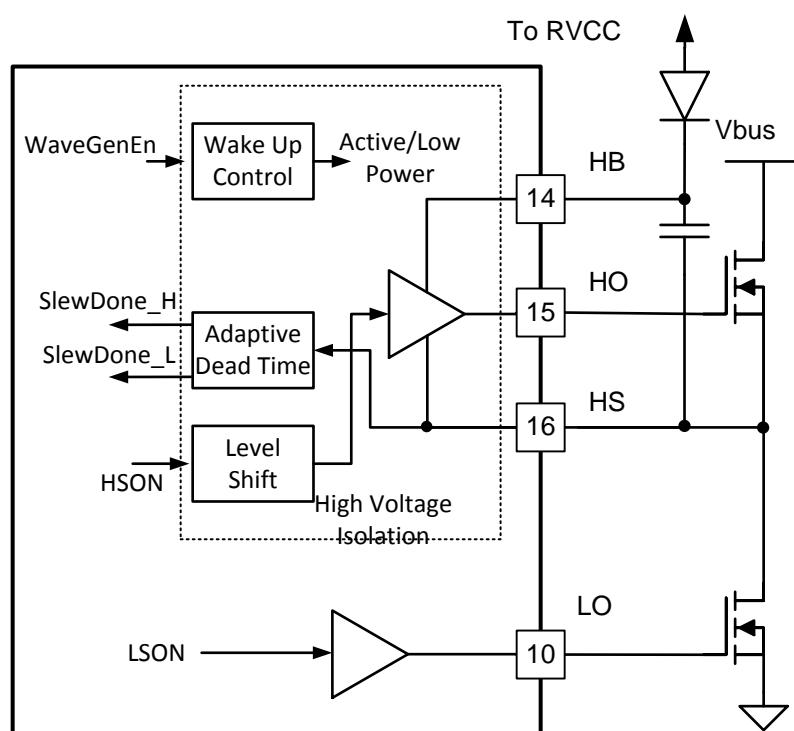

### 7.3.13 高電圧ゲート・ドライバ

2次側ゲート・ドライバ出力はLOです。このゲート・ドライバは、12V RVCCレールにより電力を供給されます。

1次側ドライバ・モジュールは、3つの物理デバイス・ピンで構成されています。HBとHSは、それぞれ1次側ドライバの正と負のレールを形成し、HOは1次ハーフブリッジMOSFETのゲートに接続します。

2次ハーフブリッジMOSFETが導通している間は、導通している2次MOSFETを経由してHSをGNDに短絡します。このとき、1次側ドライバ用の電力は、高電圧ダイオードDBOOTを経由してRVCCから取得され、容量CBOOTはRVCCからダイオードの順方向電圧降下を減じた分まで充電されます。

1次ハーフブリッジMOSFETが導通している間は、HSをLLC入力電圧レールに接続します。このとき、HVダイオードは逆バイアスされ、CBOOTに蓄積した電荷によって1次側ドライバに電力が供給されます。

アダプティブデッドタイムの調整に向けて、HSピンのスルーが検出されます。HSピンのスルーが終了して初めて、次のゲートがオンになります。

1次側および2次側ゲート・ドライバは、いずれも低電圧誤動作防止(UVLO)機能を備えています。2次側ゲート・ドライバUVLOはRVCCに実装され、1次側ゲート・ドライバUVLOは(HB - HS)電圧に実装されています。

軽負荷動作時には、UCC256301はバースト・モードに入ります。バースト・オフ期間中は、ゲート・ドライバが低消費電力モードに入って、消費電力を削減します。

ゲート・ドライバのブロック図を図 40に示します。

図 40. ゲート・ドライバ・ブロック図

## 機能説明 (continued)

### 7.3.14 保護機能

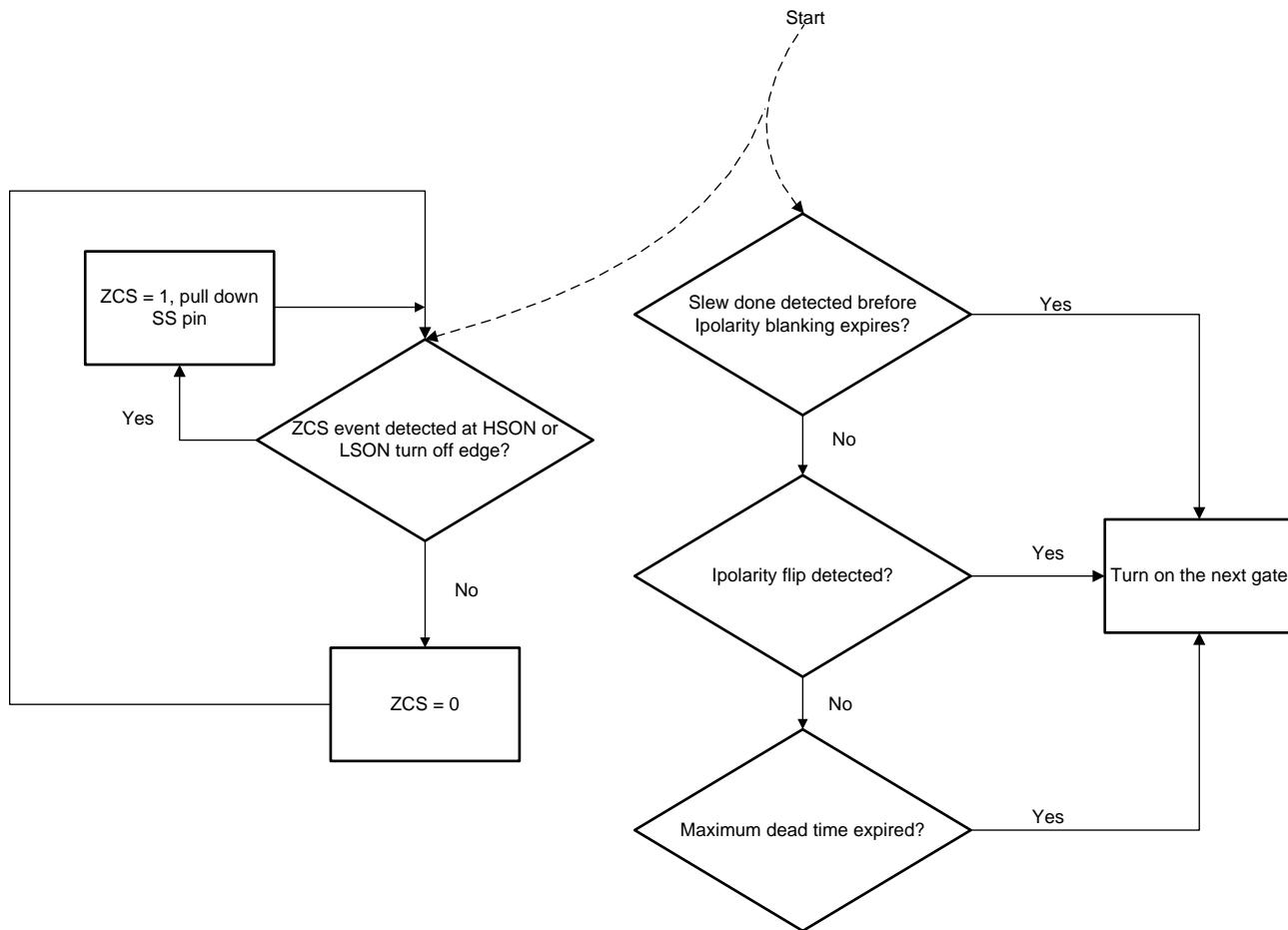

#### 7.3.14.1 ZCS領域回避

容量性領域とは、スイッチング周波数が上昇すると電圧利得が大きくなるLLC動作領域をいいます。これはZCS領域とも呼ばれています。容量性モードでの動作は、次の2つの理由により回避する必要があります。

- 容量性領域では帰還ループが正帰還になる

- ボディ・ダイオードの逆回復により、MOSFETが損傷を受けることがある

容量性領域での動作が発生しないようにするには、まずスルー完了信号を利用する必要があります。スルー完了信号が検出されれば、逆方向のボディ・ダイオードが導通しているはずではなく、次のFETをオンにすることを示唆しています。スルーが検出されなければ、IPolarity信号を利用します。次のIPolarity反転事象で、次のゲートがオンになります。IPolarity反転は、容量性動作サイクルがすでに終わったことを示しています。共振電流は逆方向に流れ、スイッチ・ノードの放電を開始します。容量性動作サイクルが終わっていれば、システムは高周波振動段に入り、ここで回路の寄生要素により振動周波数が確定します。この段では、ボディ・ダイオードはもう導通していないので、次のゲートをオンにすることができます。

ただし、高周波振動段では共振電流が非常に小さくなるため、IPolarityを検出し損なうことがあります。このような場合には、最大デッドタイム・タイマの満了により、次のゲートがオンになります。

逆方向のボディ・ダイオードが導通しているときに次のゲートがオンになるのを防ぐだけでなく、容量性領域動作が検出されないサイクルになるまで、スイッチング周波数を強制的に上げます。

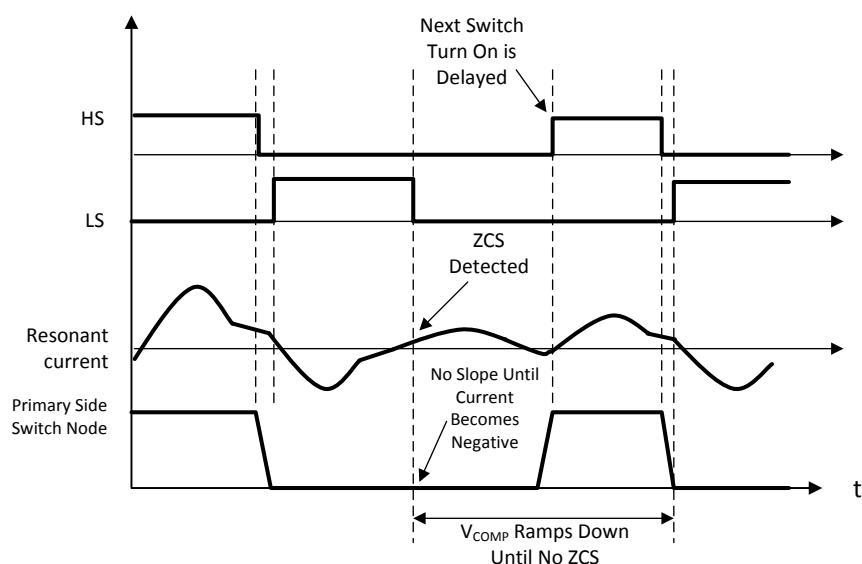

容量性領域検出は、HSONまたはLSON立ち下がりエッジにおける共振電流極性を確認して行います。共振電流がLSON立ち下がりエッジにおいて正であったり、HSON立ち下がりエッジにおいて負である場合には、波形発生器のZCS信号が高くなります。容量性領域動作のない半サイクルが生じるまで、ZCS信号は高い状態を維持します。

スイッチング周波数の強制上昇は、抵抗を介してSSピンをGNDにプルダウンすることにより実行されます。詳細はSSピンの節に述べます。

以下は容量性領域回避動作のフローチャートです。

機能説明 (continued)

図 41. ゲート・ドライバ・ブロック図

図 42. ZCS事象のタイミング・チャート

## 機能説明 (continued)

### 7.3.14.2 過電流保護 (OCP)

次の3つのレベルのOCPがあります。

1. OCP1: ピーク電流保護(最も高い閾値)

1. 異常検出時の動作: OCP1サイクルをカウントし、カウンタが既定値を超えたたら電力段を停止する

2. OCP2: 平均入力電流保護(高い閾値)

1. 異常検出時の動作: 閾値を上回る状態が2ms間続くと停止する

3. OCP3: 平均入力電流保護(低い閾値)

1. 異常検出時の動作: 閾値を上回る状態が50ms間続くと停止する

回路ブロック図については、「[共振電流検知](#)」節で述べています。

### 7.3.14.3 過出力電圧保護(VOUTOVP)

これは出力過電圧保護機能です。VOUTOVPの閾値は、バイアス巻線電圧検知で設定されます。VOUTOVPトリップ・ポイントは、BWピンの分圧器を構成して設定することができます。

### 7.3.14.4 過入力電圧保護(VINOVP)

これは入力過電圧保護機能です。異常検出時の動作については、BLKの節で述べています。トリップ・ポイントは、BWピンの分圧器を構成して設定することができます。

### 7.3.14.5 低入力電圧保護(VINUVP)

これは入力低電圧保護機能です。異常検出時の動作については、BLKの節で述べています。トリップ・ポイントは、BWピンの分圧器を構成して設定することができます。

### 7.3.14.6 ブートUVLO

これは1次側ゲート・ドライバUVLOです。(HB – HS)電圧が閾値を下回ると、1次側ゲートの出力が遮断されます。

### 7.3.14.7 RVCC UVLO

これは電圧が制御された12VのUVLOです。RVCC電圧が閾値を下回ると、1次側ゲート出力と2次側ゲート出力の両方がオフになります。

### 7.3.14.8 過熱保護(OTP)

これはデバイス過熱保護機能です。OTP異常が検出されたとき、デバイスがスイッチング中であれば、スイッチングは停止します。デバイスがHV起動段でJFETがオンの場合には、JFETがオフになります。OTP異常処理については、「[デバイスの機能モード](#)」節で詳述します。

このシステムには、次の2つのデジタル・ステートマシンがあります。

- システム状態/異常検出ステートマシン

- 波形発生器ステートマシン

システム状態制御ステートマシンは、システムの動作状態と異常を制御します。波形発生器ステートマシンは、ゲート・ドライバの挙動を制御します。

## 7.4 デバイスの機能モード

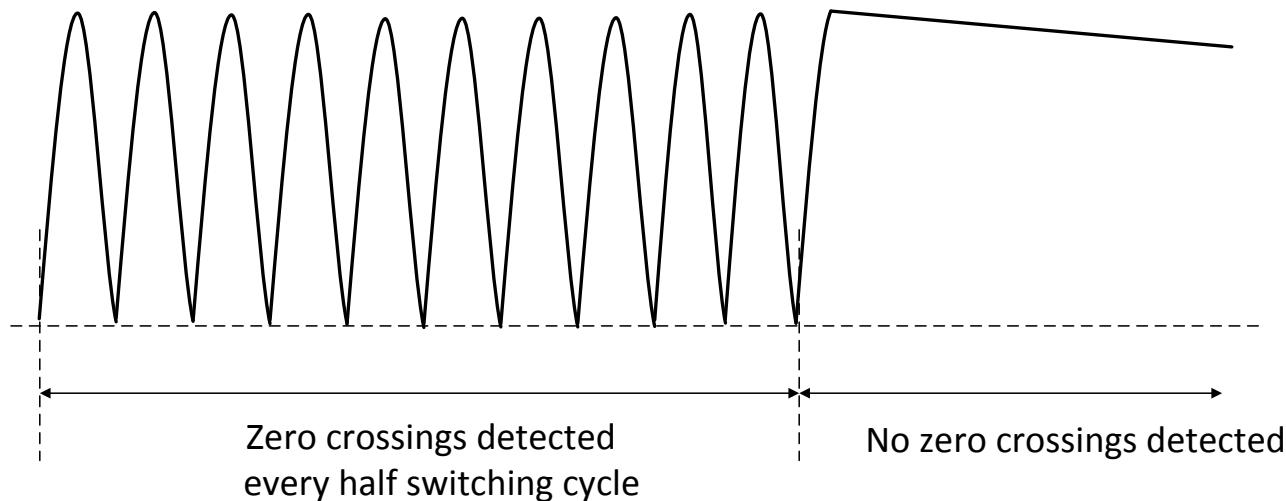

### 7.4.1 バースト・モード制御

LLCコンバータ電力段の効率は、出力の降下に伴って急激に低下します。合理的な軽負荷効率を維持するには、LLCコンバータをバースト・モードで動作させる必要があります。このモードでは、LLCコンバータが短いバースト期間に比較的高電力で動作し、その後のスペース期間ではすべてのスイッチングが停止します。バースト期間中には、過剰電荷を出力容量に移して蓄積します。スペース期間中には、この蓄積した電荷を使用して、負荷電流を供給します。効果的な軽負荷対策の提供は、絶縁膜の1次側にあるLLCコントローラに固有の課題です。これは、帰還要求信号( $V_{COMP}$ )が主に入力/出力電圧比の関数となっており、負荷電流とはゆるい関係にしかないためです。 $V_{COMP}$ 電圧ウインドウで2つの閾値を設定してLLCコンバータのオン/オフを切り替える通常の方法は、効果的ではありません。従来の方法に伴うもう1つの問題は、バーストがオンになると $V_{COMP}$ によってスイッチング・パルスが確定し(通常は最初のバースト・オン時)、出力電圧が上昇するにつれて減衰するということです。その結果、インダクタ電流は最初は大きく、その後減衰します。最初の大電流が機械的振動を引き起こす可能性があるため、これは最適とはいえません。その後の高いスイッチング周波数により、2つの大きなスイッチング損失が生じることもあります。

高度なバースト・モードの実現には、次のような機能が必要とされます。

- 各バーストにより供給される電力は、一定の負荷に対して比較的一定である必要があります。

- バースト電力は、合理的なLLCコンバータ効率を実現するために十分高く、また音響ノイズや過剰な出力電圧リップルを回避するために十分低く設定します。

- バースト・オン時には、最高の効率を実現するために、可能な限り速やかに平均容量電圧を $V_{IN}/2$ に安定させる必要があります。

- スイッチング周波数や各バースト・パルスのバースト電力レベルを効率的な動作に最適化する必要があります。

- 各バーストのバースト・パターンを比較的一定にする必要があります。

- 可聴ノイズをなくす必要があります。

- 入力電圧範囲全体でバースト・モード性能が安定している必要があります。

HHC方式により、バースト・モードの制御は非常に簡単になりました。このブロック図は、UCC25630のバースト・モード制御方式の機能を正確に描写したものです。

図 43. バースト・モード制御ブロック図

制御動作には、1)電圧ループ補償出力( $V_{COMP}$ )と2)バースト・モード閾値レベル(BMT)という2つの信号のうち高いほうを選択します。 $V_{COMP}$ がBMTを下回ると、固定スイッチング・サイクル数だけスイッチングを継続してから停止します。COMPがBMTを上回っていれば、常時スイッチングを行います。ソフトスタートがまだ実行されていなければ、COMPを送信します(ソフトスタート・ランプにより制御)。BMTは調整可能であり、入力電圧に応じて変更されます。共振容量電圧が $V_{IN}/2$ と等しくなると、各バースト・オン期間の最後のパルスがオフになります。HHC方式において、これはVCR電圧が同相電圧VCMと等しいことにほぼ相当します。この動作により、各バースト・オフ期間において共振容量電圧は $V_{IN}/2$ 程度に維持されるため、バースト・オン期間中に可能な限り速やかにバースト・パターンを安定させることができます。

## デバイスの機能モード (continued)

### 7.4.2 高電圧起動

UCC256301は自己バイアス起動方式を採用しているため、補助フライバック電力段を個別に用意する必要がありません。最初にACプラグを差し込むと、PFCとLLCの両方がオフになります。HVピンJFETがオンになり、HVピンに接続されているソース端子からVCC容量に電流を供給し始めます。VCCピン電圧がそのVCCStartSwitching閾値を上回ると電流源はオフになり、RVCCがオンになってPFCをオンにします。PFC出力電圧が一定レベルに達すると、LLCがオンになります。LLCが動作して出力電圧が安定すると、バイアス巻線がPFCコントローラとLLCコントローラの両方に電流を供給します。この動作については、「デバイスの機能モード」節で詳述します。

### 7.4.3 Xコンデンサ放電

ダイオード・ブリッジ整流器のAC側でEMCフィルタに使用するXコンデンサは、一定時間内に合理的な電圧まで放電できる手段を備えていなければなりません。これは、メイン・コードのピンに電圧がいつまでも滞留しないようにするためにです。

通常は、明示的な放電抵抗を容量と並列に入れることにより、このような放電経路が提供されますが、そうした場合、電源がACに接続されている限り、この抵抗によって固定した継続的な電力損失が生じるため、極めて低いスタンバイ消費電力を達成する上で大きな問題になりかねません。

容量100nFごとに、最大10MΩのブリーダ抵抗を並列に追加する必要があります。330nFという標準的な容量の標準的な60W～100W電源では、3MΩの放電抵抗が必要になります。公称230Vの高電圧では、これらの抵抗により17.63mWの継続的な電力損失が生じます。このため、スイッチ型放電経路を使用してXコンデンサを放電し、静的かつ継続的な電力損失を回避する別の方法を見つける必要があります。

Xコンデンサ放電に関しては、いくつかの規格があります。IEC60950およびIEC60065では放電時定数を1秒以内としており、IEC62368ではACプラグを抜いてから2秒後とし、Xコンデンサの残りの電圧は60V未満としています(容量300nF以上の場合)。UCC256301は、アクティブ放電方式の採用により、最大5μFのXコンデンサの高速放電をサポートしています。

各規格の要件を満たすには、AC切断事象を検出する必要があります。UCC256301では、HVピンによりACゼロクロスを監視して、AC切断を検出できます。ACが存在すれば、1つの入力サイクルでACゼロクロスが2回発生します。ACが切断されると、長時間にわたりゼロクロスは発生しません。図 44に整流AC波形を示します。この図では、最後の半ACサイクルのピーク時にACが切斷されています。実際には、1つのスイッチング・サイクルのどの時点でも切斷できます。

図 44. AC切斷波形

## デバイスの機能モード (continued)

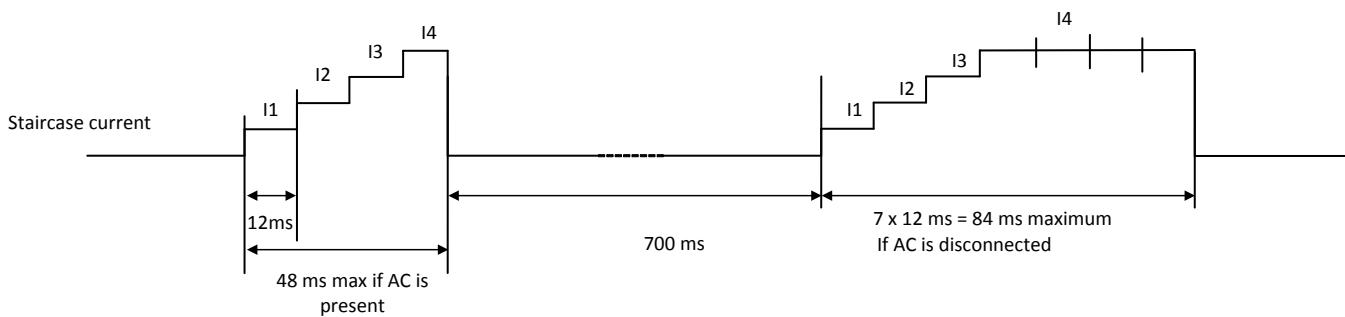

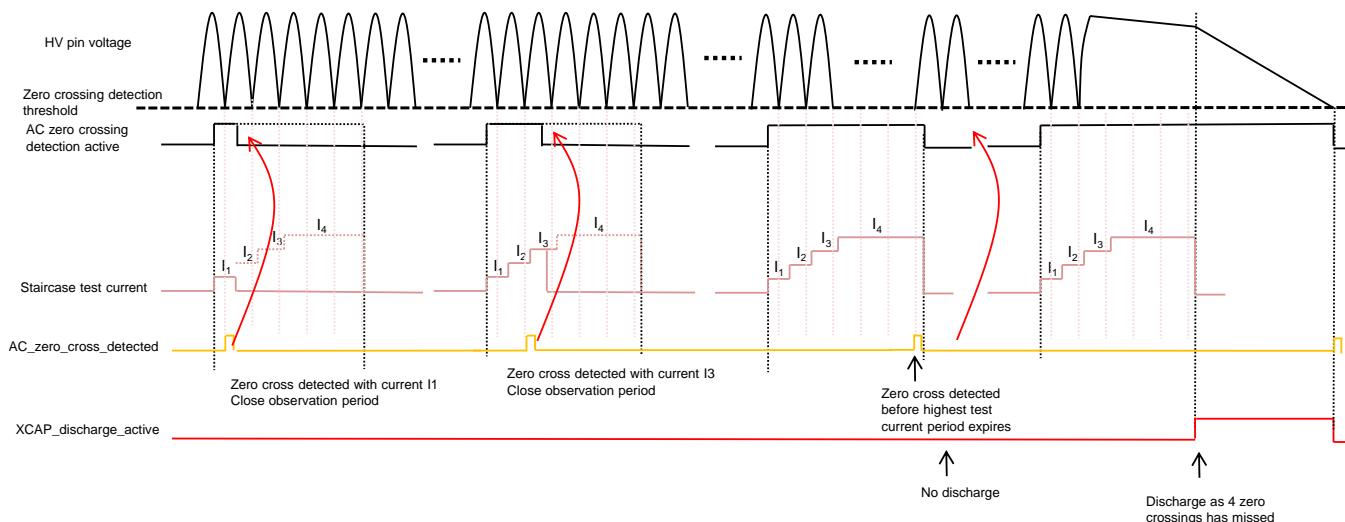

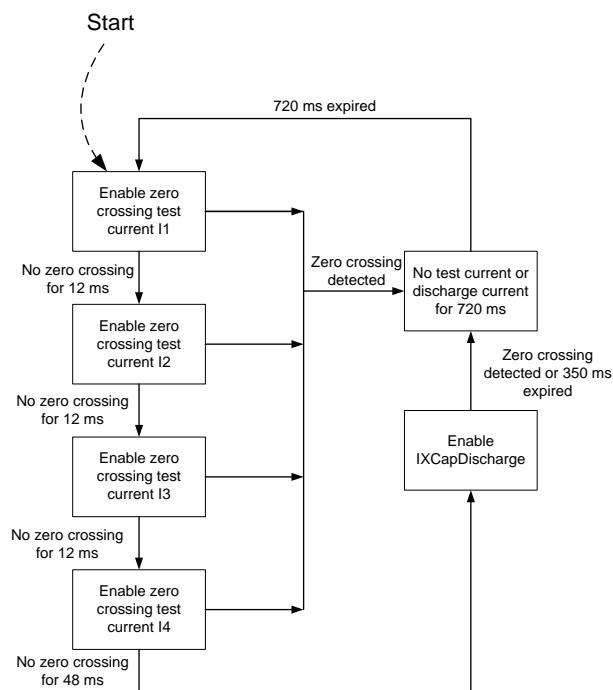

ゼロクロスを確実に検出し、消費電力を削減するために、700msごとに階段テスト電流が生成されます。最も高いテスト電流設定で連続して4回ゼロクロスが検出されなければ、AC切断が確認され、XCapDischarge電流源がオンになります。以下の波形は、階段電流波形を示しています。

図 45. Xコンデンサ放電における階段テスト電流

信頼性の高いACゼロクロス検知を実現するには、テスト電流が必要です。簡単にいうと、非常に軽い負荷では、ACブリッジ整流ダイオードの漏れ電流がゼロクロス検出に影響するからです。HVピンの追加テスト電流により、漏れ電流の問題を克服し、HVピンでACゼロクロスを確実に検出できるようになります。いずれのテスト電流段でもゼロクロスが1回検出されれば、ACは切断されていないことになります。テスト電流は直ちに停止し、システムは700msの無テスト電流段に移行します。

図 46. さまざまな階段電流波形

図 46 にさまざまな階段電流波形を示します。最後の波形は、AC切断が検出され、Xコンデンサの放電が可能であることを示しています。350ms経過するまで、Xコンデンサの放電が可能です。ACゼロクロス機能はあらゆる動作モードで利用可能であり、いつでも利用できます。図 47にACゼロクロス検出とXコンデンサ放電のフローチャートを示します。

## デバイスの機能モード (continued)

放電電流IXCapDischargeは、JFETをオンにすることで生じ、JFETソース端子からGNDへの電流源をオンにします。VCCに放電するのではなく、GNDに放電する理由は、VCCがVCCStartSwitchingに達するのを防ぐためです。ACプラグを抜いた直後にOVP事象が発生すると、VCCの電圧がVCCStartSwitchingにほぼ達してしまいます。

ラッチアップ状態では、JFETはすでにオンになり、VCCループのパス要素となっています。JFETソース端子とVCC端子の間のスイッチは閉じています。JFETをVCC端子から切り離さずに、Xコンデンサ放電電流源がオンになると、放電電流はまずVCC電圧を放電しなければならず、長時間にわたって大量の電流を流し続ける必要があります。この問題を回避するため、ラッチアップ状態では、まずJFETをVCCから切り離します。放電フェーズが終了したら、JFETとVCCの間を短絡状態に戻します。以下にラッチアップ状態におけるXコンデンサ放電の回路図と手順を示します。

図 47. AC ZCDとXコンデンサ放電のフローチャート

## デバイスの機能モード (continued)

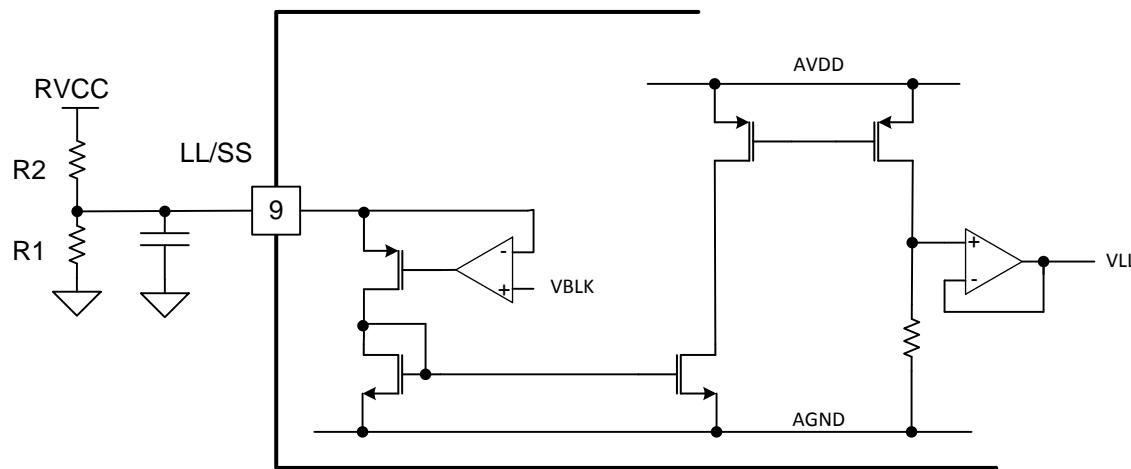

### 7.4.4 ソフトスタートとバースト・モード閾値

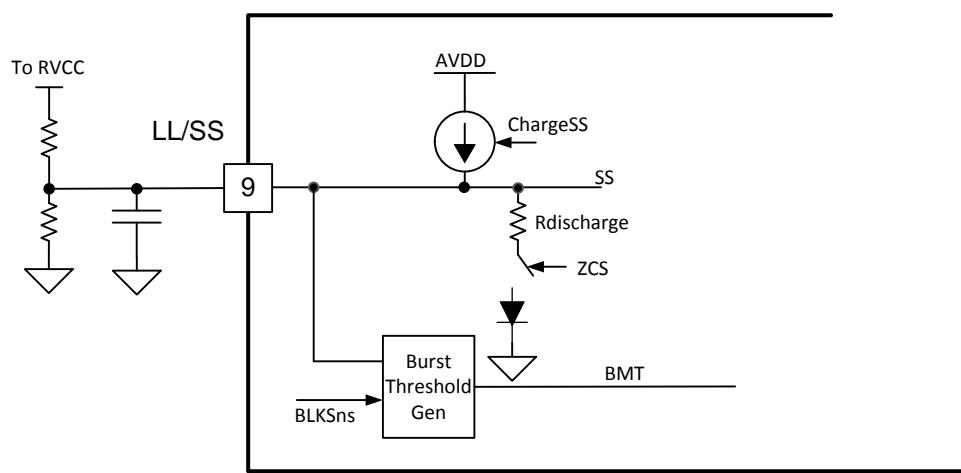

ソフトスタートの調整とバースト・モード閾値の調整は、LL/SSという1つのピンに多重化されます。また、ZCS領域動作が生じると、抵抗を通じてこのピンがGNDにプルダウンされ、スイッチング周波数が上昇します。

内部定電流源は、ソフトスタート容量を充電して、ソフトスタート・コマンドを生成します。ソフトスタート期間は、充電ブート段が実行された直後に開始し、FBreplicaがSSピン電圧より低くなると終了します。

ソフトスタートが実行された後、SS電圧はAVDDに切り替わり、FBチェーンに送られます。それからLL/SSピンを使用して、バースト・モード閾値を生成します。UCC256301では、入力電圧範囲全体にわたって、同じバースト・モード電力レベルを維持します。これは、検知されたBLK電圧に応じてバースト・モード閾値を変更することにより実現します。

抵抗出力の調整は、バースト・モード閾値の設定と、BLK電圧に応じた閾値の変更という2つの自由をもたらします。正しく調整すれば、電力段は常に一定の出力電流レベルでバースト・モードに入るため、従来よりはるかにシステムを最適化しやすくなります。

図 48. LL/SS ブロック図

## デバイスの機能モード (continued)

### 7.4.5 システム状態/異常検出ステートマシン

以下にシステム状態シーケンスの概要を述べます。

状態遷移図は、UCC25630の電源が入っていない状態からスタートします。システムを電源につなぐと、HVピンJFETがオンになり、HVピンに接続されているソース端子からVCC容量に電流を供給し始めます。VCC端子電圧がそのVCCStartSwitching閾値を超えると、システム状態がJFETOFFに変わります。PFC出力電圧が一定レベルに達すると、LLCがオンになります。LLCが動作し始めるまでは、LOピンが高く維持されてLLCブリッジのHSノードが低く抑えられるため、HBピンとHSピンの間の容量をVCCからブートストラップ・ダイオードを経由して充電できます。UCC256301は、ブート容量がフル充電されたことを確認するため、一定の時間CHARGE\_BOOT状態のまとなります。LLC出力電圧が一定レベルに達すると、PFCとLLCの両方にLLC変圧器バイアス巻線から電力が供給されます。負荷が一定レベルを下回ると、LLCはバースト・モードで動作します。

異常状態が発生すると、動作を停止したり、一定時間一時停止してから自動的にリスタートします。これにより、持続的な異常状態があれば、何度もリスタートを試みるため、UCC256301や電力コンバータの温度が上昇を続けることはありません。

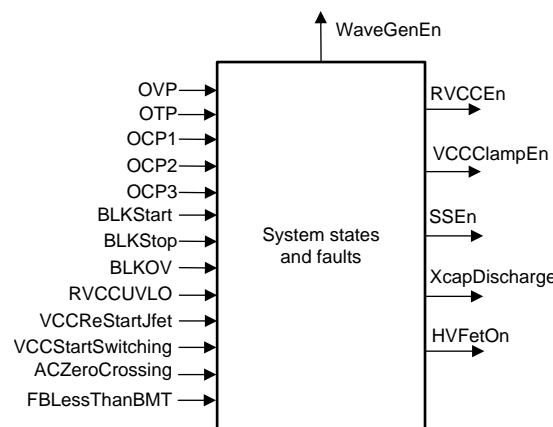

図 49. システム状態/異常検出ステートマシンのブロック図

## デバイスの機能モード (continued)

表 1に図 49の入力と出力をまとめます。

表 1. システム状態/異常検出ステートマシン・ ブロック図の入力と出力

| 信号名               | I/O | 説明                                                       |

|-------------------|-----|----------------------------------------------------------|

| OVP               | I   | 出力過電圧異常                                                  |

| OTP               | I   | 過熱異常                                                     |

| OCP1              | I   | ピーク電流異常                                                  |

| OCP2              | I   | 平均電流異常(2msタイマ)                                           |

| OCP3              | I   | 平均電流異常(50msタイマ)                                          |

| BLKStart          | I   | バルク電圧が開始閾値を上回っている                                        |

| BLKStop           | I   | バルク電圧が停止閾値を下回っている                                        |

| BLKOV             | I   | バルク過電圧異常                                                 |

| RVCCUVLO          | I   | RVCC UVLO異常                                              |

| VCCReStartJfet    | I   | VCCがリスタート閾値を下回っている                                       |

| VCCStartSwitching | I   | VCCがスタート・スイッチング閾値を上回っている(この閾値は自己バイアス・モードと外部バイアス・モードで異なる) |

| ACZeroCrossing    | I   | ACゼロクロスが検出された                                            |

| FBLessThanBMT     | I   | FBReplica電圧がバースト・モード閾値を下回っている                            |

| WaveGenEn         | O   | 波形発生器をオンにする                                              |

| RVCCEn            | O   | RVCCイネーブル                                                |

| VCCClampEn        | O   | VCCクランプ・モードをオンにする(詳細はVCC端子の節)                            |

| SSEn              | O   | ソフトスタートを有効にする                                            |

| XcapDischarge     | O   | Xコンデンサ放電が可能になる                                           |

| HVFetOn           | O   | JFETをオンまたはオフにする                                          |

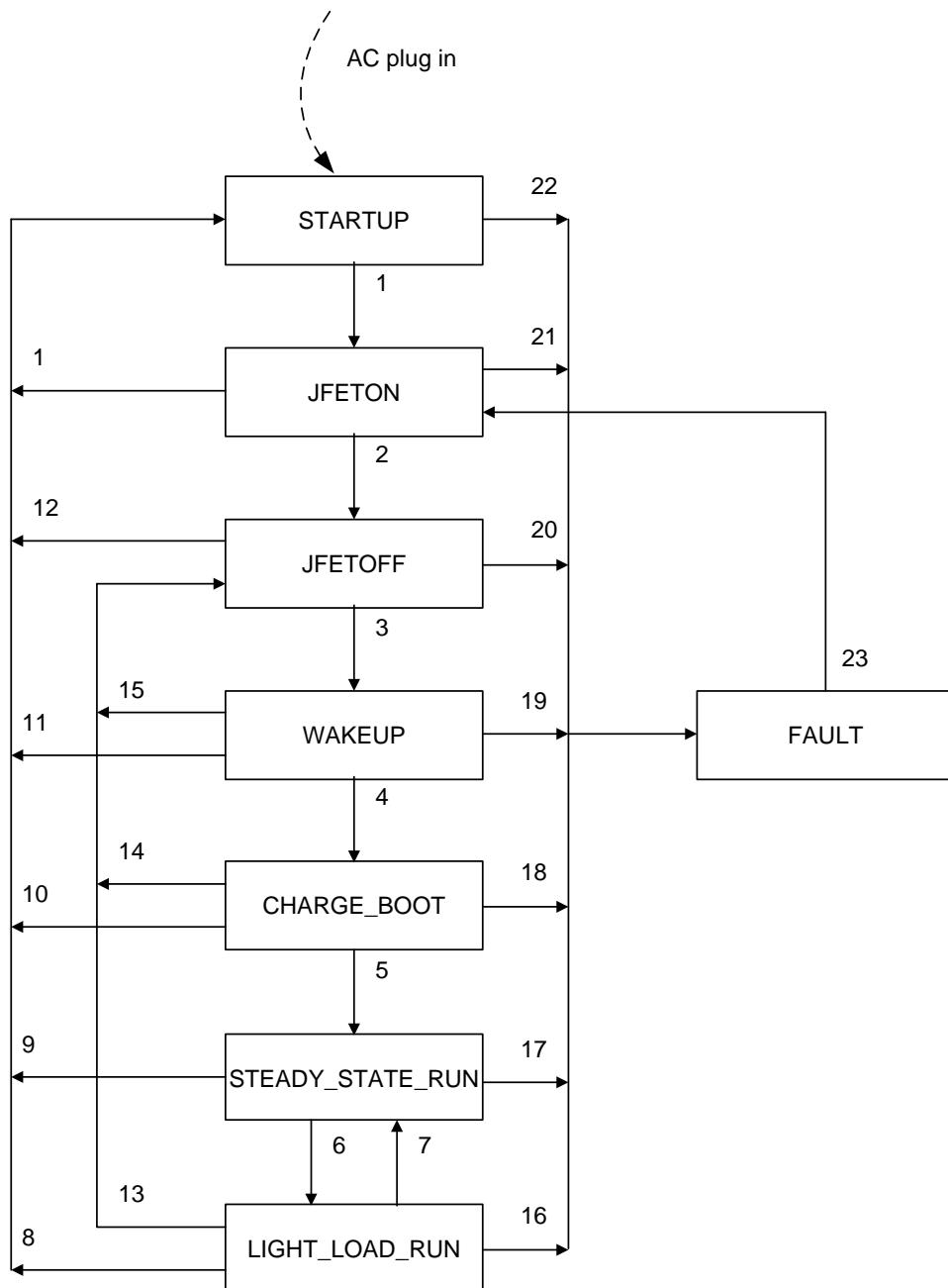

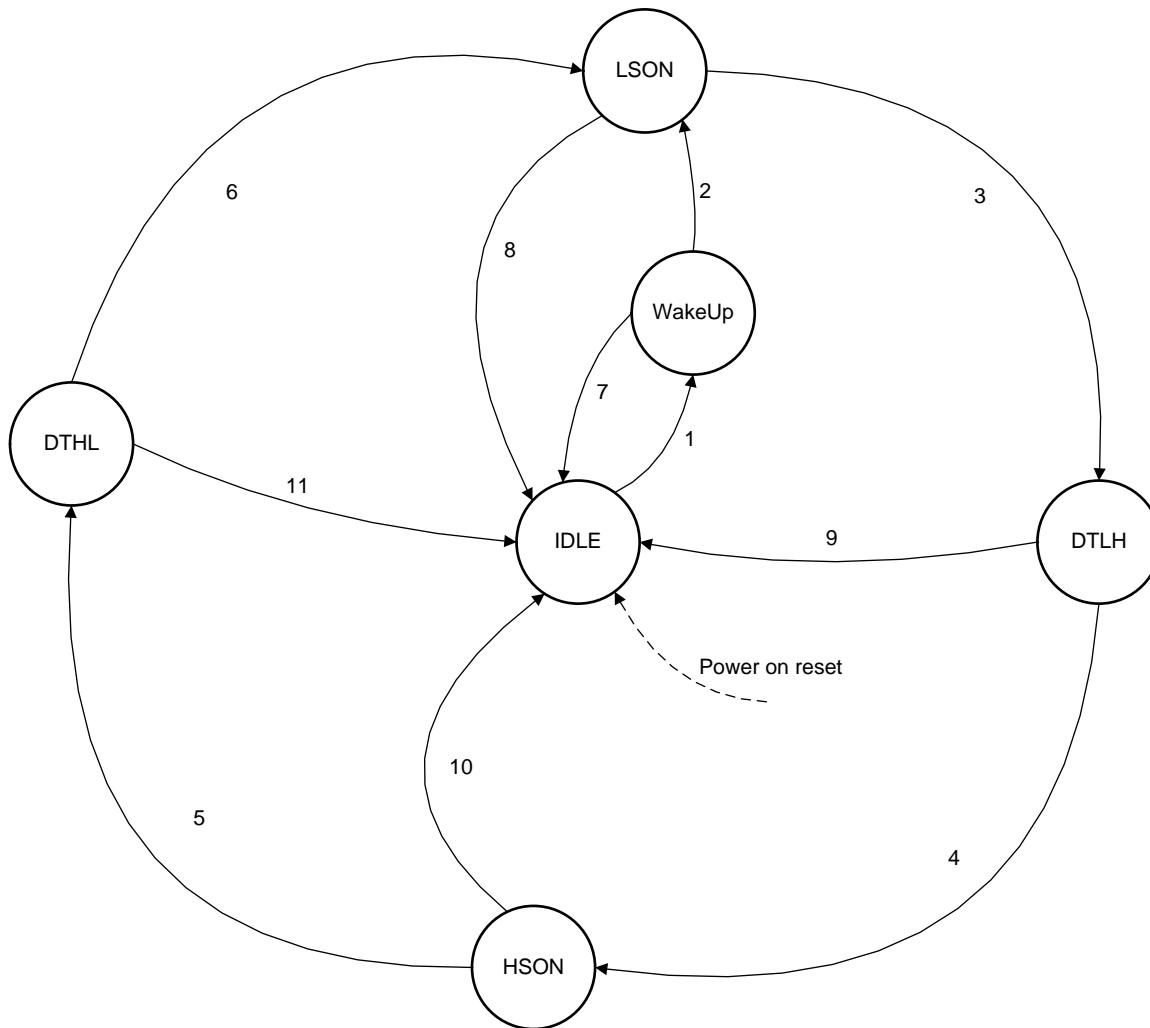

ステートマシンを図 50 に示し、各状態と状態遷移条件の説明をその下の表にまとめます。

図 50. システム状態/異常検出ステートマシン

**表 2. システム状態/異常検出ステートマシンの各状態<sup>(1)</sup>**

| 状態               | 出力状態                                                                     | 説明                                                                                                                  |

|------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| STARTUP          | WaveGenEn = 0<br>RVCCEn = 0<br>VCCClampEn = 1<br>SSEn = 0<br>HVFetOn = 1 | これはパワー・オン・リセット(POR)後の最初の状態です。この状態では、HV JFETがオンになり、VCC電圧が13Vに制御されている電圧クランプ状態で動作していることから、内部回路がトリム設定を初期化して起動することができます。 |

| JFETON           | WaveGenEn = 0<br>RVCCEn = 0<br>VCCClampEn = 0<br>SSEn = 0<br>HVFetOn = 1 | この状態では、JFETはオンです。VCCクランプ・モードは無効です。HV起動電流はIHVHighに制御されています。                                                          |

| JFETOFF          | WaveGenEn = 0<br>RVCCEn = 1<br>VCCClampEn = 0<br>SSEn = 0<br>HVFetOn = 0 | VCCがVCCStartSwitching閾値を上回るとJFETがオフになり、JFETOFF状態に入れります。制御されたRVCCがオンになります。PFCソフトスタートが開始します。                          |

| WAKEUP           | WaveGenEn = 0<br>RVCCEn = 1<br>VCCClampEn = 0<br>SSEn = 0<br>HVFetOn = 0 | BLK電圧がBLKStartレベルに達すると、WAKEUP状態に入り、アナログ回路が復帰するためにWAKEUP状態を150μs間維持します。                                              |

| CHARGE_BOOT      | WaveGenEn = 0<br>RVCCEn = 1<br>VCCClampEn = 0<br>SSEn = 0<br>HVFetOn = 0 | この状態では、2次側スイッチを一定時間オンにすることにより、BOOT容量が充電されます。                                                                        |

| STEADY_STATE_RUN | WaveGenEn = 1<br>RVCCEn = 1<br>VCCClampEn = 0<br>SSEn = 1<br>HVFetOn = 0 | この状態では、波形発生器が有効です。ソフトスタート機能が有効です。LLCがソフトスタートを開始します。ソフトスタートが完了すると通常動作に入れります。                                         |

| LIGHT_LOAD_RUN   | WaveGenEn = 1<br>RVCCEn = 1<br>VCCClampEn = 0<br>SSEn = 1<br>HVFetOn = 0 | 通常動作中にFBReplicaがバースト・モード閾値を下回るとLIGHT_LOAD_RUNモードに入れます。FBLessThanBMT時間を作カウントします。この時間が200msを超えた場合には異常とみなし、再起動します。     |

| FAULT            | WaveGenEn = 0<br>RVCCEn = 0<br>VCCClampEn = 0<br>SSEn = 0<br>HVFetOn = 0 | 異常状態が生じた後、FAULT状態に入り、1秒経ってからリスタートします。1秒タイムによりクールダウンできるため、持続的異常の場合に何度も起動を繰り返すことを防げます。                                |

(1) Xコンデンサ放電は、ACプラグの抜き取り検出に依存するものであり、システム状態/異常検出ステートマシンには依存しません。詳細は「[Xコンデンサ放電](#)」に述べており、この表には記載していません。

**表 3. システム状態/異常検出ステートマシンの状態遷移条件**

| 状態遷移条件 | 説明                                                                                              |

|--------|-------------------------------------------------------------------------------------------------|

| 1      | システム準備完了(トリムの初期化完了)                                                                             |

| 2      | VCCStartSwitching = 1<br>VCCReStartJfet = 0                                                     |

| 3      | BLKStart = 1<br>BLKStop = 0<br>BLKOV = 0<br>RVCCUVLO = 0                                        |

| 4      | BLKStart = 1<br>BLKStop = 0<br>BLKOV = 0<br>RVCCUVLO = 0<br>FBLessThanBMT = 0                   |

| 5      | 充電ブート完了                                                                                         |

| 6      | FBLessThanBMT = 1                                                                               |

| 7      | FBLessThanBMT = 0                                                                               |

| 8      | VCCReStartJfet = 1                                                                              |

| 9      | VCCReStartJfet = 1                                                                              |

| 10     | VCCReStartJfet = 1                                                                              |

| 11     | VCCReStartJfet = 1                                                                              |

| 12     | VCCReStartJfet = 1                                                                              |

| 13     | FBLessThanBMTタイムアウト                                                                             |

| 14     | BLKOV = 1                                                                                       |

| 15     | BLKOV = 1                                                                                       |

| 16     | OTP = 1またはBLKOV = 1または<br>BLKStop = 1またはOVPまたはOCP1またはOCP2タイムアウトまたは<br>OCP3タイムアウトまたはRVCCUVLO = 1 |

| 17     | OTP = 1またはBLKOV = 1または<br>BLKStop = 1またはOVPまたはOCP1またはOCP2タイムアウトまたは<br>OCP3タイムアウトまたはRVCCUVLO = 1 |

| 18     | OTP = 1                                                                                         |

| 19     | OTP = 1                                                                                         |

| 20     | OTP = 1                                                                                         |

| 21     | OTP = 1                                                                                         |

| 22     | OTP = 1                                                                                         |

| 23     | 1秒間一時停止タイムアウト                                                                                   |

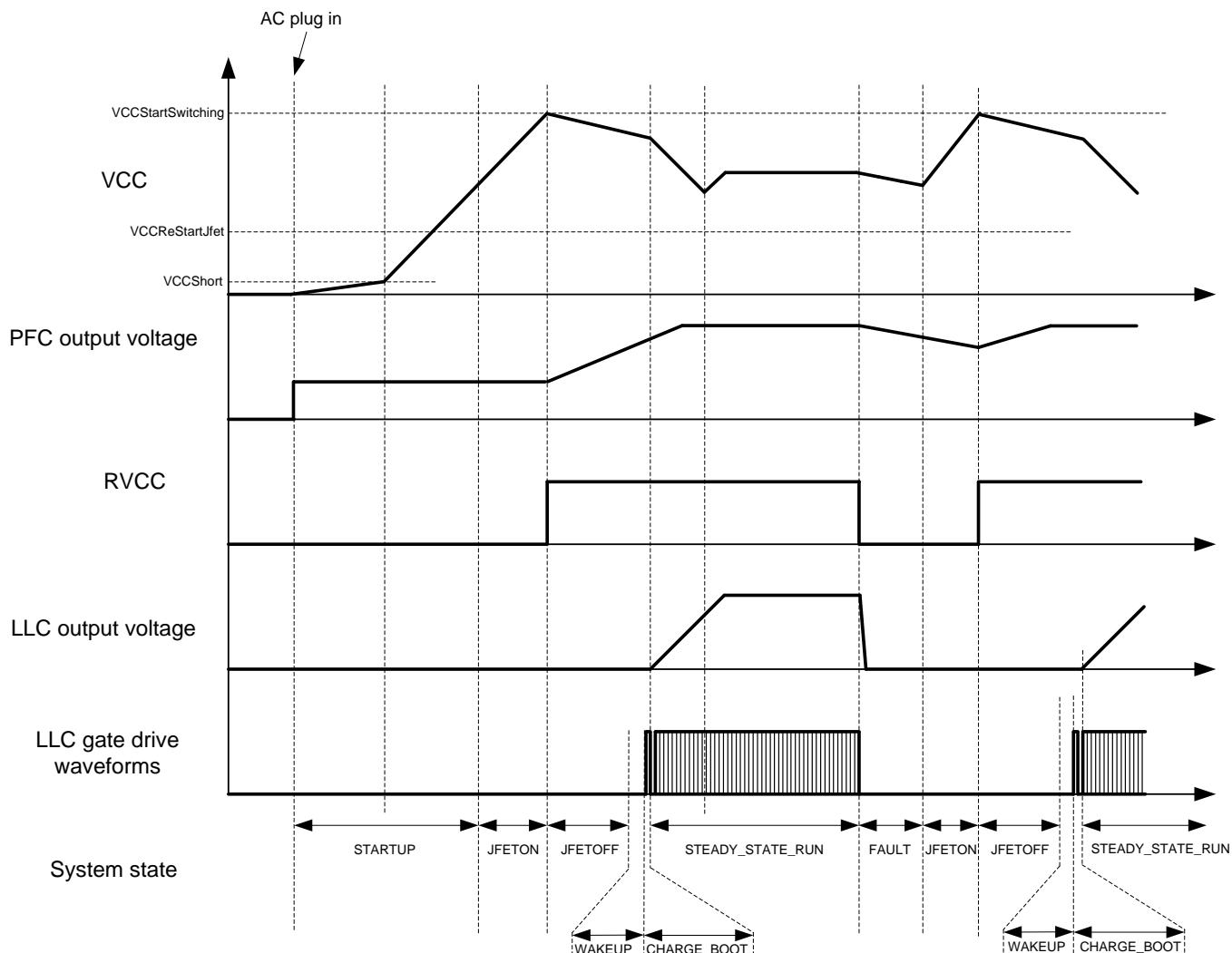

図 51 は最もよく使用されている状態遷移のみを示しています(起動状態において異常がなく、すべての状態がタイミング・チャートに取り込まれていると仮定)。ステートマシンによって、さまざまな状態遷移が発生しますが、この節では捕捉していません。

図 51 に通常の起動手順を示します。システムは通常動作に入り、その後、異常(OCP、OVP、またはOTP)が発生します。

注

OCP1およびOVPは高速異常であるため、まず波形発生器ステートマシンで処理されます。

1秒間一時停止した後リスタートするようにシステムを設定します。

図 51. システム状態/異常検出のタイミング・チャート

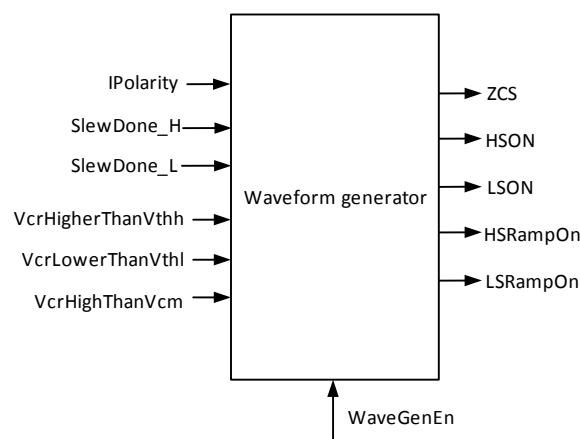

#### 7.4.6 波形発生器ステートマシン

波形発生器モジュールは、ハイブリッドヒステリシス制御、アダプティブデッドタイム、ZCS保護機能を実装するステートマシンで構成されています。各LLC動作サイクルは、HSON、DTHL、LSON、DTLHという4つの期間に分かれます。加えて、IDLE状態とWAKEUP状態があります。

このステートマシンの初期状態はIDLEです。IDLE状態では、システムが低消費電力モードで動作します。WaveGenEnコマンドを受信すると、ステートマシンはWAKEUP状態に入り、さまざまな回路ブロックをオンにします。WAKEUPタイマが満了すると、システムはLSON(2次側オン)状態に入ります。LSON状態は、デッドタイムであるDTLH(2次から1次までのデッドタイム)状態に移行します。DTLH状態の後、1次側がオンになります。システムはHSONに入ります。HSON状態はDTHL(1次から2次までのデッドタイム)状態に移行します。DTHL状態の後、システムはLSON状態に戻ります。

各状態には最小および最大タイマがあります。状態遷移条件とその説明を以下に詳述します。

図 52. 波形発生器ステートマシン・ ブロック図

表 4 に波形発生器ステートマシン・ ブロック図の入力と出力をまとめます。

注

OVPおよびOCP1異常はここに記載されていません。しかし、これらは波形発生器ステートマシンで処理された後、システム状態/異常検出ステートマシンに渡されます。

表 4. 波形発生器ステートマシンの入力と出力

| 信号名               | I/O | 説明                                                                                                    |

|-------------------|-----|-------------------------------------------------------------------------------------------------------|

| IPolarity         | I   | 共振電流の極性(注: この信号にはデッドタイム中に1usのブランкиング時間があります。ここに記載するIPolarity信号はブランкиング後のものです。詳細については、ISNSの節を参照してください) |

| SlewDone_H        | I   | 1次側スイッチ・ノードが2次から1次へのスルーブルを完了                                                                          |

| SlewDone_L        | I   | 1次側スイッチ・ノードが1次から2次へのスルーブルを完了                                                                          |

| VcrHigherThanVthh | I   | VCR電圧が1次閾値Vthhを上回っている                                                                                 |

| VcrLowerThanVthl  | I   | VCR電圧が2次閾値Vthlを下回っている                                                                                 |

| VcrHighThanVcm    | I   | VCR電圧が同相電圧Vcmを上回っている                                                                                  |

| WaveGenEn         | I   | 波形発生器をオンにする                                                                                           |

| ZCS               | O   | ゼロ電流スイッチングがディセーブル                                                                                     |

| HSON              | O   | 1次側ゲート・ドライバ・オン                                                                                        |

| LSON              | O   | 2次側ゲート・ドライバ・オン                                                                                        |

| HSRampOn          | O   | 1次側補償電流ランプ・オン                                                                                         |

| LSRampOn          | O   | 2次側補償電流ランプ・オン                                                                                         |

ステートマシンを図 53に示し、各状態および状態遷移条件の説明を表 5に記載します。

図 53. 波形発生器ステートマシン

**表 5. 波形発生器ステートマシンの状態**

| 状態     | 出力状態                                                                | 説明                                                                                                                                                                                                      |

|--------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IDLE   | HSON = 0<br>LSON = 0<br>HSRampOn = 0<br>LSRampOn = 0<br>ZCS = 0     | この状態では、1次側、2次側ともにオフです。さまざまな回路が低消費電力モードで動作しています。これはPOR後の最初の状態です。バースト・オフ期間中もシステムはIDLE状態です。IDLE状態に入ると、バースト・サイクル・カウンタ、スイッチング・サイクル・カウンタ、OCP1カウンタ、OVPカウンタを初期化します。WaveGenEn_Rising = 1であれば、起動サイクル・カウンタを初期化します。 |

| WakeUp | HSON = 0<br>LSON = 0<br>HSRampOn = 0<br>LSRampOn = 0<br>ZCS = 0     | この状態では、内部回路が低消費電力モードから復帰します。                                                                                                                                                                            |

| LSON   | HSON = 0<br>LSON = 1<br>HSRampOn = 0<br>LSRampOn = 1<br>ZCS = 0または1 | この状態では、2次側ゲートがオンになり、2次側ランプ電流源がオンになります。ZCSは検出された結果によって0または1になります。詳細はZCSの節に述べます。2次側オン・タイマをオンにします。                                                                                                         |

| DTLH   | HSON = 0<br>LSON = 0<br>HSRampOn = 1<br>LSRampOn = 0<br>ZCS = 0または1 | 2次側オンから1次側オンまでのデッドタイム。2次側ランプ電流源がオフになります。1次側ランプ電流源がオンになります。デッドタイム・タイマをオンにします。                                                                                                                            |

| HSON   | HSON = 1<br>LSON = 0<br>HSRampOn = 1<br>LSRampOn = 0<br>ZCS = 0または1 | この状態では、1次側ゲートがオンになり、1次側ランプ電流源がオンになります。ZCSは検出された結果によって0または1になります。詳細はZCSの節に述べます。1次側オン・タイマをオンにします。                                                                                                         |

| DTHL   | HSON = 0<br>LSON = 0<br>HSRampOn = 0<br>LSRampOn = 1<br>ZCS = 0または1 | 1次側オンから2次側オンまでのデッドタイム。1次側ランプ電流源がオフになります。2次側ランプ電流源がオンになります。デッドタイム・タイマをオンにします。                                                                                                                            |

**表 6. 波形発生器ステートマシンの状態遷移条件**

| 状態遷移条件 | 説明                                                                                                                                                                                                                                            |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | WaveGenEn = 1 および FBLessThanBMT = 0 および 最小 IDLE 時間満了                                                                                                                                                                                          |

| 2      | 復帰時間満了                                                                                                                                                                                                                                        |

| 3      | (VcrLowerThanVthl = 1 または LSON 最大タイマ満了) および LSON 最小タイマ満了                                                                                                                                                                                      |

| 4      | StartUpCounterExpired = 0 および DTStartUpTimerExpired = 1<br>DTMaxTimerExpired = 1<br>SlewDone_H = 1<br>SlewDone_H = 1 および MeasuredDTExpired = 1 (注: デッドタイム測定/一致機能が必要かどうかに応じて、トリム・ビットを使用して、この条件と上記の条件を選択可能)<br>IPolarityFallingEdgeDetected = 1 |

| 5      | (VcrHigherThanVthh = 1 または HSON 最大タイマ満了) および HSON 最小タイマ満了                                                                                                                                                                                     |

| 6      | StartUpCounterExpired = 0 および DTStartUpTimerExpired = 1<br>DTMaxTimerExpired = 1<br>SlewDone_L = 1<br>IPolarityFallingEdgeDetected = 1                                                                                                        |

| 7      | WaveGenEn = 0                                                                                                                                                                                                                                 |

| 8      | WaveGenEn = 0<br>(VcrLowerThanVthl = 1 または LSON 最大タイマ満了) および LSON 最小タイマ満了 および (OCP1 カウンタ満了 または OVP カウンタ満了)                                                                                                                                    |

| 9      | WaveGenEn = 0                                                                                                                                                                                                                                 |

| 10     | WaveGenEn = 0<br>BurstModeCountExpire = 1 および VcrHigherThanVcm = 1 および FBLessThanBMT = 1 および HSON 最小タイマ満了                                                                                                                                     |

| 11     | WaveGenEn = 0                                                                                                                                                                                                                                 |

**表 7. 波形発生器ステートマシンの内部カウンタおよびタイマ**

| 内部変数             | 説明                                                                                                                            |

|------------------|-------------------------------------------------------------------------------------------------------------------------------|

| スイッチング・サイクル・カウンタ | このカウンタはスイッチング・サイクルをカウントします。                                                                                                   |

| OVPカウンタ          | バイアス巻線過電圧カウンタ。このカウンタはバイアス巻線過電圧が生じるたびに減算します。                                                                                   |

| 起動カウンタ           | 起動カウンタ。波形発生器が2次から1次へのトグルをオンにすると、カウンタが15にセットされ、その後スイッチング・サイクルごとに減算します。カウンタが0になると、起動デッドタイム満了によりデッドタイム状態は終了となります。                |

| バースト・サイクル・カウンタ   | バースト・カウンタ。カウンタが15にセットされ、その後「0」になるまでスイッチング・サイクルごとに減算します。カウンタが「0」のとき FBLessThanBMT = 1 であれば、FBLessThanBMT = 0 になるまでスイッチャは停止します。 |

| OCP1カウンタ         | OCP1カウンタ。OCP1が発生すると、カウンタが4にセットされ、その後「0」になるまでスイッチング・サイクルごとに減算します。                                                              |

| ウェークアップ・タイマ      | WakeUp状態タイマ                                                                                                                   |

| DT最大タイマ          | 最大デッドタイム・タイマ                                                                                                                  |

| 起動デッドタイム最大タイマ    | 起動カウンタが満了する前の最初の数起動サイクルに対するデッドタイム最大クランプ                                                                                       |

| ゲート・オン最小タイマ      | 最小ゲート・オン時間タイマ                                                                                                                 |

| ゲート・オン最大タイマ      | 最大ゲート・オン時間タイマ                                                                                                                 |

## 8 アプリケーションと実装

### 注

以降のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

UCC256301は、LLC方式が実装されている幅広い用途に使用できます。より簡単に使用できるよう、TIは次のようなツールを用意して、製品の機能を紹介しています。

- フル機能EVM/ハードウェア

- Excel設計計算ツール

- シミュレーションモデル

- ハイブリッドヒステリシス制御理論に関するアプリケーションノート

以下に代表的な設計例を記載します。

### 8.2 代表的なアプリケーション

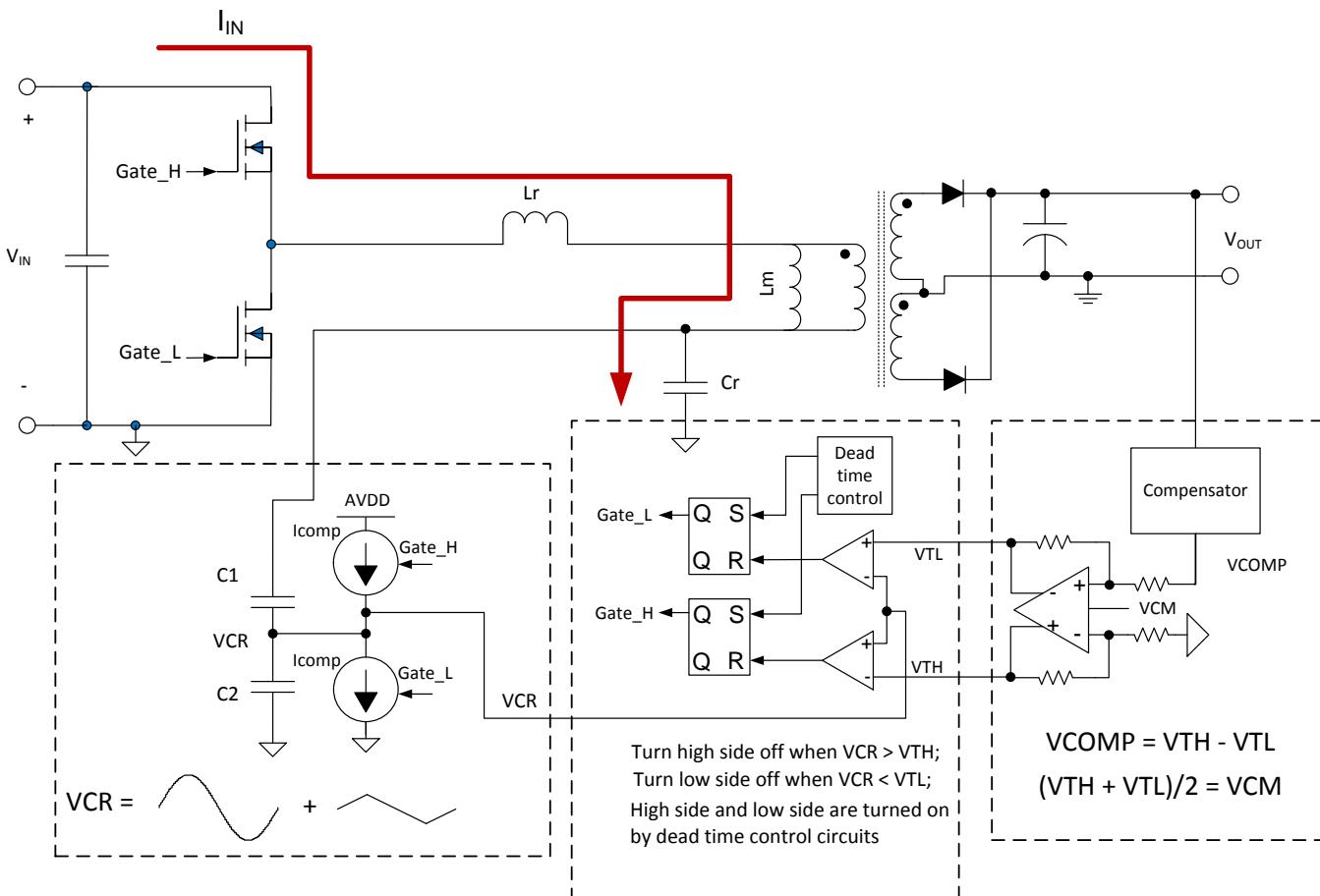

以下にUCC256301をコントローラとする代表的なハーフブリッジLLCアプリケーションを示します。

Copyright © 2017, Texas Instruments Incorporated

## 代表的なアプリケーション (continued)

### 8.2.1 設計要件

設計仕様を表 8 にまとめます。

表 8. システム設計仕様

| PARAMETER     | TEST CONDITIONS       | MIN | TYP   | MAX | UNITS |

|---------------|-----------------------|-----|-------|-----|-------|

| <b>入力特性</b>   |                       |     |       |     |       |

| DC電圧範囲        |                       | 340 | 390   | 410 | VDC   |

| AC電圧範囲        |                       | 85  |       | 264 | VAC   |

| AC電圧周波数       |                       | 47  |       | 63  | Hz    |

| 入力DC UVLOオン   |                       |     | 320   |     | VDC   |

| 入力DC UVLOオフ   |                       |     | 140   |     | VDC   |

| 入力DC電流        | 入力 = 340VDC、全負荷 = 10A |     | 0.383 |     | A     |

| 入力DC電流        | 入力 = 390VDC、全負荷 = 10A |     | 0.331 |     | A     |

| 入力DC電流        | 入力 = 410VDC、全負荷 = 10A |     | 0.315 |     | A     |

| <b>出力特性</b>   |                       |     |       |     |       |

| 出力電圧、VOUT     | 無負荷 ~ 全負荷             |     | 12    |     | VDC   |

| 出力負荷電流、IOUT   | 340VDC ~ 410VDC       |     |       | 10  | A     |

| 出力電圧リップル      | 390VDC および全負荷 = 10A   |     | 130   |     | mVpp  |

| <b>システム特性</b> |                       |     |       |     |       |

| スイッチング周波数     |                       | 53  |       | 160 | kHz   |

| ピーク効率         | 390VDC、負荷 = ??A       |     | 92.9  |     |       |

| 動作温度範囲        | 自然対流                  |     | 25    |     | °C    |

## 8.2.2 詳細な設計手順

### 8.2.2.1 LLC電力段要件

設計は、LLC電力段コンポーネントの各値を決めるところから始まります。ここに述べるLLC電力段の設計手順は、TIアプリケーションノート『LLC共振ハーフブリッジ・パワー・コンバータ』から引用したものです。このアプリケーションノートでは、使用する各式の由来が十分に説明されています。以下の式は、LLC方式の解析によく用いられるFHA (First Harmonic Approximation)法に基づきます。この手法は、あらゆる設計の出発点には適しているものの、最終設計にはFHAの結果、回路シミュレーション、ハードウェア・テストを組み合わせる反復アプローチが必要です。TIアプリケーションノート『SLUA733、UCC29950のLLC設計』には、これに代わる設計手法が記載されています。

### 8.2.2.2 LLC利得範囲

まず、公称入力電圧と公称出力電圧から変圧器の巻数比を求めます。

$$n = \frac{V_{IN(nom)} / 2}{V_{OUT(nom)}} = \frac{390 / 2}{12} = 16.25 \Rightarrow 16 \quad (6)$$

それから、LLC利得範囲 $M_{g(min)}$ と $M_{g(max)}$ を求めます。整流ダイオードで 0.5Vの降下( $V_f$ )があり、他の損失によりさらに0.5Vの降下( $V_{loss}$ )があると仮定します。

$$M_{g(min)} = n \frac{V_{OUT(min)} + V_f}{V_{IN(max)} / 2} = 16 \frac{12 + 0.5}{410 / 2} = 0.976 \quad (7)$$

$$M_{g(max)} = n \frac{V_{OUT(max)} + V_f + V_{loss}}{V_{IN(min)} / 2} = 16 \frac{12 + 0.5 + 0.5}{340 / 2} = 1.224 \quad (8)$$

### 8.2.2.3 $L_n$ と $Q_e$ を選択する

$L_n$ は磁化インダクタンスと共振インダクタンスの比です。

$$L_n = \frac{L_m}{L_r} \quad (9)$$

$Q_e$ は共振タンクの品質係数です。

$$Q_e = \frac{\sqrt{L_r / C_r}}{R_e} \quad (10)$$

この式において、 $R_e$ は等価負荷抵抗です。

$L_n$ と $Q_e$ の値を選択することにより、以下に示すLLC利得曲線が描かれ、 $M_{g(\min)}$ および $M_{g(\max)}$ の波形と交差するものとします。結果として描かれる曲線のピーク利得は、 $M_{g(\max)}$ より大きくなっている必要があります。ここでは、 $L_n$ と $Q_e$ の選択方法について詳述しません。 [アプライケーションノート『UCC25630x実用設計ガイドライン』](#) および [『UCC256301設計計算ツール』](#) を参照してください。

このケースでは、選択した $L_n$ と $Q_e$ の値は次のとおりです。

$$L_n = 13.5 \quad (11)$$

$$Q_e = 0.15 \quad (12)$$

### 8.2.2.4 等価負荷抵抗を求める

式 13により等価負荷抵抗を求めます。

$$R_e = \frac{8 \times n^2}{\pi^2} \times \frac{V_{OUT(nom)}}{I_{OUT(nom)}} = \frac{8 \times 16^2}{\pi^2} \times \frac{12}{10} = 249\Omega \quad (13)$$

### 8.2.2.5 LLC共振回路の部品特性を求める

共振タンク部品特性を求める前に、公称スイッチング周波数(共振周波数)を選択する必要があります。この設計では、共振周波数として100kHzを選択します。

$$f_0 = 100\text{ kHz} \quad (14)$$

共振タンク・パラメータは次のように計算できます。

$$C_r = \frac{1}{2\pi \times Q_e \times f_0 \times R_e} = \frac{1}{2\pi \times 0.15 \times 100\text{ kHz} \times 249\Omega} = 42.6 \quad (15)$$

$$L_r = \frac{1}{(2\pi \times f_0)^2 C_r} = \frac{1}{(2\pi \times 100\text{ kHz})^2 \times 42.6\text{ nF}} = 59.5\mu\text{H} \quad (16)$$

$$L_m = L_r \times L_r = 13.5 \times 59.5\mu\text{H} = 803\mu\text{H} \quad (17)$$

予備パラメータを選択したら、最も近い実際のコンポーネントの値で利用できるものを見つけ、選択したパラメータで利得曲線を再確認し、時間領域シミュレーションを実行して回路動作を検証します。

次の共振タンク・パラメータは以下のとおりです。

$$C_r = 44\text{ nF} \quad (18)$$

$$L_r = 61.5\mu\text{H} \quad (19)$$

$$L_m = 830\mu\text{H} \quad (20)$$

最終共振タンク・パラメータに基づき、共振周波数は次のように計算できます。

$$f_0 = \frac{1}{2\pi\sqrt{L_r C_r}} = \frac{1}{2\pi\sqrt{44\text{ nF} \times 61.5\mu\text{H}}} = 96.8\text{ kHz} \quad (21)$$

新しいLLC利得曲線に基づき、最大および最小利得での正規化したスイッチング周波数は次のように求められます。

$$f_{n(Mgmax)} = 0.52 \quad (22)$$

$$f_{n(Mgmin)} = 1.15 \quad (23)$$

最大および最小スイッチング周波数は次のとおりです。

$$f_{SW(Mgmax)} = 50.3\text{ kHz} \quad (24)$$

$$f_{SW(Mgmin)} = 111.3\text{ kHz} \quad (25)$$

### 8.2.2.6 LLC 1次側電流

コンポーネントを選択するために、1次側電流を計算します。この電流は110%の過負荷条件に基づいて計算します。

1次側RMS負荷電流は次の式で求められます。

$$I_{oe} = \frac{\pi}{2\sqrt{2}} \times \frac{I_o}{n} = \frac{\pi}{2\sqrt{2}} \times \frac{1.1 \times 10 A}{16} = 0.764 A \quad (26)$$

最小スイッチング周波数でのRMS磁化電流は次の式で求められます。

$$I_m = \frac{2\sqrt{2}}{\pi} \times \frac{nV_{OUT}}{\omega L_m} = \frac{2\sqrt{2}}{\pi} \times \frac{16 \times 12}{2\pi \times 50.3 \text{kHz} \times 830 \mu H} = 0.659 A \quad (27)$$

共振タンクの総電流は次の式で求められます。

$$I_r = \sqrt{I_m^2 + I_{oe}^2} = \sqrt{(0.764 A)^2 + (0.659 A)^2} = 1.009 A \quad (28)$$

### 8.2.2.7 LLC 2次側電流

2次側の総RMS負荷電流は、1次側電流( $I_{oe}$ )から2次側に換算した電流です。

$$I_{oes} = n \times I_{oe} = 16 \times 0.764 A = 12.218 A \quad (29)$$

この設計では、変圧器の2次側にセンタータップ(巻線の中間を引き出した端子)が付いています。各2次側変圧器巻線の電流は次の式で計算できます。

$$I_{ws} = \frac{\sqrt{2} \times I_{oes}}{2} = \frac{\sqrt{2} \times 12.218 A}{2} = 8.639 A \quad (30)$$

該当する半波平均電流は次のとおりです。

$$I_{sav} = \frac{\sqrt{2} \times I_{oes}}{2} = \frac{\sqrt{2} \times 12.218 A}{\pi} = 5.503 A \quad (31)$$

### 8.2.2.8 LLC変圧器

HVセルフ起動機能を利用するには、バイアス巻線が必要です。VCC電圧が13Vを上回るようにバイアス巻線を設計することをお勧めします。

変圧器は、以下の仕様で構築または購入できます。

- ターン比: 1次 : 2次 : バイアス = 32 : 2 : 3

- 1次端子電圧: 450V<sub>ac</sub>

- 1次磁化インダクタンス:  $L_M = 830 \mu H$

- 1次側巻線定格電流:  $I_r = 1.009 A$

- 2次端子電圧: 36V<sub>ac</sub>

- 2次巻線定格電流:  $I_{ws} = 8.639 A$

- 最小スイッチング周波数: 50.3kHz

- 最大スイッチング周波数: 111.3kHz

- 1次側と2次側の絶縁: IEC60950強化絶縁

通常動作時の最小動作周波数は上で計算したとおりですが、停止時にはLLCはZCS境界条件を少し上回る、より低い周波数で動作できます。共振回路、変圧器、共振インダクタの磁性部品の定格は、この低い周波数で動作するものとします。

### 8.2.2.9 LLC共振インダクタ

共振インダクタのAC電圧は、そのインピーダンスと電流との積で求められます。

$$V_{L_R} = \omega L_R I_R = 2\pi \times 50.3 \times 10^3 \times 61.5 \times 10^{-6} \times 1.009 = 19.607V \quad (32)$$

インダクタは、以下の仕様で構築または購入できます。

- インダクタンス:  $L_r = 61.5\mu\text{H}$

- 定格電流:  $I_r = 1.009\text{A}$

- 端子AC電圧:

- 周波数範囲: 50.3kHz ~ 111.3kHz

通常動作時の最小動作周波数は上で計算したとおりですが、停止時にはLLCはZCS境界条件を少し上回る、より低い周波数で動作できます。共振回路、変圧器、共振インダクタの磁性部品の定格は、この低い周波数で動作するものとします。

### 8.2.2.10 LLC共振容量

この容量は高周波でフル1次電流を伝導します。部品の過熱を防止するため、散逸係数の小さい部品が必要です。

共振容量のAC電圧は、そのインピーダンスと電流との積で求められます。

$$V_{CR} = \frac{I_r}{\omega C_r} = \frac{1.009}{2\pi \times 50.3 \times 10^3 \times 44 \times 10^{-9}} = 72.5V \quad (33)$$

$$V_{CR(rms)} = \sqrt{\left(\frac{V_{IN(max)}}{2}\right)^2 + V_{CR}^2} = \sqrt{\left(\frac{410}{2}\right)^2 + 72.5^2} = 217.4V \quad (34)$$

ピーク電圧:

$$V_{CR(peak)} = \frac{V_{IN(max)}}{2} + \sqrt{2}V_{CR} = \frac{410}{2} + \sqrt{2} \times 72.5 = 307.5V \quad (35)$$

谷電圧:

$$V_{CR(valley)} = \frac{V_{IN(max)}}{2} - \sqrt{2}V_{CR} = \frac{410}{2} - \sqrt{2} \times 72.5 = 102.5V \quad (36)$$

定格電流:

$$I_r = 1.009\text{A} \quad (37)$$

### 8.2.2.11 LLC 1次側MOSFET

各MOSFETは、入力電圧をそれぞれの最大印加電圧と認識します。次のようにMOSFETの定格電圧は最大バルク電圧の1.5倍とします。

$$V_{QLLC(peak)} = 1.5 \times V_{IN(max)} = 615V \quad (38)$$

次のようにMOSFETの定格電流は最大1次側RMS電流の1.1倍とします。

$$I_{QLLC} = 1.1 \times I_r = 1.109\text{A} \quad (39)$$

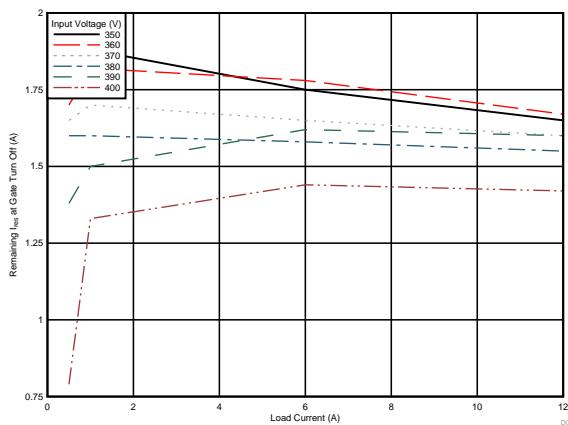

### 8.2.2.12 アダプティブデッドタイムの設計における考慮事項

共振タンクを設計して、1次側MOSFETを選定したら、コンバータのZVS動作を再確認する必要があります。ゲート・ターンオフ・エッジで、スイッチ・ノードを放電するのに十分な電流が共振インダクタに残っていなければ、ZVSは実現しません。UCC256301は、スイッチ・ノードのスルーリングに基づくアダプティブデッドタイムを実装しています。スルーチェミングの検出範囲は1V/ns ~ 50V/nsです。

ZVS動作を確認するには、一連の時間領域シミュレーションを実行し、ゲート・ターンオフ・エッジでの共振電流を捕捉します。プロットの例を以下に示します。

図 54. アダプティブデッドタイム制御

上記の図は、5%負荷で最大スイッチング周波数が生じ、5%負荷でシステムがバーストを開始すると仮定したものです。

このプロットによれば、当該動作範囲で、タンクに残っている最小共振電流は $I_{min} = 0.8A$ です。スルーレートを計算するには、1次側スイッチ・ノードの寄生容量を知る必要があります。この値はMOSFETのデータシートから推計できます。このケースでは、 $C_{switchnode} = 400pF$ です。最小スルーレートは次の式で求められます。

$$\frac{I_{MIN}}{C_{switchnode}} = \frac{0.8A}{400pF} = 2V/ns \quad (40)$$

これは、1V/nsの最小検出可能スルーレートを上回っています。

### 8.2.2.13 LLC整流ダイオード

出力ダイオードの定格電圧は次の式で求められます。

$$V_{DB} = 1.2 \times \frac{V_{IN(max)}}{n} = 1.2 \times \frac{410}{16} = 30.75V \quad (41)$$

出力ダイオードの定格電流は次の式で求められます。

$$I_{SAV} = \frac{\sqrt{2} \times I_{OES}}{\pi} = \frac{\sqrt{2} \times 12.218}{\pi} = 5.5A \quad (42)$$

### 8.2.2.14 LLC出力容量

LLCコンバータ方式は出力フィルタを必要としませんが、小型の2次段フィルタ・インダクタは出力ノイズ最大値と最小値との差を低減するのに役立ちます。出力容量が整流器の全波出力電流を伝導するものと仮定すると、容量の定格リップル電流は次のとおりです。

$$I_{RECT} = \frac{\pi}{2\sqrt{2}} I_{OUT} = \frac{\pi}{2\sqrt{2}} \times 10 = 11.11A \quad (43)$$

12Vの出力電圧に対して定格20Vを採用します。

$$V_{LLCcap} = 20V \quad (44)$$

この容量のRMS定格電流は次のとおりです。

$$I_{C(out)} = \sqrt{\left(\frac{\pi}{2\sqrt{2}} I_{OUT}\right)^2 - I_{OUT}^2} = \sqrt{\left(\frac{\pi}{2\sqrt{2}} \times 10\right)^2 - 10^2} = 4.84A \quad (45)$$

導電性高分子技術を採用した固体アルミニウム容量は、定格リップル電流が高いため、ここでは良い選択肢となります。1つの容量の定格リップル電流では十分でないため、多くの場合、複数の容量を並列接続します。

LLC段の出力時のリップル電圧は、容量に流れるAC電流量の関数です。この電圧を推計するため、負荷のDC電流を含むすべての電流がフィルタ容量に流れるものと仮定します。

$$ESR_{max} = \frac{V_{OUT(pk-pk)}}{I_{RECT}(pk)} = \frac{0.3V}{2\frac{\pi}{4} \times 10A} = 19m\Omega \quad (46)$$

容量の仕様は次のとおりです。

- 定格電圧: 20V

- 定格リップル電流: 4.84A

- ESR: 19mΩ未満

### 8.2.2.15 HVピン直列抵抗

HVピンに複数の抵抗を直列につないで、UCC256301の消費電力を制限します。推奨するHVピン直列抵抗は5kΩです。

### 8.2.2.16 BLKピン分圧器

BLKピンはLLC入力電圧を検知して、LLCコンバータをオンおよびオフにするタイミングを決定します。UCC256301の型番によって、BLKの閾値は異なります。

バルク起動電圧を340Vとすると、BLK抵抗分圧比は次のように計算できます。

$$k_{BLK} = \frac{340V}{3V} = 113.33 \quad (47)$$

BLKピン分圧抵抗の望ましい消費電力は  $P_{BLKsns} = 10mW$  です。BLKが検知する抵抗の合計値は次の式で求められます。

$$R_{BLKsns} = \frac{V_{IN(nom)}^2}{P_{BLKsns}} = \frac{390^2}{0.01} = 15.21M\Omega \quad (48)$$

2次BLK分圧抵抗値は次の式で求められます。

$$R_{BLKlower} = \frac{R_{BLKsns}}{k_{BLK}} = \frac{15.21M\Omega}{113.33} = 134k\Omega \quad (49)$$

1次BLK分圧抵抗値は次の式で求められます。

$$R_{BLKupper} = R_{BLKsns} - R_{BLKlower} = 15.08M\Omega \quad (50)$$

実際のバルク電圧閾値は次のように計算できます。

$$V_{BulkStart} = 340V \quad (51)$$

$$V_{BulkStop} = 340V \times \frac{0.9}{3} = 102V \quad (52)$$

$$V_{BulkOVRise} = 340V \times \frac{4}{3} = 453V \quad (53)$$

$$V_{BulkOVFall} = 340V \times \frac{3.75}{3} = 425V \quad (54)$$

### 8.2.2.17 BWピン分圧器

BWピンはバイアス巻線により出力を検知し、電力段を過電圧から保護します。通常の出力電圧は12Vです。バイアス巻線のターン数は3で、2次側巻線のターン数は2です。したがって、バイアス巻線の公称電圧は次の式で求められます。

$$V_{BiasWindingNom} = 12V \times \frac{3}{2} = 18V \quad (55)$$

この設計に望ましいOVPの閾値は、公称値の115%です。UCC256301のOVP閾値レベルは4Vであるため、公称BWピン電圧は次の式で求められます。

$$V_{BWnom} = \frac{4V}{115\%} = 3.48V \quad (56)$$

BW分圧抵抗の2次抵抗を10kΩとします。

$$R_{BWlower} = 10k\Omega \quad (57)$$

1次抵抗は次の式で計算できます。

$$R_{BWupper} = R_{BWlower} \times \left( \frac{V_{BiasWindingNom} - V_{BWnom}}{V_{BWnom}} \right) = 10k\Omega \times \left( \frac{18 - 3.48}{3.48} \right) = 41.75k\Omega \quad (58)$$

### 8.2.2.18 ISNSピン微分器

ISNS端子の電圧設定にて過電流を検出する値を調整できます。OCP1はピーク電流保護レベルであり、OCP2およびOCP3は平均電流保護レベルです。閾値電圧は、それぞれ0.6V、0.8V、4Vです。

OCP3のレベルを全負荷の150%に設定します。これにより、全負荷で検知される平均入力電流レベルは次の式で求められます。

$$V_{ISNSfullload} = \frac{0.6V}{150\%} = 0.4V \quad (59)$$

そこで電流検知比は次のように計算できます。

$$k_{ISNS} = \frac{V_{ISNSfullload}}{\left( \frac{P_{OUT}}{\eta} \times \frac{1}{V_{bulknom}} \right)} = \frac{0.4V}{\left( \frac{120W}{0.94} \times \frac{1}{390V} \right)} = 1.222 \Omega \quad (60)$$

抵抗に比べて高電圧容量の選択肢は少ないため、まず電流検知容量を選定します。

$$C_{ISNS} = 150 \text{ pF} \quad (61)$$

それから必要なISNS抵抗値を計算します。

$$R_{ISNS} = \frac{k_{ISNS} C_r}{C_{ISNS}} = \frac{1.222 \Omega \times 44n}{150p} = 358.45 \Omega \quad (62)$$

電流検知比を求めたら、全負荷時のピークISNSピン電圧を次のように計算できます。

$$V_{ISNSpeak} = \sqrt{2} I_r \times k_{ISNS} = \sqrt{2} \times 1.009A \times 1.222 \Omega = 1.74V \quad (63)$$

OCP1レベルでのピーク共振電流は次の式で求められます。

$$I_{respeakOCP1} = \frac{4V}{1.222\Omega} = 3.27A \quad (64)$$

OCP1レベルでのピーク2次側電流は次の式で求められます。

$$I_{secpeakOCP1} = I_{respeakOCP1} \frac{N_{pri}}{N_{sec}} = 3.27A \times \frac{32}{2} = 52.37A \quad (65)$$

### 8.2.2.19 VCRピン・分圧容量

VCRピンの分圧容量は、(1)共振容量電圧の分割比、(2)追加する周波数補償の量という2つのパラメータを設定します。分圧容量が満たすべき第一の基準は、過負荷条件下でVCRピンのピーク・ツー・ピーク電圧が6V以内であることです。

すでに述べているように、VCOMP電圧、 $\Delta VCR$ 、スイッチング期間、入力平均電流、VCR分圧容量の関係を式 66 に示します。

$$VCOMP = \Delta VCR \approx \frac{C_1}{C_1 + C_2} \frac{1}{C_r} \times I_{IN(avg)} \times T + I_{COMP} \times \frac{1}{C_1 + C_2} \times \frac{T}{2} \quad (66)$$

この式において、 $C_1$ は分圧容量の1次容量であり、 $C_{12}$ は分圧容量の2次容量です。VCOMPは、分割された共振容量電圧と、VCRピン内部電流源から生じた電圧という2つの部分で分担されます。内部電流源の分担を $K_{VCRRamp}$ と定義します。

$$K_{VCRRamp} = \frac{I_{COMP} \times \frac{1}{C_1 + C_2} \times \frac{T}{2}}{\frac{C_1}{C_1 + C_2} \frac{1}{C_r} \times I_{IN(avg)} \times T + I_{COMP} \times \frac{1}{C_1 + C_2} \times \frac{T}{2}} = \frac{1}{\frac{C_1}{C_r} \frac{I_{IN(avg)}}{I_{COMP}} \times 2 + 1} \quad (67)$$

$C_1$ および $C_2$ は、 $K_{VCRRamp}$ が0.1~0.6の範囲内に収まり、過負荷条件下ではVCOMPが6Vを下回るように選択します。この例では、 $C_1 = 150\text{pF}$ および $C_2 = 15\text{nF}$ を選択します。

### 8.2.2.20 バースト・モードの調整

バースト・モード調整インターフェイスにより、入力電圧に応じて変化するバースト・モード閾値電圧(VLL)の調整が可能です。これにより、 $V_{IN}$ 範囲全体にわたって安定したバースト閾値が実現し、 $V_{IN}$ 範囲全体にわたって効率曲線がより安定したものになります。

VLL電圧とBLKピン電圧の間には次の関係があります。

$$VLL = a \times VBLK + b \quad (68)$$

この式では、VLLはバースト・モード閾値電圧、VBLKはBLKピン電圧で、aとbという2つのパラメータを2つの外付け抵抗で調整できます。

ソフトスタートが完了すると、検知されたBLKピン電圧が、バッファによりIC内部からLL/SSピンに印加されます。以下の図に示すとおり、これにより、調整抵抗 $R_{LLUpper}$ と $R_{LLLLower}$ を流れる電流に差が生じます。LL/SSピンに流入する電流の差は、定倍され、 $250\text{k}\Omega$ の抵抗 $R_{II}$ に印加されます。 $R_{II}$ の電圧をVLLとして用います。

図 55. バースト・モードの調整

そこでVLLとVBLKの関係が次のように導き出されます。

$$\frac{VRVCC - VBLK}{R_{LLUpper}} - \frac{VBLK}{R_{LLLLower}} = \frac{VLL}{R_{LL}} \quad (69)$$

式 69を並べ替えると式 70になります。

$$VLL = -\frac{(R_{LLUpper} + R_{LLLLower}) \times R_{LL}}{R_{LLUpper} R_{LLLLower}} \times VBLK + \frac{R_{LL}}{R_{LLUpper}} VRVCC \quad (70)$$

$R_{LLUpper}$  と  $R_{LLLLower}$  を求めるには、2組の(VLL、VBLK)値が必要です。VBLKはBLKピンから直接測定できます。VLLレベルは、帰還オプトカプラ・エミッタとGNDの間に  $10k\Omega$  の抵抗を入れることによって測定できます。 $10k\Omega$  の抵抗で測定された電圧が  $V_{10k}$  だと仮定します。そこでVLL電圧は次のように計算できます。

$$VLL = \left( I_{FB} - \frac{V_{10\,k\Omega}}{10\,k\Omega} \right) \times 100\,k\Omega \quad (71)$$

$R_{LLUpper}$ を削除します。これにより、VLL電圧はその最小値である0.7Vとなります。この値は内部回路設計で決まります。それから負荷電流を望ましいバースト・モード閾値負荷レベルに調整し、この条件で電力段がバーストしないことを確認します。例えば、10%負荷が望ましいバースト・モード閾値レベルだとします。10Aを全負荷条件とし、負荷電流を1Aに設定します。負荷電流を設定したら、入力電圧を2種類の電圧に変更し、2種類の測定値を記録します( $V10k$ 、 $VBLK$ )。そこで式 70および式 71に基づき、 $R_{LLUpper}$ と $R_{LLLLower}$ の解を出すことができます。

この例では、2次抵抗が402kΩ、1次抵抗が732kΩとなります。

### 8.2.2.21 ソフトスタート容量

ソフトスタート容量は、ソフトスタート・ランプの速度を設定します。ソフトスタート時間は負荷条件によって変わります。全負荷または過負荷条件では、ソフトスタート時間が最長となります。ソフトスタート時間の正確な値を計算するのは容易ではありません。しかし、全負荷条件下の最長ソフトスタート時間は次の式で推計できます。

$$T_{SS} = \frac{7V \times C_{SS}}{25\mu A} \quad (72)$$

150nFのソフトスタート容量を使用した場合、式 72により最長ソフトスタート時間は42msとなります。

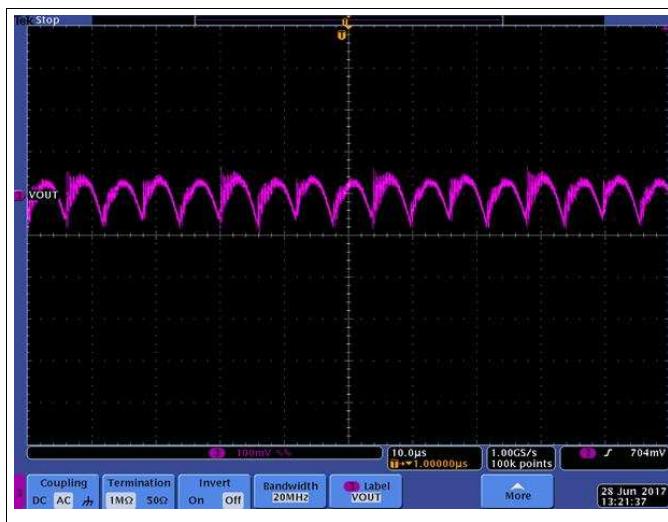

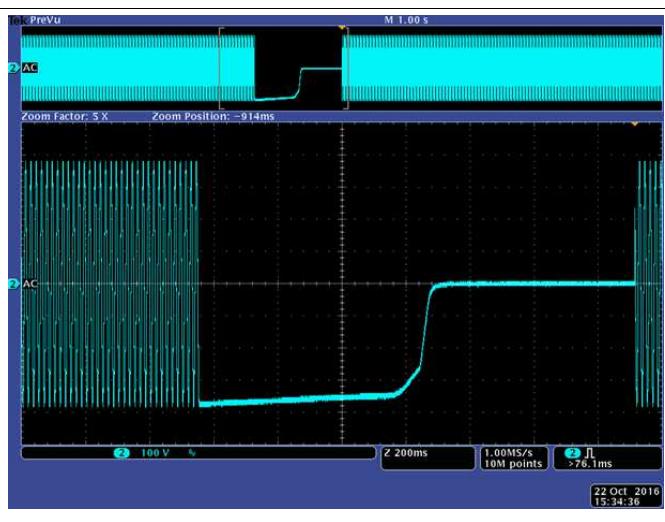

### 8.2.3 アプリケーション曲線

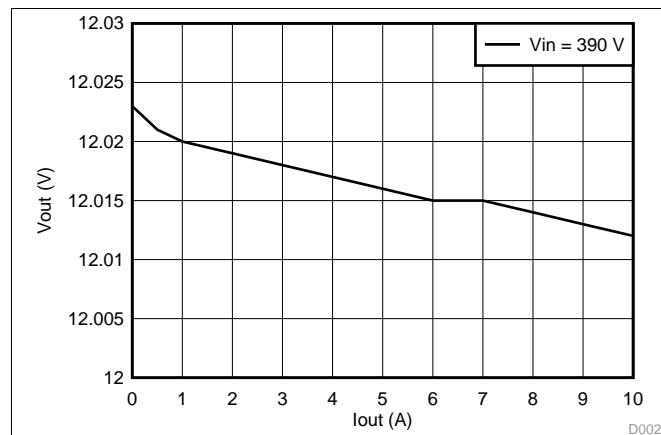

図 56.

図 57.

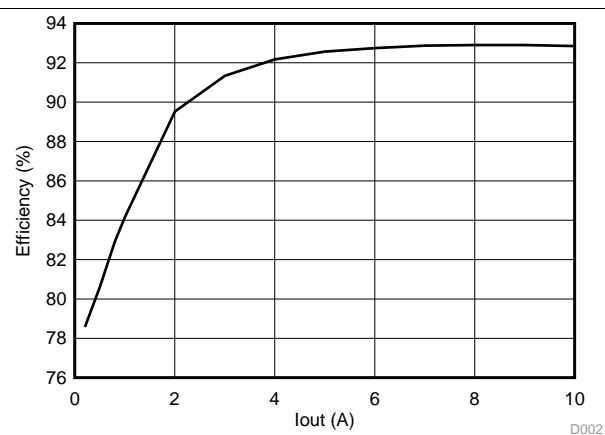

図 58.

図 59.

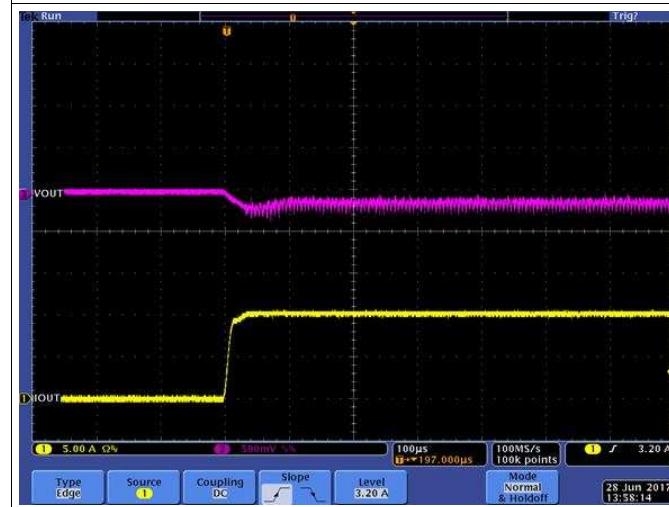

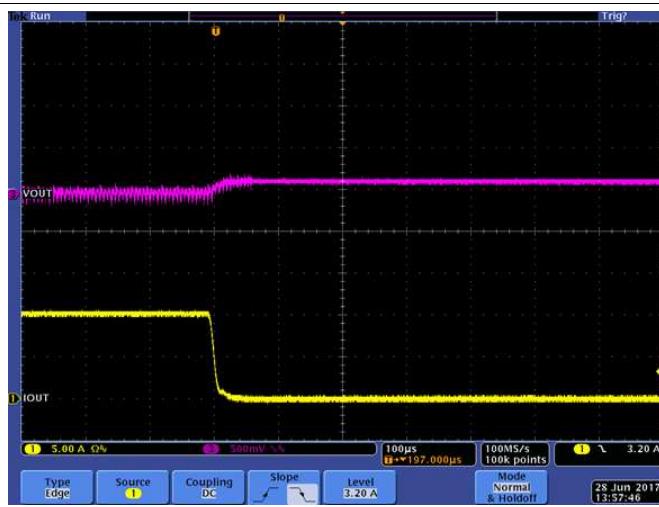

**図 60.**

**図 61.**

## 9 電源に関する推奨事項

### 9.1 VCC容量

VCC容量は、システムに必要な総起動電荷量に基づいて決定する必要があります。起動電荷は、ほとんどゲート・ドライバ回路によって消費されます。このため、総起動電荷量は、起動スイッチング周波数、MOSFETゲート電荷、ソフトスタート時間から推計できます。

システムに必要な総起動電荷量を仮定し、式 73に示します。

$$Q_{tot} = 1.6 \text{ mC} \quad (73)$$

PFCおよびLLC起動フェーズにおいて、許容される最大VCC電圧降下は次のとおりです。

$$V_{ccdropmax} = 26V - 10.5V = 15.5V \quad (74)$$

必要とされる最小VCC容量:

$$C_{VCC} = \frac{Q_{tot}}{V_{ccdropmax}} = \frac{1.6 \text{ mC}}{15.5V} = 103 \mu\text{F} \quad (75)$$

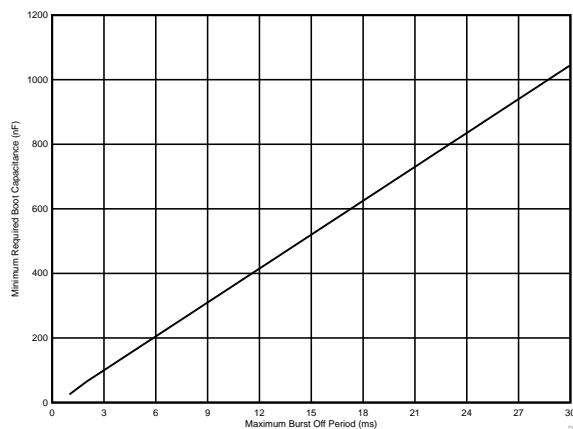

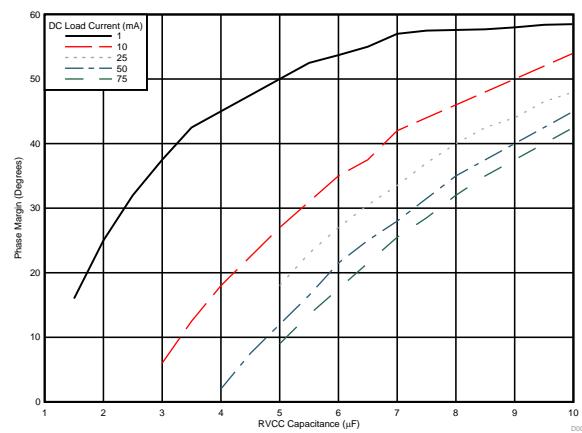

110 $\mu$ Fの容量を選択します。