UCC23511 JAJSHR2B - SEPTEMBER 2019 - REVISED OCTOBER 2020

# UCC23511 ソース 1.5A、シンク 2A、5.7kV<sub>RMS</sub>、フォトカプラ互換、 シングル・チャネル絶縁型ゲート・ドライバ

### 1 特長

Texas

INSTRUMENTS

- フォトカプラ互換入力付きの 5.7kV<sub>RMS</sub> シングル・チャ ネル絶縁型ゲート・ドライバ

- 光絶縁型ゲート・ドライバに対して、ピン互換でドロップ イン・アップグレード可能

- ソース 1.5A、シンク 2A のピーク出力電流

- 最大 33V の出力ドライバ電源電圧

- 8V (B) または 12V の VCC UVLO を選択可能 •

- レール・ツー・レール出力 •

- 伝搬遅延時間:105ns 以下

- 部品間遅延ばらつき:25ns 以下

- パルス幅歪み:35ns 以下

- 同相過渡耐性 (CMTI):150kV/µs 以上

- 絶縁バリアの寿命:50年超

- 入力段で 13V の逆極性電圧を扱えるためインターロッ クをサポート可能

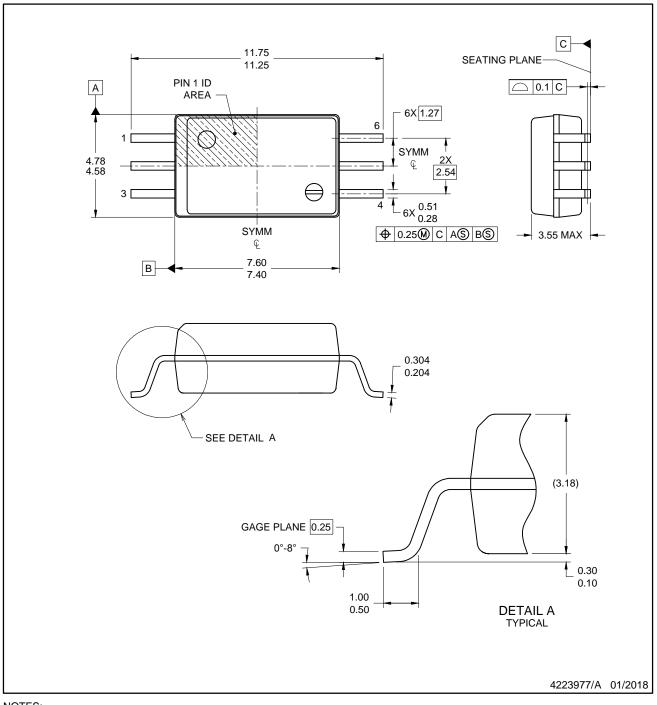

- 沿面距離と空間距離が 8.5mm を超える、ストレッチ SO-6 パッケージ

- 動作時の接合部温度、T」:-40℃~+150℃

- 安全性関連の認定 (予定):

- UL 1577 に準拠した絶縁耐圧:5.7kV<sub>RMS</sub> (1 分間)

- 8000 VPK 強化絶縁 DIN V VDE V0884-11:2017-01 準拠

- GB4943.1-2011 準拠の CQC 認定

## 2 アプリケーション

- 産業用モータ制御ドライブ

- 産業用電源、UPS

- 太陽光インバータ

- 誘導加熱

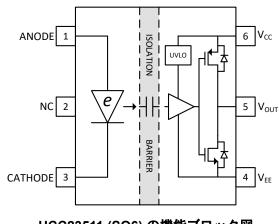

UCC23511 (SO6)の機能ブロック図

## 3 概要

UCC23511 は、IGBT、MOSFET、SiC MOSFET 用の、 フォトカプラ互換、シングル・チャネル絶縁型ゲート・ドライ バです。ソース 1.5A、シンク 2A のピーク電流を出力で き、5.7kV<sub>RMS</sub>の強化絶縁定格を持っています。電源電圧 範囲が 33V と高いため、バイポーラ電源を使用して IGBT および SiC パワー FET を効果的に駆動できます。 UCC23511 は、ローサイドとハイサイドの両方のパワー FET を駆動できます。主な機能と特性は、標準的なフォト カプラ・ベースのゲート・ドライバに比べて性能と信頼性を 大幅に向上させると同時に、回路設計とレイアウト設計の 両方でピン互換性を維持しています。同相過渡耐性 (CMTI) が高く、伝搬遅延時間が短く、パルス幅歪みが小 さいという特長があります。厳密なプロセス制御により、部 品間スキューも小さくなっています。入力段はダイオード・ エミュレーション (ediode) であり、従来の LED に比べて、 長期的な信頼性と優れた経時特性を実現します。本デバ イスは、沿面距離と空間距離がどちらも 8.5mm を超え、 材料グループ I (比較トラッキング指数 (CTI) > 600V) の モールド・コンパウンドを使用した、ストレッチ SO6 パッケ ージで供給されます。UCC23511 は高性能で信頼性が 高いため、あらゆる種類のモータ駆動、ソーラー・インバー タ、産業用電源、電化製品に最適です。高い温度で動作 するため、従来のフォトカプラでは対応できなかったアプリ ケーションで活用する機会が広がります。

製品情報(1)

| 部品番号     | パッケージ             | 本体サイズ (公称)     |

|----------|-------------------|----------------|

| UCC23511 | ストレッチ <b>SO-6</b> | 7.5mm × 4.68mm |

利用可能なすべてのパッケージについては、このデータシートの (1)末尾にある注文情報を参照してください。

## **Table of Contents**

| 1 | 特長1                                    |   |

|---|----------------------------------------|---|

|   | アプリケーション1                              |   |

|   | 既要1                                    |   |

| 4 | Revision History                       |   |

| 5 | Pin Configuration and Function         | 3 |

|   | Pin Functions                          | 3 |

| 6 | Specifications                         | Ł |

|   | 6.1 Absolute Maximum Ratings4          | ł |

|   | 6.2 ESD Ratings                        | Ł |

|   | 6.3 Recommended Operating Conditions4  | Ł |

|   | 6.4 Thermal Information4               |   |

|   | 6.5 Power Ratings                      | 5 |

|   | 6.6 Insulation Specifications6         | 3 |

|   | 6.7 Safety-Related Certifications7     | 7 |

|   | 6.8 Safety Limiting Values7            | 7 |

|   | 6.9 Electrical Characteristics         | 3 |

|   | 6.10 Switching Characteristics         |   |

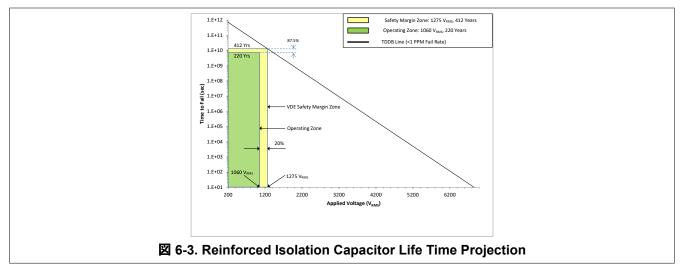

|   | 6.11 Insulation Characteristics Curves | ) |

|   | 6.12 Typical Characteristics11         |   |

| 7 | Parameter Measurement Information13    | 3 |

| 7.1 Propagation Delay, rise time and fall time  | 13 |

|-------------------------------------------------|----|

| 7.2 I <sub>OH</sub> and I <sub>OL</sub> testing |    |

| 7.3 CMTI Testing                                |    |

| 8 Detailed Description                          |    |

| 8.1 Overview                                    |    |

| 8.2 Functional Block Diagram                    |    |

| 8.3 Feature Description.                        |    |

| 8.4 Device Functional Modes                     |    |

| 9 Application and Implementation                |    |

| 9.1 Application Information                     |    |

| 9.2 Typical Application                         |    |

| 10 Power Supply Recommendations                 |    |

| 11 Layout                                       |    |

| 11.1 Layout Guidelines                          |    |

| 11.2 Layout Example                             |    |

| 11.3 PCB Material                               |    |

| 11.4 Custom Design With WEBENCH® Tools          |    |

| 12 Mechanical, Packaging, and Orderable         |    |

| Information                                     | 22 |

|                                                 |    |

|                                                 |    |

### **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| CI | hanges from Revision A (October 2019) to Revision B (October 2020) | Page |

|----|--------------------------------------------------------------------|------|

| •  | Added UCC23511B orderble to include 8-V UVLO option                | 8    |

| Changes from Revision * (September 2019) to Revision A (October 2019) | Page |

|-----------------------------------------------------------------------|------|

| <ul> <li>マーケティング・ステータスを「事前情報」から「初版リリース」に変更</li> </ul>                 | 1    |

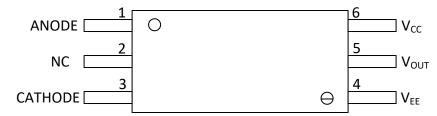

### **5** Pin Configuration and Function

#### 図 5-1. UCC23511 Package SO-6 Top View

### **Pin Functions**

| PIN              |                 |   |                             |  |  |

|------------------|-----------------|---|-----------------------------|--|--|

| NAME             | NO.<br>UCC23511 |   | DESCRIPTION                 |  |  |

| NAME             |                 |   |                             |  |  |

| ANODE            | 1               | I | Anode                       |  |  |

| CATHODE          | 3               | I | Cathode                     |  |  |

| NC               | 2               | - | No Connection               |  |  |

| V <sub>CC</sub>  | 6               | Р | Positive output supply rail |  |  |

| V <sub>EE</sub>  | 4               | Р | Negative output supply rail |  |  |

| V <sub>OUT</sub> | 5               | 0 | Gate-drive output           |  |  |

(1) P = Power, G = Ground, I = Input, O = Output

## 6 Specifications

### 6.1 Absolute Maximum Ratings

Over operating free air temperature range (unless otherwise noted)<sup>(1)</sup>

|                              |                                         | MIN  | MAX | UNIT |

|------------------------------|-----------------------------------------|------|-----|------|

| Average Input Current        | I <sub>F(AVG)</sub>                     | -    | 25  | mA   |

| Peak Transient Input Current | I <sub>F(TRAN)</sub> <1us pulse, 300pps |      | 1   | А    |

| Reverse Input Voltage        | V <sub>R(MAX)</sub>                     |      | 14  | V    |

| Output supply voltage        | V <sub>CC</sub> – V <sub>EE</sub>       | -0.3 | 35  | V    |

| Output signal voltage        | V <sub>OUT</sub> – V <sub>CC</sub>      |      | 0.3 | V    |

| Output signal voltage        | V <sub>OUT</sub> – V <sub>EE</sub>      | -0.3 |     | V    |

| Junction temperature         | T <sub>J</sub> <sup>(2)</sup>           | -40  | 150 | °C   |

| Storage temperature          | T <sub>stg</sub>                        | -65  | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) To maintain the recommended operating conditions for T<sub>J</sub>, see the  $\frac{2}{2} \frac{2}{3} \frac{6.4}{6.4}$  section.

### 6.2 ESD Ratings

|                    |               |                                                                                | VALUE | UNIT |

|--------------------|---------------|--------------------------------------------------------------------------------|-------|------|

|                    | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±4000 |      |

| V <sub>(ESD)</sub> |               | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

|                      |                                                           |                                 | MIN | NOM MAX | UNIT |

|----------------------|-----------------------------------------------------------|---------------------------------|-----|---------|------|

| V <sub>CC</sub>      | Output Supply Voltage(V <sub>CC</sub> – V <sub>EE</sub> ) | UCC23511 (12-V<br>UVLO Version) | 14  | 33      | V    |

| V <sub>CC</sub>      | Output Supply Voltage(V <sub>CC</sub> – V <sub>EE</sub> ) | UCC23511B (8-V<br>UVLO Version) | 10  | 33      | V    |

| I <sub>F</sub> (ON)  | Input Diode Forward Current (Diode "ON")                  |                                 | 7   | 16      | mA   |

| V <sub>F</sub> (OFF) | Anode voltage - Cathode voltage (Diode "OFF")             |                                 | -13 | 0.9     | V    |

| TJ                   | Junction temperature                                      |                                 | -40 | 150     | °C   |

| T <sub>A</sub>       | Ambient temperature                                       |                                 | -40 | 125     | °C   |

#### **6.4 Thermal Information**

|                       |                                              | UCC23511 |      |

|-----------------------|----------------------------------------------|----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | SO6      | UNIT |

|                       |                                              | 6 Pins   |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 126      | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 66.1     | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 62.8     | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 29.6     | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 60.8     | °C/W |

(1) For more information about traditional and new thermal metrics, see the http://www.ti.com/lit/SPRA953 application report.

### 6.5 Power Ratings

|                 | PARAMETER                                      | TEST CONDITIONS                                                                                                        | MIN | TYP | MAX | UNIT |

|-----------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| P <sub>D</sub>  | Maximum power dissipation on input and output  | V <sub>CC</sub> = 20 V, I <sub>F</sub> = 10mA 10-kHz, 50% duty<br>cycle, square wave,180-nF load, T <sub>A</sub> =25°C |     |     | 750 | mW   |

| P <sub>D1</sub> | Maximum input power dissipation <sup>(1)</sup> |                                                                                                                        |     |     | 10  | mW   |

| P <sub>D2</sub> | Maximum output power dissipation               |                                                                                                                        |     |     | 740 | mW   |

(1) Recommended maximum PD1 = 40mW. Absolute maximum PD1 = 55mW

### 6.6 Insulation Specifications

|                   | PARAMETER                                             | TEST CONDITIONS                                                                                                                                                                                                  | SPECIFIC<br>ATION | UNIT             |

|-------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|

| CLR               | External clearance <sup>(1)</sup>                     | Shortest terminal-to-terminal distance through air                                                                                                                                                               | >8.5              | mm               |

| CPG               | External Creepage <sup>(1)</sup>                      | Shortest terminal-to-terminal distance across the package surface                                                                                                                                                | >8.5              | mm               |

| DTI               | Distance through the insulation                       | Minimum internal gap (internal clearance)                                                                                                                                                                        | >17               | μm               |

| СТІ               | Comparative tracking index                            | DIN EN 60112 (VDE 0303-11); IEC 60112                                                                                                                                                                            | >600              | V                |

|                   | Material Group                                        | According to IEC 60664-1                                                                                                                                                                                         | I                 |                  |

|                   |                                                       | Rated mains voltage ≤ 600 V <sub>RMS</sub>                                                                                                                                                                       | I-IV              |                  |

|                   | Overvoltage category per IEC 60664-1                  | Rated mains voltage ≤ 1000 V <sub>RMS</sub>                                                                                                                                                                      | 1-111             |                  |

| DIN V VD          | DE 0884-11 (VDE V 0884-11) <sup>(2)</sup>             |                                                                                                                                                                                                                  |                   |                  |

| V <sub>IORM</sub> | Maximum repetitive peak isolation voltage             | AC voltage (bipolar)                                                                                                                                                                                             | 2121              | V <sub>PK</sub>  |

| V <sub>IOWM</sub> | Maximum isolation working voltage                     | AC voltage (sine wave); time-dependent dielectric<br>breakdown (TDDB) test; see Figure 1                                                                                                                         | 1500              | V <sub>RMS</sub> |

|                   |                                                       | DC voltage                                                                                                                                                                                                       | 2121              | V <sub>DC</sub>  |

| V <sub>IOTM</sub> | Maximum transient isolation voltage                   | $V_{TEST} = V_{IOTM}$ , t = 60 sec (qualification)<br>$V_{TEST} = 1.2 \times V_{IOTM}$ , t = 1 s (100% production)                                                                                               | 8000              | V <sub>PK</sub>  |

| V <sub>IOSM</sub> | Maximum surge isolation voltage <sup>(3)</sup>        | Test method per IEC 62368, 1.2/50 ms waveform, $V_{TEST}$ = 1.6 x $V_{IOSM}$ = 12800 $V_{PK}$ (qualification)                                                                                                    | 8000              | V <sub>PK</sub>  |

|                   |                                                       | $ \begin{array}{l} \mbox{Method a: After I/O safety test subgroup 2/3, V_{ini} = $V_{IOTM}$, $t_{ini} = 60 s; V_{pd(m)} = 1.2 x V_{IORM} = 1800 V_{PK}$, $t_m = $10 s$ \end{array} $                             | ≤5                |                  |

| q <sub>pd</sub>   | Apparent charge <sup>(4)</sup>                        | Method a: After environmental tests subgroup 1,<br>$V_{ini} = V_{IOTM}$ , $t_{ini} = 60$ s; $V_{pd(m)} = 1.6$ x $V_{IORM} = 2400$ $V_{PK}$ , $t_m = 10$ s                                                        | ≤5                | рС               |

|                   |                                                       | Method b1: At routine test (100% production) and preconditioning (type test), $V_{ini} = V_{IOTM}$ , $t_{ini} = 1$ s; $V_{pd(m)} = 1.875 \text{ x } V_{IORM} = 2813 V_{PK}$ , $t_m = 1$ s                        | ≤5                |                  |

| C <sub>IO</sub>   | Barrier capacitance, input to output <sup>(5)</sup>   | V <sub>IO</sub> = 0.4 x sin (2πft), f = 1 MHz                                                                                                                                                                    | 0.5               | pF               |

|                   |                                                       | V <sub>IO</sub> = 500 V, T <sub>A</sub> = 25°C                                                                                                                                                                   | >10 <sup>12</sup> |                  |

| R <sub>IO</sub>   | Insulation resistance, input to output <sup>(5)</sup> | $V_{IO} = 500 \text{ V}, \ 100^{\circ}\text{C} \le \text{T}_{A} \le 125^{\circ}\text{C}$                                                                                                                         | >10 <sup>11</sup> | Ω                |

|                   |                                                       | V <sub>IO</sub> = 500 V at T <sub>S</sub> = 150°C                                                                                                                                                                | >10 <sup>9</sup>  |                  |

|                   | Pollution degree                                      |                                                                                                                                                                                                                  | 2                 |                  |

|                   | Climatic category                                     |                                                                                                                                                                                                                  | 40/125/21         |                  |

| UL 1577           |                                                       |                                                                                                                                                                                                                  | I                 |                  |

| V <sub>ISO</sub>  | Withstand isolation voltage                           | $\label{eq:VTEST} \begin{array}{l} V_{TEST} = V_{ISO} = 5700 \; V_{RMS},  t = 60 \; s \; (qualification), \\ V_{TEST} = 1.2 \; x \; V_{ISO} = 6840 \; V_{RMS},  t = 1 \; s \; (100\% \\ production) \end{array}$ | 5700              | V <sub>RMS</sub> |

|                   |                                                       |                                                                                                                                                                                                                  |                   |                  |

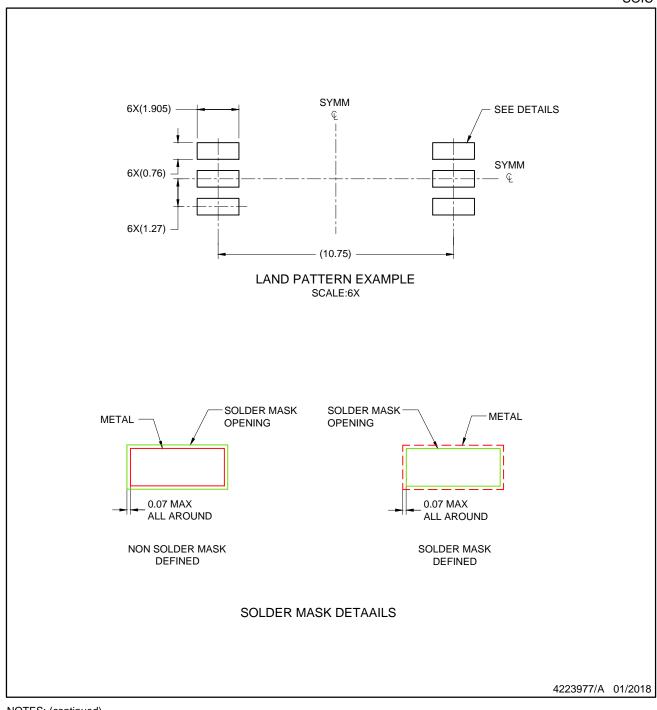

(1) Creepage and clearance requirements should be applied according to the specific equipment isolation standards of an application. Care should be taken to maintain the creepage and clearance distance of a board design to ensure that the mounting pads of the isolator on the printed-circuit board do not reduce this distance. Creepage and clearance on a printed-circuit board become equal in certain cases. Techniques such as inserting grooves, ribs, or both on a printed-circuit board are used to help increase these specifications.

(2) This coupler is suitable for safe electrical insulation only within the safety ratings. Compliance with the safety ratings shall be ensured by means of suitable protective circuits.

- (3) Testing is carried out in air or oil to determine the intrinsic surge immunity of the isolation barrier.

- (4) Apparent charge is electrical discharge caused by a partial discharge (pd).

(5) All pins on each side of the barrier tied together creating a two-pin device.

### 6.7 Safety-Related Certifications

| VDE                                                                                                                                                                                        | UL                                                                    | CQC                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------|

| Plan to certify according to DIN V VDE V 0884-11: 2017-01                                                                                                                                  | Plan to certify according to UL 1577<br>Component Recognition Program | Plan to certify according to GB4943.1-2011                    |

| Reinforced insulation Maximum transient isolation voltage, $8000 V_{PK}$ ;<br>Maximum repetitive peak isolation voltage, 2121 $V_{PK}$ ;<br>Maximum surge isolation voltage, $8000 V_{PK}$ | Single protection, 5700 V <sub>RMS</sub>                              | Reinforced insulation, Altitude ≤ 5000 m,<br>Tropical Climate |

| Certificate planned <sup>(1)</sup>                                                                                                                                                         | File number: E181974 <sup>(1)</sup>                                   | Certificate planned <sup>(1)</sup>                            |

(1) UCC23511B certification in progress

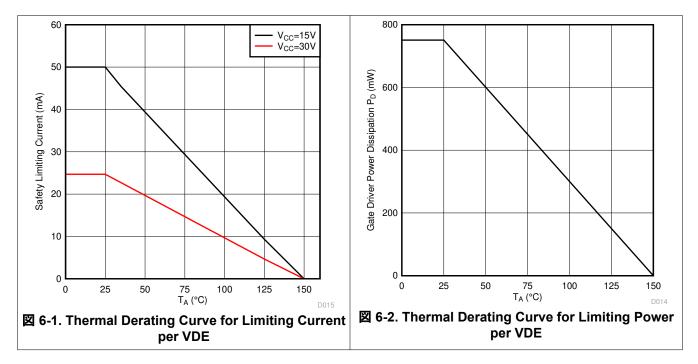

#### 6.8 Safety Limiting Values

| PARAMETER      |                                           | TEST CONDITIONS                                                                          | MIN | TYP | MAX | UNIT      |  |  |

|----------------|-------------------------------------------|------------------------------------------------------------------------------------------|-----|-----|-----|-----------|--|--|

|                |                                           | $R_{qJA} = 126^{\circ}C/W, V_{I} = 15 V, T_{J} = 150^{\circ}C,$<br>$T_{A} = 25^{\circ}C$ | Э,  |     | 50  |           |  |  |

| IS             | Safety input, output, or supply current   | $R_{qJA} = 126^{\circ}C/W, V_{I} = 30 V, T_{J} = 150^{\circ}C,$<br>$T_{A} = 25^{\circ}C$ |     |     | 25  | — mA<br>5 |  |  |

| Ps             | Safety input, output, or total power      | R <sub>qJA</sub> = 126°C/W, T <sub>J</sub> = 150°C, T <sub>A</sub> = 25°C                |     |     | 750 | mW        |  |  |

| Τ <sub>S</sub> | Maximum safety temperature <sup>(1)</sup> |                                                                                          |     |     | 150 | °C        |  |  |

(1) The maximum safety temperature,  $T_S$ , has the same value as the maximum junction temperature,  $T_J$ , specified for the device. The  $I_S$  and  $P_S$  parameters represent the safety current and safety power respectively. The maximum limits of  $I_S$  and  $P_S$  should not be exceeded. These limits vary with the ambient temperature,  $T_A$ . The junction-to-air thermal resistance,  $R_{qJA}$ , in the Thermal Information table is that of a device installed on a high-K test board for leaded surface-mount packages. Use these equations to calculate the value for each parameter:  $T_J = T_A + R_{qJA}$  ' P, where P is the power dissipated in the device.  $T_{J(max)} = T_S = T_A + R_{qJA}$  ' P<sub>S</sub>, where  $T_{J(max)}$  is the maximum allowed junction temperature.  $P_S = I_S$  ' V<sub>1</sub>, where VI is the maximum supply voltage.

### **6.9 Electrical Characteristics**

Unless otherwise noted, all typical values are at  $T_A = 25^{\circ}$ C,  $V_{CC}-V_{EE}= 15$ V,  $V_{EE}=$  GND. All min and max specifications are at recommended operating conditions ( $T_J = -40$ C to  $150^{\circ}$ C,  $I_{F(on)}= 7$  mA to 16 mA,  $V_{EE}=$  GND,  $V_{CC}= 15$  V to 30 V,  $V_{F(off)}= -5$ V to 0.8V)

| PARAMETER           |                                             | TEST CONDITIONS MIN                                                                                                                                                                                        |      | TYP  | MAX  | UNIT  |

|---------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| INPUT               |                                             | L L                                                                                                                                                                                                        |      |      | I    |       |

| I <sub>FLH</sub>    | Input Forward Threshold Current Low to High | V <sub>OUT</sub> > 5 V, Cg = 1 nF                                                                                                                                                                          | 1.5  | 2.8  | 4    | mA    |

| V <sub>F</sub>      | Input Forward Voltage                       | I <sub>F</sub> =10 mA                                                                                                                                                                                      | 1.8  | 2.1  | 2.4  | V     |

| V <sub>F_HL</sub>   | Threshold Input Voltage High to Low         | V < 5 V, Cg = 1 nF                                                                                                                                                                                         | 0.9  |      |      | V     |

| ΔV <sub>F</sub> /ΔT | Temp Coefficient of Input Forward Voltage   | I <sub>F</sub> =10 mA                                                                                                                                                                                      |      | 1    | 1.35 | mV/°C |

| V <sub>R</sub>      | Input Reverse Breakdown Voltage             | I <sub>R</sub> = 10 uA                                                                                                                                                                                     | 15   |      |      | V     |

| C <sub>IN</sub>     | Input Capacitance                           | F = 0.5 MHz                                                                                                                                                                                                |      | 15   |      | pF    |

| OUTPUT              |                                             | · · · · ·                                                                                                                                                                                                  |      |      |      |       |

| I <sub>OH</sub>     | High Level Peak Output Current              | $\label{eq:lemma} \begin{array}{l} I_F = 10 \text{ mA}, V_{CC} = 15V, \\ C_{LOAD} = 0.18 \text{uF}, \\ R_G  total = 6\Omega \\ (^1),  C_{VDD} = 10 \text{uF}, \\ Pulse \ width < 10 \text{us} \end{array}$ | 1    | 1.5  |      | A     |

| I <sub>OL</sub>     | Low Level Peak Output Current               | $\label{eq:constraint} \begin{array}{l} V_F{=}\;0\;V,V_{CC}\;{=}15V,\\ C_{LOAD}{=}0.18uF,\\ R_{G\_total}{=}6\Omega^{(1)},\\ C_{VDD}{=}10uF,\\ Pulse\;width\;{<}10us \end{array}$                           | 1    | 2.0  |      | A     |

| V <sub>OH</sub>     | High Level Output Voltage                   | $I_F$ = 10 mA, $I_O$ = -20mA<br>(with respect to VCC)                                                                                                                                                      | 0.07 | 0.18 | 0.36 | V     |

|                     |                                             | $I_{\rm F}$ = 10 mA, $I_{\rm O}$ = 0 mA                                                                                                                                                                    |      | VCC  |      | V     |

| V <sub>OL</sub>     | Low Level Output Voltage                    | $V_{\rm F}$ = 0 V, I <sub>O</sub> = 20 mA                                                                                                                                                                  |      |      | 25   | mV    |

| I <sub>CC_Н</sub>   | Output Supply Current (Diode On)            | $I_{\rm F}$ = 10 mA, $I_{\rm O}$ = 0 mA                                                                                                                                                                    |      |      | 2.2  | mA    |

| I <sub>CC_L</sub>   | Output Supply Current (Diode Off)           | $V_{F} = 0 V, I_{O} = 0 mA$                                                                                                                                                                                |      |      | 2    | mA    |

| UNDER V             | OLTAGE LOCKOUT, UCC23511 (12-V UVLO V       | ersion)                                                                                                                                                                                                    |      |      |      |       |

| UVLO <sub>R</sub>   | Under Voltage Lockout VCC rising            | V <sub>CC_Rising</sub> , I <sub>F</sub> =10 mA                                                                                                                                                             | 11   | 12.5 | 13.5 | V     |

| UVLO <sub>F</sub>   | Under Voltage Lockout VCC falling           | V <sub>CC_Falling</sub> , I <sub>F</sub> =10 mA                                                                                                                                                            | 10   | 11.5 | 12.5 | V     |

| UVLO <sub>HYS</sub> | UVLO Hysteresis                             |                                                                                                                                                                                                            |      | 1.0  |      | V     |

| UNDER V             | OLTAGE LOCKOUT, UCC23511B (8-V UVLO V       | ersion)                                                                                                                                                                                                    |      |      |      |       |

| UVLO <sub>R</sub>   | Under Voltage Lockout VCC rising            | V <sub>CC_Rising</sub> , I <sub>F</sub> =10 mA                                                                                                                                                             | 7.8  | 8.5  | 9.2  | V     |

| UVLO <sub>F</sub>   | Under Voltage Lockout VCC falling           | V <sub>CC_Falling</sub> , I <sub>F</sub> =10 mA                                                                                                                                                            | 7.05 | 7.75 | 8.45 | V     |

| UVLO <sub>HYS</sub> | UVLO Hysteresis                             |                                                                                                                                                                                                            |      | 0.75 |      | V     |

(1)  $R_{G\_total}$  is the total gate resistance. It includes the external gate resistor on the PCB + the internal gate resistance of the power switch. Min  $R_{G\_total}$  of 4 $\Omega$  is recommended (for  $V_{CC}-V_{EE}$  =15V). For more details, refer to section 9 (Application and Implementation) of this datasheet.

### 6.10 Switching Characteristics

Unless otherwise noted, all typical values are at  $T_A = 25^{\circ}$ C,  $V_{CC}$ - $V_{EE}$ = 30 V,  $V_{EE}$ = GND. All min and max specifications are at recommended operating conditions ( $T_J$  = -40 to 150°C,  $I_{F(ON)}$ = 7 mA to 16 mA,  $V_{EE}$ = GND,  $V_{CC}$ = 15 V to 30 V,  $V_{F(OFF)}$ = -5V to 0.8V)

| PARAMETER             |                                                                                | TEST CONDITIONS                                                                                   | MIN | TYP | MAX | UNIT  |

|-----------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| t <sub>r</sub>        | Output-signal Rise Time                                                        |                                                                                                   |     |     | 28  | ns    |

| t <sub>f</sub>        | Output-signal Fall Time                                                        |                                                                                                   |     |     | 25  | ns    |

| t <sub>PLH</sub>      | Propagation Delay, Low to High                                                 | Cg = 1nF<br>F <sub>SW</sub> = 20 kHz, (50% Duty Cycle)                                            |     | 70  | 105 | ns    |

| t <sub>PHL</sub>      | Propagation Delay, High to Low                                                 | VCC=15V                                                                                           |     | 70  | 105 | ns    |

| t <sub>PWD</sub>      | Pulse Width Distortion  t <sub>PHL</sub> – t <sub>PLH</sub>                    |                                                                                                   |     |     | 35  | ns    |

| t <sub>sk(pp)</sub>   | Part-to-Part Skew in Propagation<br>Delay Between any Two Parts <sup>(1)</sup> | Cg = 1nF<br>F <sub>SW</sub> = 20 kHz, (50% Duty Cycle)<br>VCC=15V, I <sub>F</sub> =10mA           |     |     | 25  | ns    |

| t <sub>UVLO_rec</sub> | UVLO Recovery Delay                                                            | V <sub>CC</sub> Rising from 0V to 15V                                                             |     | 20  | 30  | μs    |

| CMTI <sub>H</sub>     | Common-mode Transient<br>Immunity (Output High)                                | $I_F$ = 10 mA, $V_{CM}$ = 1500 V, $V_{CC}$ = 30 V, $T_A$ = 25°C                                   | 150 |     |     | kV/µs |

| CMTIL                 | Common-mode Transient<br>Immunity (Output Low)                                 | $V_{F} = 0 \text{ V}, V_{CM} = 1500 \text{ V}, V_{CC} = 30 \text{ V}, T_{A} = 25^{\circ}\text{C}$ | 150 |     |     | kV/µs |

(1) t<sub>sk(pp)</sub> is the magnitude of the difference in propagation delay times between the output of different devices switching in the same direction while operating at identical supply voltages, temperature, input signals and loads ensured by characterization.

#### 6.11 Insulation Characteristics Curves

UCC23511 JAJSHR2B – SEPTEMBER 2019 – REVISED OCTOBER 2020

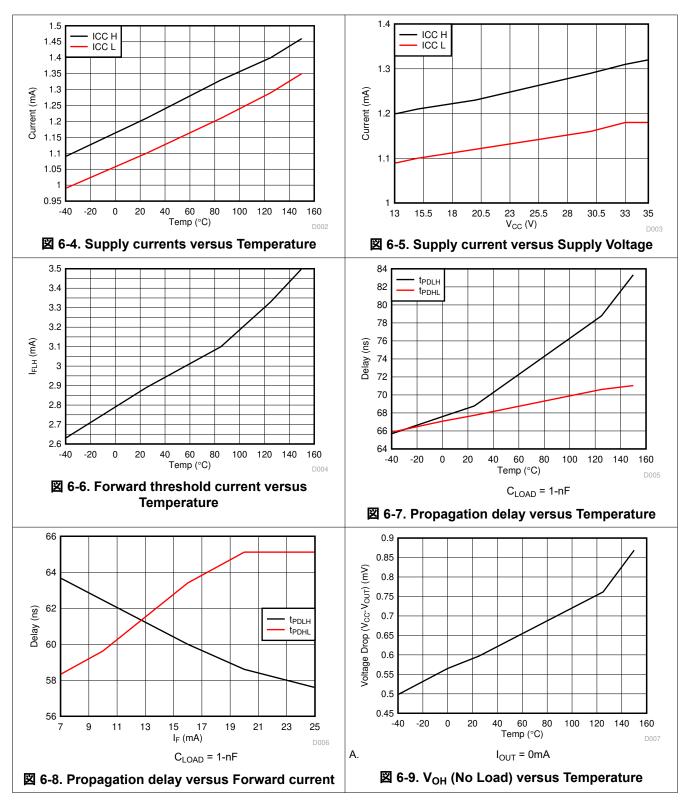

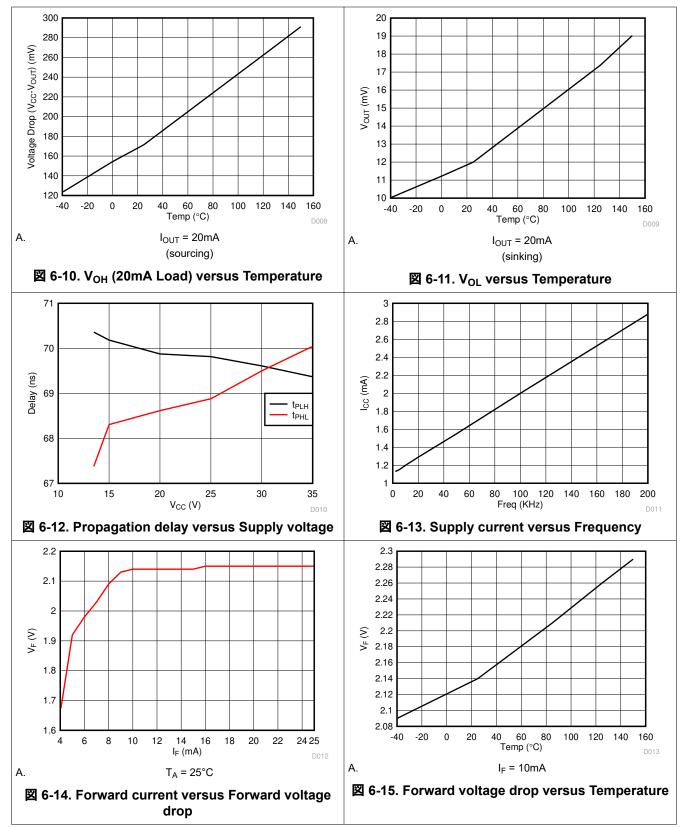

### 6.12 Typical Characteristics

$V_{CC}$ = 15 V, 1- $\mu$ F capacitor from  $V_{CC}$  to  $V_{EE}$ ,  $C_{LOAD}$  = 1 nF for timing tests and 180nF for I<sub>OH</sub> and I<sub>OL</sub> tests, T<sub>J</sub> = - 40°C to +150°C, (unless otherwise noted)

UCC23511 JAJSHR2B – SEPTEMBER 2019 – REVISED OCTOBER 2020

### 7 Parameter Measurement Information

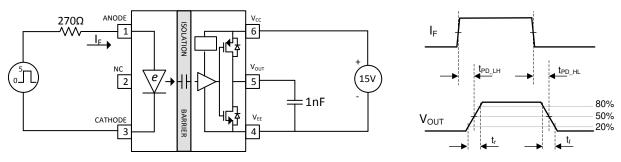

### 7.1 Propagation Delay, rise time and fall time

$\boxtimes$  7-1 shows the propagation delay from the input forward current I<sub>F</sub>, to V<sub>OUT</sub>. This figures also shows the circuit used to measure the rise (t<sub>r</sub>) and fall (t<sub>f</sub>) times and the propagation delays t<sub>PDLH</sub> and t<sub>PDHL</sub>.

図 7-1. I<sub>F</sub> to V<sub>OUT</sub> Propagation Delay, Rise Time and Fall Time

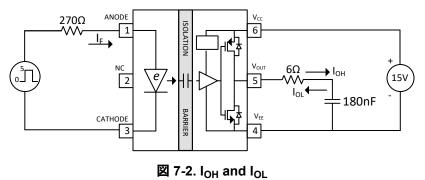

#### 7.2 I<sub>OH</sub> and I<sub>OL</sub> testing

⊠ 7-2 shows the circuit used to measure the output drive currents I<sub>OH</sub> and I<sub>OL</sub>. A series resistor of 6 Ω and a load capacitance of 180 nF are used at the output. The peak dv/dt of the capacitor voltage is measured in order to determine the peak source and sink currents of the gate driver.

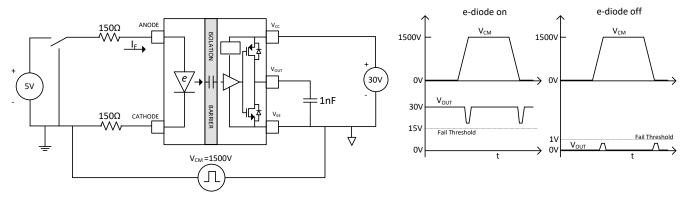

### 7.3 CMTI Testing

⊠ 7-3 is the simplified diagram of the CMTI testing. Common mode voltage is set to 1500V. The test is performed with  $I_F = 6mA$  (VOUT= High) and  $I_F = 0mA$  ( $V_{OUT} = LOW$ ). The diagram also shows the fail criteria for both cases. During the application on the CMTI pulse with  $I_F = 6mA$ , if  $V_{OUT}$  drops from VCC to ½VCC it is considered as a failure. With  $I_F = 0mA$ , if  $V_{OUT}$  rises above 1V, it is considered as a failure.

## 8 Detailed Description

### 8.1 Overview

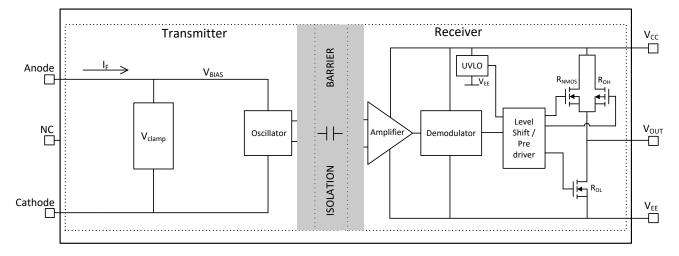

UCC23511 is a single channel isolated gate driver, with an opto-compatible input stage, that can drive IGBTs, MOSFETs and SiC FETs. It has 1.5-A source and 2-A sink peak output current capability with max output driver supply voltage of 33V. The inputs and the outputs are galvanically isolated. UCC23511 is offered in an industry standard 6 pin (SO6) package with >8.5mm creepage and clearance. It has a working voltage of 1060- $V_{RMS}$ , reinforced isolation rating of 5.7- $kV_{RMS}$  for 60s and a surge rating of 8- $kV_{PK}$ . It is pin-to-pin compatible with standard opto isolated gate drivers. While standard opto isolated gate drivers use an LED as the input stage, UCC23511 uses an emulated diode (or "e-diode") as the input stage which does not use light emission to transmit signals across the isolation barrier. The input stage is isolated from the driver stage by dual, series HV SiO<sub>2</sub> capacitors in full differential configuration that not only provides reinforced isolation but also offers best-inclass common mode transient immunity of >150kV/us. The e-diode input stage along with capacitive isolation technology gives UCC23511 several performance advantages over standard opto isolated gate drivers. They are as follows:

1.

- 1. Since the e-diode does not use light emission for its operation, the reliability and aging characteristics of UCC23511 are naturally superior to those of standard opto isolated gate drivers.

- 2. Higher ambient operating temperature range of 125°C, compared to only 105°C for most opto isolated gate drivers

- 3. The e-diode forward voltage drop has less part-to-part variation and smaller variation across temperature. Hence, the operating point of the input stage is more stable and predictable across different parts and operating temperature.

- 4. Higher common mode transient immunity than opto isolated gate drivers

- 5. Smaller propagation delay than opto isolated gate drivers

- 6. Due to superior process controls achievable in capacitive isolation compared to opto isolation, there is less part-to-part skew in the prop delay, making the system design simpler and more robust

- 7. Smaller pulse width distortion than opto isolated gate drivers

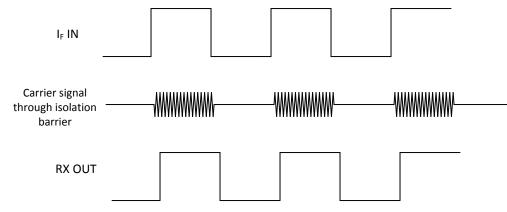

The signal across the isolation has an on-off keying (OOK) modulation scheme to transmit the digital data across a silicon dioxide based isolation barrier (see  $\boxtimes$  8-1). The transmitter sends a high-frequency carrier across the barrier to represent one digital state and sends no signal to represent the other digital state. The receiver demodulates the signal after advanced signal conditioning and produces the output through a buffer stage. The UCC23511 also incorporates advanced circuit techniques to maximize the CMTI performance and minimize the radiated emissions from the high frequency carrier and IO buffer switching.  $\boxtimes$  8-2 shows conceptual detail of how the OOK scheme works.

### 8.2 Functional Block Diagram

#### 図 8-1. Conceptual Block Diagram of a Isolated Gate Driver with an Opto Emulated Input Stage (SO6 pkg)

図 8-2. On-Off Keying (OOK) Based Modulation Scheme

### 8.3 Feature Description

#### 8.3.1 Power Supply

Since the input stage is an emulated diode, no power supply is needed at the input.

The output supply, V<sub>CC</sub>, supports a voltage range from 14V to 33V. For operation with bipolar supplies, the power device is turned off with a negative voltage on the gate with respect to the emitter or source. This configuration prevents the power device from unintentionally turning on because of current induced from the Miller effect. The typical values of the V<sub>CC</sub> and V<sub>EE</sub> output supplies for bipolar operation are 15V and -8V with respect to GND for IGBTs, and 20V and -5V for SiC MOSFETs.

For operation with unipolar supply, the  $V_{CC}$  supply is connected to 15V with respect to GND for IGBTs, and 20V for SiC MOSFETs. The  $V_{EE}$  supply is connected to 0V.

#### 8.3.2 Input Stage

The input stage of UCC23511 is simply the e-diode and therefore has an Anode (Pin 1) and a Cathode (Pin 3). Pin 2 has no internal connection and can be left open or connected to ground. The input stage does not have a power and ground pin. When the e-diode is forward biased by applying a positive voltage to the Anode with respect to the Cathode, a forward current  $I_F$  flows into the e-diode. The forward voltage drop across the e-diode is 2.1V (typ). An external resistor should be used to limit the forward current. The recommended range for the forward current is 7mA to 16mA. When  $I_F$  exceeds the threshold current  $I_{FLH}(2.8mA typ.)$  a high frequency signal

Copyright © 2023 Texas Instruments Incorporated

#### UCC23511 JAJSHR2B – SEPTEMBER 2019 – REVISED OCTOBER 2020

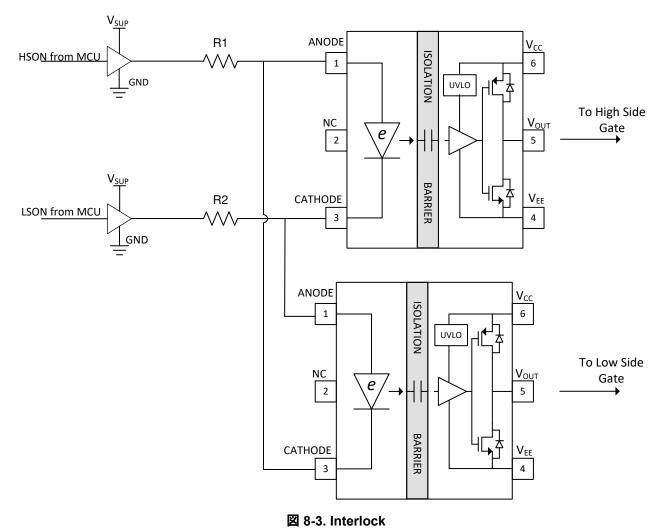

is transmitted across the isolation barrier through the high voltage SiO<sub>2</sub> capacitors. The HF signal is detected by the receiver and V<sub>OUT</sub> is driven high. See  $\forall 2 \neq 2 \Rightarrow 9.2.2.1$  for information on selecting the input resistor. The dynamic impedance of the e-diode is very small(<1.0 $\Omega$ ) and the temperature coefficient of the e-diode forward voltage drop is <1.35mV/°C. This leads to excellent stability of the forward current I<sub>F</sub> across all operating conditions. If the Anode voltage drops below V<sub>F\_HL</sub> (0.9V), or reverse biased, the gate driver output is driven low. The reverse breakdown voltage of the e-diode is >15V. So for normal operation, a reverse bias of up to 13V is allowed. The large reverse breakdown voltage of the e-diode enables UCC23511 to be operated in interlock architecture (see example in 🛛 8-3) where V<sub>SUP</sub> can be as high as 12V. The system designer has the flexibility to choose a 3.3V, 5.0V or up to 12V PWM signal source to drive the input stage of UCC23511 using an appropriate input resistor. The example shows two gate drivers driving a set of IGBTs. The inputs of the gate drivers are connected as shown and driven by two buffers that are controlled by the MCU. Interlock architecture prevents both the e-diodes from being "ON" at the same time, preventing shoot through in the IGBTs. It also ensures that if both PWM signals are erroneously stuck high (or low) simultaneously, both gate driver outputs will be driven low.

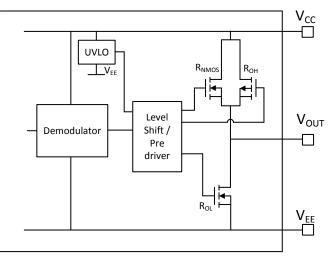

#### 8.3.3 Output Stage

The output stages of the UCC23511 family feature a pullup structure that delivers the highest peak-source current when it is most needed which is during the Miller plateau region of the power-switch turnon transition (when the power-switch drain or collector voltage experiences dV/dt). The output stage pullup structure features a P-channel MOSFET and an additional pull-up N-channel MOSFET in parallel. The function of the N-channel MOSFET is to provide a brief boost in the peak-sourcing current, enabling fast turnon. Fast turnon is

accomplished by briefly turning on the N-channel MOSFET during a narrow instant when the output is changing states from low to high. The on-resistance of this N-channel MOSFET ( $R_{NMOS}$ ) is approximately 5.1  $\Omega$  when activated.

| R <sub>NMOS</sub> | R <sub>OH</sub> | R <sub>OL</sub> | UNIT |  |  |  |  |  |

|-------------------|-----------------|-----------------|------|--|--|--|--|--|

| 5.1               | 5.1 9.5         |                 | Ω    |  |  |  |  |  |

#### 表 8-1. UCC23511 On-Resistance

The R<sub>OH</sub> parameter is a DC measurement and is representative of the on-resistance of the P-channel device only. This parameter is only for the P-channel device because the pullup N-channel device is held in the OFF state in DC condition and is turned on only for a brief instant when the output is changing states from low to high. Therefore, the effective resistance of the UCC23511 pullup stage during this brief turnon phase is much lower than what is represented by the R<sub>OH</sub> parameter, yielding a faster turn on. The turnon-phase output resistance is the parallel combination  $R_{OH} \parallel R_{NMOS}$ .

The pulldown structure in the UCC23511 is simply composed of an N-channel MOSFET. The output voltage swing between  $V_{CC}$  and  $V_{EE}$  provides rail-to-rail operation because of the MOS-out stage which delivers very low dropout.

🛛 8-4. Output Stage

### 8.3.4 Protection Features

### 8.3.4.1 Undervoltage Lockout (UVLO)

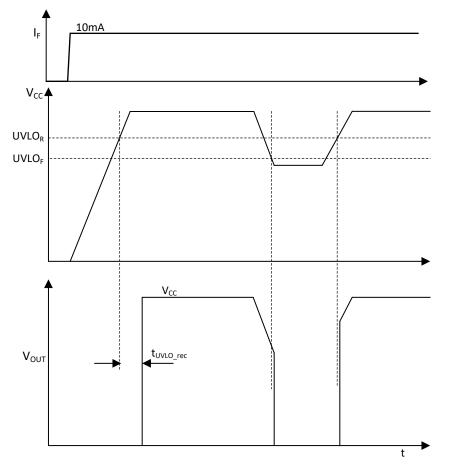

UVLO function is implemented for  $V_{CC}$  and  $V_{EE}$  pins to prevent an under-driven condition on IGBTs and MOSFETs. When  $V_{CC}$  is lower than UVLO<sub>R</sub> at device start-up or lower than UVLO<sub>F</sub> after start-up, the voltage-supply UVLO feature holds the effected output low, regardless of the input forward current as shown in  $\gtrsim 8-2$ . The  $V_{CC}$  UVLO protection has a hysteresis feature (UVLO<sub>hys</sub>). This hysteresis prevents chatter when the power supply produces ground noise which allows the device to permit small drops in bias voltage, which occurs when the device starts switching and operating current consumption increases suddenly.

When  $V_{CC}$  drops below UVLO<sub>F</sub>, a delay,  $t_{UVLO\_rec}$  occurs on the output when the supply voltage rises above UVLO<sub>R</sub> again.

#### 8.3.4.2 Active Pulldown

The active pull-down function is used to pull the IGBT or MOSFET gate to the low state when no power is connected to the  $V_{CC}$  supply. This feature prevents false IGBT and MOSFET turn-on by clamping  $V_{OUT}$  pin to approximately 2V.

When the output stage of the driver is in an unbiased condition (V<sub>CC</sub> floating), the driver outputs (see  $\boxtimes$  8-4) are held low by an active clamp circuit that limits the voltage rise on the driver outputs. In this condition, the upper PMOS & NMOS are held off while the lower NMOS gate is tied to the driver output through an internal 500-k $\Omega$  resistor. In this configuration, the lower NMOS device effectively clamps the output (V<sub>OUT</sub>) to less than 2V.

#### 8.3.4.3 Short-Circuit Clamping

The short-circuit clamping function is used to clamp voltages at the driver output and pull the output pin  $V_{OUT}$  slightly higher than the  $V_{CC}$  voltage during short-circuit conditions. The short-circuit clamping function helps protect the IGBT or MOSFET gate from overvoltage breakdown or degradation. The short-circuit clamping function is implemented by adding a diode connection between the dedicated pins and the  $V_{CC}$  pin inside the driver. The internal diodes can conduct up to 500-mA current for a duration of 10 µs and a continuous current of 20 mA. Use external Schottky diodes to improve current conduction capability as needed.

#### 8.4 Device Functional Modes

表 8-2 lists the functional modes for UCC23511

#### 表 8-2. Function Table for UCC23511 with VCC Rising

| e-diode                                   | VCC                     | V <sub>OUT</sub> |

|-------------------------------------------|-------------------------|------------------|

| OFF (I <sub>F</sub> < I <sub>FLH</sub> )  | 0V - 33V                | Low              |

| ON (I <sub>F</sub> > I <sub>FLH</sub> )   | 0V - UVLO <sub>R</sub>  | Low              |

| ON ( (I <sub>F</sub> > I <sub>FLH</sub> ) | UVLO <sub>R</sub> - 33V | High             |

#### 表 8-3. Function Table for UCC23511 with VCC Falling

| e-diode                                   | VCC                     | V <sub>OUT</sub> |

|-------------------------------------------|-------------------------|------------------|

| OFF (I <sub>F</sub> < I <sub>FLH</sub> )  | 0V - 33V                | Low              |

| ON (I <sub>F</sub> > I <sub>FLH</sub> )   | UVLO <sub>F</sub> - 0V  | Low              |

| ON ( (I <sub>F</sub> > I <sub>FLH</sub> ) | 33V - UVLO <sub>F</sub> | High             |

#### 8.4.1 ESD Structure

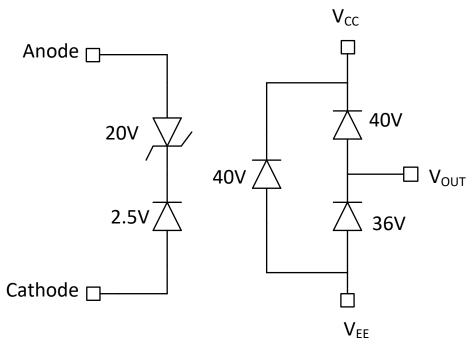

⊠ 8-6 shows the multiple diodes involved in the ESD protection components of the UCC23511 device . This provides pictorial representation of the absolute maximum rating for the device.

🛛 8-6. ESD Structure

### 9 Application and Implementation

注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を 保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことに なります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 9.1 Application Information

UCC23511 is a single channel, isolated gate driver with opto-compatible input for power semiconductor devices, such as MOSFETs, IGBTs, or SiC MOSFETs. It is intended for use in applications such as motor control, industrial inverters, and switched-mode power supplies. It differs from standard opto isolated gate drivers as it does not have an LED input stage. Instead of an LED, it has an emulated diode (e-diode). To turn the e-diode "ON", a forward current in the range of 7mA to 16mA should be driven into the Anode. This will drive the gate driver output High and turn on the power FET. Typically, MCU's are not capable of providing the required forward current. Hence a buffer has to be used between the MCU and the input stage of UCC23511. Typical buffer power supplies are either 5V or 3.3V. A resistor is needed between the buffer and the input stage of UCC23511 to limit the current. It is simple, but important to choose the right value of resistance. The resistor tolerance, buffer supply voltage tolerance and output impedance of the buffer, have to be considered in the resistor selection. This will ensure that the e-diode forward current stays within the recommended range of 7mA to 16mA. Detailed design recommendations are given in the  $\frac{1}{2}\sqrt{2} = \sqrt{9.1}$ . The current driven input stage offers excellent noise immunity that is need in high power motor drive systems, especially in cases where the MCU cannot be located close to the isolated gate driver. UCC23511 offers best in class CMTI performance of >150kV/us at 1500V common mode voltages.

The e-diode is capable of 25mA continuous in the forward direction. The forward voltage drop of the e-diode has a very tight part to part variation (1.8V min to 2.4V max). The temperature coefficient of the forward drop is <1.35mV/°C. The dynamic impedance of the e-diode in the forward biased region is  $\sim 1\Omega$ . All of these factors contribute in excellent stability of the e-diode forward current. To turn the e-diode "OFF", the Anode - Cathode voltage should be <0.8V, or I<sub>F</sub> should be <I<sub>FLH</sub>. The e-diode can also be reverse biased up to 13V (14V abs max) in order to turn it off and bring the gate driver output low. The large reverse breakdown voltage of the input stage provides system designers the flexibility to drive the input stage with 12V PWM signals without the need for an additional clamping circuit on the Anode and Cathode pin.

The output power supply for UCC23511 can be as high as 33V (35V abs max). The output power supply can be configured externally as a single isolated supply up to 33V or isolated bipolar supply such that  $V_{CC}-V_{EE}$  does not exceed 33V, or it can be bootstrapped (with external diode & capacitor) if the system uses a single power supply with respect to the power ground. Typical quiescent power supply current from  $V_{CC}$  is 1.2mA (max 2.2mA).

#### 9.2 Typical Application

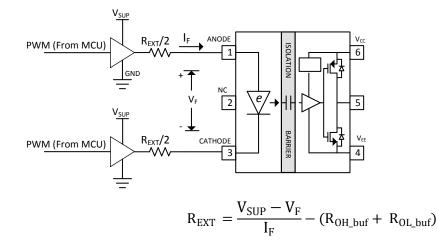

V<sub>SUP</sub>  $R_{EXT}/2 \ge$ Q ANODE Vcd ISOLATION 1 6  $I_{F}$ 15V VOUT RGON NC R<sub>G</sub> е 5 2 -╢ ۰Λ٨ BARRIER  $R_{\text{GOFF}}$ CATHODE  $\mathsf{V}_{\mathsf{EE}}$ 4 3 R<sub>EXT</sub>/2≥ Q PWM M1 GND

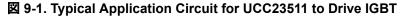

The circuit in  $\boxtimes$  9-1, shows a typical application for driving IGBTs.

#### 9.2.1 Design Requirements

表 9-1 lists the recommended conditions to observe the input and output of the UCC23511 gate driver.

| PARAMETER           | VALUE | UNIT |

|---------------------|-------|------|

| V <sub>CC</sub>     | 15    | V    |

| I <sub>F</sub>      | 10    | mA   |

| Switching frequency | 8     | kHz  |

#### 表 9-1. UCC23511 Design Requirements

#### 9.2.2 Detailed Design Procedure

#### 9.2.2.1 Selecting the Input Resistor

The input resistor limits the current that flows into the e-diode when it is forward biased. The threshold current  $I_{FLH}$  is 2.8 mA typ. The recommended operating range for the forward current is 7 mA to 16 mA (e-diode ON). All the electrical specifications are guaranteed in this range. The resistor should be selected such that for typical operating conditions,  $I_F$  is 10 mA. Following are the list of factors that will affect the exact value of this current:

- 1. Supply Voltage V<sub>SUP</sub> variation

- 2. Manufacturer's tolerance for the resistor and variation due to temperature

- 3. e-diode forward voltage drop variation (at I<sub>F</sub>=10 mA, V<sub>F</sub>= typ 2.1 V, min 1.8 V, max 2.4 V, with a temperature coefficient <1.35 mV/°C and dynamic impedance <1  $\Omega$ )

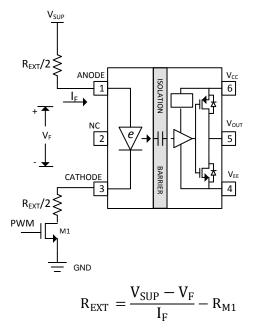

See  $\boxtimes$  9-2 for the schematic using a single NMOS and split resistor combination to drive the input stage of UCC23511. The input resistor can be selected using the equation shown.

#### 図 9-2. Configuration 1: Driving the input stage of UCC23511 with a single NMOS and split resistors

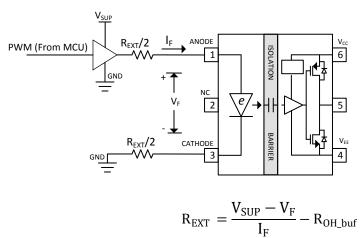

Driving the input stage of UCC23511 using a single buffer is shown in  $\boxtimes$  9-3 and using 2 buffers is shown in  $\boxtimes$  9-4

#### 図 9-3. Configuration 2: Driving the input stage of UCC23511 with one Buffer and split resistors

#### 2 9-4. Configuration 3: Driving the input stage of UCC23511 with 2 buffers and split resistors

₹ 9-2 shows the range of values for R<sub>EXT</sub> for the 3 different configurations shown in ⊠ 9-2, ⊠ 9-3 and ⊠ 9-4. The assumptions used in deriving the range for R<sub>EXT</sub> are as follows:

- 1. Target forward current  $I_F$  is 7mA min, 10mA typ and 16mA max

- 2. e-diode forward voltage drop is 1.8V to 2.4V

- 3. V<sub>SUP</sub> (Buffer supply voltage) is 5V with ±5% tolerance

- 4. Manufacturer's tolerance for  $R_{EXT}$  is 1%

- 5. NMOS resistance is  $0.25\Omega$  to  $1.0\Omega$  (for configuration 1)

- 6. R<sub>OH</sub>(buffer output impedance in output "High" state) is 13Ω min, 18Ω typ and 22Ω max

- 7.  $R_{OL}$  (buffer output impedance in "Low" state) is 10 $\Omega$  min, 14 $\Omega$  typ and 17 $\Omega$  max

| A 9-2. REXT values to brive the input Stage |                    |     |     |  |  |  |  |  |  |

|---------------------------------------------|--------------------|-----|-----|--|--|--|--|--|--|

|                                             | R <sub>EXT</sub> Ω |     |     |  |  |  |  |  |  |

| Configuration                               | Min                | Тур | Мах |  |  |  |  |  |  |

| Single NMOS and<br>R <sub>EXT</sub>         | 218                | 290 | 331 |  |  |  |  |  |  |

| Single Buffer and R <sub>EXT</sub>          | 204                | 272 | 311 |  |  |  |  |  |  |

| Two Buffers and $\mathrm{R}_{\mathrm{EXT}}$ | 194                | 259 | 294 |  |  |  |  |  |  |

### 表 9-2. $\rm R_{EXT}$ Values to Drive The Input Stage

#### 9.2.2.2 Gate Driver Output Resistor

The external gate-driver resistors,  $R_{G(ON)}$  and  $R_{G(OFF)}$  are used to:

- 1. Limit ringing caused by parasitic inductances and capacitances

- 2. Limit ringing caused by high voltage or high current switching dv/dt, di/dt, and body-diode reverse recovery

- 3. Fine-tune gate drive strength, specifically peak sink and source current to optimize the switching loss

- 4. Reduce electromagnetic interference (EMI)

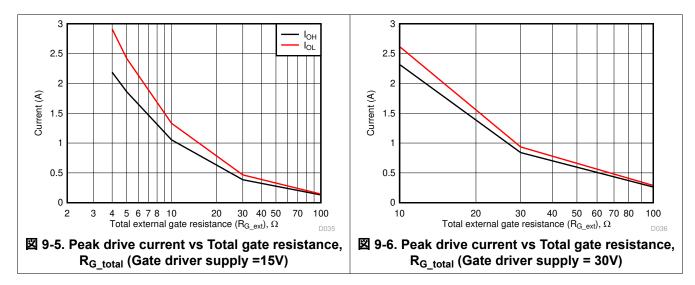

The output stage of UCC23511 has a pull up structure consisting of a P-channel MOSFET and an N-channel MOSFET in parallel, as shown in  $\boxtimes$  8-4. The N-channel MOSFET provides the peak current that charges the gate of the IGBT (or power switch) while the P-channel MOSFET ensures that V<sub>OUT</sub> will go all the way upto V<sub>CC</sub>.  $\boxtimes$  9-1 shows the internal gate resistance, R<sub>G\_int</sub> of the power switch. R<sub>G\_int</sub> is usually specified in the datasheet of the power switch. When turning the power switch "on", the gate driver sees a total gate resistance R<sub>G\_total</sub> = R<sub>GON</sub> + R<sub>G\_int</sub> and when turning the power switch "off", the gate driver sees a total gate resistance R<sub>G\_total</sub> = R<sub>GOFF</sub> + R<sub>G\_int</sub> in series with the gate capacitance where,

- R<sub>GON</sub> is the external resistance on the pcb for turn "on"

- R<sub>GOFF</sub> is the external resistance on the pcb for turn "off"

#### UCC23511 JAJSHR2B - SEPTEMBER 2019 - REVISED OCTOBER 2020

- R<sub>G int</sub> is the internal gate resistance of the power switch that can be found in the data sheet of the power switch

- Ideal diodes zero resistance and zero voltage drop are assumed on both the turn-on and turn-off paths, for simplicity.

To illustrate the procedure to select R<sub>GON</sub> and R<sub>GOFF</sub>, let us consider the following example with the assumptions listed below:

- 1. Power switch internal gate resistance is 2 ohms

- 2. Desired charging current is 1.5A

- 3. Desired discharging current is 1.7A

- Gate driver supply is 15 V 4.

For this example, since  $V_{CC}$ =15V, use the typical curves shown in 🗵 9-5. It can be seen that we need a total turn on resistance of 7 ohms (peak charging current of 1.5A) and a total turn off resistance of 8 ohms (peak discharging current of 1.7A). Subtracting the internal gate resistance of the power switch, we get R<sub>GON</sub>= 7 ohms - 2 ohms = 5 ohms, and  $R_{GOFF}$  = 8 ohms- 2 ohms = 6 ohms.

Use 表 9-3 to find the minimum gate resistance to be used with UCC23511 when driving a power switch. The values shown includes the power switch internal gate resistance R<sub>G int</sub>. Hence, R<sub>G int</sub> must be subtracted from the values shown to determine the value of the resistor to populate on the printed circuit board.

| 表 9-3. Minimum gate resistor ( $\Omega$ )                  |    |  |  |  |  |  |  |  |

|------------------------------------------------------------|----|--|--|--|--|--|--|--|

| Gate driver supply V <sub>CC</sub> -V <sub>EE</sub><br>(V) |    |  |  |  |  |  |  |  |

| 15                                                         | 4  |  |  |  |  |  |  |  |

| 23                                                         | 7  |  |  |  |  |  |  |  |

| 30                                                         | 10 |  |  |  |  |  |  |  |

###

The diodes shown in series with each,  $R_{GON}$  and  $R_{GOFF}$ , in 🗵 9-1 ensure the gate drive current flows through the intended path, respectively, during turn-on and turn-off. Note that the diode forward drop will reduce the voltage level at the gate of the power switch. To achieve rail-to-rail gate voltage levels, add a resistor from the  $V_{OUT}$  pin to the power switch gate, with a resistance value approximately 20 times higher than R<sub>GON</sub> and R<sub>GOFF</sub>. For the examples described in this section, a good choice is 100  $\Omega$  to 200  $\Omega$ .

注

The estimated peak current is also influenced by PCB layout and load capacitance. Parasitic inductance in the gate-driver loop can slow down the peak gate-drive current and introduce overshoot and undershoot. Therefore, TI strongly recommends that the gate-driver loop should be minimized. Conversely, the peak source and sink current is dominated by loop parasitics when the load capacitance ( $C_{ISS}$ ) of the power transistor is very small (typically less than 1 nF) because the rising and falling time is too small and close to the parasitic ringing period.

#### 9.2.2.3 Estimate Gate-Driver Power Loss

The total loss,  $P_G$ , in the gate-driver subsystem includes the power losses ( $P_{GD}$ ) of the UCC23511 device and the power losses in the peripheral circuitry, such as the external gate-drive resistor.

The  $P_{GD}$  value is the key power loss which determines the thermal safety-related limits of the UCC23511 device, and it can be estimated by calculating losses from several components.

The first component is the static power loss,  $P_{GDQ}$ , which includes power dissipated in the input stage ( $P_{GDQ\_IN}$ ) as well as the quiescent power dissipated in the output stage ( $P_{GDQ\_OUT}$ ) when operating with a certain switching frequency under no load.  $P_{GDQ\_IN}$  is determined by  $I_F$  and  $V_F$  and is given by  $\ddagger$  1. The  $P_{GDQ\_OUT}$  parameter is measured on the bench with no load connected to  $V_{OUT}$  pin at a given  $V_{CC}$ , switching frequency, and ambient temperature. In this example,  $V_{CC}$  is 15 V. The current on the power supply, with PWM switching at 10 kHz, is measured to be  $I_{CC}$  = 1.33 mA. Therefore, use  $\ddagger 2$  to calculate  $P_{GDQ\_OUT}$ .

$$P_{GDQ\_IN} = \frac{1}{2} * V_F * I_F$$

(1)

$$P_{GDQ\_OUT} = V_{CC} * I_{CC}$$

The total quiescent power (without any load capacitance) dissipated in the gate driver is given by the sum of  $\neq 1$  and  $\neq 2$  as shown in  $\neq 3$

$$P_{GDQ} = P_{GDQ_{IN}} + P_{GDQ_{OUT}} = 10 \text{ mW} + 20 \text{mW} = 30 \text{mW}$$

(3)

The second component is the switching operation loss,  $P_{GDSW}$ , with a given load capacitance which the driver charges and discharges the load during each switching cycle. Use  $\neq$  4 to calculate the total dynamic loss from load switching,  $P_{GSW}$ .

$$\mathsf{P}_{\mathsf{GSW}} = \mathsf{V}_{\mathsf{CC2}} \times \mathsf{Q}_{\mathsf{G}} \times \mathsf{f}_{\mathsf{SW}} \tag{4}$$

where

• Q<sub>G</sub> is the gate charge of the power transistor at V<sub>CC</sub>.

So, for this example application the total dynamic loss from load switching is approximately 18 mW as calculated in  $\pm 5$ .

$$P_{GSW} = 15 V \times 120 nC \times 10 kHz = 18 mW$$

$Q_G$  represents the total gate charge of the power transistor switching 520 V at 50 A, and is subject to change with different testing conditions. The UCC23511 gate-driver loss on the output stage,  $P_{GDO}$ , is part of  $P_{GSW}$ .  $P_{GDO}$  is equal to  $P_{GSW}$  if the external gate-driver resistance and power-transistor internal resistance are 0  $\Omega$ , and

(5)

(2)

(6)

(7)

(8)

all the gate driver-loss will be dissipated inside the UCC23511. If an external turn-on and turn-off resistance exists, the total loss is distributed between the gate driver pull-up/down resistance, external gate resistance, and power-transistor internal resistance. Importantly, the pull-up/down resistance is a linear and fixed resistance if the source/sink current is not saturated to 1.5A/2.0A, however, it will be non-linear if the source/sink current is saturated. Therefore, P<sub>GDO</sub> is different in these two scenarios.

#### Case 1 - Linear Pull-Up/Down Resistor:

$$P_{GDO} = \frac{P_{GSW}}{2} \left[ \frac{R_{OH} || R_{NMOS}}{R_{OH} || R_{NMOS} + R_{GON} + R_{GFET\_int}} + \frac{R_{OL}}{R_{OL} + R_{GOFF} + R_{GFET\_int}} \right]$$

In this design example, all the predicted source and sink currents are less than 1.5 A and 2.0 A, therefore, use  $\neq$  6 to estimate the UCC23511 gate-driver loss.

$$P_{GDO} = \frac{18 \text{ mW}}{2} \left[ \frac{9.5\Omega || 5.1\Omega}{9.5\Omega || 5.1\Omega + 5.1\Omega + 0\Omega} + \frac{0.4\Omega}{0.4\Omega + 10\Omega + 0\Omega} \right] = 3.9 \text{ mW}$$

#### Case 2 - Nonlinear Pull-Up/Down Resistor:

$$P_{GDO} = f_{sw} x \left[ 4.5A x \int_{0}^{T_{R_s} Sys} (V_{CC} - V_{OUT}(t)) dt + 5.3A x \int_{0}^{T_{F_s} Sys} V_{OUT}(t) dt \right]$$

where

V<sub>OUT(t)</sub> is the gate-driver OUT pin voltage during the turnon and turnoff period. In cases where the output is saturated for some time, this value can be simplified as a constant-current source (1.5 A at turnon and 2.0 A at turnoff) charging or discharging a load capacitor. Then, the V<sub>OUT(t)</sub> waveform will be linear and the T<sub>R Svs</sub> and T<sub>F Sys</sub> can be easily predicted.

For some scenarios, if only one of the pullup or pulldown circuits is saturated and another one is not, the P<sub>GDO</sub> is a combination of case 1 and case 2, and the equations can be easily identified for the pullup and pulldown based on this discussion.

Use  $\neq$  9 to calculate the total gate-driver loss dissipated in the UCC23511 gate driver, P<sub>GD</sub>.

$$P_{GD} = P_{GDO} + P_{GDO} = 30 \text{mW} + 3.9 \text{mW} = 33.9 \text{mW}$$

#### 9.2.2.4 Estimating Junction Temperature

Use  $\neq \pm 10$  to estimate the junction temperature (T<sub>1</sub>) of UCC23511.

$$T_{J} = T_{C} + \Psi_{JT} \times P_{GD}$$

<sup>(10)</sup>

where

$T_{C}$  is the UCC23511 case-top temperature measured with a thermocouple or some other instrument.

$\Psi_{JT}$  is the junction-to-top characterization parameter from the table.

Using the junction-to-top characterization parameter ( $\Psi_{\text{IT}}$ ) instead of the junction-to-case thermal resistance  $(R_{\theta,IC})$  can greatly improve the accuracy of the junction temperature estimation. The majority of the thermal energy of most ICs is released into the PCB through the package leads, whereas only a small percentage of the total energy is released through the top of the case (where thermocouple measurements are usually conducted). The  $R_{\theta,IC}$  resistance can only be used effectively when most of the thermal energy is released through the case,

(9)

such as with metal packages or when a heat sink is applied to an IC package. In all other cases, use of  $R_{\theta JC}$  will inaccurately estimate the true junction temperature. The  $\Psi_{JT}$  parameter is experimentally derived by assuming that the dominant energy leaving through the top of the IC will be similar in both the testing environment and the application environment. As long as the recommended layout guidelines are observed, junction temperature estimations can be made accurately to within a few degrees Celsius.

#### 9.2.2.5 Selecting V<sub>CC</sub> Capacitor

Bypass capacitors for V<sub>CC</sub> is essential for achieving reliable performance. TI recommends choosing low-ESR and low-ESL, surface-mount, multi-layer ceramic capacitors (MLCC) with sufficient voltage ratings, temperature coefficients, and capacitance tolerances. A 50-V,  $10-\mu$ F MLCC and a 50-V,  $0.22-\mu$ F MLCC are selected for the C<sub>VCC</sub> capacitor. If the bias power supply output is located a relatively long distance from the V<sub>CC</sub> pin, a tantalum or electrolytic capacitor with a value greater than 10  $\mu$ F should be used in parallel with C<sub>VCC</sub>.

注

DC bias on some MLCCs will impact the actual capacitance value. For example, a 25-V, 1- $\mu$ F X7R capacitor is measured to be only 500 nF when a DC bias of 15-V<sub>DC</sub> is applied.

### **10 Power Supply Recommendations**

The recommended input supply voltage (V<sub>CC</sub>) for the UCC23511 device is from 14V to 33V. The lower limit of the range of output bias-supply voltage (V<sub>CC</sub>) is determined by the internal UVLO protection feature of the device. V<sub>CC</sub> voltage should not fall below the UVLO threshold for normal operation, or else the gate-driver outputs can become clamped low for more than 20  $\mu$ s by the UVLO protection feature. The higher limit of the V<sub>CC</sub> range depends on the maximum gate voltage of the power device that is driven by the UCC23511 device, and should not exceed the recommended maximum V<sub>CC</sub> of 33 V. A local bypass capacitor should be placed between the V<sub>CC</sub> and V<sub>EE</sub> pins, with a value of 220-nF to 10- $\mu$ F for device biasing. TI recommends placing an additional 100-nF capacitor in parallel with the device biasing capacitor for high frequency filtering. Both capacitors should be positioned as close to the device as possible. Low-ESR, ceramic surface-mount capacitors are recommended.

If only a single, primary-side power supply is available in an application, isolated power can be generated for the secondary side with the help of a transformer driver such as Texas Instruments' SN6501 or SN6505A. For such applications, detailed power supply design and transformer selection recommendations are available in *SN6501 Transformer Driver for Isolated Power Supplies* data sheet and *SN6505A Low-Noise 1-A Transformer Drivers for Isolated Power Supplies* data sheet.

## 11 Layout

### 11.1 Layout Guidelines

Designers must pay close attention to PCB layout to achieve optimum performance for the UCC23511. Some key guidelines are:

- Component placement:

- Low-ESR and low-ESL capacitors must be connected close to the device between the V<sub>CC</sub> and V<sub>EE</sub> pins to bypass noise and to support high peak currents when turning on the external power transistor.

- To avoid large negative transients on the V<sub>EE</sub> pins connected to the switch node, the parasitic inductances between the source of the top transistor and the source of the bottom transistor must be minimized.

- Grounding considerations:

- Limiting the high peak currents that charge and discharge the transistor gates to a minimal physical area is essential. This limitation decreases the loop inductance and minimizes noise on the gate terminals of the transistors. The gate driver must be placed as close as possible to the transistors.

- High-voltage considerations:

- To ensure isolation performance between the primary and secondary side, avoid placing any PCB traces or copper below the driver device. A PCB cutout or groove is recommended in order to prevent contamination that may compromise the isolation performance.

- Thermal considerations:

- A large amount of power may be dissipated by the UCC23511 if the driving voltage is high, the load is heavy, or the switching frequency is high. Proper PCB layout can help dissipate heat from the device to the PCB and minimize junction-to-board thermal impedance (θ<sub>JB</sub>).

- Increasing the PCB copper connecting to the V<sub>CC</sub> and V<sub>EE</sub> pins is recommended, with priority on

maximizing the connection to V<sub>EE</sub>. However, the previously mentioned high-voltage PCB considerations

must be maintained.

- If the system has multiple layers, TI also recommends connecting the V<sub>CC</sub> and V<sub>EE</sub> pins to internal ground or power planes through multiple vias of adequate size. These vias should be located close to the IC pins to maximize thermal conductivity. However, keep in mind that no traces or coppers from different high voltage planes are overlapping.

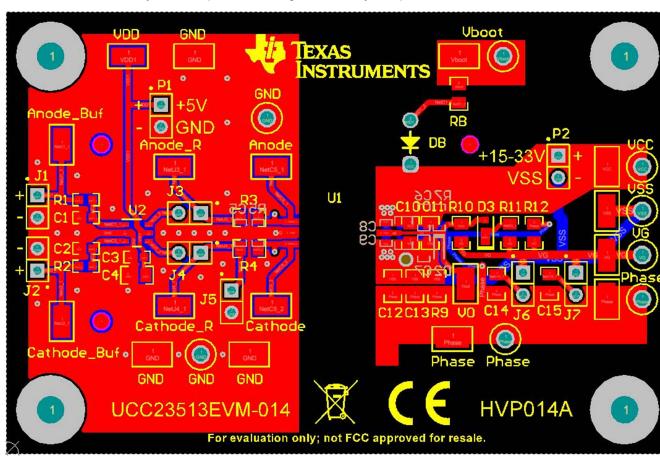

### 11.2 Layout Example

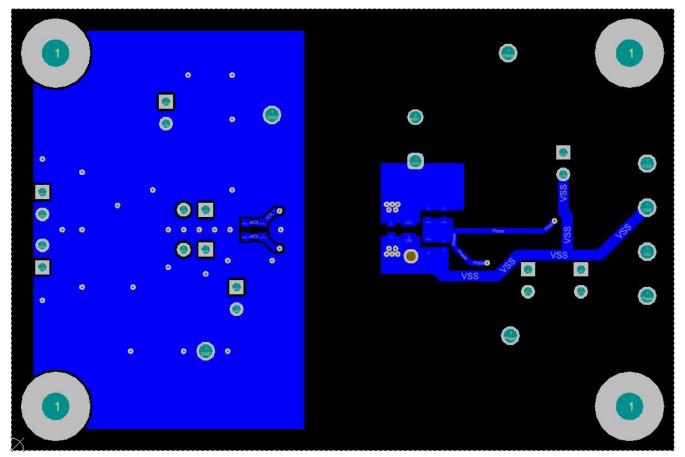

I1-1 shows a PCB layout example with the signals and key components labeled.

A. No PCB traces or copper are located between the primary and secondary side, which ensures isolation performance.

図 11-1. Layout Example

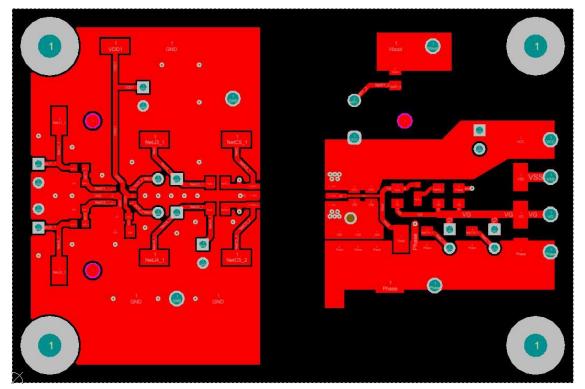

$\boxtimes$  11-2 and  $\boxtimes$  11-3 show the top and bottom layer traces and copper.

図 11-2. Top-Layer Traces and Copper

#### UCC23511 JAJSHR2B – SEPTEMBER 2019 – REVISED OCTOBER 2020

図 11-3. Bottom-Layer Traces and Copper (Flipped)

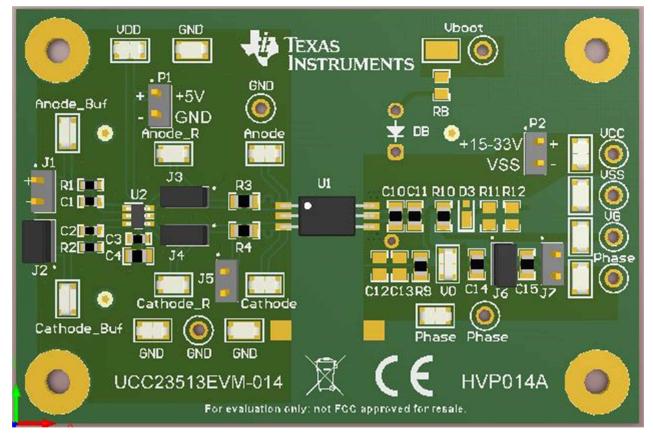

$\boxtimes$  11-4 shows the 3D layout of the top view of the PCB.

UCC23511 JAJSHR2B – SEPTEMBER 2019 – REVISED OCTOBER 2020

A. The location of the PCB cutout between primary side and secondary sides ensures isolation performance.

#### 図 11-4. 3-D PCB View

### 11.3 PCB Material

Use standard FR-4 UL94V-0 printed circuit board. This PCB is preferred over cheaper alternatives because of lower dielectric losses at high frequencies, less moisture absorption, greater strength and stiffness, and the self-extinguishing flammability-characteristics.

### 11.4 Custom Design With WEBENCH® Tools

Click here to create a custom design using the UCC3511 device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage ( $V_{IN}$ ), output voltage ( $V_{OUT}$ ), and output current ( $I_{OUT}$ ) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- · Run thermal simulations to understand board thermal performance

- Export customized schematic and layout into popular CAD formats

- Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

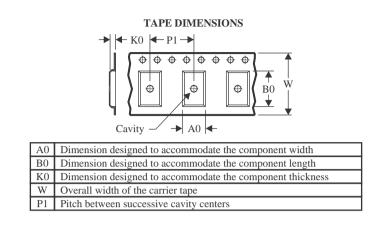

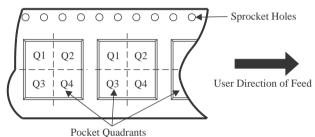

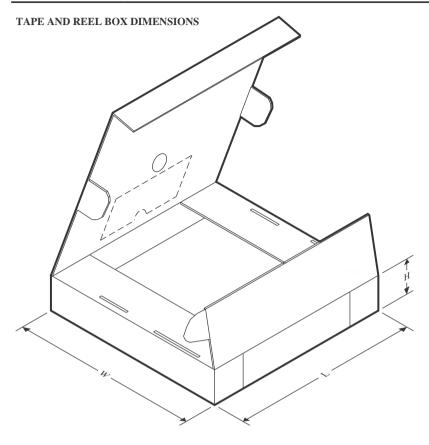

### 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

#### **PACKAGING INFORMATION**

| Orderable part number | Status   | Material type | Package   Pins | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/         | Op temp (°C) | Part marking |

|-----------------------|----------|---------------|----------------|-----------------------|------|---------------|---------------------|--------------|--------------|

|                       | (1)      | (2)           |                |                       | (3)  | Ball material | Peak reflow         |              | (6)          |

|                       |          |               |                |                       |      | (4)           | (5)                 |              |              |

| UCC23511BDWY          | Obsolete | Production    | SOIC (DWY)   6 | -                     | -    | Call TI       | Call TI             | -40 to 125   | UC23511B     |

| UCC23511BDWYR         | Active   | Production    | SOIC (DWY)   6 | 850   LARGE T&R       | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | UC23511B     |

| UCC23511BDWYR.A       | Active   | Production    | SOIC (DWY)   6 | 850   LARGE T&R       | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | UC23511B     |

| UCC23511BDWYR.B       | Active   | Production    | SOIC (DWY)   6 | 850   LARGE T&R       | -    | Call TI       | Call TI             | -40 to 125   |              |

| UCC23511DWY           | Obsolete | Production    | SOIC (DWY)   6 | -                     | -    | Call TI       | Call TI             | -40 to 125   | UCC23511     |

| UCC23511DWYR          | Active   | Production    | SOIC (DWY)   6 | 850   LARGE T&R       | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | UCC23511     |

| UCC23511DWYR.A        | Active   | Production    | SOIC (DWY)   6 | 850   LARGE T&R       | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | UCC23511     |

| UCC23511DWYR.B        | Active   | Production    | SOIC (DWY)   6 | 850   LARGE T&R       | -    | Call TI       | Call TI             | -40 to 125   |              |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.