# UCC21540-Q1

## 強化絶縁型デュアルチャネルゲートドライバ

### 1 特長

- 次の結果で AEC Q100 認定済み

- デバイス温度グレード 1

- 機能安全品質管理**

- 機能安全システムの設計に役立つ資料を利用可能

- 接合部温度範囲 : -40°C ~ +150°C

- 最大 18V の VDD 出力駆動電源

- 5V および 8V VDD UVLO オプション

- 125V/ns を超える CMTI

- スイッチング パラメータ :

- 伝搬遅延時間 : 33ns (代表値)

- 最大パルス幅歪み : 6ns

- 最大 VDD 電源オン遅延 : 10μs

### 2 アプリケーション

- HEV および EV バッテリ充電器

- AC/DC および DC/DC 電源の絶縁型コンバータ

- モータ・ドライブとインバータ

- 無停電電源 (UPS)

### 3 概要

UCC21540-Q1 デバイスは、デッド タイムをプログラムでき広い温度範囲に対応する絶縁型デュアルチャネル ゲート ドライバです。極端な温度条件下でも安定した性能を提供し、堅牢性に優れています。ピーク電流はソース 4A、シンク 6A で、パワー MOSFET、IGBT、GaN トランジスタを駆動するように設計されています。

UCC21540-Q1 は、2 つのローサイド ドライバ、2 つのハイサイド ドライバ、または 1 つのハーフブリッジ ドライバとして構成可能です。入力側は、5.7KV<sub>RMS</sub> の絶縁バリアによって 2 つの出力ドライバと分離されており、同相過渡耐性 (CMTI) は 125V/ns 以上です。

保護機能として、抵抗によりプログラム可能なデッドタイム、両方の出力を同時にシャットダウンするディセーブル機能、入力ピンでの最大 -5V、50ns までのスパイクに対する負電圧耐性があります。すべての電源が UVLO 機能を備えています。

#### 製品情報 (1)

| 部品番号            | I <sub>PK</sub> | REC.VDD 電源電圧の最小値 | パッケージ         |

|-----------------|-----------------|------------------|---------------|

| UCC21540QDWKQ1  | 4.0A/6.0A       | 9.2 V            | DWK (SOIC 14) |

| UCC21540AQDWKQ1 | 4.0A/6.0A       | 6.0 V            | DWK (SOIC 14) |

(1) 供給されているすべてのパッケージについては、[セクション 14](#) を参照してください。

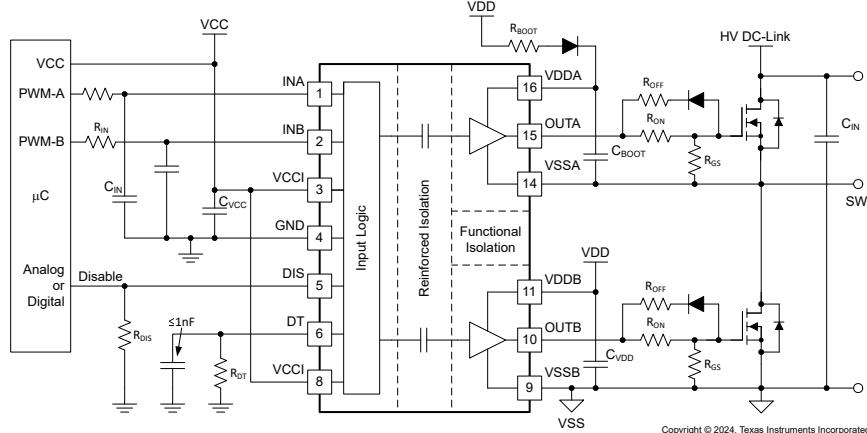

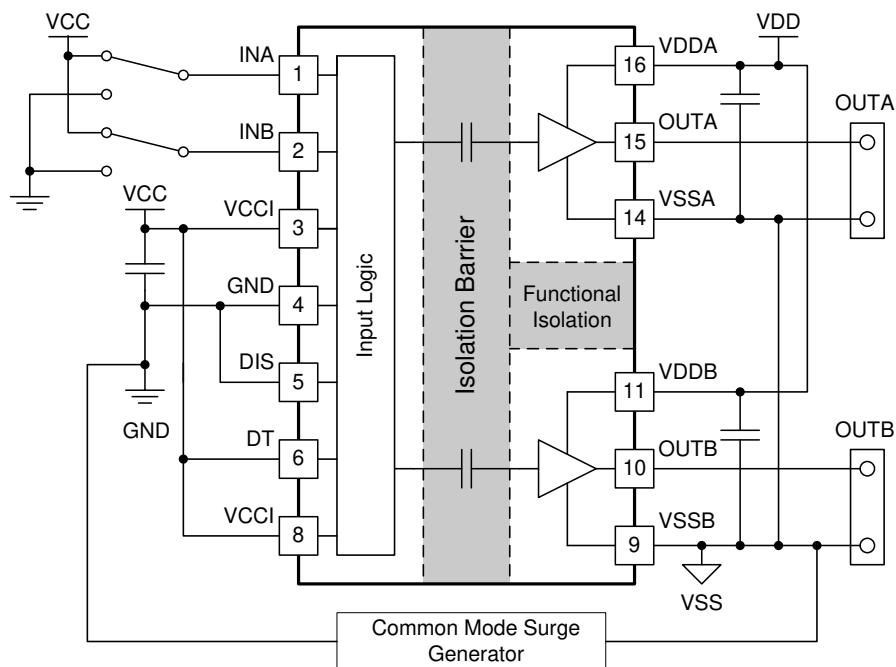

#### 代表的なアプリケーション

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあります。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                       |    |                         |    |

|-----------------------|----|-------------------------|----|

| 1 特長                  | 1  | 7.7 CMTI テスト            | 17 |

| 2 アプリケーション            | 1  | 8 詳細説明                  | 18 |

| 3 概要                  | 1  | 8.1 概要                  | 18 |

| 4 デバイス比較表             | 3  | 8.2 機能ブロック図             | 18 |

| 5 ピン構成および機能           | 3  | 8.3 機能説明                | 19 |

| 6 仕様                  | 5  | 8.4 デバイスの機能モード          | 22 |

| 6.1 絶対最大定格            | 5  | 9 アプリケーションと実装           | 24 |

| 6.2 ESD 定格            | 5  | 9.1 アプリケーション情報          | 24 |

| 6.3 推奨動作条件            | 5  | 9.2 代表的なアプリケーション        | 24 |

| 6.4 熱に関する情報           | 6  | 10 電源に関する推奨事項           | 34 |

| 6.5 電力定格              | 6  | 11 レイアウト                | 35 |

| 6.6 絶縁仕様              | 6  | 11.1 レイアウトのガイドライン       | 35 |

| 6.7 安全限界値             | 7  | 11.2 レイアウト例             | 36 |

| 6.8 電気的特性             | 8  | 12 デバイスおよびドキュメントのサポート   | 38 |

| 6.9 スイッチング特性          | 9  | 12.1 サード・パーティ製品に関する免責事項 | 38 |

| 6.10 絶縁特性曲線           | 10 | 12.2 ドキュメントのサポート        | 38 |

| 6.11 代表的特性            | 11 | 12.3 ドキュメントの更新通知を受け取る方法 | 38 |

| 7 パラメータ測定情報           | 14 | 12.4 サポート・リソース          | 38 |

| 7.1 最小パルス             | 14 | 12.5 商標                 | 38 |

| 7.2 伝搬遅延とパルス幅歪み       | 14 | 12.6 静電気放電に関する注意事項      | 38 |

| 7.3 立ち上がりおよび立ち下がり時間   | 14 | 12.7 用語集                | 38 |

| 7.4 入力とディスエーブルの応答時間   | 15 | 13 改訂履歴                 | 38 |

| 7.5 プログラム可能なデッドタイム    | 15 | 14 メカニカル、パッケージ、および注文情報  | 40 |

| 7.6 電源オン時の出力の UVLO 遅延 | 16 |                         |    |

## 4 デバイス比較表

| デバイスのオプション      | UVLO | ピーク電流         | パッケージ   |

|-----------------|------|---------------|---------|

| UCC21540QDWKQ1  | 8.0V | 4A ソース、6A シンク | SOIC-14 |

| UCC21540AQDWKQ1 | 5.0V | 4A ソース、6A シンク | SOIC-14 |

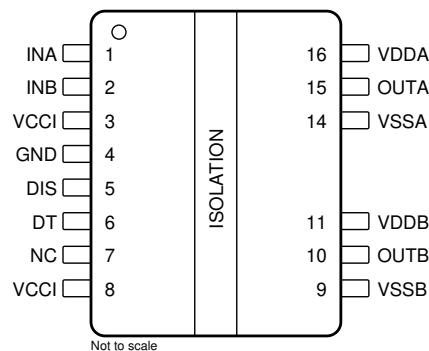

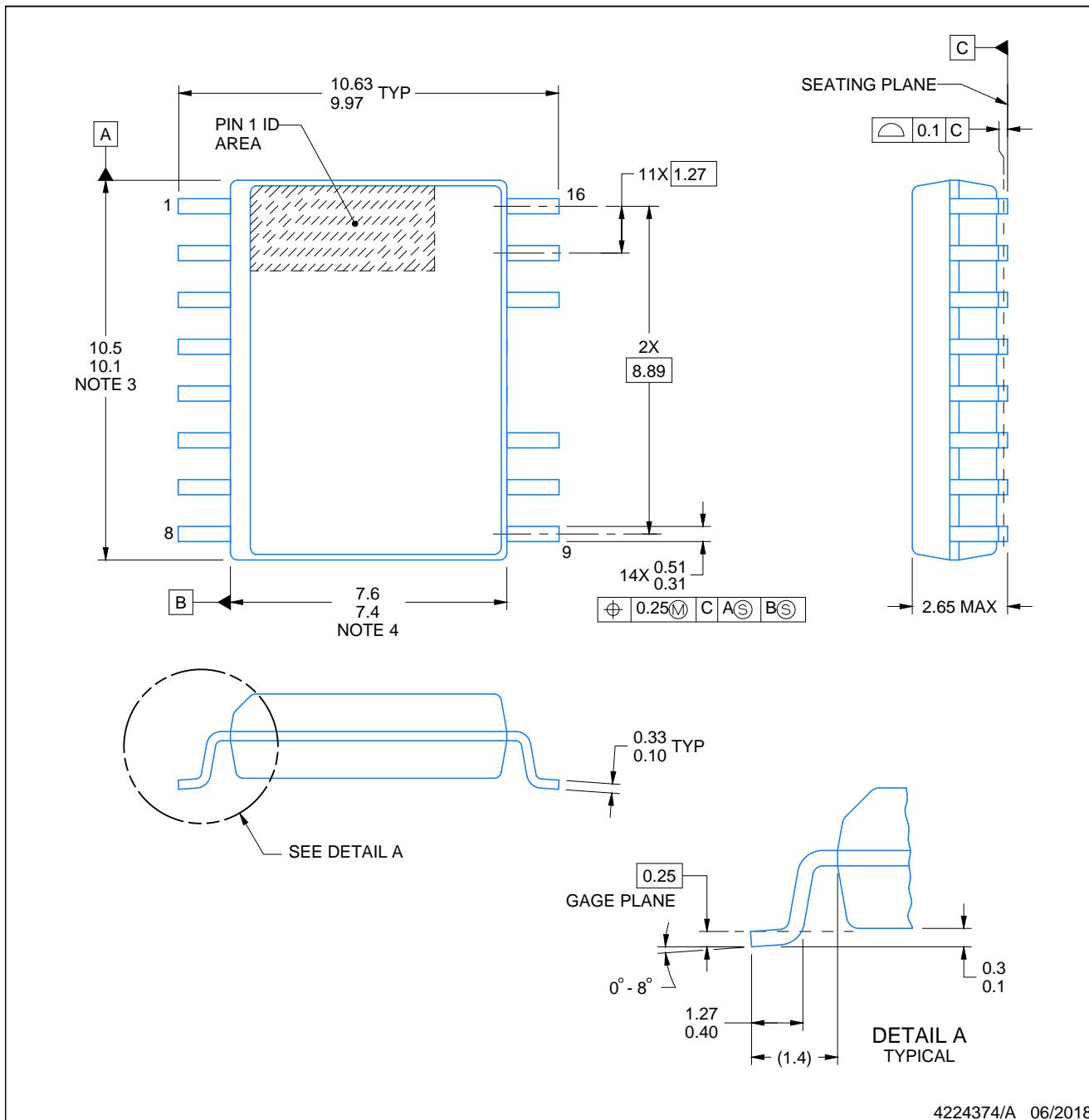

## 5 ピン構成および機能

図 5-1. DWK パッケージ 14 ピン SOIC 上面図

表 5-1. ピンの機能

| ピン   | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                    |

|------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称   | 番号                 |                                                                                                                                                                                                                                                                                       |

| DIS  | 5                  | I<br>High にアサートすると両方のドライバ出力はディセーブルされ、Low に設定するとイネーブルされます。このピンを使わない場合、ノイズ耐性を向上させるためにグランドに接続することを推奨します。離れた場所にあるマイクロコントローラに接続するときは、DIS ピンに近接して配置した約 1nF の低 ESR/ESL コンデンサを使ってバイパスします。                                                                                                     |

| DT   | 6                  | I<br>DT ピンの設定：<br>• DT を VCCI に接続すると、DT 機能は無効になり、出力がオーバーラップできるようになります。<br>• DT と GND の間に抵抗 ( $R_{DT}$ (kΩ)) を配置することで、次の式に従ってデッドタイムを調整できます。<br>$DT (ns) = 10 \times R_{DT} (k\Omega)$ 。ノイズ耐性を向上させるため、DT ピンに近接して配置した 1nF 以下のセラミック コンデンサでこのピンをバイパスすることを推奨します。DT をフローティングのままにすることは推奨しません。 |

| GND  | 4                  | P<br>1 次側のグランド基準。1 次側のすべての信号はこのグランドを基準とします。                                                                                                                                                                                                                                           |

| INA  | 1                  | I<br>A チャネルの入力信号。INA 入力は TTL/CMOS 互換の入力スレッショルドを持っています。このピンは、オープンのままにすると内部で Low にプルされます。このピンを使わない場合、ノイズ耐性を向上させるためにグランドに接続することを推奨します。                                                                                                                                                   |

| INB  | 2                  | I<br>B チャネルの入力信号。INB 入力は TTL/CMOS 互換の入力スレッショルドを持っています。このピンは、オープンのままにすると内部で Low にプルされます。このピンを使わない場合、ノイズ耐性を向上させるためにグランドに接続することを推奨します。                                                                                                                                                   |

| NC   | 7                  | —<br>内部接続なしこのピンはオープンのまま、VCCI に接続、GND に接続のいずれかにできます。                                                                                                                                                                                                                                   |

| NC   | 12                 | —<br>SOIC-14 DWK パッケージの場合、ピン 12 とピン 13 は除去されています。                                                                                                                                                                                                                                     |

| NC   | 13                 | —                                                                                                                                                                                                                                                                                     |

| OUTA | 15                 | O<br>ドライバ A の出力。A チャネルの FET または IGBT のゲートに接続します。                                                                                                                                                                                                                                      |

| OUTB | 10                 | O<br>ドライバ B の出力。B チャネルの FET または IGBT のゲートに接続します。                                                                                                                                                                                                                                      |

| VCCI | 3                  | P<br>1 次側の電源電圧。本デバイスにできる限り近づけて配置した低 ESR/ESL コンデンサを使って GND に対して局所的にデカッピングします。                                                                                                                                                                                                          |

| VCCI | 8                  | P<br>このピンはピン 3 と内部で短絡しています。<br>ピン 8~4 の代わりにピン 3~4 をバイパスすることを推奨します。                                                                                                                                                                                                                    |

| VDDA | 16                 | P<br>ドライバ A の 2 次側電源。本デバイスにできる限り近づけて配置した低 ESR/ESL コンデンサを使って VSSA に対して局所的にデカッピングします。                                                                                                                                                                                                   |

表 5-1. ピンの機能 (続き)

| ピン   |    | タイプ <sup>(1)</sup> | 説明                                                                              |

|------|----|--------------------|---------------------------------------------------------------------------------|

| 名称   | 番号 |                    |                                                                                 |

| VDDB | 11 | P                  | ドライバ B の 2 次側電源。本デバイスにできる限り近づけて配置した低 ESR/ESL コンデンサを使って VSSB に対して局所的にデカップリングします。 |

| VSSA | 14 | P                  | 2 次側のドライバ A のグランド。2 次側の A チャネルのグランドリファレンス電圧。                                    |

| VSSB | 9  | P                  | 2 次側のドライバ B のグランド。2 次側の B チャネルのグランドリファレンス電圧。                                    |

(1) P = 電源、I = 入力、O = 出力

## 6 仕様

### 6.1 絶対最大定格

自由空気での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                             |                                         | 最小値  | 最大値                             | 単位 |

|-----------------------------|-----------------------------------------|------|---------------------------------|----|

| 入力バイアス ピン電源電圧               | VCCI (GND 基準)                           | -0.3 | 20                              | V  |

| ドライバ バイアス電源                 | VDDA-VSSA、VDBB-VSSB                     | -0.3 | 30                              | V  |

| 出力信号電圧                      | OUTA (VSSA 基準)、OUTB (VSSB 基準)           | -0.3 | $V_{VDDA}+0.3$ 、 $V_{VDBB}+0.3$ | V  |

|                             | OUTA (VSSA 基準)、OUTB (VSSB 基準)、200ns の過渡 | -2   | $V_{VDDA}+0.3$ 、 $V_{VDBB}+0.3$ | V  |

| 入力信号電圧                      | INA、INB、DIS、DT (GND 基準)                 | -0.3 | $V_{VCCI}+0.3$                  | V  |

|                             | INA、INB 過渡 (GND 基準、50ns)                | -5   | $V_{VCCI}+0.3$                  | V  |

| チャネル間絶縁電圧                   | $ VSSA-VSSB $ (DWK パッケージ)               |      | 1850                            | V  |

| 接合部温度、 $T_J$ <sup>(2)</sup> |                                         | -40  | 150                             | °C |

| 保管温度、 $T_{stg}$             |                                         | -65  | 150                             | °C |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値と等しい、またはそれを超える条件で本製品が正しく動作することを暗に示すものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

- (2)  $T_J$  の推奨動作条件を維持するには、[セクション 6.4](#) を参照してください。

### 6.2 ESD 定格

|             |                                            | 値          | 単位 |

|-------------|--------------------------------------------|------------|----|

| $V_{(ESD)}$ | 人体モデル (HBM)、AEC Q100-002 準拠 <sup>(1)</sup> | $\pm 2000$ | V  |

|             | デバイス帯電モデル (CDM)、AEC Q100-011 準拠            | $\pm 1000$ |    |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 6.3 推奨動作条件

自由空気での動作温度範囲内 (特に記述のない限り)

|               |              | 最小値 | 最大値 | 単位 |

|---------------|--------------|-----|-----|----|

| VCCI          | VCCI 入力電源電圧  | 3   | 18  | V  |

| VDDA、<br>VDBB | ドライバ出力バイアス電源 | 9.2 | 25  |    |

|               |              | 6.5 | 25  |    |

| $T_J$         | 接合部温度        | -40 | 150 | °C |

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>                    | UCC21540-Q1 | 単位   |

|-----------------------------------------|-------------|------|

|                                         | DWK (SOIC)  |      |

| R <sub>θJA</sub> 接合部から周囲への熱抵抗           | 74.1        | °C/W |

| R <sub>θJC(top)</sub> 接合部からケース(上面)への熱抵抗 | 34.1        | °C/W |

| R <sub>θJB</sub> 接合部から基板への熱抵抗           | 32.8        | °C/W |

| Ψ <sub>JT</sub> 接合部から上面への特性パラメータ        | 23.7        | °C/W |

| Ψ <sub>JB</sub> 接合部から基板への特性パラメータ        | 32.1        | °C/W |

(1) 従来および最新の熱測定基準の詳細については、アプリケーション レポート『半導体および IC パッケージの熱評価基準』(SPRA953) を参照してください。

## 6.5 電力定格

|                                              | 値   | 単位 |

|----------------------------------------------|-----|----|

| P <sub>D</sub> 消費電力                          | 950 | mW |

| P <sub>DI</sub> トランスマッタ側の消費電力                | 50  | mW |

| P <sub>DA</sub> 、P <sub>DB</sub> 各ドライバ側の消費電力 | 450 | mW |

## 6.6 絶縁仕様

| パラメータ                                            | テスト条件                                                                                                                                                                                                            | 値     | 単位               |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------|

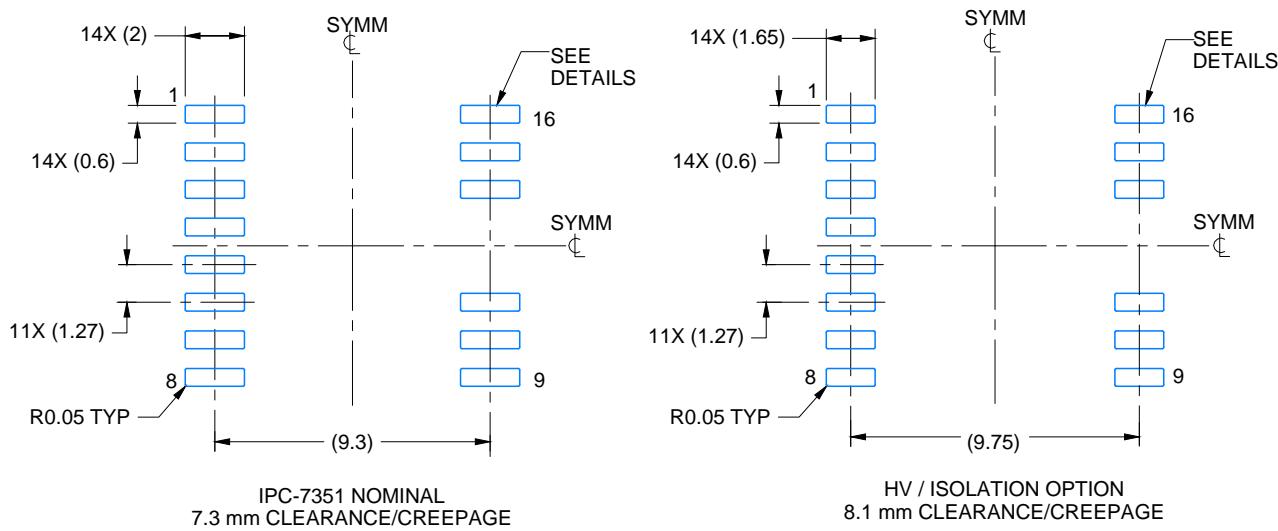

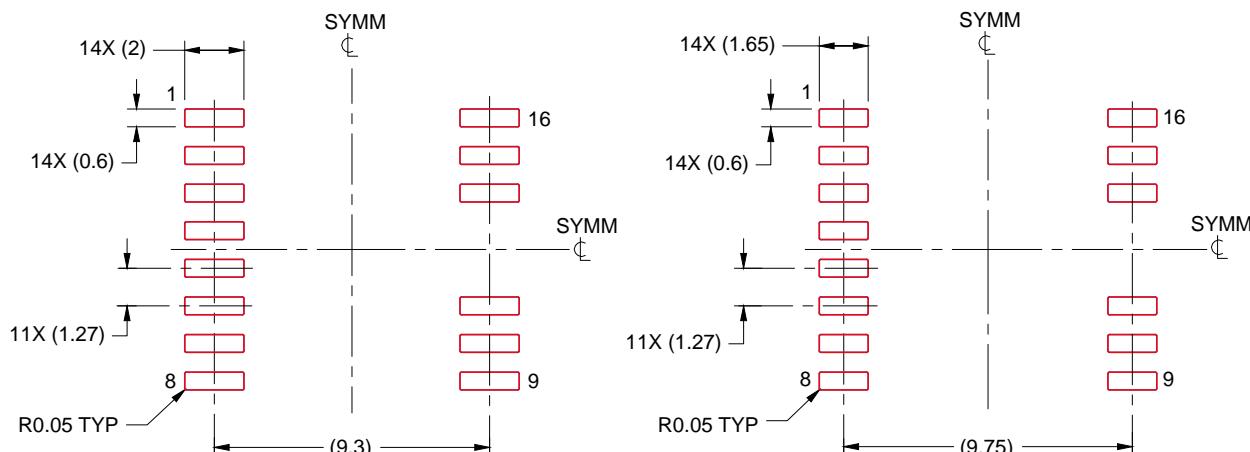

| CLR 外部空間距離 <sup>(1)</sup>                        | 空気中の最短のピン間距離                                                                                                                                                                                                     | > 8   | mm               |

| CPG 外部沿面距離 <sup>(1)</sup>                        | パッケージ表面に沿った最短のピン間距離                                                                                                                                                                                              | > 8   | mm               |

| DTI 絶縁間の距離                                       | 二重絶縁 (2 × 8.5μm) の最小内部ギャップ(内部距離)                                                                                                                                                                                 | >17   | μm               |

| CTI 比較トラッキングインデックス                               | DIN EN 60112 (VDE 0303-11)、IEC 60112                                                                                                                                                                             | > 600 | V                |

| 材料グループ                                           | IEC 60664-1 に準拠                                                                                                                                                                                                  | I     |                  |

| IEC 60664-1 に準拠した過電圧カテゴリ                         | 定格商用電源 V <sub>RMS</sub> が 600V 以下                                                                                                                                                                                | I-IV  |                  |

|                                                  | 定格商用電源 V <sub>RMS</sub> が 1000V 以下                                                                                                                                                                               | I-III |                  |

| DIN EN IEC 60747-17 (VDE 0884-17) <sup>(2)</sup> |                                                                                                                                                                                                                  |       |                  |

| V <sub>IORM</sub> 最大反復ピーク絶縁電圧                    | AC 電圧 (バイポーラ)                                                                                                                                                                                                    | 1414  | V <sub>PK</sub>  |

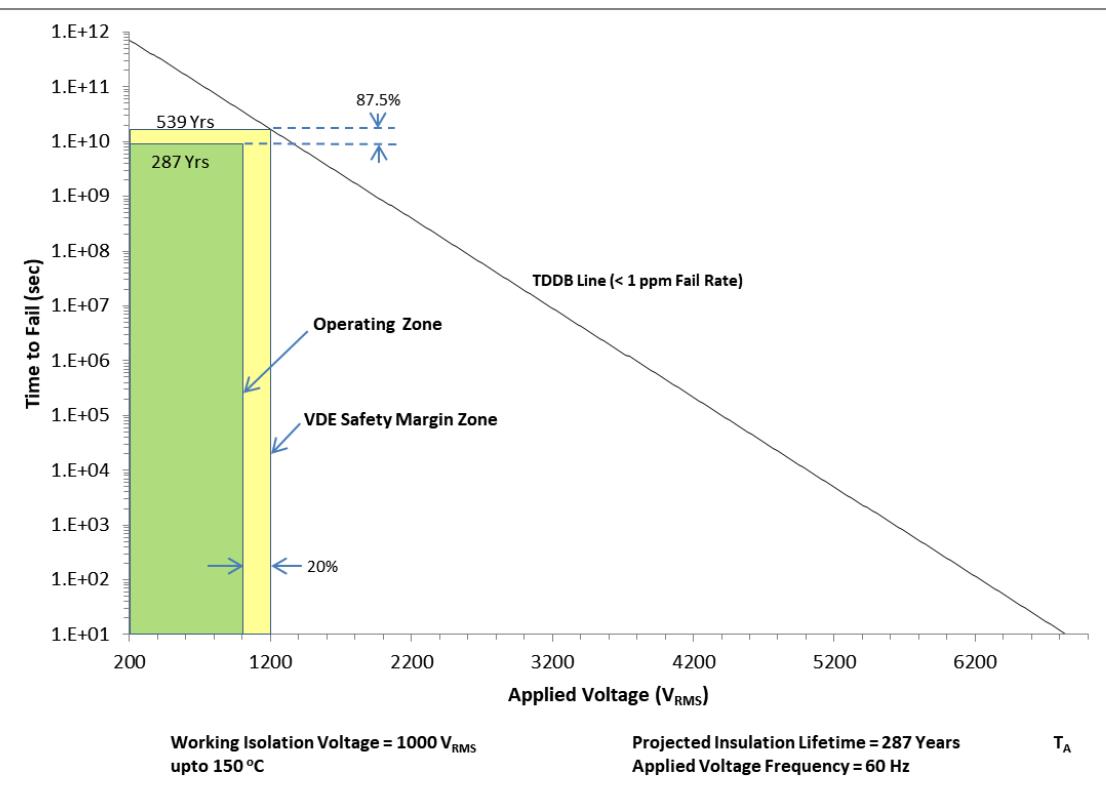

| V <sub>IOWM</sub> 最大動作絶縁電圧                       | AC 電圧 (正弦波)、絶縁膜経時破壊 (TDDB)、テスト (図 6-1 を参照。)                                                                                                                                                                      | 1000  | V <sub>RMS</sub> |

|                                                  | DC 電圧                                                                                                                                                                                                            | 1414  | V <sub>DC</sub>  |

| V <sub>IMP</sub> 最大インパルス電圧                       | IEC 62368-1 に準拠し空気中でテスト、1.2/50μs の波形                                                                                                                                                                             | 7692  | V <sub>PK</sub>  |

| V <sub>IOTM</sub> 最大過渡絶縁電圧                       | V <sub>TEST</sub> = V <sub>IOTM</sub> 、t = 60s (認定)<br>V <sub>TEST</sub> = 1.2 × V <sub>IOTM</sub> 、t = 1s (100% 出荷時)                                                                                            | 8000  | V <sub>PK</sub>  |

| V <sub>IOSM</sub> 最大サージ絶縁電圧 <sup>(3)</sup>       | IEC 62368-1 に準拠したテスト手法、1.2/50μs 波形、<br>V <sub>TEST</sub> = 1.6 × V <sub>IOSM</sub> = 12800V <sub>PK</sub> (認定)                                                                                                   | 10000 | V <sub>PK</sub>  |

| q <sub>pd</sub> 見掛けの電荷 <sup>(4)</sup>            | 方法 a、I/O 安全テスト サブグループ 2/3 の後<br>V <sub>ini</sub> = V <sub>IOTM</sub> 、t <sub>ini</sub> = 60s、<br>V <sub>pd(m)</sub> = 1.2 × V <sub>IORM</sub> = 1697V <sub>PK</sub> 、t <sub>m</sub> = 10s                        | <5    | pC               |

|                                                  | 方法 a、環境テスト サブグループ 1 の後<br>V <sub>ini</sub> = V <sub>IOTM</sub> 、t <sub>ini</sub> = 60s、<br>V <sub>pd(m)</sub> = 1.6 × V <sub>IORM</sub> = 2262V <sub>PK</sub> 、t <sub>m</sub> = 10s                              | <5    |                  |

|                                                  | 方法 b1、ルーチン テスト (100% 出荷時) および事前条件設定 (タイプ テスト)<br>V <sub>ini</sub> = 1.2 × V <sub>IOTM</sub> 、t <sub>ini</sub> = 1s、<br>V <sub>pd(m)</sub> = 1.875 × V <sub>IORM</sub> = 2651V <sub>PK</sub> 、t <sub>m</sub> = 1s | <5    |                  |

| C <sub>IO</sub> 絶縁バリア容量、入力から出力へ <sup>(5)</sup>   | V <sub>IO</sub> = 0.4 sin (2πft)、f = 1MHz                                                                                                                                                                        | 1.2   | pF               |

## 6.6 絶縁仕様 (続き)

| パラメータ                                   | テスト条件                                                                                                                       | 値           | 単位        |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------|-----------|

| $R_{IO}$<br>絶縁抵抗、入力から出力へ <sup>(5)</sup> | $V_{IO} = 500V$ ( $T_A = 25^\circ C$ 時)                                                                                     | $> 10^{12}$ | $\Omega$  |

|                                         | $V_{IO} = 500V$ ( $100^\circ C \leq T_A \leq 125^\circ C$ 時)                                                                | $> 10^{11}$ |           |

|                                         | $V_{IO} = 500V$ ( $T_S = 150^\circ C$ 時)                                                                                    | $> 10^9$    |           |

| 汚染度                                     |                                                                                                                             | 2           |           |

| 耐候性カテゴリ                                 |                                                                                                                             | 40/125/21   |           |

| <b>UL 1577</b>                          |                                                                                                                             |             |           |

| $V_{ISO}$<br>絶縁耐圧                       | $V_{TEST} = V_{ISO} = 5700V_{RMS}$ , $t = 60s$ (認定),<br>$V_{TEST} = 1.2 \times V_{ISO} = 6840V_{RMS}$ , $t = 1s$ (100% 出荷時) | 5700        | $V_{RMS}$ |

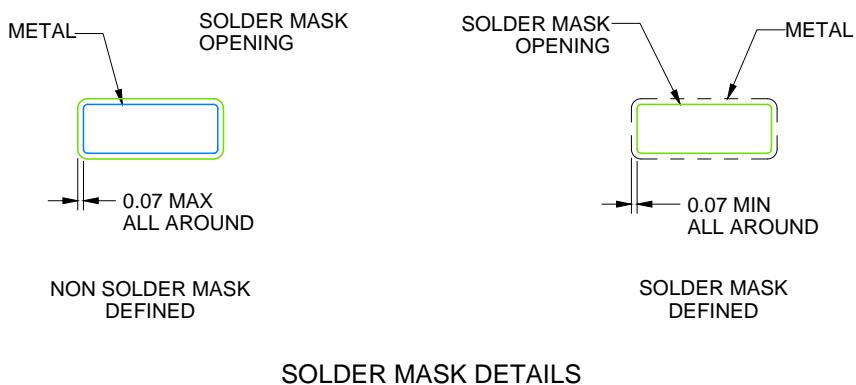

- (1) 沿面距離および空間距離の要件は、アプリケーション個別の機器絶縁規格に従って適用する必要があります。沿面距離および空間距離を維持するために、プリント基板上でアイソレータの取り付けパッドによってこの距離が短くならないように注意して基板を設計する必要があります。場合によっては、プリント基板上の沿面距離と空間距離が等しくなります。これらの規格値を増やすため、プリント基板上にグループやリブを挿入するなどの技法が使用されます。

- (2) この絶縁素子は、安全定格内に限定した安全な電気的絶縁に適しています。安全定格への準拠は、適切な保護回路によって保証する必要があります。

- (3) テストは、絶縁バリアの固有サージ耐性を判定するため、気中または油中で実行されます。

- (4) 見掛けの放電電荷とは、部分放電 (pd) により発生する放電です。

- (5) 絶縁バリアのそれぞれの側にあるすべてのピンを互いに接続して、2つの端子を持つデバイスを構成します。

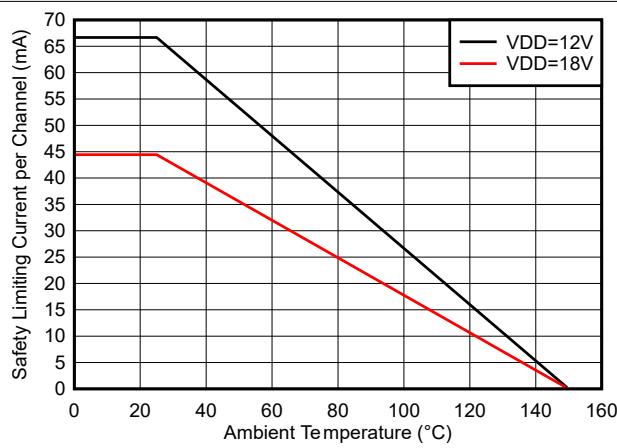

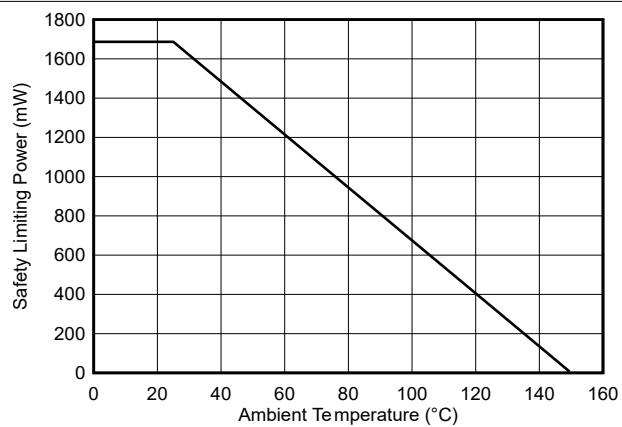

## 6.7 安全限界値

安全限界値の目的は、入力または出力回路の故障による絶縁バリアの損傷の可能性を最小限に抑えることです。

| パラメータ                        | テスト条件                                                                                                                       | 側             | 最小値 | 標準値   | 最大値 | 単位 |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------|-----|-------|-----|----|

| $I_S$<br>安全出力電源電流            | $\theta_{JA} = 74.1^\circ C/W$ 、 $V_{VDDA/B} = 12V$ 、 $T_J = 150^\circ C$ 、 $T_A = 25^\circ C$<br><a href="#">図 6-2 を参照</a> | ドライバ A、ドライバ B |     |       | 66  | mA |

| $P_S$<br>安全電源                | $\theta_{JA} = 74.1^\circ C/W$ 、 $V_{VCCI} = 5.5V$ 、 $T_J = 150^\circ C$ 、 $T_A = 25^\circ C$<br><a href="#">図 6-3 を参照</a>  | 入力            |     | 50    | mW  |    |

|                              |                                                                                                                             | ドライバ A        |     | 8 00  |     |    |

|                              |                                                                                                                             | ドライバ B        |     | 8 00  |     |    |

|                              |                                                                                                                             | 合計            |     | 1 650 |     |    |

| $T_S$<br>安全温度 <sup>(1)</sup> |                                                                                                                             |               |     | 150   |     | °C |

- (1) 最高安全温度  $T_S$  は、本デバイスに規定された最大接合部温度  $T_J$  と同じ値です。 $I_S$  および  $P_S$  パラメータはそれぞれ安全電流と安全電力を表します。 $I_S$  および  $P_S$  の最大限界値を超過してはなりません。これらの限界値は、周囲温度  $T_A$  によって異なります。

**セクション 6.4** 表にある接合部から空気への熱抵抗  $R_{\theta JA}$  は、リード付き表面実装パッケージ向けの High-K テスト ボードに実装されたデバイスの数値です。これらの式を使用して、以下のように各パラメータの値を計算します。

$$T_J = T_A + R_{\theta JA} \times P$$

ここで、 $P$  は本デバイスで消費される電力です。

$$T_{J(max)} = T_S = T_A + R_{\theta JA} \times P_S$$

ここで、 $T_{J(max)}$  は許容される最大接合部温度です。

$$P_S = I_S \times V_I$$

ここで、 $V_I$  は最大入力電圧です。

## 6.8 電気的特性

$V_{VCCI} = 3.3V$  または  $5.0V$ 、 $V_{VCCI}$  から  $GND$  に  $0.1\mu F$  のコンデンサを接続、 $VDDA/B$  から  $VSSA/B$  に  $1\mu F$  のコンデンサを接続、 $V_{VDDA} = V_{VDBB} = 15V$ 、 $VDDA$  および  $VDBB$  から  $VSSA$  および  $VSSB$  に  $1\mu F$  のコンデンサを接続、 $DT$  ピンを  $VCCI$  に接続、 $C_L = 0pF$ 、 $T_J = -40^{\circ}C \sim +150^{\circ}C$  (特に記述のない限り)<sup>(1)</sup> <sup>(2)</sup>。

| パラメータ                                            | テスト条件                                                                              | 最小値                                                                                                                            | 標準値  | 最大値  | 単位       |

|--------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------|------|----------|

| <b>供給電流</b>                                      |                                                                                    |                                                                                                                                |      |      |          |

| $I_{VCCI}$                                       | $V_{VCCI}$ 静止電流<br>$V_{INA} = 0V$ 、 $V_{INB} = 0V$                                 | 1.5                                                                                                                            | 2.0  | 2.0  | mA       |

| $I_{VDDA}$ 、 $I_{VDBB}$                          | $VDDA$ と $VDBB$ の静止電流<br>$V_{INA} = 0V$ 、 $V_{INB} = 0V$                           | 1.0                                                                                                                            | 2.5  | 2.5  | mA       |

| $I_{VCCI}$                                       | $V_{VCCI}$ 動作電流<br>チャネルあたりの電流 ( $f = 500kHz$ 、50% デューティ サイクル)                      | 3.0                                                                                                                            | 3.5  | 3.5  | mA       |

| $I_{VDDA}$ 、 $I_{VDBB}$                          | $VDDA$ と $VDBB$ の動作電流<br>チャネルあたりの電流 ( $f = 500kHz$ 、50% デューティ サイクル)、 $C_L = 100pF$ | 2.5                                                                                                                            | 4.2  | 4.2  | mA       |

| <b>VCC 電源電圧の低電圧スレッショルド</b>                       |                                                                                    |                                                                                                                                |      |      |          |

| $V_{VCCI\_ON}$                                   | UVLO 立ち上がりスレッショルド                                                                  | 2.55                                                                                                                           | 2.7  | 2.85 | V        |

| $V_{VCCI\_OFF}$                                  | UVLO 立ち下がりスレッショルド                                                                  | 2.35                                                                                                                           | 2.5  | 2.65 | V        |

| $V_{VCCI\_HYS}$                                  | UVLO スレッショルドのヒステリシス                                                                | 0.2                                                                                                                            |      |      | V        |

| <b>UCC21540-Q1 の VDD 電源電圧の低電圧スレッショルド</b>         |                                                                                    |                                                                                                                                |      |      |          |

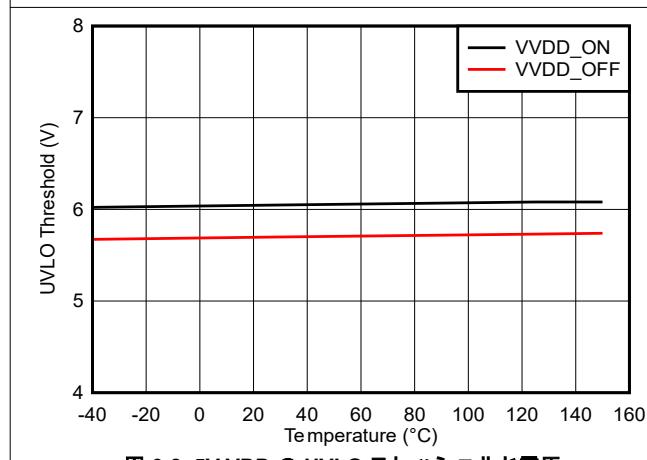

| $V_{VDDA\_ON}$ 、 $V_{VDBB\_ON}$                  | UVLO 立ち上がりスレッショルド                                                                  | 5.7                                                                                                                            | 6.0  | 6.3  | V        |

| $V_{VDDA\_OFF}$ 、 $V_{VDBB\_OFF}$                | UVLO 立ち下がりスレッショルド                                                                  | 5.4                                                                                                                            | 5.7  | 6.0  | V        |

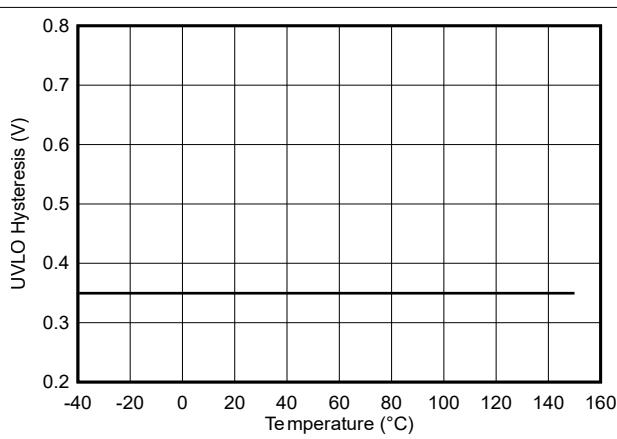

| $V_{VDDA\_HYS}$ 、 $V_{VDBB\_HYS}$                | UVLO スレッショルドのヒステリシス                                                                | 0.3                                                                                                                            |      |      | V        |

| <b>UCC21540-Q1 の VDD 電源電圧の低電圧スレッショルド</b>         |                                                                                    |                                                                                                                                |      |      |          |

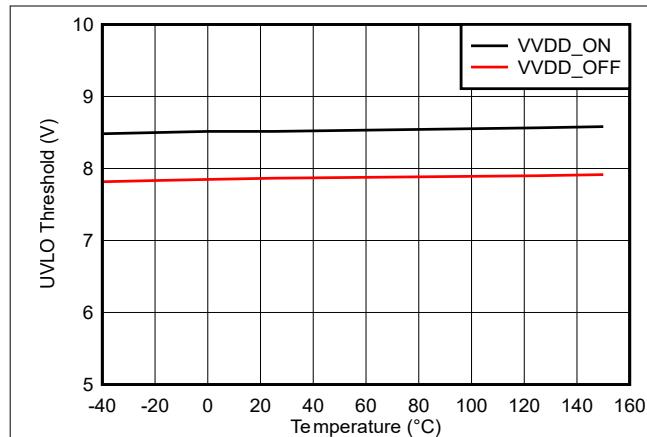

| $V_{VDDA\_ON}$ 、 $V_{VDBB\_ON}$                  | UVLO 立ち上がりスレッショルド                                                                  | 7.7                                                                                                                            | 8.5  | 8.9  | V        |

| $V_{VDDA\_OFF}$ 、 $V_{VDBB\_OFF}$                | UVLO 立ち下がりスレッショルド                                                                  | 7.2                                                                                                                            | 7.9  | 8.4  | V        |

| $V_{VDDA\_HYS}$ 、 $V_{VDBB\_HYS}$                | UVLO スレッショルドのヒステリシス                                                                | 0.6                                                                                                                            |      |      | V        |

| <b>INA、INB、DISABLE</b>                           |                                                                                    |                                                                                                                                |      |      |          |

| $V_{INA\_HYS}$ 、 $V_{INB\_HYS}$ 、 $V_{DIS\_HYS}$ | 入力 High スレッショルド電圧                                                                  | 1.2                                                                                                                            | 1.8  | 2    | V        |

| $V_{INA\_L}$ 、 $V_{INB\_L}$ 、 $V_{DIS\_L}$       | 入力 Low スレッショルド電圧                                                                   | 0.8                                                                                                                            | 1    | 1.2  | V        |

| $V_{INA\_HYS}$ 、 $V_{INB\_HYS}$ 、 $V_{DIS\_HYS}$ | 入力スレッショルドのヒステリシス                                                                   | 0.8                                                                                                                            |      |      | V        |

| <b>出力</b>                                        |                                                                                    |                                                                                                                                |      |      |          |

| $I_{OA+}$ 、 $I_{OB+}$                            | ピーク出力カソース電流                                                                        | $C_{VDD} = 10\mu F$ 、 $C_{LOAD} = 0.18\mu F$ 、 $f = 1kHz$ 、ベンチ測定                                                               | 4    |      | A        |

| $I_{OA-}$ 、 $I_{OB-}$                            | ピーク出力シンク電流                                                                         |                                                                                                                                | 6    |      | A        |

| $R_{OHA}$ 、 $R_{OHB}$                            | HIGH 状態の出力抵抗                                                                       | $I_{OUT} = -10mA$ 、 $R_{OHA}$ 、 $R_{OHB}$ は、駆動プルアップ性能を表すものではありません。詳細については、 <a href="#">セクション 8.3.4</a> の $t_{RISE}$ を参照してください。 | 5    |      | $\Omega$ |

| $R_{OLA}$ 、 $R_{OLB}$                            | Low 状態の出力抵抗                                                                        | $I_{OUT} = 10 mA$                                                                                                              | 0.55 |      | $\Omega$ |

## 6.8 電気的特性 (続き)

$V_{VCCI} = 3.3V$  または  $5.0V$ 、 $V_{VCCI}$  から  $GND$  に  $0.1\mu F$  のコンデンサを接続、 $VDDA/B$  から  $VSSA/B$  に  $1\mu F$  のコンデンサを接続、 $V_{VDDA} = V_{VDBB} = 15V$ 、 $VDDA$  および  $VDBB$  から  $VSSA$  および  $VSSB$  に  $1\mu F$  のコンデンサを接続、 $DT$  ピンを  $VCCI$  に接続、 $C_L = 0pF$ 、 $T_J = -40^{\circ}C \sim +150^{\circ}C$  (特に記述のない限り)<sup>(1) (2)</sup>。

| パラメータ                     | テスト条件                                                       | 最小値 | 標準値   | 最大値 | 単位 |

|---------------------------|-------------------------------------------------------------|-----|-------|-----|----|

| $V_{OHA}$ 、 $V_{OHB}$     | $V_{VDDA} = V_{VDBB} = 15V$ 、 $I_{OUT} = 10mA$              |     | 14.95 |     | V  |

| $V_{OLA}$ 、 $V_{OLB}$     | $V_{VDDA} = V_{VDBB} = 15V$ 、 $I_{OUT} = 10mA$              |     | 5.5   |     | mV |

| $V_{OAPDA}$ 、 $V_{OAPDB}$ | $V_{VDDA}$ と $V_{VDBB}$ は未給電、 $I_{OUTA} = I_{OUTB} = 200mA$ |     | 1.6   | 2   | V  |

### デッド タイムとオーバーラップの設定

|               |                      |                               |     |     |    |

|---------------|----------------------|-------------------------------|-----|-----|----|

| デッド タイム、 $DT$ | $DT$ ピンを $VCCI$ に接続  | オーバーラップは $INA$ 、 $INB$ によって決定 |     |     | -  |

|               | $R_{DT} = 10k\Omega$ | 80                            | 100 | 120 | ns |

|               | $R_{DT} = 20k\Omega$ | 160                           | 200 | 240 |    |

|               | $R_{DT} = 50k\Omega$ | 400                           | 500 | 600 |    |

- (1) テスト条件での電流の方向は、そのピンに入る方向が正、そのピンから出る方向が負と定義されています (特に記述のない限り)。

(2) 標準値のみが記載されたパラメータは、参照用にのみ提供しているものであり、TI が製品保証を目的として公表するデバイス仕様書の一部を構成するものではありません。

## 6.9 スイッチング特性

$V_{VCCI} = 3.3V$  または  $5.5V$ 、 $0.1\mu F$  のコンデンサを  $VCCI$  と  $GND$  の間に接続、 $V_{VDDA} = V_{VDBB} = 15V$ 、 $1\mu F$  のコンデンサを  $VDDA/VDBB$  と  $VSSA/VSSB$  の間に接続、負荷容量  $C_{OUT} = 0pF$ 、 $T_J = -40^{\circ}C \sim +150^{\circ}C$  (特に記述のない限り)<sup>(1)</sup>。

| パラメータ              | テスト条件                                                                                                       | 最小値                                                                                                                            | 標準値 | 最大値 | 単位      |

|--------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------|

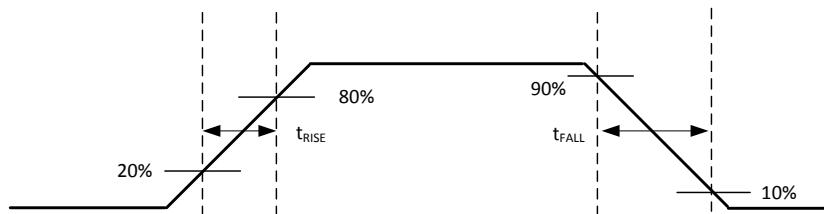

| $t_{RISE}$         | 出力立ち上がり時間 (図 7-4 を参照)<br>$C_{VDD} = 10\mu F$ 、 $C_{OUT} = 1.8nF$ 、 $V_{VDDA} = V_{VDBB} = 12V$ 、 $f = 1kHz$ |                                                                                                                                | 5   | 16  | ns      |

| $t_{FALL}$         | 出力立ち下がり時間 (図 7-4 を参照)<br>$C_{VDD} = 10\mu F$ 、 $C_{OUT} = 1.8nF$ 、 $V_{VDDA} = V_{VDBB} = 12V$ 、 $f = 1kHz$ |                                                                                                                                | 6   | 12  | ns      |

| $t_{PWmin}$        | 出力に到達する最小入力パルス幅 (図 7-1 と図 7-2 を参照)                                                                          | 入力信号が $t_{PWmin}$ より短い場合、出力は状態を変化させません。                                                                                        |     | 20  | ns      |

| $t_{PDHL}$         | 立ち下がりエッジでの伝搬遅延 (図 7-3 を参照)                                                                                  | $INx$ の HIGH スレッショルド ( $V_{INH}$ ) から出力の 10% まで                                                                                | 26  | 33  | ns      |

| $t_{PDLH}$         | 立ち上がりエッジでの伝搬遅延 (図 7-3 を参照)                                                                                  | $INx$ の LOW スレッショルド ( $V_{INL}$ ) から出力の 90% まで                                                                                 | 26  | 33  | ns      |

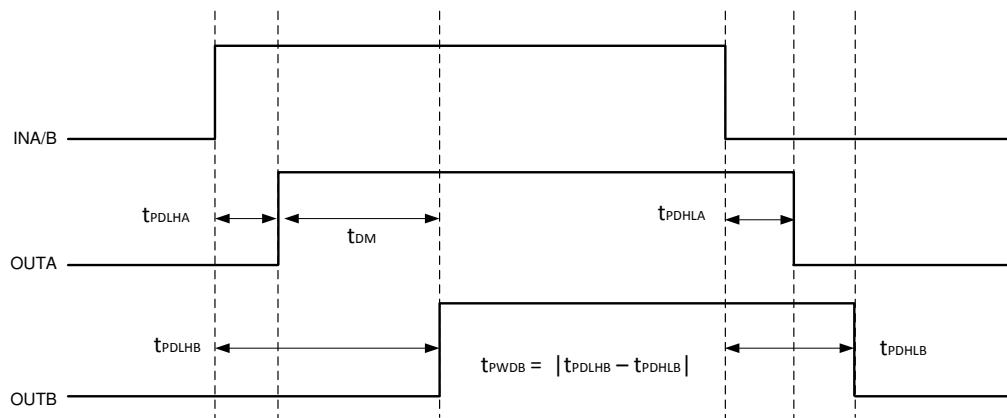

| $t_{PWD}$          | パルス幅歪み                                                                                                      | $ t_{PDLHA} - t_{PDHLA} $ 、 $ t_{PDLHB} - t_{PDHLB} $<br>(図 7-3 を参照)                                                           |     | 6   | ns      |

| $t_{DM}$           | デュアル チャネル ドライバの伝搬遅延マッチング                                                                                    | 入力パルス幅 = $100ns$ 、 $500kHz$ 、 $T_J = -40^{\circ}C \sim -10^{\circ}C$<br>$ t_{PDLHA} - t_{PDLHB} $ 、 $ t_{PDHLA} - t_{PDHLB} $  |     | 6.5 | ns      |

|                    |                                                                                                             | 入力パルス幅 = $100ns$ 、 $500kHz$ 、 $T_J = -10^{\circ}C \sim +150^{\circ}C$<br>$ t_{PDLHA} - t_{PDLHB} $ 、 $ t_{PDHLA} - t_{PDHLB} $ |     | 5   | ns      |

| $t_{VCCI+ to OUT}$ | $VCCI$ 電源オン遅延時間 : UVLO の立ち上がりから $OUTA$ 、 $OUTB$ まで (図 7-7 を参照)                                              | INA または $INB$ を $VCCI$ に接続                                                                                                     |     | 50  | $\mu s$ |

| $t_{VDD+ to OUT}$  | $VDDA$ 、 $VDBB$ の電源オン遅延時間 : UVLO の立ち上がりから $OUTA$ 、 $OUTB$ まで (図 7-8 を参照)                                    | INA または $INB$ を $VCCI$ に接続                                                                                                     |     | 10  |         |

| $ ICM_H $          | HIGH レベルの同相過渡耐性 (セクション 7.7 を参照)                                                                             | GND 対 $VSSA/B$ のスルーレート、 $INA$ と $INB$ の両方を $VCCI$ に接続、 $V_{CM} = 1000V$                                                        | 125 |     | V/ns    |

| $ ICM_L $          | LOW レベルの同相過渡耐性 (セクション 7.7 を参照)                                                                              | GND 対 $VSSA/B$ のスルーレート、 $INA$ と $INB$ の両方を $GND$ に接続、 $V_{CM} = 1000V$                                                         | 125 |     |         |

- (1) 標準値のみが記載されたパラメータは、参照用にのみ提供しているものであり、TI が製品保証を目的として公表するデバイス仕様書の一部を構成するものではありません。

## 6.10 絶縁特性曲線

図 6-1. 強化絶縁コンデンサの寿命予測

各チャネルの電流 (両チャネルを同時に動作させた場合)

図 6-2. VDE に従う制限電流の熱特性低下曲線

図 6-3. VDE に従う制限電力の熱特性低下曲線

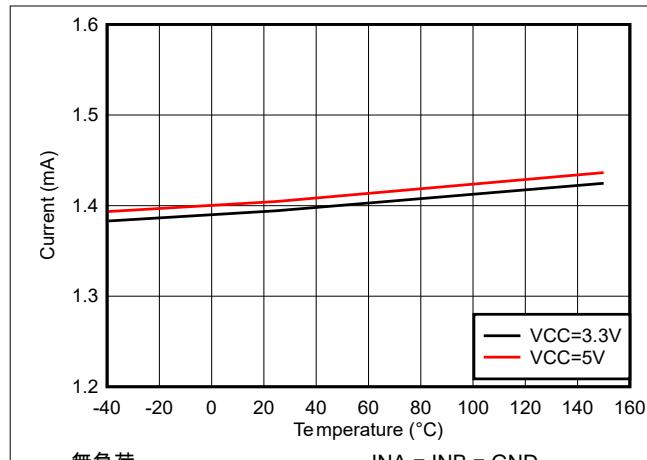

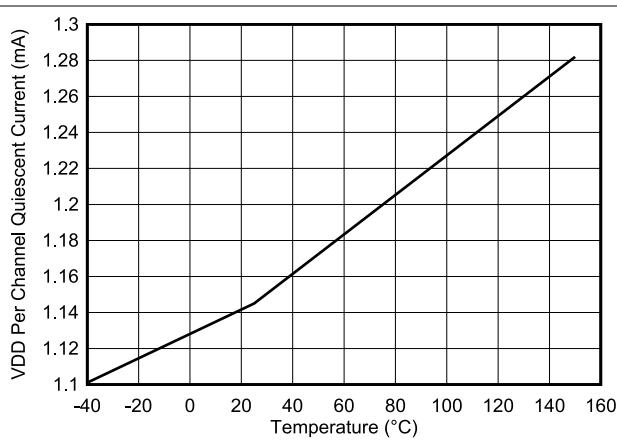

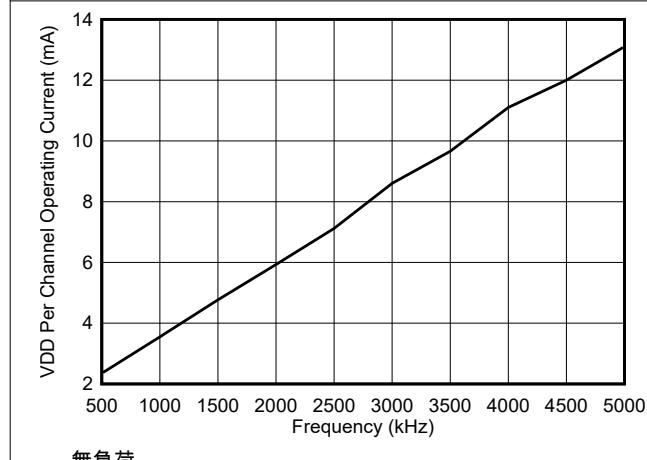

## 6.11 代表的特性

$VDDA = VDDB = 15V$ 、 $VCCI = 3.3V$  または  $5.0V$ 、DT ピンを  $VCCI$  に接続、 $T_A = 25^\circ C$ 、 $C_L = 0pF$  (特に記述のない限り)。

無負荷

$INA = INB = GND$

図 6-4. VCCI 静止時電流

無負荷

$INA = INB = GND$

図 6-5. VDD のチャネルあたりの静止電流 ( $I_{VDDA}$ 、 $I_{VDDB}$ )

無負荷

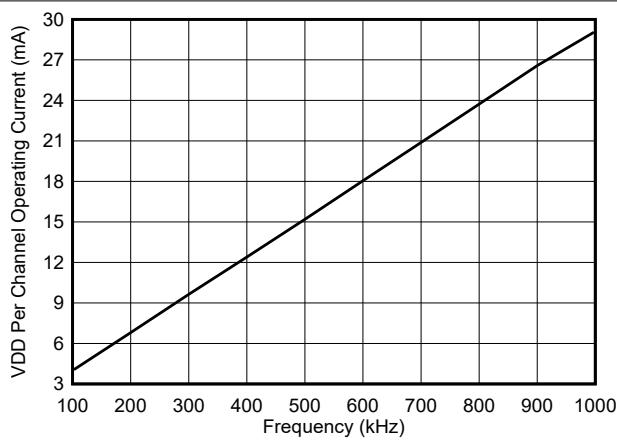

図 6-6. VDD のチャネルあたりの動作電流 -  $I_{VDDA/B}$

図 6-7. チャネルあたりの動作電流 ( $I_{VDDA/B}$ ) と周波数との関係、

1.8nF 負荷

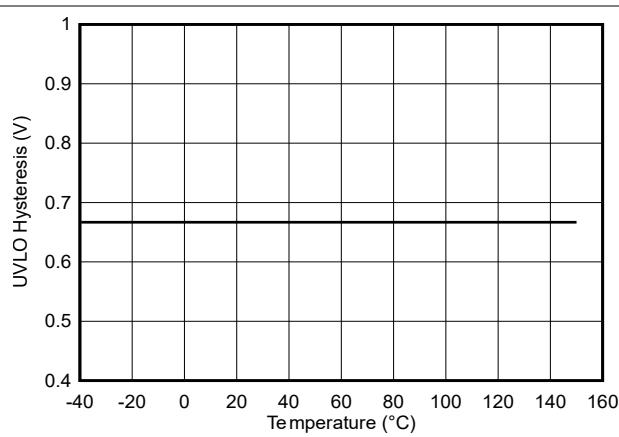

図 6-8. 5V VDD の UVLO スレッショルド電圧

図 6-9. 5V VDD の UVLO ヒステリシス電圧

## 6.11 代表的特性 (続き)

$VDDA = VDDB = 15V$ 、 $VCCI = 3.3V$  または  $5.0V$ 、DT ピンを  $VCCI$  に接続、 $T_A = 25^\circ C$ 、 $C_L = 0pF$  (特に記述のない限り)。

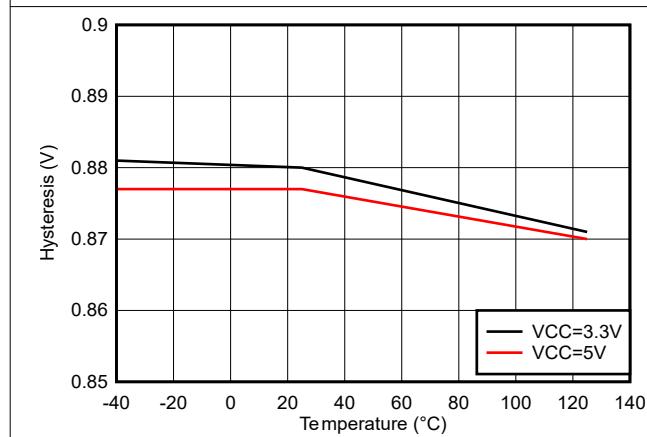

図 6-10. 8V VDD の UVLO スレッショルド電圧

図 6-11. 8V VDD の UVLO スレッショルドヒステリシス電圧

図 6-12. INA/INB/DIS の HIGH および LOW スレッショルドヒステリシス

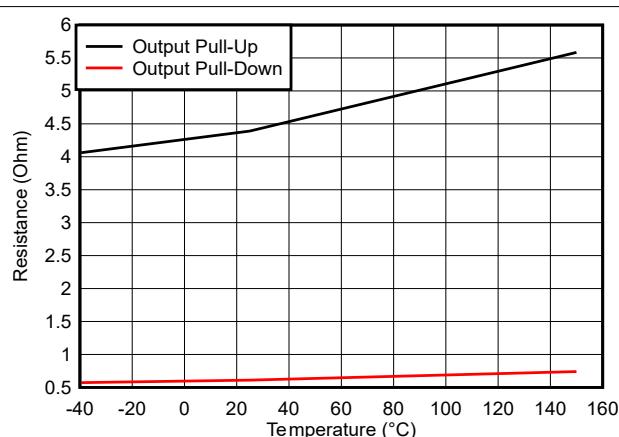

図 6-13. OUT のプルアップおよびプルダウン抵抗

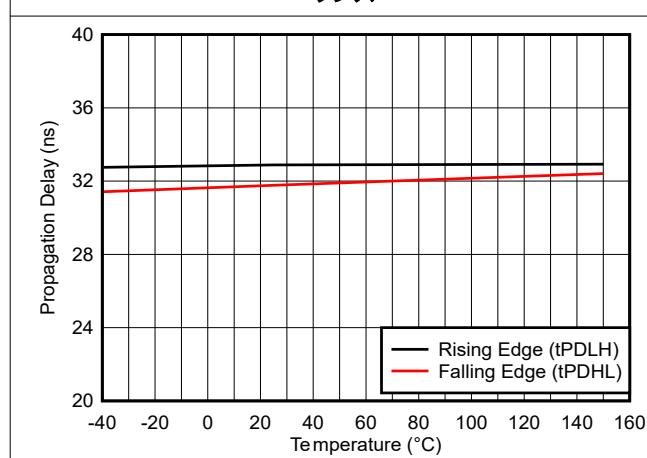

図 6-14. 伝搬遅延、立ち上がりおよび立ち下がりエッジ

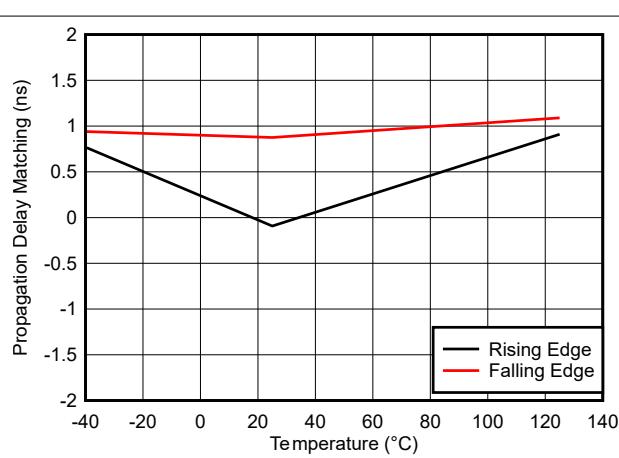

図 6-15. 伝搬遅延のマッチング、立ち上がりおよび立ち下がりエッジ

## 6.11 代表的特性 (続き)

$VDDA = VDBB = 15V$ 、 $VCCI = 3.3V$  または  $5.0V$ 、DT ピンを VCCI に接続、 $T_A = 25^\circ C$ 、 $C_L = 0pF$  (特に記述のない限り)。

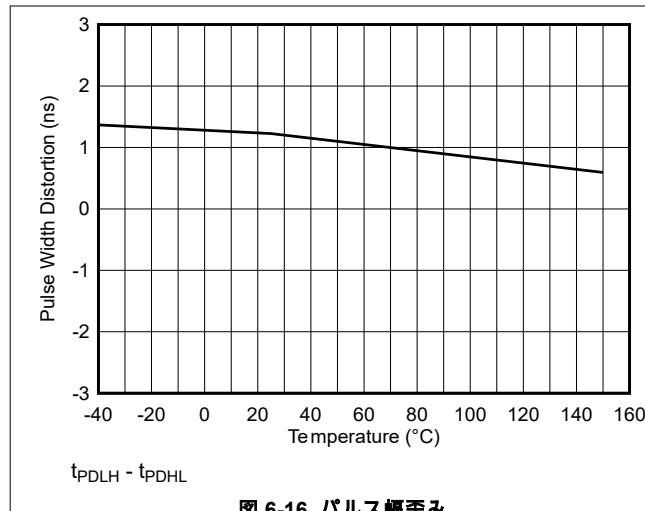

図 6-16. パルス幅歪み

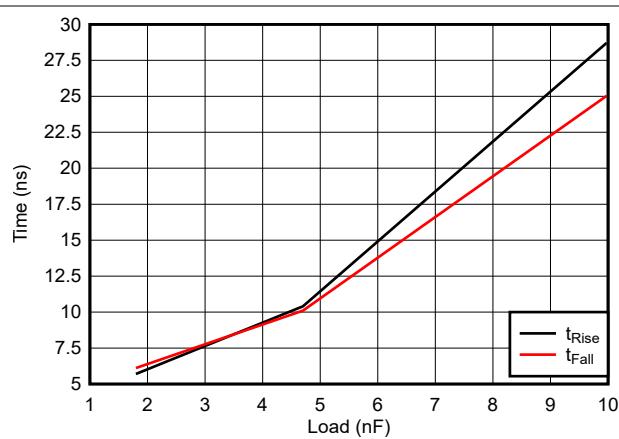

図 6-17. 負荷による立ち上がり時間と立ち下がり時間

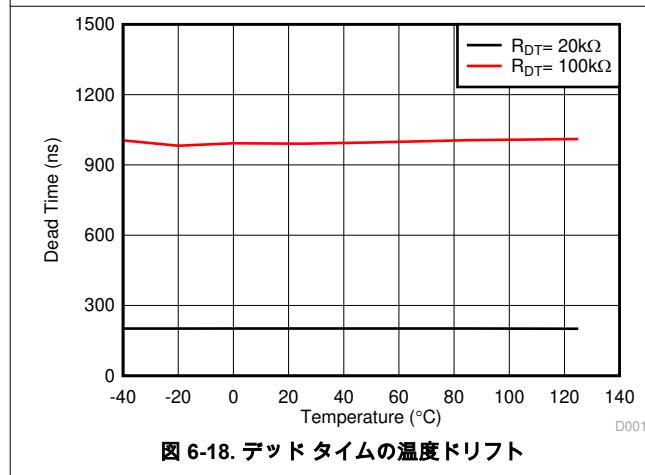

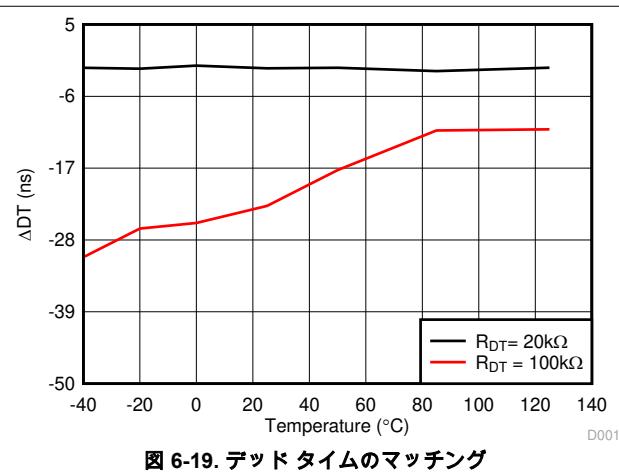

図 6-18. デッドタイムの温度ドリフト

図 6-19. デッドタイムのマッチング

## 7 パラメータ測定情報

### 7.1 最小パルス

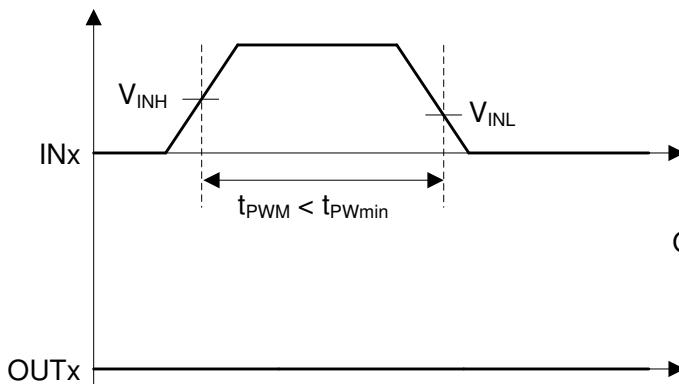

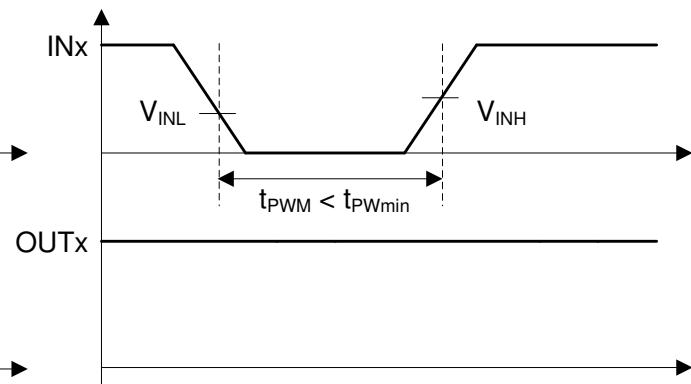

OUTA または OUTB での出力状態を確実に変化させるには、 $t_{PWmin}$  (最大値 20ns) よりも長い入力パルスを INA または INB にアサートする必要があります。グリッチ除去フィルタの動作の詳細については、図 7-1 と図 7-2 を参照してください。

図 7-1. グリッチ除去フィルタ - ターンオン

図 7-2. グリッチ除去フィルタ - ターンオフ

### 7.2 伝搬遅延とパルス幅歪み

図 7-3 に、チャネル A および B の伝搬遅延からパルス幅歪み ( $t_{PWD}$ ) と遅延マッチング ( $t_{DM}$ ) を計算する方法を示します。遅延マッチングを測定するには、両方の入力の位相を揃え、DT ピンを VCCI に短絡して出力オーバーラップを有効にする必要があります。

図 7-3. 遅延マッチングとパルス幅歪み

### 7.3 立ち上がりおよび立ち下がり時間

図 7-4 に、立ち上がり ( $t_{RISE}$ ) および立ち下がり ( $t_{FALL}$ ) 時間の測定基準を示します。立ち上がり時間と立ち下がり時間を短縮する方法の詳細については、セクション 8.3.4 を参照してください。

図 7-4. 立ち上がりおよび立ち下がり時間の測定基準

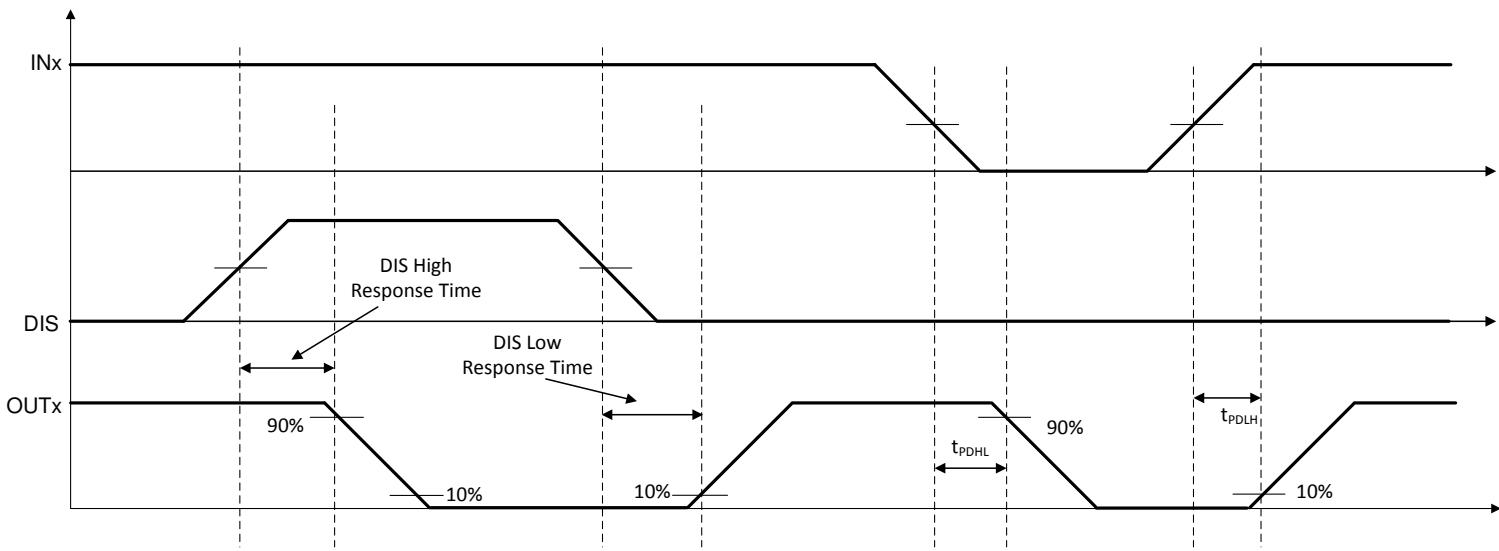

## 7.4 入力とディスエーブルの応答時間

図 7-5 に、ディスエーブル機能の応答時間を示します。詳細については [セクション 8.4.1](#) を参照してください。

図 7-5. ディスエーブル・ピンのタイミング

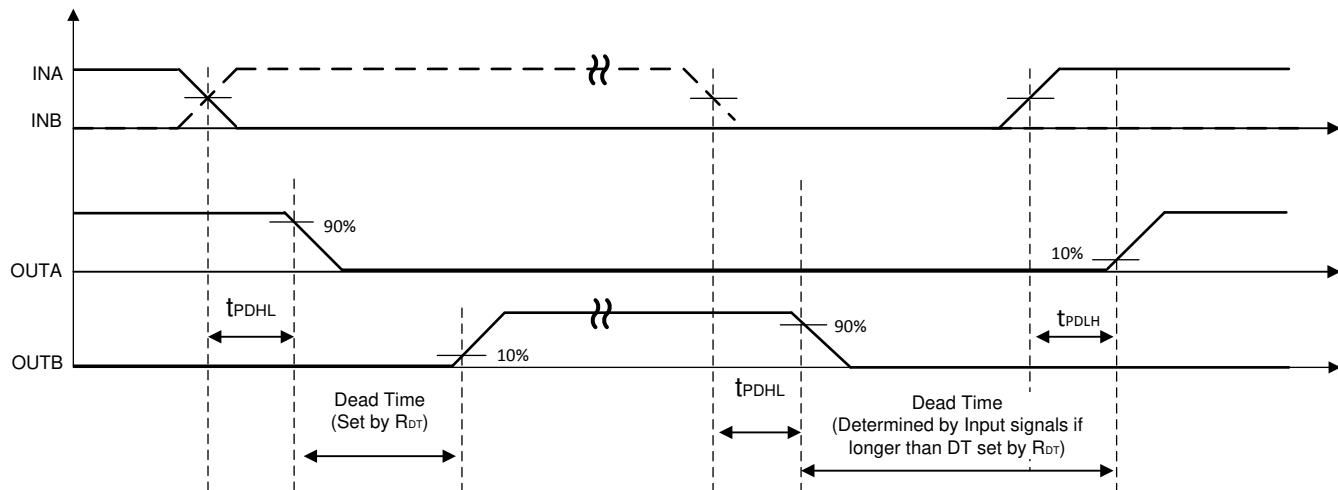

## 7.5 プログラム可能なデッドタイム

DT を VCCI に接続すると、DT 機能は無効になり、出力がオーバーラップできます。DT と GND の間に抵抗 ( $R_{DT}$ ) を配置することで、次の式に従ってデッドタイムを調整できます。 $DT (ns) = 10 \times R_{DT} (k\Omega)$ 。ノイズ耐性を向上させるため、DT ピンに近接して配置した 1nF 以下のセラミックコンデンサでこのピンをバイパスすることを推奨します。デッドタイムの詳細については、[セクション 8.4.2](#) を参照してください。

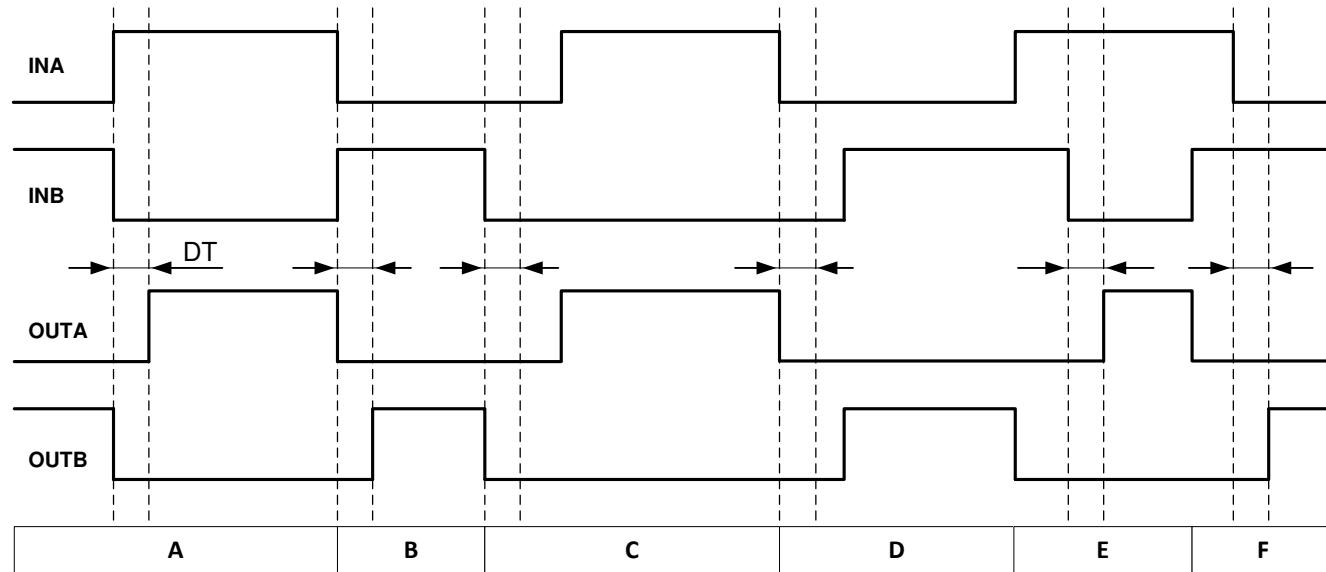

図 7-6. のデッドタイムのスイッチング パラメータ

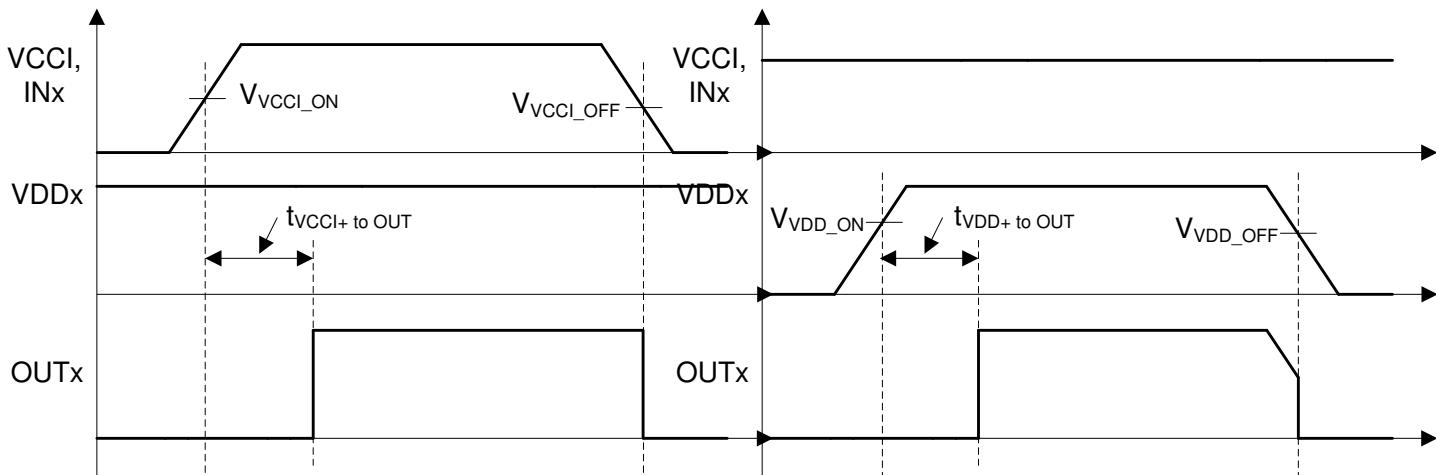

## 7.6 電源オン時の出力の UVLO 遅延

電源電圧  $V_{VCCI}$  が立ち下がりスレッショルド  $V_{VCCI\_OFF}$  未満から立ち上がりスレッショルド  $V_{VCCI\_ON}$  を越えて上昇するたびに、また電源電圧  $V_{VDDx}$  が立ち下がりスレッショルド  $V_{VDDx\_OFF}$  未満から立ち上がりスレッショルド  $V_{VDDx\_ON}$  を越えて上昇するたびに、出力が入力への応答を開始するまでに遅延が挿入されます。 $V_{VCCI}$  UVLO の場合、この遅延は  $t_{VCCI+ \text{ to } OUT}$  として定義され、最大値は  $50\mu\text{s}$  です。 $V_{VDDx}$  UVLO の場合、この遅延は  $t_{VDD+ \text{ to } OUT}$  として定義され、最大値は  $10\mu\text{s}$  です。ドライバの  $V_{VCCI}$  および  $V_{VDD}$  バイアス電源が完全に立ち上がるよう、入力信号を駆動する前にある程度のマージンを持たせることを推奨します。図 7-7 と図 7-8 に、 $V_{VCCI}$  と  $V_{VDD}$  の電源オン時の UVLO 遅延タイミング図を示します。

電源電圧  $V_{VCCI}$  が立ち下がりスレッショルド  $V_{VCCI\_OFF}$  より低下するたびに、また  $V_{VDDx}$  が立ち下がりスレッショルド  $V_{VDDx\_OFF}$  より低下するたびに、出力は入力への応答を停止し、 $2\mu\text{s}$  以内に Low に保持されます。この非対称な遅延は、 $V_{VCCI}$  または  $V_{VDDx}$  のブラウンアウト中でも安全な動作を確保するために設計されています。

$V_{VCCI}$  が喪失しても  $V_{VDDx}$  が存在する場合、出力は Low に保持されます。 $V_{VDDx}$  が喪失すると、アクティブ ブルダウン機能により出力は Low にクランプされます。UVLO 機能の詳細については、セクション 8.3.1 を参照してください。

図 7-7.  $V_{VCCI}$  電源オン時の UVLO 遅延

図 7-8.  $V_{VDDA/B}$  電源オン時の UVLO 遅延

## 7.7 CMTI テスト

図 7-9 は CMTI テスト構成の概略図です。

図 7-9. CMTI テスト構成の概略図

## 8 詳細説明

### 8.1 概要

パワー・トランジスタを高速で切り換えると共に、スイッチング電力損失を低減するため、制御デバイスの出力とパワー・トランジスタのゲートの間に大電流ゲート・ドライバがしばしば配置されます。パワー・トランジスタのゲートを駆動するのに十分な電流をコントローラが供給できないこともあります。これは、デジタル・コントローラの場合に特に当てはまります。デジタル・コントローラからの入力信号はしばしば数 mA しか供給できない 3.3V ロジック信号であるためです。

UCC21540-Q1 は、各種の電源およびモータ駆動トポロジに適合し、また各種のトランジスタを駆動するように構成できる柔軟なデュアル・ゲート・ドライバです。UCC21540-Q1 は、制御回路と簡単に組み合わせるための機能と、駆動するゲートを保護するための機能を豊富に備えています。たとえば、抵抗によりプログラム可能なデッド・タイム (DT) 制御、ディスエーブル・ピン、入力および出力電源の低電圧ロックアウト (UVLO) などです。また、入力がオープンのままである場合、または入力パルス幅が短すぎる場合、UCC21540-Q1 はその出力を LOW に保持します。デジタル電源コントローラともアナログ電源コントローラとも接続できるように、ドライバ入力は CMOS および TTL 互換です。各チャネルはそれぞれの入力ピン (INA, INB) で制御されるため、各出力は完全に独立して制御されます。

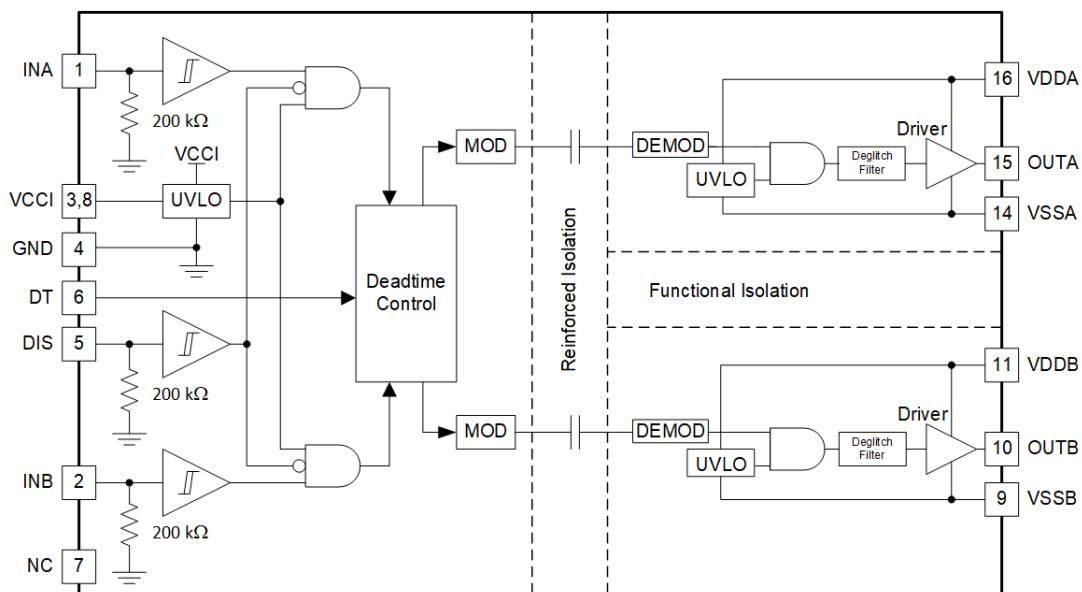

### 8.2 機能ブロック図

## 8.3 機能説明

### 8.3.1 VDD、VCCI、低電圧誤動作防止 (UVLO)

UCC21540-Q1 は、両方の出力の VDD ピンと VSS ピンの間の各電源電圧に対して低電圧誤動作防止 (UVLO) 保護機能を内蔵しています。VDD バイアス電圧がデバイスの起動時に  $V_{VDD\_ON}$  より低い場合、または起動後に  $V_{VDD\_OFF}$  を下回った場合、入力ピンの状態に関係なく、VDD UVLO 機能はチャネル出力を LOW に保持します。VDDx UVLO 機能はチャネル A とチャネル B で独立して動作するため、ハイサイド バイアスを充電する前にローサイドを出力する必要があるブートストラップ付きシステムを実現できます。

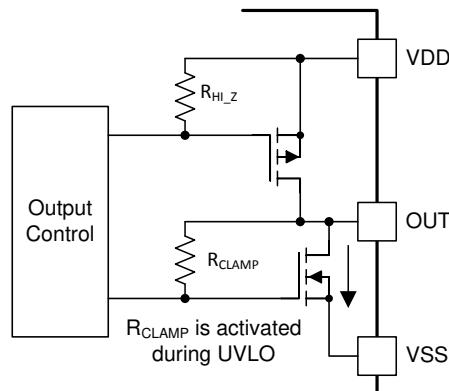

ドライバの出力段にバイアスが印加されていない場合、または UVLO 状態である場合、ドライバ出力の電圧上昇を制限するアクティブ クランプ回路によってドライバ出力は LOW に保持されます (図 8-1 を参照)。この条件では、下側の NMOS のゲートが  $R_{CLAMP}$  でドライバ出力に接続される一方で、上側の PMOS はオフに保持され、その抵抗は  $R_{Hi-Z}$  となります。この構成では、出力は下側の NMOS デバイスのスレッショルド電圧 (バイアス電力が利用可能かどうかにかかわらず約 1.6V (標準値)) に実質的にクランプされます。

図 8-1. アクティブ プルダウン機能の概略図

VDD UVLO 保護機能はヒステリシス ( $V_{VDD\_HYS}$ ) を備えています。このヒステリシスは、電源のグランド ノイズが発生したときのチャタリングを防止します。このヒステリシスにより、本デバイスはバイアス電圧の小さな電圧降下を許容することもできます。このような電圧降下は、デバイスがスイッチングを開始し動作消費電流が急増した際に発生します。

UCC21540-Q1 の入力は低電圧誤動作防止 (UVLO) 保護機能も内蔵しています。入力は、起動時に電源電圧 VCCI が  $V_{VCCI\_ON}$  を上回らないかぎり、出力に影響を与えることはできません。起動後に電源電圧 VCCI が  $V_{VCCI\_OFF}$  を下回った場合、出力は LOW に保持され、入力に応答できません。確実に安定して動作するように、VDD の UVLO と同様にヒステリシス ( $V_{VCCI\_HYS}$ ) が備わっています。

表 8-1. VCCI UVLO 機能の論理図 (1)

| 条件                                      | 入力  |     | 出力   |      |

|-----------------------------------------|-----|-----|------|------|

|                                         | INA | INB | OUTA | OUTB |

| デバイス起動中 $V_{VCCI\_GND} < V_{VCCI\_ON}$  | H   | L   | L    | L    |

| デバイス起動中 $V_{VCCI\_GND} < V_{VCCI\_ON}$  | L   | H   | L    | L    |

| デバイス起動中 $V_{VCCI\_GND} < V_{VCCI\_ON}$  | H   | H   | L    | L    |

| デバイス起動中 $V_{VCCI\_GND} < V_{VCCI\_ON}$  | L   | L   | L    | L    |

| デバイス起動後 $V_{VCCI\_GND} < V_{VCCI\_OFF}$ | H   | L   | L    | L    |

| デバイス起動後 $V_{VCCI\_GND} < V_{VCCI\_OFF}$ | L   | H   | L    | L    |

| デバイス起動後 $V_{VCCI\_GND} < V_{VCCI\_OFF}$ | H   | H   | L    | L    |

| デバイス起動後 $V_{VCCI\_GND} < V_{VCCI\_OFF}$ | L   | L   | L    | L    |

(1)  $VDDx > VDD\_ON$  とします。

表 8-2. VDDx UVLO 機能の論理図 (1)

| 条件                               | INA | INB | OUTA | OUTB |

|----------------------------------|-----|-----|------|------|

|                                  | 入力  |     | 出力   |      |

| デバイス起動中 $VDD-VSS < V_{VDD\_ON}$  | H   | L   | L    | L    |

| デバイス起動中 $VDD-VSS < V_{VDD\_ON}$  | L   | H   | L    | L    |

| デバイス起動中 $VDD-VSS < V_{VDD\_ON}$  | H   | H   | L    | L    |

| デバイス起動中 $VDD-VSS < V_{VDD\_ON}$  | L   | L   | L    | L    |

| デバイス起動後 $VDD-VSS < V_{VDD\_OFF}$ | H   | L   | L    | L    |

| デバイス起動後 $VDD-VSS < V_{VDD\_OFF}$ | L   | H   | L    | L    |

| デバイス起動後 $VDD-VSS < V_{VDD\_OFF}$ | H   | H   | L    | L    |

| デバイス起動後 $VDD-VSS < V_{VDD\_OFF}$ | L   | L   | L    | L    |

(1)  $VCCI > VCCI\_ON$  とします。

### 8.3.2 入力および出力論理表

表 8-3. 入力 / 出力論理表 (1) (2)

VCCI、VDDA、VDBB は給電されているものとします (UVLO の動作モードの詳細は [セクション 8.3.1](#) を参照してください)。表 8-3 に、INA、INB、DIS による動作と対応する出力状態を示します。

| 入力         |            | DIS | 出力   |      | 注                                                                      |

|------------|------------|-----|------|------|------------------------------------------------------------------------|

| INA        | INB        |     | OUTA | OUTB |                                                                        |

| L          | L          | L   | L    | L    |                                                                        |

| L          | H          | L   | L    | H    | デッド・タイム機能を使っている場合、デッド・タイムが経過した後に出力が遷移します。セクション 8.4.2 を参照してください。        |

| H          | L          | L   | H    | L    |                                                                        |

| H          | H          | L   | L    | L    | DT は $R_{DT}$ によって設定されます。                                              |

| H          | H          | L   | H    | H    | DT ピンを VCCI にプルアップします。                                                 |

| オープンのままにする | オープンのままにする | L   | L    | L    |                                                                        |

| X          | X          | H   | L    | L    | 離れた場所にあるマイコンに接続する場合、DIS ピンに近接して配置した 1nF 以上の低 ESR/ESL コンデンサを使ってバイパスします。 |

(1) 「X」とは、L、H、「オープンのままにする」のいずれかであることを意味します。

(2) これらのピンを使用しない場合、ノイズ耐性を向上させるため、INA、INB、DIS を GND に、DT を VCCI に接続することを推奨します。

### 8.3.3 入力段

UCC21540-Q1 の入力ピン (INA、INB、DIS) には、出力チャネルの VDD 電源電圧から完全に絶縁された TTL および CMOS 互換入力スレッショルドロジックを使っています。UCC21540-Q1 は、温度が変わってもほとんど変化しない 1.8V (標準値) の HIGH スレッショルド ( $V_{INAH}$ ) と 1V (標準値) の LOW スレッショルドを持っているため、入力ピンはロジック レベルの制御信号 (3.3V マイコンからの信号など) で簡単に駆動できます (とを参照)。0.8V という広いヒステリシス ( $V_{INA\_HYS}$ ) は良好なノイズ耐性と安定動作に役立ちます。いずれの入力をオープンのままにしても、内部プルダウン抵抗がピンを Low に強制します。これらの抵抗は、INA/B および DIS では  $200\text{k}\Omega$  (標準値) です ([セクション 8.2](#) を参照)。未使用的入力は、接地することを推奨します。

入力に印加されるすべての信号の振幅は、VCCI ピンの電圧を超えないようにする必要があります。UCC21540-Q1 は、VCCI 電圧よりも高い出力電圧を持つアナログ コントローラからは駆動できません。

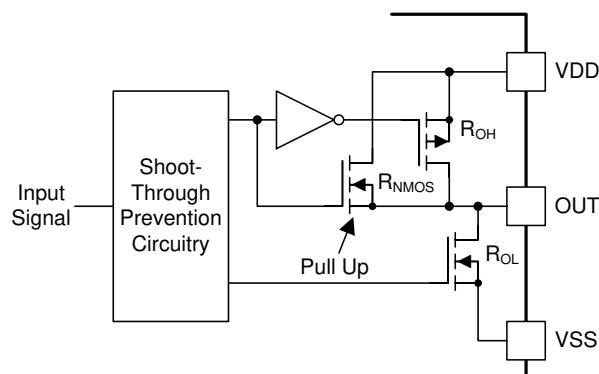

### 8.3.4 出力段

UCC21540-Q1 の出力段は、最も必要とされるとき、つまり、パワー スイッチのターンオン遷移のミラー プラトー領域の間 (パワー スイッチのドレインまたはコレクタ電圧に  $dV/dt$  が生じたとき) に最大のピーク ソース電流を供給できるプルアップ構造を採用しています。出力段のプルアップ構造は、並列接続した P チャネル MOSFET と追加のプルアップ N チャネル MOSFET を備えています。N チャネル MOSFET の役割は、ピーク ソース電流をブーストし、高速ターンオンを実現することです。出力の状態を Low から High に変更しようとする短い瞬間だけ、N チャネル MOSFET をターンオンする方法で、このような動作を実現します。

$R_{OH}$  パラメータは DC 測定値であり、P チャネル デバイスのみのオン抵抗を表します。これは、プルアップ N チャネル デバイスは DC 状態ではオフ状態に保たれ、出力が LOW から HIGH に変化する瞬間にのみターンオンするためです。このため、この短いターンオン段階の UCC21540-Q1 のプルアップ段の実効抵抗は、 $R_{OH}$  パラメータが表す値よりもはるかに小さい値です。

UCC21540-Q1 のプルダウン構造は N チャネル MOSFET で構成されています。 $R_{OL}$  パラメータ (これも DC 測定値です) は本デバイスのプルダウン状態のインピーダンスを表します。レール ツー レール動作では、出力電圧は VDD と VSS の間を変化します。

ゲート ドライバを確実に動作させるため、最小パルス幅に特に注意を払います。電気的特性表に示す最小パルス幅は、無負荷のドライバにおいて出力まで到達する最小入力パルスを表します。これは、ドライバ IC に内蔵されたグリッチ除去フィルタによって決定されます。出力状態の変化を保証し、貫通電流を防止するには、仕様の最大値よりも長い入力オン / オフ パルス幅が必要です。ドライバの負荷が重い場合、システムを確実に動作させるために特別の注意を払う必要があります。ゲート スイッチング中、ドライバが各遷移を完了する前に出力状態が変化すると、非ゼロ電流スイッチング イベントが発生します。レイアウトによって生じる寄生素子と相まって、非ゼロ電流スイッチングは内部レールのオーバーシュートとゲート ドライバの EOS 損傷の原因となる可能性があります。したがって、信頼性の高いシステム動作のために、最小出力パルス幅が求められます。この最小出力パルス幅は、ゲート容量、VDD 電源電圧、ゲート抵抗、PCB レイアウト起因の寄生素子など、複数の要因に依存します。確実に動作させるために必要な最小パルス幅は、電気的特性表に示されている最小パルス幅よりも大きい場合があります。各システムに必要な最小出力パルス幅を決定するには、システムレベルの検討を行う必要があります。

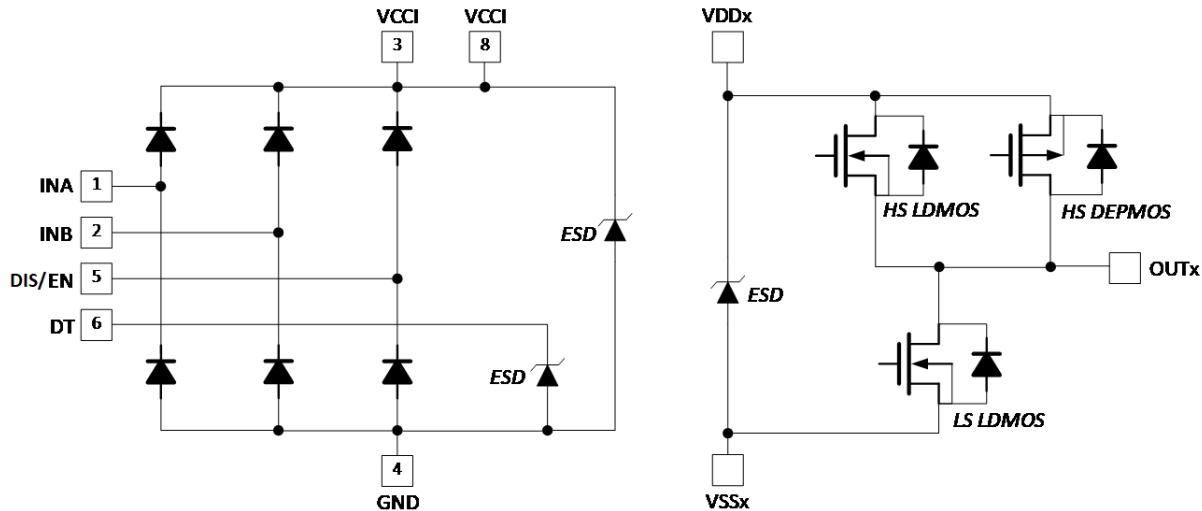

図 8-2. 出力段

### 8.3.5 UCC21540-Q1 のダイオード構造

図 8-3 に、ESD 保護素子に関する複数のダイオードを示します。これは、本デバイスの絶対最大定格を図で表したものです。

図 8-3. ESD 構造

## 8.4 デバイスの機能モード

### 8.4.1 ディセーブル ピン

DIS ピンを HIGH に設定すると、両方の出力は同時に遮断されます。DIS ピンを LOW に設定すると、UCC21540-Q1 は通常動作します。離れた場所にあるマイコンに接続する場合、DIS ピンに近接して配置した約 1nF の低 ESR/ESL コンデンサを使ってバイパスします。DIS 回路のロジック構造は、INA または INB と似ています。DIS ピンは、VCCI が UVLO スレッショルドを上回っている場合にのみ機能し (また必要とされ) ます。DIS ピンを使用しない場合、ノイズ耐性を向上させるために GND に接続することを推奨します。

### 8.4.2 プログラマブル・ デッド・ タイム (DT) ピン

UCC21540-Q1 を使うと、以下の方法でデッド・ タイム (DT) を調整できます。

#### 8.4.2.1 DT ピンを VCCI に接続

出力は入力と完全に一致し、最小デッド・ タイムはアサートされません。その結果、出力はオーバーラップできます。DT ピンを使用しない場合、ノイズ耐性を向上させるために直接 VCCI に接続することを推奨します。

#### 8.4.2.2 DT ピンと GND ピンの間に設定抵抗を接続

DT ピンと GND の間に抵抗  $R_{DT}$  を配置することで、 $t_{DT}$  を設定します。ノイズ耐性を向上させるため、DT ピンに近接して配置した 1nF 以下のセラミック コンデンサでこのピンをバイパスすることを推奨します。適切な  $R_{DT}$  値は以下のように求められます。

$$t_{DT} \approx 10 \times R_{DT} \quad (1)$$

ここで、

- $t_{DT}$  は設定されるデッド タイム (ns) です。

- $R_{DT}$  は DT ピンと GND の間の抵抗の値 ( $k\Omega$ ) です。

$R_{DT}$  はこのピンに小さな電流を設定し、それによってデッド タイムが設定されます。 $R_{DT}$  の値が増加するにつれて、DT ピンから流れ出す電流は減少します。 $R_{DT} = 100k\Omega$  の場合、DT ピンの電流は  $10\mu A$  未満です。より大きい  $R_{DT}$  値を使う場合、ノイズ耐性を高めかつ両チャネル間のデッド タイム マッチングを向上させるため、DT ピンにできるだけ近づけて  $R_{DT}$  とセラミック コンデンサ (1nF 以下) を配置することを推奨します。

片方の入力信号の立ち下がりエッジにより、他方の信号の設定済みデッド タイムが開始されます。設定済みデッド タイムとは、ドライバが両方の出力を強制的に LOW に保持する最小期間です。設定された最小値よりも長いデッド タイムが INA および INB 信号に含まれる場合、出力は設定済みデッド タイムよりも長い間 LOW に

保持されることがあります。両方の入力が同時に High になった場合、両方の出力は即座に Low に設定されます。この機能は、ハーフブリッジ アプリケーションでの貫通電流を防止するために使用され、通常動作時は設定済みデッド タイムの影響を受けません。ドライバのデッド タイム ロジックのさまざまな動作条件を以下に示し、説明します。

図 8-4. 入力信号と入出力ロジックの関係

**条件 A** : INB が Low、INA が High に遷移します。INB は即座に OUTB を LOW に設定し、設定済みデッド タイムが OUTA に割り当てられます。設定済みデッド タイムの後、OUTA は HIGH に遷移できます。

**条件 B** : INB が High、INA が Low に遷移します。今度は INA は即座に OUTA を LOW に設定し、設定済みデッド タイムが OUTB に割り当てられます。設定済みデッド タイムの後、OUTB は HIGH に遷移できます。

**条件 C** : INB が Low になりますが、INA はまだ Low のままで。INB は即座に OUTB を LOW に設定し、設定済みデッド タイムが OUTA に割り当てられます。この例では、入力信号のデッド タイムは設定済みデッド タイムよりも長くなっています。入力信号のデッド タイムが経過した後、INA が HIGH に遷移すると、OUTA は即座に HIGH に設定されます。

**条件 D** : INA が Low になりますが、INB はまだ Low のままで。INA は即座に OUTA を LOW に設定し、設定済みデッド タイムが OUTB に割り当てられます。この例では、入力信号のデッド タイムは設定済みデッド タイムよりも長くなっています。入力信号のデッド タイムが経過した後、INB が HIGH に遷移すると、OUTB は即座に HIGH に設定されます。

**条件 E** : INB と OUTB がまだ High のうちに、INA が High に遷移します。オーバーシュートを防止するため、OUTB は即座に LOW に駆動されます。その後 OUTB は LOW に遷移し、設定済みデッド タイムが OUTA に割り当てられます。OUTB はすでに Low になっているため、設定済みデッド タイムの後、OUTA は HIGH に遷移できます。

**条件 F** : INA と OUTA がまだ High のうちに、INB が High に遷移します。オーバーシュートを防止するため、OUTA は即座に LOW に駆動されます。その後 OUTA は LOW に遷移し、設定済みデッド タイムが OUTB に割り当てられます。OUTA はすでに Low になっているため、設定済みデッド タイムの後、OUTB は HIGH に遷移できます。

## 9 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 9.1 アプリケーション情報

UCC21540-Q1 は絶縁機能とバッファ駆動機能を効果的に統合しています。柔軟かつ汎用的 (最大 5.5V の VCCI と 18V の VDDA/VDBB) な UCC21540-Q1 は、MOSFET、IGBT、GaN トランジスタ用のローサイド、ハイサイド、ハイサイド / ローサイド、ハーフブリッジ・ドライバとして使えます。各種部品を統合し、先進の保護機能 (UVLO、デッド・タイム、ディスエーブル) と最適化されたスイッチング性能を備えた UCC21540-Q1 を使うと、エンタープライズ、テレコム、車載、産業アプリケーション向けにより小型かつ堅牢な設計を短期間で開発できます。

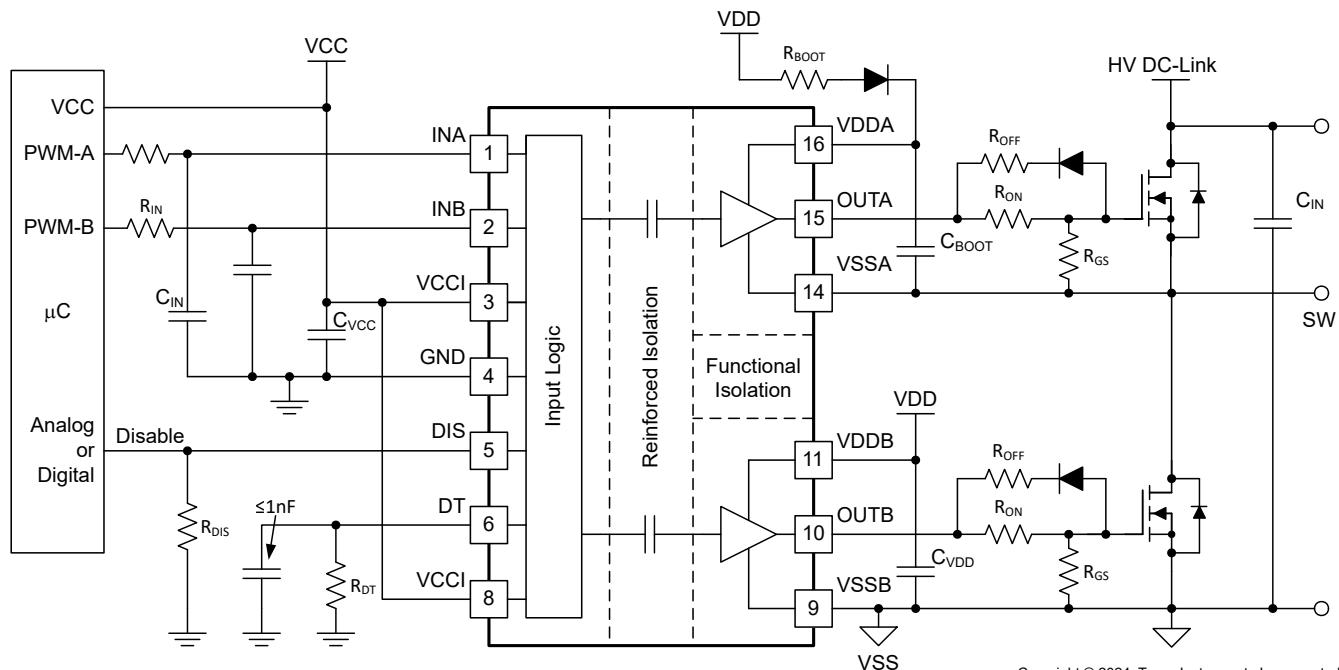

### 9.2 代表的なアプリケーション

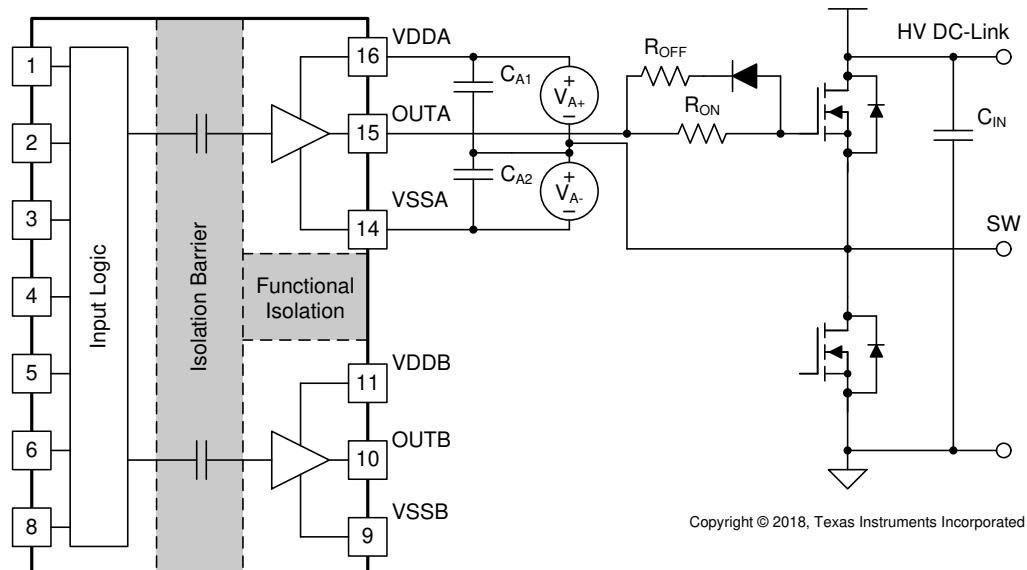

図 9-1 の回路に、UCC21540-Q1 を使って代表的なハーフ ブリッジ構成を駆動するリファレンス デザインを示します。この構成は、同期整流式降圧、同期整流式昇圧、ハーフ ブリッジ / フル ブリッジ絶縁型トポロジ、3 相モータ駆動アプリケーションなどの一般的な各種パワー コンバータ トポロジで使えます。

図 9-1. 代表的なアプリケーション回路図

### 9.2.1 設計要件

表 9-1 に、「ハイサイド - ローサイド構成の 650V MOSFET を駆動する UCC21540-Q1」のリファレンス デザイン パラメータを示します。

表 9-1. UCC21540-Q1 の設計要件

| パラメータ               | 値                                                        | 単位  |

|---------------------|----------------------------------------------------------|-----|

| パワートランジスタ           | 650V、12V の $V_{GS}$ で $150\text{m}\Omega$ の $R_{DS\_ON}$ | —   |

| VCC                 | 5.0                                                      | V   |

| VDD                 | 12                                                       | V   |

| 入力信号振幅              | 3.3                                                      | V   |

| スイッチング周波数 ( $f_s$ ) | 100                                                      | kHz |

| デッドタイム              | 200                                                      | ns  |

| DC リンク電圧            | 400                                                      | V   |

### 9.2.2 詳細な設計手順

#### 9.2.2.1 INA/INB 入力フィルタの設計

出力の信号を低速にする（または遅延させる）目的でゲート・ドライバへの信号を成形することは推奨しません。しかし、理想的でないレイアウトまたは長い PCB 配線によって生じるリンギングを除去するために小さな入力  $R_{IN-CIN}$  フィルタを使用することはできます。

このようなフィルタでは、 $0 \sim 100\Omega$  の  $R_{IN}$  と  $10 \sim 100\text{pF}$  の  $C_{IN}$  を使用する必要があります。この例では、 $R_{IN} = 51\Omega$  と  $C_{IN} = 33\text{pF}$  が選択されており、コーナー周波数は約 100MHz です。

これらの部品を選択する際は、ノイズ耐性と伝搬遅延のトレードオフに注意します。

#### 9.2.2.2 デッドタイム抵抗およびコンデンサの選択

式 1 から、デッドタイムを 200ns に設定するには  $20\text{k}\Omega$  の抵抗を選択します。ノイズ耐性を向上させるため、DT ピンに近接して  $1\text{nF}$  以下のコンデンサを並列に配置します。

#### 9.2.2.3 外部ブートストラップダイオードとその直列抵抗の選択

ブートストラップコンデンサは、ローサイドトランジスタがターンオンするごとに、外付けブートストラップダイオードを通して VDD で充電されます。コンデンサの充電には大きなピーク電流を伴うため、ブートストラップダイオード内の過渡的な消費電力が大きくなる場合があります。導通損失は、ダイオードの順方向電圧降下にも影響されます。ダイオードの導通損失と逆方向回復損失の両方が、ゲートドライバ回路の総合損失に影響を与えます。

外付けブートストラップダイオードを選択する場合、逆方向回復とそれに関連するグランドノイズバウンスによる損失を最小限に抑えるため、順方向電圧降下が小さくかつ接合部容量が小さい高耐圧の高速回復ダイオードまたは SiC ショットキーダイオードを選択することを推奨します。この例では、DC リンク電圧は  $400\text{V}_{DC}$  です。ブートストラップダイオードの定格電圧は、十分なマージンを持って DC リンク電圧よりも高くする必要があります。そのため、この例では  $600\text{V}$  超高速ダイオード MRA160T3G を選択しています。

ブートストラップ抵抗  $R_{BOOT}$  は、各スイッチングサイクル中、特に VSSA (SW) ピンに過剰な負の過渡電圧が印加された場合に、 $D_{BOOT}$  の突入電流を低減し VDDA-VSSA の電圧の上昇スルーレートを制限するために使います。 $R_{BOOT}$  の推奨値は、使用するダイオードの種類に応じて  $1\Omega \sim 20\Omega$  です。この例では、ブートストラップダイオードの突入電流を制限するため、 $2.7\Omega$  の電流制限抵抗を選択しています。最も厳しい条件での  $D_{Boot}$  のピーク電流の推定値は以下の式で表されます。

$$I_{DBoot(pk)} = \frac{V_{DD} - V_{BDF}}{R_{Boot}} = \frac{12V - 1.5V}{2.7\Omega} \approx 4A \quad (2)$$

ここで、

- $V_{BDF}$  は、約 4A の電流が流れたときのブートストラップダイオードの順方向電圧降下の推定値です。

VDDx と VSSx の間に印加する電圧が FET と UCC21540-Q1 の絶対最大定格を下回るように制限しないと、デバイスに永続的な損傷が生じる可能性もあります。

#### 9.2.2.4 ゲート・ドライバの出力抵抗

外部ゲート・ドライバ抵抗  $R_{ON}/R_{OFF}$  は以下の目的に使われます。

- 寄生インダクタンス / 容量に起因するリングングの制限

- 高電圧 / 電流スイッチングの  $dv/dt$ 、 $di/dt$ 、ボディ・ダイオードの逆方向回復に起因するリングングの制限

- ゲート駆動強度 (すなわちピーク・シンクおよびソース電流) の微調整によるスイッチング損失の最適化

- 電磁干渉 (EMI) の低減

セクション 8.3.4 で述べたように、UCC21540-Q1 は P チャネル MOSFET と追加のフルアップ N チャネル MOSFET を並列にしたフルアップ構造を備えています。これらを合わせたピーク・ソース電流は 4A です。その結果、ピーク・ソース電流は以下の式で予測できます。

$$I_{OA+} = \min \left( 4A, \frac{V_{DD} - V_{BDF}}{R_{NMOS} \parallel R_{OH} + R_{ON} + R_{GFET\_Int}} \right) \quad (3)$$

$$I_{OB+} = \min \left( 4A, \frac{V_{DD}}{R_{NMOS} \parallel R_{OH} + R_{ON} + R_{GFET\_Int}} \right) \quad (4)$$

ここで

- $R_{ON}$  : 外部ターンオン抵抗。

- $R_{GFET\_INT}$  : パワー・トランジスタの内部ゲート抵抗 (パワー・トランジスタのデータシートを参照)

- $I_{O+}$  = ピーク・ソース電流 – 4A (ゲート・ドライバ・ピーク・ソース電流) とゲート駆動ループ抵抗に基づく計算値のうちの小さい方の値

この例では以下の式で計算されます。

$$I_{OA+} = \frac{V_{DD} - V_{BDF}}{R_{NMOS} \parallel R_{OH} + R_{ON} + R_{GFET\_Int}} = \frac{12V - 0.8V}{1.47\Omega \parallel 5\Omega + 2.2\Omega + 1.5\Omega} \approx 2.3A \quad (5)$$

$$I_{OB+} = \frac{V_{DD}}{R_{NMOS} \parallel R_{OH} + R_{ON} + R_{GFET\_Int}} = \frac{12V}{1.47\Omega \parallel 5\Omega + 2.2\Omega + 1.5\Omega} \approx 2.5A \quad (6)$$

その結果、ハイサイドとローサイドのピーク・ソース電流はそれぞれ 2.3A と 2.5A となります。同様に、ピーク・シンク電流は以下の式で計算されます。

$$I_{OA-} = \min \left( 6A, \frac{V_{DD} - V_{BDF} - V_{GDF}}{R_{OL} + R_{OFF} \parallel R_{ON} + R_{GFET\_Int}} \right) \quad (7)$$

$$I_{OB-} = \min \left( 6A, \frac{V_{DD} - V_{GDF}}{R_{OL} + R_{OFF} \parallel R_{ON} + R_{GFET\_Int}} \right) \quad (8)$$

ここで

- $R_{OFF}$  : 外部ターンオフ抵抗 (この例では  $R_{OFF} = 0$ )

- $V_{GDF}$  :  $R_{OFF}$  と直列に接続された逆並列ダイオードの順方向電圧降下。この例のダイオードは MSS1P4 です。

- $I_{O-}$  : ピーク・シンク電流 – 6A (ゲート・ドライバのピーク・シンク電流) とゲート駆動ループ抵抗に基づく計算値のうちの小さい方の値

この例では以下の式で計算されます。

$$I_{OA-} = \frac{V_{DD} - V_{BDF} - V_{GDF}}{R_{OL} + R_{OFF} \parallel R_{ON} + R_{GFET\_Int}} = \frac{12V - 0.8V - 0.85V}{0.55\Omega + 0\Omega + 1.5\Omega} \approx 5.0A \quad (9)$$

$$I_{OB-} = \frac{V_{DD} - V_{GDF}}{R_{OL} + R_{OFF} \parallel R_{ON} + R_{GFET\_Int}} = \frac{12V - 0.85V}{0.55\Omega + 0\Omega + 1.5\Omega} \approx 5.4A \quad (10)$$

その結果、ハイサイドとローサイドのピーク・シンク電流はそれぞれ 5.0A と 5.4A となります。

推定ピーク電流は PCB レイアウトと負荷容量によっても影響されることに注意します。ゲート・ドライバのループの寄生インダクタンスは、ピーク・ゲート駆動電流を遅れさせ、オーバーシュートとアンダーシュートを発生させる可能性があります。そのため、ゲート・ドライバのループができるだけ小さくすることを強く推奨します。一方、パワー・トランジスタの負荷容量 ( $C_{ISS}$ ) が非常に小さい (通常 1nF 未満) 場合、ピーク・ソース / シンク電流はループ寄生素子に支配されます。なぜなら、立ち上がりおよび立ち下がり時間が非常に小さく、寄生リングの周期に近いためです。

OUTx 電圧がデータシートの絶対最大定格を (過渡を含めて) 下回るよう下回るよう制御しないと、デバイスに永続的な損傷が生じる可能性もあります。ゲートの過剰なリングを低減するため、FET のゲートの近くにフェライト・ビーズを使用することを推奨します。オーバーシュート / アンダーシュートが大きい場合、OUTx 電圧を VDDx および VSSx 電圧にクランプするために外部クランプ・ダイオードを追加することもできます。

### 9.2.2.5 ゲート - ソース間抵抗の選択

ゲート・ドライバ出力に電力が供給されておらず不定状態にある場合、ゲート - ソース間抵抗 RGS を使ってゲートをソース電圧にプルダウンすることを推奨します。この抵抗は、ゲート・ドライバがターンオンして LOW を駆動できるようになる前にミラー電流によって  $dv/dt$  起因でターンオンするリスクの低減にも役立ちます。この抵抗は、パワー・デバイスの  $V_{th}$  と CGD/CGS 比に応じて、通常  $5.1k\Omega \sim 20k\Omega$  の値に設定されます。

### 9.2.2.6 ゲート・ドライバの電力損失の推定

ゲート・ドライバ・サブシステムの総合損失  $P_G$  には、UCC21540-Q1 の電力損失 ( $P_{GD}$ ) と、外部ゲート駆動抵抗などの周辺回路の電力損失が含まれます。ブーストストラップ・ダイオードの損失は  $P_G$  に含まれず、このセクションでは触れません。

$P_{GD}$  は、UCC21540-Q1 の熱的安定性に関連する制限値を決定する主要な電力損失であり、複数の要素の損失を計算することにより推定できます。

第 1 の要素は静的電力損失  $P_{GDQ}$  です。 $P_{GDQ}$  にはドライバの静止電力損失と、特定のスイッチング周波数で動作しているドライバの自己消費電力が含まれます。 $P_{GDQ}$  は、与えられた VCCI、VDDA/VDBB、スイッチング周波数、周囲温度において、OUTA と OUTB に負荷が接続されていない状態でベンチ測定されます。とに、無負荷時の動作消費電流と動作周波数との関係を示します。この例では、 $V_{VCCI} = 5V$ 、 $V_{VDD} = 12V$  です。INA/INB を 0V から 3.3V まで 100kHz でスイッチングした場合の各電源の電流は、 $I_{VCCI} \approx 2.5mA$ 、 $I_{VDDA} = I_{VDBB} \approx 1.5mA$  と測定されます。その結果、 $P_{GDQ}$  は以下の式で計算できます。

$$P_{GDQ} = V_{VCCI} \times I_{VCCI} + V_{VDDA} \times I_{DDA} + V_{VDBB} \times I_{DDB} = 50mW \quad (11)$$

第 2 の要素はスイッチング動作損失  $P_{GDO}$  であり、所定の負荷容量によりドライバは各スイッチング・サイクル中に負荷を充放電します。負荷スイッチングによる総合動的損失  $P_{GSW}$  は以下の式で推定できます。

$$P_{GSW} = 2 \times V_{DD} \times Q_G \times f_{SW} \quad (12)$$

ここで

- $Q_G$  はパワー・トランジスタのゲート電荷です。

ターンオン / ターンオフするために分割レールを使う場合、VDD は正レールと負レールの差に等しくなります。

そのためこのアプリケーション例の場合、以下の式で表されます。

$$P_{GSW} = 2 \times 12V \times 100nC \times 100kHz = 240mW \quad (13)$$

$Q_G$  は、データシートで規定された 14A で 480V をスイッチングするパワー・トランジスタの総ゲート電荷量を表します。テスト条件が変わるとこの値も変わる可能性があります。UCC21540-Q1 の出力段のゲート・ドライバ損失 ( $P_{GDO}$ ) は  $P_{GSW}$  の一部です。外部ゲート・ドライバ抵抗がゼロの場合、 $P_{GDO}$  は  $P_{GSW}$  と等しくなり、すべてのゲート・ドライバ損失は UCC21540-Q1 の内部で消費されます。外部ターンオンおよびターンオフ抵抗が存在する場合、総合損失はゲート・ドライバのプルアップ / ダウン抵抗と外部ゲート抵抗との間で分配されます。ソース / シンク電流が 4A/6A に飽和していない場合、プルアップ / ダウン抵抗は線形かつ固定ですが、ソース / シンク電流が飽和している場合、プルアップ / ダウン抵抗は非線形であることに注意します。そのため、これらの 2 つの条件によって  $P_{GDO}$  は異なります。

ケース 1 - 線形のプルアップ / ダウン抵抗 :

$$P_{GDO} = \frac{P_{GSW}}{2} \times \left( \frac{R_{OH} \parallel R_{NMOS}}{R_{OH} \parallel R_{NMOS} + R_{ON} + R_{GFET\_Int}} + \frac{R_{OL}}{R_{OL} + R_{OFF} \parallel R_{ON} + R_{GFET\_Int}} \right) \quad (14)$$

この設計例では、想定されるすべてのソース / シンク電流は 4A/6A 未満であるため、UCC21540-Q1 のゲート・ドライバ損失は以下の式で推定できます。

$$P_{GDO} = \frac{240mW}{2} \times \left( \frac{5\Omega \parallel 1.47\Omega}{5\Omega \parallel 1.47\Omega + 2.2\Omega + 1.5\Omega} + \frac{0.55\Omega}{0.55\Omega + 0\Omega + 1.5\Omega} \right) \approx 60mW \quad (15)$$

ケース 2 - 非線形のプルアップ / ダウン抵抗 :

$$P_{GDO} = 2 \times f_{SW} \times \left[ 4A \times \int_0^{T_{R\_Sys}} (V_{DD} - V_{OUTA/B}(t)) dt + 6A \times \int_0^{T_{F\_Sys}} V_{OUTA/B}(t) dt \right] \quad (16)$$

ここで

- $V_{OUTA/B}(t)$  は、ターンオンおよびオフ過渡時のゲート・ドライバ (OUTA、OUTB) のピン電圧であり、定電流源 (ターンオン時に 4A、ターンオフ時に 6A) が負荷コンデンサを充電 / 放電するものとして簡略化できます。その結果、 $V_{OUTA/B}(t)$  波形は線形となり、 $T_{R\_Sys}$  と  $T_{F\_Sys}$  は簡単に予測できます。

一部の条件で、プルアップ回路とプルダウン回路のどちらかのみが飽和し、他方が飽和していない場合、 $P_{GDO}$  はケース 1 とケース 2 の組み合わせとなり、上記の説明に基づいて、プルアップとプルダウンに対して式を簡単に特定できます。その結果、ゲート・ドライバ UCC21540-Q1 で消費される総合ゲート・ドライバ損失  $P_{GD}$  は以下で表されます。

$$P_{GD} = P_{GDQ} + P_{GDO} \quad (17)$$

これは、本設計例では 127mW に相当します。

### 9.2.2.7 接合部温度の推定

UCC21540UCC21540-Q1 の接合部温度は以下の式で推定できます。

$$T_J = T_C + \Psi_{JT} \times P_{GD} \quad (18)$$

ここで

- $T_J$  は接合部温度です。

- $T_C$  は、熱電対またはその他の手段で測定された UCC21540-Q1 のケース上面温度です。

- $\Psi_{JT}$  は、セクション 6.4 の表に記載されている接合部から上面への熱特性パラメータです。

接合部から上面への熱抵抗の代わりに接合部から上面への熱特性パラメータ ( $\Psi_{JT}$ ) を使用することで、接合部温度の推定の精度を大幅に向上させることができます。ほとんどの IC の熱エネルギーの大半は、パッケージのリードを経由して PCB に放散されるのに対して、全エネルギーのごく一部のみがケース上面から放散されます(通常は熱電対で測定されます)。 $R_{\Theta JC}$  は、熱エネルギーの大部分がケースを通して放散される場合(例: 金属パッケージが使われている場合、IC パッケージにヒートシンクが取り付けられている場合)にのみ有効に使用できます。それ以外の場合に  $R_{\Theta JC}$  を使っても、真の接合部温度を正確に推定することはできません。 $\Psi_{JT}$  は、IC の上面を通して放散されるエネルギー量が、テスト環境とアプリケーション環境で同等であると仮定することで実験的に求められます。推奨レイアウト・ガイドラインが守られている限り、接合部温度は数°C以内の精度で推定できます。詳細については、セクション 11.1 と『半導体および IC パッケージの熱評価基準』アプリケーション・レポートを参照してください。

### 9.2.2.8 VCCI、VDDA/B コンデンサの選択

VCCI、VDDA、VDBB のバイパス・コンデンサは、信頼性を高めるために不可欠です。満足できる電圧定格、温度係数、静電容量公差の表面実装型の低 ESR/ESL 多層セラミック・コンデンサ (MLCC) を推奨します。MLCC の DC バイアスは実際の容量値に影響を与えることに注意します。たとえば、25V、1μF X7R のコンデンサは、15V<sub>DC</sub> の DC バイアスを印加した場合、わずか 500nF として測定されます。

#### 9.2.2.8.1 VCCI コンデンサの選択

VCCI に接続されたバイパス・コンデンサは、1 次側ロジックに必要な過渡電流と総消費電流に対応しますが、これはわずか数 mA です。したがって、この用途には 100nF 以上の 25V MLCC を推奨します。バイアス電源出力が VCCI ピンから比較的離れた場所にある場合、1μF 以上の値のタンタルまたは電解コンデンサを MLCC と並列に配置する必要があります。

#### 9.2.2.8.2 VDDA (ブートストラップ) コンデンサの選択

ブートストラップ電源構成の VDDA コンデンサ(ブートストラップ・コンデンサとも呼びます)によって、最大 4A のゲート駆動過渡電流、ピーク・ソース電流、パワー・トランジスタの安定したゲート駆動電圧を実現しています。

スイッチング・サイクルごとに必要な総電荷量は以下の式で推定できます。

$$Q_{Total} = Q_G + \frac{I_{VDD} @ 100kHz (No Load)}{f_{SW}} = 100nC + \frac{1.5mA}{100kHz} = 115nC \quad (19)$$

ここで

- $Q_{Total}$  : 必要な総電荷量

- $Q_G$  : パワー・トランジスタのゲート電荷量

- $I_{VDD}$  : チャネルの自己消費電流(無負荷、100kHz 時)

- $f_{SW}$  : ゲート・ドライバのスイッチング周波数

したがって、 $C_{Boot}$  の最小値の絶対条件は次のとおりです。

$$C_{Boot} = \frac{Q_{Total}}{\Delta V_{VDDA}} = \frac{115nC}{0.5V} = 230nF \quad (20)$$

ここで

- $\Delta V_{VDDA}$  は VDDA での電圧リップルであり、この例では 0.5V です。

実際には、 $C_{Boot}$  の値は計算値よりも大きくなります。そうすることで、DC バイアス電圧によって生じる静電容量の変化と、あるいは負荷過渡によって電力段がパルスをスキップする状況を許容できます。したがって、 $C_{Boot}$  の値にマージンを含め、 $C_{Boot}$  を VDD ピンと VSS ピンのできるだけ近くに配置することを推奨します。この例では、50V、1 $\mu$ F のコンデンサを選択しています。

$$C_{Boot}=1\mu F \quad (21)$$

ブートストラップ・コンデンサを選択する際は、VDD と VSS の間の電圧がセクション 6.3 に示した推奨最小動作レベルを下回らないように注意する必要があります。ブートストラップ・コンデンサの値は、パワー・デバイスをスイッチングするための初期の電荷を供給した後、ハイサイドのオン時間が継続する間ゲート・ドライバの静止電流を継続的に供給できるように設定する必要があります。

ハイサイド電源電圧が UVLO 立ち下がりスレッショルドを下回ると、ハイサイド・ゲート・ドライバ出力はターンオフし、パワー・デバイスをオフに切り替えます。パワー・デバイスを制御せずにハード・スイッチングを行うと、ドライバ出力に高  $di/dt$  および高  $dv/dt$  過渡が発生し、デバイスに永続的な損傷が生じる可能性があります。

広い周波数範囲にわたって AC インピーダンスをさらに低減するため、低 ESL/ESR のバイパス・コンデンサを VDDx - VSSx ピンのごく近くに配置することを推奨します。この例では、過渡性能を最適化するため、100nF の X7R セラミック・コンデンサを  $C_{Boot}$  と並列に配置しています。

### 注

大きすぎる  $C_{BOOT}$  は不適切です。 $C_{BOOT}$  が最初の数サイクルでは充電されず、 $V_{BOOT}$  が UVLO を下回ったままになる可能性があります。その場合、ハイサイド FET は入力信号コマンドに従いません。また、初期の  $C_{BOOT}$  充電サイクル中、ブートストラップ・ダイオードに大きな逆方向回復電流および損失が生じます。

#### 9.2.2.8.3 VDDB コンデンサの選択

チャネル B の電流要件はチャネル A と同じであるため、VDDB コンデンサ (図 9-1 の  $C_{VDD}$ ) が必要です。ブートストラップ構成を使ったこの例では、VDDB コンデンサはブートストラップ・ダイオードを通して VDDA にも電流を供給します。10 $\mu$ F (50V) の MLCC と 220nF (50V) の MLCC を  $C_{VDD}$  として選択しています。バイアス電源出力が VDDB ピンから比較的離れた場所にある場合、10 $\mu$ F を超える値のタンタルまたは電解コンデンサを  $C_{VDD}$  と並列に接続する必要があります。

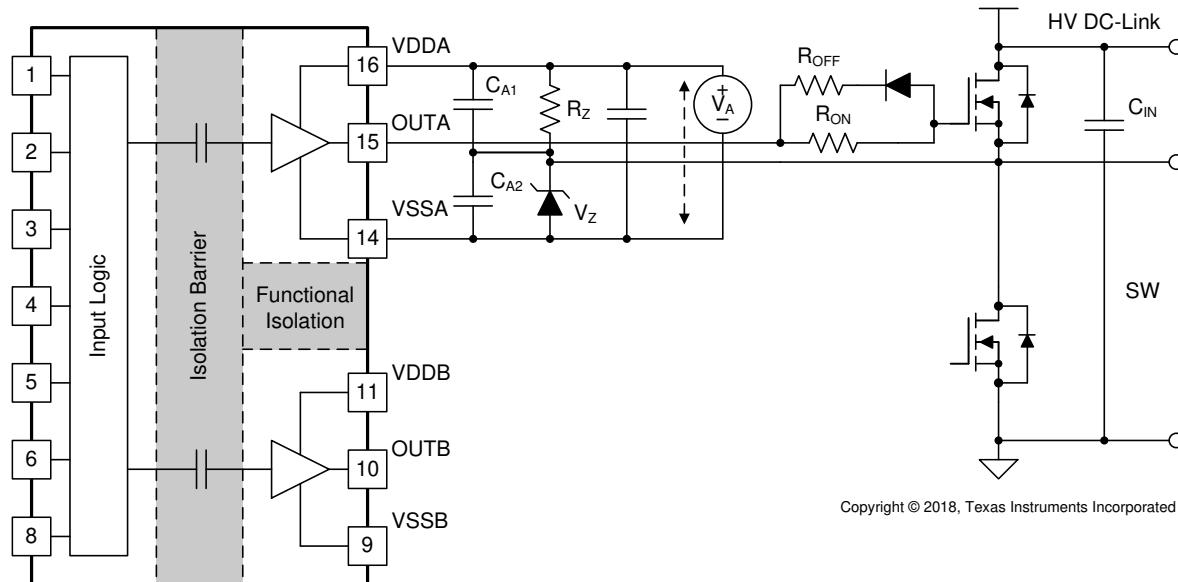

#### 9.2.2.9 出力段の負バイアスを使う応用回路

理想的でない PCB レイアウトと長いパッケージ・リード (TO-220 および TO-247 タイプのパッケージなど) によって寄生インダクタンスが付くと、高  $di/dt$  および  $dv/dt$  スイッチング中、パワー・トランジスタのゲート - ソース間駆動電圧にリンギングが生じる可能性があります。リンギングがスレッショルド電圧を上回る場合、予期しないターンオンのリスクがあり、貫通電流のリスクさえあります。ゲート駆動に負のバイアスを印加することは、このようなリンギングをスレッショルドよりも低く保つための一般的な方法です。負のゲート駆動バイアスの実装方法の例をいくつか以下に示します。

図 9-2 に第 1 の例を示します。この例では、絶縁型電源の出力段に接続したツエナー・ダイオードを使って負バイアスを印加することでチャネル A ドライバをターンオフさせています。この負バイアスはツエナー・ダイオード電圧によって設定されます。絶縁型電源  $V_A$  の電圧が 17V である場合、ターンオフ電圧は -5.1V、ターンオン電圧は 17V - 5.1V ≈ 12V です。チャネル B ドライバ回路は、チャネル A と同じです。そのため、この

構成では 1 つのハーフブリッジ構成に対して 2 つの電源が必要であり、 $R_Z$  によって定常的に電力が消費されます。

図 9-2. 絶縁型バイアス電源の出力に接続したツエナー・ダイオードによる負バイアス印加

図 9-3 に、2 つの電源 (または 1 つの 1 入力 2 出力電源) を使う別の例を示します。電源  $V_{A+}$  が正の駆動出力電圧を決定し、電源  $V_{A-}$  が負のターンオフ電圧を決定します。チャネル B の構成はチャネル A と同じです。この方法は第 1 の例よりも多くの電源を必要としますが、正および負レール電圧をより柔軟に設定できます。

図 9-3.2 つの絶縁型バイアス電源による負バイアス印加

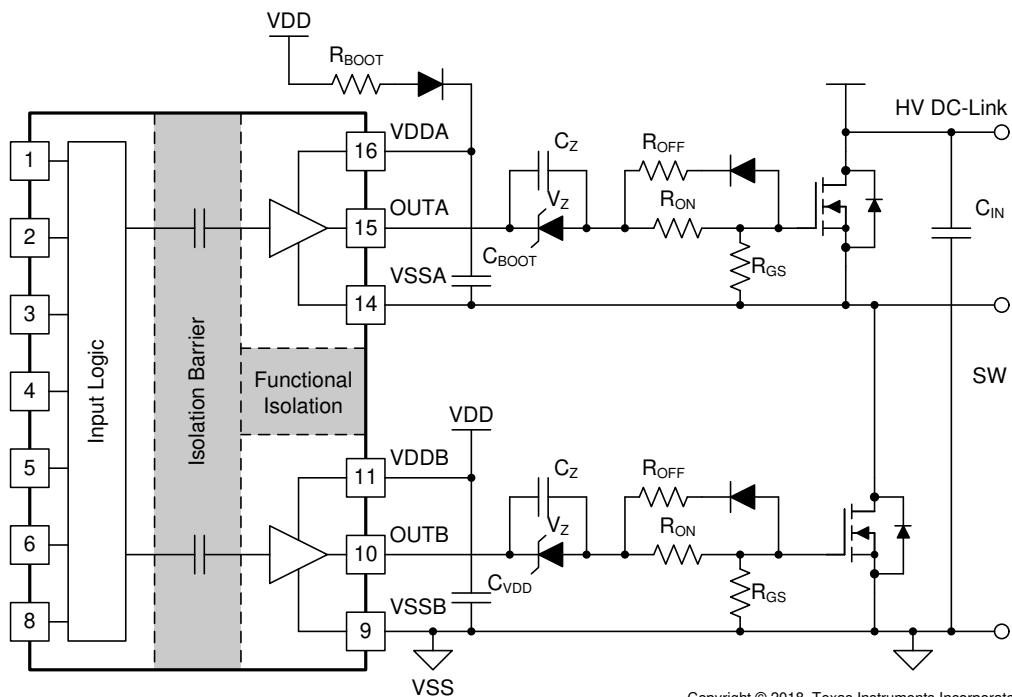

図 9-4 に示す最後の例は単一電源構成であり、ゲート駆動ループ内のツエナー・ダイオードによって負バイアスを生成しています。この方法の利点は、1 つの電源のみを使い、ブートストラップ電源をハイサイド駆動に使えることです。この設計は、3 つの方法のうちでコストと設計工数が最も少なくて済みます。しかし、この方法には以下の制約があります。

1. 負のゲート駆動バイアスはツエナー・ダイオードのみによって決まるのではなく、デューティ・サイクルによっても影響されます。これは、デューティ・サイクルが変化すると負バイアス電圧が変化することを意味

しています。そのため、固定デューティ・サイクル(約50%)のコンバータ(例:可変周波数共振コンバータ、位相シフト・コンバータ)がこの方法に適しています。

2. 推進電源電圧範囲を維持するには、ハイサイド VDDA-VSSA として十分な電圧を維持する必要があります。これは、ブートストラップ・コンデンサをリフレッシュするために、各スイッチング・サイクルの間、ロー・サイド・スイッチをターンオンさせ、またはボディ・ダイオード(または逆並列ダイオード)にフリー・ホイール電流を流す必要があることを意味します。そのため、他の2つの回路例と同様のハイサイド専用電源を使わない限り、ハイサイドを100%デューティ・サイクルにすることはできません。

図 9-4. 1つの電源とゲート駆動経路内のツエナー・ダイオードによる負バイアス印加

### 9.2.3 アプリケーション曲線

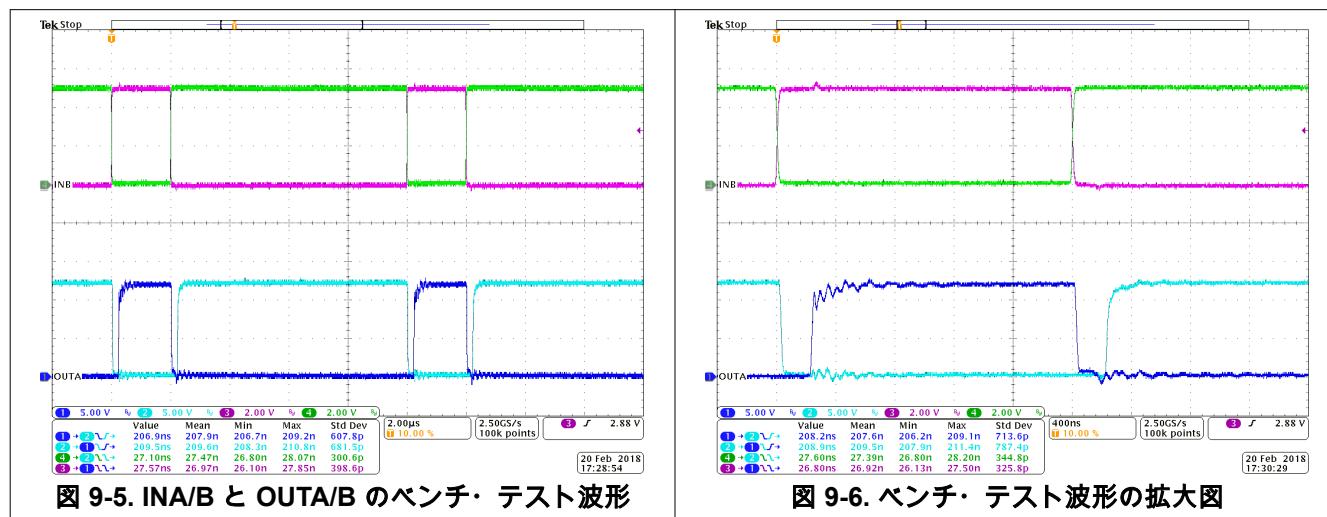

図 9-5 と図 9-6 に、図 9-1 に示す設計例の以下の条件におけるベンチ・テスト波形を示します。VCC = 5.0V、VDD = 12V、f<sub>SW</sub> = 100kHz、V<sub>DC-Link</sub> = 400V。

チャネル 1 (青) : ハイサイド・パワー・トランジスタのゲート - ソース間の信号

チャネル 2 (シアン) : ローサイド・パワー・トランジスタのゲート - ソース間の信号

チャネル 3 (ピンク) : INA ピンの信号

チャネル 4 (緑) : INB ピンの信号

図 9-5 で、INA と INB に 3.3V、20%/80% デューティ・サイクルの相補信号が印加されています。パワー・トランジスタのゲート駆動信号には 200ns のデッド・タイムが挿入されており、DC リンクには 400V の高電圧が印加されています (図 9-5 の測定部を参照)。高電圧が印加されている場合、帯域幅がより狭い差動プローブが使われるため、達成可能な測定精度が制限されることに注意します。

図 9-6 に、図 9-5 の波形の拡大図と、伝搬遅延とデッド・タイムの測定値を示します。出力波形はパワー・トランジスタのゲート・ピンとソース・ピンの間で測定され、ドライバの OUTA ピンと OUTB ピンからは直接測定されないことに注意します。

図 9-5. INA/B と OUTA/B のベンチ・テスト波形

図 9-6. ベンチ・テスト波形の拡大図

## 10 電源に関する推奨事項

UCC21540-Q1 の推奨入力電源電圧 (VCCI) は 3V ~ 5.5V です。出力バイアス電源電圧 (VDDA/VDDB) は 6.0V ~ 18V です。このバイアス電源範囲の下限は、各デバイスの内部低電圧誤動作防止 (UVLO) 保護機能によって決定されます。通常動作中、VDD と VCCI はそれぞれの UVLO スレッショルドを下回ることはできません。UVLO の詳細については、[セクション 8.3.1](#) を参照してください。VDDA/VDDB 範囲の上限は、UCC21540-Q1 によって駆動されるパワー・デバイスの最大ゲート電圧で決まります。VDDA/VDDB の最大電圧の推奨値は 18V です。

容量性負荷を接続した出力を HIGH に駆動する際の電流を供給するため、VDD ピンと VSS ピンの間にロード・バイパス・コンデンサを配置する必要があります。このコンデンサは、寄生インピーダンスを最小化するため、本デバイスにできる限り近づけて配置する必要があります。低 ESR の表面実装型セラミック・コンデンサを推奨します。バイパス・コンデンサのインピーダンスが大きすぎると、抵抗性および誘導性寄生素子により、IC のピンで観測される電源電圧が UVLO スレッショルドを予期せず下回る可能性があります。VDD と VSS の間の高周波ノイズをフィルタ処理するには、高い周波数でよりインピーダンスが小さい第 2 のコンデンサを配置することが有効です。たとえば、第 1 のバイパス・コンデンサを 1 $\mu$ F、第 2 の高周波バイパス・コンデンサを 100nF とすることができます。

同様に、VCCI ピンと GND ピンの間にもバイパス・コンデンサを配置する必要があります。UCC21540-Q1 の入力側の論理回路が消費する電流は小さいことを考慮して、このバイパス・コンデンサの最小値として 100nF を推奨します。

## 11 レイアウト

### 11.1 レイアウトのガイドライン

UCC21540-Q1 の性能を最適化するため、これらの PCB レイアウト・ ガイドラインを考慮します。

#### 11.1.1 部品の配置に関する注意事項

- 外付けパワー パソコンをターンオンさせる際の大きなピーク電流に対応するため、VCCI ピンと GND ピンの間と VDD ピンと VSS ピンの間に低 ESR かつ低 ESL のコンデンサを本デバイスに近接して接続する必要があります。

- ブリッジ構成のスイッチ ノード VSSA (HS) ピンでの大きな負の過渡を防止するため、上側トランジスタのソースと下側トランジスタのソースとの間の寄生インダクタンスを最小限に抑える必要があります。

- 離れた場所にあるマイコンまたは高インピーダンス源で DIS ピンを駆動する際のノイズ耐性を向上させるため、DIS ピンと GND の間に小容量のバイパス コンデンサ (1000pF 以上) を追加することを推奨します。

- デッド タイム機能を使う場合、内部デッド タイム回路にノイズが意図せず結合することを防ぐため、設定抵抗  $R_{DT}$  とバイパス コンデンサは UCC21540-Q1 の DT ピンに近接して配置することを推奨します。このコンデンサは  $\leq 1nF$  とします。

#### 11.1.2 接地に関する注意事項

- トランジスタのゲートを充放電する大きなピーク電流を、最小限の物理的ループ面積に制限することは不可欠です。そうすることで、ループのインダクタンスが小さくなり、トランジスタのゲート端子のノイズが最小限に抑えられます。ゲート・ ドライバは、トランジスタのできるだけ近くに配置する必要があります。

- ブーストストラップ・ コンデンサ、ブーストストラップ・ ダイオード、VSSB に対するローカル・ バイパス・ コンデンサ、ローサイド・ トランジスタのボディ / 逆並列ダイオードを含む大電流経路に注意を払います。ブーストストラップ・ コンデンサは、VDD バイパス・ コンデンサによってブーストストラップ・ ダイオードを通してサイクルごとに再充電されます。この再充電は短い時間間隔で行われ、大きなピーク電流を必要とします。回路基板上のループの長さと面積を最小化することは、動作の信頼性を確保する上で重要です。

#### 11.1.3 高電圧に関する注意事項

- 1 次側と 2 次側の間の絶縁性能を確保するため、ドライバ・ デバイスの下には PCB パターンも銅箔も配置しないようにします。絶縁性能を低下させるおそれがある汚染を防止するため、PCB カットアウトを推奨します。

- ハーフブリッジまたはハイサイド / ローサイド構成の場合、PCB レイアウトのハイサイドのパターンとローサイドのパターンの空間距離を最大限に広げます。DWK パッケージでは、より高いバス電圧に対応するため、ピン 12 とピン 13 を除去することで 3.3mm 以上の沿面距離を確保しています。

#### 11.1.4 熱に関する注意事項

- 駆動電圧が高い、負荷が重い、スイッチング周波数が高い、のいずれかの場合、UCC21540-Q1 は大きな電力を消費する可能性があります (詳細は [セクション 9.2.2.6](#) を参照)。適切な PCB レイアウトは、デバイスから PCB に熱を放散し接合部から基板への熱抵抗 ( $\theta_{JB}$ ) を最小化するのに役立ちます。

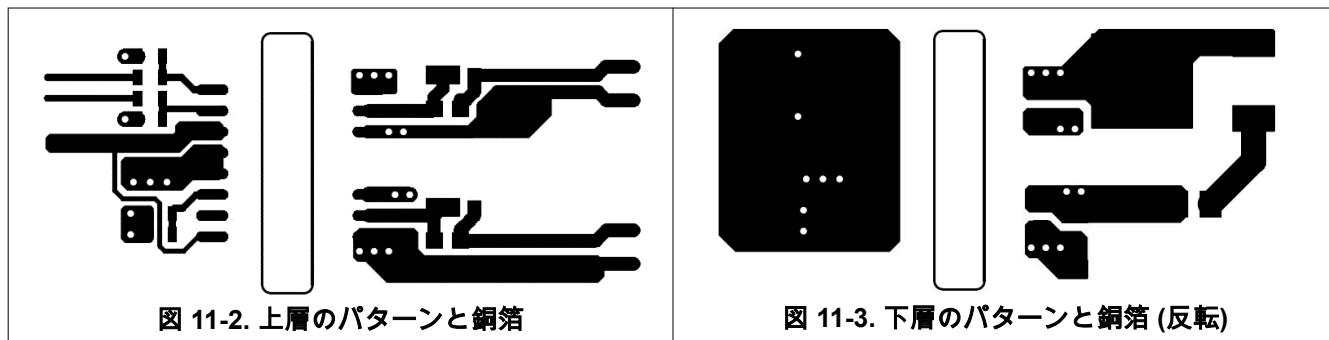

- VDDA、VDBB、VSSA、VSSB ピンに接続する PCB 銅箔の面積を増やし、VSSA、VSSB との接続を優先して最大化することを推奨します ([図 11-2](#) と [図 11-3](#) を参照)。しかし、上述の高電圧 PCB に関する注意事項は守る必要があります。

- システムに複数の層が存在する場合、VDDA、VDBB、VSSA、VSSB ピンを内部グランドまたは電源プレーンに適切なサイズの複数のビアで接続することも推奨します。異なる高電圧プレーンのパターン / 銅箔が重ならないようにします。

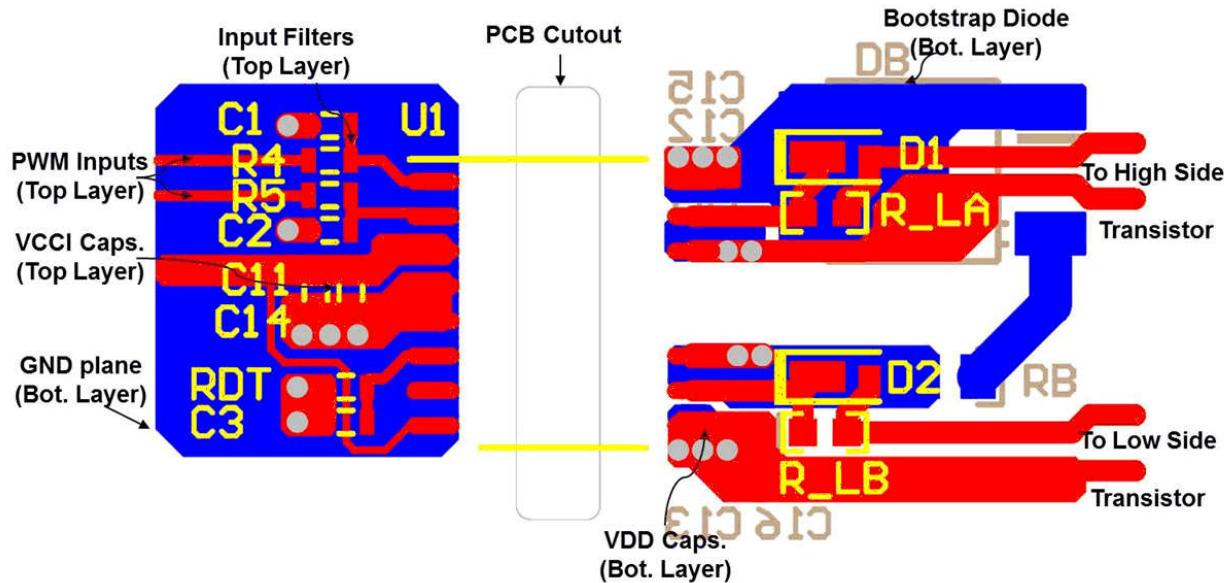

## 11.2 レイアウト例

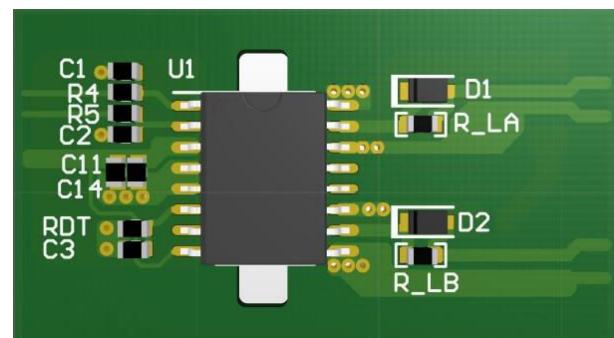

図 11-1 に、SOIC-14 DW パッケージに合わせて信号と主要部品を表示した 2 層 PCB のレイアウト例を示します。このパッケージは、ピン 12 とピン 13 が除去されています。詳細については、UCC21540EVM 設計 - 『UCC21540EVM ユーザー・ガイド』を参照してください。

図 11-1. レイアウト例

図 11-2 と図 11-3 に上層と下層のパターンと銅箔を示します。

### 注

1 次側と 2 次側の間に PCB パターンも銅箔も存在しないため、絶縁性能を確保できます。

高電圧動作に備えて沿面距離を最大化するため、出力段のハイサイド・ゲート・ドライバとローサイド・ゲート・ドライバの PCB パターンの間隔が広げられています。これにより、高  $dv/dt$  が発生する可能性があるスイッチング・ノード VSSA (SW) とローサイド・ゲート・ドライバの間の寄生容量結合によるクロストークも最小化されます。

図 11-2. 上層のパターンと銅箔

図 11-3. 下層のパターンと銅箔 (反転)

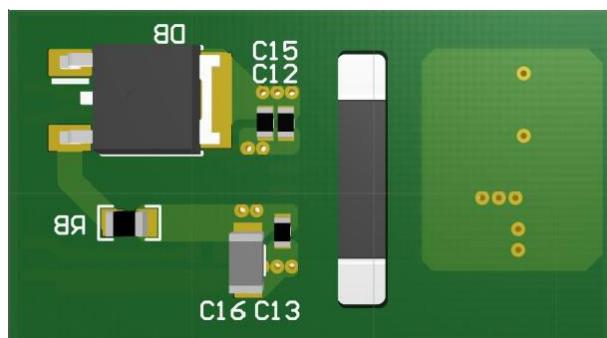

図 11-4 と図 11-5 に、3D レイアウト画像 (上面図と底面図) を示します。

注

1 次側と 2 次側の間の PCB カットアウトの場所に注意します。これにより、絶縁性能を確保しています。

図 11-4. PCB の 3D 上面図

図 11-5. PCB の 3D 底面図

## 12 デバイスおよびドキュメントのサポート

### 12.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

### 12.2 ドキュメントのサポート

#### 12.2.1 関連資料

関連資料については、『[絶縁に関する用語](#)』を参照してください。

### 12.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 12.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 12.5 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 12.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 12.7 用語集

[テキサス・インスツルメンツ用語集](#) この用語集には、用語や略語の一覧および定義が記載されています。

## 13 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision C (February 2021) to Revision D (August 2024) | Page |

|---------------------------------------------------------------------|------|

| ・ 「特長」の HBM および CDM ESD 分類レベルを更新.....                               | 1    |

| ・ CMTI を 100V/ns を超える値から 125V/ns を超える値に変更.....                      | 1    |

| ・ 伝搬遅延を 40ns (最大値) から 33ns (標準値) に変更.....                           | 1    |

| ・ 最大遅延マッチング 5ns の箇条書き項目を削除.....                                     | 1    |

| ・ 最大パルス幅歪みの値を 5.5ns から 6ns に変更.....                                 | 1    |

| ・ 最大 VDD 電源オン遅延の 35us を最大 10us に変更.....                             | 1    |

| ・ 「認定、認定進行中」の箇条書き項目を削除.....                                         | 1    |

| ・ 最小 100V/ns の CMTI を 125V/ns に変更.....                              | 1    |

| ・ 5ns より短い入力過渡を除去するという文を削除.....                                     | 1    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| • 入力ピンの負電圧の処理方法を、200ns について -2V から 50ns について -5V に変更.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1 |

| • 回路図 DT コンデンサのサイズを 2.2nF 以上から 1nF 以下に変更.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1 |

| • DT ピンの推奨される状態と DT ピンのコンデンサ サイズを変更.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3 |

| • VCCI の絶対最大値を 6V から 20V に変更.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5 |

| • VDDA-VSSA と VDDB-VSSB の絶対最大値を 20V から 30V に変更.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5 |

| • 新しくリリースされたデータシートに合わせて、-0.5V の最小値をすべて -0.3V に変更.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5 |

| • 新しくリリースされたデータシートに合わせて、すべての絶対最大値を電源 +0.5V から電源 +0.3V に変更.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5 |

| • 入力信号電圧過渡テスト条件を 50ns に、絶対最小値を -5V に変更.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5 |

| • ESD 業界標準に合わせて ESD の仕様を HBM = ±4000、CDM = ±1500 から HBM = ±2000、CDM = ±1000 に更新 .....                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5 |

| • VCCI (推奨最大値) を 5.5V から 18V に変更.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5 |

| • VDDA-VSSA と VDDB-VSSB の推奨最大値を 18V から 25V に変更.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5 |