# TXE81XX-Q1 車載用 16 ビットおよび 24 ビット SPI バス I/O エクスパンダ (割り込み出力、リセット入力、I/O 構成レジスタ付き)

## 1 特長

- 車載アプリケーション用に AEC-Q100 認定済み:

- 温度グレード 1: -40°C ~ +125°C, T<sub>A</sub>

- 機能安全対応**

- 機能安全システムの設計に役立つ資料を利用可能

- 1.65V ~ 5.5V の動作電源電圧範囲

- Low スタンバイ消費電流: 2.3µA (標準値)

- SPI SCLK 周波数

- 10MHz (3.3V ~ 5.5V)

- 5MHz (1.65V ~ 5.5V)

- アクティブ Low のリセット入力 (RESET)

- 5V 許容の入力および出力ポート

- 組み込みフェイルセーフ I/O 機能

- オープンドレインのアクティブ Low 割り込み出力 (INT)

- GPIO のすべての入力で、個別の I/O 制御とグリッチフィルタをサポート

- SPI デイジー チェーンをサポート

- I/O 読み取りバースト モードをサポート

- I/O 極性反転をサポート

- 最後の I/O 状態を維持するためのバスホールド機能

- 大電流の駆動能力を持つラッチ付き出力により、LED を直接駆動

- AEC Q100-004 準拠で 100mA 超のラッチアップ性能

- AEC - Q100 要件を上回る ESD 保護

- 人体モデルで 2000V (AEC - Q100-002)

- 荷電デバイス モデルで 1000V (AEC Q100-011)

## 2 アプリケーション

- 車載用インフォテインメントおよびクラスタ

- ボディエレクトロニクスおよび照明

- ハイブリッド、電動、パワートレイン システム

- GPIO が制限されたプロセッサを使用する製品

## 3 説明

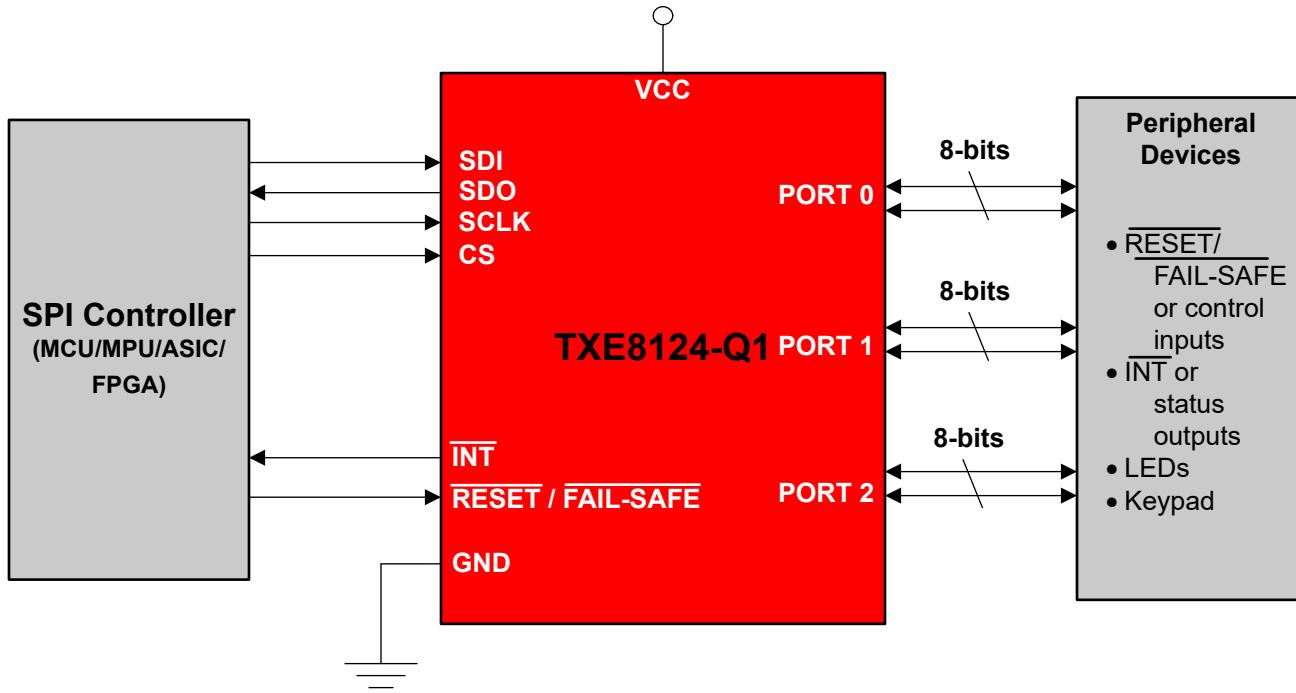

TXE81XX-Q1 デバイスは、4 線式シリアル ペリフェラルインターフェイス (SPI) プロトコル用の汎用パラレル入出力 (I/O) 拡張を提供し、1.65V ~ 5.5V V<sub>CC</sub> 動作用に設計されています。

このデバイスは、3.3V ~ 5.5V で 10MHz、1.65V ~ 5.5V で 5MHz をサポートしています。TXE81XX-Q1 をはじめとする I/O エクスパンダは、スイッチ、センサ、プッシュボタン、LED、ファンに I/O を追加する必要がある場合に、簡単なソリューションとして使用できます。

TXE81XX-Q1 デバイスには、速度、消費電力、柔軟性の観点から I/O 性能を向上させるように設計された追加機能を備えた I/O ポートがあります。追加機能としては、イネーブル/ディセーブル プルアップ抵抗およびプルダウン抵抗、ラッチ可能な入力、マスク可能な割り込み、割り込みステータス レジスタ、プログラム可能なオープンドレインまたはプッシュプル出力、および FAIL-SAFE ピンでイネーブルになるフェイルセーフ レジスタ モードがあります。

### パッケージ情報

| 部品番号 <sup>(1)</sup> | パッケージ <sup>(2)</sup> | パッケージ サイズ <sup>(3)</sup> |

|---------------------|----------------------|--------------------------|

| TXE8124-Q1          | (VSSOP, 32)          | 8mm × 5mm                |

|                     | (VQFN, 32)           | 5mm × 5mm                |

| TXE8116-Q1          | (VSSOP, 24)          | 6mm × 5mm                |

|                     | (VQFN, 24)           | 4mm × 4mm                |

(1) TXE8124-Q1 は I/O ポート 0, 1, 2 をサポートし、TXE8116-Q1 は I/O ポート 0 および 1 をサポートしています。

(2) 詳細については、セクション 11 を参照してください。

(3) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

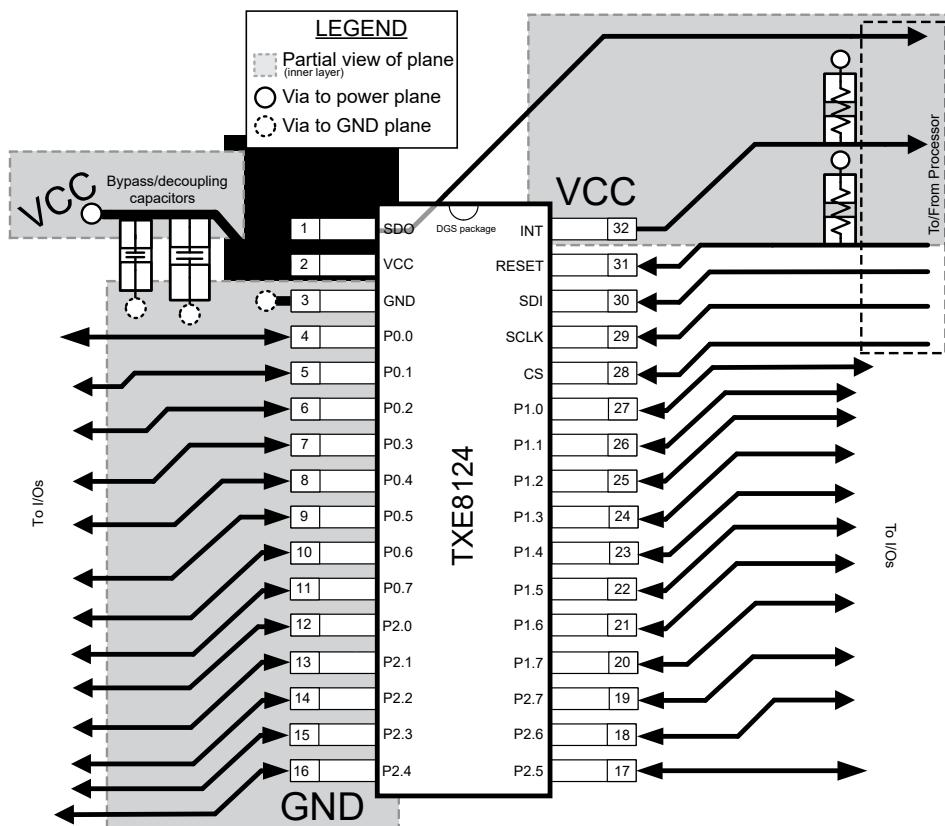

概略回路図

## 目次

|                         |    |                             |    |

|-------------------------|----|-----------------------------|----|

| 1 特長.....               | 1  | 7.3 機能説明.....               | 18 |

| 2 アプリケーション.....         | 1  | 7.4 デバイスの機能モード.....         | 25 |

| 3 説明.....               | 1  | 7.5 プログラミング.....            | 25 |

| 4 ピン構成および機能.....        | 4  | 7.6 レジスタ マップ.....           | 27 |

| 5 仕様.....               | 6  | 8 アプリケーションと実装.....          | 35 |

| 5.1 絶対最大定格.....         | 6  | 8.1 アプリケーション情報.....         | 35 |

| 5.2 ESD レーティング.....     | 6  | 8.2 電源に関する推奨事項.....         | 35 |

| 5.3 推奨動作条件.....         | 6  | 8.3 レイアウト.....              | 37 |

| 5.4 熱に関する情報.....        | 7  | 9 デバイスおよびドキュメントのサポート.....   | 38 |

| 5.5 電気的特性.....          | 8  | 9.1 ドキュメントの更新通知を受け取る方法..... | 38 |

| 5.6 タイミング要件.....        | 10 | 9.2 サポート・リソース.....          | 38 |

| 5.7 SPI バスのタイミング要件..... | 11 | 9.3 商標.....                 | 38 |

| 5.8 スイッチング特性.....       | 11 | 9.4 静電気放電に関する注意事項.....      | 38 |

| 6 パラメータ測定情報.....        | 12 | 9.5 用語集.....                | 38 |

| 7 詳細説明.....             | 17 | 10 改訂履歴.....                | 38 |

| 7.1 概要.....             | 17 | 11 メカニカル、パッケージ、および注文情報..... | 38 |

| 7.2 機能ブロック図.....        | 17 |                             |    |

## 4 ピン構成および機能

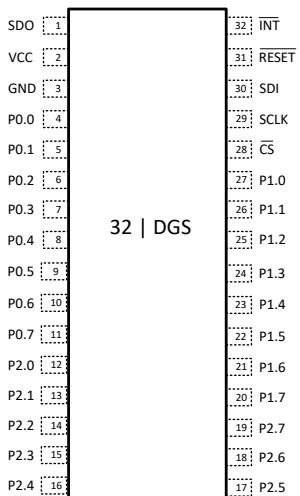

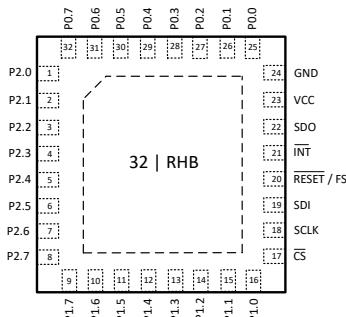

図 4-1. TXE8124-Q1 DGS (VSSOP) パッケージ、32 ピン (上面図)

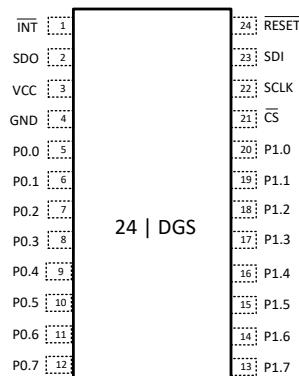

図 4-2. TXE8116-Q1 DGS (VSSOP) パッケージ、24 ピン (上面図)

図 4-3. TXE8124-Q1 RHB (VQFN) パッケージ、32 ピン (上面図)

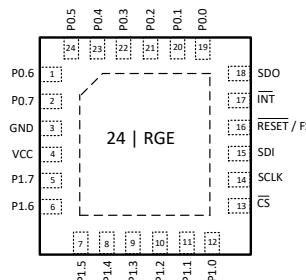

図 4-4. TXE8116-Q1 RGE (VQFN) パッケージ、24 ピン (上面図)

**表 4-1. ピンの機能**

| 名称                  | ピン                            |                               |                         |                         |     | タイプ <sup>(1)</sup>                                             | 説明 |

|---------------------|-------------------------------|-------------------------------|-------------------------|-------------------------|-----|----------------------------------------------------------------|----|

|                     | TXE8124<br>-Q1<br>VSSOP3<br>2 | TXE8116<br>-Q1<br>VSSOP2<br>4 | TXE8124<br>-Q1<br>RHB32 | TXE8116<br>-Q1<br>RGE24 |     |                                                                |    |

| P2.0                | 12                            | -                             | 1                       | -                       | I/O | P ポート入出力。電源投入時にポート 2 - IO #0 は入力として設定されます                      |    |

| P2.1                | 13                            | -                             | 2                       | -                       | I/O | P ポート入出力。電源投入時にポート 2 - IO #1 は入力として設定されます                      |    |

| P2.2                | 14                            | -                             | 3                       | -                       | I/O | P ポート入出力。電源投入時にポート 2 - IO #2 は入力として設定されます                      |    |

| P2.3                | 15                            | -                             | 4                       | -                       | I/O | P ポート入出力。電源投入時にポート 2 - IO #3 は入力として設定されます                      |    |

| P2.4                | 16                            | -                             | 5                       | -                       | I/O | P ポート入出力。電源投入時にポート 2 - IO #4 は入力として設定されます                      |    |

| P2.5                | 17                            | -                             | 6                       | -                       | I/O | P ポート入出力。電源投入時にポート 2 - IO #5 は入力として設定されます                      |    |

| P2.6                | 18                            | -                             | 7                       | -                       | I/O | P ポート入出力。電源投入時にポート 2 - IO #6 は入力として設定されます                      |    |

| P2.7                | 19                            | -                             | 8                       | -                       | I/O | P ポート入出力。電源投入時にポート 2 - IO #7 は入力として設定されます                      |    |

| P1.7                | 20                            | 13                            | 9                       | 5                       | I/O | P ポート入出力。電源投入時にポート 1 - IO #7 は入力として設定されます                      |    |

| P1.6                | 21                            | 14                            | 10                      | 6                       | I/O | P ポート入出力。電源投入時にポート 1 - IO #6 は入力として設定されます                      |    |

| P1.5                | 22                            | 15                            | 11                      | 7                       | I/O | P ポート入出力。電源投入時にポート 1 - IO #5 は入力として設定されます                      |    |

| P1.4                | 23                            | 16                            | 12                      | 8                       | I/O | P ポート入出力。電源投入時にポート 1 - IO #4 は入力として設定されます                      |    |

| P1.3                | 24                            | 17                            | 13                      | 9                       | I/O | P ポート入出力。電源投入時にポート 1 - IO #3 は入力として設定されます                      |    |

| P1.2                | 25                            | 18                            | 14                      | 10                      | I/O | P ポート入出力。電源投入時にポート 1 - IO #2 は入力として設定されます                      |    |

| P1.1                | 26                            | 19                            | 15                      | 11                      | I/O | P ポート入出力。電源投入時にポート 1 - IO #1 は入力として設定されます                      |    |

| P1.0                | 27                            | 20                            | 16                      | 12                      | I/O | P ポート入出力。電源投入時にポート 1 - IO #0 は入力として設定されます                      |    |

| CS                  | 28                            | 21                            | 17                      | 13                      | I   | SPI チップ セレクト入力。内部プルアップ抵抗                                       |    |

| SCLK                | 29                            | 22                            | 18                      | 14                      | I   | SPI シリアル クロック入力。内部プルダウン抵抗                                      |    |

| SDI                 | 30                            | 23                            | 19                      | 15                      | I   | SPI シリアル データ入力。                                                |    |

| RESET/<br>FAIL-SAFE | 31                            | 24                            | 20                      | 16                      | I   | アクティブ Low リセットまたはフェイルセーフ入力。外付けプルアップ抵抗が V <sub>CC</sub> に接続します。 |    |

| INT                 | 32                            | 1                             | 21                      | 17                      | O   | オープンドレイン割り込み出力。外付けプルアップ抵抗が V <sub>CC</sub> に接続します。             |    |

| SDO                 | 1                             | 2                             | 22                      | 18                      | O   | SPI シリアル データ出力。プッシュ プル出力                                       |    |

| VCC                 | 2                             | 3                             | 23                      | 4                       | P   | 電源電圧                                                           |    |

| GND                 | 3                             | 4                             | 24                      | 3                       | G   | グランド                                                           |    |

| P0.0                | 4                             | 5                             | 25                      | 19                      | I/O | P ポート入出力。電源投入時にポート 0 - IO #0 は入力として設定されます                      |    |

| P0.1                | 5                             | 6                             | 26                      | 20                      | I/O | P ポート入出力。電源投入時にポート 0 - IO #1 は入力として設定されます                      |    |

| P0.2                | 6                             | 7                             | 27                      | 21                      | I/O | P ポート入出力。電源投入時にポート 0 - IO #2 は入力として設定されます                      |    |

| P0.3                | 7                             | 8                             | 28                      | 22                      | I/O | P ポート入出力。電源投入時にポート 0 - IO #3 は入力として設定されます                      |    |

| P0.4                | 8                             | 9                             | 29                      | 23                      | I/O | P ポート入出力。電源投入時にポート 0 - IO #4 は入力として設定されます                      |    |

| P0.5                | 9                             | 10                            | 30                      | 24                      | I/O | P ポート入出力。電源投入時にポート 0 - IO #5 は入力として設定されます                      |    |

| P0.6                | 10                            | 11                            | 31                      | 1                       | I/O | P ポート入出力。電源投入時にポート 0 - IO #6 は入力として設定されます                      |    |

| P0.7                | 11                            | 12                            | 32                      | 2                       | I/O | P ポート入出力。電源投入時にポート 0 - IO #7 は入力として設定されます                      |    |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グランド、P = 電源

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                  |                                         |                   |                                                         | 最小値  | 最大値  | 単位 |

|------------------|-----------------------------------------|-------------------|---------------------------------------------------------|------|------|----|

| V <sub>CC</sub>  | 電源電圧                                    |                   |                                                         | -0.5 | 6.5  | V  |

| V <sub>I</sub>   | 入力電圧 <sup>(2)</sup>                     |                   |                                                         | -0.5 | 6.5  | V  |

| V <sub>O</sub>   | 出力電圧 <sup>(2)</sup>                     |                   |                                                         | -0.5 | 6.5  | V  |

| I <sub>IK</sub>  | 入力クランプ電流                                | RESET、SCLK、SDI、CS | V <sub>I</sub> < 0                                      |      | -20  | mA |

| I <sub>OK</sub>  | 出力クランプ電流                                | INT、SDO           | V <sub>O</sub> < 0                                      |      | -20  | mA |

| I <sub>IOK</sub> | 入力 / 出力クランプ電流                           | P0.0~P2.7         | V <sub>O</sub> < 0 または V <sub>O</sub> > V <sub>CC</sub> |      | ±20  | mA |

| I <sub>OL</sub>  | 連続出力 Low 電流                             |                   | V <sub>O</sub> = 0~V <sub>CC</sub>                      |      | 50   | mA |

| I <sub>OH</sub>  | 連続出力 High 電流                            |                   | V <sub>O</sub> = 0~V <sub>CC</sub>                      |      | -50  | mA |

| I <sub>CC</sub>  | GND を流れる連続電流 <sup>(3)</sup>             |                   |                                                         |      | -200 | mA |

| I <sub>CC</sub>  | V <sub>CC</sub> を流れる連続電流 <sup>(3)</sup> |                   |                                                         |      | 160  | mA |

| T <sub>J</sub>   | 接合部温度                                   |                   |                                                         | -40  | 150  | °C |

| T <sub>stg</sub> | 保存温度                                    |                   |                                                         | -40  | 150  | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) 入力と出力の電流の定格を順守しても、入力の負電圧と出力電圧の定格を超えることがあります。

- (3) 合計電流は、全負荷で実行できるチャネルの数を制限します。

### 5.2 ESD レーティング

|                    |      |                                                    | 値     | 単位 |

|--------------------|------|----------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、AEC Q100-002 に準拠、すべてのピン <sup>(1)</sup> | ±2000 | V  |

|                    |      | デバイス帶電モデル (CDM)、AEC Q100-011 に準拠、すべてのピン            | ±1000 |    |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI/ESDA/JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 5.3 推奨動作条件

外気温度範囲での動作時 (特に記述がない限り)

|                 |                                       |                    | 最小値                        | 最大値 | 単位 |

|-----------------|---------------------------------------|--------------------|----------------------------|-----|----|

| V <sub>CC</sub> | 電源電圧                                  |                    | 1.65                       | 5.5 | V  |

| V <sub>IH</sub> | High レベル入力電圧                          | P0.0~P2.7          | 0.7 × V <sub>CC</sub>      | VCC | V  |

|                 |                                       | SCLK、SDI、CS、RESET、 | 0.7 × V <sub>CC</sub>      | VCC |    |

| V <sub>IL</sub> | Low レベル入力電圧                           | P0.0~P2.7          | -0.5 0.3 × V <sub>CC</sub> |     | V  |

|                 |                                       | SCLK、SDI、CS、RESET、 | -0.5 0.3 × V <sub>CC</sub> |     |    |

| I <sub>OH</sub> | High レベル出力電流 (V <sub>CC</sub> ≥ 2.3V) | P0.0~P2.7          |                            | -10 | mA |

|                 | High レベル出力電流 (V <sub>CC</sub> < 2.3V) |                    |                            | -5  | mA |

| I <sub>OL</sub> | Low レベル出力電流                           | P0.0~P2.7          |                            | 25  | mA |

| T <sub>A</sub>  | 周囲温度                                  |                    | -40                        | 130 | °C |

| T <sub>J</sub>  | 接合部温度                                 |                    | -40                        | 150 | °C |

## 5.4 热に関する情報

| 热評価基準 <sup>(1)</sup> |                   | パッケージ       |             |            |            | 単位   |

|----------------------|-------------------|-------------|-------------|------------|------------|------|

|                      |                   | DGS (VSSOP) | DGS (VSSOP) | RHB (VQFN) | RGE (VQFN) |      |

|                      |                   | 32 ピン       | 24 ピン       | 32 ピン      | 24 ピン      |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗      | 80.1        | 86.5        | 44.1       | 43.0       | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース(上面)への熱抵抗 | 35.4        | 34.5        | 35.6       | 39.9       | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗      | 44.1        | 48.2        | 25.0       | 21.0       | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ  | 2.0         | 1.4         | 2.7        | 2.2        | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ  | 43.7        | 47.8        | 24.9       | 21.0       | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース(底面)への熱抵抗 | 該当なし        | 該当なし        | 14.2       | 13.0       | °C/W |

(1) 従来および最新の热評価基準の詳細については、『半導体およびICパッケージの热評価基準』アプリケーションノートを参照してください。

## 5.5 電気的特性

外気温度範囲での動作時 (特に記述がない限り)

| パラメータ             |                                   | テスト条件                                                        | V <sub>CC</sub>                                                                                                                                                                     | 最小値                                      | 標準値                   | 最大値  | 単位   |    |

|-------------------|-----------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------|------|------|----|

| V <sub>IK</sub>   | 入力ダイオードクランプ電圧                     | I <sub>I</sub> = -18mA                                       | V <sub>CC</sub>                                                                                                                                                                     | -1.2                                     |                       |      | V    |    |

| V <sub>PORR</sub> | パワーONリセット電圧、V <sub>CC</sub> 立ち上がり | V <sub>I</sub> = V <sub>CC</sub> または GND, I <sub>O</sub> = 0 | V <sub>CC</sub>                                                                                                                                                                     | 1.35                                     | 1.05                  |      | V    |    |

| V <sub>PORF</sub> |                                   |                                                              |                                                                                                                                                                                     |                                          |                       |      |      |    |

| V <sub>OH</sub>   | High レベル出力電圧 <sup>(1)</sup>       | P ポート                                                        | I <sub>OH</sub> = -4mA                                                                                                                                                              | 1.65V                                    | 1.31                  |      | V    |    |

|                   |                                   |                                                              |                                                                                                                                                                                     | 2.3V                                     | 1.73                  |      |      |    |

|                   |                                   |                                                              | I <sub>OH</sub> = -8mA                                                                                                                                                              | 3V                                       | 2.4                   |      |      |    |

|                   |                                   |                                                              |                                                                                                                                                                                     | 4.5V                                     | 4.0                   |      |      |    |

|                   |                                   |                                                              |                                                                                                                                                                                     | 5.5V                                     | 4.95                  |      |      |    |

|                   |                                   |                                                              |                                                                                                                                                                                     | 1.65V ~ 5.5V                             | V <sub>CC</sub> - 0.4 |      |      |    |

| V <sub>OL</sub>   | Low レベル出力電圧                       | SDO                                                          | I <sub>OL</sub> = -3mA                                                                                                                                                              | 1.65V ~ 5.5V                             |                       | 0.4  | V    |    |

| I <sub>OL</sub>   | Low レベル出力電流                       | INT                                                          | I <sub>OL</sub> = 4mA                                                                                                                                                               | 1.65V                                    |                       | 0.22 | mA   |    |

|                   |                                   |                                                              |                                                                                                                                                                                     | 2.3V                                     |                       | 0.36 |      |    |

|                   |                                   |                                                              | I <sub>OL</sub> = 8mA                                                                                                                                                               | 3V                                       |                       | 0.25 |      |    |

|                   |                                   |                                                              |                                                                                                                                                                                     | 4.5V                                     |                       | 0.17 |      |    |

|                   |                                   |                                                              |                                                                                                                                                                                     | 5.5V                                     |                       | 0.15 |      |    |

| V <sub>OL</sub>   | Low レベル出力電圧                       | SDO                                                          | I <sub>OL</sub> = 3mA                                                                                                                                                               | 1.65V ~ 5.5V                             |                       | 0.4  | V    |    |

| I <sub>OL</sub>   | Low レベル出力電流                       | INT                                                          | V <sub>OL</sub> = 0.4 V                                                                                                                                                             | 1.65V ~ 5.5V                             | 4                     |      | mA   |    |

| I <sub>I</sub>    | 入力リーク電流                           | P ポート                                                        | V <sub>I</sub> = V <sub>CC</sub> または GND                                                                                                                                            | 1.65V ~ 5.5V                             |                       | ±1   | μA   |    |

|                   |                                   |                                                              | V <sub>I</sub> = 3.6V                                                                                                                                                               | 0V                                       |                       | ±1   |      |    |

|                   |                                   |                                                              | SDI、RESET                                                                                                                                                                           | V <sub>I</sub> = V <sub>CC</sub> または GND | 1.65V ~ 5.5V          | ±1   |      |    |

| I <sub>I</sub>    | 入力リーク電流                           | SCLK                                                         | V <sub>I</sub> = GND                                                                                                                                                                | 1.65V ~ 5.5V                             |                       | ±1   | μA   |    |

| I <sub>I</sub>    | 入力リーク電流                           | SCLK                                                         | V <sub>I</sub> = V <sub>CC</sub>                                                                                                                                                    | 1.65V ~ 5.5V                             |                       | ±65  | μA   |    |

| I <sub>I</sub>    | 入力リーク電流                           | CS                                                           | V <sub>I</sub> = V <sub>CC</sub>                                                                                                                                                    | 1.65V ~ 5.5V                             |                       | ±1   | μA   |    |

| I <sub>I</sub>    | 入力リーク電流                           | CS                                                           | V <sub>I</sub> = GND                                                                                                                                                                | 1.65V ~ 5.5V                             |                       | ±65  | μA   |    |

| I <sub>CC</sub>   | 静止時電流                             | スタンバイ モード                                                    | SDI、CS および RESET = V <sub>CC</sub> ,<br>P ポート = V <sub>CC</sub> または GND、<br>I/O = 入力、I <sub>O</sub> = 0mA<br>f <sub>SCLK</sub> = 0MHz、<br>-40°C < T <sub>A</sub> ≤ 85°C、I/O レジスタ無効  | 5.5V                                     |                       | 2.3  | 8    | μA |

|                   |                                   |                                                              |                                                                                                                                                                                     | 3.6V                                     |                       | 2    | 7.5  | μA |

|                   |                                   |                                                              |                                                                                                                                                                                     | 2.7V                                     |                       | 1.8  | 7.2  | μA |

|                   |                                   |                                                              |                                                                                                                                                                                     | 1.65V ~ 1.95V                            |                       | 1.7  | 7    | μA |

|                   |                                   |                                                              | SDI、CS および RESET = V <sub>CC</sub> ,<br>P ポート = V <sub>CC</sub> または GND、<br>I/O = 入力、I <sub>O</sub> = 0mA<br>f <sub>SCLK</sub> = 0MHz、<br>-40°C < T <sub>A</sub> ≤ 125°C、I/O レジスタ無効 | 5.5V                                     |                       | 2.3  | 26   | μA |

|                   |                                   |                                                              |                                                                                                                                                                                     | 3.6V                                     |                       | 2    | 24   |    |

|                   |                                   |                                                              |                                                                                                                                                                                     | 2.7V                                     |                       | 1.8  | 23.6 |    |

|                   |                                   |                                                              |                                                                                                                                                                                     | 1.65V ~ 1.95V                            |                       | 1.7  | 23.4 |    |

外気温度範囲での動作時(特に記述がない限り)

| パラメータ                |                        | テスト条件                          | V <sub>CC</sub>                                                                                                                                                                                    | 最小値           | 標準値  | 最大値 | 単位 |

|----------------------|------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|-----|----|

| I <sub>CC</sub>      | アクティブ電流                | アクティブ モード<br>(5MHz)            | SDI、CS および RESET = V <sub>CC</sub> 、<br>P ポート = V <sub>CC</sub> または GND、<br>I/O = 入力、I <sub>O</sub> = 0mA<br>f <sub>SCLK</sub> = 5MHz、SDO の 100pF 負荷<br>−40°C < T <sub>A</sub> ≤ 125°C、I/O レジスタ無効  | 5.5V          | 150  | 170 | μA |

|                      |                        |                                |                                                                                                                                                                                                    | 3.6V          | 132  | 140 |    |

|                      |                        |                                |                                                                                                                                                                                                    | 2.7V          | 127  | 135 |    |

|                      |                        |                                |                                                                                                                                                                                                    | 1.65V ~ 1.95V | 124  | 130 |    |

|                      |                        | アクティブ モード<br>(10MHz)           | SDI、CS および RESET = V <sub>CC</sub> 、<br>P ポート = V <sub>CC</sub> または GND、<br>I/O = 入力、I <sub>O</sub> = 0mA<br>f <sub>SCLK</sub> = 10MHz、SDO の 100pF 負荷<br>−40°C < T <sub>A</sub> ≤ 125°C、I/O レジスタ無効 | 5.5V          | 292  | 350 | μA |

|                      |                        |                                |                                                                                                                                                                                                    | 3.6V          | 257  | 285 |    |

|                      |                        |                                |                                                                                                                                                                                                    | 2.7V          | 240  | 270 |    |

|                      |                        |                                |                                                                                                                                                                                                    | 1.65V ~ 1.95V | 242  | 260 |    |

| I <sub>BHL</sub>     | バスホールド low 維持電流        |                                | V <sub>I</sub> = 0.58                                                                                                                                                                              | 1.65V         | 35   |     | μA |

|                      |                        |                                | V <sub>I</sub> = 0.70                                                                                                                                                                              | 2.3V          | 50   |     |    |

|                      |                        |                                | V <sub>I</sub> = 0.80                                                                                                                                                                              | 3V            | 60   |     |    |

|                      |                        |                                | V <sub>I</sub> = 1.35                                                                                                                                                                              | 4.5V          | 105  |     |    |

| I <sub>BHH</sub>     | バスホールド high 維持電流       |                                | V <sub>I</sub> = 1.07                                                                                                                                                                              | 1.65V         | -75  |     | μA |

|                      |                        |                                | V <sub>I</sub> = 1.70                                                                                                                                                                              | 2.3V          | -85  |     |    |

|                      |                        |                                | V <sub>I</sub> = 2.00                                                                                                                                                                              | 3V            | -140 |     |    |

|                      |                        |                                | V <sub>I</sub> = 3.15                                                                                                                                                                              | 4.5V          | -180 |     |    |

| I <sub>BHLO</sub>    | バスホールド low オーバードライブ電流  | 入力電圧を 0 から V <sub>CC</sub> に上昇 |                                                                                                                                                                                                    | 1.95V         | 170  |     | μA |

|                      |                        |                                |                                                                                                                                                                                                    | 2.7V          | 260  |     |    |

|                      |                        |                                |                                                                                                                                                                                                    | 3.6V          | 340  |     |    |

|                      |                        |                                |                                                                                                                                                                                                    | 5.5V          | 500  |     |    |

| I <sub>BHHO</sub>    | バスホールド high オーバードライブ電流 | 入力電圧を V <sub>CC</sub> から 0 に上昇 |                                                                                                                                                                                                    | 1.95V         | -170 |     | μA |

|                      |                        |                                |                                                                                                                                                                                                    | 2.7V          | -260 |     |    |

|                      |                        |                                |                                                                                                                                                                                                    | 3.6V          | -340 |     |    |

|                      |                        |                                |                                                                                                                                                                                                    | 5.5V          | -500 |     |    |

| R <sub>pu(int)</sub> | 内部プルアップ抵抗              | CS                             |                                                                                                                                                                                                    | 70            | 100  | 140 | kΩ |

|                      |                        | P ポート                          |                                                                                                                                                                                                    | 70            | 100  | 140 | kΩ |

| R <sub>pd(int)</sub> | 内部プルダウン抵抗              | P ポート                          |                                                                                                                                                                                                    | 70            | 100  | 140 |    |

|                      |                        | SCLK                           |                                                                                                                                                                                                    | 70            | 100  | 140 | kΩ |

| C <sub>I</sub>       | 入力ピン容量                 | SCLK                           | V <sub>I</sub> = V <sub>CC</sub> または GND                                                                                                                                                           | 1.65V ~ 5.5V  | 8    | pF  |    |

|                      |                        | SDI                            |                                                                                                                                                                                                    |               | 8    | pF  |    |

|                      |                        | CS                             |                                                                                                                                                                                                    |               | 8    | pF  |    |

|                      |                        | RESET                          |                                                                                                                                                                                                    |               | 8    | pF  |    |

| C <sub>IO</sub>      | 入力 / 出力ピンの容量           | P ポート                          | V <sub>IO</sub> = V <sub>CC</sub> または GND                                                                                                                                                          | 1.65V ~ 5.5V  |      | 8.5 | pF |

(1) 各 I/O は、外部で最大 10mA に制限する必要があります

## 5.6 タイミング要件

外気温度範囲での動作時 (特に記述がない限り)

|                   |                                                                                 | 最小値                                           | 最大値  | 単位 |

|-------------------|---------------------------------------------------------------------------------|-----------------------------------------------|------|----|

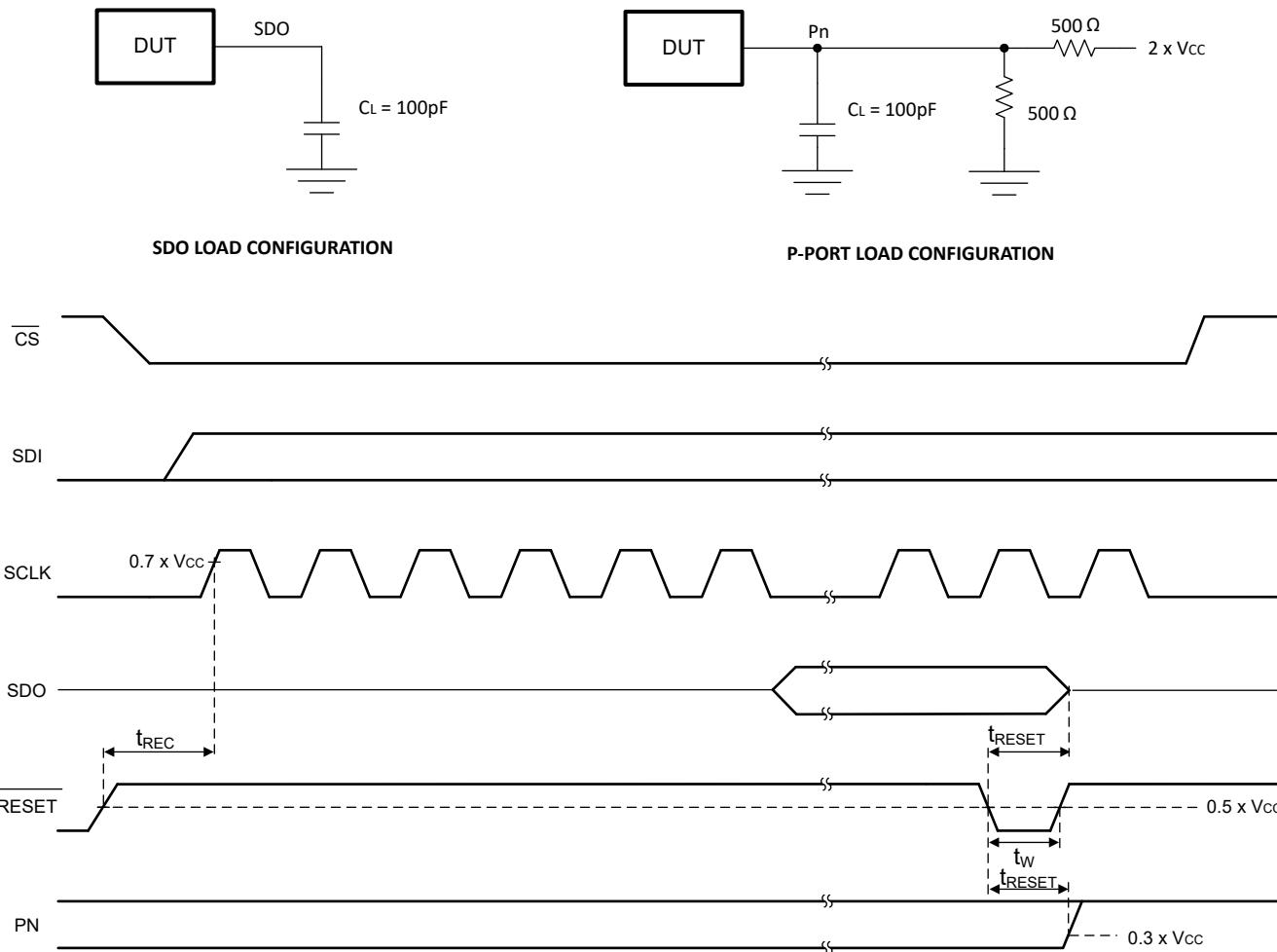

| <b>RESET</b>      |                                                                                 |                                               |      |    |

| $t_w$             | リセットパルス幅、SDO $C_{LOAD} = 100\text{pF}$ (図 6-1)                                  | 100                                           |      | ns |

| $t_{REC}$         | リセット復帰時間、SDO $C_{LOAD} = 100\text{pF}$ (図 6-1)                                  |                                               | 100  | ns |

| $t_{RESET}$       | リセットまでの時間、SDO $C_{LOAD} = 100\text{pF}$ (図 6-1)                                 |                                               | 80   | ns |

| <b>パワーオン リセット</b> |                                                                                 |                                               |      |    |

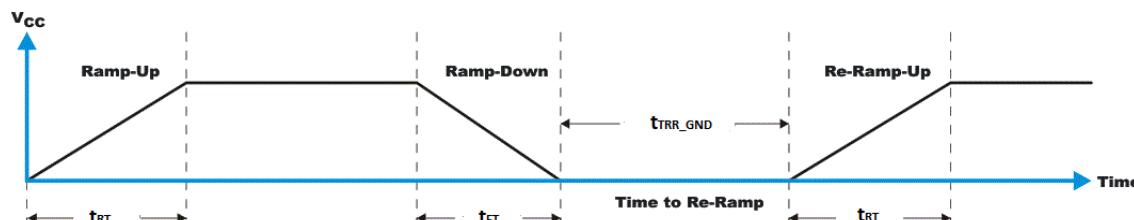

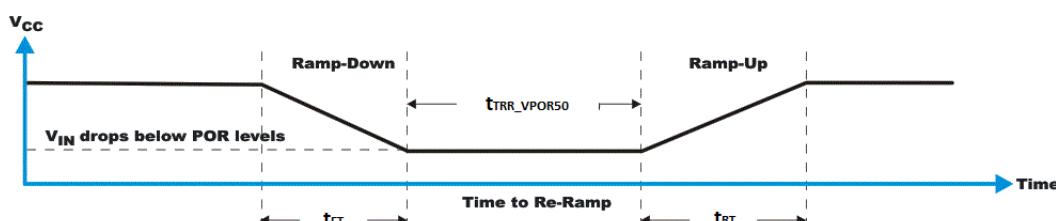

| $t_{FT}$          | 落下率 (図 8-3) (図 8-4)                                                             | 0.1                                           | 2000 | ms |

| $t_{RT}$          | 立ち上がりレート (図 8-3) (図 8-4)                                                        | 0.1                                           | 2000 | ms |

| $t_{TRR_GND}$     | 再ランプ時間 ( $V_{CC}$ が GND まで低下する場合) (図 8-3)                                       | 1                                             |      | μs |

| $t_{TRR_POR0}$    | 再ランプ時間 ( $V_{CC}$ が $V_{POR\_MIN} - 50\text{mV}$ まで低下する場合) (図 8-4)              | 40                                            |      | μs |

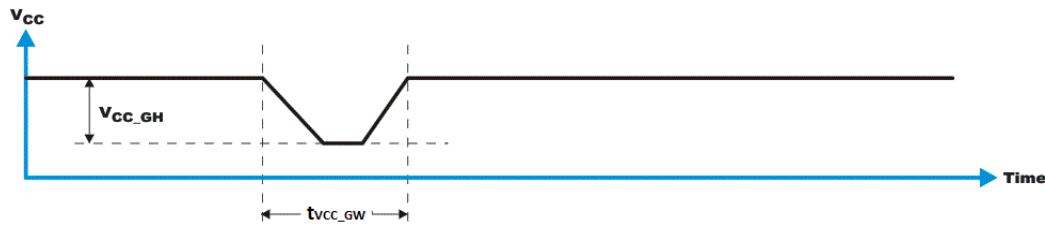

| $V_{CC\_GH}$      | $V_{CC}$ にグリッチが発生することはあるが、 $t_{VCC\_GW} = 1\mu\text{s}$ のときに機能が途絶しないレベル (図 8-5) |                                               | 1.2  | V  |

| $t_{VCC\_GW}$     | $V_{CC\_GH} = 0.5 \times V_{CC}$ のときに、機能が途絶しないグリッチ幅 (図 8-5)                     |                                               | 10   | μs |

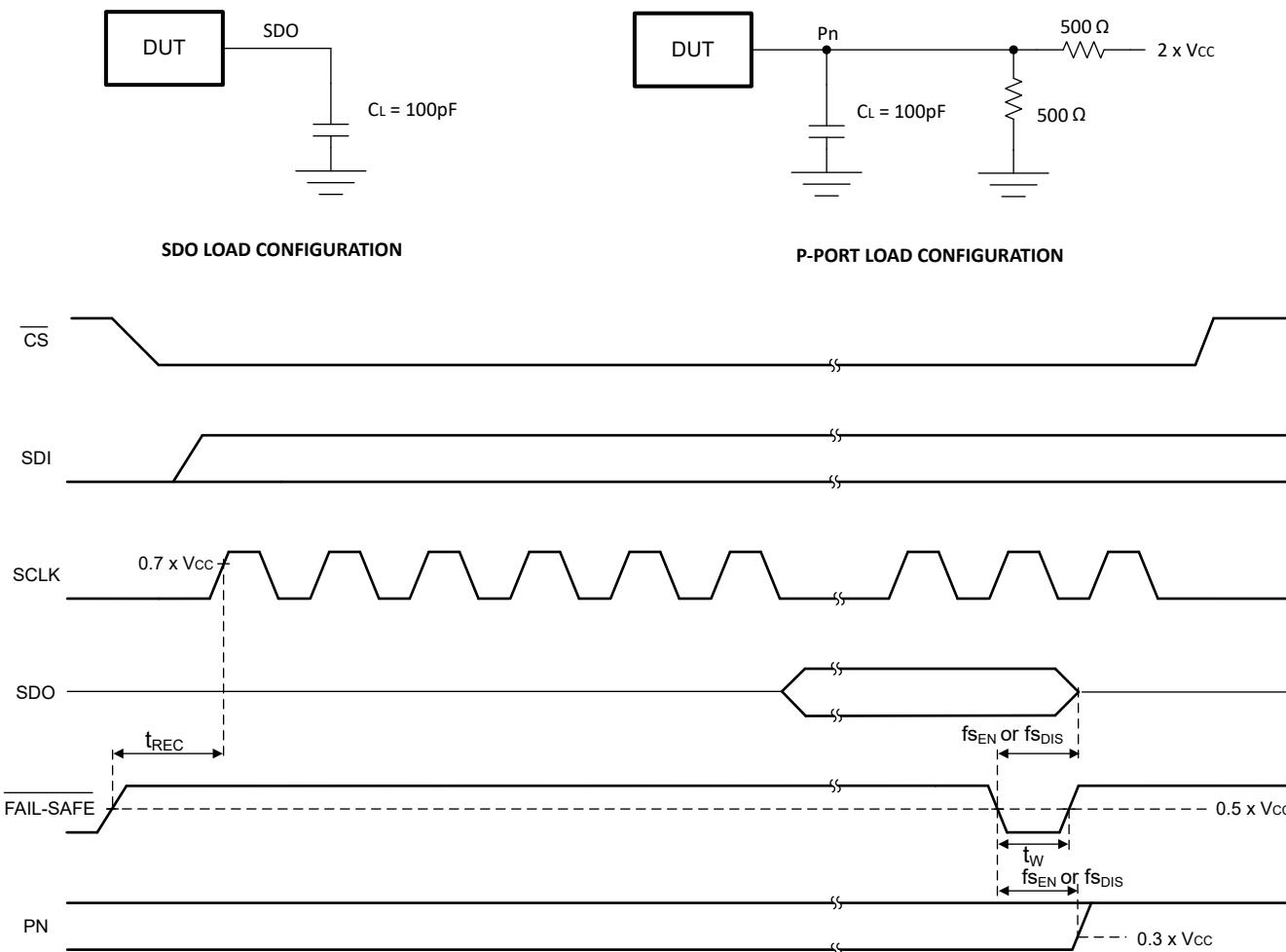

| <b>フェイルセーフ IO</b> |                                                                                 |                                               |      |    |

| $f_{SEN}$         | フェイルセーフ IO 有効時間 (100pF 負荷) (図 6-2)                                              | 通常モードでは出力 High、フェイルセーフモードでは出力 Low             | 100  | ns |

|                   |                                                                                 | 通常モードでは出力 Low、フェイルセーフモードでは出力 high             | 100  | ns |

|                   |                                                                                 | 通常モードでは出力 high、フェイルセーフモードでは入力 (500Ω のプルダウン負荷) | 70   | ns |

|                   |                                                                                 | 通常モードでは出力 Low、フェイルセーフモードでは入力 (500Ω のプルダウン負荷)  | 70   | ns |

| $f_{DIS}$         | フェイルセーフ IO 無効時間 (100pF 負荷) (図 6-2)                                              | 通常モードでは出力 High、フェイルセーフモードでは出力 Low             | 100  | ns |

|                   |                                                                                 | 通常モードでは出力 Low、フェイルセーフモードでは出力 high             | 100  | ns |

|                   |                                                                                 | 通常モードでは入力、フェイルセーフモードでは出力 High (500Ω プルダウン負荷)  | 110  | ns |

|                   |                                                                                 | 通常モードでは入力、フェイルセーフモードでは出力 Low (500Ω プルダウン負荷)   | 90   | ns |

| <b>デジタル IO</b>    |                                                                                 |                                               |      |    |

| $T_{GW}$          | デジタル グリッチ フィルタ幅                                                                 | 70                                            | 230  | ns |

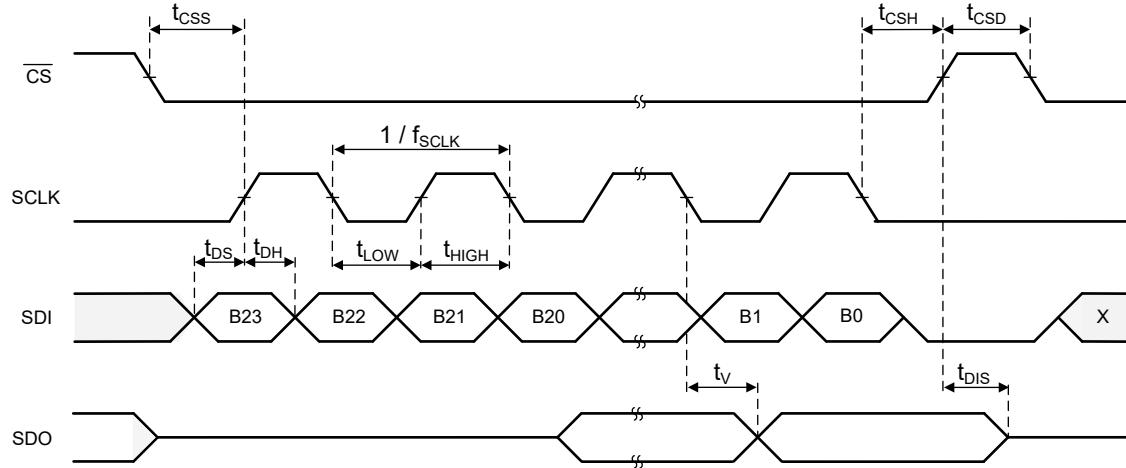

## 5.7 SPI バスのタイミング要件

自由気流での動作温度範囲内、および SDO  $C_{LOAD} = 100\text{pF}$  (特に記述のない限り) (図 6-3 を参照)

|                       |                                                    | 最小値 | 最大値 | 単位  |

|-----------------------|----------------------------------------------------|-----|-----|-----|

| <b>SPI バス - 10MHz</b> |                                                    |     |     |     |

| $t_{SCLK}$            | SPI クロック周波数、 $3.3\text{V} < V_{CC} < 5.5\text{V}$  |     | 10  | MHz |

| $t_{CSS}$             | $\overline{CS}$ から SCLK 立ち上がりまでのセットアップ時間           | 50  |     | ns  |

| $t_{CSH}$             | SCLK から $\overline{CS}$ への立ち下がりデアサートホールド時間         | 50  |     | ns  |

| $t_{CSD}$             | $\overline{CS}$ ディセーブル時間                           | 50  |     | ns  |

| $t_{DS}$              | SDI から SCLK までのセットアップ時間                            | 10  |     | ns  |

| $t_{DH}$              | SDI から SCLK までのホールド時間                              | 10  |     | ns  |

| $t_{LOW}$             | SCLK Low 時間                                        | 45  |     | ns  |

| $t_{HIGH}$            | SCLK High 時間                                       | 45  |     | ns  |

| $t_V(\text{SDO})$     | SDO の有効時間                                          |     | 27  | ns  |

| $t_{DIS}(\text{SDO})$ | SDO ディセーブル時間                                       |     | 50  | ns  |

| <b>SPI バス - 5MHz</b>  |                                                    |     |     |     |

| $t_{SCLK}$            | SPI クロック周波数、 $1.65\text{V} < V_{CC} < 5.5\text{V}$ |     | 5   | MHz |

| $t_{CSS}$             | $\overline{CS}$ から SCLK 立ち上がりまでのセットアップ時間           | 50  |     | ns  |

| $t_{CSH}$             | SCLK から $\overline{CS}$ への立ち下がりデアサートホールド時間         | 100 |     | ns  |

| $t_{CSD}$             | $\overline{CS}$ ディセーブル時間                           | 100 |     | ns  |

| $t_{DS}$              | SDI から SCLK までのセットアップ時間                            | 10  |     | ns  |

| $t_{DH}$              | SDI から SCLK までのホールド時間                              | 10  |     | ns  |

| $t_{LOW}$             | SCLK Low 時間                                        | 90  |     | ns  |

| $t_{HIGH}$            | SCLK High 時間                                       | 90  |     | ns  |

| $t_V(\text{SDO})$     | SDO の有効時間                                          |     | 54  | ns  |

| $t_{DIS}(\text{SDO})$ | SDO ディセーブル時間                                       |     | 100 | ns  |

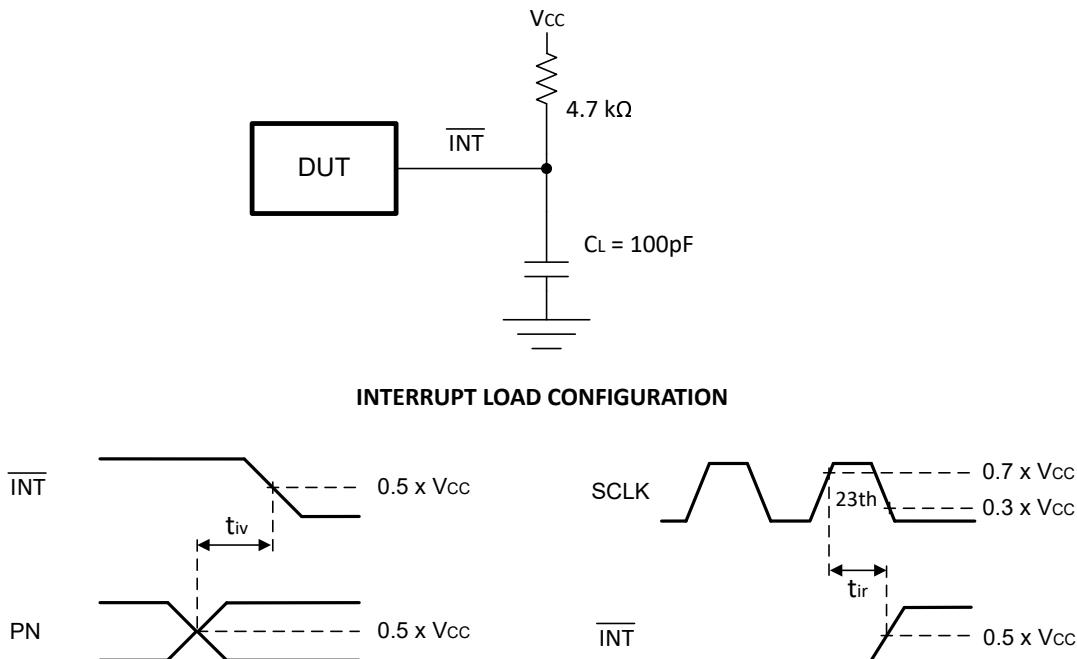

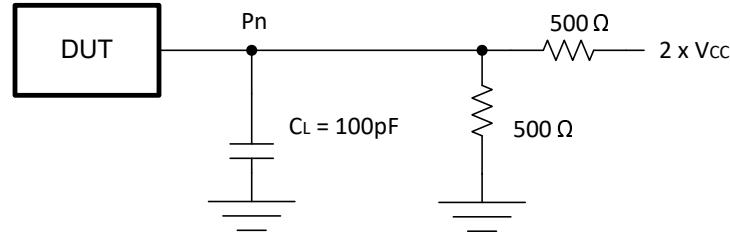

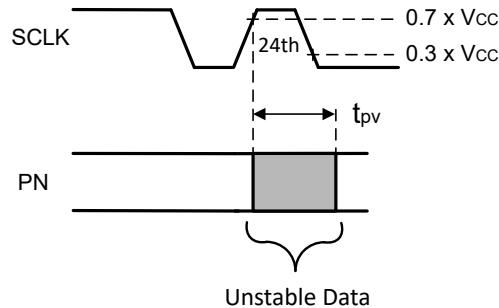

## 5.8 スイッチング特性

外気温度範囲での動作時 (特に記述がない限り)

| パラメータ    | 始点 (入力)                                                                             | 終点 (出力) | 最小値   | 標準値 | 最大値 | 単位 |

|----------|-------------------------------------------------------------------------------------|---------|-------|-----|-----|----|

| $t_{IV}$ | 割り込み有効時間、INT $C_{LOAD} = 100\text{pF}$ 、 $R_{PU} = 4.7\text{k}\Omega$ (図 6-4)       | P ポート   | INT   |     | 0.2 | μs |

| $t_{Ir}$ | 割り込みリセット遅延有効時間、INT $C_{LOAD} = 100\text{pF}$ 、 $R_{PU} = 4.7\text{k}\Omega$ (図 6-4) | SCLK    | INT   |     | 0.4 | μs |

| $t_{PV}$ | 出力データ有効時間、SDO $C_{LOAD} = 100\text{pF}$ (図 6-5)                                     | SCLK    | P ポート |     | 100 | ns |

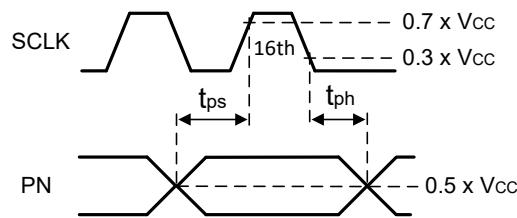

| $t_{PS}$ | 入力データ セットアップ時間、SDO $C_{LOAD} = 100\text{pF}$ (図 6-5)                                | P ポート   | SCLK  | 26  |     | ns |

| $t_{PH}$ | 入力データ ホールド時間、SDO $C_{LOAD} = 100\text{pF}$ (図 6-5)                                  | SCLK    | P ポート | 2.5 |     | ns |

## 6 パラメータ測定情報

図 6-1. リセット負荷構成

- A. 1.  $C_L$  にはプローブと治具の容量が含まれます。

- 2. すべての入力は、以下の特性を持つジェネレータから供給されます:  $PRR \leq 10\text{MHz}$ ,  $Z_0 = 50\Omega$ ,  $tr/tf \leq 10\text{ns}$ 。

- 3. すべてのパラメータと波形が、すべてのデバイスに適用できるわけではありません。

図 6-2. フェイルセーフ負荷構成

- A.

1.  $C_L$  にはプローブと治具の容量が含まれます。

2. すべての入力は、以下の特性を持つジェネレータから供給されます:  $PRR \leq 10\text{MHz}$ ,  $Z_0 = 50\Omega$ ,  $tr/tf \leq 10\text{ns}$ 。

3. フェイルセーフピンは、RESETピンとの共有ピンです。

4. すべてのパラメータと波形が、すべてのデバイスに適用できるわけではありません。

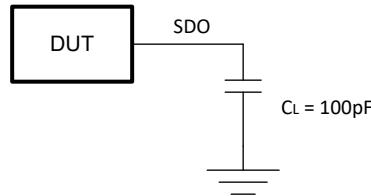

SDO LOAD CONFIGURATION

図 6-3. SPI タイミング図 - 入力

A.  $C_L$  にはプローブと治具の容量が含まれます。

図 6-4. 割り込み負荷構成

- A. 1.  $C_L$  にはプローブと治具の容量が含まれます。

- 2. すべての入力は、以下の特性を持つジェネレータから供給されます:  $PRR \leq 10\text{MHz}$ ,  $Z_0 = 50\Omega$ ,  $t_r/t_f \leq 10\text{ns}$ 。

**P-PORT LOAD CONFIGURATION**

**WRITE MODE ( $\overline{R}/\overline{W} = 0$ )**

**READ MODE ( $\overline{R}/\overline{W} = 1$ )**

**図 6-5. P ポートの負荷構成およびタイミング波形**

- A. 1.  $C_L$  にはプローブと治具の容量が含まれます。

2.  $t_{pv}$  は、SCLK で  $0.7 \times V_{CC}$  から 50% の I/O (On) 出力まで測定されます。

3. すべての入力は、以下の特性を持つジエネレータから供給されます: PRR  $\leq 10MHz$ ,  $Z_o = 50\Omega$ ,  $t_r/t_f \leq 10ns$ 。

## 7 詳細説明

### 7.1 概要

TXE81XX-Q1 のデジタルコアは 24 ビットのレジスタで構成されており、ユーザーは I/O ポートの特定を構成することができます。電源オン時、またはリセット後に、I/O は入力として構成されます。ただし、方向構成レジスタに書き込むことにより、システムコントローラは I/O を入力または出力のどちらにも構成することができます。各入力または出力のデータは、対応する入力ポートレジスタまたは出力ポートレジスタに保持されます。入力ポートレジスタの極性は、極性反転レジスタで反転できます。ソフトウェアリセットレジスタを除くすべてのレジスタは、システムコントローラによって読み取り可能です。

TXE81XX-Q1 には、I/O ポートの強化に特化した構成可能な I/O 機能が搭載されています。構成可能な I/O 機能とレジスタには、プルアップ抵抗とプルダウン抵抗のイネーブルとディセーブル、ラッチ可能な入力、マスク可能な割り込み、割り込みステータスレジスタ、個別のプログラム可能なオープンドレインまたはプッシュプル出力が含まれています。これらの構成レジスタにより柔軟性が向上するため、I/O は強化され、ユーザーは消費電力やスピードの設計を最適化できるようになります。

デバイスの他の機能には、入力ポートの状態が変化するたびに **INT** ピンで発生する割り込みがあります。デバイスをデフォルトの状態にリセットするには、**RESET** ピンに Low 論理レベルを印加するか、ソフトウェアリセットコマンドを送信するか、またはデバイスの電源を一度切ってパワーオンリセットを行います。TXE81XX-Q1 のオープンドレイン割り込み (**INT**) 出力は、いずれかの入力状態が対応する **Input Port** レジスタの状態と異なる場合にアクティブになって、入力状態が変化したことをシステムコントローラに示すために使用されます。**INT** ピンは、プロセッサの割り込み入力に接続することができます。このラインで割り込み信号を送信することにより、デバイスは SPI バスで通信しなくとも、リモート I/O ポートに受信データがあるかどうかをプロセッサに通知することができます。デバイスは、シンプルなターゲットデバイスとして機能します。

タイムアウト時またはその他の不正な動作時に、**RESET** 入力ピンに low をアサートするか、または **V<sub>CC</sub>** ピンへの電源を一度切ってパワーオンリセット (POR) することにより、システムコントローラはデバイスをリセットします。リセットによりレジスタはデフォルト状態に戻り、SPI ステートマシンが初期化されます。**RESET** 機能でも POR でも、同じようにリセット / 初期化を行えますが、**RESET** 機能はデバイスの電源をオフにする必要はありません。

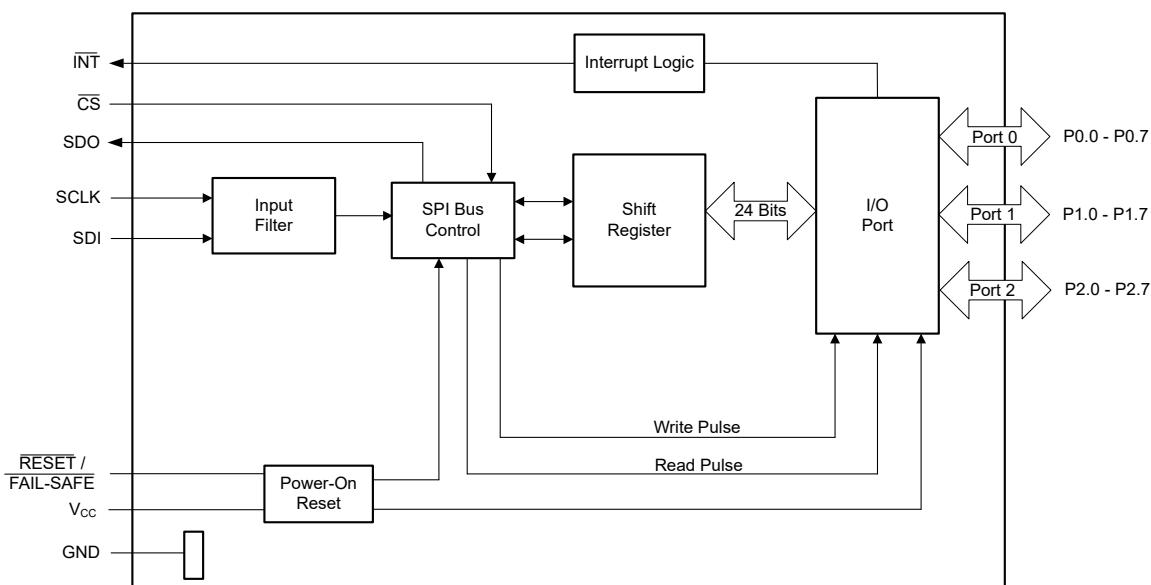

### 7.2 機能ブロック図

A. すべての I/O は、リセット時に入力に設定されます。

図 7-1. ロジック図

A. 電源オンまたはリセット時に、すべてのレジスタがデフォルト値に戻ります。

**図 7-2. P0.0 から P2.7 の概略回路図**

## 7.3 機能説明

### 7.3.1 I/O ポート

I/O が入力として構成されている場合、FET Q1 と Q2 はオフになり (図 7-2 を参照)、高インピーダンス入力が生成されます。

I/O が出力として構成されている場合、Q1 または Q2 は出力ポートレジスタの状態に応じてイネーブルになります。この場合、I/O ピンと電源または GND の間に低インピーダンスのパスがあります。この I/O ピンに印加される外部電圧は、適切に動作させるために推奨レベルを超えないようにする必要があります。

### 7.3.2 割り込み出力 (INT)

TXE81XX-Q1 デバイスは、入力 I/O のいずれかの立ち上がりエッジまたは立ち下がりエッジで割り込みを生成します (その I/O の割り込みがマスクされていない場合)。入力状態が変化すると、対応する割り込みフラグビットが設定され、INT 出力がアサートされます。

そのポートのすべての割り込みフラグビットが 0 にクリアされるまで、割り込みはアクティブのまま維持されます。割り込みフラグステータスレジスタは、割り込みを自動的にクリアしません。

出力として構成された I/O は、割り込みを生成しません。実際のピンレベルが、保存されている入力ポートレジスタ値と一致しない場合、ピンを出力から入力に切り替えると、障害割り込みが発生する可能性があります。

I/O ポートがあらかじめ入力状態にあり、出力に切り替わる割り込みを検出しても、割り込みフラグはクリアされません。割り込みピンのみがマスクされます。ポートが入力として再構成されると、割り込みは元に戻ります。

INT ピンはオープンドレインであり、割り込み機能を使用するには V<sub>CC</sub> への外部プルアップ抵抗が必要です。それ以外の場合は、フローティングのままにできます。

以下の条件では、割り込みステータスビットがクリアされ、INT ピンがデアサートされます。

- **RESET** ピンからのハードウェアリセット- POR が割り込みをアサートする際、割り込みが一時的にデアサートされます

- フェイルセーフ モードに移行 - 割り込みは無効化およびデアサートされます

- 割り込みフラグ ステータスレジスタの読み取り

- 割り込みマスク レジスタで対応するビットを 1 に設定

TXE81XX-Q1 には 4 種類の割り込みがあります。

1. **スマート割り込み** - スマート割り込みは、I/O ポートレベルでスマート割り込みレジスタの対応するポートビットを設定することでイネーブルまたはディセーブルになります。スマート割り込み(対応するレジスタビットを 0 とする)がイネーブルで、割り込みが生成されると、I/O 状態が初期ロジック状態に戻るか、割り込みフラグ ステータスレジスタを読み取った場合、割り込みがクリアされます。たとえば、入力ポートレジスタを読み取った場合や、I/O 状態が初期状態に戻った場合、割り込みフラグ ステータスレジスタで読み取り動作がない場合でも、割り込みはクリアされます。各種の割り込みクリアシナリオについては、表 7-1 を参照してください。スマート割り込みがイネーブルの場合、入力 IO トグル周波数は 50ns 超である必要があります。そうしないと、割り込みクリアが見逃される可能性があります。これを回避するには、入力グリッチ フィルタイネーブルレジスタでデジタル グリッチ フィルタをイネーブルにします。

**表 7-1. スマート割り込み用の割り込みフラグ クリア シナリオ**

| スマート割り込み | I/O 入力が変化したときの CS 状態 | 割り込みフラグ クリア                                                                                                                                                                                      |

|----------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 無効       | CS = High            | CS を Low、SPI が割り込みフラグ ステータスレジスタを読み取り                                                                                                                                                             |

| 無効       | CS = Low             | 割り込みフラグ ステータスレジスタの読み取り                                                                                                                                                                           |

| イネーブル    | CS = High            | <ul style="list-style-type: none"> <li>a. CS を Low、SPI が入力ポートレジスタを読み取り</li> <li>b. I/O 状態が初期状態に戻ります</li> <li>c. CS を Low、SPI が割り込みフラグ ステータスレジスタを読み取り</li> </ul>                                  |

| イネーブル    | CS = Low             | <ul style="list-style-type: none"> <li>a. 入力ポートレジスタ読み取りの場合または I/O 状態が初期状態に戻った場合、割り込みフラグは直ちにクリアされません。CS が High になり、30ns を超えて保持されると、割り込みフラグがクリアされます。</li> <li>b. 割り込みフラグ ステータスレジスタの読み取り</li> </ul> |

2. **通常の割り込み** - スマート割り込みがディセーブル(対応するレジスタビットが 1)の場合、I/O 状態を初期ロジック状態に戻すと、割り込みをクリアできず、割り込みフラグ ステータスレジスタを読み取る場合にのみ、割り込みがクリアされます。

3. **POR 割り込み** - 各 POR 回復のフォルトステータスレジスタに POR フォルトビットが設定され、割り込みも生成されます。割り込みは、フォルトステータスレジスタが読み取られたときにのみクリアされます。

4. **フェイルセーフ冗長性障害割り込み** - フェイルセーフ冗長性チェックがイネーブルの場合、およびフェイルセーフ冗長性チェック エラーが発生した場合、フォルトステータスレジスタでフェイルセーフ同期フォルトビットが設定されます。これにより、割り込みも生成されます。割り込みは、フォルトステータスレジスタが読み取られたときにのみクリアされます。

### 割り込みマスク

すべての入力 I/O からの割り込みは、デフォルトではマスクされていません。割り込みをマスクするには、割り込みマスクレジスタで対応する I/O ビットを設定する必要があります。POR 回復によって生成された割り込みはマスクできません。

入力 I/O の状態が変化し、割り込みマスク レジスタの対応ビットが 1 に設定されると、割り込みはマスクされ、INT ピンはアサートされません。割り込みフラグ ステータス レジスタの対応ビットも 0 のままになり、割り込みマスク ビットによってブロックされます。

フェイルセーフ冗長チェック イネーブル ビットが 0 の場合、フェイルセーフ冗長性チェックが失敗したことによって生成される割り込みはディセーブルになります。

マルチ ポートコマンドを使用すると、同時に複数のポートを割り込みマスク用に構成できます。

### 7.3.3 リセット入力(RESET)

RESET 入力をアサートして、V<sub>CC</sub> 電源を動作レベルに保持しながら、システムを初期化することができます。リセットを行うには、t<sub>W</sub> の最短時間の間、RESET ピンを Low に保持します。TXE81XX-Q1 のレジスタと SPI のステートマシンは、RESET が Low に設定されると、デフォルト状態に変更されます。RESET が High に設定されると、P ポートの I/O レベルは外部から、またはコントローラを使用して変更できます。アクティブ接続が使用されない場合、この入力には V<sub>CC</sub> へのプルアップ抵抗が必要です。RESET がトグル切り替えされると、Input Port レジスタは GPIO ピンの状態を反映して更新されます。

### 7.3.4 フェイルセーフモード

SPI コントローラは、この機能を有効にし、ピンの機能をリセットからフェイルセーフに変更するために、フェイルセーフ有効化レジスタをプログラムすることで、TXE81XX-Q1 をフェイルセーフ状態に設定するオプションを持っています。

このレジスタは、POR イベントまたはその他の故障シナリオ中にクリアされる可能性があります。SPI コントローラへの割り込みを生成する故障シナリオがある場合、SPI コントローラは毎回このレジスタを書き換える必要があります。割り込みが生成されると、SPI コントローラは故障ステータス レジスタを読み取って割り込みの原因を把握できます。

TXE81XX-Q1 をフェイルセーフ モードに設定するには、フェイルセーフ イネーブル レジスタのビット 0 を 1 にする必要があります。

冗長性を確保するには、2 つのデバイス構成レジスタに書き込んで I/O 構成をプログラムする必要があります。これらのレジスタのいずれかが破損し、内容が一致しない場合は、割り込みが発生します。

たとえば、フェイルセーフ モードで I/O ピン P0.1 を出力し、High に設定する場合、フェイルセーフ モードを構成するシーケンスは次のようになります。

1. フェイルセーフイネーブル レジスタ 1 のビット 0 (アドレス: 0x1200) を 1 として構成

2. フェイルセーフイネーブル レジスタ 2 のビット 0 (アドレス: 0x1300) を 1 として構成

3. フェイルセーフ方向構成レジスタ 1 のポート 0 のビット 1 (P0.1) (アドレス: 0x1400) を 1 に設定

4. フェイルセーフ方向構成レジスタ 2 のポート 0 のビット 1 (P0.1) (アドレス: 0x1500) を 1 に設定

5. フェイルセーフ出力レジスタ 1 のポート 0 のビット 1 (P0.1) (アドレス: 0x1600) を 1 に設定

6. フェイルセーフ出力レジスタ 2 のポート 0 のビット 1 (P0.1) (アドレス: 0x1700) を 1 に設定

7. フェイルセーフ冗長性チェック レジスタのビット 0 (アドレス: 0x1800) を 1 に設定

8. RESET/FAIL-SAFE ピンをアサート

### 7.3.5 ソフトウェアリセット呼び出し

ソフトウェアリセット呼び出しは、SPI バス上のコントローラから送信されるコマンドであり、コマンドをサポートする SPI ターゲットデバイスに電源投入時のデフォルト状態にリセットするように指示します。

TXE8116-Q1/TXE8124-Q1 デバイスは、通信に 24 ビットの SPI フレームを使用します。たとえば、ソフトウェアリセットコマンドを介してレジスタリセットをトリガするには、コントローラは SPI フレームを次のように構成できます。

| B23 | B22 | B21 | B20 | B19 | B18 | B17 | B16 | B15 | B14 | B13 | B12 | B11 | B10 | B9 | B8 | B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| 0   | 0   | 0   | 1   | 1   | 0   | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  |    |

コントローラ側でのこのコマンドのサンプルコードは次のとおりです。

```

// SPI レジスタアドレスを定義する

#define REGISTER_CMD_BYTE 0x1A // リセット レジスタのレジスタコマンド バイト

#define DATA_BITS 0x2 // レジスタリセットをトリガするには、B1 を 1、B0 を 0 に設定します。

#define READ_WRITE_BIT 0 // 書き込み操作の場合は 0、読み取り操作の場合は 1

// 24 ビット SPI フレームを I/O エクスパンダに送信する関数(MSB ファースト)

void SPI_Send(uint32_t data) {

// ハードウェア SPI ペリフェラルを使用して 24 ビットデータをビットごとに送信 (MSB ファースト)

for (int i = 23; i >= 0; i--) {

SPI_Transmit((data >> i) & 0x01); // MSB を最初にシフトアウト

}

}

// SPI I/O エクスパンダにソフトウェアリセット コマンドを送信する機能

void SPI_Software_Reset(void) {

uint32_t frame = 0;

// 読み取り書き込みビット(ビット 23)を設定する

frame |= (READ_WRITE_BIT << 23);

// レジスタ アドレスを設定する(ビット 20~16)

frame |= (REGISTER_CMD_BYTE << 16);

// データビット(ビット 7-0)を設定

frame |= (DATA_BITS & 0xFF); // 下位 8 ビットのみを使用するようにする

// CS を low にプルするとターゲット デバイスが選択される

CS_LOW();

// 構築した SPI フレームを送信する(MSB ファースト)

SPI_Send(frame);

// 送信後にデバイスの選択を解除するには CS を High にプルする

CS_HIGH();

}

```

### 7.3.6 パースト モード

パースト モード読み取りトランザクションでは、初期アドレスはコントローラ デバイスによって指定され、周辺装置に送信されます。後続のアクセスでは、アドレスは次のポートに対応する次の有効なアドレス(2 番目のアドレス バイト)に自動的にインクリメントされます。この自動アドレス インクリメントは、CS がアクティブ low のままで、SCLK パルスが周辺デバイスによって受信される限り継続されます。

バースト モード トランザクションは、指定された機能 (最初のアドレス バイト) の最後のポート アドレスに到達するまで、有効なポート アドレスごとにアドレスを自動的に進めながら順次続行されます。最後の有効なポート アドレスに到達すると、周辺機器は SDO からすべて 0 を出力し、有効なデータ シーケンスの終了を示します。

バースト モードでは、特定の機能の最後のポート アドレスに到達した後、新しい機能アドレスに自動的に増加しないことに注意することが重要です。さらなるトランザクションが必要な場合、コントローラは新しい機能アドレスを手動で指定する必要があります。

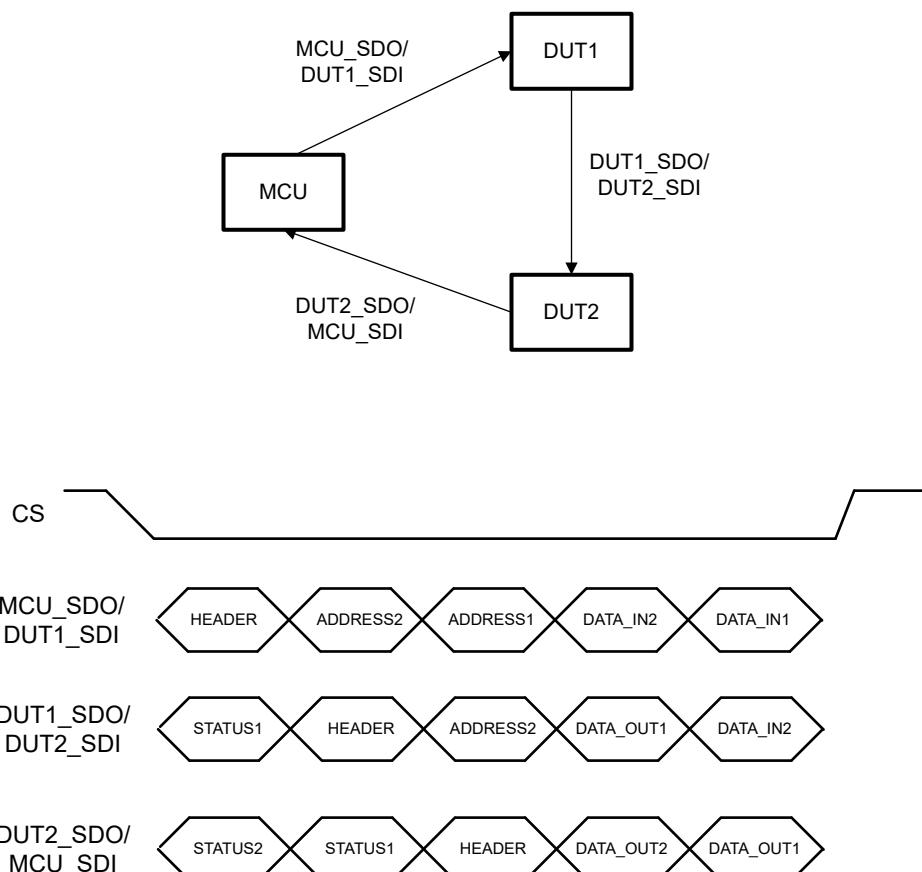

### 7.3.7 デイジーチェーン

複数の TXE81XX-Q1 デバイスをデイジーチェーン構成で接続すると、サポートされる I/O ポートの数を拡張できます。コントローラはまず、チェーン内で最も遠いデバイス (コントローラの SDI から最も遠く、コントローラの SDO に最も近いデバイス) のレジスタ アドレスを送信します。ヘッダに続いて、このレジスタ アドレスが最初に送信され、最も遠いデバイスとの通信が開始されます。

通信がチェーンに沿って進むにつれて、後続の各デバイスのレジスタ アドレスが順番に送信されます。最後に、コントローラに最も近いデバイス (コントローラに最も近い SDI に接続されている) のレジスタ アドレスが最後に送信されます。これにより、データがチェーン内を順番に流れ、各デバイスがデータを受信して次のデバイスに転送するようになります。

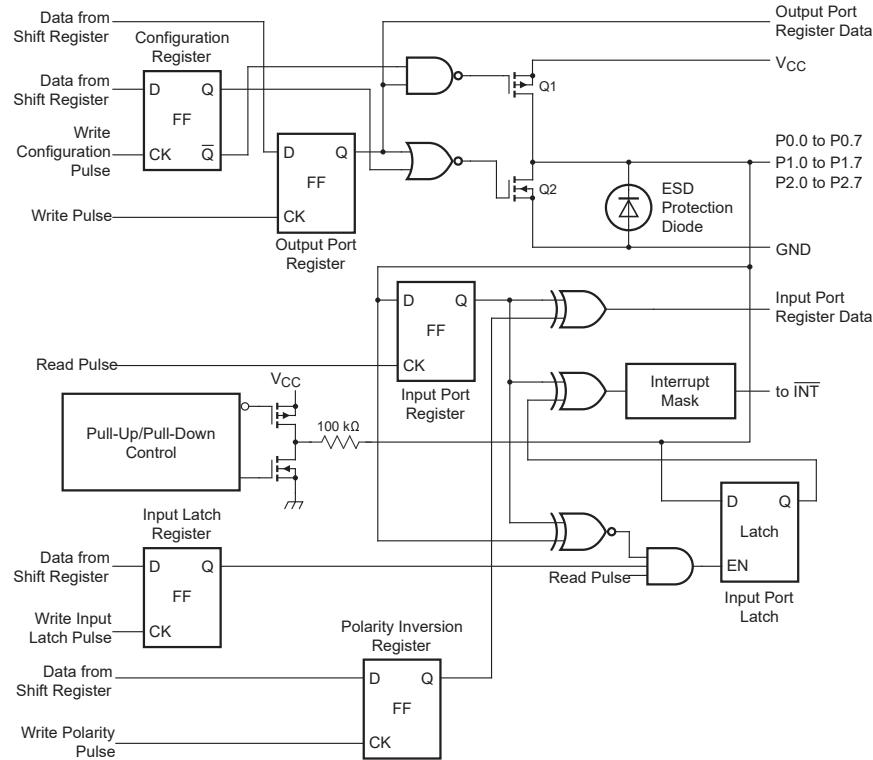

各 SPI トランザクションは、次の 4 種類のセグメントで構成されます。ステータス、ヘッダ、アドレス (レジスタ アドレス)、およびデータは以下に示すとおりです。ヘッダはオプションのセグメントであり、デイジーチェーンが有効な場合にのみ存在します。

SDI 上の SPI データ入力データは、SCLK の low エッジから high エッジでサンプリングされます。SDO 上の SPI 出力データは、SCLK の high エッジから low エッジに変更されます。

デイジーチェーントランザクションのフレームについては、図 7-3 を参照してください。最終デバイスに到達するまで、同じシーケンスがチェーン全体にわたって繰り返されます。

図 7-3. SPI デイジーチェーン データ フレーム

#### ヘッダ セグメント

ヘッダ セグメントのビット 15 と 14 はヘッダ ID です。これは、デバイス コントローラーがヘッダ セグメントが受信されていることを検出するために使用されます。

ビット [15:14]: ヘッダ ID。0 と 1 はこれがヘッダ セグメントであることを示します。

ビット [13]: 予約済み。

ビット [12:0]: ヘッダ セグメントのビット 12 ~ 0 は、デイジーチェーン内のデバイスの数を決定します。

#### アドレス セグメント (レジスタ アドレス)

ビット 15 は SPI 動作モードを示します (1 = 読み取り操作、0 = 書き込み操作)。レジスタ アドレスについては、図 7-5 の最初のバイトと 2 番目のバイトを参照してください。

#### ステータス セグメント

ステータス セグメントは 16 ビットで、データ形式は次のとおりです。

ビット [15:14]: ビット 15 と 14 は両方とも 1 であり、これがステータス セグメントであることを示します。

ビット [13:8]: 故障ステータス レジスタのビット 5 ~ 0 については、[故障ステータス レジスタ](#) を参照してください。

ビット [7:0]: ビット 7 ~ 0 は 0 です。

たとえば、MCU と 2 つの SPI 周辺デバイスに SPI デイジーチェーン構成がある場合、デバイス間の図とデータ形式については、図 7-4 を参照してください。

図 7-4. SPI デイジーチェーンの図

最も遠いデバイス (MCU の SDI から最も遠い/MCU の SDO に最も近い) のレジスタ アドレスは、ヘッダの後に MCU によって最初に送信され、最も近いデバイス (SDI に最も近い) のアドレスは MCU によって最後に送信されます。

### 7.3.8 マルチポート

2番目のバイトの LSB はマルチポート機能を有効にします。このビットが 1 の場合、データバイトの各ビットは個別のポートを参照します。したがって、LSB ビット B0 は P0 ポート、B1 は P1 ポート、B2 は P2 ポートを参照します。マルチポートプログラミングを使用すると、特定のポートのすべての I/O は同じ構成になります。

たとえば、P1 のすべての I/O を 1 に設定するには、コントローラは GPIO 方向を出力として設定し、P1 ポートを設定します。

コントローラ側でのこのコマンドのサンプルコードは次のとおりです。

// SPI レジスタアドレスを定義する

```

#define REGISTER_CMD_BYTE 0x4 // 方向構成レジスタのレジスタコマンドバイト

#define REGISTER_CMD_OUTPUT 0x3 // 出力ポートレジスタのレジスタコマンドバイト

#define DATA_BITS 0x2 // B1 を 1、B0 を 0 に設定して P1 ポートを設定します

#define READ_WRITE_BIT 0 // 書き込み操作の場合は 0、読み取り操作の場合は 1

```

// 24ビット SPI フレームを I/O エクスパンダに送信する関数(MSB ファースト)

```

void SPI_Send(uint32_t data) {

// ハードウェア SPI ペリフェラルを使用して 24 ビットデータをビットごとに送信 (MSB ファースト)

for (int i = 23; i >= 0; i--) {

SPI_Transmit((data >> i) & 0x01); // MSB を最初にシフトアウト

}

}

```

// SPI I/O エクスパンダにマルチポートコマンドを送信する機能

```

void SPI_Multi_Port_Dir(void) {

uint32_t frame = 0;

// 読み取り書き込みビット(ビット 23)を設定する

frame |= (READ_WRITE_BIT << 23);

// レジスタアドレスを設定する(ビット 20~16)

frame |= (REGISTER_CMD_BYTE << 16);

// データビット(ビット 7-0)を設定

frame |= (DATA_BITS & 0xFF); // 下位 8 ビットのみを使用するようにする

// CS を low にプルするとターゲットデバイスが選択される

CS_LOW();

// 構築した SPI フレームを送信する (MSB ファースト)

SPI_Send(frame);

// 送信後にデバイスの選択を解除するには CS を High にプルする

CS_HIGH();

}

```

```

void SPI_Multi_Port_Output(void) {

uint32_t frame = 0;

// 読み取り書き込みビット(ビット23)を設定する

frame |= (READ_WRITE_BIT << 23);

// レジスタアドレスを設定する(ビット20~16)

frame |= (REGISTER_CMD_OUTPUT << 16);

// データビット(ビット7~0)を設定

frame |= (DATA_BITS & 0xFF); // 下位8ビットのみを使用するようにする

// CSをlowにプルするとターゲットデバイスが選択される

CS_LOW();

// 構築したSPIフレームを送信する(MSBファースト)

SPI_Send(frame);

// 送信後にデバイスの選択を解除するにはCSをHighにプルする

CS_HIGH();

}

```

## 7.4 デバイスの機能モード

### 7.4.1 パワーオンリセット

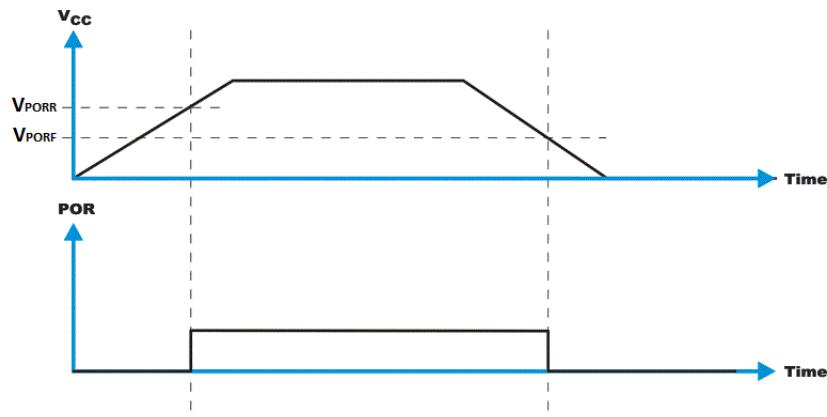

デバイスに0Vから電源が供給され、 $V_{CC}$ に適用されるとき、内部パワーオンリセットにより、電源が $V_{POR}$ に達するまでTXE81XX-Q1はリセット状態に保持されます。その時点でリセット状態が解除され、TXE81XX-Q1レジスタとSPIステートマシンはデフォルト状態に初期化されます。パワーリセットサイクルを行うには、その後で $V_{CC}$ を $V_{PORF}$ 未満まで $t_{TRR\_POR\_50}$ の時間だけ下げてから、再び動作電圧まで戻す必要があります。

## 7.5 プログラミング

### 7.5.1 SPI インターフェイス

TXE81XX-Q1デバイスは、SPIインターフェイスを使用してデバイス構成、動作パラメータを設定し、診断情報を読み取ります。SPIプロトコルは、シリアルクロック(SCLK)、アクティブLOWチップセレクト( $\overline{CS}$ )、シリアルデータ入力(SDI)、シリアルデータ出力(SDO)の3つの入力と1つの出力を使用します。クロックパルスとデータがデバイスに入力される前に、 $\overline{CS}$ をlowに駆動する必要があります。 $\overline{CS}$ がhighの場合、デバイスはSCLKとSDI上のすべてのアクティビティを無視します。

TXE81XX-Q1デバイスは、SPIモード0(CPOL=0,CPHA=0)をサポートしています。アイドル時、クロック(SCLK)はLowになります。データはSCLKの立ち上がりエッジでサンプリングされ、立ち下がりエッジで変更されます。

TXE81XX-Q1では、独立したチップセレクトを備えたSPIバスに加えて、デイジーチェーン構成もサポートされています。複数の周辺機器を直列に接続し、1つのデバイスの出力を次のデバイスの入力に供給することができます。デイジーチェーンは、チェーン全体に必要なCSラインが1つだけなので、 $\overline{CS}$ ラインの数を減らすのに役立ちます。データは、各クロックサイクル中にチェーン内のすべてのデバイスを介して移行されます。

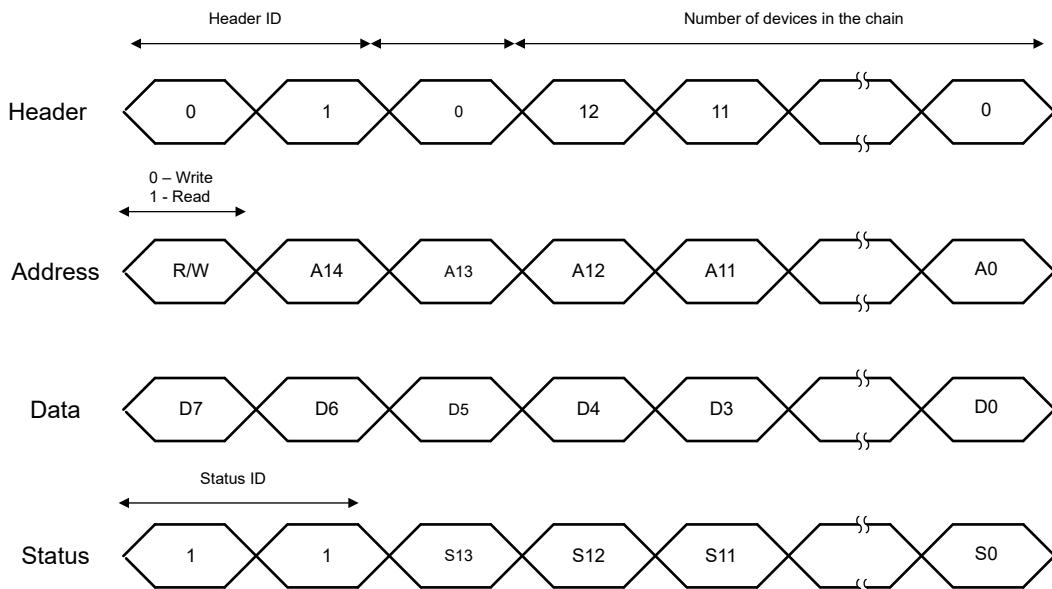

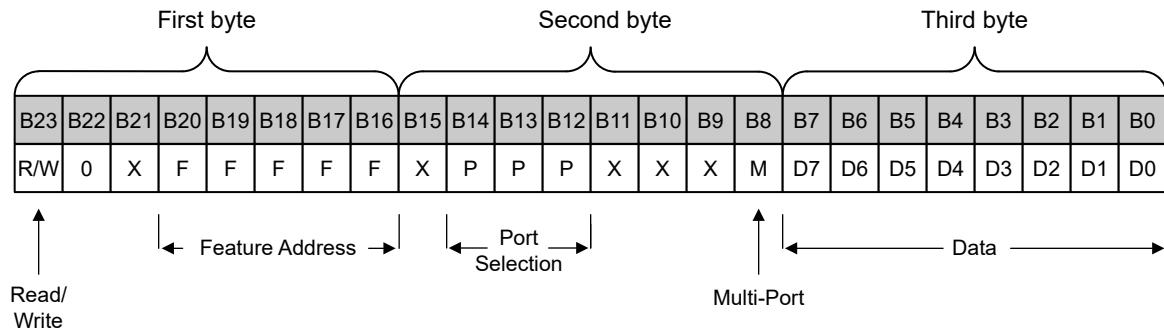

### 7.5.2 SPI データ形式

TXE81XX-Q1のデータ形式を図7-5に示します。

**図 7-5. TXE81XX-Q1 SPI ワード アドレス**

TXE81XX-Q1 SPI ワードの長さは 24 ビットで、24 ビットのデータを MSB ファースト方式でデバイスに移行します。SCLK の立ち上がりエッジの間、SPI データは安定している必要があります。

SDI データ長は少なくとも 24 ビットまたは $[16 + (N \times 8)]$  ビットである必要があります (N は書き込むデータバイト数、 $N \geq 1$ )。SDO 経由でデータ出力を読み取る場合、最初の 16 アドレスビットの後にデータバイトの読み取りが開始されます。

### 7.5.3 書き込み

SPI 書き込み動作は、コントローラ デバイスから周辺デバイスにデータを送信するために使用されます。この動作は SPI バスを介して実行され、コントローラ デバイスがクロック (SCLK) を制御してデータを周辺装置に送信します。SPI 書き込みは、通常、周辺装置の構成、制御コマンドの送信、データの転送に使用されます。

#### SPI 書き込み手順

1.  $\overline{CS}$  を low に駆動します。これにより、内部シフトレジスタが有効になります。

2. 24 ビットのデータを MSB ファースト方式でデバイスに移行します (MSB ビット)。SCLK の立ち上がりエッジの間、データは安定している必要があります。

3. MSB ビットは、書き込み動作であることを示す「0」である必要があります。

4. 16 ビットのステータスが SDO で送信されます。最初の 2 ビットは 2'b11 です (ステータス セグメントであることを示します)。次の 6 ビットは、[故障ステータス レジスタ](#) のビット 5 ~ 0 です。最後の 8 ビットはすべて 0 です。

5. 最後のデータビットが転送された後、転送するデータがない場合は SCLK を low に駆動します。

6. データバイトが SDI に送られると、レジスタの以前の内容が SDO に送られます。

7. 書き込みサイクルを終了するために  $\overline{CS}$  をデアサー (High に駆動) します。

### 7.5.4 読み取り

TXE81XX-Q1 の SPI 読み取り動作は、特定のレジスタからデータを取得するために使用されます。

この動作では、レジスタにアクセスしてそのデータを読み取るコマンドを TXE81XX-Q1 に送信します。

#### SPI 読み取り動作手順:

1.  $\overline{CS}$  を low に駆動します。これにより、内部シフトレジスタが有効になります。

2. 24 ビットのデータを MSB ファースト方式でデバイスに移行します。SCLK の立ち上がりエッジの間、データは安定している必要があります。

3. MSB ビットは、読み取り専用転送であることを示す「1」である必要があります。

4. 3 番目のデータバイトは NOP (無動作) であり、ダミー データバイトです。

5. 16 ビットのステータスが SDO で送信されます。最初の 2 ビットは 2'b11 です (ステータス セグメントであることを示します)。次の 6 ビットは、[故障ステータス レジスタ](#) のビット 5 ~ 0 です。最後の 8 ビットはすべて 0 です。

6. 読み取りデータはステータスビットに続いて SDO にシフト出力されます。

7. 最後のデータビットが転送された後、転送するデータがない場合は SCLK を low に駆動します。

8. 読み取りサイクルを終了するために  $\overline{CS}$  をデアサー (High に駆動) します。

## 7.6 レジスタ マップ

### 7.6.1 制御レジスタ：読み取り/書き込みおよび機能アドレス (B23-B16)

通信は、 $\overline{CS}$  ピンを low にして SCLK ピンをクロックすることによって開始されます。通信の最初のバイトは、読み取り/書き込み構成とさまざまな機能設定です。コマンド アドレスは機能 (入力、出力、極性反転、フェイルセーフなど) を制御し、ポート アドレスは使用するポートを選択します。マルチポートの有効化/無効化ビットは、2 番目のバイト (B8) の LSB です。

新しいコマンドが送信されると、アドレス指定されたレジスタは、新しいコマンド バイトが送信されるまで、読み取りによってアクセスが継続されます。電源投入時、ハードウェアリセット時、またはソフトウェアリセット時に、制御レジスタはデフォルトで 0x0 に設定されます。

## ADVANCE INFORMATION

| 制御レジスタ (機能アドレス) |     |     |     |     | コマンド バイト (16進数) | レジスタ                  | マルチポート | プロトコル           | 電源投入時のデフォルト値                         |

|-----------------|-----|-----|-----|-----|-----------------|-----------------------|--------|-----------------|--------------------------------------|

| B20             | B19 | B18 | B17 | B16 |                 |                       |        |                 |                                      |

| 0               | 0   | 0   | 0   | 0   | 0x0             | スクラッチ レジスタ            | なし     | バイトの読み取り / 書き込み | 0x0                                  |

| 0               | 0   | 0   | 0   | 1   | 0x1             | Device_ID             | なし     | バイトの読み取り        | 0x0 - TXE8116-Q1<br>0x1 - TXE8124-Q1 |

| 0               | 0   | 0   | 1   | 0   | 0x2             | 入力ポートレジスタ             | あり     | バイトの読み取り        | 0x0                                  |

| 0               | 0   | 0   | 1   | 1   | 0x3             | 出力ポートレジスタ             | あり     | バイトの読み取り / 書き込み | 0x0                                  |

| 0               | 0   | 1   | 0   | 0   | 0x4             | 方向構成レジスタ              | あり     | バイトの読み取り / 書き込み | 0x0                                  |

| 0               | 0   | 1   | 0   | 1   | 0x5             | 極性反転レジスタ              | あり     | バイトの読み取り / 書き込み | 0x0                                  |

| 0               | 0   | 1   | 1   | 0   | 0x6             | プッシュプル/オーブンドライン選択レジスタ | あり     | バイトの読み取り / 書き込み | 0x0                                  |

| 0               | 1   | 0   | 0   | 0   | 0x8             | プルアップまたはプルダウン有効レジスタ   | あり     | バイトの読み取り / 書き込み | 0x0                                  |

| 0               | 1   | 0   | 0   | 1   | 0x9             | プルアップまたはプルダウン選択レジスタ   | あり     | バイトの読み取り / 書き込み | 0x0                                  |

| 0               | 1   | 0   | 1   | 0   | 0xA             | バス ホルダ レジスタ           | あり     | バイトの読み取り / 書き込み | 0x0                                  |

| 0               | 1   | 0   | 1   | 1   | 0xB             | スマート割り込みレジスタ          | なし     | バイトの読み取り / 書き込み | 0x0                                  |

| 0               | 1   | 1   | 0   | 0   | 0xC             | 割り込みマスク レジスタ          | あり     | バイトの読み取り / 書き込み | 0xFF                                 |

| 0               | 1   | 1   | 0   | 1   | 0xD             | 入力グリッヂ フィルタ有効レジスタ     | なし     | バイトの読み取り / 書き込み | 0x0                                  |

| 0               | 1   | 1   | 1   | 0   | 0xE             | 割り込みフラグ ステータス レジスタ    | なし     | バイトの読み取り        | 0x0                                  |

| 0               | 1   | 1   | 1   | 1   | 0xF             | 割り込みポート ステータス レジスタ    | なし     | バイトの読み取り        | 0x0                                  |

| 1               | 0   | 0   | 1   | 0   | 0x12            | フェイルセーフ有効レジスタ 1       | なし     | バイトの読み取り / 書き込み | 0x0                                  |

| 1               | 0   | 0   | 1   | 1   | 0x13            | フェイルセーフ有効レジスタ 2       | あり     | バイトの読み取り / 書き込み | 0x0                                  |

| 1               | 0   | 1   | 0   | 0   | 0x14            | フェイルセーフ方向構成レジスタ 1.    | あり     | バイトの読み取り / 書き込み | 0x0                                  |

| 1               | 0   | 1   | 0   | 1   | 0x15            | フェイルセーフ方向構成レジスタ 2.    | あり     | バイトの読み取り / 書き込み | 0x0                                  |

| 1               | 0   | 1   | 1   | 0   | 0x16            | フェイルセーフ出力レジスタ 1       | あり     | バイトの読み取り / 書き込み | 0x0                                  |

| 1               | 0   | 1   | 1   | 1   | 0x17            | フェイルセーフ出力レジスタ 2       | あり     | バイトの読み取り / 書き込み | 0x0                                  |

| 1               | 1   | 0   | 0   | 0   | 0x18            | フェイルセーフ冗長性チェック レジスタ   | なし     | バイトの読み取り / 書き込み | 0x0                                  |

| 1               | 1   | 0   | 0   | 1   | 0x19            | フォルト ステータス レジスタ       | なし     | バイトの読み取り        | 0x1                                  |

| 1               | 1   | 0   | 1   | 0   | 0x1A            | ソフトウェアリセット レジスタ       | なし     | 書き込みバイト         | 0x0                                  |

### 7.6.2 制御レジスタ : ポート選択とマルチポート (B15-B8)

2番目のバイトは、どの I/O ポートを構成するか、およびマルチポートの有効化/無効化を指定します。マルチポートビットにより、デバイスは複数のポートを並列に処理できるようになります。このビットが 1 に設定されている場合、データバイト

(3番目のバイト)の各ビットは個々のポートを参照します。たとえば、データ バイトのビット 0 は P0 ポート、ビット 1 は P1 ポート、ビット 2 は P2 ポートを参照します。マルチ ポートが有効になっている場合、特定のポートのすべての I/O は同じ構成になります。

| 制御レジスタ (ポート選択) |     |     | ポート                        |

|----------------|-----|-----|----------------------------|

| B14            | B13 | B12 |                            |

| 0              | 0   | 0   | IO ポート 0                   |

| 0              | 0   | 1   | IO ポート 1                   |

| 0              | 1   | 0   | IO ポート 2 (TXE8116-Q1 では無効) |

### 7.6.3 レジスタの説明

この章では各レジスタについて説明します。レジスタ アドレスは TXE8116-Q1/TXE8124-Q1 SPI ワードの 1 番目と 2 番目のバイトであり、デフォルト値は TXE8116-Q1/TXE8124-Q1 SPI ワードの 3 番目のバイトであるレジスタの電源投入時のデフォルト値です。

この章では、B23 (読み取り/書き込みビット) と B8 (マルチポートビット) は考慮していません。B23 が High (1) の場合は読み取り操作が選択され、B23 が low (0) の場合は書き込み操作が選択されます。マルチポートを有効にするには、B8 の High (1) を設定する必要があります。

#### スクラッチ レジスタ (レジスタ アドレス:0x0、デフォルト値:0x0)

スクラッチ レジスタは、ブランク レジスタとの間でコードを読み書きし、コーディングの問題を解決するためのテスト レジスタです。

#### デバイス ID レジスタ (レジスタ アドレス:0x100、デフォルト値:0x1)

デバイス ID レジスタは、デバイス ID を持つ読み取り専用レジスタです。

**表 7-2. デバイス ID レジスタ**

| デバイス ID | デバイス       |

|---------|------------|

| 1       | TXE8124-Q1 |

| 0       | TXE8116-Q1 |

#### 入力ポート レジスタ (レジスタ アドレス:0x200 - 0x220、デフォルト値:0x0)

入力ポート レジスタには、IO ピンに入ってくる ロジック レベルが反映されます。入力ポート レジスタは読み取り専用です。これらのレジスタに書き込みを行っても、影響はありません。

**表 7-3. 入力ポート レジスタ 0、1、2**

| ポート ID              | レジスタ・アドレス | ビット値              |

|---------------------|-----------|-------------------|

| 0                   | 0x200     | 0 - Low, 1 - high |

| 1                   | 0x210     |                   |

| 2 (TXE8116-Q1 では無効) | 0x220     |                   |

#### 出力ポート レジスタ (レジスタ アドレス:0x300 - 0x320、デフォルト値:0x0)

出力ポート レジスタは、方向構成レジスタによって出力として定義された IO ピンの出力ロジック レベルを示します。これらのレジスタのビット値は、入力として定義された IO ピンには影響しません。

**表 7-4. 出力ポートレジスタ 0、1、2**

| ポート ID              | レジスタ・アドレス | ビット値              |

|---------------------|-----------|-------------------|

| 0                   | 0x300     | 0 - Low, 1 - high |

| 1                   | 0x310     |                   |

| 2 (TXE8116-Q1 では無効) | 0x320     |                   |

**方向構成レジスタ (レジスタ アドレス:0x400 - 0x420、デフォルト値:0x0)**

方向構成レジスタは、I/O ピンの方向を構成します。これらのレジスタのビットが 0 に設定されている場合、対応するポートピンはハイインピーダンス入力として有効になります。これらのレジスタのビットを 1 に設定すると、対応するポートピンは出力として有効になります。

**表 7-5. 方向構成レジスタ 0、1、2**

| ポート ID              | レジスタ・アドレス | ビット値          |

|---------------------|-----------|---------------|

| 0                   | 0x400     | 0 - 入力、1 - 出力 |

| 1                   | 0x410     |               |

| 2 (TXE8116-Q1 では無効) | 0x420     |               |

**極性反転レジスタ (レジスタ アドレス:0x500 - 0x520、デフォルト値:0x0)**

極性反転レジスタは、方向構成レジスタによって入力または出力として定義された I/O ピンの極性反転を可能にします。これらのレジスタのビットが 1 に設定されている場合、入力レジスタ内の対応するポートピンの極性が反転されます。このレジスタのビットが 0 に設定されている場合、対応するポートの極性は反転されません。

入力モード中に極性反転が有効になっていると、内部状態は切り替わりますが、割り込みは生成されません。

**表 7-6. 極性反転レジスタ 0、1、2**

| ポート ID              | レジスタ・アドレス | ビット値           |

|---------------------|-----------|----------------|

| 0                   | 0x500     | 0 - 非反転、1 - 反転 |

| 1                   | 0x510     |                |

| 2 (TXE8116-Q1 では無効) | 0x520     |                |

**プッシュプル/オープンドレイン選択レジスタ (レジスタ アドレス:0x600 - 0x620、デフォルト値:0x0)**

プッシュプル/オープンドレイン選択レジスタは、出力タイプを設定します。これらのレジスタのビットが 0 に設定されている場合、対応するポートピンはプッシュプル出力として有効になります。これらのレジスタのビットが 1 に設定されている場合、対応するポートピンはオープンドレイン出力として有効になります。

**表 7-7. プッシュプル/オープンドレイン選択レジスタ 0、1、2**

| ポート ID              | レジスタ・アドレス | ビット値                    |

|---------------------|-----------|-------------------------|

| 0                   | 0x600     | 0 - プッシュプル、1 - オープンドレイン |

| 1                   | 0x610     |                         |

| 2 (TXE8116-Q1 では無効) | 0x620     |                         |

**プルアップまたはプルダウン有効レジスタ (レジスタ アドレス:0x800 - 0x820、デフォルト値:0x0)**

プルアップまたはプルダウン有効レジスタを使用すると、ユーザーは I/O ピン上のプルアップ/プルダウン抵抗を有効または無効にすることができます。ビットを 1 にセットすると、プルアップ / プルダウン抵抗を選択することができます。ビットを 0 にセットすると、I/O ピンからプルアップ / プルダウン抵抗が切断されます。

**表 7-8. プルアップまたはプルダウン有効レジスタ 0、1、2**

| ポート ID              | レジスタ・アドレス | ビット値          |

|---------------------|-----------|---------------|

| 0                   | 0x800     | 0 - 無効、1 - 有効 |

| 1                   | 0x810     |               |

| 2 (TXE8116-Q1 では無効) | 0x820     |               |

**プルアップまたはプルダウン選択レジスタ (レジスタ アドレス:0x900 - 0x920、デフォルト値:0x0)**

プルアップ/プルダウン選択レジスタをプログラムすることにより、I/O ポートをプルアップ抵抗またはプルダウン抵抗を持つように構成できます。ビットを 1 に設定すると、その I/O ピンに  $100\text{k}\Omega$  のプルアップ抵抗が選択されます。ビットを 0 に設定すると、その I/O ピンに  $100\text{k}\Omega$  のプルダウン抵抗が選択されます。プルアップ/ダウン有効が 0 の場合、このレジスタに書き込んでも I/O ピンには影響しません。

**表 7-9. プルアップまたはプルダウン選択レジスタ 0、1、2**

| ポート ID              | レジスタ・アドレス | ビット値                                                        |

|---------------------|-----------|-------------------------------------------------------------|

| 0                   | 0x900     | 0 - $100\text{k}\Omega$ プルダウン、1 - $100\text{k}\Omega$ プルアップ |

| 1                   | 0x910     |                                                             |

| 2 (TXE8116-Q1 では無効) | 0x920     |                                                             |

**バス ホルダ レジスタ (レジスタ アドレス:0xA00 - 0xA20、デフォルト値:0x0)**

バス ホルダ レジスタは、I/O ピンの入力ラッチを有効または無効にします。これらのレジスタは、IO ピンが入力ピンとして構成されている場合にのみ有効です。バス ホルダ レジスタのビットが 0 の場合、対応する入力 IO ピンの状態はラッチされません。

**表 7-10. バス ホルダ レジスタ レジスタ 0、1、2**

| ポート ID              | レジスタ・アドレス | ビット値          |

|---------------------|-----------|---------------|

| 0                   | 0xA00     | 0 - 無効、1 - 有効 |

| 1                   | 0xA10     |               |

| 2 (TXE8116-Q1 では無効) | 0xA20     |               |

**スマート割り込みレジスタ (レジスタ アドレス:0xB00、デフォルト値:0x0)**

スマート割り込みレジスタ ビットが 0 (スマート割り込みが有効) に設定されている場合、任意の入力ピンの状態変化によって割り込みが生成され、入力が初期状態に戻ると割り込みはクリアされます。

スマート割り込みレジスタ ビットが 1 (スマート割り込み無効) に設定されている場合、任意の入力ピンの状態変化によって割り込みが生成され、入力が初期状態に戻っても割り込みはクリアされません。割り込みステータス フラグ レジスタを読み取ると、割り込みがクリアされます。

この機能はポート レベルで有効になっており、個々の I/O を構成することはできません。このデバイスには 3 つのポートがあるため、ビット 3 からビット 7 は予約されています。

**表 7-11. スマート割り込みレジスタ**

| レジスタ・アドレス | ビット値  |                       |                       |                       |

|-----------|-------|-----------------------|-----------------------|-----------------------|

| 0xB00     | B3~B7 | B2                    | B1                    | B0                    |

|           | 予約済み  | 0:ポート 2 有効、1:ポート 2 無効 | 0:ポート 1 有効、1:ポート 1 無効 | 0:ポート 0 有効、1:ポート 0 無効 |

**割り込みマスク レジスタ (レジスタ アドレス:0xC00 - 0xC20、デフォルト値:0xFF)**

割り込みマスク レジスタはデフォルトで 1 に設定されています。対応するマスク ビットを 0 に設定することで割り込みを有効にすることができます。

割り込みマスク レジスタの対応するビットが 1 に設定されている場合、割り込みはマスクされ、割り込みピンはアサートされません。割り込みマスク レジスタの対応ビットが 0 にセットされると、割り込みピンがアサートされます。このデバイスには 3 つの割り込みマスク レジスタがあります。

**表 7-12. 割り込みマスク レジスタ 0、1、2**

| ポート ID              | レジスタ・アドレス | ビット値          |

|---------------------|-----------|---------------|

| 0                   | 0xC00     | 0 - 無効、1 - 有効 |

| 1                   | 0xC10     |               |

| 2 (TXE8116-Q1 では無効) | 0xC20     |               |

#### 入力グリッチ フィルタ有効化レジスタ (レジスタ アドレス:0xD00 - 0xD20、デフォルト値:0x0)

グリッチ フィルタは GPIO のすべての入力に存在します。これらのフィルタはデフォルトでは無効になっています。グリッチ フィルタを有効にするには、入力グリッチ フィルタ有効レジスタの I/O ピンの対応するビットを 1 に設定する必要があります。このデバイスには 3 つの入力グリッチ フィルタ有効化レジスタがあります。

**表 7-13. 入力グリッチフィルタ有効化レジスタ 0、1、2**

| ポート ID              | レジスタ・アドレス | ビット値          |

|---------------------|-----------|---------------|

| 0                   | 0xD00     | 0 - 無効、1 - 有効 |

| 1                   | 0xD10     |               |

| 2 (TXE8116-Q1 では無効) | 0xD20     |               |