# TUSB5461-Q1 Automotive DisplayPort™ Alt モード、USB Type-C® ソース 8.1Gbps リニアリドライバクロスポイントスイッチ

## 1 特長

- 車載アプリケーション向けに AEC-Q100 認証済み

- 温度: -40°C ~ 105°C, T<sub>A</sub>

- USB Type-C® クロスポイントスイッチで、次の仕様をサポート

- USB 3.2 + 2つの DisplayPort™ レーン

- 4つの DisplayPort™ レーン

- USB 3.2 x1 で最大 5Gbps

- VESA® DisplayPort™ 2.1 で最大 8.1Gbps

- D\_DFP のピン割り当て C, D, E をサポート

- USB DFP レシーバについて、適応型または固定のイコライゼーションを選択可能。

- UFP トランスマッタでリニアおよび制限付きリドライバをサポート

- 制限付きリドライバオプションでは、TX 電圧スイングと TX イコライゼーション制御の両方を使用可能

- 800mVpp から 1100mVpp まで 4 レベルの TX 電圧スイング

- TX プリシュートとディエンファシス

- 超低消費電力アーキテクチャ

- 2.5GHz で最大 12dB のイコライゼーション

- DisplayPort™ リンクトレーニングに対して透過的

- GPIO または I<sup>2</sup>C により設定可能

- ホットプラグ対応

- 5mm × 7mm、0.5mm ピッチの VQFN パッケージ

## 2 アプリケーション

- 後部座席用エンターテインメント

- 車載用ヘッドユニット

- 車載用インフォテインメントおよびクラスター

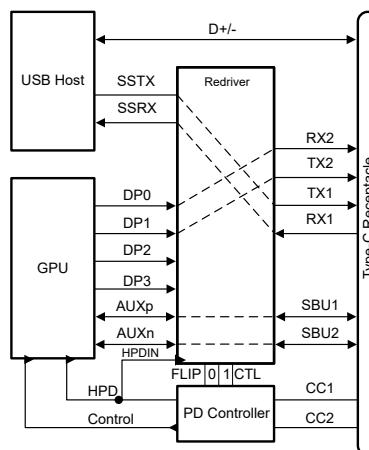

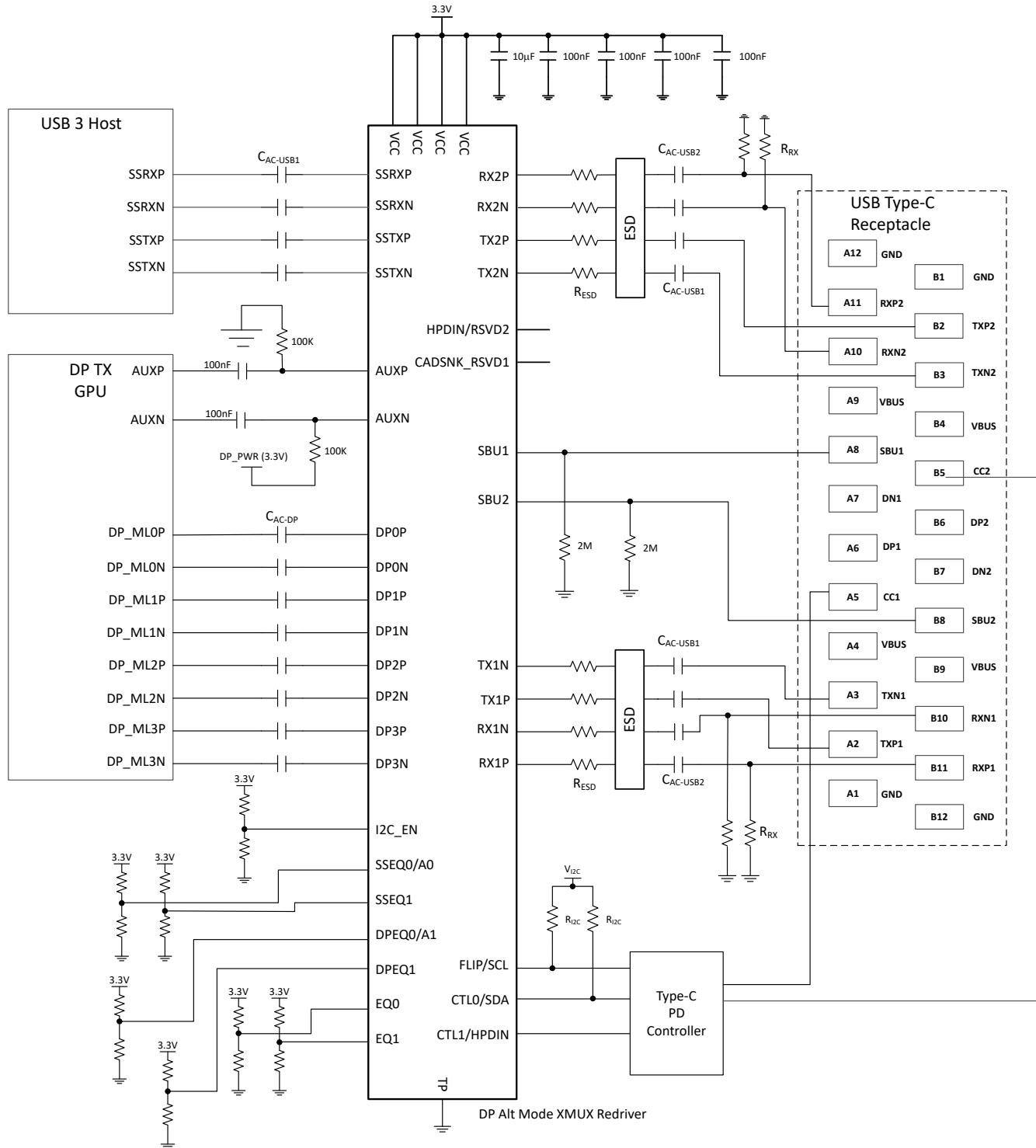

概略回路図

## 3 概要

TUSB5461-Q1 は、USB Type-C® 経由で VESA® DisplayPort™ Alt Mode を再送信するスイッチで、最大 5Gbps の USB 3.2 データ転送速度と、下流向きポート（ホスト）用の最大 8.1Gbps の DisplayPort™ 2.1 をサポートしています。このデバイスは、USB Type-C® 規格の VESA® DisplayPort™ Alt モードから、構成 C, D, E に使用されます。このリニアリドライバはプロトコルに依存せず、HDMI® Alt モードなど他の USB Type-C® Alt モードインターフェイスもサポートできます。

また、TUSB5461-Q1 は適応型レシーバイコライゼーション（AEQ）機能も内蔵しており、USB デバイスと TUSB5461-Q1 との間で最適な ISI 補償設定を自動的に見つけることができます。AEQ は、USB ホストと USB デバイス間の相互運用性を向上させるために、最適な設定を見つけ出します。TUSB5461-Q1 は単一の 3.3V 電源で動作し、車載グレード 2 の温度範囲に対応しています。

### パッケージ情報

| 部品番号        | パッケージ <sup>(1)</sup> | パッケージサイズ <sup>(2)</sup> |

|-------------|----------------------|-------------------------|

| TUSB5461-Q1 | RGF (VQFN, 40)       | 5mm × 7mm               |

- (1) 供給されているすべてのパッケージについては、[セクション 11](#) を参照してください。

(2) パッケージサイズ（長さ × 幅）は公称値であり、該当する場合はピンも含まれます。

## 目次

|                       |           |                               |           |

|-----------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>           | <b>1</b>  | 6.4 デバイスの機能モード                | 25        |

| <b>2 アプリケーション</b>     | <b>1</b>  | 6.5 プログラミング                   | 33        |

| <b>3 概要</b>           | <b>1</b>  | <b>7 レジスタ マップ</b>             | <b>39</b> |

| <b>4 ピン構成および機能</b>    | <b>3</b>  | 7.1 TUSB5461-Q1 レジスタ          | 39        |

| <b>5 仕様</b>           | <b>6</b>  | <b>8 アプリケーションと実装</b>          | <b>50</b> |

| 5.1 絶対最大定格            | 6         | 8.1 アプリケーション情報                | 50        |

| 5.2 ESD 定格            | 6         | 8.2 代表的なアプリケーション              | 50        |

| 5.3 推奨動作条件            | 6         | 8.3 システム例                     | 55        |

| 5.4 熱に関する情報           | 6         | 8.4 電源に関する推奨事項                | 58        |

| 5.5 電源特性              | 7         | 8.5 レイアウト                     | 58        |

| 5.6 制御 I/O DC の電気的特性  | 7         | <b>9 デバイスおよびドキュメントのサポート</b>   | <b>60</b> |

| 5.7 USB および DP の電気的特性 | 9         | 9.1 ドキュメントの更新通知を受け取る方法        | 60        |

| 5.8 タイミング要件           | 12        | 9.2 サポート・リソース                 | 60        |

| 5.9 スイッチング特性          | 13        | 9.3 商標                        | 60        |

| 5.10 代表的特性            | 15        | 9.4 静電気放電に関する注意事項             | 60        |

| <b>6 詳細説明</b>         | <b>22</b> | 9.5 用語集                       | 60        |

| 6.1 概要                | 22        | <b>10 改訂履歴</b>                | <b>60</b> |

| 6.2 機能ブロック図           | 23        | <b>11 メカニカル、パッケージ、および注文情報</b> | <b>60</b> |

| 6.3 機能説明              | 24        |                               |           |

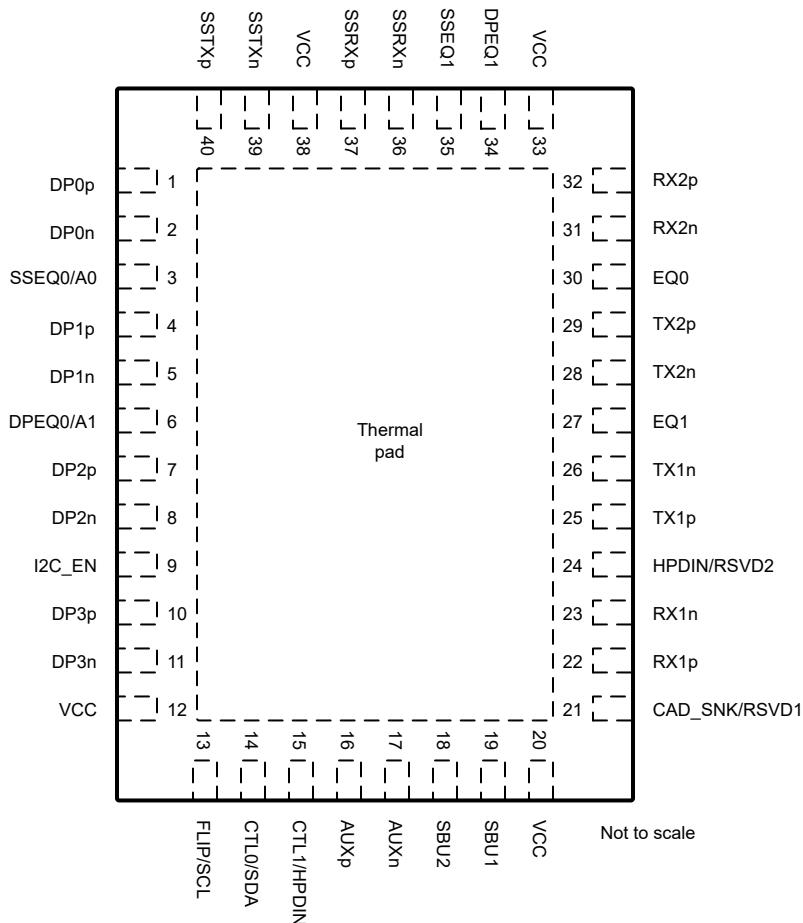

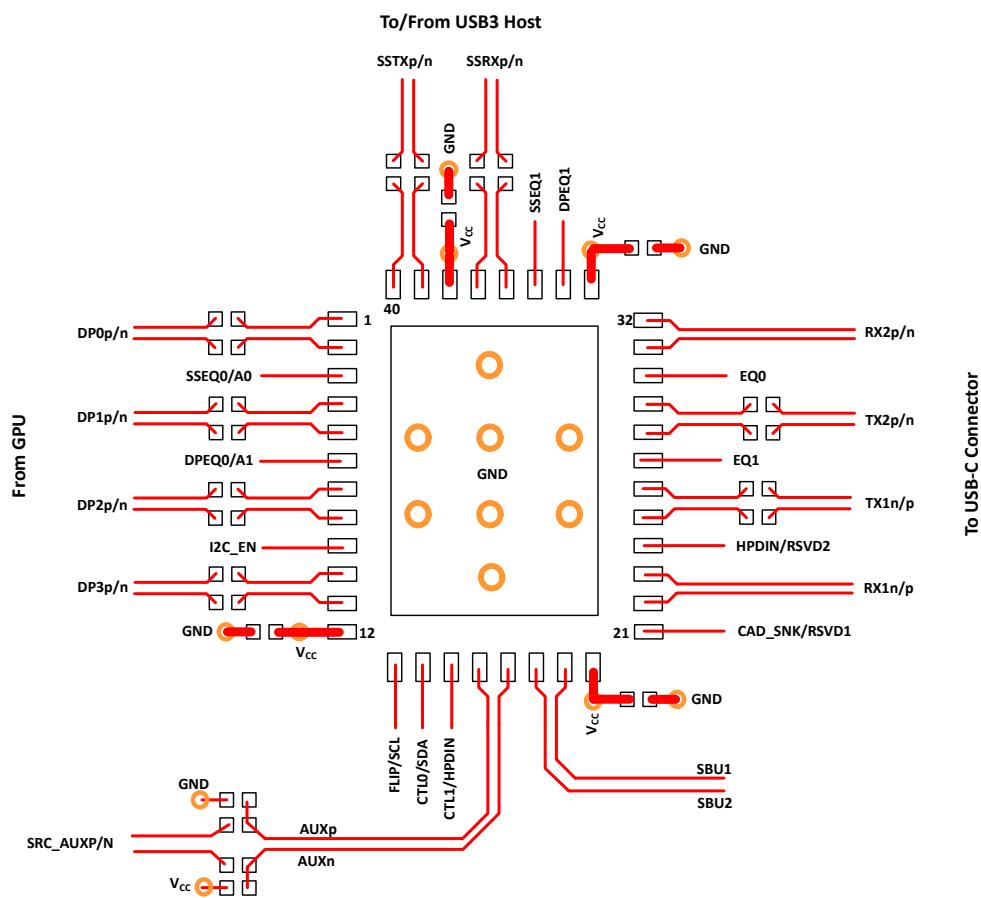

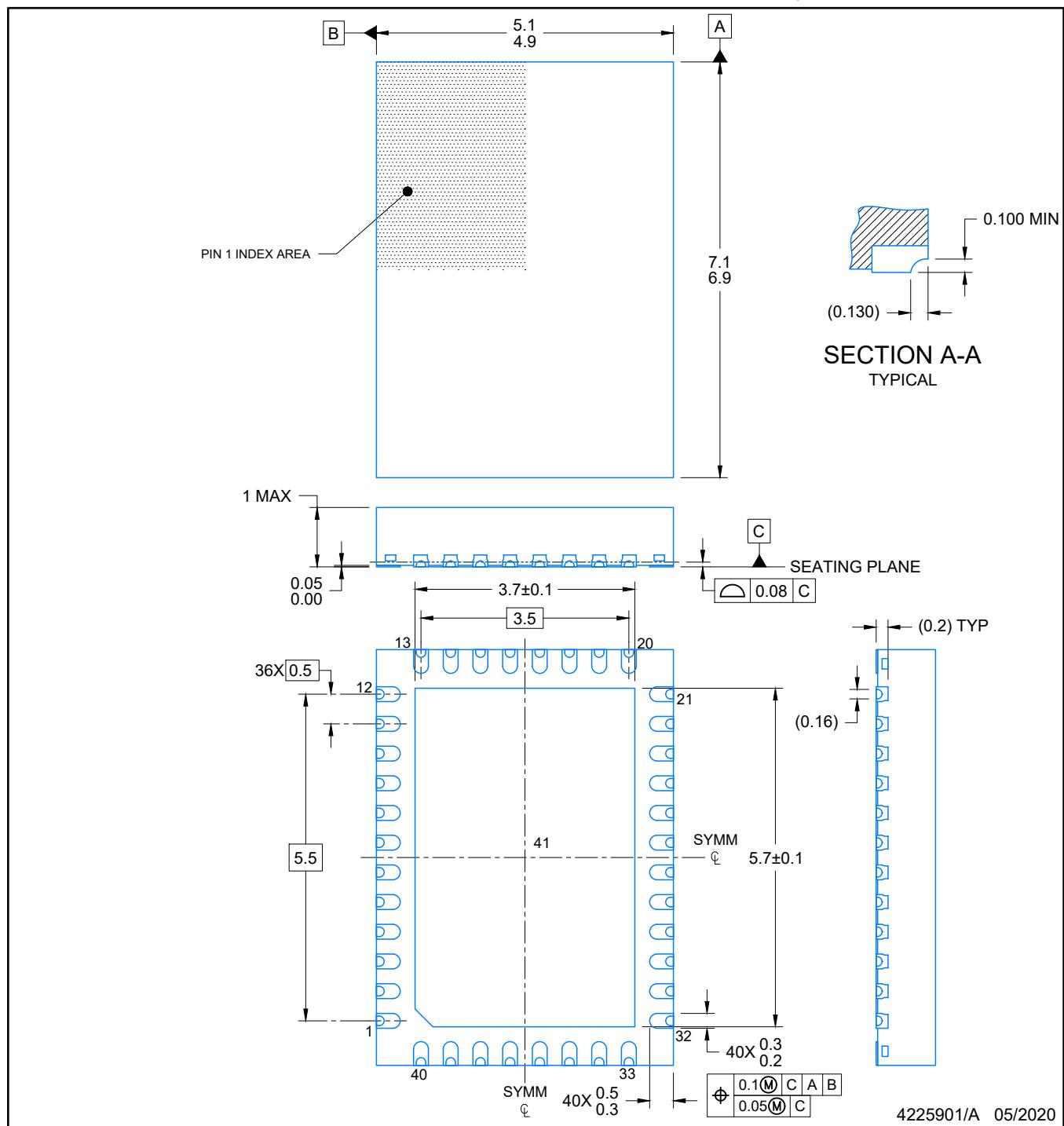

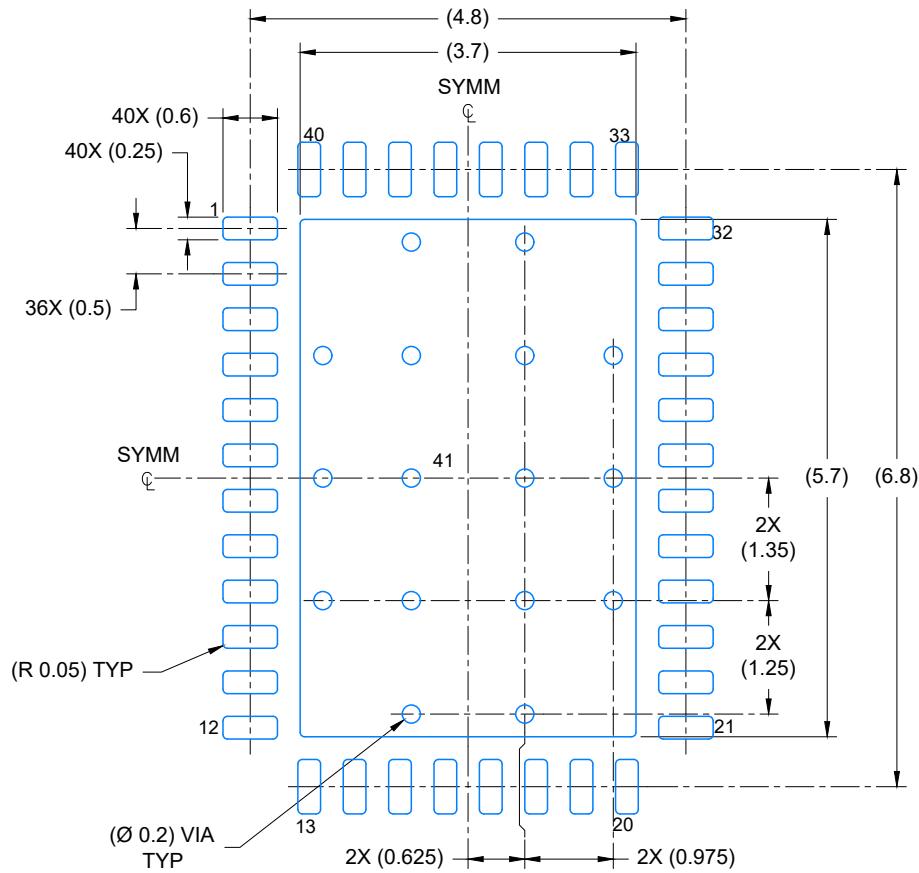

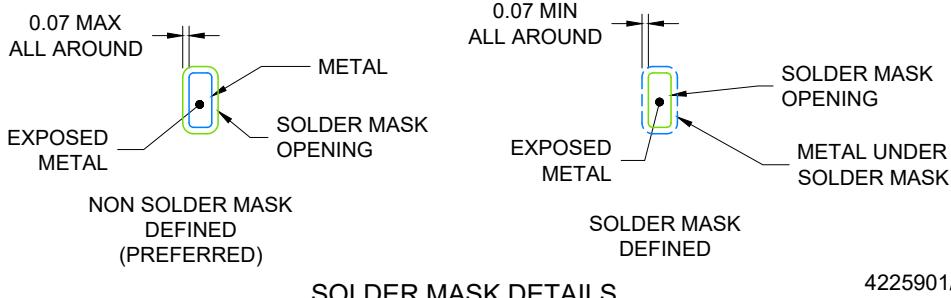

## 4 ピン構成および機能

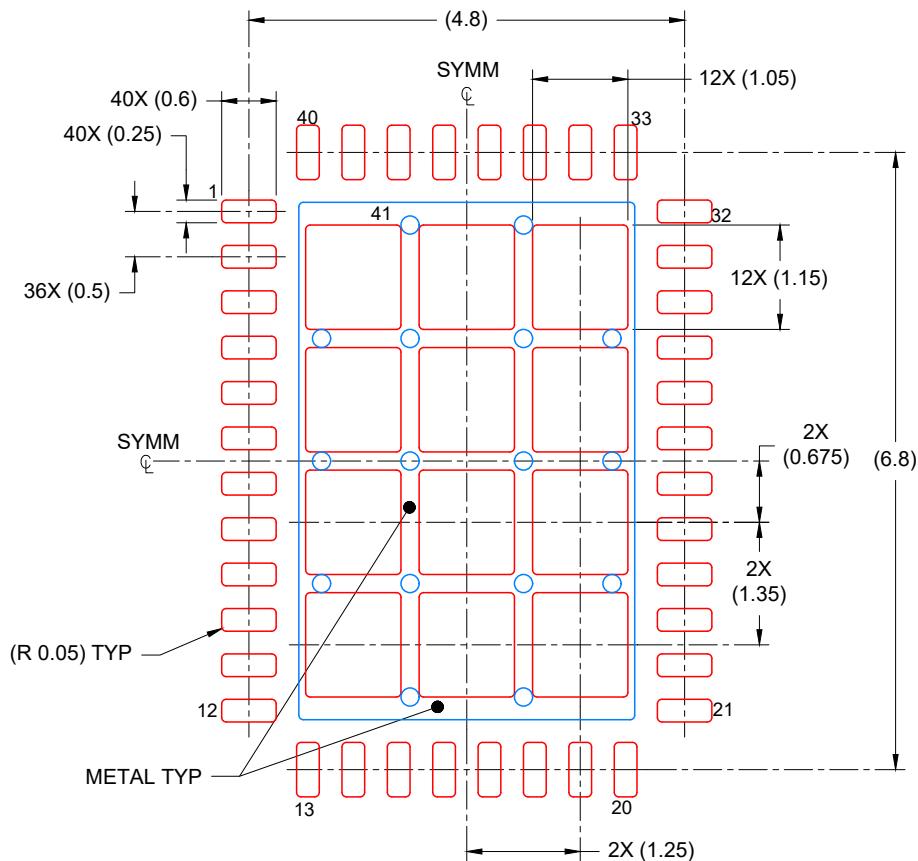

図 4-1. TUSB5461-Q1 RGF パッケージ、40 ピン VQFN (上面図)

表 4-1. TUSB5461-Q1 のピンの機能

| ピン   |    | I/O    | 説明                                               |

|------|----|--------|--------------------------------------------------|

| 名称   | 番号 |        |                                                  |

| DP0p | 1  | 差動 I   | DisplayPort レーン 0 の DP 差動正入力。                    |

| DP0n | 2  | 差動 I   | DisplayPort レーン 0 の DP 差動負入力。                    |

| DP1p | 4  | 差動 I   | DisplayPort レーン 1 の DP 差動正入力。                    |

| DP1n | 5  | 差動 I   | DisplayPort レーン 1 の DP 差動負入力。                    |

| DP2p | 7  | 差動 I   | DisplayPort レーン 2 の DP 差動正入力。                    |

| DP2n | 8  | 差動 I   | DisplayPort レーン 2 の DP 差動負入力。                    |

| DP3p | 10 | 差動 I   | DisplayPort レーン 3 の DP 差動正入力。                    |

| DP3n | 11 | 差動 I   | DisplayPort レーン 3 の DP 差動負入力。                    |

| RX1n | 23 | 差動 I/O | DisplayPort の差動負出力、USB3.2 ダウンストリーム側ポートの場合の差動負入力。 |

| RX1p | 22 | 差動 I/O | DisplayPort の差動正出力と、USB3.2 ダウンストリーム側ポートの差動正入力。   |

| TX1n | 26 | 差動 O   | DisplayPort または USB3.2 ダウンストリーム側ポートの差動負出力。       |

| TX1p | 25 | 差動 O   | DisplayPort または USB 3.2 ダウンストリーム側ポートの差動正出力。      |

| TX2p | 29 | 差動 O   | DisplayPort または USB 3.2 ダウンストリーム側ポートの差動正出力。      |

| TX2n | 28 | 差動 O   | DisplayPort または USB 3.2 ダウンストリーム側ポートの差動負出力。      |

| RX2p | 32 | 差動 I/O | DisplayPort の差動正出力と、USB3.2 ダウンストリーム側ポートの差動正入力。   |

| RX2n | 31 | 差動 I/O | DisplayPort の差動負出力、USB3.2 ダウンストリーム側ポートの場合の差動負入力。 |

**表 4-1. TUSB5461-Q1 のピンの機能 (続き)**

| ピン                           |                   | I/O                           | 説明                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------|-------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                           | 番号                |                               |                                                                                                                                                                                                                                                                                                                                                                                                   |

| SSTXp                        | 40                | 差動 I                          | USB3.2 アップストリーム側ポートの差動正入力。                                                                                                                                                                                                                                                                                                                                                                        |

| SSTXn                        | 39                | 差動 I                          | USB3.2 アップストリーム側ポートの差動負入力。                                                                                                                                                                                                                                                                                                                                                                        |

| SSRXp                        | 37                | 差動 O                          | USB3.2 アップストリーム側ポートの差動正出力。                                                                                                                                                                                                                                                                                                                                                                        |

| SSRxn                        | 36                | 差動 O                          | USB3.2 アップストリーム側ポートの差動負出力。                                                                                                                                                                                                                                                                                                                                                                        |

| EQ1                          | 27                | 4 レベル I                       | このピンを EQ0 とともに使用する場合、USB レシーバ イコライザ ゲインを、下流側の RX1 および RX2 用に設定します。イコライゼーション設定の詳細については、表 6-7 を参照してください。                                                                                                                                                                                                                                                                                            |

| EQ0                          | 30                | 4 レベル I                       | このピンを EQ1 とともに使用する場合、USB レシーバ イコライザ ゲインを、下流側の RX1 および RX2 用に設定します。イコライゼーション設定の詳細については、表 6-7 を参照してください。                                                                                                                                                                                                                                                                                            |

| CAD_SNK/RSVD1 <sup>(1)</sup> | 21                | I/O (PD)                      | I <sup>2</sup> C_EN ! = 0 の場合、このピンは予約済みです。未使用時は、オープンのままにしてください。I <sup>2</sup> C_EN = 0 の場合、このピンは CAD_SNK(L = AUX スヌープが有効、H = AUX スヌープが無効で、すべてのレーンがアクティブ)です。                                                                                                                                                                                                                                       |

| HPDIN/RSVD2 <sup>(1)</sup>   | 24                | I/O (PD)                      | I <sup>2</sup> C_EN ! = 0 の場合、このピンは予約済みです。未使用時は、オープンのままにしてください。I <sup>2</sup> C_EN = 0 の場合、このピンは DisplayPort シンクから受信したホットプラグ検出の入力です。HPDIN が Low の状態が 2ms を超えると、すべての DisplayPort レーンが無効になり、AUX-to-SBU スイッチは閉じたままとなります。                                                                                                                                                                             |

| I <sup>2</sup> C_EN          | 9                 | 4 レベル I                       | I <sup>2</sup> C プログラミング モードまたは GPIO プログラミング選択。<br>0 = GPIO モード(I <sup>2</sup> C 無効)、アダプティブ EQ 無効。<br>R = TI テスト モード(3.3V で I <sup>2</sup> C が有効)<br>、EQ0 = 「0」および EQ1 = 「0」のとき、F = I <sup>2</sup> C は 1.8V で有効。それ以外の場合、GPIO モード(I <sup>2</sup> C は有効)、アダプティブ EQ が有効。<br>1 = 3.3V で I <sup>2</sup> C が有効。                                                                                         |

| SBU1                         | 19                | I/O, CMOS                     | SBU1 の詳細を示します。TI では、このピンを Type-C レセプタクルの SBU1 ピンに DC 結合することを推奨します。GND との間に 2MΩ の抵抗も推奨されます。                                                                                                                                                                                                                                                                                                        |

| SBU2                         | 18                | I/O, CMOS                     | SBU2 の詳細を示します。TI では、このピンを Type-C レセプタクルの SBU2 ピンに DC 結合することを推奨します。GND との間に 2MΩ の抵抗も推奨されます。                                                                                                                                                                                                                                                                                                        |

| AUXp                         | 16                | I/O, CMOS                     | AUXp, AC カップリング コンデンサを経由して DisplayPort ソースに接続された DisplayPort AUX の正の I/O。AC カップリング コンデンサに加えて、このピンと GND の間に 100K の抵抗も必要です。このピンは AUXN とともに TUSB5461-Q1 によって AUX スヌーピングに使用され、Type-C の方向に基づいて SBU1/2 にルーティングされます。                                                                                                                                                                                     |

| AUXn                         | 17                | I/O, CMOS                     | AUXn, AC カップリング コンデンサを経由して DisplayPort ソースに接続された DisplayPort AUX の負の I/O。AC カップリング コンデンサに加えて、このピンで VCC(3.3V)との間に 100K の抵抗も必要です。このピンは AUXP とともに TUSB5461-Q1 によって AUX スヌーピングに使用され、Type-C の方向に基づいて SBU1/2 にルーティングされます。                                                                                                                                                                               |

| DPEQ1                        | 34                | 4 レベル I                       | DisplayPort レシーバ EQ。DPEQ0 に加えて、このピンは DisplayPort レシーバのイコライゼーション ゲインを選択します。イコライゼーション設定の詳細については、表 6-9 を参照してください。                                                                                                                                                                                                                                                                                    |

| DPEQ0/A1                     | 6                 | 4 レベル I                       | DisplayPort レシーバ EQ。DPEQ1 に加えて、このピンは DisplayPort レシーバのイコライゼーション ゲインを選択します。I <sup>2</sup> C_EN が「0」でない場合、このピンは TUSB5461-Q1 の I <sup>2</sup> C アドレスも設定します。イコライゼーション設定の詳細については、表 6-9 を参照してください。                                                                                                                                                                                                      |

| SSEQ1                        | 35                | 4 レベル I                       | SSEQ0 とともに、アップストリーム側の SSTXP/N の USB レシーバ イコライザ ゲインを設定します。イコライゼーション設定の詳細については、表 6-8 を参照してください。                                                                                                                                                                                                                                                                                                     |

| SSEQ0/A0                     | 3                 | 4 レベル I                       | SSEQ1 とともに、アップストリーム側の SSTXP/N の USB レシーバ イコライザ ゲインを設定します。I <sup>2</sup> C_EN が「0」でない場合、このピンは TUSB5461-Q1 の I <sup>2</sup> C アドレスも設定します。イコライゼーション設定の詳細については、表 6-8 を参照してください。                                                                                                                                                                                                                       |

| FLIP/SCL                     | 13                | 2 レベル I                       | I <sup>2</sup> C_EN = '0' のとき、これはフリップ制御ピンです。それ以外の場合、このピンは I <sup>2</sup> C クロックです。I <sup>2</sup> C クロックに使用する場合は、このピンを I <sup>2</sup> C コントローラの VCC I <sup>2</sup> C 電源にプルアップします。                                                                                                                                                                                                                  |

| CTL0/SDA                     | 14                | 2 レベル I                       | I <sup>2</sup> C_EN = '0' のとき、これは USB3 シンチ制御ピンです。それ以外の場合、このピンは I <sup>2</sup> C データです。I <sup>2</sup> C データに使用する場合は、このピンを I <sup>2</sup> C コントローラの VCC I <sup>2</sup> C 電源にプルアップします。                                                                                                                                                                                                               |

| CTL1/HPDIN                   | 15                | 2 レベル I<br>(フェイエルセーブ)<br>(PD) | DP Alt モード スイッチ制御ピン。I <sup>2</sup> C_EN = '0' のとき、このピンは DisplayPort 機能を有効化または無効化します。それ以外の場合、I <sup>2</sup> C_EN が「0」でない場合、DisplayPort 機能は I <sup>2</sup> C レジスタにより有効化および無効化されます。<br>L = DisplayPort は無効。<br>H = DisplayPort は有効。<br>I <sup>2</sup> C_EN が「0」でない場合、このピンは DisplayPort シンクから受信したホット プラグ検出の入力です。<br>HPDIN が Low の状態が 2ms を超えると、すべての DisplayPort レーンが無効になり、AUX-to-SBU スイッチは閉じたままとなります。 |

| VCC                          | 12, 20, 33,<br>38 | P                             | 3.3V 電源                                                                                                                                                                                                                                                                                                                                                                                           |

**表 4-1. TUSB5461-Q1 のピンの機能 (続き)**

| ピン       |    | I/O | 説明   |

|----------|----|-----|------|

| 名称       | 番号 |     |      |

| サーマル パッド |    | G   | グランド |

(1) フェイإلセーフ I/O 以外。VCC が取り外された状態でピンをアクティブに High に駆動すると、VCC ピンにリーク電圧が発生します。

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                        |                 | 最小値  | 最大値 | 単位 |

|------------------------|-----------------|------|-----|----|

| 電源電圧範囲                 | V <sub>CC</sub> | -0.3 | 4   | V  |

| 任意の入力または出力ピンの電圧範囲      | 正入力と負入力との間の差動電圧 | -2.5 | 2.5 | V  |

|                        | 差動入力での電圧        | -0.5 | 4   | V  |

|                        | CMOS 入力         | -0.5 | 4   | V  |

| 最大接合部温度、T <sub>J</sub> |                 | -40  | 125 | °C |

| 保管温度、T <sub>stg</sub>  |                 | -65  | 150 | °C |

- (1) 「絶対最大定格」の範囲外での動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|                    |      | 値                                                  | 単位    |

|--------------------|------|----------------------------------------------------|-------|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、AEC Q100-002 <sup>(1)</sup> に準拠、すべてのピン | ±2000 |

|                    |      | デバイス帯電モデル (CDM)、AEQ Q100-011 に準拠、すべてのピン            | ±1500 |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI/ESDA/JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                    |                                    | 最小値 | 公称値 | 最大値 | 単位 |

|--------------------|------------------------------------|-----|-----|-----|----|

| V <sub>CC</sub>    | メイン電源                              | 3.0 | 3.3 | 3.6 | V  |

|                    | メイン電源ランプ要件                         | 0.1 |     | 50  | ms |

| V <sub>(I2C)</sub> | SDA と SCL に外部抵抗をプルアップする電源          | 1.7 |     | 3.6 | V  |

| V <sub>(PSN)</sub> | V <sub>CC</sub> ピンの電源ノイズ (4MHz 未満) |     |     | 100 | mV |

| T <sub>A</sub>     | 自由空気での動作温度                         | -40 |     | 105 | °C |

| T <sub>PCB</sub>   | PCB 温度 (デバイスから 1mm 離れた場所)          | -40 |     | 112 | °C |

### 5.4 热に関する情報

| 熱評価基準 <sup>(1)</sup>  |                     | デバイス       | 単位   |

|-----------------------|---------------------|------------|------|

|                       |                     | RGF (VQFN) |      |

|                       |                     | 40 ピン      |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 29.4       | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 18.9       | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 11.0       | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 0.3        | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ    | 10.9       | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース (底面) への熱抵抗 | 3.6        | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 5.5 電源特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                           | テスト条件                                                                                                                            | 最小値 | 標準値   | 最大値 | 単位 |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|----|

| P <sub>CC(ACTIVE-USB)</sub>     | 平均アクティブ電力 (USB のみ)<br>U0 でのリンク、EQ 制御ピン = NC、PRBS7 パターン、V <sub>ID</sub> = 1000mV <sub>PP</sub> 、LINR_L3、CTL1 = L、CTL0 = H         |     | 270   |     | mW |

| P <sub>CC(ACTIVE-USB-DP1)</sub> | 平均アクティブ電力 (USB + 2 レーン DP)<br>U0 でのリンク、EQ 制御ピン = NC、PRBS7 パターン、V <sub>ID</sub> = 1000mV <sub>PP</sub> 、LINR_L3、CTL1 = H、CTL0 = H |     | 520   |     | mW |

| P <sub>CC(ACTIVE-4DP)</sub>     | 平均アクティブ電力 (4 レーン DP のみ)<br>8.1Gbps で動作時の 4 つのアクティブな DP レーン、PRBS7 パターン、CTL1 = H、CTL0 = L、LINR_L3、                                 |     | 500   |     | mW |

| P <sub>CC(NC-USB)</sub>         | 接続されていない場合の平均電力<br>USB3 デバイスは TXP/TXN に接続されていない、CTL1 = L、CTL0 = H、                                                               |     | 1.7   |     | mW |

| P <sub>CC(U2U3)</sub>           | U2/U3 における平均電力<br>U2 または U3 でのリンク、USB モードのみ、CTL1 = L、CTL0 = H、                                                                   |     | 2.0   |     | mW |

| P <sub>CC(HPDLOW-4DP)</sub>     | HPDIN = L の場合の 4 レーン DP のみの電力<br>CTL1 = H、CTL0 = L、HPDIN = L、                                                                    |     | 0.475 |     | mW |

| P <sub>CC(DISABLED-I2C)</sub>   | I <sup>2</sup> C モードでのデバイスの無効電力<br>I <sup>2</sup> C_EN ! = 0、HPDIN = L、CTLSEL = 0x0、                                             |     | 0.122 |     | mW |

| P <sub>CC(DISABLED)</sub>       | デバイスの無効電力<br>CTL1 = L、CTL0 = L、I <sup>2</sup> C_EN = 0、HPDIN = L、                                                                |     | 0.110 |     | mW |

## 5.6 制御 I/O DC の電気的特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                                                            | テスト条件                                                                                                 | 最小値  | 標準値  | 最大値 | 単位 |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------|------|-----|----|

| <b>4 レベル入力</b>                                                   |                                                                                                       |      |      |     |    |

| I <sub>IH</sub>                                                  | High レベル入力電流<br>V <sub>CC</sub> = 3.6V、V <sub>IN</sub> = 3.6V                                         | 20   | 60   |     | μA |

| I <sub>IL</sub>                                                  | Low レベル入力電流<br>V <sub>CC</sub> = 3.6V、V <sub>IN</sub> = 0V                                            | -100 | -40  |     | μA |

| 4 レベル V <sub>TH</sub>                                            | スレッショルド 0/R<br>V <sub>CC</sub> = 3.3V                                                                 |      | 0.55 |     | V  |

| 4 レベル V <sub>TH</sub>                                            | スレッショルド R/Float<br>V <sub>CC</sub> = 3.3V                                                             |      | 1.65 |     | V  |

| 4 レベル V <sub>TH</sub>                                            | スレッショルド Float/1<br>V <sub>CC</sub> = 3.3V                                                             |      | 2.7  |     | V  |

| R <sub>PU</sub>                                                  | 内部プルアップ抵抗                                                                                             |      | 48   |     | kΩ |

| R <sub>PD</sub>                                                  | 内部プルダウン抵抗                                                                                             |      | 98   |     | kΩ |

| <b>2 ステート CMOS 入力 (CTL0, CTL1, FLIP)。CTL0 と FLIP はフェイリセーフです。</b> |                                                                                                       |      |      |     |    |

| V <sub>IH</sub>                                                  | High レベル入力電圧<br>V <sub>CC</sub> = 3.0 V                                                               | 2    | 3.6  |     | V  |

| V <sub>IL</sub>                                                  | Low レベル入力電圧<br>V <sub>CC</sub> = 3.6 V                                                                | 0    | 0.8  |     | V  |

| R <sub>PD</sub>                                                  | HPDIN, CADSNK の内部プルダウン抵抗                                                                              | 300  | 500  | 600 | kΩ |

| R <sub>PD</sub>                                                  | CTL1 の内部プルダウン抵抗                                                                                       | 300  | 400  | 600 | kΩ |

| I <sub>IH_CTL1</sub>                                             | CTL1 の High レベル入力電流<br>V <sub>IN</sub> = 3.6V                                                         | -12  | 12   |     | μA |

| I <sub>IL_CTL1</sub>                                             | CTL1 の Low レベル入力電流<br>V <sub>IN</sub> = GND、V <sub>CC</sub> = 3.6V                                    | -1   | 1    |     | μA |

| I <sub>IH_HPD_CAD</sub>                                          | HPDIN, CADSNK の High レベル入力電流<br>V <sub>IN</sub> = 3.6V                                                | -11  | 11   |     | μA |

| I <sub>IL_HPD_CAD</sub>                                          | HPDIN, CADSNK の Low レベル入力電流<br>V <sub>IN</sub> = GND、V <sub>CC</sub> = 3.6V                           | -1   | 1    |     | μA |

| I <sub>IH_CTL0_FLIP</sub>                                        | CTL0 および FLIP の High レベル入力電流<br>V <sub>IN</sub> = 3.6V, I <sup>2</sup> C_EN = 0                       | -1   | 2    |     | μA |

| I <sub>IL_CTL0_FLIP</sub>                                        | CTL0 および FLIP の Low レベル入力電流<br>V <sub>IN</sub> = GND、V <sub>CC</sub> = 3.6V, I <sup>2</sup> C_EN = 0, | -1   | 1    |     | μA |

| <b>I<sup>2</sup>C 制御ピン (SCL, SDA)</b>                            |                                                                                                       |      |      |     |    |

| V <sub>IH_3p3V</sub>                                             | 3.3V の I <sup>2</sup> C レベルに構成したときの High レベル入力電圧<br>I <sup>2</sup> C_EN = 1                           | 2.0  | 3.6  |     | V  |

| V <sub>IL_3p3V</sub>                                             | 3.3V の I <sup>2</sup> C レベルに構成したときの Low レベル入力電圧<br>I <sup>2</sup> C_EN = 1                            | 0    | 0.8  |     | V  |

| V <sub>IH_1p8V</sub>                                             | 1.8V の I <sup>2</sup> C レベルに構成したときの High レベル入力電圧<br>I <sup>2</sup> C_EN = F                           | 1.2  |      |     | V  |

| V <sub>IL_1p8V</sub>                                             | 1.8V の I <sup>2</sup> C レベルに構成したときの Low レベル入力電圧<br>I <sup>2</sup> C_EN = F                            | 0    | 0.6  |     | V  |

| V <sub>OL</sub>                                                  | Low レベル出力電圧<br>I <sup>2</sup> C_EN = 0, I <sub>OL</sub> = 6mA                                         | 0    | 0.4  |     | V  |

| I <sub>OL</sub>                                                  | Low レベル出力電流<br>I <sup>2</sup> C_EN = 0, V <sub>OL</sub> = 0.4V                                        | 20   |      |     | mA |

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                  | テスト条件                                                                  | 最小値 | 標準値  | 最大値     | 単位       |

|------------------------|------------------------------------------------------------------------|-----|------|---------|----------|

| $I_{(I^2C)}$           | 入力電流<br>$0.1 \times V_{(I^2C)} < \text{入力電圧} < 3.3V$                   | -1  | 1    | $\mu A$ |          |

| $C_{(I^2C)}$           | 入力容量                                                                   |     | 10   | $pF$    |          |

| $C_{(I^2C\_FM+, BUS)}$ | FM+(1MHz) での I <sup>2</sup> C バス容量                                     |     | 150  | $pF$    |          |

| $C_{(I^2C\_FM\_BUS)}$  | FM (400kHz) での I <sup>2</sup> C バス容量                                   |     | 150  | $pF$    |          |

| $R_{(EXT\_I^2C\_FM+)}$ | FM+(1MHz) で動作時の SDA と SCL の両方の外付け抵抗<br>$C_{(I^2C\_FM+, BUS)} = 150pF$  | 620 | 820  | 910     | $\Omega$ |

| $R_{(EXT\_I^2C\_FM)}$  | FM+(400kHz) で動作時の SDA と SCL の両方の外付け抵抗<br>$C_{(I^2C\_FM\_BUS)} = 150pF$ | 620 | 1500 | 2200    | $\Omega$ |

## 5.7 USB および DP の電気的特性

自由気流での動作温度および電圧範囲内 (特に記述のない限り)

| パラメータ                                             | テスト条件                                                  | 最小値                                                                 | 標準値  | 最大値  | 単位    |

|---------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------|------|------|-------|

| <b>USB Gen 2 差動レシーバ (RX1p/n, RX2p/n, SSTXp/n)</b> |                                                        |                                                                     |      |      |       |

| $V_{(RX-DIFF-PP)}$                                | 入力差動ピーク ツー ピーク電圧スイングの線形ダイナミックレンジ                       | AC 結合の差動ピーク ツー ピーク信号を、リファレンス チャネルを通過した CTLE 後で測定                    | 1200 |      | mVppd |

| $V_{(RX-DC-CM)}$                                  | レシーバの同相電圧バイアス (DC)                                     |                                                                     | 0    |      | V     |

| $V_{RX\_CM-INST}$                                 | 次の動作状態での最大瞬時 RX DC 同相電圧変化:オフからオン、無効から接続解除、U3 から接続解除。   | 200kΩ 負荷を使用して、AC 結合コンデンサのリドライバ以外の側で測定。                              | -500 | 1000 | mV    |

| $V_{RX\_CM-INST}$                                 | 次の動作状態での最大瞬時 RX DC 同相電圧変化:接続解除から U0、U0 から U3、U3 から U0。 | 50Ω 負荷を使用して、AC 結合コンデンサのリドライバ以外の側で測定。                                | -300 | 1000 | mV    |

| $R_{(RX-DIFF-DC)}$                                | 差動入力インピーダンス (DC)                                       | TXP/TXN で USB3 デバイスが検出された後に存在                                       | 72   | 90   | 120   |

| $R_{(RX-CM-DC)}$                                  | レシーバの DC コモン モード インピーダンス                               | TXP/TXN で USB3 デバイスが検出された後に存在                                       | 18   | 30   | Ω     |

| $Z_{(RX-HIGH-IMP-DC-POS)}$                        | 終端がディスエーブルの場合のコモン モード入力インピーダンス (DC)                    | TXP/TXN で USB3 デバイスが検出されない場合に存在。GND に対して 0V~500mV の範囲にわたって測定。       | 25   |      | kΩ    |

| $V_{(SIGNAL-DET-DIFF-PP)}$                        | 入力差動ピーク ツー ピーク信号検出のアサート レベル                            | 5Gbps で、入力損失なし、PRBS7 パターン                                           | 80   |      | mVppd |

| $V_{(RX-IDLE-DET-DIFF-PP)}$                       | 入力差動ピーク ツー ピーク信号検出のデアサート レベル                           | 5Gbps で、入力損失なし、PRBS7 パターン                                           | 60   |      | mVppd |

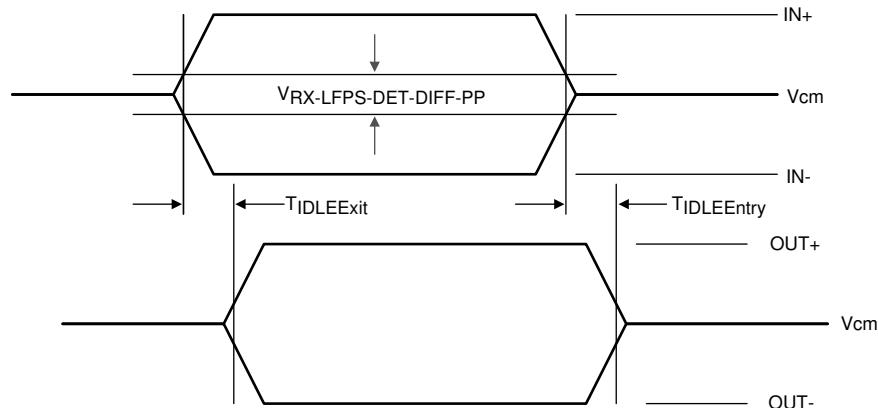

| $V_{(RX-LFPS-DET-DIFF-PP)}$                       | 低周波数周期信号 (LFPS) 検出スレッシュホールド                            | VCC = 3.3V、25°C ≤ TA ≤ 105°C、25MHz および 300mVppd VIN でテスト、最小値未満はスケルチ | 100  | 300  | mVppd |

| $V_{(RX-CM-AC-P)}$                                | ピーク RX AC 同相電圧                                         | パッケージビンで測定                                                          |      | 150  | mVppd |

| $R_{L(RX-DIFF)}$                                  | 差動リターン ロス                                              | 90Ω で 50MHz から 1.25GHz、                                             | -19  |      | dB    |

| $R_{L(RX-DIFF)}$                                  | 差動リターン ロス                                              | 90Ω で 2.5GHz、                                                       | -15  |      | dB    |

| $R_{L(RX-CM)}$                                    | 同相リターン ロス                                              | 90Ω で 50MHz から 2.5GHz、                                              | -10  |      | dB    |

| $E_{Q\_SSTX0}$                                    | 100MHz での SSTX レシーバ イコライゼーション                          | FLIPSEL = 0, SSEQ_SEL = 0、                                          | 1.8  |      | dB    |

| $E_{Q\_SSTX0}$                                    | 100MHz での SSTX レシーバ イコライゼーション                          | FLIPSEL = 1, SSEQ_SEL = 0、                                          | 2.1  |      | dB    |

| $E_{Q\_SSTX15}$                                   | 100MHz での SSTX レシーバ イコライゼーション                          | FLIPSEL = 0, SSEQ_SEL = 15、                                         | 3.6  |      | dB    |

| $E_{Q\_SSTX15}$                                   | 100MHz での SSTX レシーバ イコライゼーション                          | FLIPSEL = 1, SSEQ_SEL = 15、                                         | 4.0  |      | dB    |

| $E_{Q\_SSTX15}$                                   | 2.5GHz での SSTX レシーバ イコライゼーション                          | FLIPSEL = 0, SSEQ_SEL = 15、                                         | 12.0 |      | dB    |

| $E_{Q\_SSTX15}$                                   | 2.5GHz での SSTX レシーバ イコライゼーション                          | FLIPSEL = 1, SSEQ_SEL = 15、                                         | 12.2 |      | dB    |

| $E_{Q\_RX0}$                                      | 100MHz での RX1 レシーバ イコライゼーション                           | FLIPSEL = 0, EQ1_SEL = 0、                                           | 1.7  |      | dB    |

| $E_{Q\_RX15}$                                     | 100MHz での RX1 レシーバ イコライゼーション                           | FLIPSEL = 0, EQ1_SEL = 15、                                          | 3.5  |      | dB    |

| $E_{Q\_RX15}$                                     | 2.5GHz での RX1 レシーバ イコライゼーション                           | FLIPSEL = 0, EQ1_SEL = 15、                                          | 11.6 |      | dB    |

| $E_{Q\_RX0}$                                      | 100MHz での RX2 レシーバ イコライゼーション                           | FLIPSEL = 1, EQ2_SEL = 0、                                           | 2.0  |      | dB    |

| $E_{Q\_RX15}$                                     | 100MHz での RX2 レシーバ イコライゼーション                           | FLIPSEL = 1, EQ2_SEL = 15、                                          | 3.8  |      | dB    |

| $E_{Q\_RX15}$                                     | 2.5GHz での RX2 レシーバ イコライゼーション                           | FLIPSEL = 1, EQ2_SEL = 15、                                          | 11.4 |      | dB    |

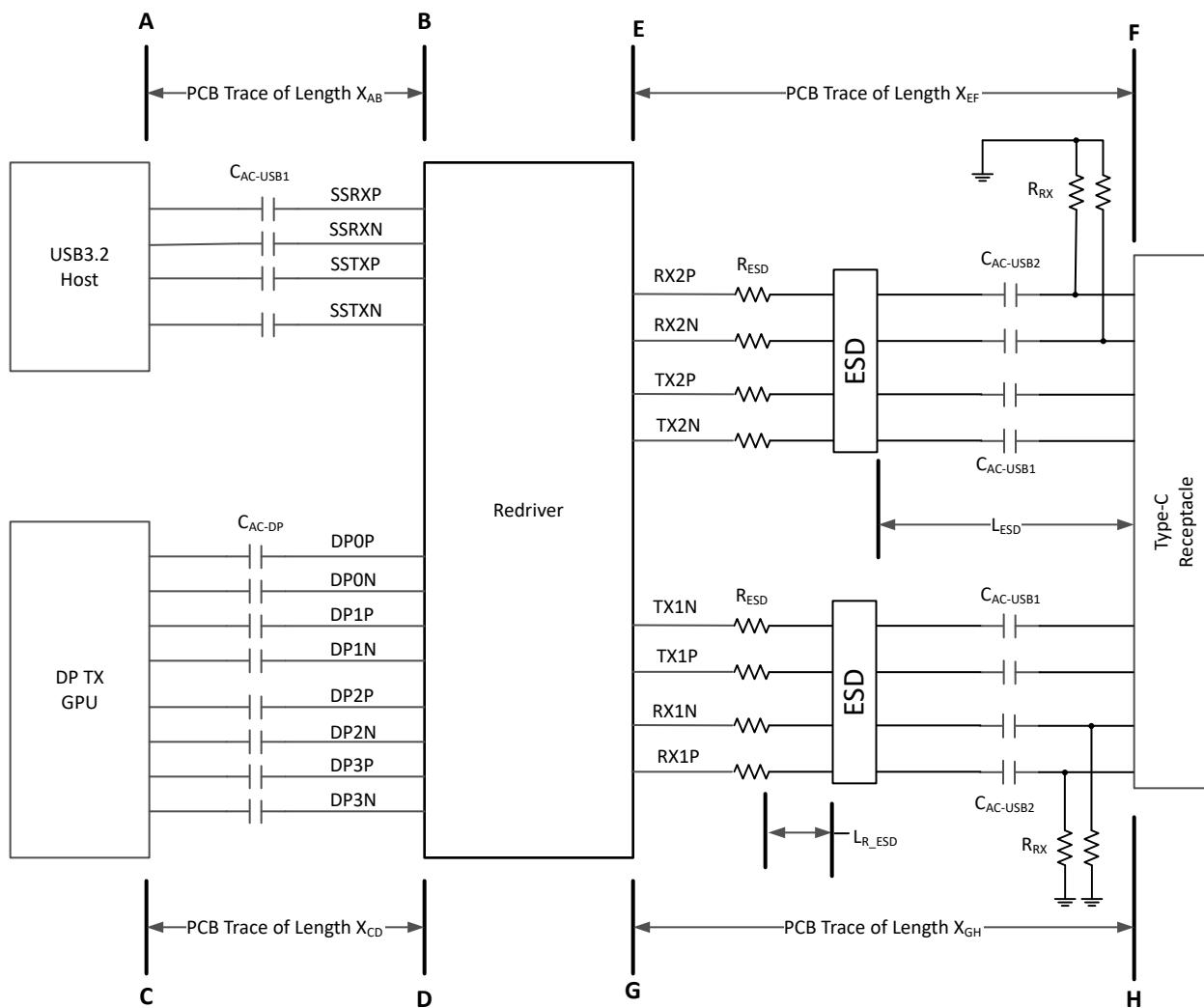

| $C_{AC-USB1}$                                     | SSTX に外部 AC カップリング コンデンサが必要                            |                                                                     | 75   | 265  | nF    |

自由気流での動作温度および電圧範囲内 (特に記述のない限り)

| パラメータ                                             | テスト条件                                                         | 最小値                                                                                                      | 標準値   | 最大値  | 単位    |

|---------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------|------|-------|

| C <sub>AC-USB2</sub>                              | RX1 および RX2 にオプションの外部 AC カップリング コンデンサを接続可能。                   | 297                                                                                                      | 363   | nF   |       |

| <b>USB Gen 2 差動トランシッタ (TX1p/n、TX2p/n、SSRXp/n)</b> |                                                               |                                                                                                          |       |      |       |

| V <sub>TX(DIFF-PP)</sub>                          | トランシッタのダイナミック差動電圧スイング範囲。                                      | 1200                                                                                                     | mVppd |      |       |

| V <sub>TX(RCV-DETECT)</sub>                       | レシーバの検出中に許容される電圧の変化量                                          | T <sub>A</sub> = 25°C 時、                                                                                 | 600   | mV   |       |

| V <sub>TX-CM-INST</sub>                           | 次の動作状態での最大瞬時 TX DC 同相電圧変化: オフからオン、オンからオフ、無効から接続解除、U3 から接続解除。  | 200kΩ 負荷を使用して、AC 結合コンデンサのリドライバ以外の側でシングル エンドを測定。                                                          | -500  | 1000 | mV    |

| V <sub>TX-CM-INST</sub>                           | 次の動作状態での最大瞬時 TX DC 同相電圧変化: 接続解除から U0、U0 から U2/U3、U2/U3 から U0。 | 50Ω 負荷を使用して、AC 結合コンデンサのリドライバ以外の側でシングル エンドを測定。                                                            | -300  | 1000 | mV    |

| V <sub>TX(CM-IDLE-DELTA)</sub>                    | U2/U3 で LPFS をアクティブに送信していない状態でのトランシッタのアイドル同相電圧変化              |                                                                                                          | -300  | 600  | mV    |

| V <sub>TX(DC-CM)</sub>                            | トランシッタの同相電圧バイアス (DC)                                          |                                                                                                          | 0.5   | 1.1  | V     |

| V <sub>TX(CM-AC-PP-ACTIVE)</sub>                  | Tx AC 同相電圧 (アクティブ時)                                           | 時間と振幅の両方に関する T <sub>xp</sub> + T <sub>xn</sub> からの最大不一致                                                  |       | 100  | mVpp  |

| V <sub>TX(IDLE-DIFF-AC-PP)</sub>                  | AC 電気的アイドル時の差動ピークツーピーク出力電圧                                    | DC 成分を除去するハイパス フィルタ (HPF) 後のパッケージ ピンの場合、HPF = 1/LPF、RX 端子に AC または DC 信号を印加しない。                           | 0     | 10   | mV    |

| V <sub>TX(IDLE-DIFF-DC)</sub>                     | DC 電気的アイドル時の差動出力電圧                                            | AC 成分を除去するローパス フィルタ (LPF) 後のパッケージ ピンの場合、LPF = 1/HPF、RX 端子に AC または DC 信号を印加しない。                           | 0     | 14   | mV    |

| V <sub>TX(CM-DC-ACTIVE-IDLE-DELTA)</sub>          | U1 と U0 との間の絶対 DC 同相電圧                                        | パッケージ ピンの場合                                                                                              |       | 200  | mV    |

| R <sub>TX(DIFF)</sub>                             | ドライバの差動インピーダンス                                                |                                                                                                          | 72    | 90   | Ω     |

| R <sub>TX(CM)</sub>                               | ドライバのコモン モード インピーダンス                                          | 0V~500mV の AC グランドを基準として測定                                                                               | 18    | 30   | Ω     |

| V <sub>SSRX-LIMITED-VODL0</sub>                   | 制限付きリドライバと LINR_L0 用に構成した場合の SSRX 差動ピークツーピーク電圧                | TX_PRESHOOT_EN = 0、<br>TX_DEEMPHASIS_EN = 0、                                                             |       | 725  | mVppd |

| V <sub>SSRX-LIMITED-VODL1</sub>                   | 制限付きリドライバと LINR_L1 用に構成した場合の SSRX 差動ピークツーピーク電圧                | TX_PRESHOOT_EN = 0、<br>TX_DEEMPHASIS_EN = 0、                                                             |       | 850  | mVppd |

| V <sub>SSRX-LIMITED-VODL2</sub>                   | 制限付きリドライバと LINR_L2 用に構成した場合の SSRX 差動ピークツーピーク電圧                | TX_PRESHOOT_EN = 0、<br>TX_DEEMPHASIS_EN = 0、                                                             |       | 1000 | mVppd |

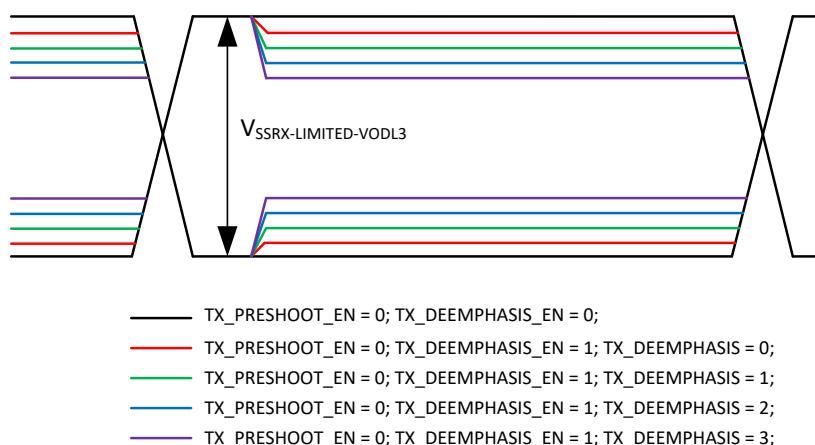

| V <sub>SSRX-LIMITED-VODL3</sub>                   | 制限付きリドライバと LINR_L3 用に構成した場合の SSRX 差動ピークツーピーク電圧                | TX_PRESHOOT_EN = 0、<br>TX_DEEMPHASIS_EN = 0、                                                             |       | 1100 | mVppd |

| V <sub>SSRX-DE-RATIO0</sub>                       | 制限付きリドライバおよびディエンファシスがイネーブルになるように構成されている場合の SSRX ディエンファシス。     | TX_PRESHOOT_EN = 0、<br>TX_DEEMPHASIS_EN = 1、<br>TX_DEEPHASIS = 2'b00、<br>USB_SSRX_VOD = 2'b00 (LINR_L3)、 |       | -1.5 | dB    |

| V <sub>SSRX-DE-RATIO1</sub>                       | 制限付きリドライバおよびディエンファシスがイネーブルになるように構成されている場合の SSRX ディエンファシス。     | TX_PRESHOOT_EN = 0、<br>TX_DEEMPHASIS_EN = 1、<br>TX_DEEPHASIS = 2'b01、<br>USB_SSRX_VOD = 2'b00 (LINR_L3)、 |       | -2.1 | dB    |

| V <sub>SSRX-DE-RATIO2</sub>                       | 制限付きリドライバおよびディエンファシスがイネーブルになるように構成されている場合の SSRX ディエンファシス。     | TX_PRESHOOT_EN = 0、<br>TX_DEEMPHASIS_EN = 1、<br>TX_DEEPHASIS = 2'b10、<br>USB_SSRX_VOD = 2'b00 (LINR_L3)、 |       | -3.2 | dB    |

自由気流での動作温度および電圧範囲内 (特に記述のない限り)

| パラメータ                   |                                                                  | テスト条件                                                                                                                          | 最小値 | 標準値   | 最大値 | 単位    |

|-------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|-------|

| $V_{SSRX-DE-RATIO3}$    | 制限付きリドライバおよびディエンファシスがイネーブルになるように構成されている場合の <b>SSRX</b> ディエンファシス。 | TX_PRESHOOT_EN = 0,<br>TX_DEEMPHASIS_EN = 1,<br>TX_DEEPHASIS = 2'b11,<br>USB_SSRX_VOD = 2'b00 (LINR_L3),                       |     | -3.8  |     | dB    |

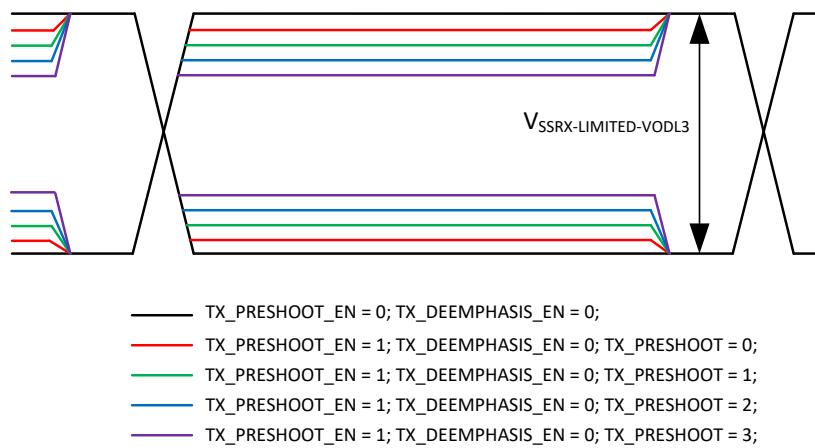

| $V_{SSRX-PRESH-RATIO0}$ | 制限付きリドライバおよびプリショートがイネーブルになるように構成されている場合の <b>SSRX</b> プリショートレベル。  | TX_PRESHOOT_EN = 1,<br>TX_DEEMPHASIS_EN = 0,<br>TX_PRESHOOT = 2'b00,<br>USB_SSRX_VOD = 2'b00 (LINR_L3),                        |     | 1.5   |     | dB    |

| $V_{SSRX-PRESH-RATIO1}$ | 制限付きリドライバおよびプリショートがイネーブルになるように構成されている場合の <b>SSRX</b> プリショートレベル。  | TX_PRESHOOT_EN = 1,<br>TX_DEEMPHASIS_EN = 0,<br>TX_PRESHOOT = 2'b01,<br>USB_SSRX_VOD = 2'b00 (LINR_L3),                        |     | 2.0   |     | dB    |

| $V_{SSRX-PRESH-RATIO2}$ | 制限付きリドライバおよびプリショートがイネーブルになるように構成されている場合の <b>SSRX</b> プリショートレベル。  | TX_PRESHOOT_EN = 1,<br>TX_DEEMPHASIS_EN = 0,<br>TX_PRESHOOT = 2'b10,<br>USB_SSRX_VOD = 2'b00 (LINR_L3),                        |     | 2.3   |     | dB    |

| $V_{SSRX-PRESH-RATIO3}$ | 制限付きリドライバおよびプリショートがイネーブルになるように構成されている場合の <b>SSRX</b> プリショートレベル。  | TX_PRESHOOT_EN = 1,<br>TX_DEEMPHASIS_EN = 0,<br>TX_PRESHOOT = 2'b11,<br>USB_SSRX_VOD = 2'b00 (LINR_L3),                        |     | 2.8   |     | dB    |

| $I_{TX(SHORT)}$         | TX 短絡電流                                                          | TX± は GND へ短絡                                                                                                                  |     | 40    |     | mA    |

| $R_{LTX(DIFF)}$         | 差動リターン ロス                                                        | 50MHz~1.25GHz (90Ω 時)                                                                                                          |     | -20   |     | dB    |

| $R_{LTX(DIFF)}$         | 差動リターン ロス                                                        | 90Ω で 2.5GHz                                                                                                                   |     | -20   |     | dB    |

| $R_{LTX(CM)}$           | 同相リターン ロス                                                        | 50MHz~2.5GHz (90Ω 時)                                                                                                           |     | -8.5  |     | dB    |

| $C_{TX-AC(COUPING)}$    | 必須の外付け AC カップリング コンデンサ                                           |                                                                                                                                | 75  | 265   |     | nF    |

| <b>AC の特性</b>           |                                                                  |                                                                                                                                |     |       |     |       |

| クロストーク                  | TX と RX 信号のペア間の差動クロストーク                                          | 2.5GHz 時、EQ = 0,                                                                                                               |     | -40   |     | dB    |

| $CP_{LF-LINRL0}$        | LINR_L0 設定時の低周波数における -1dB 圧縮ポイント。                                | 100MHz、200mVpp < $V_{ID}$ < 1200mVpp, EQ = 0                                                                                   |     | 750   |     | mVppd |

| $CP_{HF-LINRL0}$        | LINR_L0 設定時の高周波数における -1dB 圧縮ポイント。                                | 2.5GHz、200mVpp < $V_{ID}$ < 1200mVpp, EQ = 0                                                                                   |     | 725   |     | mVppd |

| $CP_{HF-LINRL0}$        | LINR_L0 設定時の高周波数における -1dB 圧縮ポイント。                                | 5GHz、200mVpp < $V_{ID}$ < 1200mVpp, EQ = 0                                                                                     |     | 675   |     | mVppd |

| $CP_{LF-LINRL1}$        | LINR_L1 設定時の低周波数における -1dB 圧縮ポイント。                                | 100MHz、200mVpp < $V_{ID}$ < 1200mVpp, EQ = 0                                                                                   |     | 850   |     | mVppd |

| $CP_{HF-LINRL1}$        | LINR_L1 設定時の高周波数における -1dB 圧縮ポイント。                                | 2.5GHz、200mVpp < $V_{ID}$ < 1200mVpp, EQ = 0                                                                                   |     | 825   |     | mVppd |

| $CP_{HF-LINRL1}$        | LINR_L1 設定時の高周波数における -1dB 圧縮ポイント。                                | 5GHz、200mVpp < $V_{ID}$ < 1200mVpp, EQ = 0                                                                                     |     | 740   |     | mVppd |

| $CP_{LF-LINRL2}$        | LINR_L2 設定時の低周波数における -1dB 圧縮ポイント。                                | 100MHz、200mVpp < $V_{ID}$ < 1200mVpp, EQ = 0                                                                                   |     | 975   |     | mVppd |

| $CP_{HF-LINRL2}$        | LINR_L2 設定時の高周波数における -1dB 圧縮ポイント。                                | 2.5GHz、200mVpp < $V_{ID}$ < 1200mVpp, EQ = 0                                                                                   |     | 950   |     | mVppd |

| $CP_{HF-LINRL2}$        | LINR_L2 設定時の高周波数における -1dB 圧縮ポイント。                                | 5GHz、200mVpp < $V_{ID}$ < 1200mVpp, EQ = 0                                                                                     |     | 800   |     | mVppd |

| $CP_{LF-LINRL3}$        | LINR_L3 設定時の低周波数における -1dB 圧縮ポイント。                                | 100MHz、200mVpp < $V_{ID}$ < 1200mVpp, EQ = 0                                                                                   |     | 1050  |     | mVppd |

| $CP_{HF-LINRL3}$        | LINR_L3 設定時の高周波数における -1dB 圧縮ポイント。                                | 2.5GHz、200mVpp < $V_{ID}$ < 1200mVpp, EQ = 0                                                                                   |     | 980   |     | mVppd |

| $CP_{HF-LINRL3}$        | LINR_L3 設定時の高周波数における -1dB 圧縮ポイント。                                | 5GHz、200mVpp < $V_{ID}$ < 1200mVpp, EQ = 0                                                                                     |     | 775   |     | mVppd |

| $t_{TX\_DJ}$            | TX 出力の確定的残留ジッタ                                                   | $V_{ID} = 1Vppd$ 、最適な EQ 設定、12 インチ プリチャネル (5GHz で SDD21 = -11.2dB)、1.6 インチ ポスト チャネル (5GHz で SDD21 = -1.8dB)、PRBS7、5Gbps で USB3 |     | 0.025 |     | UI    |

自由気流での動作温度および電圧範囲内 (特に記述のない限り)

| パラメータ                                                    |                                                                                        | テスト条件                                                                                                                     | 最小値   | 標準値  | 最大値 | 単位   |

|----------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------|------|-----|------|

| $t_{TX\_DJ}$                                             | TX 出力の確定的残留ジッタ                                                                         | VID = 0.8Vppd、最適な EQ 設定、12 インチ ブリチャネル (5GHz で SDD21 = -8.2dB)、1.6 インチ ポスト チャネル (5GHz で SDD21 = -1.8dB)、PRBS7、8.1Gbps で DP |       | 0.06 |     | UI   |

| <b>DisplayPort レシーバ(DP[3:0]p/n)</b>                      |                                                                                        |                                                                                                                           |       |      |     |      |

| $V_{ID(PP)}$                                             | ピークツー ピークの入力差動ダイナミック電圧範囲                                                               |                                                                                                                           |       | 1400 |     | V    |

| $V_{IC}$                                                 | 入力同相電圧                                                                                 |                                                                                                                           | 0.8   | 1.75 | 2   | V    |

| $V_{RX\_CM-INST}$                                        | 次の動作状態での最大瞬時 RX DC 同相電圧変化: オフからオン、ディスエーブルから 4DP 低電力、4DP アクティブからディスエーブル。 <sup>(1)</sup> | 200kΩ 負荷を使用して、AC 結合コンデンサのリドライバ以外の側でシングル エンドを測定。                                                                           | -1200 | 1000 |     | mV   |

| $V_{RX\_CM-INST}$                                        | 次の動作状態での最大瞬時 RX DC 同相電圧変化: ディスエーブルから 4DP アクティブ (D0)、D0 から D3、D3 から D0。                 | 50Ω 負荷を使用して、AC 結合コンデンサのリドライバ以外の側でシングル エンドを測定。                                                                             | -500  | 1000 |     | mV   |

| $d_R$                                                    | データ レート                                                                                |                                                                                                                           |       |      | 8.1 | Gbps |

| $R_{(ti)}$                                               | 入力端末抵抗                                                                                 |                                                                                                                           | 72    | 90   | 110 | Ω    |

| $C_{(AC)}$                                               | 必須の外付け AC カップリング コンデンサ                                                                 |                                                                                                                           | 75    | 265  |     | nF   |

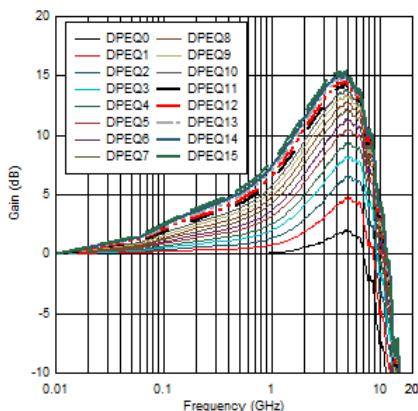

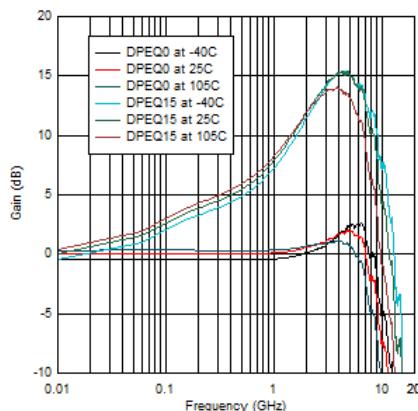

| $E_{Q\_DP0}$                                             | 100MHz での DP0 レシーバ イコライゼーション                                                           | FLIPSEL = 0、DP0EQ_SEL = 0、                                                                                                |       | -0.2 |     | dB   |

| $E_{Q\_DP15}$                                            | 100MHz での DP0 レシーバ イコライゼーション                                                           | FLIPSEL = 0、DP0EQ_SEL = 15                                                                                                |       | 2.3  |     | dB   |

| $E_{Q\_DP0}$                                             | 4.05GHz での DP0 レシーバ イコライゼーション                                                          | FLIPSEL = 0、DP0EQ_SEL = 0、                                                                                                |       | 0.6  |     | dB   |

| $E_{Q\_DP15}$                                            | 4.05GHz での DP0 レシーバ イコライゼーション                                                          | FLIPSEL = 0、DP0EQ_SEL = 15                                                                                                |       | 14.5 |     | dB   |

| <b>DisplayPort トランスマッタ (TX1p/n、TX2p/n、RX1p/n、RX2p/n)</b> |                                                                                        |                                                                                                                           |       |      |     |      |

| $V_{TX-CM-INST}$                                         | 次の動作状態での最大瞬時 TX DC 同相電圧変化: ディスエーブルから 4DP アクティブ (D0)、D0 から D3、D3 から D0。                 | 50Ω 負荷を使用して、AC 結合コンデンサのリドライバ以外の側で測定。                                                                                      | -500  | 1000 |     | mV   |

| $V_{TX-CM-INST}$                                         | 次の動作状態での最大瞬時 TX DC 同相電圧変化: ディスエーブルから 4DP 低電力、4DP アクティブからディスエーブル                        | 200kΩ 負荷を使用して、AC 結合コンデンサのリドライバ以外の側で測定。                                                                                    | -1000 | 1000 |     | mV   |

| $V_{TX(DC-CM)}$                                          | トランスマッタの同相電圧バイアス (DC)                                                                  |                                                                                                                           | 0.6   | 1    |     | V    |

| $R_{TX(DIFF)}$                                           | ドライバの差動インピーダンス                                                                         |                                                                                                                           | 72    | 90   | 120 | Ω    |

| <b>AUXp または AUXn と SBU1 または SBU2</b>                     |                                                                                        |                                                                                                                           |       |      |     |      |

| $R_{ON}$                                                 | 出力オン抵抗                                                                                 | $V_{CC} = 3.3V$ 、AUXp の $V_I = 0V \sim 0.4V$ 、<br>AUXn の $V_I = 2.7V \sim 3.6V$                                           |       |      | 6   | Ω    |

| $\Delta R_{ON}$                                          | ペア内でのオン抵抗の不整合                                                                          | $V_{CC} = 3.3V$ 、AUXP の $V_I = 0V \sim 0.4V$ 、<br>AUXN の $V_I = 2.7V \sim 3.6V$                                           |       |      | 1.0 | Ω    |

| $R_{ON(FLAT)}$                                           | オン抵抗の平坦性 ( $R_{ON}$ の最大値 - $R_{ON}$ の最小値) は、VCC と温度が同じ状況で測定                            | $V_{CC} = 3.3V$ 、AUXp の $V_I = 0V \sim 0.4V$ 、<br>AUXn の $V_I = 2.7V \sim 3.6V$                                           |       |      | 1.0 | Ω    |

| $V_{(AUXP\_DC\_CM)}$                                     | AUXp と SBU1 の AUX チャネル DC 同相電圧。                                                        | $V_{CC} = 3.3V$ 、                                                                                                         | 0     | 0.4  |     | V    |

| $V_{(AUXN\_DC\_CM)}$                                     | AUXn と SBU2 の AUX チャネル DC 同相電圧                                                         | $V_{CC} = 3.3V$ 、                                                                                                         | 2.7   | 3.6  |     | V    |

(1) DPTX 終端を無効にする前にリドライバを無効にすることで、GPU (DPTX) が観測する瞬間的な同相変位を最小化できます。

## 5.8 タイミング要件

|                 |                   |                 | 最小値 | 公称値 | 最大値 | 単位 |

|-----------------|-------------------|-----------------|-----|-----|-----|----|

| <b>USB3.2</b>   |                   |                 |     |     |     |    |

| $t_{IDLEEntry}$ | U0 から電気的アイドルまでの遅延 | 図 6-4 を参照してください |     | 10  |     | ns |

|                       |                                             |                                                    | 最小値 | 公称値 | 最大値 | 単位 |

|-----------------------|---------------------------------------------|----------------------------------------------------|-----|-----|-----|----|

| $t_{IDLEExit\_U1}$    | U1 既存時間: 電気的アイドルのブレークから LFPS の転送まで          | 図 6-4 を参照してください                                    |     | 6   |     | ns |

| $t_{IDLEExit\_U2U3}$  | U2/U3 終了時間: 電気的アイドル状態のブレークから LFPS の転送まで     | 図 6-4 を参照してください                                    |     | 10  |     | μs |

| $t_{RXDET\_INTVL}$    | 切断中の RX 検出間隔                                |                                                    |     | 12  |     | ms |

| $t_{IDLEExit\_DISC}$  | 切断終了時間                                      |                                                    |     | 10  |     | μs |

| $t_{Exit\_SHTDN}$     | シャットダウン終了時間                                 |                                                    |     | 1   |     | ms |

| $t_{AEQ\_FULL\_DONE}$ | フル AEQ モードでの動作時に最適な EQ 設定を得るための最大時間。        |                                                    |     | 300 |     | μs |

| $t_{AEQ\_FAST\_DONE}$ | 高速 AEQ モードでの動作時に適切な EQ 設定を決定するための最大時間。      |                                                    |     | 60  |     | μs |

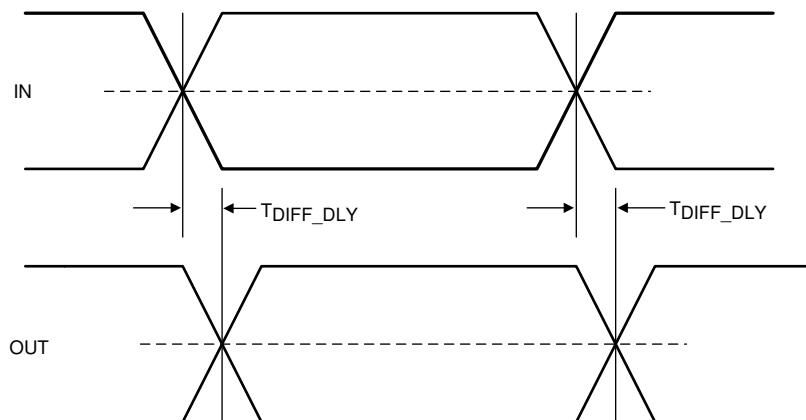

| $t_{DIFF\_DLY}$       | 差動伝搬遅延                                      | 図 6-3 を参照してください                                    |     | 300 |     | ps |

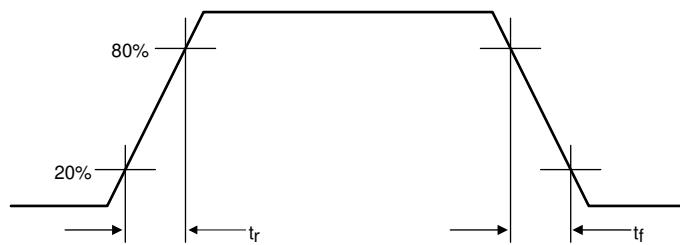

| $t_R, t_F$            | 出力立ち上がり / 立ち下がり時間                           | 出力ピンから 1.7 インチで測定された差動電圧の 20%~80% 図 6-5 を参照してください。 |     | 40  |     | ps |

| $t_{RF\_MM}$          | 出力立ち上がり / 立ち下がり時間の不一致                       | 出力ピンから 1.7 インチで測定された差動電圧の 20%~80%                  |     | 2.6 |     | ps |

| <b>パワーアップ</b>         |                                             |                                                    |     |     |     |    |

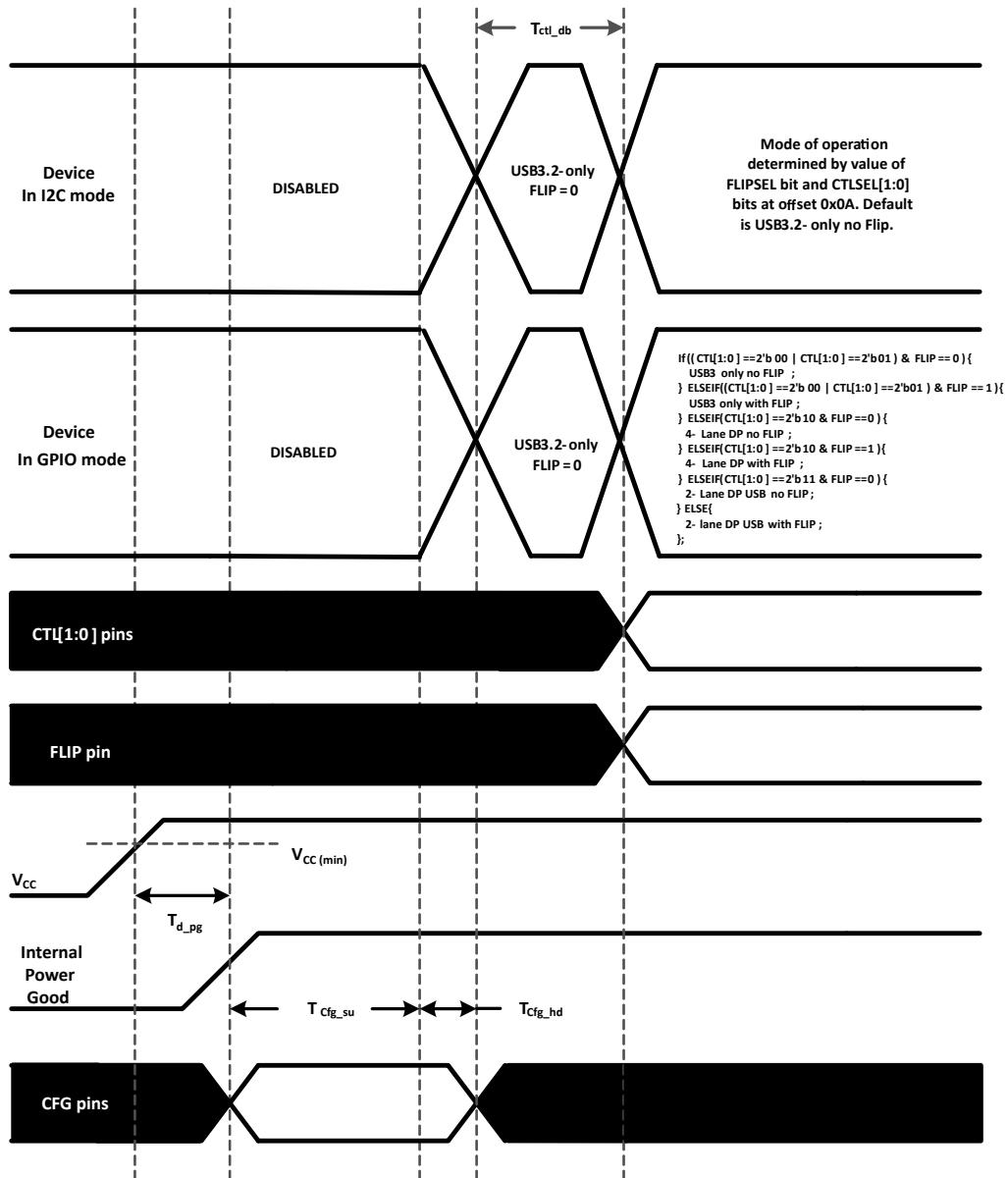

| $t_{D\_PG}$           | $V_{CC}$ (min) から内部パワー グッドが High にアサートされるまで | 図 6-10 を参照してください                                   |     | 27  |     | ms |

| $t_{CFG\_SU}$         | CFG <sup>(1)</sup> ピンの設定 <sup>(2)</sup>     | 図 6-10 を参照してください                                   |     | 800 |     | μs |

| $t_{CFG\_HD}$         | CFG <sup>(1)</sup> ピンホールド                   | 図 6-10 を参照してください                                   |     | 10  |     | μs |

| $t_{CTL\_DB}$         | CTL[1:0] と FLIP ピンのデバウンス                    | 図 6-10 を参照してください                                   |     | 16  |     | ms |

(1) 以下のピンは CFG ピンで構成されます。 I2C\_EN、EQ[1:0]、SSEQ[1:0]、および DPEQ[1:0]。

(2) 推奨される CFG ピンは、 $V_{CC}$  が最小のとき安定するようにしてください。

## 5.9 スイッチング特性

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                                          | テスト条件                                                                      | 最小値                       | 標準値  | 最大値 | 単位  |

|------------------------------------------------|----------------------------------------------------------------------------|---------------------------|------|-----|-----|

| <b>AUXp または AUXn と SBU1 または SBU2</b>           |                                                                            |                           |      |     |     |

| $t_{AUX\_PD}$                                  | スイッチ伝搬遅延                                                                   |                           |      | 400 | ps  |

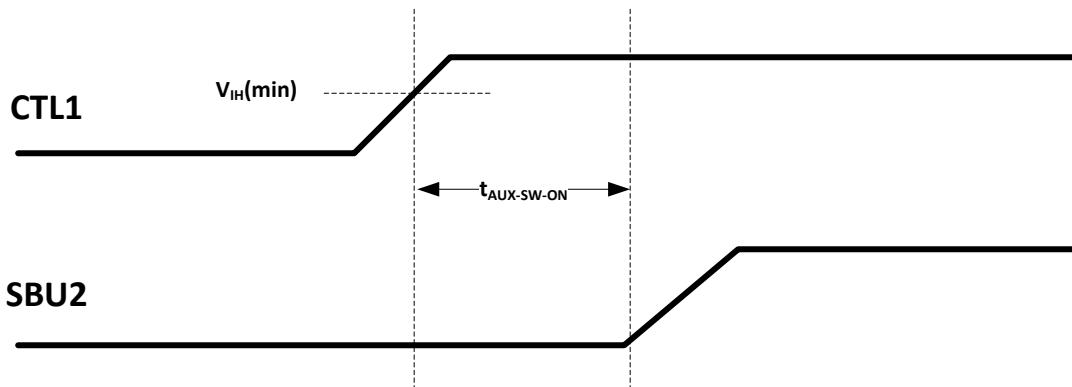

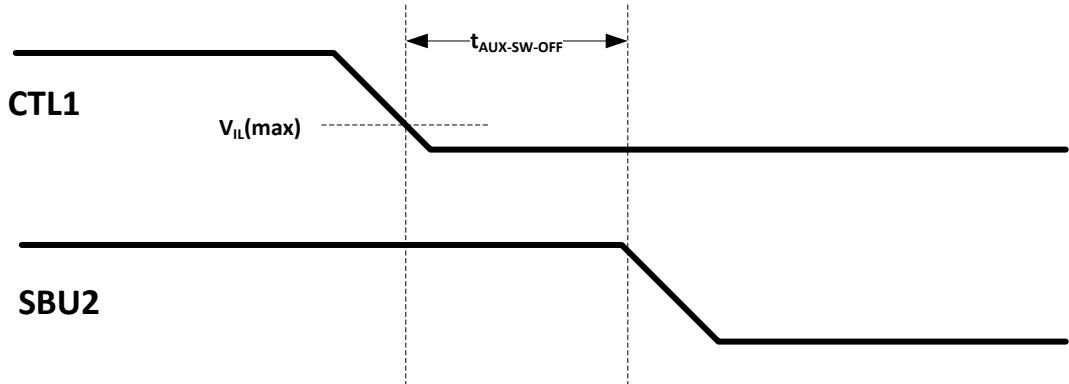

| $t_{AUX\_SW\_OFF}$                             | CTL1 からスイッチ オフになるまでのスイッチング時間。 TCTL1_DEBOUNCE は含まれません                       | 図 6-7 を参照してください。          |      | 500 | ns  |

| $t_{AUX\_SW\_ON}$                              | CTL1 からスイッチオンになるまでのスイッチング時間                                                | 図 6-6 を参照してください。          |      | 500 | ns  |

| <b>USB および DisplayPort モードの遷移要件 (GPIO モード)</b> |                                                                            |                           |      |     |     |

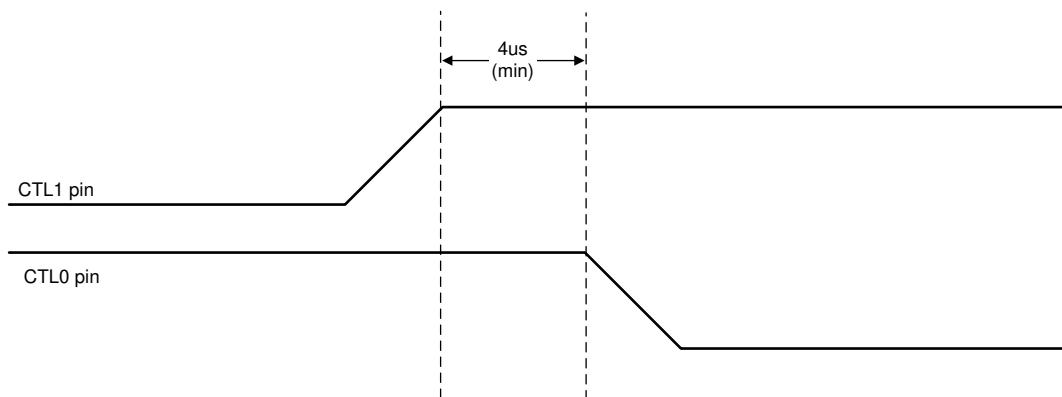

| $t_{GP\_USB\_4DP}$                             | USB3 専用モードから 4 レーン DisplayPort モードへ、またはその逆に遷移するときの CTL0 と CTL1 の最小オーバーラップ。 | $I2C\_EN = 0$ 。図 6-2 を参照。 | 4    |     | μs  |

| <b>CTL1 および HPDIN</b>                          |                                                                            |                           |      |     |     |

| $t_{HPDIN\_DEBOUNCE}$                          | H から L に遷移するときの CTL1 および HPDIN デバウンス時間。                                    |                           | 2    | 10  | ms  |

| <b>I<sup>2</sup>C</b>                          |                                                                            |                           |      |     |     |

| $f_{SCL}$                                      | I <sup>2</sup> C クロック周波数                                                   |                           |      | 1   | MHz |

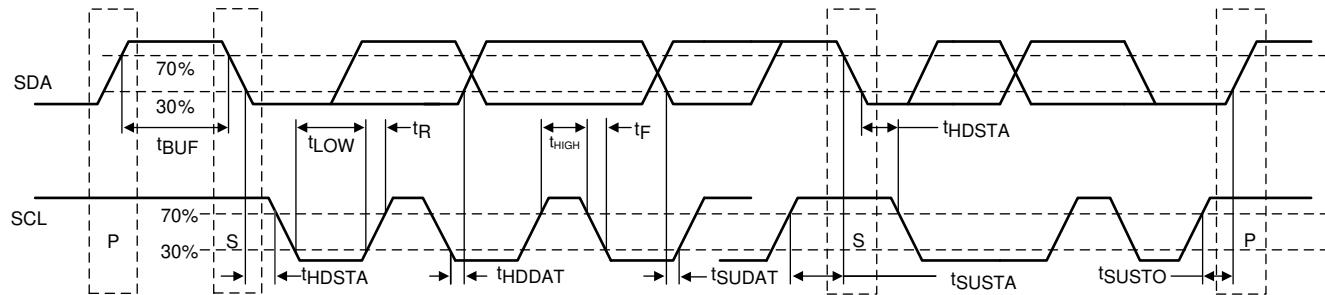

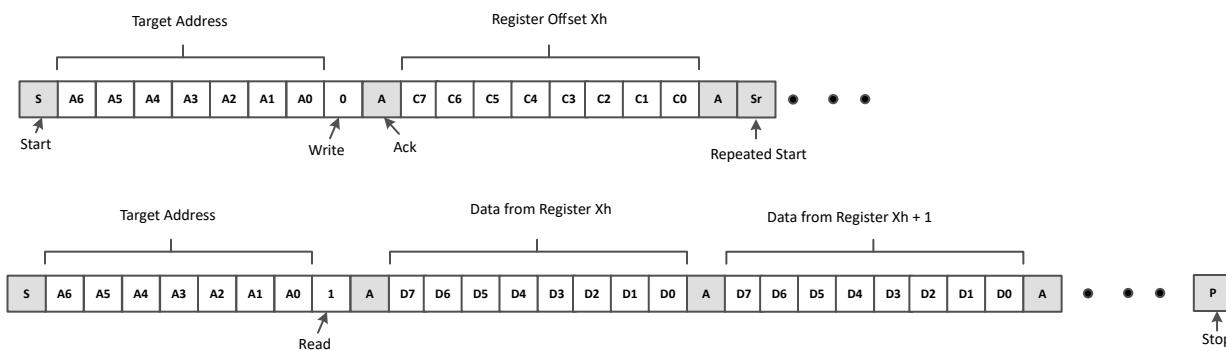

| $t_{BUF}$                                      | START 条件と STOP 条件の間でのバス開放時間                                                | 図 6-1 を参照してください           | 0.5  |     | μs  |

| $t_{HDSTA}$                                    | リピートスタートコンディションの後のホールド時間。この時間が経過すると、最初のクロック パルスが生成されます                     | 図 6-1 を参照してください           | 0.26 |     | μs  |

| $t_{LOW}$                                      | I <sup>2</sup> C クロックの Low 時間                                              | 図 6-1 を参照してください           | 0.5  |     | μs  |

| $t_{HIGH}$                                     | I <sup>2</sup> C クロックの High 時間                                             | 図 6-1 を参照してください           | 0.26 |     | μs  |

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ       |                           | テスト条件           | 最小値   | 標準値 | 最大値 | 単位 |

|-------------|---------------------------|-----------------|-------|-----|-----|----|

| $t_{SUSTA}$ | 反復開始条件のセットアップ時間           | 図 6-1 を参照してください | 0.26  |     |     | μs |

| $t_{HDDAT}$ | データホールド時間                 | 図 6-1 を参照してください | 0.008 |     |     | μs |

| $t_{SUDAT}$ | データ セットアップ時間              | 図 6-1 を参照してください | 50    |     |     | ns |

| $t_R$       | SDA 信号と SCL 信号の両方の立ち上がり時間 | 図 6-1 を参照してください |       |     | 120 | ns |

| $t_F$       | SDA 信号と SCL 信号の両方の立ち下がり時間 | 図 6-1 を参照してください | 1.2   |     | 120 | ns |

| $t_{SUSTO}$ | 停止条件のセットアップ時間             | 図 6-1 を参照してください | 0.26  |     |     | μs |

| $C_b$       | 各バス ラインの容量性負荷             |                 |       |     | 150 | pF |

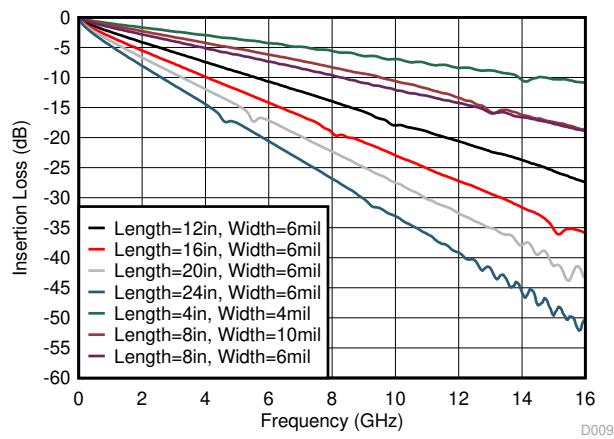

## 5.10 代表的特性

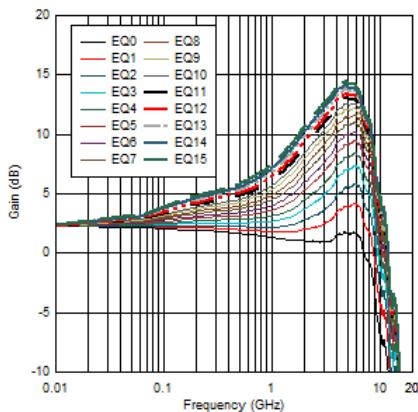

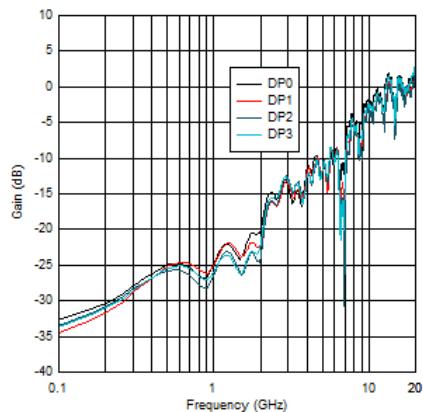

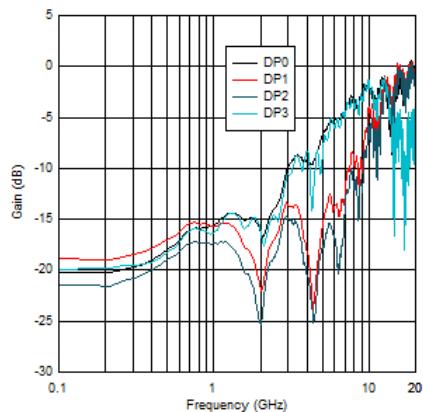

図 5-1. DisplayPort EQ 設定曲線

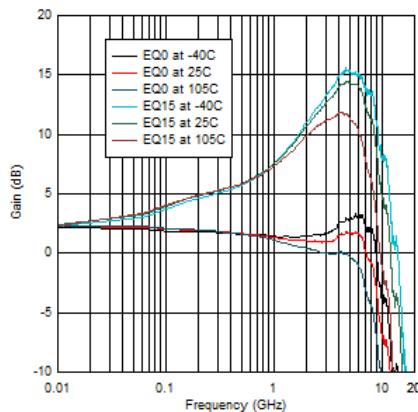

図 5-2. 温度範囲全体にわたる DisplayPort EQ 設定曲線

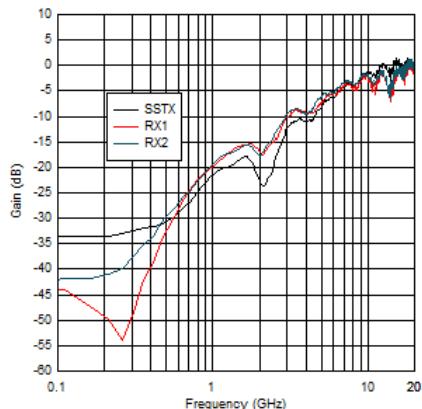

図 5-3. USB RX1 EQ 設定曲線

図 5-4. 全温度範囲にわたる USB RX1 EQ 設定曲線

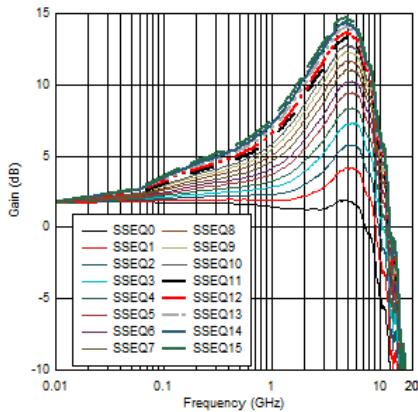

図 5-5. USB SSTX EQ 設定曲線

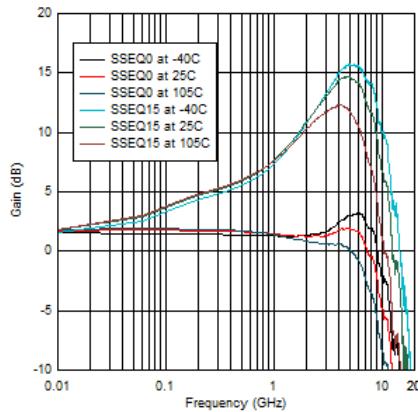

図 5-6. 温度範囲全体にわたる USB SSTX EQ 設定曲線

## 5.10 代表的特性 (続き)

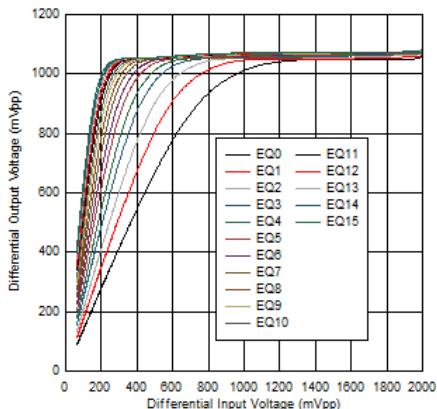

図 5-7. 4.05GHz での DisplayPort 直線性曲線

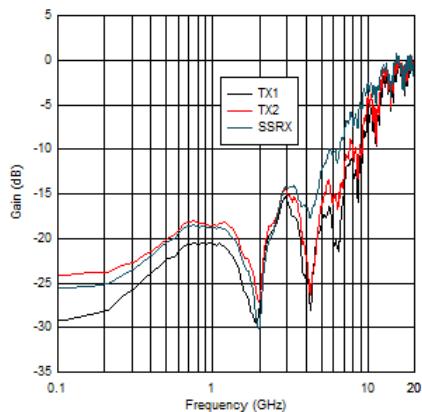

図 5-8. USB 入力のリターン ロス性能

図 5-9. DisplayPort 入力のリターン ロス性能

図 5-10. USB 出力のリターン ロス性能

図 5-11. DisplayPort 出力のリターン ロス性能

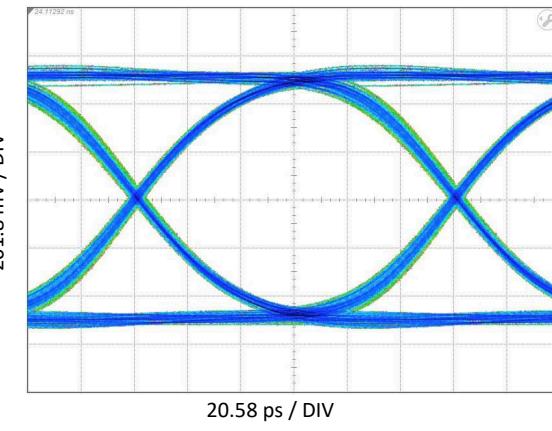

図 5-12. 8.1Gbps での 12 インチ入力 PCB トレースによる

DisplayPort HBR3 のアイパターン性能

## 5.10 代表的特性 (続き)

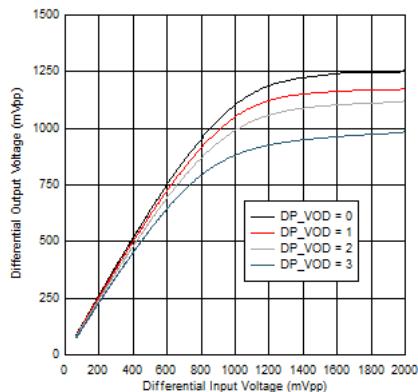

図 5-13. 100MHz での DP VOD 直線性設定

図 5-14. 5GHz での DP VOD 直線性設定

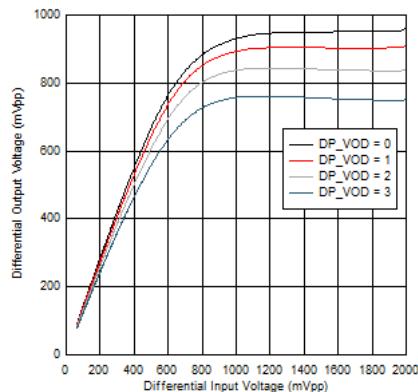

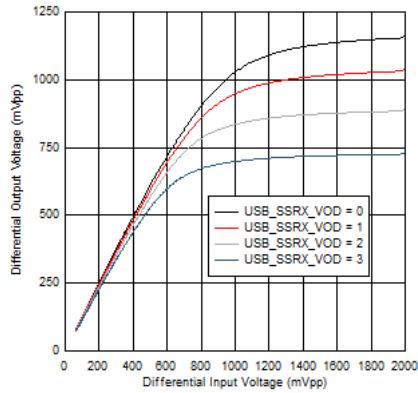

図 5-15. 100MHz での USB SSRX VOD 直線性設定

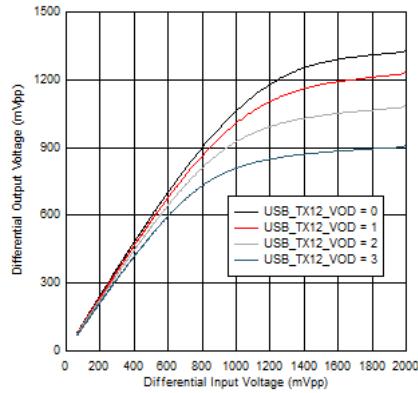

図 5-16. 100MHz での USB TX1 VOD 直線性設定

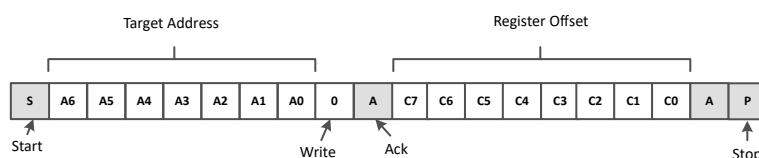

## パラメータ測定情報

図 6-1. I<sup>2</sup>C のタイミング図の定義

図 6-2. GPIO モードでの USB から 4 レーン DisplayPort

図 6-3. 伝搬遅延

図 6-4. 電気的アイドル モードの終了および開始遅延

図 6-5. 出力の立ち上がりおよび立ち下り時間

Copyright © 2017, Texas Instruments Incorporated

図 6-6. AUX から SBU へのスイッチ オンのタイミング図

図 6-7. AUX から SBU へのスイッチ オフのタイミング図

図 6-8. SSRX 制限ディエンファシスのみ

図 6-9. SSRX 制限プリシュートのみ

図 6-10. パワーオンタイミング

## 6 詳細説明

### 6.1 概要

TUSB5461-Q1 は、USB Type-C 経由の VESA DisplayPort Alt モードに対応したリドライバ スイッチであり、下流側ポートにおいて最大 8.1Gbps の DisplayPort データレートをサポートします。このデバイスは、第 5 世代の USB リドライバ テクノロジー と、DFP レシーバにおける適応型イコライゼーション機能 を採用しています。本デバイスは、USB Type-C 経由の VESA DisplayPort Alt モードにおける DFP 構成 C, D、および E に使用されます。

TUSB5461-Q1 は、USB 3.2 または DisplayPort 2.1 の信号が PCB やケーブルを通過する際に発生するシンボル間干渉 (ISI) によるケーブルおよび基板配線損失を補償するために、複数レベルの受信イコライゼーションを提供します。TUSB5461-Q1 は 3.3V 電源で動作し、車載グレード 2 の温度範囲に対応しています。

ホスト アプリケーションにおいて、TUSB5461-Q1 は USB 3.2 および DisplayPort バージョン 2.1 のトラスマッタのコンプライアンス テストおよびレシーバ ビジッタ耐性 テストの両方にシステムが合格することを可能にします。このリドライバは、チャネル損失を補償するイコライゼーションを適用して受信データを補正し、高い差動電圧で信号を出力します。各チャネルには、ゲイン設定を選択できるレシーバ イコライザーが搭載されています。TUSB5461-Q1 レシーバ前の挿入損失量に基づいてイコライゼーションを設定します。各チャネルのイコライゼーションは、EQ[1:0], SSEQ[1:0], DPEQ[1:0] ピンを使用して個別に制御できます。

TUSB5461-Q1 の高度ステートマシンにより、このデバイスはホストおよびデバイスに対して透過的に動作します。電源投入後、TUSB5461-Q1 は TX ペアでレシーバ検出を定期的に実行します。デバイスが USB 3.2 レシーバを検出すると、RX 終端がイネーブルになり、TUSB5461-Q1 をリドライブする準備ができます。

このデバイスの超低消費電力アキテクチャは、3.3V の電源で動作し、性能向上を実現しています。自動的な LFPS ディエンファシス制御により、システムはさらに USB3.2 に準拠できます。

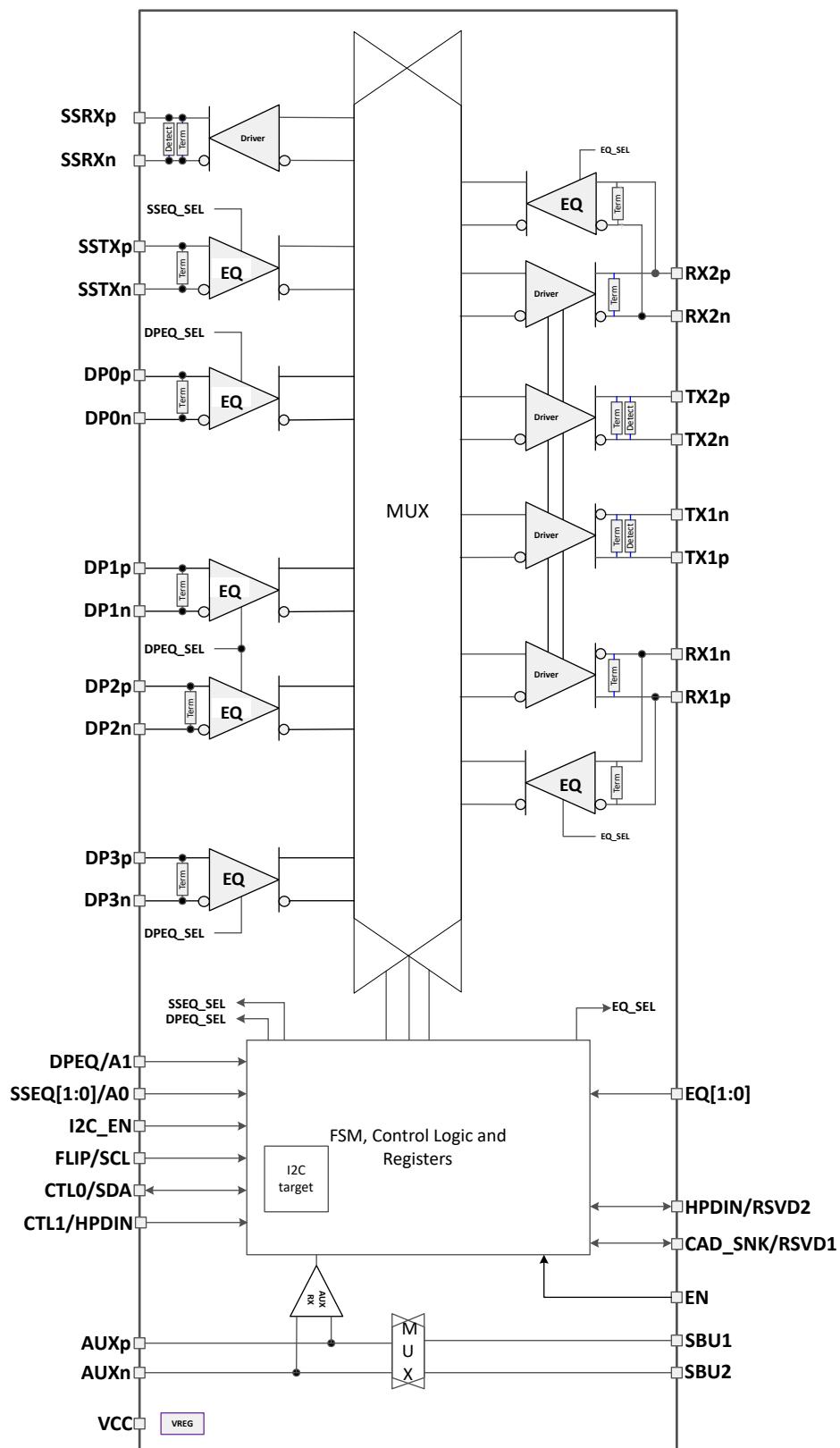

## 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 USB 3.2

TUSB5461-Q1 は、最大 5Gbps の USB 3.2 データレートに対応しています。TUSB5461-Q1 は、USB で定義されたすべての電力状態(U0、U1、U2、U3)をサポートしています。TUSB5461-Q1 は、リニアリドライバであるため、デバイスは USB3.2 物理層トラフィックをデコードできません。TUSB5461-Q1 は、レシーバ終端、電気的アイドル、LFPS、および SuperSpeed 信号レートなどの実際の物理層の状態を監視し、USB 3.2 インターフェイスの USB 電力状態を判別します。

TUSB5461-Q1 は、インテリジェントな低周波数周期信号(LFPS)検出器を備えています。LFPS 検出器は低周波信号を自動的に検出し、レシーバのイコライゼーション機能を無効にします。LFPS を受信していない場合、TUSB5461-Q1 は EQ[1:0] ピンおよび SSEQ[1:0] ピン、または EQ1\_SEL、EQ2\_SEL、SEQ\_SEL レジスタに設定された値に基づいてレシーバイコライゼーションを有効にします。

### 6.3.2 ディスプレイポート

TUSB5461-Q1 は、最大 8.1Gbps のデータ速度で最大 4 つの DisplayPort レーンをサポートします。TUSB5461-Q1 は、DisplayPort モードに設定されている場合、DisplayPort ソースと DisplayPort シンク間を通過するネイティブ AUX トラフィックを監視します。消費電力を低減するために、TUSB5461-Q1 は AUX トランザクションの内容に基づいてアクティブな DisplayPort レーン数を管理します。TUSB5461-Q1 は、DisplayPort シンクの DPCD レジスタ 0x00101 (LANE\_COUNT\_SET) および 0x00600 (SET\_POWER\_STATE) へのネイティブ AUX 書き込みをスヌープします。TUSB5461-Q1 は、LANE\_COUNT\_SET に書き込まれた値に基づいてレーンを無効化または有効化します。SET\_POWER\_STATE が D3 のとき、TUSB5461-Q1 はすべてのレーンを無効化します。それ以外の場合、アクティブなレーンは LANE\_COUNT\_SET の値に基づいています。

DisplayPort AUX スヌーピングは、デフォルトで有効になっていますが、AUX\_SNOOP\_DISABLE レジスタを変更することで無効化することもできます。AUX スヌープが無効化されている場合、TUSB5461-Q1 の DisplayPort レーンの管理は、各種構成レジスタを介して制御されます。TUSB5461-Q1 が GPIO モード(I2C\_EN = "0")で有効になっている場合、CAD\_SNK ピンを使用して AUX スヌープを無効にすることができます。CAD\_SNK ピンが High の場合、AUX スヌープ機能は無効になり、4 本すべての DisplayPort レーンがアクティブになります。

### 6.3.3 4 レベル入力

TUSB5461-Q1 には、イコライゼーションゲインを制御し、TUSB5461-Q1 をさまざまな動作モードに設定するための 4 レベル入力ピン(I2C\_EN、EQ[1:0]、DPEQ[1:0]、SSEQ[1:0])があります。これらの 4 レベル入力は、抵抗分圧回路を使用して 4 つの有効なレベルを設定し、より広範な制御設定を可能にします。内部プルアップ抵抗およびプルダウン抵抗が実装されています。これらの内部抵抗は、外部抵抗と組み合わせることで、所定の電圧レベルを実現します。

表 6-1. 4 レベル制御ピンの設定

| レベル | 設定                            |

|-----|-------------------------------|

| 0   | 1KΩ(許容誤差 5%)の抵抗を GND に接続します。  |

| R   | 20KΩ(許容誤差 5%)の抵抗を GND に接続します。 |

| F   | フロート(ピンはオープンのままにする)           |

| 1   | 1KΩ 5% を V <sub>CC</sub> に接続。 |

#### 注

すべての 4 レベル入力は、内部リセットの立ち上がりエッジ後にラッチされます。 $t_{cfg\_hd}$  の後、消費電力を削減するため、内部プルアップおよびプルダウン抵抗を絶縁します。

### 6.3.4 レシーバのリニアイコライゼーション

レシーバのイコライゼーションは、TUSB5461-Q1 の入力前にシステムでのチャネル挿入損失とシンボル間干渉を補償することを目的としています。レシーバは、高周波成分を基準として信号の低周波数成分を減衰させることで、これらの損失を克服します。TUSB5461-Q1 レシーバの入力前のチャネル挿入損失に対応するように、適切なゲイン設定を選択します。2 本の 4 レベル入力ピンにより、最大 16 件のイコライゼーション設定が可能です。USB3.2 上流パス、USB3.2 下流パス、および DisplayPort には、それぞれ 2 つの 4 レベル入力があります。TUSB5461-Q1 は、I<sup>2</sup>C レジスタを介して設定を調整できる柔軟性も備えています。

TUSB5461-Q1 は、USB-C 下流側ポートのレシーバ(RX1 および RX2)向けに、3 種類のイコライザ機能を実装しています: 固定 EQ、高速アダプティブ EQ(Fast AEQ)、およびフルアダプティブ EQ(Full AEQ)。デフォルトの操作は固定 EQ です。固定 EQ 動作では、USB-C レセプタクルに接続されるすべてのデバイス(ケーブルの有無を問わず)に対して、単一の設定が使用されます。高速 AEQ 機能は、短いチャネルと長いチャネルを区別できます。短いチャネルは、ケーブルなしで USB-C レセプタクルに直接接続する USB 3.2 デバイスの低損失の使用事例を表しています。長いチャネルは、USB ケーブル経由でレセプタクルに接続する USB 3.2 デバイスの損失の大きい使用事例です。高速 AEQ モードでは、TUSB5461-Q1 がチャネルの長さ(ショートまたはロング)に基づいて、あらかじめ決められた 2 つの設定のいずれかを選択します。TUSB5461-Q1 がフル AEQ に設定されている場合、TUSB5461-Q1 は USB デバイスが USB-C レセプタクルに接続されるたびに、最適なイコライゼーション設定を自動的に判定します。フル AEQ モードでは、TUSB5461-Q1 はチャネルが短い、長い、またはその中間であっても、常に最適な設定を判定します。フル AEQ 機能はデフォルトで無効になっていますが、レジスタを介して有効にできます。

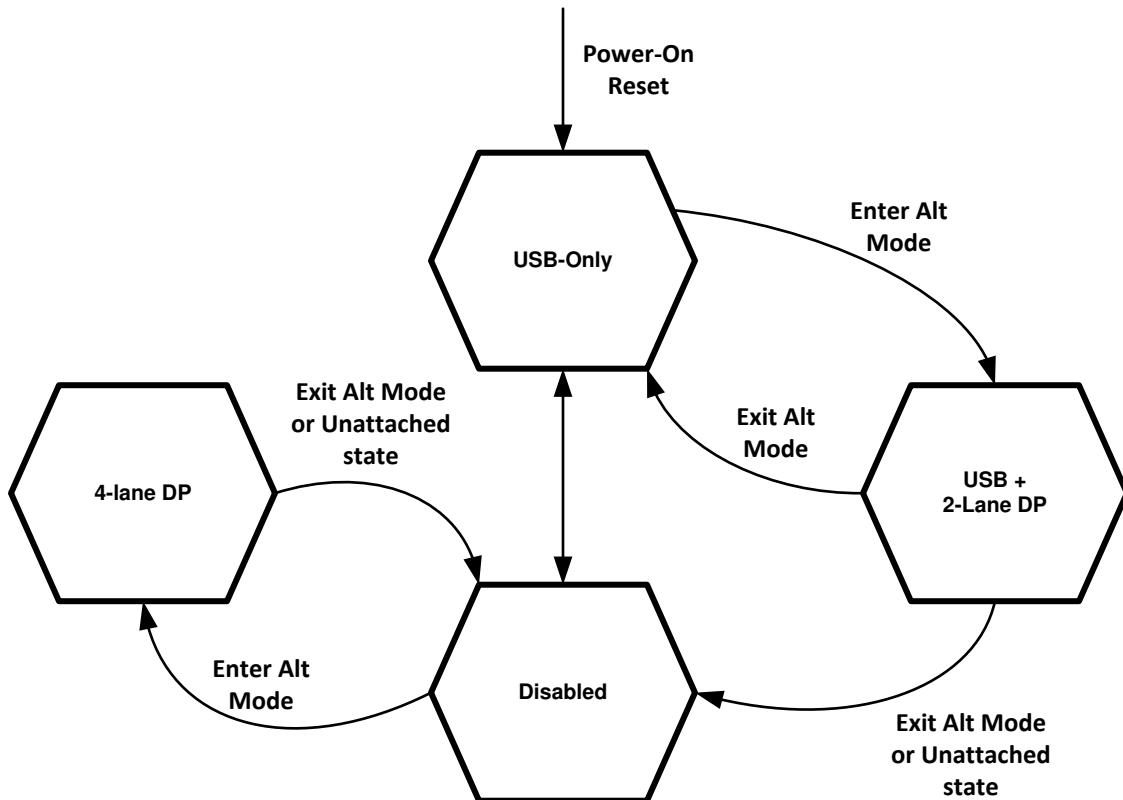

## 6.4 デバイスの機能モード

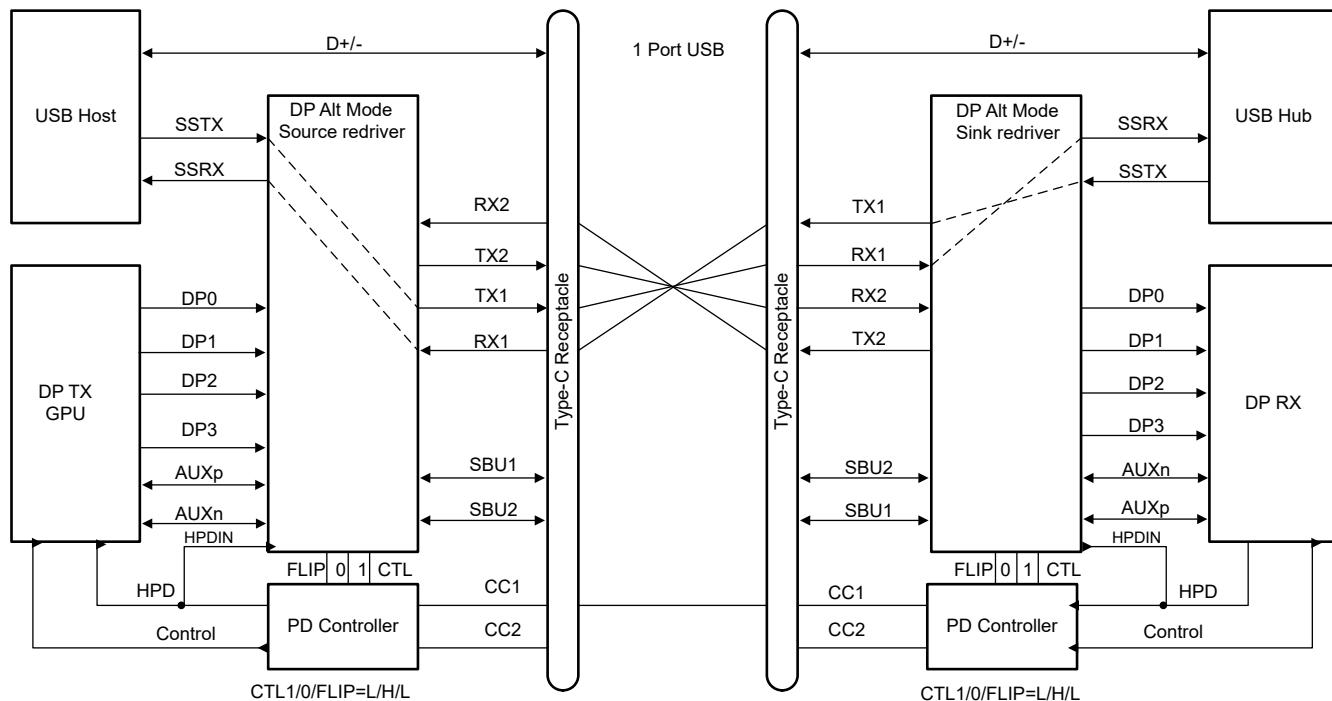

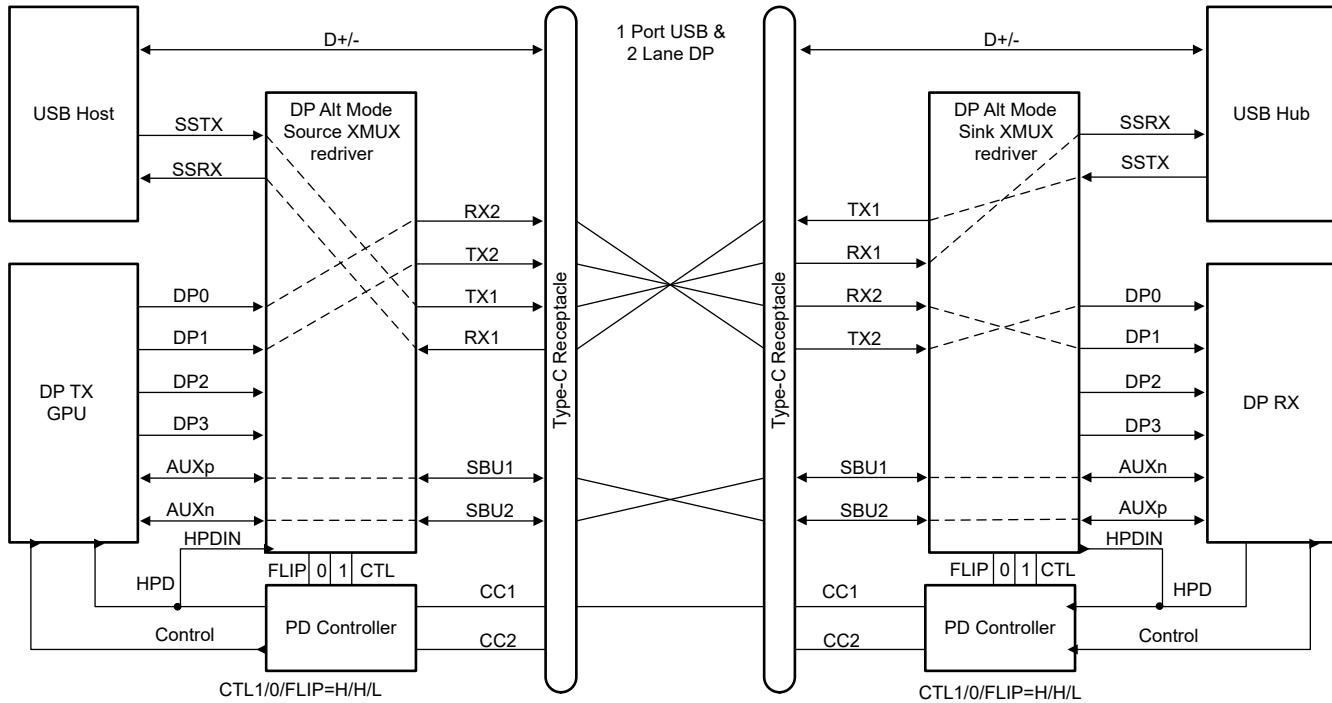

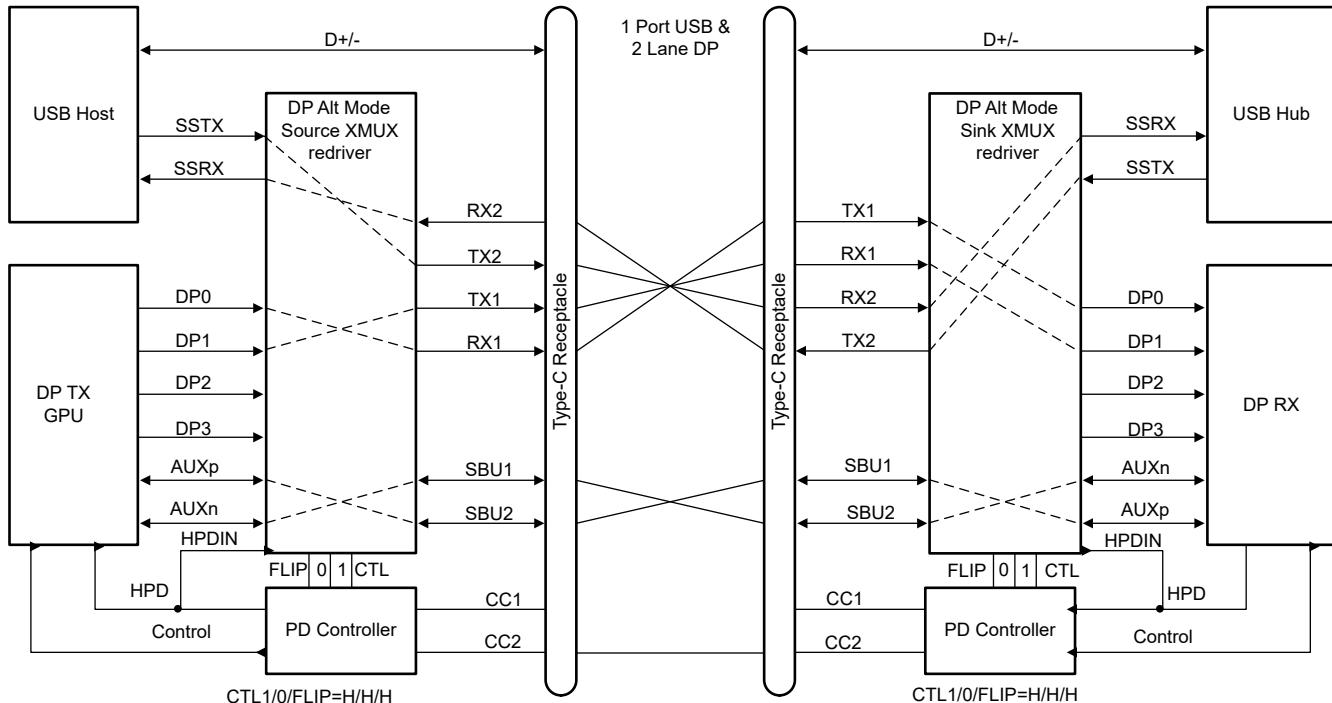

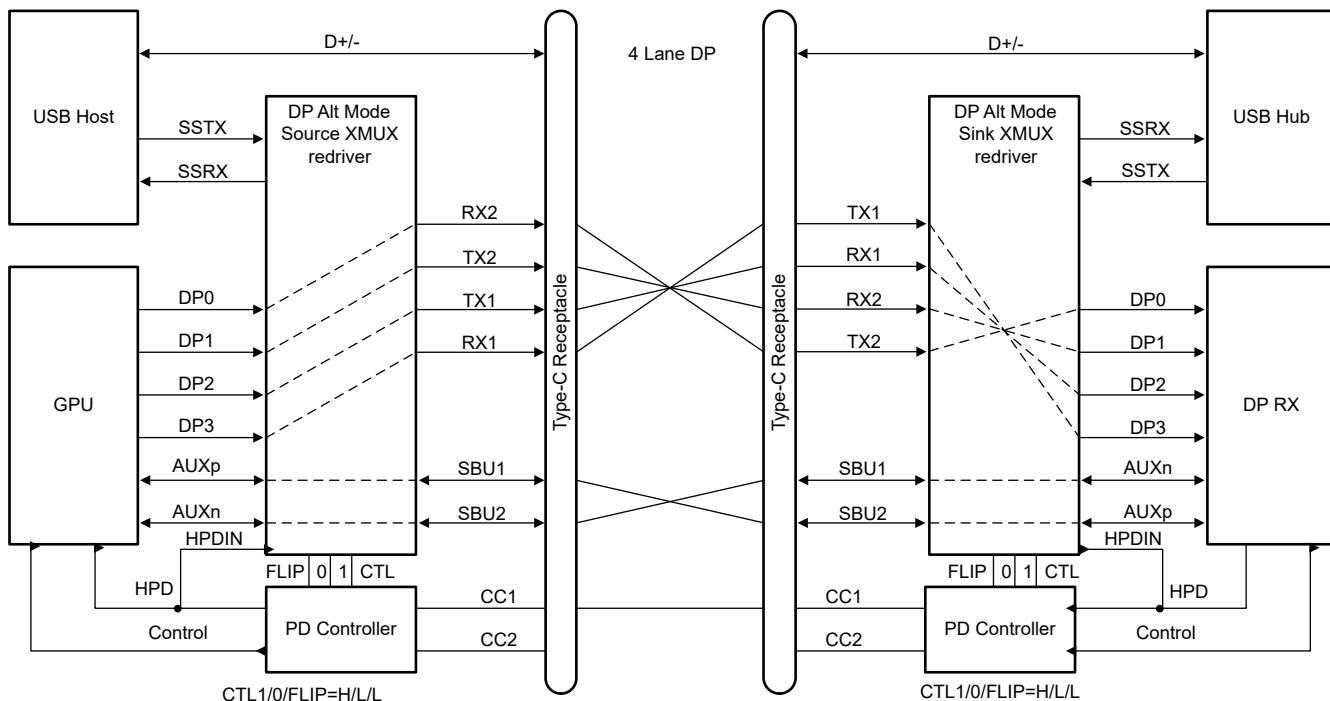

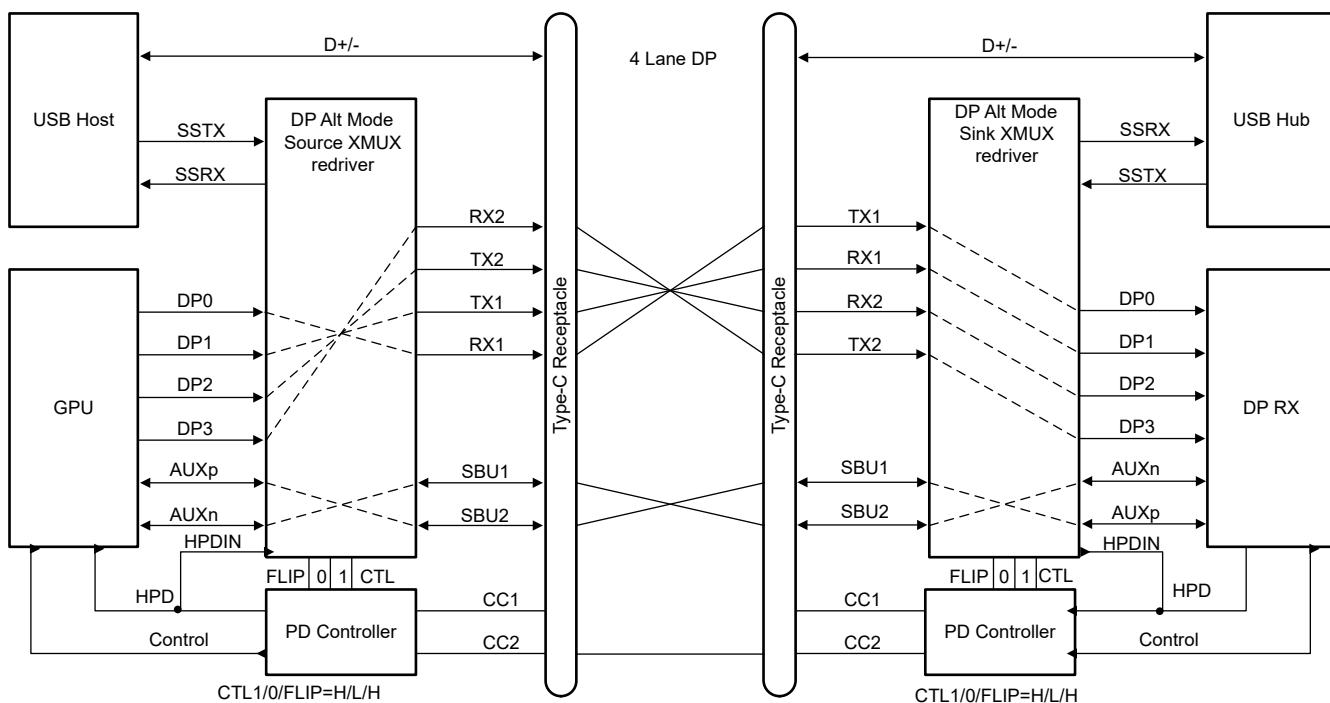

### 6.4.1 GPIO モードでのデバイス構成

I<sub>2</sub>C\_EN が “0” の場合、または I<sub>2</sub>C\_EN が “F” かつ (EQ0 が “0” かつ EQ1 が “0” ではない) 場合、TUSB5461-Q1 は GPIO 構成になります。TUSB5461-Q1 は、次の構成をサポートしています: USB 3.2 のみ、2 レーンの DisplayPort + USB 3.2、または 4 レーンの DisplayPort(USB 3.2 なし)。CTL1 ピンは、DisplayPort を有効にするかどうかを制御します。CTL1 と CTL0 の組み合わせによって、USB 3.2 のみ、2 レーンの DisplayPort、または 4 レーンの DisplayPort が選択されます(詳細は [表 6-2](#) を参照)。[表 6-3](#) に基づいて、AUXp および AUXn と SBU1 または SBU2 とのマッピングが制御されます。

電源投入後(V<sub>CC</sub> を 0V から 3.3V に)、TUSB5461-Q1 はデフォルトで USB3.2 モードになります。USB PD コントローラは、Type-C ポートにデバイスが接続されていないことを検出した場合、または接続されたデバイスによって USB3.2 動作が不要と判断された場合に、CTL0 ピンを Low から High、再び Low に遷移させることで、TUSB5461-Q1 を USB3.2 モードから解除する必要があります。

**表 6-2. GPIO 構成制御**

| CTL1 ピン | CTL0 ピン | FLIP ピン | TUSB5461-Q1 構成                               | VESA DisplayPort ALT モード DFP_D 設定 |

|---------|---------|---------|----------------------------------------------|-----------------------------------|

| L       | L       | L       | パワーダウン                                       | —                                 |

| L       | L       | H       | パワーダウン                                       | —                                 |

| L       | H       | L       | 1 ポート USB 3.2 — フリップ機能なし                     | —                                 |

| L       | H       | H       | 1 ポート USB 3.2 — フリップ機能あり                     | —                                 |

| H       | L       | L       | 4 レーン DP — フリップ機能なし                          | C と E                             |

| H       | L       | H       | 4 レーン DP — フリップ機能あり                          | C と E                             |

| H       | H       | L       | 1 ポート USB 3.2 + 2 レーン DisplayPort — フリップ機能なし | D                                 |

| H       | H       | H       | 1 ポート USB 3.2 + 2 レーン DisplayPort — フリップ機能あり | D                                 |

**表 6-3. GPIO による AUXp/AUXn と SBU1/SBU2 のマッピング**

| CTL1 ピン | FLIP ピン | マッピング                      |

|---------|---------|----------------------------|

| H       | L       | AUXp → SBU1<br>AUXn → SBU2 |

| H       | H       | AUXp → SBU2<br>AUXn → SBU1 |

| L > 2ms | X       | オープン                       |

表 6-4 は、TUSB5461-Q1 デバイスの MUX ルーティングを示しています。この表は、I<sup>2</sup>C と GPIO の両方の構成モードに有効です。

**表 6-4. 入力から出力へのマッピング**

| <b>CTL1 ピン</b> | <b>CTL0 ピン</b> | <b>FLIP ピン</b> | <b>送信元</b>  | <b>送信先</b>  |

|----------------|----------------|----------------|-------------|-------------|

|                |                |                | <b>入力ピン</b> | <b>出力ピン</b> |

| L              | L              | L              | 該当なし        | 該当なし        |

| L              | L              | H              | 該当なし        | 該当なし        |

| L              | H              | L              | RX1P        | SSRXP       |

|                |                |                | RX1N        | SSRXN       |

|                |                |                | SSTXP       | TX1P        |

|                |                |                | SSTXN       | TX1N        |

| L              | H              | H              | RX2P        | SSRXP       |

|                |                |                | RX2N        | SSRXN       |

|                |                |                | SSTXP       | TX2P        |

|                |                |                | SSTXN       | TX2P        |

| H              | L              | L              | DP0P        | RX2P        |

|                |                |                | DP0N        | RX2N        |

|                |                |                | DP1P        | TX2P        |

|                |                |                | DP1N        | TX2N        |

|                |                |                | DP2P        | TX1P        |

|                |                |                | DP2N        | TX1N        |

|                |                |                | DP3P        | RX1P        |

|                |                |                | DP3N        | RX1N        |

| H              | L              | H              | DP0P        | RX1P        |

|                |                |                | DP0N        | RX1N        |

|                |                |                | DP1P        | TX1P        |

|                |                |                | DP1N        | TX1N        |

|                |                |                | DP2P        | TX2P        |

|                |                |                | DP2N        | TX2N        |

|                |                |                | DP3P        | RX2P        |

|                |                |                | DP3N        | RX2N        |

| H              | H              | L              | RX1P        | SSRXP       |

|                |                |                | RX1N        | SSRXN       |

|                |                |                | SSTXP       | TX1P        |

|                |                |                | SSTXN       | TX1N        |

|                |                |                | DP0P        | RX2P        |

|                |                |                | DP0N        | RX2N        |

|                |                |                | DP1P        | TX2P        |

|                |                |                | DP1N        | TX2N        |

| H              | H              | H              | RX2P        | SSRXP       |

|                |                |                | RX2N        | SSRXN       |

|                |                |                | SSTXP       | TX2P        |

|                |                |                | SSTXN       | TX2N        |

|                |                |                | DP0P        | RX1P        |

|                |                |                | DP0N        | RX1N        |

|                |                |                | DP1P        | TX1P        |

|                |                |                | DP1N        | TX1N        |

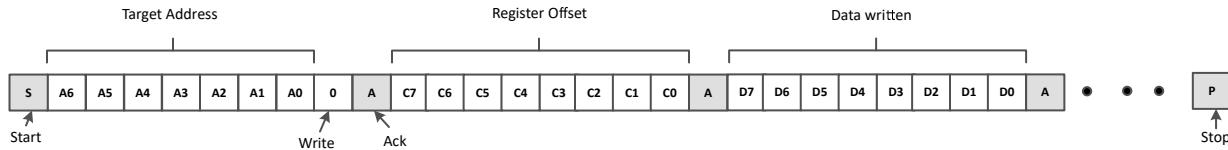

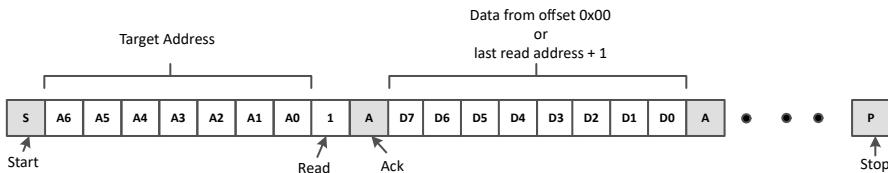

#### 6.4.2 I<sup>2</sup>C プログラミングによるデバイス構成

TUSB5461-Q1 は、I<sup>2</sup>C\_EN が “0” でない場合、または I<sup>2</sup>C\_EN が “F” かつ EQ0 が “0” かつ EQ1 が “0” の場合に I<sup>2</sup>C モードになります。GPIO モードで定義されているのと同じ構成が、I<sup>2</sup>C モードでも使用できます。TUSB5461-Q1 の USB 3.2 および DisplayPort の構成は、表 6-5 に基づいて制御されます。表 6-6 に基づいて、AUXp および AUXn と SBU1 または SBU2 とのマッピングが制御されます。

表 6-5. I<sup>2</sup>C コントローラ制御

| レジスタ    |         |         | TUSB5461-Q1 構成                               | VESA DisplayPort ALT モード DFP_D 設定 |

|---------|---------|---------|----------------------------------------------|-----------------------------------|

| CTLSEL1 | CTLSEL0 | FLIPSEL |                                              |                                   |

| 0       | 0       | 0       | パワーダウン                                       | —                                 |

| 0       | 0       | 1       | パワーダウン                                       | —                                 |

| 0       | 1       | 0       | 1 ポート USB 3.2 — フリップ機能なし                     | —                                 |

| 0       | 1       | 1       | 1 ポート USB 3.2 — フリップ機能あり                     | —                                 |

| 1       | 0       | 0       | 4 レーン DP — フリップ機能なし                          | C と E                             |

| 1       | 0       | 1       | 4 レーン DP — フリップ機能あり                          | C と E                             |

| 1       | 1       | 0       | 1 ポート USB 3.2 + 2 レーン DisplayPort — フリップ機能なし | D                                 |

| 1       | 1       | 1       | 1 ポート USB 3.2 + 2 レーン DisplayPort — フリップ機能あり | D                                 |

表 6-6. I<sup>2</sup>C による AUXp/AUXn と SBU1/SBU2 のマッピング

| レジスタ         |              |         |         | マッピング                      |

|--------------|--------------|---------|---------|----------------------------|

| AUX_SBU_OVR1 | AUX_SBU_OVR0 | CTLSEL1 | FLIPSEL |                            |

| 0            | 0            | 1       | 0       | AUXp → SBU1<br>AUXn → SBU2 |

| 0            | 0            | 1       | 1       | AUXp → SBU2<br>AUXn → SBU1 |

| 0            | 0            | 0       | X       | オープン                       |

| 0            | 1            | X       | X       | AUXp → SBU1<br>AUXn → SBU2 |

| 1            | 0            | X       | X       | AUXp → SBU2<br>AUXn → SBU1 |

| 1            | 1            | X       | X       | オープン                       |

#### 6.4.3 DisplayPort モード

TUSB5461-Q1 は、最大 8.1Gbps のデータ速度で最大 4 つの DisplayPort レーンをサポートします。TUSB5461-Q1 は、GPIO 制御または I<sup>2</sup>C レジスタ制御により DisplayPort で有効化できます。I<sup>2</sup>C\_EN が「0」の場合、DisplayPort は表 6-2 に基づいて制御されます。GPIO モードでない場合、DisplayPort 機能の有効化は I<sup>2</sup>C レジスタにより制御されます。

#### 6.4.4 直線性 EQ の構成

各 TUSB5461-Q1 レシーバ レーンは、レシーバのイコライゼーションのために独立して制御します。レシーバのイコライゼーション ゲイン値は、I<sup>2</sup>C レジスタと GPIO のどちらかにより制御可能です。表 6-7 は、TUSB5461-Q1 が GPIO モードのときに利用可能な各組み合わせに対するゲイン値を示しています。これらと同じオプションは、I<sup>2</sup>C モードでも利用可能であり、レジスタ DP0EQ\_SEL、DP1EQ\_SEL、DP2EQ\_SEL、DP3EQ\_SEL、EQ1\_SEL、EQ2\_SEL、および SSEQ\_SEL を更新することで設定できます。

**表 6-7. USB 下流側ポート レシーバ (RX1 および RX2 ピン) のイコライゼーション制御**

| レジスタ:EQ1_SEL または<br>EQ2_SEL<br>イコライゼーション設定# | EQ1 ピン レベル | EQ0 ピン レベル | EQ ゲイン 2.5(GHz)から 100MHz<br>でのゲインを引いた値<br>(dB) |

|---------------------------------------------|------------|------------|------------------------------------------------|

| 0                                           | 0          | 0          | -1.0                                           |

| 1                                           | 0          | R          | 0.0                                            |

| 2                                           | 0          | F          | 0.9                                            |

| 3                                           | 0          | 1          | 1.8                                            |

| 4                                           | R          | 0          | 2.6                                            |

| 5                                           | R          | R          | 3.4                                            |

| 6                                           | R          | F          | 4.0                                            |

| 7                                           | R          | 1          | 4.6                                            |

| 8                                           | F          | 0          | 5.2                                            |

| 9                                           | F          | R          | 5.7                                            |

| 10                                          | F          | F          | 6.1                                            |